2.6.38.4内核CMOS摄像头移植移植成功

MTK+移植camera说明

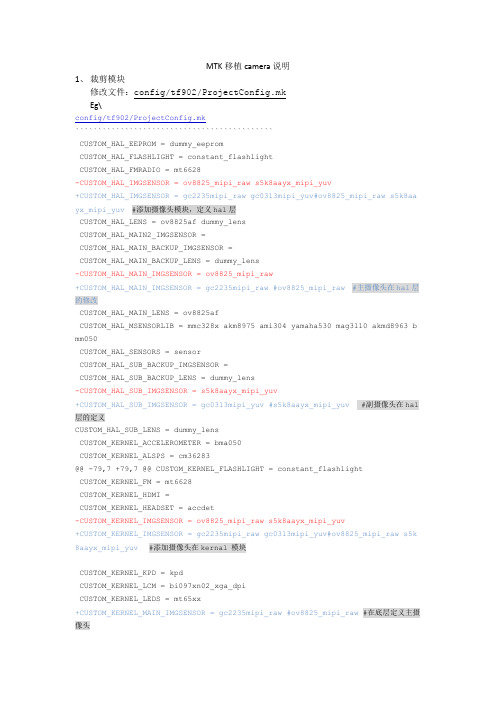

MTK移植camera说明1、裁剪模块修改文件:config/tf902/ProjectConfig.mkEg\config/tf902/ProjectConfig.mk````````````````````````````````````````````CUSTOM_HAL_EEPROM = dummy_eepromCUSTOM_HAL_FLASHLIGHT = constant_flashlightCUSTOM_HAL_FMRADIO = mt6628-CUSTOM_HAL_IMGSENSOR = ov8825_mipi_raw s5k8aayx_mipi_yuv+CUSTOM_HAL_IMGSENSOR = gc2235mipi_raw gc0313mipi_yuv#ov8825_mipi_raw s5k8aa yx_mipi_yuv #添加摄像头模块,定义hal层CUSTOM_HAL_LENS = ov8825af dummy_lensCUSTOM_HAL_MAIN2_IMGSENSOR =CUSTOM_HAL_MAIN_BACKUP_IMGSENSOR =CUSTOM_HAL_MAIN_BACKUP_LENS = dummy_lens-CUSTOM_HAL_MAIN_IMGSENSOR = ov8825_mipi_raw+CUSTOM_HAL_MAIN_IMGSENSOR = gc2235mipi_raw #ov8825_mipi_raw #主摄像头在hal层的修改CUSTOM_HAL_MAIN_LENS = ov8825afCUSTOM_HAL_MSENSORLIB = mmc328x akm8975 ami304 yamaha530 mag3110 akmd8963 b mm050CUSTOM_HAL_SENSORS = sensorCUSTOM_HAL_SUB_BACKUP_IMGSENSOR =CUSTOM_HAL_SUB_BACKUP_LENS = dummy_lens-CUSTOM_HAL_SUB_IMGSENSOR = s5k8aayx_mipi_yuv+CUSTOM_HAL_SUB_IMGSENSOR = gc0313mipi_yuv #s5k8aayx_mipi_yuv #副摄像头在hal 层的定义CUSTOM_HAL_SUB_LENS = dummy_lensCUSTOM_KERNEL_ACCELEROMETER = bma050CUSTOM_KERNEL_ALSPS = cm36283@@ -79,7 +79,7 @@ CUSTOM_KERNEL_FLASHLIGHT = constant_flashlightCUSTOM_KERNEL_FM = mt6628CUSTOM_KERNEL_HDMI =CUSTOM_KERNEL_HEADSET = accdet-CUSTOM_KERNEL_IMGSENSOR = ov8825_mipi_raw s5k8aayx_mipi_yuv+CUSTOM_KERNEL_IMGSENSOR = gc2235mipi_raw gc0313mipi_yuv#ov8825_mipi_raw s5k 8aayx_mipi_yuv #添加摄像头在kernal 模块CUSTOM_KERNEL_KPD = kpdCUSTOM_KERNEL_LCM = bi097xn02_xga_dpiCUSTOM_KERNEL_LEDS = mt65xx+CUSTOM_KERNEL_MAIN_IMGSENSOR = gc2235mipi_raw #ov8825_mipi_raw #在底层定义主摄像头CUSTOM_KERNEL_MAIN_LENS = ov8825afCUSTOM_KERNEL_RTC = rtcCUSTOM_KERNEL_SOUND = amp_6320pmic_spkCUSTOM_KERNEL_SSW = ssw_genericCUSTOM_KERNEL_SUB_BACKUP_IMGSENSOR =CUSTOM_KERNEL_SUB_BACKUP_LENS = dummy_lens-CUSTOM_KERNEL_SUB_IMGSENSOR = s5k8aayx_mipi_yuv+CUSTOM_KERNEL_SUB_IMGSENSOR = gc0313mipi_yuv#s5k8aayx_mipi_yuv #在底层定义副摄像头CUSTOM_KERNEL_SUB_LENS = dummy_lensCUSTOM_KERNEL_TOUCHPANEL = GT82X #cy8ctma300 GT818B-fpgaCUSTOM_KERNEL_USB = mt6577上面的修改是在平台没有默认AF(自动对焦)的功能(mtk6517和mtk6577\mtk6572的平台没有默认AF功能),mtk6589的平台默认就支持AF功能。

松下 AG-HPX173MC 说明书

准备工作

电池 ..................................................................... 12 充电 ......................................................................... 12 安装和卸下电源 ................................................... 13 安装和卸下电池 ..................................................... 13 连接和断开电源线 ................................................. 13 调整手带 .............................................................. 14 连接背带 .............................................................. 14 拆卸和安装镜头罩 ................................................ 14 遥控 ..................................................................... 15 插入电池 ................................................................. 15 遥控设置 ................................................................. 15 开启/关闭摄像机 .................................................. 16 提示灯 .................................................................. 16 寻像器 .................................................................. 17 使用寻像器 ............................................................. 17 使用 LCD ................................................................ 18 加强轮廓 ................................................................. 18 调整显示屏显示 ..................................................... 19 调整背光灯 ............................................................. 20 按垂直和水平方向翻转图像 ................................. 20 在全画面和非全画面之间切换 ............................. 20 设置日历 .............................................................. 21

canon eos 450d 数位相机 说明书

目錄目錄目錄操作注意事項快速入門指南部件名稱部件名稱)部件名稱部件名稱部件名稱部件名稱為電池充電開啟電源32 3剩餘可拍攝數量安裝及移除鏡頭基本操作選單操作及設定1234561 23格式化記憶卡如下所示顯示選單螢幕或影像時,半按快門按鈕,您即可立即返回拍攝設定螢幕(左圖所示)。

按下<B>按鈕開啟或關閉螢幕。

當您戴太陽鏡注視觀景器時按下<B>按鈕關閉螢幕。

如靠近光管,液晶螢幕可能會自動關閉。

如發生這種情況,請避免靠近光關於自動亮度優化在基本拍攝區模式中,會啟用自動亮度優化以自動調整影像,從而獲得最佳亮度及對比度。

在創意拍攝區模式中亦會預設設定自動亮度優視乎場景而定,將主體向左或向右移動以平衡背景並獲得更好的視角。

模式下,半按快門按鈕對靜止主體對焦時然後完全按下快門按鈕拍攝相片。

對焦鎖定也可在其他基本拍攝區模式中使用(<5>運動除外拍攝竅門主體距離背景越遠越好。

主體距離背景越遠,背景看起來就會越模糊。

在簡單、深色的背景前,也可更突出主體。

使用遠攝鏡頭。

如有變焦鏡頭,請使用遠攝端使主體上半身覆蓋整個畫面。

必要時,拍攝竅門使用簡單背景。

簡單背景可使花朵等更加突出。

盡量靠近主體。

檢查鏡頭的最近對焦距離。

某些鏡頭上有<40.25m/0.8ft頭最近對焦距離是從相機上的<V> (焦平面)標記至主體的距離拍攝竅門使用遠攝鏡頭。

建議使用遠攝鏡頭,以便您從遠處拍攝。

使用中央自動對焦點進行對焦。

將中央自動對焦點覆蓋拍攝主體,然後半按快門按鈕進行對焦。

自動對焦時,相機會持續發出輕微的提示音。

如無法對焦,觀景器中的對。

FCC声明说明书

Federal Communications Commission (FCC) Statement (011898)This equipment has been tested and found to comply with the limits for a Class B digital device, pursuant to Part 15 of FCC Rules. These limits are designed to provide reasonable protection against harmful interference in a residential installation. This equipment generates, uses and can radiate radio frequency energy and, if not installed and used in accordance with instructions contained in this manual, may cause harmful interference to radio and television communications. However, there is no guarantee that interference will not occur in a particular installation.If this equipment does cause harmful interference to radio or television reception, which can be determined by turning the equipment off and on, the user is encouraged to try to correct the interference by one or more of the following measures:-REORIENT OR RELOCATE THE RECEIVING ANTENNA-INCREASE THE SEPARATION BETWEEN THE EQUIPMENT AND THE RECEIVER -CONNECT THE EQUIPMENT INTO AN OUTLET ON A CIRCUIT DIFFERENT FROM THAT OF THE RECEIVER-CONSULT THE DEALER OR AN EXPERIENCED AUDIO/TELEVISION TECHNICIANNOTE:Connecting this device to peripheral devices that do not comply with Class B requirements, or using an unshielded peripheral data cable, could also result in harmful interference to radio or television reception.The user is cautioned that any changes or modifications not expressly approved by the party responsible for compliance could void the user’s authority to operate this equipment.To ensure that the use of this product does not contribute to interference, it isnecessary to use shielded I/O cables.CopyrightThis manual is copyrighted with all rights reserved. No portion of this manual may be copied or reproduced by any means.While every precaution has been taken in the preparation of this manual, no responsibility for errors or omissions is assumed. Neither is any liability assumed for damages resulting from the use of the information contained herein.TrademarksAll brand names, logos and registered trademarks mentioned are property of their respective owners.Table of ContentsHARDWARE CONFIGURATION (3)Key Features (3)Motherboard Layout (5)Jumper Settings (6)CPU Speed Selection (6)SW1, SW2 - CPU Frequency Ratio (6)SW3 - VID[0:4] Code to Voltage Definition (7)J7 - CMOS Clear (8)J2 - On Board AC97 Codec Sound (8)Pin Assignment (9)HARDWARE SETUP (10)T o Install DIMMs (10)Installing a New Processor (11)To Install a Processor to ZIF Socket (11)Connect the processor Fan Connector (11)BIOS SETUP (12)Starting Setup (12)Main Menu (13)Standard CMOS Features (14)Advanced BIOS Features (16)Advanced Chipset Features (16)Integrated Peripherals (16)Power Management Setup (16)PnP/PCI Configurations (16)PC Health Status (16)Frequency/Voltage Control (16)Set Supervisor/User Password (16)Flash Update Procedure (18)APPENDIX (19)Select the Heatsink (19)Select the Power Supply (20)HARDWARE CONFIGURATIONKey Features:Chipset•VIA® KT133/KT133A Chipset.Processor•Full support for the AMD Duron TM and Athlon TM processors using Socket A.•Supports 100MHz & 133MHz (optional) bus speed including all processors using Socket A.VRM 9.0 (Voltage Regulator Modules) on Board•Flexible motherboard design with on board VRM 9.0.System Memory• A total of three 168-pin DIMM sockets (3.3V Synchronous DRAM).•Supports Synchronous DRAM PC100/PC133.•Memory size up to 1.5G bytes.•Supports SDRAM memory types.•Supports single-density DIMMs of 1MB, 2MB, 4MB, 8MB and 16MB depth (x64).•Supports double-density DIMMs of 2MB, 4MB, 8MB, 16MB and 32MB depth (x64).•Supports single & double sided DIMMs.•Banks of different DRAM types depths can be mixed.System BIOS•2MB flash BIOS supporting PnP, APM, ATAPI and Windows® 95.•Auto detects and supports LBA hard disks with capacities up to 8.4GB.•Full support of ACPI & DMI.•Easy to upgrade BIOS by end-user.Dual BIOS•As our dual BIOS use the awdflash ver.7.83 to flash the dual BIOS, so our dual BIOS support the flash type of the awdflash ver.7.83, such as Syncmos,ATMEL etc..•The normal boot sequence is from main BIOS. If one BIOS is fail to boot, you can press the ‘Reset’ button to boot from the other BIOS (Note: no every time issuccess, you can try it several times or touch button time is enough long, forexample 2~3 second).•If the BIOS error that contained in compressed part of BIOS bin file, our dual BIOS can know to automatic flash, but the boot block error can not know to flash, that is: If the BIOS bin file is damage, it will auto flash BIOS, and if the bin file is OKeven different with the board bin file, computer will boot normal without enter the flash screen). If the user want to flash the BIOS unconditionally, you can press the ‘Alt + F2’ key to flash another BIOS.On-board I/O•On board two PCI fast IDE ports supporting up to 4 ATA and Ultra DMA33/66/ 100 (optional) IDE devices.•Supports bus master IDE, PIO mode 4 (up to 16.6M bytes/sec) and Ultra DMA33/66/100 (optional) (up to 33/66/100M (optional) bytes/sec) transfer.•One ECP/EPP parallel port.•Two 16550-compatible UART serial ports.•One floppy port, supports two FDDs of 360KB, 720KB, 1.2MB, 1.44MB and 2.88MB capacity.•Four USB ports.•PS/2 mouse port.•PS/2 keyboard port.•Infrared (IrDA) is supported.•One Line/Speaker out, one Mic in, one Line in and MIDI/Game port (optional).Plug-and-Play•Supports plug-and-play specification 1.1.•Plug-and-play for DOS, Windows® 3.X, Windows® 95 as well as Windows® 98.•Fully steerable PCI interrupts.On-board AC97 Sound•Integrated AC97 controller with standard AC97 codec.•Direct Sound and Sound Blaster compatible.•Full-Duplex 16-bit record and playback.•PnP and APM 1.2 support.On-board Creative Sound (optional)•Creative ES1373 Audio controller.•128 voice wave table synthesizer.•DOS game compatibility.•PCI bus master for fast DMA.•Fully compliant with PC97 power management specification.(Note: If Creative PCI Sound is on board, only Primary AMR Card can be used. If Creative PCI Sound is enabled, Bus Master Device on one PCI cannot be used.)Power Management•Supports SMM, APM and ACPI.•Break switch for instant suspend/resume on system operations.•Energy star “Green PC” compliant .•WOL (Wake-On-Lan) Header support.•External Modem Ring-in Wake-up support.•Support auto setting or manual setting for CPU voltage.•Supports suspend-to-RAM (STR) (optional).Expansion Slots• 5 PCI bus master slots (Rev. 2.1 compliant).• 1 Audio Modem Riser (AMR) (optional).• 1 ISA slot (1 ISA slot share with 1 PCI slot).• 1 universal AGP slot (AGP 2.0 compliant - 4X mode support).CAUTIONStatic electricity can harm delicate components of the motherboard. To prevent damage caused by static electricity, discharge the static electricity from yourbody before you touch any of the computers electronic components.Motherboard LayoutThe following diagrams show the relative positions of the jumpers, connectors, major components and memory banks on the motherboard.# The AMR slot is optional.NOTE1)Be sure to check the cable orientation in order to match the colored strip tothe pin 1 end of the connector.2)When you start up the system, please wait for 5 seconds after you poweron AC.Jumper SettingsThis chapter explains how to configure the motherboard’s hardware. Before using your computer, make sure all jumpers and DRAM modules are set correctly. Refer to this chapter whenever in doubt.CPU Speed SelectionIn this motherboard, you can set the CPU speed by manual or auto way, but over clock isn’t recommended.SW1, SW2 - CPU Frequency RatioSW2[1:5]SW1[1:4] SW2[1:5] CPU FREQ1 2 3 4 5SW3 - VID[0:4] Code to Voltage DefinitionSW1(6) Off, Auto Setting SW1(6) On, Manual Setting。

MIPS芯片架构说明

MIPS32™ Architecture For Programmers Volume I: Introduction to the MIPS32™ArchitectureDocument Number: MD00082Revision 2.00June 8, 2003MIPS Technologies, Inc.1225 Charleston RoadMountain View, CA 94043-1353Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Copyright ©2001-2003 MIPS Technologies, Inc. All rights reserved.Unpublished rights (if any) reserved under the copyright laws of the United States of America and other countries.This document contains information that is proprietary to MIPS Technologies, Inc. ("MIPS Technologies"). Any copying,reproducing,modifying or use of this information(in whole or in part)that is not expressly permitted in writing by MIPS Technologies or an authorized third party is strictly prohibited. At a minimum, this information is protected under unfair competition and copyright laws. Violations thereof may result in criminal penalties and fines.Any document provided in source format(i.e.,in a modifiable form such as in FrameMaker or Microsoft Word format) is subject to use and distribution restrictions that are independent of and supplemental to any and all confidentiality restrictions. UNDER NO CIRCUMSTANCES MAY A DOCUMENT PROVIDED IN SOURCE FORMAT BE DISTRIBUTED TO A THIRD PARTY IN SOURCE FORMAT WITHOUT THE EXPRESS WRITTEN PERMISSION OF MIPS TECHNOLOGIES, INC.MIPS Technologies reserves the right to change the information contained in this document to improve function,design or otherwise.MIPS Technologies does not assume any liability arising out of the application or use of this information, or of any error or omission in such information. Any warranties, whether express, statutory, implied or otherwise, including but not limited to the implied warranties of merchantability orfitness for a particular purpose,are excluded. Except as expressly provided in any written license agreement from MIPS Technologies or an authorized third party,the furnishing of this document does not give recipient any license to any intellectual property rights,including any patent rights, that cover the information in this document.The information contained in this document shall not be exported or transferred for the purpose of reexporting in violation of any U.S. or non-U.S. regulation, treaty, Executive Order, law, statute, amendment or supplement thereto. The information contained in this document constitutes one or more of the following: commercial computer software, commercial computer software documentation or other commercial items.If the user of this information,or any related documentation of any kind,including related technical data or manuals,is an agency,department,or other entity of the United States government ("Government"), the use, duplication, reproduction, release, modification, disclosure, or transfer of this information, or any related documentation of any kind, is restricted in accordance with Federal Acquisition Regulation12.212for civilian agencies and Defense Federal Acquisition Regulation Supplement227.7202 for military agencies.The use of this information by the Government is further restricted in accordance with the terms of the license agreement(s) and/or applicable contract terms and conditions covering this information from MIPS Technologies or an authorized third party.MIPS,R3000,R4000,R5000and R10000are among the registered trademarks of MIPS Technologies,Inc.in the United States and other countries,and MIPS16,MIPS16e,MIPS32,MIPS64,MIPS-3D,MIPS-based,MIPS I,MIPS II,MIPS III,MIPS IV,MIPS V,MIPSsim,SmartMIPS,MIPS Technologies logo,4K,4Kc,4Km,4Kp,4KE,4KEc,4KEm,4KEp, 4KS, 4KSc, 4KSd, M4K, 5K, 5Kc, 5Kf, 20Kc, 25Kf, ASMACRO, ATLAS, At the Core of the User Experience., BusBridge, CoreFPGA, CoreLV, EC, JALGO, MALTA, MDMX, MGB, PDtrace, Pipeline, Pro, Pro Series, SEAD, SEAD-2, SOC-it and YAMON are among the trademarks of MIPS Technologies, Inc.All other trademarks referred to herein are the property of their respective owners.Template: B1.08, Built with tags: 2B ARCH MIPS32MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Table of ContentsChapter 1 About This Book (1)1.1 Typographical Conventions (1)1.1.1 Italic Text (1)1.1.2 Bold Text (1)1.1.3 Courier Text (1)1.2 UNPREDICTABLE and UNDEFINED (2)1.2.1 UNPREDICTABLE (2)1.2.2 UNDEFINED (2)1.3 Special Symbols in Pseudocode Notation (2)1.4 For More Information (4)Chapter 2 The MIPS Architecture: An Introduction (7)2.1 MIPS32 and MIPS64 Overview (7)2.1.1 Historical Perspective (7)2.1.2 Architectural Evolution (7)2.1.3 Architectural Changes Relative to the MIPS I through MIPS V Architectures (9)2.2 Compliance and Subsetting (9)2.3 Components of the MIPS Architecture (10)2.3.1 MIPS Instruction Set Architecture (ISA) (10)2.3.2 MIPS Privileged Resource Architecture (PRA) (10)2.3.3 MIPS Application Specific Extensions (ASEs) (10)2.3.4 MIPS User Defined Instructions (UDIs) (11)2.4 Architecture Versus Implementation (11)2.5 Relationship between the MIPS32 and MIPS64 Architectures (11)2.6 Instructions, Sorted by ISA (12)2.6.1 List of MIPS32 Instructions (12)2.6.2 List of MIPS64 Instructions (13)2.7 Pipeline Architecture (13)2.7.1 Pipeline Stages and Execution Rates (13)2.7.2 Parallel Pipeline (14)2.7.3 Superpipeline (14)2.7.4 Superscalar Pipeline (14)2.8 Load/Store Architecture (15)2.9 Programming Model (15)2.9.1 CPU Data Formats (16)2.9.2 FPU Data Formats (16)2.9.3 Coprocessors (CP0-CP3) (16)2.9.4 CPU Registers (16)2.9.5 FPU Registers (18)2.9.6 Byte Ordering and Endianness (21)2.9.7 Memory Access Types (25)2.9.8 Implementation-Specific Access Types (26)2.9.9 Cache Coherence Algorithms and Access Types (26)2.9.10 Mixing Access Types (26)Chapter 3 Application Specific Extensions (27)3.1 Description of ASEs (27)3.2 List of Application Specific Instructions (28)3.2.1 The MIPS16e Application Specific Extension to the MIPS32Architecture (28)3.2.2 The MDMX Application Specific Extension to the MIPS64 Architecture (28)3.2.3 The MIPS-3D Application Specific Extension to the MIPS64 Architecture (28)MIPS32™ Architecture For Programmers Volume I, Revision 2.00i Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.3.2.4 The SmartMIPS Application Specific Extension to the MIPS32 Architecture (28)Chapter 4 Overview of the CPU Instruction Set (29)4.1 CPU Instructions, Grouped By Function (29)4.1.1 CPU Load and Store Instructions (29)4.1.2 Computational Instructions (32)4.1.3 Jump and Branch Instructions (35)4.1.4 Miscellaneous Instructions (37)4.1.5 Coprocessor Instructions (40)4.2 CPU Instruction Formats (41)Chapter 5 Overview of the FPU Instruction Set (43)5.1 Binary Compatibility (43)5.2 Enabling the Floating Point Coprocessor (44)5.3 IEEE Standard 754 (44)5.4 FPU Data Types (44)5.4.1 Floating Point Formats (44)5.4.2 Fixed Point Formats (48)5.5 Floating Point Register Types (48)5.5.1 FPU Register Models (49)5.5.2 Binary Data Transfers (32-Bit and 64-Bit) (49)5.5.3 FPRs and Formatted Operand Layout (50)5.6 Floating Point Control Registers (FCRs) (50)5.6.1 Floating Point Implementation Register (FIR, CP1 Control Register 0) (51)5.6.2 Floating Point Control and Status Register (FCSR, CP1 Control Register 31) (53)5.6.3 Floating Point Condition Codes Register (FCCR, CP1 Control Register 25) (55)5.6.4 Floating Point Exceptions Register (FEXR, CP1 Control Register 26) (56)5.6.5 Floating Point Enables Register (FENR, CP1 Control Register 28) (56)5.7 Formats of Values Used in FP Registers (57)5.8 FPU Exceptions (58)5.8.1 Exception Conditions (59)5.9 FPU Instructions (62)5.9.1 Data Transfer Instructions (62)5.9.2 Arithmetic Instructions (63)5.9.3 Conversion Instructions (65)5.9.4 Formatted Operand-Value Move Instructions (66)5.9.5 Conditional Branch Instructions (67)5.9.6 Miscellaneous Instructions (68)5.10 Valid Operands for FPU Instructions (68)5.11 FPU Instruction Formats (70)5.11.1 Implementation Note (71)Appendix A Instruction Bit Encodings (75)A.1 Instruction Encodings and Instruction Classes (75)A.2 Instruction Bit Encoding Tables (75)A.3 Floating Point Unit Instruction Format Encodings (82)Appendix B Revision History (85)ii MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Figure 2-1: Relationship between the MIPS32 and MIPS64 Architectures (11)Figure 2-2: One-Deep Single-Completion Instruction Pipeline (13)Figure 2-3: Four-Deep Single-Completion Pipeline (14)Figure 2-4: Four-Deep Superpipeline (14)Figure 2-5: Four-Way Superscalar Pipeline (15)Figure 2-6: CPU Registers (18)Figure 2-7: FPU Registers for a 32-bit FPU (20)Figure 2-8: FPU Registers for a 64-bit FPU if Status FR is 1 (21)Figure 2-9: FPU Registers for a 64-bit FPU if Status FR is 0 (22)Figure 2-10: Big-Endian Byte Ordering (23)Figure 2-11: Little-Endian Byte Ordering (23)Figure 2-12: Big-Endian Data in Doubleword Format (24)Figure 2-13: Little-Endian Data in Doubleword Format (24)Figure 2-14: Big-Endian Misaligned Word Addressing (25)Figure 2-15: Little-Endian Misaligned Word Addressing (25)Figure 3-1: MIPS ISAs and ASEs (27)Figure 3-2: User-Mode MIPS ISAs and Optional ASEs (27)Figure 4-1: Immediate (I-Type) CPU Instruction Format (42)Figure 4-2: Jump (J-Type) CPU Instruction Format (42)Figure 4-3: Register (R-Type) CPU Instruction Format (42)Figure 5-1: Single-Precisions Floating Point Format (S) (45)Figure 5-2: Double-Precisions Floating Point Format (D) (45)Figure 5-3: Paired Single Floating Point Format (PS) (46)Figure 5-4: Word Fixed Point Format (W) (48)Figure 5-5: Longword Fixed Point Format (L) (48)Figure 5-6: FPU Word Load and Move-to Operations (49)Figure 5-7: FPU Doubleword Load and Move-to Operations (50)Figure 5-8: Single Floating Point or Word Fixed Point Operand in an FPR (50)Figure 5-9: Double Floating Point or Longword Fixed Point Operand in an FPR (50)Figure 5-10: Paired-Single Floating Point Operand in an FPR (50)Figure 5-11: FIR Register Format (51)Figure 5-12: FCSR Register Format (53)Figure 5-13: FCCR Register Format (55)Figure 5-14: FEXR Register Format (56)Figure 5-15: FENR Register Format (56)Figure 5-16: Effect of FPU Operations on the Format of Values Held in FPRs (58)Figure 5-17: I-Type (Immediate) FPU Instruction Format (71)Figure 5-18: R-Type (Register) FPU Instruction Format (71)Figure 5-19: Register-Immediate FPU Instruction Format (71)Figure 5-20: Condition Code, Immediate FPU Instruction Format (71)Figure 5-21: Formatted FPU Compare Instruction Format (71)Figure 5-22: FP RegisterMove, Conditional Instruction Format (71)Figure 5-23: Four-Register Formatted Arithmetic FPU Instruction Format (72)Figure 5-24: Register Index FPU Instruction Format (72)Figure 5-25: Register Index Hint FPU Instruction Format (72)Figure 5-26: Condition Code, Register Integer FPU Instruction Format (72)Figure A-1: Sample Bit Encoding Table (76)MIPS32™ Architecture For Programmers Volume I, Revision 2.00iii Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Table 1-1: Symbols Used in Instruction Operation Statements (2)Table 2-1: MIPS32 Instructions (12)Table 2-2: MIPS64 Instructions (13)Table 2-3: Unaligned Load and Store Instructions (24)Table 4-1: Load and Store Operations Using Register + Offset Addressing Mode (30)Table 4-2: Aligned CPU Load/Store Instructions (30)Table 4-3: Unaligned CPU Load and Store Instructions (31)Table 4-4: Atomic Update CPU Load and Store Instructions (31)Table 4-5: Coprocessor Load and Store Instructions (31)Table 4-6: FPU Load and Store Instructions Using Register+Register Addressing (32)Table 4-7: ALU Instructions With an Immediate Operand (33)Table 4-8: Three-Operand ALU Instructions (33)Table 4-9: Two-Operand ALU Instructions (34)Table 4-10: Shift Instructions (34)Table 4-11: Multiply/Divide Instructions (35)Table 4-12: Unconditional Jump Within a 256 Megabyte Region (36)Table 4-13: PC-Relative Conditional Branch Instructions Comparing Two Registers (36)Table 4-14: PC-Relative Conditional Branch Instructions Comparing With Zero (37)Table 4-15: Deprecated Branch Likely Instructions (37)Table 4-16: Serialization Instruction (38)Table 4-17: System Call and Breakpoint Instructions (38)Table 4-18: Trap-on-Condition Instructions Comparing Two Registers (38)Table 4-19: Trap-on-Condition Instructions Comparing an Immediate Value (38)Table 4-20: CPU Conditional Move Instructions (39)Table 4-21: Prefetch Instructions (39)Table 4-22: NOP Instructions (40)Table 4-23: Coprocessor Definition and Use in the MIPS Architecture (40)Table 4-24: CPU Instruction Format Fields (42)Table 5-1: Parameters of Floating Point Data Types (45)Table 5-2: Value of Single or Double Floating Point DataType Encoding (46)Table 5-3: Value Supplied When a New Quiet NaN Is Created (47)Table 5-4: FIR Register Field Descriptions (51)Table 5-5: FCSR Register Field Descriptions (53)Table 5-6: Cause, Enable, and Flag Bit Definitions (55)Table 5-7: Rounding Mode Definitions (55)Table 5-8: FCCR Register Field Descriptions (56)Table 5-9: FEXR Register Field Descriptions (56)Table 5-10: FENR Register Field Descriptions (57)Table 5-11: Default Result for IEEE Exceptions Not Trapped Precisely (60)Table 5-12: FPU Data Transfer Instructions (62)Table 5-13: FPU Loads and Stores Using Register+Offset Address Mode (63)Table 5-14: FPU Loads and Using Register+Register Address Mode (63)Table 5-15: FPU Move To and From Instructions (63)Table 5-16: FPU IEEE Arithmetic Operations (64)Table 5-17: FPU-Approximate Arithmetic Operations (64)Table 5-18: FPU Multiply-Accumulate Arithmetic Operations (65)Table 5-19: FPU Conversion Operations Using the FCSR Rounding Mode (65)Table 5-20: FPU Conversion Operations Using a Directed Rounding Mode (65)Table 5-21: FPU Formatted Operand Move Instructions (66)Table 5-22: FPU Conditional Move on True/False Instructions (66)iv MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Table 5-23: FPU Conditional Move on Zero/Nonzero Instructions (67)Table 5-24: FPU Conditional Branch Instructions (67)Table 5-25: Deprecated FPU Conditional Branch Likely Instructions (67)Table 5-26: CPU Conditional Move on FPU True/False Instructions (68)Table 5-27: FPU Operand Format Field (fmt, fmt3) Encoding (68)Table 5-28: Valid Formats for FPU Operations (69)Table 5-29: FPU Instruction Format Fields (72)Table A-1: Symbols Used in the Instruction Encoding Tables (76)Table A-2: MIPS32 Encoding of the Opcode Field (77)Table A-3: MIPS32 SPECIAL Opcode Encoding of Function Field (78)Table A-4: MIPS32 REGIMM Encoding of rt Field (78)Table A-5: MIPS32 SPECIAL2 Encoding of Function Field (78)Table A-6: MIPS32 SPECIAL3 Encoding of Function Field for Release 2 of the Architecture (78)Table A-7: MIPS32 MOVCI Encoding of tf Bit (79)Table A-8: MIPS32 SRL Encoding of Shift/Rotate (79)Table A-9: MIPS32 SRLV Encoding of Shift/Rotate (79)Table A-10: MIPS32 BSHFL Encoding of sa Field (79)Table A-11: MIPS32 COP0 Encoding of rs Field (79)Table A-12: MIPS32 COP0 Encoding of Function Field When rs=CO (80)Table A-13: MIPS32 COP1 Encoding of rs Field (80)Table A-14: MIPS32 COP1 Encoding of Function Field When rs=S (80)Table A-15: MIPS32 COP1 Encoding of Function Field When rs=D (81)Table A-16: MIPS32 COP1 Encoding of Function Field When rs=W or L (81)Table A-17: MIPS64 COP1 Encoding of Function Field When rs=PS (81)Table A-18: MIPS32 COP1 Encoding of tf Bit When rs=S, D, or PS, Function=MOVCF (81)Table A-19: MIPS32 COP2 Encoding of rs Field (82)Table A-20: MIPS64 COP1X Encoding of Function Field (82)Table A-21: Floating Point Unit Instruction Format Encodings (82)MIPS32™ Architecture For Programmers Volume I, Revision 2.00v Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.vi MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Chapter 1About This BookThe MIPS32™ Architecture For Programmers V olume I comes as a multi-volume set.•V olume I describes conventions used throughout the document set, and provides an introduction to the MIPS32™Architecture•V olume II provides detailed descriptions of each instruction in the MIPS32™ instruction set•V olume III describes the MIPS32™Privileged Resource Architecture which defines and governs the behavior of the privileged resources included in a MIPS32™ processor implementation•V olume IV-a describes the MIPS16e™ Application-Specific Extension to the MIPS32™ Architecture•V olume IV-b describes the MDMX™ Application-Specific Extension to the MIPS32™ Architecture and is notapplicable to the MIPS32™ document set•V olume IV-c describes the MIPS-3D™ Application-Specific Extension to the MIPS64™ Architecture and is notapplicable to the MIPS32™ document set•V olume IV-d describes the SmartMIPS™Application-Specific Extension to the MIPS32™ Architecture1.1Typographical ConventionsThis section describes the use of italic,bold and courier fonts in this book.1.1.1Italic Text•is used for emphasis•is used for bits,fields,registers, that are important from a software perspective (for instance, address bits used bysoftware,and programmablefields and registers),and variousfloating point instruction formats,such as S,D,and PS •is used for the memory access types, such as cached and uncached1.1.2Bold Text•represents a term that is being defined•is used for bits andfields that are important from a hardware perspective (for instance,register bits, which are not programmable but accessible only to hardware)•is used for ranges of numbers; the range is indicated by an ellipsis. For instance,5..1indicates numbers 5 through 1•is used to emphasize UNPREDICTABLE and UNDEFINED behavior, as defined below.1.1.3Courier TextCourier fixed-width font is used for text that is displayed on the screen, and for examples of code and instruction pseudocode.MIPS32™ Architecture For Programmers Volume I, Revision 2.001 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.Chapter 1 About This Book1.2UNPREDICTABLE and UNDEFINEDThe terms UNPREDICTABLE and UNDEFINED are used throughout this book to describe the behavior of theprocessor in certain cases.UNDEFINED behavior or operations can occur only as the result of executing instructions in a privileged mode (i.e., in Kernel Mode or Debug Mode, or with the CP0 usable bit set in the Status register).Unprivileged software can never cause UNDEFINED behavior or operations. Conversely, both privileged andunprivileged software can cause UNPREDICTABLE results or operations.1.2.1UNPREDICTABLEUNPREDICTABLE results may vary from processor implementation to implementation,instruction to instruction,or as a function of time on the same implementation or instruction. Software can never depend on results that areUNPREDICTABLE.UNPREDICTABLE operations may cause a result to be generated or not.If a result is generated, it is UNPREDICTABLE.UNPREDICTABLE operations may cause arbitrary exceptions.UNPREDICTABLE results or operations have several implementation restrictions:•Implementations of operations generating UNPREDICTABLE results must not depend on any data source(memory or internal state) which is inaccessible in the current processor mode•UNPREDICTABLE operations must not read, write, or modify the contents of memory or internal state which is inaccessible in the current processor mode. For example,UNPREDICTABLE operations executed in user modemust not access memory or internal state that is only accessible in Kernel Mode or Debug Mode or in another process •UNPREDICTABLE operations must not halt or hang the processor1.2.2UNDEFINEDUNDEFINED operations or behavior may vary from processor implementation to implementation, instruction toinstruction, or as a function of time on the same implementation or instruction.UNDEFINED operations or behavior may vary from nothing to creating an environment in which execution can no longer continue.UNDEFINED operations or behavior may cause data loss.UNDEFINED operations or behavior has one implementation restriction:•UNDEFINED operations or behavior must not cause the processor to hang(that is,enter a state from which there is no exit other than powering down the processor).The assertion of any of the reset signals must restore the processor to an operational state1.3Special Symbols in Pseudocode NotationIn this book, algorithmic descriptions of an operation are described as pseudocode in a high-level language notation resembling Pascal. Special symbols used in the pseudocode notation are listed in Table 1-1.Table 1-1 Symbols Used in Instruction Operation StatementsSymbol Meaning←Assignment=, ≠Tests for equality and inequality||Bit string concatenationx y A y-bit string formed by y copies of the single-bit value x2MIPS32™ Architecture For Programmers Volume I, Revision 2.00 Copyright © 2001-2003 MIPS Technologies Inc. All rights reserved.1.3Special Symbols in Pseudocode Notationb#n A constant value n in base b.For instance10#100represents the decimal value100,2#100represents the binary value 100 (decimal 4), and 16#100 represents the hexadecimal value 100 (decimal 256). If the "b#" prefix is omitted, the default base is 10.x y..z Selection of bits y through z of bit string x.Little-endian bit notation(rightmost bit is0)is used.If y is less than z, this expression is an empty (zero length) bit string.+, −2’s complement or floating point arithmetic: addition, subtraction∗, ×2’s complement or floating point multiplication (both used for either)div2’s complement integer divisionmod2’s complement modulo/Floating point division<2’s complement less-than comparison>2’s complement greater-than comparison≤2’s complement less-than or equal comparison≥2’s complement greater-than or equal comparisonnor Bitwise logical NORxor Bitwise logical XORand Bitwise logical ANDor Bitwise logical ORGPRLEN The length in bits (32 or 64) of the CPU general-purpose registersGPR[x]CPU general-purpose register x. The content of GPR[0] is always zero.SGPR[s,x]In Release 2 of the Architecture, multiple copies of the CPU general-purpose registers may be implemented.SGPR[s,x] refers to GPR set s, register x. GPR[x] is a short-hand notation for SGPR[ SRSCtl CSS, x].FPR[x]Floating Point operand register xFCC[CC]Floating Point condition code CC.FCC[0] has the same value as COC[1].FPR[x]Floating Point (Coprocessor unit 1), general register xCPR[z,x,s]Coprocessor unit z, general register x,select sCP2CPR[x]Coprocessor unit 2, general register xCCR[z,x]Coprocessor unit z, control register xCP2CCR[x]Coprocessor unit 2, control register xCOC[z]Coprocessor unit z condition signalXlat[x]Translation of the MIPS16e GPR number x into the corresponding 32-bit GPR numberBigEndianMem Endian mode as configured at chip reset (0→Little-Endian, 1→ Big-Endian). Specifies the endianness of the memory interface(see LoadMemory and StoreMemory pseudocode function descriptions),and the endianness of Kernel and Supervisor mode execution.BigEndianCPU The endianness for load and store instructions (0→ Little-Endian, 1→ Big-Endian). In User mode, this endianness may be switched by setting the RE bit in the Status register.Thus,BigEndianCPU may be computed as (BigEndianMem XOR ReverseEndian).Table 1-1 Symbols Used in Instruction Operation StatementsSymbol MeaningChapter 1 About This Book1.4For More InformationVarious MIPS RISC processor manuals and additional information about MIPS products can be found at the MIPS URL:ReverseEndianSignal to reverse the endianness of load and store instructions.This feature is available in User mode only,and is implemented by setting the RE bit of the Status register.Thus,ReverseEndian may be computed as (SR RE and User mode).LLbitBit of virtual state used to specify operation for instructions that provide atomic read-modify-write.LLbit is set when a linked load occurs; it is tested and cleared by the conditional store. It is cleared, during other CPU operation,when a store to the location would no longer be atomic.In particular,it is cleared by exception return instructions.I :,I+n :,I-n :This occurs as a prefix to Operation description lines and functions as a label. It indicates the instruction time during which the pseudocode appears to “execute.” Unless otherwise indicated, all effects of the currentinstruction appear to occur during the instruction time of the current instruction.No label is equivalent to a time label of I . Sometimes effects of an instruction appear to occur either earlier or later — that is, during theinstruction time of another instruction.When this happens,the instruction operation is written in sections labeled with the instruction time,relative to the current instruction I ,in which the effect of that pseudocode appears to occur.For example,an instruction may have a result that is not available until after the next instruction.Such an instruction has the portion of the instruction operation description that writes the result register in a section labeled I +1.The effect of pseudocode statements for the current instruction labelled I +1appears to occur “at the same time”as the effect of pseudocode statements labeled I for the following instruction.Within one pseudocode sequence,the effects of the statements take place in order. However, between sequences of statements for differentinstructions that occur “at the same time,” there is no defined order. Programs must not depend on a particular order of evaluation between such sections.PCThe Program Counter value.During the instruction time of an instruction,this is the address of the instruction word. The address of the instruction that occurs during the next instruction time is determined by assigning a value to PC during an instruction time. If no value is assigned to PC during an instruction time by anypseudocode statement,it is automatically incremented by either 2(in the case of a 16-bit MIPS16e instruction)or 4before the next instruction time.A taken branch assigns the target address to the PC during the instruction time of the instruction in the branch delay slot.PABITSThe number of physical address bits implemented is represented by the symbol PABITS.As such,if 36physical address bits were implemented, the size of the physical address space would be 2PABITS = 236 bytes.FP32RegistersModeIndicates whether the FPU has 32-bit or 64-bit floating point registers (FPRs).In MIPS32,the FPU has 3232-bit FPRs in which 64-bit data types are stored in even-odd pairs of FPRs.In MIPS64,the FPU has 3264-bit FPRs in which 64-bit data types are stored in any FPR.In MIPS32implementations,FP32RegistersMode is always a 0.MIPS64implementations have a compatibility mode in which the processor references the FPRs as if it were a MIPS32 implementation. In such a caseFP32RegisterMode is computed from the FR bit in the Status register.If this bit is a 0,the processor operates as if it had 32 32-bit FPRs. If this bit is a 1, the processor operates with 32 64-bit FPRs.The value of FP32RegistersMode is computed from the FR bit in the Status register.InstructionInBranchDelaySlotIndicates whether the instruction at the Program Counter address was executed in the delay slot of a branch or jump. This condition reflects the dynamic state of the instruction, not the static state. That is, the value is false if a branch or jump occurs to an instruction whose PC immediately follows a branch or jump, but which is not executed in the delay slot of a branch or jump.SignalException(exce ption, argument)Causes an exception to be signaled, using the exception parameter as the type of exception and the argument parameter as an exception-specific argument). Control does not return from this pseudocode function - the exception is signaled at the point of the call.Table 1-1 Symbols Used in Instruction Operation StatementsSymbolMeaning。

Nikon COOLPIX P90数码相机 说明书

数码相机用户手册商标信息•Microsoft、Windows 和 Windows Vista 是 Microsoft Corporation 在美国和/或其它国家的注册商标或商标。

•Macintosh、Mac OS 和 QuickTime 是 Apple Inc. 的商标。

•Adobe 和 Acrobat 是 Adobe Systems Inc. 的注册商标。

•SD 标志是 SD Card Association 的商标。

•PictBridge 是商标。

•在本手册或随尼康产品提供的其它文件中所提及的所有其它商标名称,分别为其相关所有者所持有的商标或注册商标。

简介开始步骤A基本拍摄和播放:自动模式y/x根据场景拍摄a /y自动拍摄笑脸d运动连拍模式使用 A、B、C、D、E 和 F 拍摄照片c更多播放说明D短片E声音录制连接到电视机、计算机和打印机d拍摄、播放和设定菜单技术注释i安全须知为防止损坏您的尼康产品,或为避免您或他人受伤,在使用本设备前请阅读完下列安全须知。

请将这些安全指示放在便于使用者查阅的位置。

不遵守本节中所列举的注意事项可能会引起的后果用以下符号标注:警告发生故障时请关闭电源烟或发出异味时,请拔出交流电源适配器并立刻取出电池,注意勿被灼伤。

若在此情形下继续使用可能导致受伤。

请在取下或断开电源后,将器材送到尼康授权的维修服务中心进行检查。

请勿拆卸相机零件可能导致受伤。

只有合格的技术人员才可进行修理。

万一由于跌落或其它意外事故引起相机或交流电源适配器的开裂,请拔下产品和/或取出电池,然后将产品送至尼康授权的维修服务中心进行检查。

请勿在有易燃气体的地方使用相机或交流电源适配器请勿在有易燃气体的地方使用电子设备,以避免发生爆炸或火灾。

小心使用相机背带部。

请将本产品放在儿童无法取到的地方请特别注意防止婴儿将电池或其它小部件放入口中。

发生的人身伤害。

ii安全须知使用电池时的注意事项使用本产品的电池时请注意以下事项:•更换电池之前,请关闭相机电源。

MU70-SU0 LGA2011插座R3主板 用户手册说明书

2-3-6-1 IOAT 配置...................................................................................................84

-3-

第3章

2-3-2-3 CPU T State Control(CPU T 状态控制)............................................73

2-3-3 Common RefCode Configuration(通用 RefCode 配置)..............74

2-3-5-1 内存拓扑.....................................................................................................79

2-3-5-2 内存热效应................................................................................................80

目录

包装箱物品...........................................................................................................5 MU70-SU0 主板布局..........................................................................................6 框图.......................................................................................................................9 第 1 章 硬件安装.............................................................................................10

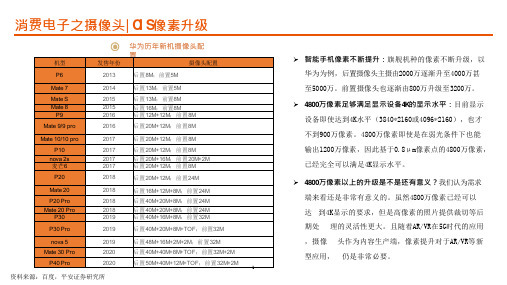

消费电子摄像头市场与技术分析

成像质量的提升,也极大地 推 动了图像传感器(CIS)市 场 的爆发。2019年每部手机摄像

头的使用量约为3.1个,预 计

2021年 将 达 到 4.3个 。 2019年

智 能 手 机 用 CIS 的 市 场 规 模 是 137.5亿 美 元 , 预计2022年 将 达 到 233.5亿 美 元 ,复 合 增 长 率达到19.3%。

76.2

9.1%

36

13%

2.56

93.3

12.5%

39

7%

2.71

106.1

13.3%

43

10%

3.20

137.5

25.8%

48

12%

3.40

163.6

11.7%

64

33%

3.30

211.4

11.6%

73

14%

3.20

233.5

3

同比

22% 14% 30% 19% 29% 10%

➢ 智能手机摄像头搭载量不断 提 升:手机从双摄向多摄趋势发

P30

P30 Pro

2018 2018 2018 2019

2019

后置16M+12M+8M;前置24M

后置40M+20M+8M;前置24M 后置40M+20M+8M;前置24M 后置40M+16M+8M;前置32M

后置40M+20M+8M+TOF;前置32M

nova 5 Mate 30 Pro

P40 Pro

TOF性能更优

基于A6G2CM6G2C核心板移植WM8960驱动

基于A6G2CM6G2C核⼼板移植WM8960驱动⼴州致远电⼦有限公司移植WM8960 基于A6G2C/M6G2C 核⼼板修订历史⽬录第1章适⽤范围 (1)第2章开发环境 (2)第3章技术实现 (3)3.1硬件连接 (3)3.2解压内核源码 (3)3.3调整设备树 (3)3.3.1更新sound结点 (4)3.3.2修改sai2结点 (5)3.3.3增加codec结点 (6)3.4编译WM8960 (6)3.5增加系统补丁 (7)第4章免责声明 (8)第1章适⽤范围本⽂主要介绍在EPC-6G2C-L(M6G2C)上,移植WM8960驱动。

其应⽤原理及移植步骤,也适⽤于A6GxC系列其他产品。

第2章开发环境●开发主机环境:Ubuntu 12.04(64 位)、gcc-linaro-arm-linux-gnueabihf-4.9-2014.09系列交叉⼯具链。

●硬件清单:A6G2C/M6G2C核⼼板+带WM8960芯⽚的底板(底板其它配置与EPC-6G2C-L⼀致)。

●软件资源:光盘EPC_IoT_M6GxC_A6GxC内核源码包:linux-src-bsp-4.1.15.tar.gz(或者更⾼版本光盘资料提供的内核源码包)。

第3章技术实现注意:在开始进⾏下⾯的操作之前,请⾸先确认ubuntu 主机的开发环境已经搭建好。

如需了解这⽅⾯的内容,请参考产品光盘资料中的《嵌⼊式Linux开发教程(上册) ——基于EPC-M6G2C-L.pdf》,第6章嵌⼊式Linux开发环境构建。

3.1 硬件连接WM8960需要与CPU的任意⼀路SAI接⼝以及I2C接⼝连接。

如WM8960与CPU的SAI2接⼝连接,则对应的引脚连接应该是:具体的硬件电路可参考《wm8960电路.xps》。

请注意:A6G2C核⼼板上的SAI2的引脚有外接电容,这个会影响波形产⽣,因此如果使⽤SAI2时需要去除核⼼板上SAI2相关的电容。

同样的,Iot-6G2C-L及EPC-6G2C-L底板的SAI2的引脚也有外接电容,也需要去除。

星光机 V-1用户手册说明书

星光机目录1前言 (1)1.1包装内容 (1)1.2包装开拆 (1)1.3标识符号 (1)1.4免责声明 (1)1.5安全须知 (1)1.5.1个人安全 (2)1.5.2安装和装配 (2)1.5.3电源和接线 (2)1.5.4操作 (2)2产品介绍 (3)2.1产品描述 (3)2.2产品特点 (3)2.3外观概述 (3)2.4机器尺寸 (4)3技术参数 (4)4设定安装 (5)4.1交流电源 (5)4.2交流插头 (5)4.3复位过载保护器 (5)4.4DMX连接 (6)4.5安装 (6)4.5.1方位 (6)4.5.2装配 (6)5操作机器 (6)5.1准备工作 (6)5.2机身控制面板 (6)5.3机身控制模式及操作 (6)5.3.1操作指导 (6)5.3.2菜单页面 (7)5.4DMX控制模式及操作 (8)5.4.1起始地址 (8)5.4.2DMX模式菜单页面 (8)5.4.3DMX通道设置和数值 (9)5.5喷花高度与喷花密度的关系 (9)5.6运行时间 (9)5.6.1查询运行时间 (9)5.6.2运行时间耗尽 (10)5.7高级设定页面 (10)5.7.1进入和退出高级设定页面 (10)5.7.2高级设定菜单页面 (10)6星光粉 (10)6.1识别和激活星光粉 (10)6.2添加星光粉 (11)6.3星光粉注意事项 (11)7技术信息 (11)7.1机器维护 (11)7.2储存 (11)7.2.1机器储存 (11)7.2.2星光粉储存和回收 (11)7.3一般故障 (12)7.3.1故障描述 (12)7.3.2故障菜单页面 (12)11前言1.1包装内容1.2 包装开拆收到机器后,请小心拆开包装箱,检查所有内容,以确保所有零配件都齐全并处于良好的状态。

如果外包装及任何部件因运输过程出现损坏或缺少,请立即联络承运商或经销商,并以原包装退回。

1.3标识符号符号含义注意关于安装,配置或操作的关键信息。

华硕B85M-G_PLUS_Manual说明书

plustek Network Video Recorder 说明书

安裝設定技術指導© 2010 版權所有,翻印必究。

未經允許不得翻印本手冊其中任何一部份。

本手冊內容提及之公司名稱和註冊商標均屬於各公司和所有者。

本手冊中所有內容都經過仔細考證,儘管如此,我們不排除可能由於疏忽、偶然情形或其他原因造成本手冊出現錯誤、遺漏、或不恰當表述,我們對這類錯誤、遺漏或不恰當表述不承擔任何責任和義務。

本手冊內容若有更動,恕不另行通知。

本公司NVR產品應使用於合法用途,某些國家或州當地法律明文禁止該等產品的某些特定的用途,例如因特定目地而秘密進行錄製聲音或影像訊息。

如果對該產品被建議的使用方式合法有疑問,請諮詢當地法律顧問後再行使用。

本產品的設計和製造得到持續改進,以符合新的環保要求。

我們致力於將產品符合全球環保標準。

請您向當地相關部門諮詢報廢該類物品的處理方法。

本產品的外包裝可被回收再利用。

注意回收再利用 (僅用於歐洲國家)保護環境!禁止將這種産品扔進家居類廢物垃圾箱。

請把它交給您所在居民區的廢物免費處理中心處理。

本使用手冊的螢幕圖例使用Windows XP畫面。

若您使用的系統是Windows 2000, Vista或7,您螢幕上的實際畫面會略有不同,但功能是一樣的。

目錄簡介 (1)關於本使用手冊 (1)本手冊所使用的標示 (1)圖示說明 (1)安全注意事項 (2)NVR主要功能 (2)系統需求 (3)產品包裝附件 (3)NVR 4000/4200/4300 (4)NVR Slim240 (4)NVR 4200V (5)產品外觀 (6)NVR 4000/4200 (6)NVR 4300 (7)NVR Slim240 (8)NVR 4200V (9)第一章. 安裝NVR (10)安裝NVR系統 (10)I. 連接網路攝影機(IP Cameras) (10)II. 連接監控攝影機(CCTV Cameras)及影像伺服器(Video Servers) (14)第二章. 如何使用NVR (19)登入 NVR (19)方法一.搜索工具程式 (Network Device Search Tool) (19)方法二. IE 地址欄 (20)設定精靈 (21)步驟 1 - 系統設定 (21)步驟 2 - WAN設定 (22)步驟 3 - LAN設定 (23)新增網路攝影機 (23)NVR觀看視窗 (25)語言 (25)即時預覽 (25)錄影事件記錄 (27)物體移動偵測 (30)登出 NVR (31)第三章. NVR進階設定 (32)設定精靈 (32)步驟 1 - 系統設定 (33)步驟 2 - WAN設定 (33)步驟 3 - LAN設定 (34)本機資訊 (35)系統狀態 (35)網路攝影機 (36)網路資訊 (36)WAN (36)LAN (40)客戶端清單 (41)網路攝影機 (41)裝置管理 (42)影像設定 (44)硬碟資訊 (45)系統資訊 (46)使用者資訊 (46)維護 (47)事件記錄 (48)系統設定 (49)日期與時間設定 (49)資料庫 (50)管理 (50)資料管理 (51)排程設定 (51)錄影排程 (51)事件排程 (52)安全控管 (53)事件設定 (53)警報通知 (55)事件記錄 (56)第四章. 技術資訊 (57)LED指示燈 (57)搜索工具程式 (57)IP設定資訊 (58)透過NVR使用動態IP位址 (59)代理伺服器 (60)重新設定 NVR (62)NVR關機 (62)附錄A: 專有名詞 (63)附錄B: 規格 (66)附錄C: 售後服務和保證 (71)産品保證聲明 (71)FCC 射頻干擾聲明書 (72)聯繫PLUSTEK (73)簡介歡迎選購我們的産品。

X210V3硬件手册

1.5

WINCE6.0 系统........................................................................................................5

1.6

产品简介 ................................................................................................................... 5

2.4.1 电源开关和插座.............................................................................................17

2.4.2 调试串口.........................................................................................................17

2.3.8 J8(电容屏扩展口)...........................................................................................16

2.3.9 J5(SDIO WIFI 接口).......................................................................................16

X210V3硬件手册

深圳市九鼎创展科技有限公司

版权声明 本手册版权归属深圳市九鼎创展科技有限公司所有, 并保留一切 权力。非经九鼎创展同意(书面形式),任何单位及个人不得擅自摘录 本手册部分或全部,违者我们将追究其法律责任。

Camera_Sensor_RockChip参考说明_v3.0.1

1、RK30 cif 电源控制说明;

钟以崇

2、rk30 camera driver v0.2.b 用户自定义

sensor 序列说明;

3、版本约定说明;

4、模组与驱动 flip 及 mirror 匹配说明;

5、Camera_test v1.1 版本

2012‐6‐18 1、ICS r3 cts 测试,单个前置摄像头测试 邓达龙

v2.7.2 v2.7.3 V2.7.4

2012‐4‐20

1.CameraHal v0.2.a 关于 ICS cts 以下 2 邓达龙 项 : testPreviewFpsRange 、 testCameraToSurfaceTextureMetadata 测 试在某些机器概率性测试不过的说明

2012‐5‐18

Camera 支持 USB 摄像头 Camera CTS 部分说明

增加摄像头方向说明 Camera 数码变焦支持 Android4.0 以及 kernel 3.0 说明

邓达龙 邓达龙

邓达龙 邓达龙 邓达龙 洪慧斌

测试帧率说明

邓达龙

审核

V2.2

2012‐02‐07 4.0.3 ICS cts 测 试 项 补 充 说 明 邓达龙

(CameraGLTest、SystemFeaturesTest、

CamcorderProfileTest)

V2.3

2012‐02‐21 针对开发商培训增加部分硬件调试内容 邓达龙

V2.4

2012‐3‐22

1 增加软件支持最多 6 个 sensor 的配置 邓达龙

说明;

2 CameraHal v0.2.3/v0.2.4, Camera driver

RockChip Camera 联系人:

BR8220 芯片数据手册 v1.01

FUJIFILM 富数码相机 说明书

相机使用方法

拍摄照片 (q 自动模式)................................... 22 采用对焦和曝光锁定拍摄照片 ..................... 26 AF 辅助灯 .................................................... 28 调节构图显示内容 ....................................... 28 观看图像 .............................................................. 30 使用删除按钮................................................... 34

相机连接

连接电视机 ....................................................... 102 将相机直接连接至打印机 — PictBridge 功能 .... 103

软件安装

在 Windows 计算机中的安装 ............................ 在 Mac OS X 中的安装 ..................................... 连接计算机 ....................................................... FinePixViewer 的使用方法 ....................... 107 110 113 116

高级功能 — 拍摄

使用拍摄功能 — 设置步骤 ................................... 35 设置拍摄模式 ...................................................... 38 q 自动........................................................ 38 /? 场景定位......................................... 38 双重防抖 ................................................ 46 </M 光圈优先 AE/ 快门优先 AE ................. 46 s 手动 ...................................................... 50

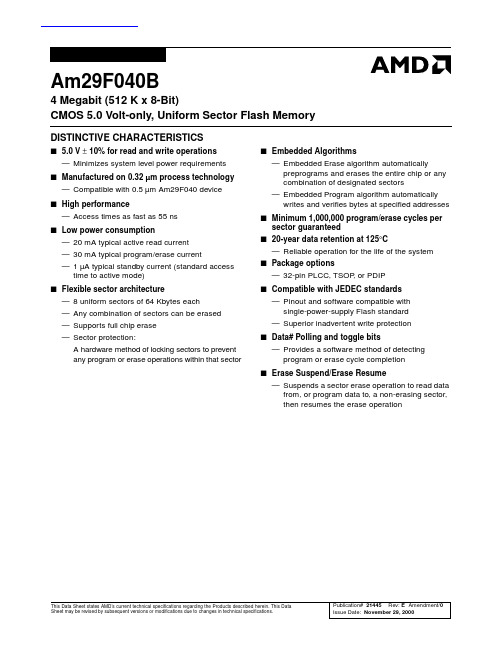

26817.pdf

This Data Sheet states AMD’s current technical specifications regarding the Products described herein. This Data Sheet may be revised by subsequent versions or modifications due to changes in technical specifications.Publication# 21445Rev: E Amendment/0 Issue Date: November 29, 2000Am29F040B4 Megabit (512 K x 8-Bit)CMOS 5.0 Volt-only, Uniform Sector Flash Memory DISTINCTIVE CHARACTERISTICSs 5.0 V ± 10% for read and write operations —Minimizes system level power requirementss Manufactured on 0.32µm process technology —Compatible with 0.5 µm Am29F040 devices High performance—Access times as fast as 55 nss Low power consumption—20 mA typical active read current—30 mA typical program/erase current—1 µA typical standby current (standard access time to active mode)s Flexible sector architecture—8 uniform sectors of 64 Kbytes each—Any combination of sectors can be erased—Supports full chip erase—Sector protection:A hardware method of locking sectors to preventany program or erase operations within that sector s Embedded Algorithms—Embedded Erase algorithm automatically preprograms and erases the entire chip or anycombination of designated sectors—Embedded Program algorithm automatically writes and verifies bytes at specified addresses s Minimum 1,000,000 program/erase cycles per sector guaranteeds20-year data retention at 125°C—Reliable operation for the life of the systems Package options—32-pin PLCC, TSOP, or PDIPs Compatible with JEDEC standards—Pinout and software compatible withsingle-power-supply Flash standard—Superior inadvertent write protections Data# Polling and toggle bits—Provides a software method of detecting program or erase cycle completions Erase Suspend/Erase Resume—Suspends a sector erase operation to read data from, or program data to, a non-erasing sector,then resumes the erase operation查询Am29F040B供应商GENERAL DESCRIPTIONThe Am29F040B is a 4 Mbit, 5.0 volt-only Flash mem-ory organized as 524,288 Kbytes of 8 bits each. The 512 Kbytes of data are divided into eight sectors of 64 Kbytes each for flexible erase capability. The 8 bits of data appear on DQ0–DQ7. The Am29F040B is offered in 32-pin PLCC, TSOP, and PDIP packages. This device is designed to be programmed in-system with the stan-dard system 5.0 volt V CC supply. A 12.0 volt V PP is not required for write or erase operations. The device can also be programmed in standard EPROM programmers. This device is manufactured using AMD’s 0.32 µm pro-cess technology, and offers all the features and benefits of the Am29F040, which was manufactured using 0.5 µm process technology. In addtion, the Am29F040B has a second toggle bit, DQ2, and also of-fers the ability to program in the Erase Suspend mode. The standard Am29F040B offers access times of 55, 70, 90, 120, and 150 ns, allowing high-speed micropro-cessors to operate without wait states. To eliminate bus contention the device has separate chip enable (CE#), write enable (WE#) and output enable (OE#) controls. The device requires only a single 5.0 volt power sup-ply for both read and write functions. Internally generated and regulated voltages are provided for the program and erase operations.The device is entirely command set compatible with the JEDEC single-power-supply Flash standard. Com-mands are written to the command register using standard microprocessor write timings. Register con-tents serve as input to an internal state-machine that controls the erase and programming circuitry. Write cy-cles also internally latch addresses and data needed for the programming and erase operations. Reading data out of the device is similar to reading from other Flash or EPROM devices.Device programming occurs by executing the program command sequence. This initiates the Embedded Program algorithm—an internal algorithm that auto-matically times the program pulse widths and verifies proper cell margin.Device erasure occurs by executing the erase com-mand sequence. This initiates the Embedded Erase algorithm—an internal algorithm that automatically preprograms the array (if it is not already programmed) before executing the erase operation. During erase, the device automatically times the erase pulse widths and verifies proper cell margin.The host system can detect whether a program or erase operation is complete by reading the DQ7 (Data# Polling) and DQ6 (toggle) status bits. After a program or erase cycle has been completed, the device is ready to read array data or accept another command.The sector erase architecture allows memory sectors to be erased and reprogrammed without affecting the data contents of other sectors. The device is fully erased when shipped from the factory.Hardware data protection measures include a low V CC detector that automatically inhibits write opera-tions during power transitions. The hardware sector protection feature disables both program and erase operations in any combination of the sectors of mem-ory. This can be achieved via programming equipment. The Erase Suspend feature enables the user to put erase on hold for any period of time to read data from, or program data to, any sector that is not selected for erasure. True background erase can thus be achieved. The system can place the device into the standby mode. Power consumption is greatly reduced in this mode. AMD’s Flash technology combines years of Flash memory manufacturing experience to produce the highest levels of quality, reliability and cost effective-ness. The device electrically erases all bits within a sector simultaneously via Fowler-Nordheim tunneling. The data is programmed using hot electron injection.2Am29F040BTABLE OF CONTENTSProduct Selector Guide. . . . . . . . . . . . . . . . . . . . . 4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 Connection Diagrams . . . . . . . . . . . . . . . . . . . . . . 5 Pin Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . 6 Logic Symbol. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6 Ordering Information. . . . . . . . . . . . . . . . . . . . . . . 7 Device Bus Operations . . . . . . . . . . . . . . . . . . . . . 8 Table 1. Am29F040B Device Bus Operations (8)Requirements for Reading Array Data (8)Writing Commands/Command Sequences (8)Program and Erase Operation Status (8)Standby Mode (8)Output Disable Mode (9)Table 2. Sector Addresses Table (9)Autoselect Mode (10)Table 3. Am29F040B Autoselect Codes (High Voltage Method) (10)Sector Protection/Unprotection (10)Hardware Data Protection (10)Low V CC Write Inhibit (10)Write Pulse “Glitch” Protection (10)Logical Inhibit (10)Power-Up Write Inhibit (10)Command Definitions . . . . . . . . . . . . . . . . . . . . . 11 Reading Array Data (11)Reset Command (11)Autoselect Command Sequence (11)Byte Program Command Sequence (11)Figure 1. Program Operation (12)Chip Erase Command Sequence (12)Sector Erase Command Sequence (12)Erase Suspend/Erase Resume Commands (13)Figure 2. Erase Operation (13)Command Definitions (14)Table 4. Am29F040B Command Definitions (14)Write Operation Status . . . . . . . . . . . . . . . . . . . . 15 DQ7: Data# Polling (15)Figure 3. Data# Polling Algorithm (15)DQ6: Toggle Bit I (16)DQ2: Toggle Bit II (16)Reading Toggle Bits DQ6/DQ2 (16)DQ5: Exceeded Timing Limits (16)DQ3: Sector Erase Timer (17)Figure 4. Toggle Bit Algorithm (17)Table 5. Write Operation Status.......................................................18Absolute Maximum Ratings. . . . . . . . . . . . . . . . . 19 Figure 5. Maximum Negative Overshoot Waveform (19)Figure 6. Maximum Positive Overshoot Waveform (19)Operating Ranges. . . . . . . . . . . . . . . . . . . . . . . . . 19 DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 20 TTL/NMOS Compatible (20)CMOS Compatible (20)Test Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . 21 Figure 7. Test Setup (21)Table 6. Test Specifications (21)Key to Switching Waveforms. . . . . . . . . . . . . . . . 21 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 22 Read Only Operations (22)Figure 8. Read Operation Timings (22)Erase and Program Operations (23)Figure 9. Program Operation Timings (24)Figure 10. Chip/Sector Erase Operation Timings (24)Figure 11. Data# Polling Timings (During Embedded Algorithms) 25 Figure 12. Toggle Bit Timings (During Embedded Algorithms) (25)Figure 13. DQ2 vs. DQ6 (26)AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . 27 Erase and Program Operations (27)Alternate CE# Controlled Writes (27)Figure 14. Alternate CE# Controlled Write Operation Timings (28)Erase and Programming Performance. . . . . . . . 29 Latchup Characteristics. . . . . . . . . . . . . . . . . . . . 29 TSOP Pin Capacitance . . . . . . . . . . . . . . . . . . . . 29 PLCC and PDIP Pin Capacitance. . . . . . . . . . . . . 30 Data Retention. . . . . . . . . . . . . . . . . . . . . . . . . . . . 30 Physical Dimensions . . . . . . . . . . . . . . . . . . . . . . 31 PD 032—32-Pin Plastic DIP (31)PL 032—32-Pin Plastic Leaded Chip Carrier (32)TS 032—32-Pin Standard Thin Small Package (33)TSR032—32-Pin Reversed Thin Small Outline Package (34)Revision Summary . . . . . . . . . . . . . . . . . . . . . . . . 35 Revision A (May 1997) (35)Revision B (January 1998) (35)Revision B+1 (January 1998) (35)Revision B+2 (April 1998) (35)Revision C (January 1999) (35)Revision C+1 (February 1999) (35)Revision C+2 (May 17, 1999) (35)Revision D (November 15, 1999) (35)Revision E (November 29, 2000) (35)Am29F040B34Am29F040BPRODUCT SELECTOR GUIDENote: See the “AC Characteristics” section for more information.BLOCK DIAGRAMFamily Part Number Am29F040BSpeed OptionV CC = 5.0 V ± 5%-55V CC = 5.0 V ± 10%-70-90-120-150Max access time, ns (t ACC )557090120150Max CE# access time, ns (t CE )557090120150Max OE# access time, ns (t OE )2530355055Erase Voltage GeneratorY -GatingCell MatrixX-Decoder Y -Decoder A d d r e s s L a t c hChip Enable Output EnableLogicPGM Voltage GeneratorTimerV CC DetectorState Control Command RegisterWE#CE#OE#A0–A18STBSTBDQ0–DQ7V CC V SSData Latch Input/Output BuffersAm29F040B5CONNECTION DIAGRAMSV CCWE#A17A14A13A8A9A11OE#A10CE#DQ7DQ6DQ5DQ4DQ3A18A16A15A12A7A6A5A4A3A2A1A0DQ0DQ1DQ2V SS1234567891011121314151632313029282726252423222120191817PDIPPIN CONFIGURATIONA0–A18=Address InputsDQ0–DQ7=Data Input/OutputCE#=Chip EnableWE#=Write EnableOE#=Output EnableV SS=Device GroundV CC=+5.0 V single power supply(see Product Selector Guide fordevice speed ratings and voltagesupply tolerances)LOGIC SYMBOL198DQ0–DQ7A0–A18CE#OE#WE#6Am29F040BAm29F040B 7ORDERING INFORMATION Standard ProductsAMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of the following: Valid CombinationsValid Combinations list configurations planned to be sup-ported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.Am29F040B-55ECTEMPERATURE RANGE C =Commercial(0°C to +70°C)I = Industrial (–40°C to +85°C)E =Extended (–55°C to +125°C)PACKAGE TYPE P =32-Pin Plastic DIP (PD 032)J =32-Pin Rectangular Plastic Leaded Chip Carrier (PL 032)E =32-Pin Thin Small Outline Package (TSOP) Standard Pinout (TS 032)F =32-Pin Thin Small Outline Package (TSOP) Reverse Pinout (TSR032)SPEED OPTIONSee Product Selector Guide and Valid CombinationsDEVICE NUMBER/DESCRIPTION Am29F040B4 Megabit (512 K x 8-Bit) CMOS 5.0 Volt-only Sector Erase Flash Memory 5.0 V Read, Program, and EraseValid CombinationsV CC Voltage AM29F040B-55JC, JI, JE, EC, EI, EE, FC, FI, FE 5.0 V ± 5%AM29F040B-70 5.0 V ± 10%AM29F040B-90PC, PI, PE, JC, JI, JE, EC, EI, EE,FC, FI, FEAM29F040B-120AM29F040B-150DEVICE BUS OPERATIONSThis section describes the requirements and use of the device bus operations, which are initiated through the internal command register. The command register it-self does not occupy any addressable memory location. The register is composed of latches that store the commands, along with the address and data infor-mation needed to execute the command. The contents of the register serve as inputs to the internal state ma-chine. The state machine outputs dictate the function of the device. The appropriate device bus operations table lists the inputs and control levels required, and the resulting output. The following subsections describe each of these operations in further detail.Table 1.Am29F040B Device Bus OperationsLegend:L = Logic Low = V IL, H = Logic High = V IH, V ID = 12.0 ± 0.5 V, X = Don’t Care, D IN = Data In, D OUT = Data Out, A IN = Address In Note: See the “Sector Protection/Unprotection” section. for more information.Requirements for Reading Array DataTo read array data from the outputs, the system must drive the CE# and OE# pins to V IL. CE# is the power control and selects the device. OE# is the output con-trol and gates array data to the output pins. WE# should remain at V IH.The internal state machine is set for reading array data upon device power-up, or after a hardware reset. This ensures that no spurious alteration of the memory con-tent occurs during the power transition. No command is necessary in this mode to obtain array data. Standard microprocessor read cycles that assert valid addresses on the device address inputs produce valid data on the device data outputs. The device remains enabled for read access until the command register contents are altered.See “Reading Array Data” for more information. Refer to the AC Read Operations table for timing specifica-tions and to the Read Operations Timings diagram for the timing waveforms. I CC1 in the DC Characteristics table represents the active current specification for reading array data.Writing Commands/Command Sequences To write a command or command sequence (which in-cludes programming data to the device and erasing sectors of memory), the system must drive WE# and CE# to V IL, and OE# to V IH.An erase operation can erase one sector, multiple sec-tors, or the entire device. The Sector Address Tables indicate the address space that each sector occupies.A “sector address” consists of the address bits required to uniquely select a sector. See the “Command Defini-tions” section for details on erasing a sector or the entire chip, or suspending/resuming the erase operation.After the system writes the autoselect command se-quence, the device enters the autoselect mode. The system can then read autoselect codes from the inter-nal register (which is separate from the memory array) on DQ7–DQ0. Standard read cycle timings apply in this mode. Refer to the “Autoselect Mode” and “Autoselect Command Sequence” sections for more information.I CC2 in the DC Characteristics table represents the ac-tive current specification for the write mode. The “AC Characteristics” section contains timing specification tables and timing diagrams for write operations.Program and Erase Operation Status During an erase or program operation, the system may check the status of the operation by reading the status bits on DQ7–DQ0. Standard read cycle timings and I CC read specifications apply. Refer to “Write Operation Status” for more information, and to each AC Charac-teristics section for timing diagrams.Standby ModeWhen the system is not reading or writing to the device, it can place the device in the standby mode. In this mode, current consumption is greatly reduced, and theOperation CE#OE#WE#A0–A20DQ0–DQ7 Read L L H A IN D OUT Write L H L A IN D IN CMOS Standby V CC ± 0.5 V X X X High-Z TTL Standby H X X X High-Z Output Disable L H H X High-Z8Am29F040BAm29F040B 9outputs are placed in the high impedance state, inde-pendent of the OE# input.The device enters the CMOS standby mode when the CE# pin is held at V CC ± 0.5 V. (Note that this is a more restricted voltage range than V IH .) The device enters the TTL standby mode when CE# is held at V IH . The device requires the standard access time (t CE ) before it is ready to read data.If the device is deselected during erasure or program-ming, the device draws active current until the operation is completed.I CC3 in the DC Characteristics tables represents the standby current specification.Output Disable ModeWhen the OE# input is at V IH , output from the device is disabled. The output pins are placed in the high imped-ance state.Table 2.Sector Addresses TableNote: All sectors are 64 Kbytes in size.Sector A18A17A16Address Range SA000000000h–0FFFFh SA100110000h–1FFFFh SA201020000h–2FFFFh SA301130000h–3FFFFh SA410040000h–4FFFFh SA510150000h–5FFFFh SA611060000h–6FFFFh SA711170000h–7FFFFhAutoselect ModeThe autoselect mode provides manufacturer and de-vice identification, and sector protection verification, through identifier codes output on DQ7–DQ0. This mode is primarily intended for programming equipment to automatically match a device to be programmed with its corresponding programming algorithm. However, the autoselect codes can also be accessed in-system through the command register.When using programming equipment, the autoselect mode requires V ID (11.5 V to 12.5 V) on address pin A9. Address pins A6, A1, and A0 must be as shown in Autoselect Codes (High Voltage Method) table. In addi-tion, when verifying sector protection, the sector address must appear on the appropriate highest order address bits. Refer to the corresponding Sector Ad-dress Tables. The Command Definitions table shows the remaining address bits that are don’t care. When all necessary bits have been set as required, the program-ming equipment may then read the corresponding identifier code on DQ7–DQ0.To access the autoselect codes in-system, the host system can issue the autoselect command via the command register, as shown in the Command Defini-tions table. This method does not require V ID. See “Command Definitions” for details on using the autose-lect mode.Table 3.Am29F040B Autoselect Codes (High Voltage Method)Sector Protection/UnprotectionThe hardware sector protection feature disables both program and erase operations in any sector. The hard-ware sector unprotection feature re-enables both program and erase operations in previously protected sectors.Sector protection/unprotection must be implemented using programming equipment. The procedure re-quires a high voltage (V ID) on address pin A9 and the control pins. Details on this method are provided in a supplement, publication number 19957. Contact an AMD representative to obtain a copy of the appropriate document.The device is shipped with all sectors unprotected. AMD offers the option of programming and protecting sectors at its factory prior to shipping the device through AMD’s ExpressFlash™ Service. Contact an AMD representative for details.It is possible to determine whether a sector is protected or unprotected. See “Autoselect Mode” for details. Hardware Data ProtectionThe command sequence requirement of unlock cycles for programming or erasing provides data protection against inadvertent writes (refer to the Command Defi-nitions table). In addition, the following hardware data protection measures prevent accidental erasure or pro-gramming, which might otherwise be caused by spurious system level signals during V CC power-up and power-down transitions, or from system noise.Low V CC Write InhibitWhen V CC is less than V LKO, the device does not ac-cept any write cycles. This protects data during V CC power-up and power-down. The command register and all internal program/erase circuits are disabled, and the device resets. Subsequent writes are ignored until V CC is greater than V LKO. The system must provide the proper signals to the control pins to prevent uninten-tional writes when V CC is greater than V LKO.Write Pulse “Glitch” ProtectionNoise pulses of less than 5 ns (typical) on OE#, CE# or WE# do not initiate a write cycle.Logical InhibitWrite cycles are inhibited by holding any one of OE# = V IL, CE# = V IH or WE# = V IH. To initiate a write cycle, CE# and WE# must be a logical zero while OE# is a logical one.Power-Up Write InhibitIf WE# = CE# = V IL and OE# = V IH during power up, the device does not accept commands on the rising edge of WE#. The internal state machine is automatically reset to reading array data on power-up.Description A18–A16A15–A10A9A8–A7A6A5–A2A1A0Identifier Code on DQ7-DQ0Manufacturer ID: AMD X X V ID X V IL X V IL V IL01h Device ID: Am29F040B X X V ID X V IL X V IL V IH A4hSector Protection VerificationSectorAddressX V ID X V IL X V IH V IL01h (protected)00h (unprotected)10Am29F040BCOMMAND DEFINITIONSWriting specific address and data commands or se-quences into the command register initiates device operations. The Command Definitions table defines the valid register command sequences. Writing incorrect address and data values or writing them in the im-proper sequence resets the device to reading array data.All addresses are latched on the falling edge of WE# or CE#, whichever happens later. All data is latched on the rising edge of WE# or CE#, whichever happens first. Refer to the appropriate timing diagrams in the “AC Characteristics” section.Reading Array DataThe device is automatically set to reading array data after device power-up. No commands are required to retrieve data. The device is also ready to read array data after completing an Embedded Program or Em-bedded Erase algorithm.After the device accepts an Erase Suspend command, the device enters the Erase Suspend mode. The sys-tem can read array data using the standard read timings, except that if it reads at an address within erase-suspended sectors, the device outputs status data. After completing a programming operation in the Erase Suspend mode, the system may once again read array data with the same exception. See “Erase Suspend/Erase Resume Commands” for more infor-mation on this mode.The system must issue the reset command to re-en-able the device for reading array data if DQ5 goes high, or while in the autoselect mode. See the “Reset Com-mand” section, next.See also “Requirements for Reading Array Data” in the “Device Bus Operations” section for more information. The Read Operations table provides the read parame-ters, and Read Operation Timings diagram shows the timing diagram.Reset CommandWriting the reset command to the device resets the de-vice to reading array data. Address bits are don’t care for this command.The reset command may be written between the se-quence cycles in an erase command sequence before erasing begins. This resets the device to reading array data. Once erasure begins, however, the device ig-nores reset commands until the operation is complete. The reset command may be written between the se-quence cycles in a program command sequence before programming begins. This resets the device to reading array data (also applies to programming in Erase Suspend mode). Once programming begins,however, the device ignores reset commands until the operation is complete.The reset command may be written between the se-quence cycles in an autoselect command sequence. Once in the autoselect mode, the reset command must be written to return to reading array data (also applies to autoselect during Erase Suspend).If DQ5 goes high during a program or erase operation, writing the reset command returns the device to read-ing array data (also applies during Erase Suspend). Autoselect Command SequenceThe autoselect command sequence allows the host system to access the manufacturer and devices codes, and determine whether or not a sector is protected. The Command Definitions table shows the address and data requirements. This method is an alternative to that shown in the Autoselect Codes (High Voltage Method) table, which is intended for PROM program-mers and requires V ID on address bit A9.The autoselect command sequence is initiated by writ-ing two unlock cycles, followed by the autoselect command. The device then enters the autoselect mode, and the system may read at any address any number of times, without initiating another command sequence.A read cycle at address XX00h or retrieves the manu-facturer code. A read cycle at address XX01h returns the device code. A read cycle containing a sector ad-dress (SA) and the address 02h in returns 01h if that sector is protected, or 00h if it is unprotected. Refer to the Sector Address tables for valid sector addresses. The system must write the reset command to exit the autoselect mode and return to reading array data. Byte Program Command Sequence Programming is a four-bus-cycle operation. The pro-gram command sequence is initiated by writing two unlock write cycles, followed by the program set-up command. The program address and data are written next, which in turn initiate the Embedded Program al-gorithm. The system is not required to provide further controls or timings. The device automatically provides internally generated program pulses and verify the pro-grammed cell margin. The Command Definitions take shows the address and data requirements for the byte program command sequence.When the Embedded Program algorithm is complete, the device then returns to reading array data and ad-dresses are no longer latched. The system can determine the status of the program operation by using DQ7 or DQ6. See “Write Operation Status” for informa-tion on these status bits.Any commands written to the device during the Em-bedded Program Algorithm are ignored. Programming is allowed in any sequence and across sector boundaries. A bit cannot be programmed from a “0” back to a “1”. Attempting to do so may halt the operation and set DQ5 to “1”, or cause the Data# Polling algorithm to indicate the operation was suc-cessful. However, a succeeding read will show that the data is still “0”. Only erase operations can convert a “0”to a “1”.Note: See the appropriate Command Definitions table for program command sequence.Figure 1.Program OperationChip Erase Command SequenceChip erase is a six-bus-cycle operation. The chip erase command sequence is initiated by writing two unlock cycles, followed by a set-up command. Two additional unlock write cycles are then followed by the chip erase command, which in turn invokes the Embedded Erase algorithm. The device does not require the system to preprogram prior to erase. The Embedded Erase algo-rithm automatically preprograms and verifies the entire memory for an all zero data pattern prior to electrical erase. The system is not required to provide any con-trols or timings during these operations. The Command Definitions table shows the address and data require-ments for the chip erase command sequence.Any commands written to the chip during the Embed-ded Erase algorithm are ignored.The system can determine the status of the erase op-eration by using DQ7, DQ6, or DQ2. See “Write Operation Status” for information on these status bits. When the Embedded Erase algorithm is complete, the device returns to reading array data and addresses are no longer latched.Figure 2 illustrates the algorithm for the erase opera-tion. See the Erase/Program Operations tables in “AC Characteristics” for parameters, and to the Chip/Sector Erase Operation Timings for timing waveforms. Sector Erase Command SequenceSector erase is a six bus cycle operation. The sector erase command sequence is initiated by writing two un-lock cycles, followed by a set-up command. Two additional unlock write cycles are then followed by the address of the sector to be erased, and the sector erase command. The Command Definitions table shows the address and data requirements for the sec-tor erase command sequence.The device does not require the system to preprogram the memory prior to erase. The Embedded Erase algo-rithm automatically programs and verifies the sector for an all zero data pattern prior to electrical erase. The system is not required to provide any controls or tim-ings during these operations.After the command sequence is written, a sector erase time-out of 50 µs begins. During the time-out period, additional sector addresses and sector erase com-mands may be written. Loading the sector erase buffer may be done in any sequence, and the number of sec-tors may be from one sector to all sectors. The time between these additional cycles must be less than 50µs, otherwise the last address and command might not be accepted, and erasure may begin. It is recom-mended that processor interrupts be disabled during this time to ensure all commands are accepted. The in-terrupts can be re-enabled after the last Sector Erase command is written. If the time between additional sec-tor erase commands can be assumed to be less than 50 µs, the system need not monitor DQ3. Any com-mand other than Sector Erase or Erase Suspend during the time-out period resets the device to reading array data. The system must rewrite the com-mand sequence and any additional sector addresses and commands.。

微星摄像头更换教程

微星摄像头更换教程

更换微星摄像头的步骤如下:

1. 首先,关闭电脑并断开电源。

2. 打开电脑的屏幕盖板(通常在笔记本电脑上),然后找到摄像头覆盖物。

3. 用小刀轻轻松动摄像头覆盖物的边缘,将其从屏幕上取下。

4. 在摄像头的周围可能会有一些胶带或其他固定物。

根据需要,小心地解开它们。

5. 解开固定物之后,您可以看到两个或四个螺丝固定摄像头在屏幕上。

使用螺丝刀或适当的工具将它们卸下。

6. 当螺丝全部卸下后,您就可以从屏幕上移下现有的摄像头了。

7. 取下摄像头后,将新的微星摄像头放置在原来的位置上。

8. 将螺丝重新固定在摄像头上。

9. 将固定物重新连接到摄像头周围。

10. 将摄像头覆盖物放回原位,确保它牢固地粘在屏幕上。

11. 关闭屏幕盖板,并插入电源。

12. 打开电脑,测试新摄像头是否正常工作。

请注意,在更换摄像头之前,请确认您拥有适当的技能和工具以避免损坏设备。

如果您不确定操作步骤,建议请专业人士来完成更换摄像头的工作。

此外,确保新的摄像头与您的电脑兼容并正确安装驱动程序。

canon佳能 嵌入式安装套件 SR600-VB 安装指南

嵌入式安装套件SR600-VB 安装指南YT1-9640-003嵌入式安装套件SR600-VB 是专门与VB-H630D ,VB-H6100VE ,VB-H6100D ,VB-M6000VE ,VB-M6000D (以下简称摄像机)配合使用的另购产品。

使用该产品,可以将摄像机嵌入安装到天花板上。

本“安装指南”对使用嵌入式安装套件SR600-VB 的安装方法进行说明。

为确保正确使用,请务必阅读“安全注意事项” 部分。

阅读本安装指南后,请将其放在方便取阅的地方以便日后参考。

除本“安装指南”外,还请阅读摄像机随附的“安装指南”和“操作指南”(包含在安装程序CD-ROM 中)。

* 有关最新信息(固件和随附软件、用户手册、操作环境等),请访问佳能网站。

* 部分摄像机不在某些国家或地区出售。

注意请让专业安装人员进行所有摄像机的安装工作。

请勿尝试自行安装摄像机。

否则,可能会导致意外事故,如摄像机跌落或电击。

检查随附的项目本产品随附以下项目。

如有任何缺失,请联系产品购买处的经销商。

1. 嵌入式吊顶外罩 ×12. 天花板支架1 ×13. 天花板支架2 ×14. 天花板背面支架 ×25. 模板 ×1安全注意事项本节介绍使用摄像机时必须遵守的注意事项。

如果不遵守这些注意事项,可能会导致人身伤害、死亡和/或财产损坏。

请仔细阅读以下信息并确保遵守注意事项。

安装注意事项中文© CANON INC. 2015Printed in T aiwan表示安全注意事项的符号本安装指南使用以下标记表示用户需要了解的重要信息,以保证安全使用本产品。

请确保遵守这些项目。

在户外安装摄像机时的注意事项(VB-H6100VE ,VB-M6000VE)在户外安装VB-H6100VE ,VB-M6000VE 时,请小心操作以保持其防水/防尘能力。

请务必阅读摄像机随附的“安装指南” > “在户外安装摄像机时的注意事项”。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。