详解TSV(硅通孔技术)封装技术

硅通孔技术TSV研究ppt课件

TSV技术面临的难题:

➢在价格与成本之间的极大障碍

➢新技术的不确定性所隐含的风险

➢实际的量产需求

1

概述

发展 状况

TSV 的 应用

GaAs 基TSV 20/03/2020

TSV的研究动态

TSV参数 最小TSV直

径 最小TSV间

3

TSV封装剖面图

概述

发展 状况

TSV 的 应用

TSV的研究动态

TSV的关键技术之一——通孔刻蚀

➢ 前通孔(via first):

在 IC 制 造 过 程 中 制 作 通 孔,分为前道互连和后 道互连

➢ 后通孔(via last) :

制造完成之后制作通孔

GaAs

基TSV 20/03/2020

4

概述

台积电有在28nm以下工艺量产三维LSI的意向。

TSV的 应用

GaAs 基TSV 20/03/2020

以多种尺寸和配置而形成的TSV 和再布线层

12

连接300mm晶圆和半导体芯片的微凸点

TSV的研究动态

概述

2010年12月三星公司采用TSV技术,成功开发出基于该 公司先进的绿色DDR3芯片的8GB RDIMM内存。

感测器

OsmiumTM from Aptina 9

TSV的研究动态

概述

发展 状况

应用TSV的影像感测器实例

2009年3月, 意法半导体推出市场上首款集成扩展景深 (EDoF)功能的1/4英寸光学格式3百万像素Raw Bayer传感器。 意法半导体最新的影像传感器可实现最小6.5 x 6.5mm的相机 模块,而且图像锐利度和使用体验非常出色,同时还兼有尺 寸和成本优势,是一款智能型自动对焦相机解决方案。

tsv的主要工艺步骤及方法

tsv的主要工艺步骤及方法一、制造硅通孔硅通孔(TSV)的制造是TSV技术的核心步骤之一。

在这一步,通过物理或化学方法在芯片上制造出穿透硅片的孔洞,这些孔洞将用于实现芯片间的垂直互连。

有多种方法可以用来制造硅通孔,包括但不限于深反应离子刻蚀(DRIE)、激光钻孔等。

二、填充硅通孔在硅通孔制造完成后,需要对其进行填充,以实现电信号的传输。

填充材料一般选用导电金属,如铜、钨等。

填充硅通孔的方法有化学气相沉积(CVD)、物理气相沉积(PVD)和电镀等。

选择合适的填充方法需要根据实际应用需求和工艺条件来决定。

三、连接硅通孔填充完硅通孔后,需要进行硅通孔间的连接,以实现芯片间的互连。

连接方法可以采用焊接、导电胶等。

在连接过程中,需要确保连接稳定可靠,以防止在后续使用中出现脱落或接触不良等问题。

四、测试与验证在完成硅通孔的制造、填充和连接后,需要进行测试与验证,以确保TSV 技术能够满足实际应用需求。

测试内容包括但不限于:导通性能测试、机械性能测试和可靠性测试等。

通过测试与验证,可以及时发现并解决潜在的问题,提高TSV技术的可靠性和稳定性。

五、封装与集成在TSV技术应用中,封装与集成是关键步骤之一。

通过封装与集成,可以将多个芯片垂直堆叠在一起,实现更小体积、更高性能的电子系统。

在封装与集成过程中,需要考虑到散热、信号传输、电源分配等问题,以确保整个系统的稳定运行。

六、可靠性评估TSV技术的可靠性是评估其性能的重要指标之一。

可靠性评估可以通过多种方法来实现,如加速老化试验、环境适应性试验等。

通过可靠性评估,可以了解TSV技术在不同环境和工作条件下的性能表现,为后续改进和优化提供依据。

七、失效分析失效分析是TSV技术中重要的一环,通过对失效样品的检测和分析,可以了解失效的原因和机制,从而提出相应的改进措施。

失效分析方法包括扫描电子显微镜(SEM)、能谱分析(EDS)等。

通过失效分析,可以提高TSV技术的可靠性和稳定性,为实际应用提供更加可靠的解决方案。

TSV工艺技术

TSV工艺技术TSV(Through Silicon Via)工艺技术是一种用于三维集成电路中的先进封装技术。

这种技术通过在硅片上钻孔,然后在孔中填充金属,实现了不同层次芯片之间的电连接,从而实现了高密度的芯片封装和高速数据传输。

TSV工艺技术具有许多优点。

首先,它可以提供更高的集成密度。

传统的芯片封装技术中,芯片仅能在一个平面上布置,而TSV技术使得芯片的多层堆叠成为可能。

通过将多个芯片垂直堆叠在一起,可以有效地提高芯片的整体集成度。

其次,TSV技术还可以提供更短的信号传输路径,减少信号传输延迟。

因为TSV是直接通过硅片内部传输信号,相比于传统的外部线路,信号的传输路径更短,从而能够提供更高的数据传输速率。

另外,TSV还可以减少芯片之间的串扰,提高电路的稳定性和可靠性。

TSV工艺技术的实现主要包括三个步骤:孔钻孔、金属填充和封装。

首先,通过激光钻孔或机械钻孔的方式,在硅片上形成所需的孔洞。

这一步骤需要高度精确的控制,以避免对芯片造成损伤。

接下来,将金属填充到孔洞中。

填充材料通常选择铜或钨,因为它们具有良好的导电性能。

填充金属可以使用物理气相沉积或浸涂的方法,以确保孔洞充满金属。

最后,将填充完毕的芯片进行封装,以保护芯片和TSV结构。

TSV工艺技术在电子行业中有广泛应用。

首先,它可以提高芯片的性能和功能。

通过TSV技术,不同功能的芯片可以堆叠在一起,并通过TSV连接进行互联,从而实现更复杂的电路功能。

其次,TSV技术可以减小芯片尺寸。

由于芯片堆叠在一起,芯片的整体尺寸可以减小,从而实现更小型化的设备。

此外,TSV技术还可以降低能耗。

由于TSV可以提供更短的信号传输路径,电路的响应速度更快,功耗更低。

最后,TSV 工艺技术为芯片的延伸和升级提供了可能。

当芯片发展到一定阶段,无法再单独升级时,可以通过TSV连接新的芯片层来实现升级,延长设备的使用寿命。

总之,TSV工艺技术是一种用于三维集成电路中的高级封装技术。

TSV基础知识介绍

比如,用于三维IC的TSV刻蚀设备必须将刻蚀腔清洗 步骤设计成常规清洗流程,是设备能够在生产和清 洗模式之间迅速转换,使得腔室始终保持纯净状态, 同时满足高量产对速度、工艺可预见性和工艺重复 的要求;这类刻蚀系统还必须具有单台设备刻蚀所 有材料的工艺处理能力,尽可能减小设备和设施的 成本,消除工艺转移和排队造成的延迟,为客户在 产能和设备拥有成本方面提供竞争力。另外,由于 目前高端IC产品都使用300毫米晶圆,保证晶圆表面 工艺处理的均匀性,TSV的刻蚀需要使用平面状等 离子源(Planar Plasma)。

TSV Technology

Frank

TSV Technology

TSV為直通矽晶穿孔(Through-Silicon Via)封裝 技術;因為製程微縮和低介電值材料的限 制,3D堆疊式封裝技術已被視為能否以較 小尺寸來製造高效能晶片的關鍵,而TSV技 術是透過以垂直導通來整合晶圓堆疊的方 式,以達到晶片間的電氣互連。此一技術 能夠以更低的成本有效提高系統的整合度 與效能。

对于刻蚀工艺模式的选择,业界目前仍在比较SSP (Steady State Processes)和RAP(Rapid Alternating Processes)技术。据了解,RAP刻蚀的选择性 (selectivity)很高,可以刻蚀纵宽比很大通孔,速 度也快,但是表面粗糙度是个挑战;SSP工艺和常规 的刻蚀接近,速度高而且制作的侧壁光滑,不过 Selectivity和Undercut的控制是难点。Steve认为,对 用户来说真正满意的方案是,机台能够根据应用的 要求进行工艺的选择和整合,实现两种模式的切换, 整体控制刻蚀速度、selectivity、侧壁光滑性和纵宽 比。当然,这需要大量的工艺知识积累,以及对所 vid Butler 10月在SEMICON Europa 期间的演讲中,比较了以上两种最基本的集成 方案(表1)。可以看出,Via-first工艺的设计 需要在IC设计阶段进行,对关键尺寸(CD)控 制的要求比Via-last制程更为严格。Lam Research公司3D IC刻蚀产品线资深产品经理 Steve Lassig则认为,对于TSV工艺开发,目前 最需要的是业界尽早就最佳工艺集成方案达成 共识。正是因为业界未能达到共识,目前硅通 孔技术可以说还处于开发的早期阶段。

tsv封装 概念 -回复

tsv封装概念-回复什么是TSV封装?如何进行TSV封装?TSV封装有哪些应用领域?这些问题。

TSV封装(Through-Silicon Via Packaging)是一种集成电路封装技术,它包括将硅片(Silicon wafer)与封装材料进行堆叠和连接的过程。

通过使用微小的垂直通孔(Via),TSV技术可以将不同功能层之间的电路连接起来,从而实现高度集成的封装方案。

TSV封装的过程可以分为以下几个步骤来进行:1. 制备硅片:首先需要准备硅片,这通常是通过硅晶圆的形式提供的。

晶圆制造过程可以包括去除表面缺陷、化学机械抛光(CMP)、清洗等步骤。

2. 制造TSV:在硅片上制造垂直通孔。

这可以通过多种技术来实现,包括湿法腐蚀、干法腐蚀、激光加工等。

TSV的尺寸通常非常小,可以达到微米级别。

3. 堆叠封装:将多个硅片进行堆叠,并使用封装材料进行连接。

封装材料可以选择有机封装材料(例如环氧树脂)、无机封装材料(例如玻璃)、金属封装材料(例如铜)等。

堆叠封装可以使用简单的层叠方式,也可以使用先进的三维堆叠技术。

4. 封装工艺:根据封装材料的特性,使用合适的工艺进行封装,例如热压封装、UV固化等。

封装工艺可以确保封装材料与硅片的良好连接和密封。

5. 测试和包装:完成封装后,需要对封装芯片进行测试和包装。

测试可以包括电性能测试、可靠性测试、热敏性测试等。

测试合格的芯片可以进一步进行包装,例如微型封装、BGA封装等。

TSV封装具有广泛的应用领域,主要包括以下几个方面:1. 高性能计算:TSV封装可以实现多个处理器核心的高度集成,提供更高的计算能力和处理速度。

在超级计算机、服务器和工作站等领域,TSV封装已经成为了重要的技术手段。

2. 全球定位系统(GPS):GPS设备需要高度集成的封装方案,以满足复杂的导航和定位功能。

TSV封装可以提供更小尺寸、更高性能的GPS模块,使得GPS设备在车载导航、智能手机等应用中得到广泛应用。

半导体tsv工艺

半导体tsv工艺

半导体TSV工艺是一种新型的三维封装技术,它是通过在晶圆上开孔,将芯片内部的电路通过垂直连接器连接到晶圆的另一侧,从而实现芯片内部电路的三维堆叠。

TSV是Through Silicon Via的缩写,意为通过硅通孔。

半导体TSV工艺是一种先进的封装技术,它可以将多个芯片进行堆叠,从而实现更高的性能和更小的封装尺寸。

相比传统的封装技术,半导体TSV工艺具有以下优点:

1.更高的性能:半导体TSV工艺可以将多个芯片堆叠在一起,从而实现更高的性能。

由于芯片之间的距离更近,信号传输速度更快,同时也减少了信号传输的损失。

2.更小的封装尺寸:半导体TSV工艺可以将多个芯片堆叠在一起,从而实现更小的封装尺寸。

这对于移动设备等小型电子产品来说非常有利,可以实现更小巧的设计。

3.更低的功耗:半导体TSV工艺可以实现更短的信号传输路径,从而减少功耗。

这对于需要长时间使用的电子产品来说非常有利。

半导体TSV工艺的制造过程包括以下步骤:

1.晶圆准备:首先需要准备好晶圆,并在晶圆上进行刻蚀和清洗等处理,以便后续的工艺步骤。

2.TSV开孔:在晶圆上开孔,通过硅通孔将芯片内部的电路连接到晶圆的另一侧。

3.金属填充:将金属填充到开孔中,以便后续的连接。

4.封装:将多个芯片堆叠在一起,并进行封装,以保护芯片并提高性能。

半导体TSV工艺是一种非常先进的封装技术,它可以实现更高的性能和更小的封装尺寸。

随着电子产品的不断发展,半导体TSV工艺将会越来越广泛地应用于各种领域。

TSV技术

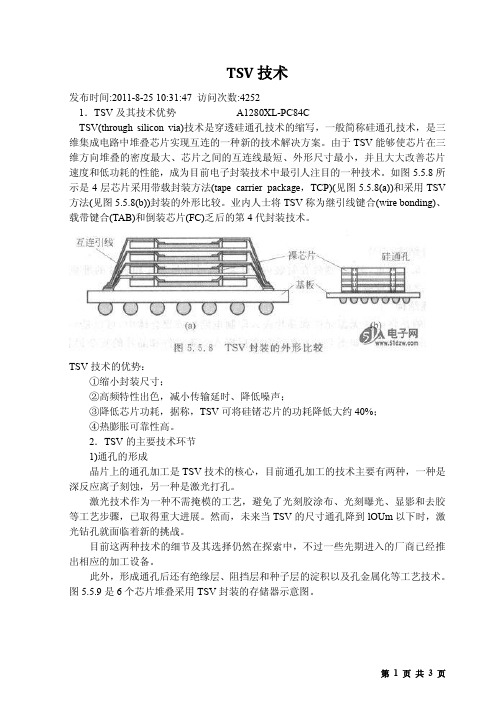

TSV技术发布时间:2011-8-25 10:31:47 访问次数:42521.TSV及其技术优势A1280XL-PC84CTSV(through silicon via)技术是穿透硅通孔技术的缩写,一般简称硅通孔技术,是三维集成电路中堆叠芯片实现互连的一种新的技术解决方案。

由于TSV能够使芯片在三维方向堆叠的密度最大、芯片之间的互连线最短、外形尺寸最小,并且大大改善芯片速度和低功耗的性能,成为目前电子封装技术中最引人注目的一种技术。

如图5.5.8所示是4层芯片采用带载封装方法(tape carrier package,TCP)(见图5.5.8(a))和采用TSV 方法(见图5.5.8(b))封装的外形比较。

业内人士将TSV称为继引线键合(wire bonding)、载带键合(TAB)和倒装芯片(FC)乏后的第4代封装技术。

TSV技术的优势:①缩小封装尺寸;②高频特性出色,减小传输延时、降低噪声;③降低芯片功耗,据称,TSV可将硅锗芯片的功耗降低大约40%;④热膨胀可靠性高。

2.TSV的主要技术环节1)通孔的形成晶片上的通孔加工是TSV技术的核心,目前通孔加工的技术主要有两种,一种是深反应离子刻蚀,另一种是激光打孔。

激光技术作为一种不需掩模的工艺,避免了光刻胶涂布、光刻曝光、显影和去胶等工艺步骤,已取得重大进展。

然而,未来当TSV的尺寸通孔降到lOUm以下时,激光钻孔就面临着新的挑战。

目前这两种技术的细节及其选择仍然在探索中,不过一些先期进入的厂商已经推出相应的加工设备。

此外,形成通孔后还有绝缘层、阻挡层和种子层的淀积以及孔金属化等工艺技术。

图5.5.9是6个芯片堆叠采用TSV封装的存储器示意图。

2)晶片减薄如果不用于3D封装,目前0.3~0.4mm的晶片厚度没有问题,但如果晶片用于3D封装则需要减薄,以保证形成通孔的孔径与厚度比例在合理范围,并且最终封装的厚度可以接受。

即使不考虑层堆叠的要求,单是芯片间的通乳互连技术就要求上层芯片的厚度在20~30μm,这是现有等离子开孔及金属沉积技术比较适用的厚度。

三维集成电路封装的TSV技术

三维集成电路封装的TSV技术1.引言三维集成电路(3D IC)和基于硅介质的2.5D集成电路具有低功耗、性能高、高功能集成度[1–4]等优点,被认为是克服摩尔定律局限性的重要电路。

为实现3D 和2.5D芯片集成,需要几个关键技术,如硅通孔(TSV)、晶片减薄处理以及晶圆/芯片粘接等。

TSV技术具有缩短互连路径和缩小封装尺寸的优点,因此被认为是3D集成的核心。

在3D和2.5D芯片集成过程中,TSV工艺可分为三种类型。

当TSV工艺在CMOS工艺进行之前完成时,工艺进程定义为“通孔优先(via first)”;当TSV工艺在CMOS工艺进行中完成时,CMOS中间工艺和后道工艺只能在TSV工艺完成后制作;当TSV在完成CMOS过程后进行时,工艺进程定义为“通孔收尾(via last)”,在已进行CMOS工艺后的衬底正面或背面进行TSV工艺。

选择TSV作为最终方案是在半导体行业最终应用要求。

TSV技术已被开发用于许多应用领域,如MEMS、移动电话、CMOS图像传感器(CIS)、生物应用程序设备和存储器等。

人们对TSV工艺进行了大量研究。

目前,由于制造成本相对较高,TSV在三维集成电路和先进封装应用中尚未普遍实现[5,6]。

本文将介绍当TSV制作直径较小、纵横比较高时,TSV的相关重要制造过程及相关失效模式。

此外,TSV制备有许多重要过程,包括深层反应离子蚀刻(DRIE)、介电层衬底、阻挡层和种晶层、填充、化学机械抛光(CMP)和Cu暴露过程,上述关键技术将在下面详细介绍。

2.TSV刻蚀技术TSV蚀刻是3D集成技术中的关键制造工艺,而广泛使用的Bosch工艺是深硅蚀刻的首选。

Bosch蚀刻工艺的高蚀刻速率为5~10 μm/min,对光刻胶的刻蚀选择性为50-100,甚至对于氧化层掩膜高达200。

该过程通过以下步骤执行:(1)利用六氟化硫作为等离子体刻蚀剂进行硅刻蚀;(2)与C4F8等离子体气体结合,生成质量良好的钝化膜,以防止下一刻蚀步骤中的横向效应;(3)利用六氟化硫作为等离子体刻蚀剂,对掩蔽层和Si进行进一步的离子轰击定向刻蚀,以形成一个较深的刻蚀深度。

集成电路封装材料-硅通孔相关材料

6.1.3 发展现状及趋势

比如,WLCSP图像传感器封装,要求沉积温度低于200 oC。低温下高 台阶覆盖率绝缘层主要通过TEOS源氧化硅CVD或聚合物材料CVD获得。 使用TEOS源,可以在深宽比达到10:1的孔内,在200 oC以内的温度下, 获得超过15%的台阶覆盖率。 国内TSV-CIS封装,采用聚合物材料作为绝缘层。在高深宽比的TSVCIS封装集成技术中,聚合物绝缘层工艺受到限制,要采用TEOSPECVD方法沉积氧化硅来制造绝缘层,该技术方案处于研发阶段,没 有得到大规模量产。

图6-1 不同元器件在三维方向上基于TSV的堆叠集成

TSV技术涉及的材料:除打孔的硅基体材料和填孔材料等关键主材料外, 在工艺过程中还包含绝缘层、黏附层和种子层材料等相关材料。

图6-2 TSV各层结构示意图

目录

6.1 绝缘层 6.2 黏附层和种子层

6.1 绝缘层

6.1.1 绝缘层在先进封装中的应用 6.1.2 绝缘层材料类别和材料特性 6.1.3 发展现状及趋势 6.1.4 新技术与材料发展ຫໍສະໝຸດ 6.1.4 新技术与材料发展

新型沉积技术 1)高分子聚合气相沉积技术PVPD 将CVD应用于聚合反应是一种新的聚合方法,称为气相沉积聚合。与传统高分子薄膜制 造方法(如湿法工艺)相比优点: (1)不含溶剂、添加剂、引发剂等,纯度高,对衬底不产生损伤。 (2)可以控制薄膜厚度,通过选择适当的沉积速率和时间,可得到所需厚度。 (3)薄膜质量好,膜厚均匀,表面光滑无针孔,且可以沉积在不同形状的表面上,保 形性好。 (4)聚合与成膜工艺合二为一,简化了制造流程。

6.1.3 发展现状及趋势

旋涂工艺相比CVD和喷涂工艺,具有设备成本低等显著优势,但加工超过 5:1深宽比的TSV时具有较大挑战。开发具有旋涂工艺的聚合物材料成为 关键研究方向。 聚合物材料具备低触变性、防流动性和保形涂覆等特点。可围绕材料主体 树脂、功能性纳米填料及关键助剂等展开研究。 中科院深圳先进技术研究所相继推出2:1和3:1适用于旋涂工艺的聚合物材 料,研究5:1。

TSV可靠性综述

0引言三维集成封装技术被公认为是超越摩尔定律的第四代封装技术。

硅通孔(Through Silicon Via ,TSV)技术是三维封装技术的关键[1]。

摩尔定律指出,硅片上的晶体管数量大约每两年翻一番[2]。

然而,由于晶体管的缩放比例和漏电的限制[3],摩尔定律不能永远持续下去。

随着晶体管尺寸越来越小,晶体管数量越来越多,晶体管之间的间距也越来越小。

最终会引起量子隧穿效应,电子会在两根金属线之间隧穿,导致短路[4-5]。

因此,存在一个极限,超过这个极限,摩尔定律将失效。

一种实现突破传统摩尔定律的封装摩尔定律被提出,封装摩尔定律是基于三维集成封装技术提出的[6]。

TSV 技术是指在硅片上进行微通孔加工,在硅片内部填充导电材料,通过TSV 技术实现芯片与芯片之间的垂直互连,是三维封装技术的关键技术[7-8]。

与传统的金丝键合相比,TSV 的优点是节省了外部导体所占的三维空间。

TSV 技术可以使微电子芯片封装实现最紧密的连接和最小的三维结构。

此外,由于芯片之间的互连线长度的缩短,大大降低了互连延迟,从而提高了运行速度。

并且由于互连电阻的降低,电路的功耗也大大降低[9]。

TSV 不仅广泛地应用于信息技术,而且在飞机、汽车和生物医学等新领域都得到了广泛的应用,因为三维大规模集成电路具有很多优势,如高性能、低功耗、多功能、小体积[10]。

TSV 是一种颠覆性技术,被认为是实现“超越摩尔定律”的有效途径,在未来主流器件的设计和生产中会得到广泛应用。

1TSV 可靠性概述随着三维集成封装技术的发展,TSV 技术已成为三维堆叠封装中最关键的技术之一。

作为芯片与芯片之间重要的物理连接和电气连接,TSV 的可靠性无疑是决定TSV 可靠性综述王硕1,马奎1,2,杨发顺1,2(1.贵州大学大数据与信息工程学院,贵州贵阳550025;2.半导体功率器件可靠性教育部工程研究中心,贵州贵阳550025)摘要:对硅通孔(Through Silicon Via ,TSV)技术的可靠性进行了综述,主要分为三个方面:热应力,工艺和压阻效应。

TSV技术的发展

TSV技术的发展、挑战和展望,3D IC 技术的一体化、3D硅技术的一体化摘要:3D集成技术包括3D IC集成,3D IC封装和3D 硅集成技术。

这三者是不同的技术,并且硅通孔技术将3D IC封装技术与3D IC集成技术、3D IC硅集成技术区分开来,因为后二者使用了该技术而3D IC封装没有。

硅通孔技术(TSV)是3D IC集成技术、3D 硅集成技术的核心。

也是研究的热点。

3D集成技术起源于当代,当然,3D IC/硅集成技术的革新、挑战与展望已是讨论的热点,还有它的蓝图。

最后,通用的、更低能耗的、加强热控制的3D IC集成封装系统相继被提出。

关键词:硅通孔技术,3D IC集成技术,3D 硅集成技术,活泼的、消极的互边导电物,C2W和W2W。

说明:电子产业自从1996年以来已成为世界上最大的产业。

截止2011年底已经创造了一万五千亿美元的价值。

其中电子工业最大的发明便是电子管(1947年),这也使得John Bardeen,Walter Brattain 和William赢得了1956年的诺贝尔物理学奖。

1958年Jack Kilby发明了集成电路(也使他获得了诺贝尔奖),六个月后Robert Noyce(他因在1990年去世而未能与Jack kilby分享诺贝尔奖)首创IC集成技术。

由戈登·摩尔在1965年提出的每二年便要在电路板上将晶体管的数量翻一倍的理论(也叫摩尔定律,为了更低的能耗),在过去的46年中已成为发展微电子产业最有力的指导。

这条定律强调可以通过单片集成系统(SOC)将平面技术和所有功能的集成(在2D层面)放到单片芯片中。

另一方面,这里所有功能的集成能通过3D集成技术例如3D IC封装,3D IC 集成[1],[2],[4]-[143],[168]-[201]和3D 硅集成[1],[2],[144]-[167],[168]-[201]得到实现,这些都会在1、2小节中提及。

TSV[过硅通孔]新型互连材料以及方法探究

![TSV[过硅通孔]新型互连材料以及方法探究](https://img.taocdn.com/s3/m/1ca8fb01844769eae009ed8c.png)

5kV ×3300 5 μ m

1952 SEI

热氧化工艺后通孔局部SEM照片

TSV通孔绝缘层的制备

在某些工艺中也有沉积绝缘层之前已 经完成一些金属化或者与高温工艺不 兼容的工艺,这种情况下也可以选择 工艺温度为200~400℃的PECVD工 艺制作TSV的绝缘层。

TSV通孔的金属填充

PVD法填充金属 使用PVD的方法向 TSV通孔中填充金 属。由于TSV通孔 过大的高宽比,使 得填充效果不理想。

激光刻蚀

TSV通孔形成

DRIE刻蚀后通孔SEM照片

TSV通孔绝缘层的制备

目前TSV通孔互连材料的 研究热点多为金属材料。 金属与硅基底之间需要沉 积一层绝缘层以确保电互 连的稳定。如果该工艺之 前没有金属层,热氧化工 艺可以在侧壁形成一层致 密的SiO2,其工艺温度为 700~1150℃,具有良好 的侧壁覆盖性能。

Three Dimensional Integrated Circuit

所谓的3D-IC是指由多个晶 片纵向堆叠组成的集成电路, 每个晶片之间的器件由过硅 通孔互连。

Through-Silicon-Via TSV

TSV简介

3D电路

TSV通孔 3D-IC 互连

降低器 件的RC 延迟

增加芯片单位面 积上的器件密度

CNT空间占有率过低 CNT与上下电极金属接触电阻过大

新型材料填充

针对于: CNT空间占有率过。

CNT与上下电极金 属接触电阻过大。

提出的解决方案

新型材料填充

将会遇到的问题:

如何解决TSV过大的深 宽比所带了的: 催化剂制备问题 CNT生长问题 CNT聚合后金属填 充的问题。

Thanks for your attention

SV工艺技术

TSV技术简介

TSV作为新一代封装技术,是通过在芯片和芯片之间,晶圆和晶圆之间制 造垂直导通,实现芯片之间互连的最新技术,能够在三维方向使得堆叠密 度最大,而外形尺寸最小,大大改善了芯片速度和低功耗性能。 硅通孔技术(TSV)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导 通,实现芯片之间互连的最新技术(见下图所示)。与以往的IC封装键合和 使用凸点的叠加技术不同,TSV能够使芯片在三维方向堆叠的密度最大, 外形尺寸最小,并且大大改善芯片速度和降低功耗的性能。

硅通孔技术(TSV)示意图

TSV技术简介

TSV技术被看做是一个必然的互连解决方案,是目前倒装芯片和引线键合型 叠层芯片解决方案的很好补充。许多封装专家认为TSV是互连技术的下一阶段。 实际上,TSV可以很好取代引线键合。 TSV能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,并且大大改善 芯片速度和低功耗的性能。因此,业内人士将TSV称为继引线键合 (WireBonding)、TAB(载带自动焊)和倒装芯片(FC)之后的第四代封装技 术。

• 封装内的裸片堆叠(图a) • 封装内的封装堆叠或称封装堆叠 (图b)

图a

图b

TSV技术简介

3D封装按照封装堆叠及IC裸芯片焊接(键合)技术近二十年来经历着三个重要 阶段,如下图所示。

有人将TSV技术称之为第四代封装技术。是基于微电子装联键合技术从软铅 焊、丝焊和芯片凸点倒装焊到通孔互连技术的不断进步发展而言。

3、后续工艺

电镀完成后就可以进行凸点制作、表面微加工、重新分布层、平坦化和集成等工艺。

芯片减薄

制作超薄芯片的过程原理示意图

TSV键合技术

TSV键合技术

TSV键合采用工艺有金属—金属键合技术和高分子粘结键合等。 金属—金属键合技术是一种趋势,因为这种技术可以同时实现机械和电学的 接触界面。如铜-铜键合在350℃~400℃温度下施加压力超过30min,接着 在350℃~400℃下的氮气气氛退火30min~60min完成。这种技术使用金 属对TSV进行封帽,之后采用氧化物和金属同步CMP进行平坦化,经过专利保 护的表面处理技术,可使用标准的键合/对准机在大气环境下1min~2min实 现芯片或者晶圆的键合。在350℃温度下施加压力,在低CoO键合操作下可 以获得单一的金属界面。

硅通孔(TSV)电学传输特性分析与优化

硅通孔(TSV)电学传输特性分析与优化硅通孔(TSV)电学传输特性分析与优化摘要:硅通孔(TSV)是一种用于芯片内部互联的三维封装技术。

本文通过对TSV电学传输特性的分析与优化,探讨了TSV的制备工艺对其性能的影响,并提出了一些优化措施。

1. 引言随着芯片尺寸的不断减小和集成度的不断提高,二维封装方式逐渐不能满足芯片内部大规模互联的需求。

硅通孔(TSV)作为一种三维封装技术,能够实现芯片内部的垂直互联,为芯片的高集成度提供可能。

TSV的电学传输特性的分析与优化对于实现高性能的三维封装至关重要。

2. TSV的制备工艺TSV的制备通常包括刻蚀、填充和研磨等步骤。

刻蚀是将硅衬底上的孔洞形成的过程,可以采用干法或湿法刻蚀。

填充是将导电材料填充到TSV中,常用的填充材料有铜、银等。

研磨是将填充材料的余量删减至需要的高度,以便与芯片的上下层相连接。

制备工艺的参数设置和优化对于TSV的电学传输特性具有重要影响。

3. TSV的电学传输特性分析TSV的电学传输特性可以通过测试TSV的电阻和电容来进行分析。

电阻是TSV的主要电学性能指标之一,影响着信号传输的速度和功耗。

电阻的大小与TSV的尺寸、填充材料和制备工艺等因素有关。

电容是TSV的另一个重要性能指标,反映了TSV 的电荷传输能力。

电容的大小与TSV的尺寸、绝缘层的厚度等因素相关。

4. TSV的电学传输特性优化为了优化TSV的电学传输特性,可以采取以下措施:4.1 优化制备工艺参数制备工艺参数的优化对于TSV的电学性能具有重要影响。

如刻蚀参数的优化可以改善TSV的表面平整度,减小接触电阻。

填充材料的选择和填充参数的优化可以改善TSV的导电性能。

研磨参数的优化可以减小TSV的表面粗糙度,降低剩余电阻。

4.2 优化填充材料填充材料的选择对TSV的电阻有着重要影响。

铜是一种常用的填充材料,具有较低的电阻和较高的导电性能。

然而,铜容易产生应力,导致TSV的可靠性下降。

详解TSV(硅通孔技术)封装技术

详解TSV(硅通孔技术)封装技术硅通孔技术(Through Silicon Via,TSV)技术是一项高密度封装技术,正在逐渐取代目前工艺比较成熟的引线键合技术,被认为是第四代封装技术。

TSV 技术通过铜、钨、多晶硅等导电物质的填充,实现硅通孔的垂直电气互连。

硅通孔技术可以通过垂直互连减小互联长度,减小信号延迟,降低电容/ 电感,实现芯片间的低功耗,高速通讯,增加宽带和实现器件集成的小型化。

基于TSV 技术的3D 封装主要有以下几个方面优势:1)更好的电气互连性能,2)更宽的带宽,3)更高的互连密度,4)更低的功耗,5)更小的尺寸,6)更轻的质量。

TSV 工艺主要包括深硅刻蚀形成微孔,绝缘层/阻挡层/种子层的沉积,深孔填充,化学机械抛光,减薄、pad 的制备及再分布线制备等工艺技术。

主要工艺包括几个部分:(1)通孔的形成;(2)绝缘层、阻挡层和种子层的淀积;(3)铜的填充(电镀)、去除和再分布引线(RDL)电镀;(4)晶圆减薄;(5)晶圆/芯片对准、键合与切片。

TSV 深孔的填充技术是3D 集成的关键技术,也是难度较大的一个环节,TSV 填充效果直接关系到集成技术的可靠性和良率等问题,而高的可靠性和良率对于3D TSV 堆叠集成实用化是至关重要的。

另外一个方面为在基片减薄过程中保持良好的完整性,避免裂纹扩展是TSV 工艺过程中的另一个难点。

目前主要的技术难点分为几个方面:(1)通孔的刻蚀激光刻蚀、深反应离子刻蚀;(2)通孔的填充材料(多晶硅、铜、钨和高分子导体等)和技术(电镀、化学气相沉积、高分子涂布等);(3)工艺流程先通孔或后通孔技术;(4)堆叠形式晶圆到晶圆、芯片到晶圆或芯片到芯片;(5)键合方式直接Cu-Cu 键合、粘接、直接熔合、焊接和混合等;(6)超薄晶圆的处理是否使用载体。

目前,3D-TSV 系统封装技术主要应用于表1 TSV 三维封装应用领域经过数年研发,目前形成具有高良率、不同深宽比结构、高密度微孔、高导通率的3D 封装硅基转接板,可以广泛应用于射频、存储等芯片的三维封装领域。

3D封装与硅通孔TSV工艺技术

TSV技术简介

TSV技术

TSV (through silicon via)穿透硅通孔技术,简称硅通孔技术。TSV是利 用垂直硅通孔完成芯片间互连的方法, 由于连接距离更短、强度更高, 它能 实现更小更薄而性能更好、密度更高、尺寸和重量明显减小的封装, 同时还 能用于异种芯片之间的互连。

图1所示是4层芯片采用载带封装方法 (图 1(a))和采用TSV方法(图1(b)) 封装的外形比较。

一体机示意图(东京精密PG200/300)

芯片减薄

存在的问题:

•机械研磨和化学机械抛光还可能会在硅晶圆表面产生严重的内应力,这些应力 会引发弯曲和翘曲。同时,由于是先用铜将 TSV填满后进行 CMP工艺这样在过 程中铜和硅容易发生扩散而且破坏绝缘层,从而破坏 TSV互连。

•针对以上问题,袁娇娇等人研究通过对硅晶圆进行局部减薄来实现的局部减薄, 即将硅晶圆的大部分减薄 利用没有减薄的部分支撑硅晶圆完成表面微加工工艺 局部减薄是通过对硅晶圆局部刻蚀一定深度以达到局部减薄的目的。

TSV技术简介

1.填埋型3D封装

——在各类基板内或多层布线介质层中“埋置”R、C或IC等元器件,最上 层再贴装SMC/SMD来实现立体封装。

TSV技术简介

2.有源基板型3D封装

——Si圆片规模集成(WLS)后的有源基板上再实行多层布线,最上层再贴装 SMC/SMD。

TSV技术简介

3.叠层型3D封装

芯片减薄

减薄技术面临的首要挑战就是超薄化工艺所要求的<50μm的减薄能力。传

统上,减薄工艺仅仅需要将硅片从晶圆加工完成时的原始厚度减薄到300~ 400μm。在这个厚度上,硅片仍然具有相当的厚度来容忍减薄工程中的磨削 对硅片的损伤及内在应力,同时其刚性也足以使硅片保持原有的平整状态。 另外,随着微电子工业的迅猛发展,圆片直径越来越大,当150mm、 200mm甚至300mm圆片被减薄到150μm以下时,圆片翘曲和边缘损伤问 题变得尤为严重。

硅通孔(TSV)工艺学习报告

1. 引言............................................................................................................................ 2 2. 分类............................................................................................................................ 2 3. 优点............................................................................................................................ 2 4. 硅通孔的发展历程.................................................................................................... 3 5. 工艺流程.................................................................................................................... 3

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

详解TSV(硅通孔技术)封装技术

硅通孔技术(Through Silicon Via,TSV)技术是一项高密度封装技术,正在逐渐取代目前工艺比较成熟的引线键合技术,被认为是第四代封装技术。

TSV 技术通过铜、钨、多晶硅等导电物质的填充,实现硅通孔的垂直电气互连。

硅通孔技术可以通过垂直互连减小互联长度,减小信号延迟,降低电容/ 电感,实现芯片间的低功耗,高速通讯,增加宽带和实现器件集成的小型化。

基于TSV 技术的3D 封装主要有以下几个方面优势:

1)更好的电气互连性能,

2)更宽的带宽,

3)更高的互连密度,

4)更低的功耗,

5)更小的尺寸,

6)更轻的质量。

TSV 工艺主要包括深硅刻蚀形成微孔,绝缘层/阻挡层/种子层的沉积,

深孔填充,化学机械抛光,减薄、pad 的制备及再分布线制备等工艺技术。

主要工艺包括几个部分:

(1)通孔的形成;

(2)绝缘层、阻挡层和种子层的淀积;

(3)铜的填充(电镀)、去除和再分布引线(RDL)电镀;

(4)晶圆减薄;

(5)晶圆/芯片对准、键合与切片。

TSV 深孔的填充技术是3D 集成的关键技术,也是难度较大的一个环节,。