SpectreUltrasim与Spectre-Verilog 仿真介绍

集成电路设计CAD_EDA工具实用教程1-Spectre_Verilog数模混合仿真

同时包含模拟和数字两个仿真核

处理速度快,能处理的电路规模极大,但需要解决模拟仿真核和数字 仿真核之间的通信问题;另外,由于数字逻辑仿真器和模拟仿真器的输 入、输出数据是不一样的,还必须在模拟仿真核和数字仿真核之间实现 模拟信号和数字信号的相互转换。

共27页

Q&A

9

Creating Analog Block

3

共27页

高精度模拟/射频电路仿真器

1、Spectre/SpectreRF (Cadence)

2、Hspice/HspiceRF (Synopsys)

3、Ads (Agilent 主要针对RF) 4、Eldo (Mentor Graphics) 5、Saber (Synopsys)

4

共27页

16

Check Block Partition

Change analog & digital stop views to match the stop views in your hierarchy editor (as below)

共27页

17

Check Partition Results

Spectre–Verilog 混合信号仿真

共27页

1

几家EDA软件公司

1、Cadence 2、Synopsys(收购Avanti) 3、Mentor Graphics 4、Silvaco

5、SpringSoft

2

共27页

SPICE仿真器

SPICE : a general-purpose analog circuit simulator developed by the University of California, Berkeley. It is used for nonlinear DC, nonlinear transient, and linear AC analysis. Hspice: a general-purpose circuit simulator from Avanti. It has an extensive set of built-in device models, including models for small geometry MOSFETs and MESFETs. The program is compatible with SPICE input formats. Cadence supports a library of primitives and a full interface for Hspice. Spectre: SPICE-alike analog simulator developed by Cadence.

04_集成电路_第三讲_Spectre、Ultrasim和Spectre-Verilog_仿真介绍

共61页

pnp gnd vdc idc vpulse vpwl

vsin

14

元器件symbol视图

2020/1/3

共61页

15

模拟仿真的设置(重点)

Composerschamatic界面中 的Tools → Analog Environment项可 以打开Analog Design Environment 窗口, 如右图所示。

2020/1/3

共61页

11

2020/1/3

工具栏介绍

从上至下:

1.Check and Save

2.Save

3.Zoom in by 2 ]

4.Zoom out by 2 [

5.Stretch

s

6.Copy

c

7.Delete

Del

8.Undo

u

9.Property

q

10.Instance

i

共61页

2020/1/3

注意! View要选择symbol

共61页

13

常用analoglib库的元器件

器件 电阻 电容 电感 NMOS PMOS

npn管

Cell 名称 res cap ind

nmos4 pmos4

npn

pnp管 地

直流电压源 直流电流源 方波发生源

可编程方波发 生源

正弦波发生源

2020/1/3

一、模拟前端EDA工具简介

2020/1/3

共61页

3

电子系统的层次

上游

2020/1/3

共61页

下游

4

模拟集成电路的设计流程

1.交互式电路图输入

2.电路仿真 3.版图设计

集成电路EDA与验证技术课件:模拟集成电路设计与仿真

模拟集成电路设计与仿真

常用命令格式: (1) DEFINE 格式:DEFINE <库名> <库路径> 例: DEFINE sample /export/cadence/IC615USER5/tools.lnx86/dfII/samples/cdslib/sa mple (2) INCLUDE 格式:INCLUDE <另外一个cds.lib 的全路径>

模拟集成电路设计与仿真

图3.2 Spectre中包含的各种仿真器

模拟集成电路设计与仿真

2.精确的晶体管模型 Spectre为所有的仿真器提供一致的器件模型,这有利于 消除不同模型间的相关性,从而得到快速收敛的仿真结果。 模型的一致性也保证了器件模型在升级时可以同时应用于所 有的仿真器。 3.高效的程序语言和网表支持 Spectre仿真平台支持多种设计提取方法,并兼容绝大多 数SPICE输入平台。Spectre可以读取Spectre、SPICE以及 Verilog-A格式的器件模型,并支持标准的Verilog-AMS、 VHDL-AMS、Verilog-A、Verilog以及VHDL格式的文本输 入。

模拟集成电路设计与仿真

5.有力衔接了版图设计平台 对于完整的版图设计平台而言,Spectre是不可或缺的重 要环节,它能方便地利用提取的寄生元件参数来快速完成后 仿真(post-layout simulation)的模拟,并与前仿真(pre-layout simulation)的模拟结果作比较,紧密的连接了电路 (Schematic)和版图(layout)的设计。 6.交互的仿真模式 设计者可以在仿真过程中快速改变参数,并在不断调整 参数和模拟之中找到最佳的电路设计结果,减少电路设计者 模拟所花费的时间。

IC设计经验总结

I C设计经验总结一、芯片设计之前准备工作:1)根据具体项目的时间要求预订MPW班次,这个可以多种途径完成。

(1):一方面可以跟中科院EDA中心秦毅等老师联系,了解各个工艺以及各个班次的时间。

半导体所是EDA中心的会员单位,他们会很热心的帮助完成。

(2):另一方面可以和具体项目合作的单位如清华等,根据他们的流片时间来制定自己的流片计划。

2)仔细核对设计库的版本更新情况,包括PDK、Spectre Model以及RuleDecks。

这些信息可以直接可以从中科院EDA中心获得,或者从相应的合作单位进行沟通统一。

这一点对后续的设计很重要,请务必要引起重视。

3)得到新的工艺库必须整体的熟悉一下,好好的查看里面的Document以及Userguide之类的,里面的很多信息对实际设计很有帮助。

安装工艺库的过程会根据具体设计要求做出一些选着。

如TSMC65nm工艺库在安装过程中会提示是否选着RF工艺、电感是否使用厚层金属、MIM电容的单位面积电容值等之类的。

4)制定TapeOut的具体Schedule. 这个Schedule的制订必须请相关有经验的人来核实,第一次TapeOut的人往往缺乏实际经验,对时间的安排可能会不合理。

一旦Schedule制订好后,必须严格按照这个时间表执行。

当然必须赶早不赶晚!二、芯片设计基本系统框图一图一三、模拟IC设计基本流程3.1) 设计框图如下图二电路样式选择电路结构确定参数的选定以及仿真优化以及可靠性仿真图二3.2 电路的式样确定这个主要是根据系统设计结果,分析和确定模拟电路的详细的式样。

3.3 电路的结构确定根据单元模块电路的功耗、代价等各个指标的折中分析,确定各个单元模块的具体实现电路形式,如滤波器是无源滤波器还是有源滤波器,有正交VCO产生I/Q信号还是通过/2分频器来实现I/Q信号,用差分形式还是用单路形式等等。

在具体电路的选取过程中,我们需要查阅了大量的IEEE文献,从中选取了比较成熟的,应用较广的电路结构来进行我们的设计工作。

【VIP专享】数模混合仿真详细文档

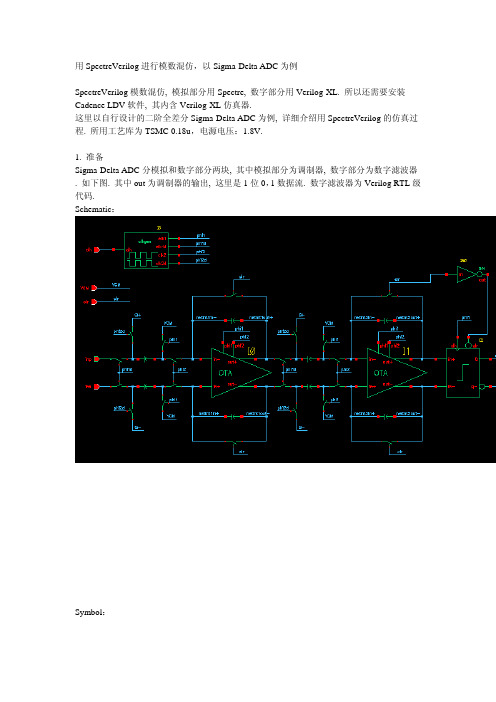

用SpectreVerilog进行模数混仿,以Sigma-Delta ADC为例SpectreVerilog模数混仿, 模拟部分用Spectre, 数字部分用Verilog-XL. 所以还需要安装Cadence LDV软件, 其内含Verilog-XL仿真器.这里以自行设计的二阶全差分Sigma-Delta ADC为例, 详细介绍用SpectreVerilog的仿真过程. 所用工艺库为TSMC 0.18u,电源电压:1.8V.1. 准备Sigma-Delta ADC分模拟和数字部分两块, 其中模拟部分为调制器, 数字部分为数字滤波器. 如下图. 其中out为调制器的输出, 这里是1位0,1数据流. 数字滤波器为Verilog RTL级代码.Schematic:Symbol:Verilog Code:module DigitalFilter (in2out, out, clk, clr, in);output in2out;output [`wordsize-1:0] out;input clk;input clr;input in;reg in2out;wire clk_half1, clk_half2;……Endmodule同时为了直观的观看输出结果,因此把输出的数字字转化为模拟量,这里用Verilog-A做一个理想的DA转换器。

因此最好事先用Spectre仿真模拟部分, 用ModelSim或Verilog-XL等仿真数字部分. 这里假定我们已有:1) 模拟部分的原理图(包括Symbol);2) 数字部分的Verilog代码,DigitalFilter.v, 模块名:DigitalFilter(in2out,out,clk,clr,in);3) 数字部分的TestBench代码, DigitalFilter_TB.v, 模块名: DigitalFilter_TB.下图为最终的系统图:2. 创建数字模块的Symbol1) 新建一个Cell, View Name为symbol, Tool: Composer-Symbol.2) 画Symbol. 简单地, 画一个矩形框, 添加几个Lable, 然后添加Pin.3) 添加Pin. 左边输入, 右边输出. 对于多位的pin可以用如out<7:0>的样式作为pin的名字. 注意: 与模拟部分相连的多位Pin最好不要用一个pin, 而要用多个. 如下图.4) 创建对应的Verilog文件. 在symbol编辑器中, Design菜单->CreatCellView->From CellView.会弹出的对话框, Tool/Data Type一栏选择Verilog-Editor, 则To View Name会变为functional.点击OK, 会弹出错误对话框, 点No. 自动弹出VI编辑器, 可以看到已经生成Verilog代码的空壳.代码文件的路径在VI编辑器的标题栏上. 下面要做的就是把我们的数字模块(不是TestBench)的代码填进去. 如果不想用VI编辑器, 也可以用其他文本编辑器. 复制代码时最好不要动自动生成的代码. 经测试, 所有代码最好放在一个文件中.这一步之后,数字部分就会有functional和symbol两个View。

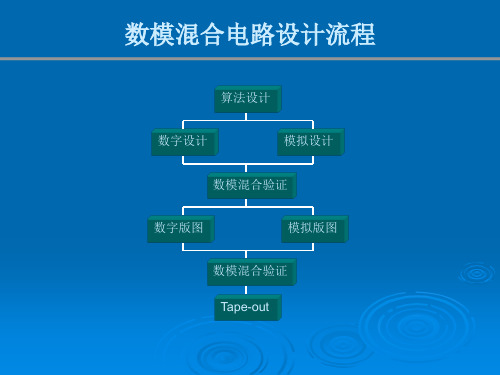

Cadence 实验系列12_数模混合电路设计_spetreVerilog!10

制作顶层文件

混合信号模拟的特点

建立层次文件

操设作置示仿例真环境

仿真

数字设计

模拟设计

2

1制作顶层文件 3

4

建立层次化文件

配置仿真环境 仿真验证

2-1 数字-模拟电路设计

1.数-模电路设计 2.数字电路设计 3. 模拟电路设计

2-1 数字-模拟电路设计

1.数-模电路设计

手工型

顺序型

偶合型

+

配对型

= spetr巢(套l型ock-step)同步法 集成型 = Cadence spetreverilog

框架型

1-1 数模混合模拟的定义

3. 混合信号模拟 Cadence spetreverilog解决方案

混合仿真环境

2.设置模式层次显示

2-4 设置仿真环境

2.设置Analog环境 1.设置仿真器工作模式

2-4 设置仿真环境

2. 配置仿真环境 2.设置引用工艺库

2-4 设置仿真环境

2. 配置仿真环境 3.设置模拟仿真器激励

2-4 设置仿真环境

2. 配置仿真环境 4.设置数字仿真器激励

2-4 设置仿真环境

schemetic

schemetic

Verilog-editor

时钟发生器

计数器

2-1 数字-模拟电路设计

1.数-模电路设计

Verilog

Lib

Counter_1

Clk_1

symbo schem

2-1 数字-模拟电路设计

1.数-模电路设计

1 建立自己的设计库 名字 design_101

2-1 数字-模拟电路设计

对Verilog仿真过程的理解

对Verilog仿真过程的理解前⾔顺序执⾏的仿真器如何仿真并⾏的Verilog语⾔?仿真器中Verilog的并⾏性是通过其语义(Verilog的语⾔含义)仿真出来的,Verilog语⾔的语义是专门为仿真定义的。

如果设计的Verilog源代码不符合Verilog仿真语义,对Verilog代码的仿真可能出现仿真歧义,也就是代码仿真结果会与综合后时间的门级⽹表功能不⼀致。

⼀、概念理解:1、仿真时间仿真电路所⽤的真实时间进⾏建模。

仿真时间由硬件电路的延时参数决定,也是硬件电仿真时间是指由仿真器维护的时间值,⽤来对仿真电路所⽤的真实时间进⾏建模路的实际⼯作时间,所有仿真⼯作都是严格按仿真时间向前推进的,在什么时间执⾏什么操作。

仿真时间与仿真软件在计算机上的运⾏时间没有任何关系。

若优先级相同,如果在当前仿真时间有多个事件需要执⾏,那么⾸先要根据它们的优先级(在事件队列中的优先级)来判定谁先谁后。

若优先级相同,则执⾏顺序随机(不同仿真器的⾏为可能不同)。

则执⾏顺序随机(不同仿真器的⾏为可能不同)2、事件驱动事件驱动类型的仿真。

Verilog语⾔⽤来对数字系统的功能和时序进⾏建模,模型的仿真过程是围绕时间来组织的。

功能仿真是⼀种事件驱动类型的仿真事件是指在特定时刻,模型中值的变化。

⼀个更新事件被执⾏后,所有对改事件敏感的进程都将以随机的顺序计算。

⽐如,在被仿真电事件路中,线⽹或寄存器的值的任何改变被认为是⼀个更新事件。

计算事件和更新事件之间循环往复的互相触发,计算事件。

计算事件和更新事件之间循环往复的互相触发,进程进程对更新事件敏感,进程(门或⾏为模型)的计算也是⼀个事件,叫做计算事推动了仿真时间向前推进。

推动了仿真时间向前推进3、进程进程是Verilog语⾔中的独⽴执⾏单元,⽤Verilog描述的数字系统正式由⼀个个进程组成的。

进程包括原语、模块(module)、initial过程块、always过程块、连续赋值语句、异步任务、过程赋值语句等。

数模混合仿真详细文档

用SpectreVerilog进行模数混仿,以Sigma-Delta ADC为例SpectreVerilog模数混仿, 模拟部分用Spectre, 数字部分用Verilog-XL. 所以还需要安装Cadence LDV软件, 其内含Verilog-XL仿真器.这里以自行设计的二阶全差分Sigma-Delta ADC为例, 详细介绍用SpectreVerilog的仿真过程. 所用工艺库为TSMC 0.18u,电源电压:1.8V.1. 准备Sigma-Delta ADC分模拟和数字部分两块, 其中模拟部分为调制器, 数字部分为数字滤波器. 如下图. 其中out为调制器的输出, 这里是1位0,1数据流. 数字滤波器为Verilog RTL级代码.Schematic:Symbol:Verilog Code:module DigitalFilter (in2out, out, clk, clr, in);output in2out;output [`wordsize-1:0] out;input clk;input clr;input in;reg in2out;wire clk_half1, clk_half2;……Endmodule同时为了直观的观看输出结果,因此把输出的数字字转化为模拟量,这里用Verilog-A做一个理想的DA转换器。

因此最好事先用Spectre仿真模拟部分, 用ModelSim或Verilog-XL等仿真数字部分. 这里假定我们已有:1) 模拟部分的原理图(包括Symbol);2) 数字部分的Verilog代码,DigitalFilter.v, 模块名:DigitalFilter(in2out,out,clk,clr,in);3) 数字部分的TestBench代码, DigitalFilter_TB.v, 模块名: DigitalFilter_TB.下图为最终的系统图:2. 创建数字模块的Symbol1) 新建一个Cell, View Name为symbol, Tool: Composer-Symbol.2) 画Symbol. 简单地, 画一个矩形框, 添加几个Lable, 然后添加Pin.3) 添加Pin. 左边输入, 右边输出. 对于多位的pin可以用如out<7:0>的样式作为pin的名字. 注意: 与模拟部分相连的多位Pin最好不要用一个pin, 而要用多个. 如下图.4) 创建对应的Verilog文件. 在symbol编辑器中, Design菜单->CreatCellView->From CellView.会弹出的对话框, Tool/Data Type一栏选择Verilog-Editor, 则To View Name会变为functional.点击OK, 会弹出错误对话框, 点No. 自动弹出VI编辑器, 可以看到已经生成Verilog代码的空壳.代码文件的路径在VI编辑器的标题栏上. 下面要做的就是把我们的数字模块(不是TestBench)的代码填进去. 如果不想用VI编辑器, 也可以用其他文本编辑器. 复制代码时最好不要动自动生成的代码. 经测试, 所有代码最好放在一个文件中.这一步之后,数字部分就会有functional和symbol两个View。

用SpectreVerilog进行模数混仿

用SpectreVerilog进行模数混仿,以Sigma-Delta ADC为例loghereloghere@SpectreVerilog模数混仿, 模拟部分用Spectre, 数字部分用Verilog-XL. 所以还需要安装Cadence LDV软件, 其内含Verilog-XL仿真器.这里以自行设计的二阶全差分Sigma-Delta ADC为例, 详细介绍用SpectreVerilog的仿真过程. 所用工艺库为TSMC 0.18u,电源电压:1.8V.1. 准备Sigma-Delta ADC分模拟和数字部分两块, 其中模拟部分为调制器, 数字部分为数字滤波器. 如下图. 其中out为调制器的输出, 这里是1位0,1数据流. 数字滤波器为Verilog RTL级代码.Schematic:Symbol:Verilog Code:module DigitalFilter (in2out, out, clk, clr, in);output in2out;output [`wordsize-1:0] out;input clk;input clr;input in;reg in2out;wire clk_half1, clk_half2;……Endmodule同时为了直观的观看输出结果,因此把输出的数字字转化为模拟量,这里用Verilog-A做一个理想的DA转换器。

因此最好事先用Spectre仿真模拟部分, 用ModelSim或Verilog-XL等仿真数字部分. 这里假定我们已有:1) 模拟部分的原理图(包括Symbol);2) 数字部分的Verilog代码,DigitalFilter.v, 模块名:DigitalFilter(in2out,out,clk,clr,in);3) 数字部分的TestBench代码, DigitalFilter_TB.v, 模块名: DigitalFilter_TB.下图为最终的系统图:2. 创建数字模块的Symbol1) 新建一个Cell, View Name为symbol, Tool: Composer-Symbol.2) 画Symbol. 简单地, 画一个矩形框, 添加几个Lable, 然后添加Pin.3) 添加Pin. 左边输入, 右边输出. 对于多位的pin可以用如out<7:0>的样式作为pin的名字. 注意: 与模拟部分相连的多位Pin最好不要用一个pin, 而要用多个. 如下图.4) 创建对应的Verilog文件. 在symbol编辑器中, Design菜单->CreatCellView->From CellView.会弹出的对话框, Tool/Data Type一栏选择Verilog-Editor, 则To View Name会变为functional.点击OK, 会弹出错误对话框, 点No. 自动弹出VI编辑器, 可以看到已经生成Verilog代码的空壳.代码文件的路径在VI编辑器的标题栏上. 下面要做的就是把我们的数字模块(不是TestBench)的代码填进去. 如果不想用VI编辑器, 也可以用其他文本编辑器. 复制代码时最好不要动自动生成的代码. 经测试, 所有代码最好放在一个文件中.这一步之后,数字部分就会有functional和symbol两个View。

集成电路设计CADEDA工具实用2-Spice_Spectre

Cadence中Spectre的模拟仿真 Hspice的使用 Ultrasim仿真技术

2020/1/30

共79页

1

模拟集成电路的设计流程

1.交互式电路图输入

2.电路仿真 3.版图设计

全定制

4.版图的验证(DRC LVS)

5.寄生参数提取

6.后仿真

7.流片

2020/1/30

2020/1/30

共79页

16

2020/1/30

工具栏介绍

从上至下:

1.Check and Save

2.Save

3.Zoom in by 2 ]

4.Zoom out by 2 [

5.Stretch

s

6.Copy

2020/1/30

共79页

4

Cadenc软件简介

Cadence 提供了一个大型的EDA 软件包,它包括: ASIC 设计

全定制IC设计工具Virtuoso Schematic Composer 电路仿真工具Analog Design Environment FPGA 设计 PCB设计

2020/1/30

共79页

12

Tools菜单

在Tools菜单下,比较常 用的菜单项有

Library Manager

Library Path Editor

Technology File Manager

Library Manager项打开的是库管 理器。在窗口的各部分中,分别 显示的是Library、Category、Cell、 View相应的内容。

共79页

6

一、进入Cadence软件包

方法一

安装并运行exeed软件, 使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,然后点击 Open。

virtuoso_mmsim简介

BENEFITS

DESIGN QUALITY AND CONVERGENCE

• Uses silicon-accurate device models across all simulators that are universally supported by all foundry process design kits (PDKs) • Supports shared syntax and abstractions across all engines and minimizes translation when moving among design domains • Features tight integration with the Virtuoso Analog Design Environment— with common use model, cross-probing, and backannotation capabilities • Features tight integration into the Incisive Logic Design Environment— with common-use model, debugging, waveform viewing, and language support • Provides a proven, comprehensive suite of high-precision analyses with a simple use model, delivering accurate results • Offers post-layout simulation and signoff analysis to ensure first-pass silicon realization success

SpectreVerilog仿真使用方法

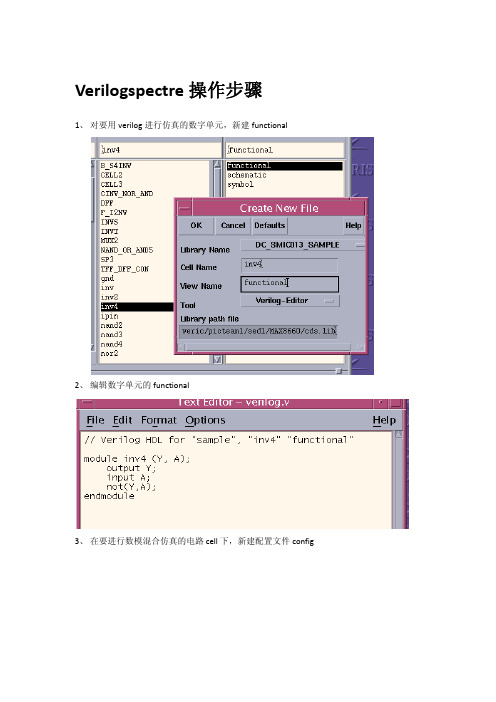

Verilogspectre操作步骤

1、对要用verilog进行仿真的数字单元,新建functional

2、编辑数字单元的functional

3、在要进行数模混合仿真的电路cell下,新建配置文件config

4、配置文件config建立后,自动弹出初始化配置窗口。

单击Browse,将config文件链接到

要数模混合仿真的电路原理图文件,点击OK保存。

5、点击Use Template… 选择要数模混合仿真的模板,这里选择spectreVerilog。

单击OK完

成初始化。

6、对要数模混合仿真的电路进行配置。

如下,将sample库内的数字单元设置用verilog仿

真,在view found栏内显示functional,表示其已经设置成数字仿真。

如果需要用模拟仿真,右击此栏,弹出如下子窗口,选择用schematic。

7、配置完成后单击保存,退出配置窗口。

双击config弹出如下窗口,上面表示打开配置文

件,下面表示打开原理图文件,这里已经配置完成,只打开原理图文件。

8、打开电路原理图后,点击tools‐> analog enviroment,弹出仿真对话框,点击setup,选

择simulator/Directory/Host…

9、弹出选择仿真器窗口,在simulator栏内选择spectreverilog作为仿真工具,点击OK。

自

动载入数模混合仿真环境。

接下来设置和spectre仿真相同,不再赘述。

verilog仿真流程

verilog仿真流程一、环境搭建在进行Verilog仿真前,首先需要搭建仿真环境。

常用的Verilog仿真工具有ModelSim、VCS等。

这里以ModelSim为例来介绍环境搭建步骤。

1. 下载ModelSim软件并安装到电脑中,根据软件的安装向导逐步操作即可。

2. 创建一个新的工程,选择File -> New -> Project来创建一个新的工程。

3. 在工程中添加需要仿真的Verilog文件,选择File -> Add to Project -> Existing File来添加Verilog文件。

4. 配置仿真波形,选择Simulate -> Start Simulation来开始仿真。

二、编写Verilog代码在搭建好仿真环境后,接下来就是编写Verilog代码。

Verilog是一种硬件描述语言,通常用来描述数字电路的行为。

Verilog代码由模块、端口和信号等组成,下面是一个简单的Verilog模块示例:```verilogmodule adder(input [7:0] a,input [7:0] b,output [8:0] sum);assign sum = a + b;endmodule```在这个示例中,我们定义了一个名为adder的模块,它有两个8位输入端口a和b,以及一个9位输出端口sum。

在模块体中,我们使用assign语句来实现a和b的加法运算,并将结果赋给sum。

三、编译Verilog代码在编写好Verilog代码后,需要对代码进行编译。

编译的目的是将Verilog代码转换成仿真可执行的二进制文件。

在ModelSim中,可以通过点击Compile按钮或者在命令行中输入vlog命令来进行编译。

```verilogvlog adder.v```这样就会生成一个adder.v文件,里面包含了编译后的二进制代码。

四、仿真测试在编译成功后,接下来就是对设计的Verilog模块进行仿真测试。

集成电路设计CAD_EDA工具实用教程1-Spectre_Verilog数模混合仿真

共27页

26

THANK YOU!

共27页

27

同时包含模拟和数字两个仿真核

处理速度快,能处理的电路规模极大,但需要解决模拟仿真核和数字 仿真核之间的通信问题;另外,由于数字逻辑仿真器和模拟仿真器的输 入、输出数据是不一样的,还必须在模拟仿真核和数字仿真核之间实现 模拟信号和数字信号的相互转换。

共27页

Q&A

9

Creating Analog Block

共27页

8

Mixed-Signal Simulator 的基本结构

以模拟电路仿真器为核心

在处理数模混合电路时将数字部分等效为相应的简化的模拟电路、或 者采用解析函数来表示逻辑模块的行为,然后对整个系统采用模拟电路 的方法进行模拟。优点:模拟结果精确、能处理的电路规模比较大,模 拟速度也有显著提高。缺点:比逻辑模拟器还是慢很多。

共27页

24

Submit the Simulation

Execute the simulation job with Run, or create the netlist with Netlist

start simulation

共27页

25

Results

数 字 输 出 数字 /模 拟输 入

模 拟 输 出

选择SpectreVerilog

共27页 23

Choose Analysis Type

Invoke the analysis setting window

For Mixed-Signal simulation, only tran is meaningful Set the simulation time Check this box to enable this simulation

SpectreUltrasim与Spectre-Verilog 仿真介绍

2019/12/12

共61页

29

Ultrasim仿真环境设置

因为UltraSim已经完全集成在Cadence的标准模拟电路仿真流程中, 我们在搭建好点电路图并且保存后,从Composer-schematic界面中 的Tools→Analog Environment项就可以打开ADE窗口。

2019/12/12

2019/12/12

共61页

11

2019/12/12

工具栏介绍

从上至下:

1.Check and Save

2.Save

3.Zoom in by 2 ]

4.Zoom out by 2 [

5.Stretch

s

6.Copy

c

7.Delete

Del

8.Undo

u

9.Property

q

10.Instance

i

2

一、模拟前端EDA工具简介

2019/12/12

共61页

3

电子系统的层次

上游

2019/12/12

共61页

下游

4

模拟集成电路的设计流程

1.交互式电路图输入

2.电路仿真 3.版图设计

全定制

4.版图的验证(DRC LVS)

5.寄生参数提取

6.后仿真 7.流片

人 VS 机器

2019/12/12

共61页

共61页

一些显 示选项 的设置

重置

analog artist。 相当于 重新打 开一个 模拟窗

口

退出

17

Setup菜单

Setup菜单

Design Simulator/directory/host Temperature Model Library Environment

★Spectres仿真手册

Spectre的使用说明前面已经介绍了电路图的设计和画法,现在我们介绍仿真,cadance 仿真工具很多,如Hspice, Spectres等等,我们这里介绍Spectre,同时以共源放大器为例,介绍DC,AC,Tran电路图如下:第一节:仿真准备开始仿真时,点击Tools,在下拉菜单中点击Analogy Environment ,见下图出现如下窗口1.1 先介绍各条命令及其下拉的子命令的作用:一:Session:菜单包括Schematic Window、Save State、Load State、Options、Reset、Quit 等菜单项。

Schematic window项回到电路图(此时仿真窗口仍存在,只是当前的活动窗口为电路图);Save State项打开相应的窗口,保存当前所设定的模拟所用到的各种。

参数。

如图所示。

窗口中的两项分别为状态名(Save As)和选择需保存的内容(What to Save)。

Load State打开相应的窗口,加载已经保存的状态。

Reset 重置analog artist。

相当于重新打开一个模拟窗口,Quit退出仿真。

二:Setup 菜单包括Design、Simulator/directory/host、Temperature、Model libraries,Stimulition,Simulation Files,Environment等菜单项:1: Design项选择所要模拟的线路图。

2: Simulator/directory/host 项选择模拟使用的模型,点击此项,出现如下图窗点击Simulator项,出现下拉菜单如下图系统提供的选项有cdsSpice、hspiceS、spectreS等等。

我们一般用到的是cdsSpice和spectre,spectreS。

其中采用spectre,spectreS进行的模拟更加精确。

我们使用的上华提供的库,应使用spectre库,下面我们只以这种工具为例说明。

(精品)ultrasim用法

简单写一下一般用法,有时间再整理一下,参考:cadence Ultrasim 用户手册。

介绍ultrasim 是cadence 的fastspice 晶体管级仿真器。

采用模型简化、模型表格化、矩阵分割、事件驱动技术、多速率仿真等技术的ultrasim 是传统spice 的速度的10X-10000X, 而精度仅仅相差1%-5%,容量提高到数十亿器件(传统spice 仅为50k)。

用法1ultrasim 已经完全集成在cadence ADE(旧称artist)环境中,同spectre 一样可以方便的调用,并提供图形界面的各个选项,具体可参考相关手册,本文重点讲述其命令行的方式使用。

用法21。

在终端输入: ultrasim xx.sp ultrasim -spectre xx.scs ultrasim -vlog xx.v 以上分别表示仿真xx.sp 文件(netlist 是hspice 格式),xx.scs (netlist 是spectre 格式),xx.v(netlist 是verilog 格式)其中的ultrasim 命令可以换成64bit 的ultrasim64 (要有64bit 机器硬件与64bit OS 以及64bit ultrasim 的支持),64bit ultrasim 可以访问超过4G 的内存。

还有一些其他选项,读者自己看吧2。

ultrasim 的仿真模式。

根据对精度和速度要求的不同,ultrasim 分为 6 种不同的仿真模式, 分别是digitalfast/digital accurate/mixed singal/analog Multi rate/analog mode/spicemode,在option 选项种分别称为df da ms amr a s . 6 种模式:数字加速、数字精度、混合信号、模拟多比率、模拟、spice 在精度上不断提高,而在速度上逐渐降低。

其中df/da 模式适用于数字电路(数字逻辑电路、门电路、触发器、ROM、RAM 等)仿真,不要把这两种模式用于模拟电路仿真。

集成电路Spice,Spectre仿真总结

集成电路_Spice,Spectre仿真总结Designers-Guide to Spice and Spectre 1995 USA Designers-Guide to Spice a nd Spectre — Ken Kundert 11.1 绪论 1. 为什么要读这本书①该书是介于算法和教你如何操作软件之间的一本书可以帮助你更好的使用Simulator的设置。

② Simulator仿出的结果可靠不精确不是否收敛应该如何处理如何设置③读完这本书你应该会 1 Simulator如何计算结果 2 Simulator会产生何种错误如何识别 3 如何提高仿真精度 4 如何克服不收敛的情况 5 对于一些特殊电路会产生什么错误如何识别 6 明白仿真器里设置convergenceerror control的一些重要参数 7 能知道仿真器的错误信息出在什么地方如何解决 2. 电路仿真软件的发展历史①直接方法求出电路的微分方程组用数值积分方法差分化然后用牛顿迭代法求解非线性代数方程组。

⇒是最准确可靠最通用的方法② Explicit integration methods ⇒方法问题很多③ relaxiton methods ⇒方法问题很多 3. Spice Options ① Global Options: Abstol控制电流默认为1pA Vntol控制电压默认为1uV Reltol相对误差对于牛顿收敛准则和截断误差准则同时起作用默认10-3对于重要电路这个应该设置小一些比如说10-5或者10-6Gmin防止非线性器件关断后的浮空节点默认为10-12 Ω-1LimptsPivrelPivtol无用处② DC Analysis Options: ltl1DC工作点最大牛顿迭代次数默认100 ltl2DC Sweep最大牛顿迭代次数默认50 ltl6Source Stepping的最大步长数增加以上3个值可以增加DC牛顿迭代收敛但是会降低速度。

cadence仿真.

2018/11/9

三、模拟仿真的设置(重点)

Composer-

schamatic界面中的

Tools → Analog Environment项可以

打开Analog Design

Environment 窗口, 如右图所示。

2018/11/9

Analog Design Simulation菜单介绍

Tools/Parametric Analysis

它提供了一种很重要的分析方法——参量分析的方法, 也即参量扫描。可以对温度,用户自定义的变量variables 进行扫描,从而找出最合适的值。

2018/11/9

其它有关的菜单项(2)

Outputs/To be plotted/selected on schematic

2018/11/9

五、运算放大器仿真实例

1、电路图的输入(共模反馈型运放),如下 图所示:

2018/11/9

2、建立Symbol图

2018/11/9

3、仿真电路图示意

2018/11/9

4、运放小信号仿真示例

电源电压Vdc=3.3 V; 交流信号源acm=1 V; 负载电容Cload=5p F; 采用Spectre分析方式,选择交流分析(ac),设置如下: Sweep Variable: Frequency Sweep Range :1 Hz~100M Hz 仿真完成后,点击 Result -> Direct Plot -> AC Gain&Phase 查看运放的幅频特性和相频特性

2、点击Tools-> Parametric Analysis设置负载电容的扫描范 围和扫描步长,其中Range Type选择From/To,Step Control选择Linear Steps

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2020/4/21

共61页

8

Cadence中Spectre的仿真

1、进入Cadence软件包 2、建立可进行Spectre模拟的单元文件 3、编辑可进行Spectre模拟的单元文件 4、模拟仿真的设置(重点) 5、模拟仿真结果的显示以及处理 6、分模块模拟(建立子模块) 7、两个实例

共61页

一些显 示选项 的设置

重置

analog artist。 相当于 重新打 开一个 模拟窗

口

退出

17

Setup菜单

Setup菜单

Design Simulator/directory/host Temperature Model Library Environment

选择所要 模拟的线

路图

选择模拟使用 的模型一般有

2020/4/21

共61页

35

2020/4/21

共61页

36

2.仿真速度设置(speed option)

Speed option可以设置总的公差容忍度tol(tol也可以单独设置),tol 包括电压、电流等所有的公差容忍度之和。Speed option有八个选项, 分别是speed=1,2,3,4,5,6,7,8。其对tol分别是 0.0001 ,0.001,0.0025,0.005,0.02,0.02,0.04,0.07,精度依次降低。通 常,如果精度要求不是很高,可以采用默认设置,而无需设置这一项。注 意:精度设置的越高,相应的速度越低。

2020/4/21

共61页

37

3.矩阵分割设置(analog option)

Ultrasim把大的电路矩阵分割成小的矩阵,以加快仿真 速度,但同时会损失一些精度。analog选项用来控制矩 阵分割的大小,通常采用默认设置。以下是适用每种 analog值的电路。

Analog=0 适用于数字电路和存储器电路 Analog=1 适用于数字电路、存储器电路和混合信号

2020/4/21

共61页

19

tran(瞬态分析)

2020/4/21

可选择三种仿真精确度:宽松的 (liberal),适中的(moderate),保 守的(conservative)。其中liberal的 仿真速度最快,但是精度最低。这种精 度的仿的设置,其精确度类似于用 SPICE2计算的仿真结果;conservative 具有最高的精确度但是速度最慢,适合 较敏感的模拟电路的仿真

共61页

20

dc(直流分析)

dc(直流分析)可以在 直流条件下对

temperature,Design Variable,Component

Parameter,Model Parameter进行扫描仿真

例如:对温度的扫描(测 量温度系数)

电路随电源电压变化的 变化曲线等

2020/4/21

共61页

21

共61页

34

1.仿真模式设置(Simulation Mode)

Simulation Mode中有6种模式,分别为Digital Fast (DF)、Digital Accurate(DA)、Mixed Signal(MS)、 Analog Multi Rate (amr)、Analog(A)和SPICE(S)。 六种模式的精度依次升高,但是仿真速度依次降低。每种 模式所利用的仿真模型也不完全相同,各种模式有相应的 应用。下面将详细介绍每种模式的应用、使用的模型以及 仿真的目标精度。

2020/4/21

共61页

16

Analog Design Simulation菜单介绍

Session菜单

Schematic Window Save State Load State Options Reset Quit

回到电路图

2020/4/21

保存当前 所设定的 模拟所用 到的各种

参数

加载已 经保存 的状态

2020/4/21

共61页

9

进入Cadence软件包

方法一

使用putty软件(缘网下 载),在Host name处填 工作站地址,端口默认, 协议(protocol)选SSH, 如图所示,在putty进行 设置;然后用exceed登 录工作站。

2020/4/21

共61页

10

方法二

1、安装winvnc软件 2、运行putty软件键入 用户名和密码,在提示 符处键入 vncserver命 令申请vnc端口 3、运行winvnc,填入 主机名称:端口号码

cdsSpice hspiceS spectre等

设置模拟 时的温度

设置库文件 的路径和仿

真方式

设置仿真的 环境

(后仿真时 需设置)

2020/4/21

共61页

18

Analysis菜单

选择模拟类型。Spectre的 分析有很多种,如右图,

最基本的有 tran(瞬态分析) dc(直流分析) ac(交流分析)。

共61页

30

此时ADE窗口默认的仿真器Simulator为spectre,为了设置使用 Ultrasim仿真器,点击Setup→Simulator/directory/host,弹出对话框 如图6.31所示。选择仿真使用的模型,在下图Simulator中选择 UltraSim。

2020/4/21

2020/4/21

共61页

11

2020/4/21

工具栏介绍

从上至下:

1.Check and Save

2.Save

3.Zoom in by 2 ]

4.Zoom out by 2 [

5.Stretch

s

6.Copy

c

7.Delete

Del

8.Undo

u

9.Property

q

10.Instance

i

共61页

2020/4/21

共61页

32

接下来选择仿真所需要的精度和速度,如图6.33所示,进入 simulation菜单,选择Option→Analog。

2020/4/21

共61页

33

2020/4/21

然后显示如图所示的simulation option窗口,它有许多选项的设置, 包括速度、精度、输出、温度, 规模等等。下面将主要介绍一下 四项仿真参数的设置,仿真模式、 仿真速度、矩阵分割以及波形文 件格式。

ac(交流分析)

ac(交流分析)是 分析电路性能随着 运行频率变化而变

化的仿真。

既可以对频率进行 扫描也可以在某个 频率下进行对其它

变量的扫描。

2020/4/21

共61页

22

Variables菜单

包括Edit等子菜单项。可以 对变量进行添加、删除、 查找、复制等操作。变量 (variables)既可以是电 路中元器件的某一个参量, 也可以是一个表达式。变 量将在参量扫描 (parametric analysis)时 用到。

Spectre、Ultrasim和 Spectre-Verilog 仿真介绍

张昊 2019年3月7日

内容提要

模拟前端EDA工具简介 Cadence中Spectre的模拟仿真 Ultrasim快速仿真技术 Spetre-Verilog混合信号仿真 Q&A

2020/4/21

共61页

2

一、模拟前端EDA工具简介

2020/4/21

共61页

6

几家EDA软件公司

1、Synopsys(收购Avanti) 2、Cadence 3、Mentor Graphics 4、Silvaco 5、SpringSoft

2020/4/21

共61页

7

Cadenc软件简介

Cadence 提供了一个大型的EDA 软件包,它包括: 模拟IC设计

2020/4/21

共61页

23

参量扫描共功能

Tools/Parametric Analysis

它提供了一种很重要的分析方法——参量分 析的方法,也即参量扫描。可以对温度,用 户自定义的变量(variables)进行扫描,从 而找出最合适的值。

2020/4/21

共61页

24

Calculator的使用

Hspice: 作为业界标准的电路仿真工具,它自带了许多器 件模型,包括小尺寸的MOSFET和MESFET。Cadence提 供了hspice的基本元件库并提供了与Hspice的全面的接口。

Spectre: 由Cadence开发的电路仿真器,在SPICE的基础 上进行了改进,使得计算的速度更快,收敛性能更好。

共61页

31

如同spectre仿真,在Setup→Model Library Setup选择模型文件的路 径,并填入仿真模型的工艺角类型。

在Analysis菜单中可以选择分析类型,从Analysis→Choose打开如图 窗口,选择瞬态分析类型tran,tran的设置只需填入仿真停止时间即 可。选择是否保存直流工作点。

2020/4/21

注意! View要选择symbol

共61页

13

常用analoglib库的元器件

器件 电阻 电容 电感 NMOS PMOS

npn管

Cell 名称 res cap ind

nmos4 pmos4

npn

pnp管 地

直流电压源 直流电流源 方波发生源

可编程方波发 生源

正弦波发生源

2020/4/21

共61页

pnp gnd vdc idc vpulse vpwl