集成电路布图设计.ppt.ppt

合集下载

第14章集成电路版图设计资料

8/8/2019

共85页

34

MOS dummy

• 在MOS两侧增加dummy poly。

• 添加dummy管,可以提 供更好的环境一致性。

8/8/2019

共85页

35

RES dummy

• 类似于MOS dummy方法增加dummy,有时会在四 周都加上。

8/8/2019

共85页

36

CAP dummy

共85页

4

• 第二张mask定义为active mask。 有源区用来定义管子的栅以及允许注入的p型或者n型扩散的源漏区。

8/8/2019

共85页

5

• 第三张mask为poly mask: 包含了多晶硅栅以及需要腐蚀成的形状。

8/8/2019

共85页

6

• 第四张mask定义为n+mask, 用来定义需要注入n+的区域。

• 不同的工艺线和工艺流程,电学参数有所不同。

• 描述内容:晶体管模型参数、各层薄层电阻、层与层间的 电容等。

• 几何设计规则是图形编辑的依据,电学设计规则是分析计 算的依据。

8/8/2019

• 完成一个反相器的版图设计

8/8/2019

8/8/2019

8/8/2019

8/8/2019

8/8/2019

8/8/2019

共85页

37

Interconnect

• 关键走线与左右或上下走线的屏蔽采用相同层或 中间层连接VSS来处理。

• 也可增大两者间的间距来减少耦合。

8/8/2019

共85页

38

Guard Ring的设计

8/8/2019

共85页

39

深阱guard ring

《集成电路版图LAYOUT设计与Cadence》讲义

LSW (Layer Selection Window)

Set drawing layer Set layer visible Set layer selectable Set valid layer Set layer purpose pair

i. Set drawing layer

工艺信息

基本概念

5、符号,截面图,版图(top view) 对应关系

Inverter

input

VDD

PMOS s

g

b

d

NMOS d

g

b

output

s

GND

Stick-diagram

INPUT

GND

VDD

OUTPUT

Legend of each layer

N-well P-diffusion N-diffusion Polysilicon

mask

芯片代工

Wafer(die)

(Foundry)

封装 (packet)

基本概念

3、Layout design 对于整个IC design 的重要意义:

对Hale Waihona Puke 数字电路设计流程来说:Layout engineer 主要是为设计者提供经过验 证的单元版图库 (library),一般来说这样 的工作主要是由一些 Foundry 和 Service 公司来完成,对于 Fabless 来说,主要是 应用已有的库和IP Core来作布局布线,以 及验证等一些工作;

1、版图设计的重要性

▪前端设计同最终芯片产品之间的一 个重要接口; ▪芯片的品质不仅依靠前端设计的优 劣,在某些情况下,同版图设计的 联系更紧密,尤其在 analog/mixsignal/RF circuit design中。

Set drawing layer Set layer visible Set layer selectable Set valid layer Set layer purpose pair

i. Set drawing layer

工艺信息

基本概念

5、符号,截面图,版图(top view) 对应关系

Inverter

input

VDD

PMOS s

g

b

d

NMOS d

g

b

output

s

GND

Stick-diagram

INPUT

GND

VDD

OUTPUT

Legend of each layer

N-well P-diffusion N-diffusion Polysilicon

mask

芯片代工

Wafer(die)

(Foundry)

封装 (packet)

基本概念

3、Layout design 对于整个IC design 的重要意义:

对Hale Waihona Puke 数字电路设计流程来说:Layout engineer 主要是为设计者提供经过验 证的单元版图库 (library),一般来说这样 的工作主要是由一些 Foundry 和 Service 公司来完成,对于 Fabless 来说,主要是 应用已有的库和IP Core来作布局布线,以 及验证等一些工作;

1、版图设计的重要性

▪前端设计同最终芯片产品之间的一 个重要接口; ▪芯片的品质不仅依靠前端设计的优 劣,在某些情况下,同版图设计的 联系更紧密,尤其在 analog/mixsignal/RF circuit design中。

半导体集成电路第4章版图设计与举例课件

线宽。 b:能保证在硅平面上显现清晰线条的最小版图设

计线宽。 前者表示所能达到的工艺水平,后者表示保

证一定成品率前提下所能达到的工艺水平。 最小掩模线宽可根据实际的工艺确定。 对TTL一般4~10um

•半导体集成电路第4章版图设计与举例

•10

二、掩膜图形最小间距

版图设计时,版图上各相邻图形间的 最小间距。 显然,制作到Si平面时,图形的实际位置将与

•

设计中常用BC短•半接导体及集成单电路第独4章B版图C设计结与举两例 种结构。

•25

二、SBD

SBD在集成电路中可作为二极管独立使

用,也可以与晶体管组合构成抗饱和晶体管。

1、SBD版图设计考虑

要求:面积小 ,减小结电容;

串连电阻小,提高钳位效果;

反向击穿电压高。

在设计中,由于rSBD 与结电容的要求相

•

△WMAT-2-0.8xjc+Wdc-B+Gmin

7、DB-I 基区窗口到隔离窗口间距

•

△WMAT+0.8xjc-0.8xjI+Wdc-c+WdI-C+Gmin

•

XjI~125%Wepi-MAX

8、Dc-B n+集电极窗口到基区窗口间距

△WMAT+0.8xjc+0.8xje+Wdc-c+Gmin

9.Wc孔 集电极n+孔宽

目的:实现电路中各个元件的电隔离

规则:

1、集电极等电位的NPN管可共用一个隔离区(基极

等电位的PNP管可共用一个隔离区)

2、二极管按晶体管原则处理。

3、原则上,所有硼扩散电阻可共用同一隔离区。

4、当集电极电位高于硼扩散电阻的电位时,晶体管

计线宽。 前者表示所能达到的工艺水平,后者表示保

证一定成品率前提下所能达到的工艺水平。 最小掩模线宽可根据实际的工艺确定。 对TTL一般4~10um

•半导体集成电路第4章版图设计与举例

•10

二、掩膜图形最小间距

版图设计时,版图上各相邻图形间的 最小间距。 显然,制作到Si平面时,图形的实际位置将与

•

设计中常用BC短•半接导体及集成单电路第独4章B版图C设计结与举两例 种结构。

•25

二、SBD

SBD在集成电路中可作为二极管独立使

用,也可以与晶体管组合构成抗饱和晶体管。

1、SBD版图设计考虑

要求:面积小 ,减小结电容;

串连电阻小,提高钳位效果;

反向击穿电压高。

在设计中,由于rSBD 与结电容的要求相

•

△WMAT-2-0.8xjc+Wdc-B+Gmin

7、DB-I 基区窗口到隔离窗口间距

•

△WMAT+0.8xjc-0.8xjI+Wdc-c+WdI-C+Gmin

•

XjI~125%Wepi-MAX

8、Dc-B n+集电极窗口到基区窗口间距

△WMAT+0.8xjc+0.8xje+Wdc-c+Gmin

9.Wc孔 集电极n+孔宽

目的:实现电路中各个元件的电隔离

规则:

1、集电极等电位的NPN管可共用一个隔离区(基极

等电位的PNP管可共用一个隔离区)

2、二极管按晶体管原则处理。

3、原则上,所有硼扩散电阻可共用同一隔离区。

4、当集电极电位高于硼扩散电阻的电位时,晶体管

集成电路版图设计

02 集成电路版图设计基础

CHAPTER

电路设计基础

01

模拟电路设计

02

运算放大器

03

比较器

04

触发器

电路设计基础

01

数字电路设计

02

组合逻辑电路

时序逻辑电路

03

04

可编程逻辑电 路

版图设计基础

版图编辑软件 ICEDrawer

版图设计基础

01

Laker

02

P甩 Pro

版图设计规则

03

版图设计基础

管的形状和尺寸等。

案例二:低功耗模拟电路版图设计

总结词

通过优化模拟电路的版图设计,实现低功耗的目的, 以满足便携式电子设备和物联网等领域的需求。

详细描述

低功耗模拟电路版图设计需要考虑模拟电路的性能和 功耗等方面,同时还需要考虑噪声和失真等方面的因 素。为了实现低功耗的设计,需要采用优化的版图设 计方法,如使用低阻抗的走线、优化晶体管的形状和 尺寸等。

3

antenna effect simulation

物理验证基础 01

P/R/O/L/C分析

热学参数分析(T)

03

02

电学参数分析(P/R/O)

电磁兼容性分析(EMC)

04

03 集成电路版图设计技术

CHAPTER

逻辑电路版图设计

逻辑电路

逻辑电路是实现逻辑运算和逻辑控制的电路,分为组合逻 辑电路和时序逻辑电路。在版图设计中,需要考虑到电路 的复杂性、功耗、速度等因素。

提高芯片的可测试性。

可制造性版图设计实践

符合制造规范

遵循制造规范和流程,确保版图设计具有良好的可制 造性。

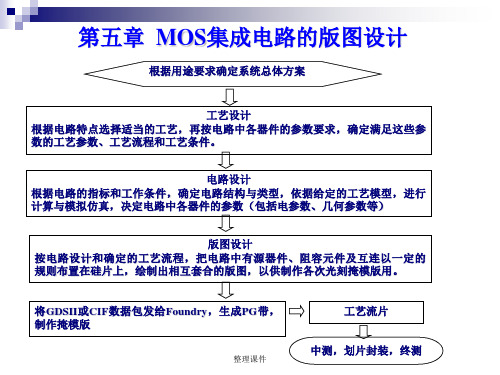

集成电路原理-MOS集成电路的版图设计

1.08(ns)

整理课件

0.0330.001

2、导电层的选择

(1)VDD、VSS尽可能选用金属导电层,并适当增加连线宽 度,只有在连线交叉“过桥”时,才考虑其他导电层。 (2)多晶硅不宜用作长连线,一般也不用于VDD、VSS电源 布线。 (3)通常应使晶体管等效电阻远大于连线电阻,以避免出 现电压的“分压”现象,影响电路正常工作。

若要形成耗尽型NMOS器件,只需在第(5)、(6)步之间加 一道掩模版,进行沟道区离子注入。

NMOS工艺流程的实质性概括: P型掺杂的单晶硅片上生长一层厚SiO2。 MK1—刻出有源区或其他扩散区(薄氧化版/扩散版)。 MK2—形成耗尽型器件时,刻出离子注入区。 MK3—刻多晶硅图形(栅、多晶硅连线)。

以多晶硅栅为掩模,进行D、S的自对准扩散。 MK4—刻接触孔。 MK5—反刻 Al。 MK6—刻钝化孔(压焊点窗口)

共用到6道掩模版 整理课件

3、硅栅CMOS工艺 (1)P阱CMOS工艺流程 • MK1—P阱版,确定P阱深扩散区域(阱注入剂量11013cm-2,

能量60KeV) • MK2—确定薄氧化区,即有源区。 • MK3—多晶硅版。 • MK4—P+版,和MK2一起确定所有的P+扩散区域 (一般为B注入,41014cm-221015cm-2,6080KeV)。 • MK5—N+版,确定所有的N+区域

(4)通过掩模版MASK对光刻胶曝光 正胶被 UV曝光的部分分解, 影被 掉显 。 负胶曝光部分聚合 ,硬 不化 被显影掉。

整理课件

(5)刻有源区。 掩模版掩蔽区域下未被曝光的光刻胶 被显影液洗掉;再将下面的SiO2用HF 刻蚀掉,露出硅片表面。

(6)淀积多晶硅 除净曝光区残留的光刻胶(丙酮), 在整个硅片上生长一层高质量的SiO2 (约1000Å),即栅氧,然后再淀积 多晶硅(12m)。

数字集成电路设计 第四章导线.ppt

导线. 17

合肥工业大学应用物理系

接触电阻(contact resistance)

• 布线层之间的转接将给导线带来额外的电阻 – 尽可能地使信号线保持在同一层上并避免过多的接触或通孔 – 使接触孔较大可以降低接触电阻(电流集聚在实际中将限制接触孔 的最大尺寸)

• 典型接触电阻,RC, (最小尺寸) – 金属或多晶至n+、p+以及金属至多晶为 5 ~ 20 – 通孔(金属至金属接触)为1 ~ 5

例4.1 金属导线电容

考虑一条布置在第一层铝上的10cm长,1m宽的铝线,计算总的电容值。

平面(平行板)电容: ( 0.1×106m2 )×30aF/m2 = 3pF

边缘电容:

2×( 0.1×106m )×40aF/m = 8pF

总电容:

11pF

现假设第二条导线布置在第一条旁边,它们之间只相隔最小允许的距离, 计算其耦合电容。

Capacitance-only

注意:这些附加的电路元件并不处在实际的单个点上,而是分布在导 线的整个长度上

导线. 6

合肥工业大学应用物理系

寄生简化

• 电感的影响可以忽略 – 如果导线的电阻很大(例如截面很小的长铝导线的情形) – 外加信号的上升和下降时间很慢

• 采用只含电容的模型 – 当导线很短,导线的截面很大时 – 当所采用的互连材料电阻率很低时

D2 C1R1 C2 R1 R2

r1

1 r2

2

Vin

c1

c2

ri-1 i-1 ri

i

ci-1

ci

rN

N VN

cN

Di C1R1 C2R1 R2 ... Ci R1 R2 ... Ri

《集成电路设计》课件

掺杂与刻蚀

在晶圆表面进行掺杂和刻蚀, 形成电路元件和互连结构。

晶圆制备

将高纯度硅晶棒进行切片,得 到晶圆片,作为集成电路制造 的基础材料。

图案转移

将设计好的电路图案通过光刻 技术转移到晶圆表面,形成电 路图形。

金属化与封装

在晶圆表面沉积金属,形成电 路的互连线路,并将单个芯片 封装成最终的产品。

集成电路工艺材料

详细描述

数字集成电路设计案例通常包括门电路设计、触发器设计、寄存器设计等,这些基本单元是构成复杂数字系统的 基石。此外,数字系统级的设计案例包括微处理器、微控制器、数字信号处理器等,这些系统级芯片广泛应用于 计算机、通信、控制等领域。

模拟集成电路设计案例

总结词

模拟集成电路设计案例主要涉及放大器、滤波器、比较器等模拟电路单元的设计,以及模拟系统级的 设计。

电视、音响、游戏机 等。

工业控制

PLC、DCS、机器人 等。

汽车电子

发动机控制、ABS、 ESP等。

02

集成电路设计基础

集成电路设计流程

需求分析

对产品需求进行调研,明确设计目标、性能 指标和限制条件。

规格制定

根据需求分析结果,制定出具体的规格说明书 ,包括芯片功能、性能参数等。

架构设计

根据规格说明书,设计出芯片的总体结构,包括 各个模块的组成和相互关系。

电路仿真工具

用于模拟电路的行为和性能, 常用的有ModelSim和 Matlab Simulink。

物理设计工具

用于将电路设计转换为版图, 常用的有Cadence和 Synopsys。

测试工具

用于测试芯片的性能和功能, 常用的有JTAG和Boundary Scan。

集成电路设计ppt

第四章 半导体集成电路基本加工工艺与设计规则 4.1 引言 4.2 集成电路基本加工工艺 4.3 CMOS工艺流程 4.4 设计规则 4.5 CMOS反相器的闩锁效应 4.6 版图设计

第五章 MOS管数字集成电路基本逻辑单元设计 5.1 NMOS管逻辑电路 5.2 静态CMOS逻辑电路 5.3 MOS管改进型逻辑电路 5.4 MOS管传输逻辑电路 5.5 触发器 5.6 移位寄存器 5.7 输入输出(I/O)单元

[3] 陈中建主译. CMOS电路设计、布局与仿真.北京:机械工 业出版社,2006.

[4](美)Wayne Wolf. Modern VLSI Design System on Silicon. 北京:科学出版社,2002.

[5] 朱正涌. 半导体集成电路. 北京:清华大学出版社,2001. [6] 王志功,沈永朝.《集成电路设计基础》电子工业出版

第六章 MOS管数字集成电路子系统设计 6.1 引言 6.2 加法器 6.3 乘法器 6.4 存储器

6.5 PLA 第七章 MOS管模拟集成电路设计基础

7.1 引言 7.2 MOS管模拟集成电路中的基本元器件 7.3 MOS模拟集成电路基本单元电路 7.4 MOS管集成运算放大器和比较器 7. 5 MOS管模拟集成电路版图设计 第八章 集成电路的测试与可测性设计

1.2 集成电路的发展

1、描述集成电路工艺技术水平的五个技术指标 (1)集成度(Integration Level)

集成度是以一个IC芯片所包含的元件(晶体管或门/数)来 衡量(包括有源和无源元件)。随着集成度的提高,使IC及使用 IC的电子设备的功能增强、速度和可靠性提高、功耗降低、体积 和重量减小、产品成本下降,从而提高了性能/价格比,不断扩 大其应用领域,因此集成度是IC技术进步的标志。为了提高集成 度采取了增大芯片面积、缩小器件特征尺寸、改进电路及结构设 计等措施。为节省芯片面积普遍采用了多层布线结构。硅晶片集 成(Wafer Scale Integration -WSI)和三维集成技术也正在研 究开发。从电子系统的角度来看,集成度的提高使IC进入系统集 成或片上系统(SoC)的时代。

北大集成电路版图设计课件_第8章 MOS场效应晶体管

V+

N阱

V-

P型衬底

三. MOS管版图设计技巧

衬底连接与阱连接 设置阱连接的经验法则是在满足设计规则的前提下,在阱的空

闲区域尽可能多地设置阱连接。比较常用的设置阱连接的方式

是用阱连接环绕MOS晶体管。设置衬底连接的经验法则也是

是在满足设计规则的前提下,在衬底的空闲区域尽可能多地设

置衬底连接。

阱

连

接

In(D / C) L (D C)

2

三. MOS管版图设计技巧

衬底连接与阱连接 制作CMOS集成电路有N阱工艺、P阱工艺和双阱工艺,无论 哪种工艺,在阱和衬底之间都存在PN结。以N阱工艺为例, 在P型衬底和N阱之间存在PN结。为了保证PN结的有效隔离, N阱的电位必须高于P型衬底的电位,最简单最可靠的方法是 将N阱接最正的电源,P型衬底接最负的电源。在版图设计中, 将设置衬底或阱连接的方式称为衬底连接或阱连接。

一. 概述

MOS晶体管是四端器件,具有源极(S)、漏极(D)、栅 极(G)和衬底(B)四个电极,按导电类型分为NMOS晶体 管和PMOS晶体管两种.

(a)NMOS

(b)PMOS

一. 概述

二. MOS管的版图

NMOS晶体管的立体图和俯视图

(a)立体图

(b)俯视图

二. MOS管的版图

图 PMOS晶体管的版图示意图

二. MOS管的版图

阱层(Well): 阱层定义在衬底上制备阱的区域。NMOS 管制备在P型衬底上,PMOS管制备在N 型衬底上。一块原始的半导体材料,掺入 的杂质类型只能有一种,即该衬底不是N 型就是P型。如果不对衬底进行加工处理 的话,该衬底只能制备一种MOS晶体管。 CMOS集成电路是把NMOS晶体管和 PMOS晶体管制备在同一个硅片衬底上, 为了能够制造CMOS集成电路,需要对衬 底进行处理,利用掺杂工艺在衬底上形成 一个区域,该区域的掺杂类型和衬底的掺 杂类型相反,这个区域就称为阱。

集成电路版图设计基础第4章:标准单元技术

cant route here

school of phye

basics of ic layout design

16

网格式布线系统要求的库设计规则 对齐输入输出:

• 输入A和输出Z不能随意放置。它们必须像所有的连线一样位于同 样的网格上。 • 保证标准单元的所有输入输出不仅在x网格上,还要在y网格上。 要保证自动布线软件在水平方向和垂直方向都能找到它们。 • 保证所有的库单元以及库单元内部的器件符合网格规则。

school of phye

basics of ic layout design

7

标准网格

- 网格式布线器

grid-based router

• techfile - PHYSICAL RULES • 最小间距minSpacing:各几何图形外边界之间的距离。

school of phye

basics of ic layout design

school of phye basics of ic layout design 11

标准网格

- 网格式布线器

grid-based router

• coarse grid example:

1 microns 2 microns

1 microns

1 microns

Minimum wire is 1 micron, minimum spacing is 1 micron, therefore, our two wires use 3 microns, and we have established center-to-center grid spacing of 2 microns for this process.

• 数字库:高度固定,宽度可变。(fixed height, variable width.) 大多数库都是这样的。 对于数字版图,特别是标准单元版图,是唯一可行的方式。 在模拟版图设计中也非常有用,甚至是全定制的AIC。

school of phye

basics of ic layout design

16

网格式布线系统要求的库设计规则 对齐输入输出:

• 输入A和输出Z不能随意放置。它们必须像所有的连线一样位于同 样的网格上。 • 保证标准单元的所有输入输出不仅在x网格上,还要在y网格上。 要保证自动布线软件在水平方向和垂直方向都能找到它们。 • 保证所有的库单元以及库单元内部的器件符合网格规则。

school of phye

basics of ic layout design

7

标准网格

- 网格式布线器

grid-based router

• techfile - PHYSICAL RULES • 最小间距minSpacing:各几何图形外边界之间的距离。

school of phye

basics of ic layout design

school of phye basics of ic layout design 11

标准网格

- 网格式布线器

grid-based router

• coarse grid example:

1 microns 2 microns

1 microns

1 microns

Minimum wire is 1 micron, minimum spacing is 1 micron, therefore, our two wires use 3 microns, and we have established center-to-center grid spacing of 2 microns for this process.

• 数字库:高度固定,宽度可变。(fixed height, variable width.) 大多数库都是这样的。 对于数字版图,特别是标准单元版图,是唯一可行的方式。 在模拟版图设计中也非常有用,甚至是全定制的AIC。

集成电路常用器件版图

感电路造成影响. ❖ 图7.27:通过P+接触孔吸收来自衬底的噪声.

5.5 保护环版图

❖ 2、防止闩锁效应 ❖ 闩锁效应是由CMOS工艺中的计生效应引起

的,对电路可靠性非常重要,一旦发生闩锁,不 仅电路无法正常工作,还会因大电流引起芯片 过热,造成物理破坏. ❖ 图7.29:寄生效应电路. ❖ 图7.30:多数载流子保护环,吸收外来的多数 载流子,避免寄生三极管的发射极被正偏.

ESD〔Electrostatic discharge

构.

5.5 保护环版图

❖ 保护环〔guard ring是有N+型的接触孔或P+ 型的接触孔转成环状,将所包围的器件与环外 的器件隔离开来,所以叫做保护环.

❖ 保护环的作用:隔离噪声,保护敏感电路不受 外界干扰;防止闩锁效应.

5.5 保护环版图

❖ 1、隔离噪声 ❖ 模拟电路的噪声一般来自衬底,噪声源会对敏

〔1反相输出 I/O PAD

❖ 考虑到电子迁移率比空穴约大2.5 倍,所 以,PMOS 管的尺寸比NMOS 管大,这样可使 倒相器的输出波形对称.

❖ 下图是将金属铝引线去除后的版图形式,通过 这个图可以清楚的看到器件的并联结构和重 掺杂隔离环的结构.

〔1反相输出 I/O PAD

5.7 电源和地线版图

5.2 电阻常见版图画法

5.2 电阻常见版图画法

5.2 电阻常见版图画法

5.2 电阻常见版图画法

❖ 对于无法使用串、并联关系来构建的电阻,可 以在单元电阻内部取部分进行构建.

❖ 图7.18的实现方式.

电阻匹配设计总结

❖ 〔1采用同一材料来制作匹配电阻 ❖ 〔2匹配电阻的宽度要相同,且要足够宽. ❖ 〔3匹配的电阻要紧密靠近 ❖ 〔4在匹配电阻阵列的两端要放置Dummy电

5.5 保护环版图

❖ 2、防止闩锁效应 ❖ 闩锁效应是由CMOS工艺中的计生效应引起

的,对电路可靠性非常重要,一旦发生闩锁,不 仅电路无法正常工作,还会因大电流引起芯片 过热,造成物理破坏. ❖ 图7.29:寄生效应电路. ❖ 图7.30:多数载流子保护环,吸收外来的多数 载流子,避免寄生三极管的发射极被正偏.

ESD〔Electrostatic discharge

构.

5.5 保护环版图

❖ 保护环〔guard ring是有N+型的接触孔或P+ 型的接触孔转成环状,将所包围的器件与环外 的器件隔离开来,所以叫做保护环.

❖ 保护环的作用:隔离噪声,保护敏感电路不受 外界干扰;防止闩锁效应.

5.5 保护环版图

❖ 1、隔离噪声 ❖ 模拟电路的噪声一般来自衬底,噪声源会对敏

〔1反相输出 I/O PAD

❖ 考虑到电子迁移率比空穴约大2.5 倍,所 以,PMOS 管的尺寸比NMOS 管大,这样可使 倒相器的输出波形对称.

❖ 下图是将金属铝引线去除后的版图形式,通过 这个图可以清楚的看到器件的并联结构和重 掺杂隔离环的结构.

〔1反相输出 I/O PAD

5.7 电源和地线版图

5.2 电阻常见版图画法

5.2 电阻常见版图画法

5.2 电阻常见版图画法

5.2 电阻常见版图画法

❖ 对于无法使用串、并联关系来构建的电阻,可 以在单元电阻内部取部分进行构建.

❖ 图7.18的实现方式.

电阻匹配设计总结

❖ 〔1采用同一材料来制作匹配电阻 ❖ 〔2匹配电阻的宽度要相同,且要足够宽. ❖ 〔3匹配的电阻要紧密靠近 ❖ 〔4在匹配电阻阵列的两端要放置Dummy电

北大集成电路版图设计课件_第5章 电容和电感精选全文

一. 电 容

3. 金属-多晶硅电容

如果利用多晶硅作为电容的下极板,金属作为电容的上极板,

就可形成金属-多晶硅电容。如图5.9所示,金属-多晶硅电容

与多晶硅-多晶硅电容相似,只不过上极板是金属而不是多晶

硅。

多晶硅

金属

C1

C2

C1

衬底

场氧化层

图 5.9 金属-多晶硅电容示意图

一. 电 容

4. 金属-金属电容 如果电容的上下极板都用金属来构成,就会形成金属-金属电

一. 电 容

Bad

Good

电容匹配规则

一. 电 容

3. 匹配电容的大小要适当。 电容的随机失配与电容面积的平方根成反比,但并不是

面积远大匹配就越好。总是存在一个最佳电容尺寸,超过 这个尺寸,梯度效应就会非常明显,从而影响匹配。

某些CMOS集成电路工艺中,正方形电容的尺寸应该介 于20μm×20μm至50μm×50μm之间。超过该尺寸的电 容应该被划分成多个单位电容,利用适当的交叉耦合减小 梯度影响,改善电容整体的匹配性。 4. 匹配电容要邻近摆放。

一. 电 容

多晶硅-多晶硅电容通常制作在场区处,由场氧化层把电容 和衬底隔开。由于场氧化层较厚,所以多晶硅-多晶硅电容的 寄生参数小,而且无横向扩散影响。通过精确控制两层多晶 硅的面积以及两层多晶硅之间的氧化层的厚度,可得到精确 的电容值。

由于多晶硅-多晶硅电容制作在场氧化层上,所以电容结构 的下方不能有氧化层台阶,因为台阶会引起电容下极板的表 面不规则,将造成介质层局部减薄和电场集中,从而破坏电 容的完整性。

金属2

(厚)电介质

金属1

一. 电 容

为了减小金属-金属电容所占用的面积,在多层金属互连系统中 可以制备叠层金属电容。多层金属平板垂直地堆叠在一起,从 上至下,每两层金属之间都存在电容。通过将奇数层金属连接 在一起作为一个电极,而将偶数层金属连接在一起作为另一个 电极。从剖面图来看,金属-金属电容是梳状交叉结构。

集成注入逻辑I2L电路课件.ppt

入电流被NPN管基区收集的多少,从而影响电路 的功耗、速度和负载能力。 提高横向PNP管电流增益α的主要途径: •减小基区宽度; •提高少子寿命; •减小发射结底部面积与侧面积之比; •尽可能提高发射结两侧杂质浓度的比值; •改善表面状态,降低表面复合速率。

CH6 集成注入逻辑(I2L)电路 12

6.3.2 I2L电路分析

IC1=a4IP 式中a3,a4为Q3、Q4的共基极电流增益。

CH6 集成注入逻辑(I2L)电路 13

-VP IP

Q3

A IB1

+VP IP

Q4

Q1 B IC1

C Q2

图6.5 两级I2L门电路

若有N0个负载,则前一级所吸收的后级注入电流 为

IC1=N0(a4IP)

(6.1)

CH6 集成注入逻辑(I2L)电路 14

对于多集电极结构晶体管,因为基区几何形状是 长条结构,因此rB一般较大,为了减小rB对电流增 益的影响,改善各集电极电流增益的不均匀性,可 采用如下办法: (1) 将集电极引线孔排列方向和注入条平行,如图 6.3(a)所示,这样基极引线孔到各集电区的距离均 匀分布,可提高各集电区的电流增益及其均匀性。

的 电 流 IP 全 部 流 向 QN2 管 的 基 极 , QN2 管 导 通 ,

VB=VBE ≈0.7V。如果IP足够大,就可使QN2处于深

饱和,其各输出端的饱和压降近似为QN2管的本征

饱和压降(VCES≈VCES0)。所以当I2L电路的输入为

高电平VOH时,其QN2管各集电极的输出为低电平,

且

p 深饱和

2 p 临界饱和

即

a 2a

4

3

所以 I 2 L 电路正常工作的条件为

CH6 集成注入逻辑(I2L)电路 12

6.3.2 I2L电路分析

IC1=a4IP 式中a3,a4为Q3、Q4的共基极电流增益。

CH6 集成注入逻辑(I2L)电路 13

-VP IP

Q3

A IB1

+VP IP

Q4

Q1 B IC1

C Q2

图6.5 两级I2L门电路

若有N0个负载,则前一级所吸收的后级注入电流 为

IC1=N0(a4IP)

(6.1)

CH6 集成注入逻辑(I2L)电路 14

对于多集电极结构晶体管,因为基区几何形状是 长条结构,因此rB一般较大,为了减小rB对电流增 益的影响,改善各集电极电流增益的不均匀性,可 采用如下办法: (1) 将集电极引线孔排列方向和注入条平行,如图 6.3(a)所示,这样基极引线孔到各集电区的距离均 匀分布,可提高各集电区的电流增益及其均匀性。

的 电 流 IP 全 部 流 向 QN2 管 的 基 极 , QN2 管 导 通 ,

VB=VBE ≈0.7V。如果IP足够大,就可使QN2处于深

饱和,其各输出端的饱和压降近似为QN2管的本征

饱和压降(VCES≈VCES0)。所以当I2L电路的输入为

高电平VOH时,其QN2管各集电极的输出为低电平,

且

p 深饱和

2 p 临界饱和

即

a 2a

4

3

所以 I 2 L 电路正常工作的条件为