DM6437介绍整理7-21

6437的OSD原理讲解

简介:OSD 是 On Screen Display 的缩写,是应用在 CRT/LCD 显示器上,在显示器的萤幕中产生一些特殊的字形或图形,让使用者得到一些讯息。

常见於家用电视机或个人 PC 电脑之显示萤幕上,当使用者操作电视机换台或调整音量、画质等,电视萤幕就会显示目前状态让使用者知道,此控制 IC 可在萤幕上的任何位置显示一些特殊字形与图形,成为人机界面上重要的讯息产生装置。

OSD支持在一个屏幕上输出5个窗口,即2个Video窗口,2个OSD窗口以及1个Cursor 窗口,实现视屏、图像、光标的叠加显示。

Venc将处理后的视屏Buffer装换为模拟视频信号输出,输出制式支持PAL和NTSC,DM6437内含4个视频DAC,因此模拟视频可以支持CVBS或者是S-Video接口OSD知识背景(在6437的VPBE中的位置作用)DM6437包括一个视频处理子系统(VPSS),带2个可配置的视频/图像外设:一个视频处理前端VPFE用于视频捕捉,一个视频处理后端VPBE用于视频输出。

VPFE包括1个CCDC(CCD 控制器),1个预览引擎Previewer, Histogram(直方图) Module, Auto-Exposure/White Balance/Focus Module (H3A), and Resizer。

CCDC与通用视频解码器,CMOS传感器以及CCDs(Charge oupled Devies)相连。

Previewer是一个实时图像处理引擎,它从CMOS传感器或CCD获取图像数据,并将之从RGB Bayer类型转换成YUV422。

Histogram和H3A模块提供原始色彩数据的统计信息供DM6437使用。

Resizer模块接受图像数据,并可以分别在水平和垂直方向从1/4x到4x做缩放处理。

VPBE相关寄存器有PID及PCR(设备控制寄存器),用于实现视频图像的输出显示。

(显示屏上的一幅图像可以分成若干个区域,每个区域可以代表不同的视频源,即来自不同的视频输出缓冲器,在输出显示之前,需要将来自不同视频输出缓冲器的视频数据复合成一个完另外,还经常需要将某些图形、字符等信息叠加到视频图像上一起输出显示,这些叠加到视频图像上的图形、字符存储于独立的缓冲器中,因而在输出显示之前,还需要将来自图形、字符缓冲器的数据复合进输出数字视频流中,)DM6437的视频输出编码既可以实现用于直接驱动模拟监视器的标准模拟视频输出,也可实现用于直接驱动带数字接口的显示器的多种标准数字视频输出。

DM6437烧写总结

DM6437烧写总结1 要了解烧写,首先要了解6437的存储器组织存储器的硬件组织原理可以参看TMSC6000结构原理与硬件设计(北京航天航空大学);具体的存储器的硬件连接可以参照合众达的DEC6437原理图。

从原理图可以知道,flash的控制信号线CE/OE/WE 都是连接与板子上面的CPLD,如需要控制读写,还要参看flash的datasheet来了解其读写时序,编写CPLD的程序,这里暂且略过,S29AL032D数据线22根,相当于内部有4M*8bit的存储空间(在flash 烧写的程序中会有一句if(FillSize > 0x100000){printf("The OUT file is too big!\n");}之所以这里是1M,不是4M,是因为后面调用fread的时候是按照4字节为单位来读取的!),地址线连接于EM_BA0-1(用于bank区分) EM_A0-A19片选是选择的cs2,因此flash用到的空间是EMIF_CS2 = 0x0x4200 0000,查看存储器映射表(详见TMS320DM6437 Digital Media Processor中table 2-3)因此,在烧写的程序中基址被定为#define FLASH_BASE ( EMIF_CS2_BASE )数据总线与dsp的连接是:EM_D0-7 8位因此,flash写数据时,指针设置为从FLASH_BASE开始的地方。

2 CCS烧写flash的办法:a.Ti提供的软件flashburn,需要将.out->rom格式;b 将编写两个工程:一个主程序工程(即用户应用程序,其中包括二次引导程序),一个搬运程序工程。

搬移程序不能使用与主程序的程序空间和中断向量表重合的物理空间,以免覆盖。

烧写时,同时打开主程序和搬移程序的PROJECT,先LOAD主程序,再LOAD搬移程序,然后执行搬移程序,烧写OK!C 用户应用程序(必须包含boot引导程序,否则无法启动)编译生成.out,然后编写烧写程序,在烧写程序中将生成的.out烧写到flash中。

TI最新达芬奇处理器DM6467 — TMDXEVM6467

TI最新达芬奇处理器DM6467 — TMDXEVM6467德州仪器(TI)最新推出了一款能够在多种应用间进行视频转码的新型达芬奇技术数字媒体处理器,这些应用包括媒体网关、多点控制设备、数字媒体适配器、视频安全监控DVR 以及IP 机顶盒等。

新型TM S320DM6467达芬奇处理器是一种基于DSP的片上系统(SoC),特别适合实时多格式高清(HD)视频编解码,并配套了完整的开发工具及数字多媒体软件。

该芯片集成了ARM926EJ-S内核与600MHz C64x+ DSP内核,并采用了高清视频协处理器、转换引擎与目标视频端口接口,在执行高清H.264 HP@ L4(1080p 30fps、1080i 60fps、720p 6 0fps)的同步多格式编码、解码与转码方面,比前代处理器性能提升了十倍。

实时多格式高清转码技术DM6467专为应对商业及消费类电子市场的高清转码挑战而设计的,通过其多内核设计,能够实现较前代数字媒体处理器高十倍的性能。

DM6467 处理器集成了ARM与DSP内核,并采用高清视频/影像协处理器(HD-VICP)、视频数据转换引擎以及目标视频端口接口。

HD-VICP 通过面向HD 1080i H.264 high profile 转码的专用加速器,实现了超过3GHz 的DSP处理能力,同时视频数据转换引擎还能管理包括垂直下调节(downscaling)、色度采样(chroma samp ling) 以及菜单覆盖(menu overlay) 等功能在内的视频处理任务。

不到300MHz的DSP内核可用于管理多格式视频转码,并为其它应用预留了足够的空间。

DM6467 可满足媒体网关与MCU 等需要转码技术的市场要求,但其强大的灵活性与高效性对要求同时进行高清编码与解码的应用来说也非常具有吸引力,如视频语音或视频安全等对于多通道标清编码要求较高的市场。

该器件的连接外设中还包括标准PCI 总线及千兆以太网。

DM6437评估板技术手册

DM6437评估板技术手册一、DM6437 EVM概述1.1 dm6437关键特性> 时钟频率达600MHz> 1个TVP5146M2视频解码器(TI提供),支持复合或S视频端子(TVP5146M2: 是一个单芯片数字视频解码器,将所有流行带宽模拟格式视频转化为数字视频分量。

它支持RGB和YPbPr输入信号分量的模数转换,并支持NTSC,PAL和SECAM复合和S-video等输入信号的模数转换并解码成YCbCr分量)> 4个视频DACV输出---支持分量输出,RGB输出,复合输出> 128M DDR2 DRAM> 提供16M non-volatile flash memory, 64M NAND flash, 2M SRAM (volatile: 易丢失的)> 提供UART, CAN(控制器局域网络,一种总线协议) I/O接口> AIC33 立体音频编码器> 10/100 MBS以太网接口> 可配置的boot load 选项> 嵌入式的JTAG 仿真器接口> 4个用户LEDs及4个用户切换点> 提供子板扩展插槽> VL YNQ接口(VLINQ是由Ti公司研制的一种宽带接口,可使用在WLAN、modems, VOIP处理器以及音频视频媒体处理器上。

是一种全双工串行通信接口,将外部扩展物理设备连接到内部总线中。

当这些外部设备连接到内部总线时,就会被映射到内部物理地址空间。

多个VL YNQ 设备会形成一个菊链,设备间采用点对点或主从模式通信。

通过VL YNQ的数据采用8B/10B 编码分包。

VLYNQ总线包括1个时钟信号(CLK)和8个发送线以及8个接受线。

所有VL YNQ 信号只能同时由一个设备控制。

一个设备的发射脚同下一个设备的接收脚相连。

VL YNQ总线的理论最高速率可达125 MHz,而实际数度取决于连接在VL YNQ总线上的物理设备。

基于TMS320DM6437的视频采集接口设计

基于TMS320DM6437的视频采集接口设计摘要:TMS320DM6437是TI公司推出一款专门面向处理多媒体信息领域的DSP,在一般的视频处理产品中得到广泛的应用,因此针对TMS320DM6437设计一种高速简单的视频信号采集电路具有重要的实用意义。

本文提出一种也是利用TI公司的高性能视频解码器TVP5146设计TMS320DM6437视频采集接口的方案,不仅能实现高速实时的视频数据采集,而且电路简单、可靠性高,容易实现。

关键词:TMS320DM6437 TVP5146 视频采集1 引言视频监控系统以直观、方便、实时性等优点被广泛应用于如交通、水利、安防等领域而成为人们一直关注的焦点,然而基于人脸识别的考勤机设计也是很热门的领域。

但是视频监控系统的广泛使用的前提是视频采集。

TMS320DM6437(以下简称DM6437)是TI公司推出的一款专门面向多媒体应用的DSP。

时钟可达600MHz,具有8个并行运算单元,处理能力达4800MIPS;采用的是二级缓存结构;具可外接64位存储器。

使用DM6437设计视频信号采集电路具有以下优点:(1)电路简单(2)高集成度(3)高速。

基于这些优点的视频设计系统是有重要的实用意义。

[1]DM6437的内部集成了存储视频数据的FIFO和视频的行、场同步信号,如果使用DM6437来做视频采集系统的话只需要在一块前端视频采集芯片即可。

本文提出一种利用TI公司的高性能视频解码器TVP5146设计DM6437视频接口的方法。

该方法不仅能实现高速实时的视频数据采集,且无需外加CPLD逻辑控制电路和FIFO缓存,具有电路简单、可靠性高、容易实现等优点。

本文首先介绍DM6437的视频端口,然后论述利用TVP5146来实现DM6437视频采集接口的方法。

2 DM6437视频端口TMS320DM6437提供了VPSS视频处理子系统,方便与各种视频格式接口。

可实现PAL/NTSC标准模拟视频输入,本系统采用的TVP5146是由TI公司推出的一款低功耗,超小封装的高性能视频解码器。

维萨拉DMT340和DM70露点仪说明文件说明书

可全面配置的维萨拉DMT340和手持式DM70露点仪1.选择何种测量方式-你需要 的是固定式仪表还是便携式 仪表?固定安装式露点仪此类仪表通常需要配置外接电源才能工作,从仅具备基本模拟输出功能到具有显示、报警继电器、数据记录、以太网连接等丰富功能,各种型号不一而足。

下面一系列的问题可以帮助缩小产品型号可选范围。

你想使用仪表做什么工作?a. 利用本地显示设备实现连续监测?选用配电板式仪表还是集成显示仪表?b.用于向某处发送控制信号或用于其他目的的信号?信号类型是哪一种?c.报警设在高位设定点还是低位设定点?d.需要进行数据记录吗?固定式安装设备即可安装在OEM设备应用的供给端,用作干燥机监测或控制,也可安装在终端用户应用的需求端,用于连接PLC、数据记录器和配电板式仪表显示设备。

便携手持式设备此类设备为电池供电的移动式设备,尺寸和功能各有不同,并针对不同应用进行了优化。

它们通常被用于现场固定式安装变送器的验证,或者压缩空气系统各个点位的抽检。

压缩空气应用中露点仪表的正确选型正确选择能够满足您特别安装需求的露点传感器和变送器型号是一项重要任务。

本指南将解答选型时您所需了解的关键性问题,为您提供帮助。

阅读本指南之后,您将获得采购决策所需的知识和工具。

维萨拉固定安装式变送器型号分类▪涵盖多种选项的变送器:DMT340系列和HMT337, HMT338▪模拟和串行信号输出:DMT143, DMT152, DPT146▪仅提供模拟信号输出型号:DMT132, DMT143L维萨拉手持式仪表▪轻便型手持式露点仪表DM70露点 -60...-10°C (-76...14°F):▪DMT340 系列 – 可全面配置的变送器▪DPT146 - 集成压力测量功能的露点变送器▪DMT143 – 适用于工业干燥机的小型变送器▪采用180M传感器的DMT143L变送器 – 适用于终端用户,仅具备模拟输出功能▪采用DMP74B探头的DM70–手持式仪表露点 -80...-10°C (-112...14°F):▪DMT152 (-112...14°F)露点变送器2.你现在使用哪一种干燥机类型?对于大多数压缩空气系统来说,干燥机类型决定了露点仪表或传感器的露点范围。

基于DM6437的图像采集和显示系统

基于DM6437的静态图像采集与显示系统设计专业:班级:姓名:学号:指导老师:实习日期:目录一、实习目的: (3)二、实习要求: (3)三、实习过程: (3)3.1、实习平台与设备介绍: (3)3.2、设计原理: (4)3.3、环境设置: (5)3.4、实习仿真: (8)3.5、硬件电路设计 (10)3.6、程序运行过程及结果 (13)3.7、程序: (14)四、实习心得: (22)一、实习目的:该课程是为电子信息工程专业本科高年级开设的专业综合实习课,目的是让学生熟悉和掌握近代信号处理的基本专业知识及实验方法,验证信号处理的基本理论及应用技术,掌握专业实验中常用的仪器设备、开发工具的使用,通过两周的设计实践培养学生综合利用所学知识进行信号处理的能力,为今后的工作学习打下坚实的基础。

二、实习要求:本实习为自选题目,本实习题目为基于DM6437的静态图像采集与显示系统设计三、实习过程:3.1、实习平台与设备介绍:EL-DM6437EVM 达芬奇视频开发板通过专用的DDR2存储控制器接口扩展了64MBytes的DDR2 SDRAM,为视频应用带来了高吞吐、高容量存储带宽,并可以扩展到最大256MByte;256MBit的Nor Flash为视频应用程序脱机运行提供了有力的容量保证;板卡通过一个视频解码芯片和CPU连接,使得CPU可以接受外部的复合视频信号输入和S信号输入,信号都是自动检测,大大提高了视频处理的灵活性;CPU还提供视频DAC,通过几个运算放大器即可把DDR2存储器内的数据输出为用户可观察到的信号,非常方便;除此之外,板卡还包括很多资源,包括音频输入输出、10M/100M的自适应以太网接口、USB2.0接口、实时时钟、4位LED 指示和4位DIP开关量输入、CAN总线及UART接口等等一系列功能;最重要的是所有外部存储器接口信号都连接到扩展接口上,用户可以通过设计外部子板扩展自己的功能。

dm6467中文

目录数字媒体片上系统TMS320DM6467T (2)ARM 子系统 (2)DSP子系统 (3)设备的配置 (3)电源供应 (3)复位 (3)中断 (3)SRM CPU 中断 (4)异步EMIFA (4)DDR2存储器控制器 (4)VIDEO 端接口(VPIF) (4)传送数据流接口(TSIF) (5)视频数据变换引擎(VDCE) (5)HPI (5)USB 2.0 (5)UART通用异步收发器 (6)Inter-Integrated Circuit (I2C) (6)脉宽调节器(PWM) (6)定时器 (6)IEEE 1149.1 JTAG (7)DEVICE CONFIGURATION (7)系统模块寄存器 (7)电源因素 (7)时钟因素 (8)启动顺序 (8)复位配置 (9)复位后的配置 (9)复用管脚的配置 (9)调试 (10)数字媒体片上系统TMS320DM6467TTMS320DM6467T利用TI’s DaVinci™技术满足下一代嵌入式设备的网络媒体编码解码应用处理需求。

ARM 子系统用于控制设备,通常用来负责配置和控制设备。

包括DSP子系统,VPSS子系统,和大量外设和内部存储器。

ARM926EJ-S精简指令,ARMv5TEJ16/32位命令设置,cp15,16K命令缓存,8K数据缓存,写缓存器,Memory Management Unit (MMU),32K Tightly-Coupled Memory (TCM) RAM 32位带宽访问,8K内部ROM(ARM bootloader for non-EMIFA boot options),Embedded Trace Module and Embedded Trace Buffer (ETM/ETB),ARM中断控制,PLL控制,Power and Sleep Controller (PSC)。

DSP子系统C64x+CPU 8个功能单元,两个寄存器文件,两个数据路径,两个通用寄存器文件(A,B)每个包含32个32bit寄存器。

多媒体TITMS320DM6437开发板硬件资源详解

多媒体TITMS320DM6437开发板硬件资源详解多媒体TI TMS320DM6437开发板硬件资源详解目录1 开发板简介 (2)2 典型运用领域 (3)3 软硬件参数 (4)4 开发资料 (6)5 电气特性 (6)6 机械尺寸图 (7)7 核心板型号 (8)8 技术支持 (9)1开发板简介基于TI TMS320DM6437的32位定点多媒体DSP处理器,适合高性能、低成本视频应用开发,最高主频为700MHz;支持8个8bit或4个16bit并行MAC运算,峰值处理能力高达5600MIPS,可实时处理8路CIF或3路D1格式的H.264编码算法;2级Cache体系结构:32KB可配置L1P、80KB可配置L1D和128KB可配置L2;64通道增强型DMA控制器EDMA3,支持复杂的数据类型的传输,利于图像数据高效传输和格式变换;视频处理子系统(VPSS):具有1个VPFE视频输入接口,支持BT.656输入,1个VPBE 视频输出接口,支持NTSC/PAL,S-Video,RGB,YPbPr输出;集成McASP、McBSP、I2C、UART、PCI、HPI、EMIFA等常见接口;核心板大小仅63.5mm*38mm;采用精密工业级B2B连接器,占用空间小,稳定性强,易插拔,防反插。

图1 TL6437-EVM正面图2 TL6437-EVM侧视图1图3 TL6437-EVM侧视图2图4 TL6437-EVM侧视图3图5 TL6437-EVM 侧视图4广州创龙自主研发的TL6437-EVM开发板是基于TMS320DM6437定点DSP核心板,大小仅63.5mm*38mm,功耗小、成本低、性价比高。

采用沉金无铅工艺的二层板设计,专业的PCB Layout保证信号完整性的同时,经过严格的质量控制,满足工业环境应用。

TL6437-EVM引出CPU全部资源信号引脚,二次开发极其容易,用户只需要专上层运用,降低了开发难度和时间成本,让产品快速上市,及时抢占市场先机。

DM6437中的PSP库介绍

DM6437中的PSP库介绍

TMS320DM6437芯片中,TI公司并不提供的CSL(Chip Support Library)进行编程操作,而是改用PSP(Proeessor Support Package)。

PSP是一种针对目标芯片进行硬件操作而在上层提供的复杂任务控制软件包,例如外设I/O传输等。

每个PSP对应一个设备,如DM6437拥有自己的PSP。

在DSP/BIOS中PSP 的基本功能是对所有外设进行设置,这些驱动以库的形式被提供,能够被链接到应用程序中。

PSP驱动由多层构成。

1、DDA层(Device Driver Adapter)

DDA层是操作系统的驱动接口。

它执行IOM调用到适当的、低层的(DDC)功能调用。

它的唯一目的就是解析操作系统的功能性内核驱动。

2、DDC层(Device driver core)

DDC层是驱动的心脏。

DDC层处理处理核心的驱动特性,与设备相关和操作系统相关的操作则调用其它的功能层。

因此,改变DDC层是唯一的步骤来改变或加强驱动器性能。

3、LLC层(Low Level Controller)

LLC层通过芯片支持库(CSL)与外设直接交互。

但是LLC层并不包含在所有PSP驱动中,一些驱动器直接在DDC层中执行LLC层的功能。

4、PAL OS

为操作系统服务的平台抽象层(PALOS)允许DDC层使用基本的操作系统功能,例如旗标处理和中断设置等。

通过使用PALOS功能替代直接调用DSP/BIOS模块,DDC层可以从操作系统中提取出来。

PALOS是一个单独的库,要包括PSP的安装,可以被多个驱动使用。

DM6437有关文档信息

DM6437应用向DSP/BIOS中增加硬中断【整理者】【提供者】43r3【详细说明】DM6437应用向DSP/BIOS中增加硬中断64+的中断系统和以往的不同,中断是基于事件的。

整个硬件CPU接收15个中断,但中断源可以支持最多128个。

64+将中断源视为事件"Event",128个事件可以分别通过配置连接到15个CPU中断。

而128个事件每连续32个可以合并到四个固定的事件中,即Event0(对应事件号0-31)、Event1(对应事件号32-63)、Event2(对应事件号64-95)、Event3(对应事件号96-127)(实际最大有效中断源为124个)。

这样可以通过数量有限的CPU中断来管理大量的中断源,使用灵活。

DSP/BIOS默认将Event0-3分别对应到HWI_INT7-10四个中断号。

TI驱动通过注册Event到这四个事件,进而对应到相应中断。

在中断HWI_INT7-10服务函数中再去判断具体是哪个事件触发的中断。

另外还有几个中断是系统硬件复位中断、NMI中断、预保留中断及仿真通讯中断。

HWI_INT4-6、HWI_INT13、HWI_INT15这5个中断是未使用中断。

用户增加中断服务的话,可以将事件号对应到这5个中断来实现。

以T1高32位定时中断为例,介绍一下DM6437应用中如何在DSP/BIOS操作系统中实现硬件中断。

首先用户需要将T1配置为双32位定时器,T1高32位定时器中断服务函数为 T1HIsr()。

将事件对应到中断HWI_INT5。

1 在DSP/BIOS图形配置界面下打开"Scheduling"->"HWI-Hardware Interrupu Service"。

2 下拉表中有15个中断。

观察各中断使用情况。

右键点击"HWI_INT5",弹出下拉菜单中选"Properties"进入中断属性编辑栏。

DM6437数字媒体处理器

达 芬奇 系 列处 理器 拥 有 非常 大 的字 节可 寻址 地址 空 + 1 . 8 V ( 供D DR 2接 1 3和 内存 ) ,+ 3 . 3 V( 供D SP输入 , 输出

缓冲及板上 的其他芯片 ) 。 衄

道康 宁光学灌 封胶助 下一代 L E D 设计 提 升质量和性 能标准

道康 宁 日前 进一 步扩 展 了其 苯 基硅 光学 灌 封胶 产 品 球 L E D光源 生 产 企 业 都 在 寻 找 创新 性 的新 材 料 解 决 方 线 ,推 出五个全新 的双组份 、热 固化产 品。新产 品的可靠 案 ,以耐受 新 的 L E D产 品更高 的 内部温 度 ,以及越 发严 性得 到进一步 提升 ,并拥有 更佳 的银电极防腐 蚀功能和 针 苛的工 作环 境 , ”道康 宁照 明解 决方 案全球 工业 总监 K a z 对日 益严苛 L E D产品设计标准的更好的耐久性。 Ma r u y a m a评 论 说 ,“ 新 的道 康 宁 的 有机 硅 光学 灌 封 胶

・

为E MI F b o o t 模 式。D M6 4 3 7仅支持小头模式 , 且不可配置。

Байду номын сангаас

提供 S / P DI F接 【 _ _ J

E vM供 电

存储 寻址

司,对字节寻址 的某些 限制 由 DM6 4 3 7相连 的外设决定 ,

外部单独的 + 5 V输入 , 然 后分 成 + 1 . 2 V( 供 DS P核 ) ,

等级 。这两款 产品具有 的更好 的气 体屏 障功 能 ,从而可 以 质量 的照 明效 果 。 ”

保护纤精细 的镀 银 L E D电极免受硫的侵蚀 。除 了能 减少发

光效率损 失外 ,这种特 性还能延长高级 L E D的整体质 量和 使用寿命 。 新 的 OE 一 7 6 2 0 、OE - 7 6 3 0和 OE - 7 6 4 0光 学密 封胶 分

DM6437处理器简述

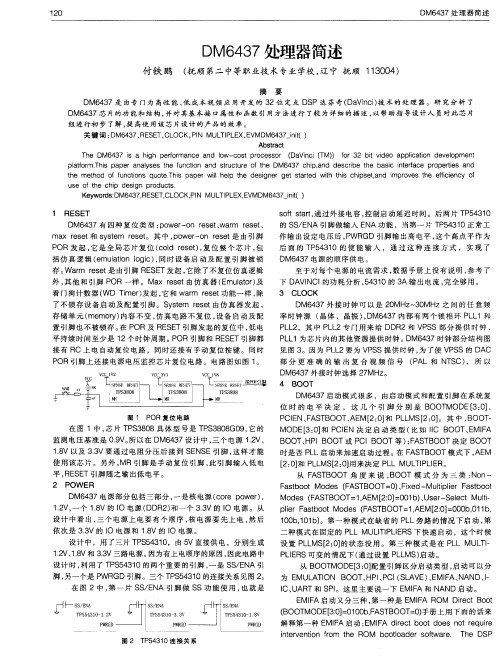

D M6 4 3 7有 四 种 复 位 类 型 : p o we r — o n r e s e t 、 wa r m r e s e t 、 ma x r e s e t 和s y s t e m r e s e t 。其 中 , p o we r — o n r e s e t 是 由 引 脚 P CR 发 起 , 它是全 局芯片复位 ( c o l d r e s e t ) , 复位整个 芯片 , 包 括仿真 逻辑 ( e mu l a t i o n l o g i c ) , 同 时 设 备 启 动 及 配 置 引 脚 被 锁 存。 Wa r m r e s e t 是 由 引脚 R E S E T发起 , 它 除 了 不 复位 仿 真 逻 辑 外, 其他和引脚 P CR一 样 。Ma x r e s e t 由仿真器 ( E mu l a t o r ) 及 看 门 狗 计 数器 ( WD T i me r ) 发起 , 它和 w a r m r e s e t 功 能一 样 , 除 了不 锁 存 设 备启 动 及 配 置 引 脚 。S y s t e m r e s e t 由仿 真 器 发 起 , 存储单元 ( me m0 r y ) 内容不变 , 仿 真电路不复位 , 设 备 启 动 及 配 置 引 脚 也 不 被 锁存 。 在P CR及 R E S E T引脚 发起 的复 位 中 , 低电 平持续时间至少是 1 2个 时钟 周 期 。 P OR 引脚 和 R E S E T引脚 都 接有 R C 上 电 自动 复 位 电路 , 同时 还 接 有 手 动 复 位 按 键 。 同 时 P OR引 脚 上 还接 电源 电压 监 控 芯 片 复位 电路 。 电路 图 如 图 1 。

1 2 0

DM6 4 3 7处理 器 简 述

DM6437原理图(ReV2.1)

T3 D4 L4 M4 P19 W16 N20

VCC1v8 R2 VCC1v8

B

R2 W3

PCIEN MXO

C3

18pF

Y1 27MHz

北

C2

18pF

M22 N22

C4 1000pF

C5 1uF

C6 0 0.1uF

PLLPWR18 MXVDD

MXI/CLKIN N21 MXVss

DM6437

M21

质量好一点

京7 TINP0L R12 17 TOUT0L 这两个直接引出去

33 33

EXT_INT4 EXT_INT5 EXT_INT6 EXT_INT7

TP2

.

VCC3v3

C7 C8

1uF 1uF

B

VCC VV+ C2C2+ C1C1+

16 6 2 5 4 3 1 11 10 8 13

A

1 6 2 7 3 8 4 9 5 10

E20 C20 C21 B20 A20 D21 B21 C16

9 10 11 12 13 14 15 16

8 7 6 5 4 3 2 1

EM_BA0 13,15,17,18,21 EM_BA1 13,15,17,18,21 EMIFA00 13,15,17,18 EM_A01_ALE 15,17,18 EM_A02_CLE 15,17,18 EMIFA03 15,17,18 EMIFA04 13,15,17,18 C_FIELD 14,18 EMIFA05 EMIFA06 EMIFA07 EMIFA08 EMIFA09 EMIFA10 EMIFA11 EMIFA12 CI7 CI6 CI5 CI4 CI3 CI2 CI1 CI0 15,17 15,17 15,17 15,17 15,17 15,17 15,17 15,17

dm7技术手册

dm7技术手册DM7是一款先进的技术产品,具备强大的功能和广泛的应用。

本手册旨在向用户提供全面而详细的使用说明,以帮助用户快速上手并熟练运用DM7。

第一部分:产品概述DM7是一种基于现代科技的全自动控制系统,具备高效、稳定、安全的特点。

它能够广泛应用于工业控制、智能家居和自动化设备等领域。

DM7的设计理念是简单易用,即使对于非专业人士来说,也能轻松地操作和理解。

第二部分:产品特性1. 高性能处理器DM7采用了先进的处理器,能够快速而精确地处理各种指令和数据。

它具备高运算速度和强大的计算能力,可以满足用户在各种复杂场景下的需求。

2. 多功能界面DM7拥有直观、友好的用户界面,采用了现代化的图形化设计,操作简单、方便。

用户可以通过触摸屏或者物理按钮来完成各种操作和设置,这使得DM7在不同使用环境下都能方便地进行控制和调整。

3. 多种连接方式DM7支持多种连接方式,如Wi-Fi、蓝牙、有线网络等,用户可以根据自己的需求选择适合的连接方式。

这样一来,DM7可以与其他设备进行快速而稳定的通信,实现更多的功能和互动。

4. 强大的扩展性DM7具备强大的扩展性,用户可以根据自己的需求,通过安装插件或者扩展板来增加更多功能和接口。

这使得DM7可以应对各种复杂的任务和需求,更好地满足用户的个性化需求。

第三部分:使用说明1. 开机和关机在使用DM7之前,确保设备已连接电源,并按下电源按钮启动。

当需要关闭DM7时,长按电源按钮,并按照屏幕上的提示进行操作。

2. 主菜单启动DM7后,进入主菜单界面。

主菜单上显示了各种功能和应用的图标,用户可以通过触摸屏或物理按钮选择需要的功能,并进入相应的界面进行操作。

3. 功能设置DM7提供了丰富的功能设置选项,用户可以根据自己的需要进行定制。

在主菜单界面中,找到“设置”图标,并点击进入。

在设置界面中,用户可以调整显示亮度、声音、语言等参数,以及其他高级设置选项。

4. 应用程序DM7预装了多个应用程序,如计算器、日历、天气等。

基于DM6437的运动目标检测系统

基于DM6437的运动目标检测系统

周建雄;张笑微

【期刊名称】《微型机与应用》

【年(卷),期】2009(028)012

【摘要】采用非参数化的核密度估计完成背景减法,设计了基于高端数字媒体处理器KM6437的实时运动目标检测系统.提出了一种有效的背景更新策略,使得背景的更新更加可靠,提高了检测的精确度.实验表明该系统能够对目标进行比较实时和准确的检测.

【总页数】5页(P54-57,61)

【作者】周建雄;张笑微

【作者单位】西南科技大学,信息工程学院,四川,绵阳,621010;西南科技大学,信息工程学院,四川,绵阳,621010

【正文语种】中文

【中图分类】TP391.4

【相关文献】

1.基于DM6437的目标跟踪系统设计与实现 [J], 刘伟

2.基于H.264和DM6437的煤矿井下视频监控系统设计 [J], 王雯;马宁

3.基于DM6437的H.264视频编码系统设计 [J], 陈鹏

4.基于DM6437的运动目标跟踪系统研究 [J], 袁晓东;牛晰

5.基于图像分解和DM6437的嵌入式车牌定位系统 [J], 王应军;赵晨萍;方惠敏

因版权原因,仅展示原文概要,查看原文内容请购买。

dm7技术手册

dm7技术手册

DM7技术手册是一款详细介绍DM7技术的文档,主要包含以下内容:

1.DM7技术概述:介绍DM7技术的背景、发展历程、应用领域等。

2.DM7系统架构:详细描述DM7系统的整体架构,包括硬件架构和软件架构,以及各个组件的相互关系和工作原理。

3.DM7软件功能与使用方法:详细介绍DM7软件的各种功能和使用方法,包括软件界面、菜单、工具栏等的使用方法和技巧。

4.DM7软件操作流程:介绍使用DM7软件的一般流程,包括数据准备、建模、结果输出等步骤。

5.DM7技术算法与实现:深入介绍DM7技术的算法原理和实现方法,包括核心算法、优化方法等。

6.DM7技术应用案例:通过实际案例介绍DM7技术的应用场景和效果,帮助用户更好地理解和应用该技术。

7.DM7技术常见问题与解决方案:汇总用户在使用DM7技术过程中遇到的问题,并提供相应的解决方案。

8.DM7技术扩展与未来发展:介绍DM7技术的未来发展方向和可能的扩展领域,为用户提供前瞻性的信息。

总之,DM7技术手册是一本全面介绍DM7技术的书籍,

可以帮助用户更好地理解、应用和掌握该技术,从而在实际

工作中发挥更大的作用。

第3章 TMS320DM6437的指令系统-DSP原理及应用-张雪英-清华大学出版社

DSP原理及应用------TMS3206437架构、指令、功能模块、程序设计及案例分析

表3-2 TMS320C64xDSP各指令对应的延迟间隙数

指令类型

延迟间隙 功能单元等待时间 读周期

NOP

0

1

Store

0

1

i

Single cycle

0

1

i

Multiply(16×16)

1

1

i

Load

4

1

i

Branch

符号 p r rsv s src1 src2 ucstn x y z

.L Unit

.M Unit √ √ √ √ √ √ √ √ √ √ √

.S Unit

.D Unit

DSP原理及应用------TMS3206437架构、指令、功能模块、程序设计及案例分析

续表

指令 MPYLH MPYLHU MPYLUHS MPYLSHU MV MVC+ MVK MVKH MVKLH NEG NORM

因此就形成了指令的功能单元之间的映射关系。一般而言, 与乘法相关的指令都在.M单元执行;需要产生数据存储器地 址的指令,在.D功能单元执行;算术逻辑运算大多在.L和.S单 元执行。

DSP原理及应用------TMS3206437架构、指令、功能模块、程序设计及案例分析

指令 ABS ADD ADDAB ADDAH ADDAW ADDK ADDU ADD2 AND B disp B IRP+

.L Unit

√ √ √ √ √

.M Unit

.S Unit √ √ √

√ √

.D Unit √

DSP原理及应用------TMS3206437架构、指令、功能模块、程序设计及案例分析

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TMS320DM6437 DMP介绍TMS320DM6437 Digital Media Processor—一种高性能数字媒体处理器:VelociTI.2结构DSP内核,先进超长指令字(VLIW)C64x+指令集特性C64x+ L1/L2存储器结构口仅支持小端模式视频处理子系统(VPSS)外部存储器接口(EMIF)增强型直接存储器访问控制器(EDMA):64个独立通道1个64位看门狗定时器2个UART(带RTS和CTS流控信号)主/从I2C总线控制器两个多通道缓冲串行接口(McBSP)多通道音频串行接口(McASP0)高端CAN控制器(HECC)16位主机接口(HPI)32位、33MHz、3.3V PCI主从接口10/100Mb/s以太网MAC(EMAC)VL YNQ接口(FPGA 接口)VL YNQTM接口(FPGA 接口)片上ROM Bootloader独特的节电模式灵活的PLL时钟产生器IEEE-1149.1(JTAG)多达111个GPIO(与其他功能复用)引脚及封装3.3V/1.8V I/O;1.2V/1.05V内部一、DaVinci DM6437 概述TMS320C64x DSP内核:TMS320DM6437是专门为高性能、低成本视频应用开发的、32位定点DSP达芬奇(DaVinci(TM)) 技术的处理器。

该器件采用TI第2代超长指令字(VLIW)结构(VelociTI.2)的TMS320C64x+ DSP内核,主频可达700MHz,支持8个8位或4个16位并行MAC (multiply-accumulates)运算,峰值处理能力高达5600MIPS。

> C64x片内有2个数据通道、8个功能单元和2个通用寄存器文件(A和B)。

8个功能单元(2个乘法器和6个算术逻辑单元)用于提高影像和图像应用的性能。

每个通用寄存器文件包含32个32-bit寄存器。

这些通用寄存器可以用做数据指针或者数据地址指针。

数据类型可为8-bit,16-bit,32-bit,40-bit,64-bit。

而8个功能单元和2个寄存器文件又分成了相同的两组,每组占用一个数据通道。

两个数据通道之间包含有两个数据交叉通路。

> C64xDSP采用超长指令字(VLIW),即在每个时钟周期最高可提供8条32位指令,总字长为256位的指令包同时分配到8个并行处理单元。

在700MHz的时钟频率下,当片内8个处理单元同时运行时,其最大处理能力可以达到5600MIPS。

> C64x DSP具有双16bit扩充功能,芯片能在一个周期内完成双16位的乘法、加减法、比较、移位等操作。

C64x通过把DSP运算压缩在较少的周期里,加速通信和图像应用。

在增强并行性的扩展中,四组8位/两组16位指令允许每秒进行约90亿次8位乘法上累加周期(MAC)运算。

C64x+ CPU:SPRU732采用2级Cache存储器体系结构,片上有32KB RAM/Cache可配置的1级程序存储器L1P,48KB RAM + 32KB RAM/Cache可配置的1级数据存储器L1D和128KB RAM/Cache 可配置的2级程序/数据存储器L2,存储器体系结构更灵活、合理,有利于提高图像处理代码/数据的吞吐率。

系统控制功能:TMS320DM6446微处理器的系统控制模块提供了看门狗(WT)、中断控制器、电源管理控制器、复位控制器及2个片上振荡器。

Clock PLLs:DM6437有两个独立控制的PLLs。

PLL1产生DSP,DMA,VPFE以及其他外设所需要的时钟频率。

PLL2产生DDR2接口和VPBE在特定模式下所需要的时钟频率。

推荐的PLLs输入时钟频率是27MHz晶振频率。

关于PLL的详细信息见SPRU978. EDMA:片上具有64通道增强型DMA控制器EDMA3,其支持复杂的数据类型的传输,有利于图像数据的高效传输和格式变换。

外部存储器接口:一个专用的32-bit、200MHz、256MB寻址空间的DDR2存储器接口用于接口高速、大容量的DDR2存储器,以存储代码和数据;一个8-bit、64MB寻址空间的异步存储器接口用于接口8位Nor Flash或Nand Flash,以存储固化代码。

片上外设:> 2个可配置的视频接口:一个专用的单通道视频输入接口,既可以方便地与各种数字视频输入标准接口,还具有常用的视频预处理功能;一个专用的单通道视频输出接口,既可以提供多种模拟视频输出标准,还可以提供各种数字视频输出标准接口,并且在视频输出之前,还支持多个视频窗口管理及在视频画面上叠加文本数据;>1个带有MDIO模块10/100M以太网MAC(EMAC),方便实现嵌入式视频网络化要求;>1个VLYNQ接口(4-bit发送,4-bit接收)>1个I2C总线接口,可无缝连接视频解码器/编码器和音频解/编码器的控制口,方便实现音/视频解/编码器的控制;>2个McBSP>1个多通道音频串口(McASP)(有4个串化器),可无缝连接音频解/编码器器件,实现模拟视频信号的输入/输出;>2个64-bit的通用定时器,每个可配置为2个32-bit的定时器>1个64位看门狗定时器> 1个用户可编程的16-bit HPI接口,方便实现主/从结构的双处理器视频处理系统。

>1个多达111管脚的GPIO,带可编程的中断或事件产生模式,和其它外设复用>2个UARTs,其中一个支持硬件交互;>3个PWM>1个high-end controller area network(CAN)控制器HECC>1个32-bit 33Mhz的PCI总线,方便与PC机接口,实现多板级并行工作。

>2个无缝外部内存接口:一个高速同步内存接口,专用于DDR2;一个异步外部内存接口EMIFA,用于速度较慢的内存或外设。

由上可知,DM6437是非常适合于作为单通道视频处理系统的主处理器,为了使DM6437适用于多通道视频监控系统,需要将多个视频通道的数据复合后,再通过DM6437片上视频输入接口输入。

二视频处理子系统(VPSS-Video Processing Sub-System)DM6437片上视频输入/输出接口统称为视频子系统VPSS。

VPSS提供一个VPFE (Video Processing Front End)输入接口,连接外部设备如图像传感器,视频解码器等,以及一个VPBE(Video Processing Back End)输出接口,连接显示设备,如模拟SDTV显示器,数字LCD面板,HDTV视频编码器等。

VPSS相关寄存器有PID,PCR(VPSS control reg)等。

VPFE用于输入数字视频数据,为多种标准的数字视频输入提供无缝接口,并为输入的数字视频数据作必要的预处理。

VPBE用于输出数字视频数据,以驱动显示器显示视频图像。

1. VPFEVPFE组成:CCD控制器(CCDC), 预处理器(Preview Engine), Resizer, Hardware 3A(H3A) Statistic Generator, Histogram blocks. 这些模块给DM6437提供了灵活有力的前端接口,描述如下:> CCDC提供一个图像传感器和数字视频源接口> Preview Engine是一个带参数的硬件图像处理模块,它用于原始彩色数据的转换:从Bayer 类型转换到YUV 4:2:2> Resizer模块缩放输入图像数据,以满足显示播放视频编码程序希望的分辨率> H3A模块循环控制Auto Focus(AF),Auto White Balance(AWB), Auto Exposure(AE)> 直方图模块处理彩色象素获取统计信息,提供给H3A模块实现各种3A(AE/AF/AWB)算法,以平滑最终的输出图像/视频VPFE相关寄存器有:CCDC(controller), PREV(preview engine/image signal processor), RESZ(resizer), HIST(Histogram), H3A(AF/AWB/AE), VPSS(VPSS Shared Buffer Logic Reg) CCDC:CCD控制器是DM6437数字视频输入接口,它从CMOS或CCD传感器中接收图像/视频数据,或从视频解码器设备接收各种格式的YUV数据。

这个模块支持以下功能特征:> 常用的Bayer类型格式> 产生HD/VD计时信号> 提供逐行和隔行扫描的传感器接口> 支持REC656/CCIR-656 标准(YCbCr 4:2:2 format, either 8- or 16-bit).> 支持YCbCr 4:2:2格式,8-bit或16-bit的离散H和VSYNC信号(行同步和场同步)> 支持高达16-bit的输入> 光黑箝位信号发生器> 快门信号控制> 数字箝位和黑电平补偿.> 支持10-bit到8-bit的A-law压缩> 写SDRAM前做低通滤波。

如果此滤波功能被启用,则输出图像每行最左端和最右端的2个像素点被裁剪> 输出数据范围从16-bit到8-bit(按8-bit输出要节省一半的存储空间)> 支持可编程的下采样> 通过一个外部写使能信号控制向DDR2的输出> 水平和垂直方向都支持高达16k像素的图像尺寸CCDC相关寄存器的内存映射212。

Preview Engine:Preview Engine是一个实时图像处理器,它接收传感器(CMOS/CCD)的未压缩的原始图像/视频数据并将之转换为YCbCr 4:2:2格式的数据。

Preview Engine的输出可以用于视频压缩和外部显示设备,如NTSC/PAL模拟编码器或数字LCD显示。

总括支持以下特点:> 接受传统的Bayer格式> 获取来自CCD/CMOS控制器或DDR2内存的图像/视频数据> 支持1280像素宽的输出> 若执行边界处理,可实现自动/强制的像素/行裁剪。

如果所有相应模块被使能,则输出图像的左右各7列像素及上下各4行像素被裁剪> 对超过1280象素宽度的输入图像做简单的水平均值化(均值因子2,4或8)> 捕捉Dark帧存储到DDR2> 从DDR2获取Dark Frame,对每个输入的原始数据帧进行黑帧减操作,逐象素的改善视频帧质量> 镜头阴影补偿。

每个输入象素乘以一个相应的8-bit增益值,结果做右移处理,右移位数可编程(0-7 bits)> 通过A-LAW解压缩将8-bit非线性数据转换成10-bit的线性数据。