Altera Recent Advances in Die Stacking and 3D FPGA

Altera Stratix V FPGA提供RLDRAM 3存储器支持

RL AM DR 3存 储 器 支 持

A tr 公 司 发 布 了 S rt 系 列 F GA, 用 于 支 持 l a e t iV ax P 适

Mi o c n技术 公 司 的下 一 代 低 延 时 DRAM ( DRAM r RL 3存

2 m ta i F GA 系 列 并 拥 有 许 多 新 的 生 产 效 率 特 8 n S rt V P x 性, 这些 特 性 使 广 大 设 计 团 队 能 够 获 得 更 快 速 的 时 序 逼

近 , 而缩 短产 品 推 出市 场 的 时 间 。 从

风 河 与 L I 合 推 出 S联 网络 通 信 多核 解 决 方 案

采 用 外 部 存 储 器 时 , 自动 缩 短 设 计 时 间便 易 用 、 观 的 部 分 可 重 配 置 设 计 利 直 流 程 , 一 步 降 低 功 耗 和 整 体 系 统 成 本 。 同 时 , 新 推 进 最 出 的 IE 版 本 还 可 提 供 一 项 低 成 本 仿 真 方 案 , 持 嵌 S 支 入式 设计 流程 。 部 分 可 重 配 置 技 术 具 备 可 即 时 调 整 的 高度 灵 活 性 , 可 以大 幅 扩 充 单 一 F GA 的容 量 。在 器 件 运 行 中 , 计 人 P 设 员 可 对 F GA 某 些 区 域 进 行 重 新 编 程 , 此 加 入 新 的 功 P 藉 能 , 器 件 其余 部 分 正 在 运行 的应 用 则 完 全不 会 受 到 任 何 而 影 响 。部分 可 重 配 置 技 术 还 可 以帮 助 设 计 人 员 有 效 地 管

S r tx V ta i GX 和 S r tx V GA。 S r t GX ta i GS FP tai V x FPGA

三星等计划利用石墨滞实现“在大面积柔性基板上制造三维存储器”

Sc 门c nd Ye c J 1 ea h oo 『

… …

I fr t n n o mai 0

脏 组 织 细 胞 同 样 的 功 能 , 还 需 要 进 一 步 确

证 。

人工 譬 让 损 7 纳 i . 髂 鲎 8 明

凰再空 来来霄望罔翼 兕 器

后 ,心 肌 细 胞 表 面 密度 是 对 照 样 本 的6 。 神 倍

经 细胞 密度 在4 天后 也增 加 了1 。 倍 论 文 合著 者 、布 朗大 学工 程 与整形 外 科 副 教 授 托 马 斯 ・ 伯 斯特 说 ,碳 纳 米 管 纤 维 编 韦 织 的 支 架 有 弹 性 而 且 耐 用 , 能像 心 脏 组 织 那 样 扩 展 收 缩 , 因此 心 肌 细 胞 和 神 经 细 胞 能在 上 面 大 量 产 生 新 细 胞 ,使 心 脏 局 部 受 伤 的地 方 再 生 。而 且 碳 纳 米 管 导 电性 能 极 佳 , 能 很 好 地 作 为 一 种 心 脏 稳 定 跳 动 所 依 赖 的连 接 电 路 来 发挥 作 用 。这 种 材 料 未 来 甚 至 能 用 来 造 出一颗 健康 的心脏 。 研 究人 员 下一 步将 改善 支架 形 状 以更 好模 拟 心 脏 电流 ,制 造 出一 种 内部 试 管 模 型 , 以

遭出 一颗健廉愈脏

当心 脏 病发 作 时 ,心壁 上某 些神 经 细胞 以 及 保 持 心 脏 节 律 跳 动 的 特 殊 细 胞 会 受 到 损 伤 ,外 科 手 术 无 法 修 复 这 种 损 伤 区域 。 据 美 国物 理 学 家 组 织 网报 道 , 最 近 ,美 国布 朗 大 学 和 印度 理 工 学 院工 程 人 员 合 作 ,给 心 脏 造 出 了一 种 人 工 纳 米 补 丁 , 经 实 验 显 示 能 让 心 脏 病 发 作 所 造 成 的 损 伤 区域 恢 复 功 能 。 该研 究发 表在近 日出版 的 《 生物材 料 学报 》上 。 这种 人 工纳 米补 丁是 一种 支 架型 的结构 , 由碳 纳 米 管 纤 维 和 一 种 官方 许 可 的聚 合 物 材 料 构 成 。研 究人 员使 用 了~ 种直 径 约2 0 m的 0n

Altera FPGA英汉术语对照表

Comm, Interface & Peripherals configuration random-access memory(CRAM) Compile Component Configuration (FPGA) Crosstalk Cyclone® III automotive grade devices D Data access data path DCFIFO DDR DDR controller Deinterleaver Block Demonstration Design Design Entry/Planning Design Partition design security Digital Signal Processing(DSP) DLL down training download manager DSP Block/Multiplier Block DSP capabilities dual-purpose pins Dynamic On-Chip Termination (OCT) Dynamic parallel termination Dynamic Reconfiguration Dynamic series termination E Electrical Idle Error Correction Coding (ECC) Error Message Ethernet External Memory Interfaces F

2D Median Filter 3rd Party EDA Synthesis 3rd Party Formal Verification A Active Parallel (AP) ALM Altera Complete Design Suite Altera Installer Altera License Setup Alpha Blending Mixer AN522 version 2.0 Analysis & Synthesis Archives Assignment Editor B Base Address Register Biasing Circuitry block diagram Board Design and Layout Board Test, Design and Layout Boot Copier boundary-scan description language (BSDL) burst length burst transfers C Cache Capacitance charge pump Carry Chain Chip Editor Chroma Resampler Color Plane Sequencer Color Space Converter Common Clock common mode voltage Common Public Radio Interface(CPRI)

资源受限--使用signaltapII调试FPGA设计中的bug

资源受限--使用signaltapII调试FPGA设计中的bug问题描述:在一次调试中发现这样的问题,用signaltapⅡ观察4个信号,结果正确,若再加一路观察信号,则时序中有错误。

好像是signaltapⅡ对原来的逻辑造成了影响,又或者是signaltapⅡ采样出来并传上电脑来的数据出错。

在网上搜索了一下,这方面的资料。

另外,通过对这方面内容的了解之后,接触到这样一个词汇:增量编译(incremental compilation)如果能好好利用quartus的这个功能,那么将在一定程度上解决FPGA设计中编译太慢的问题。

所以这个问题可以深入研究。

在网上收到一篇altera关于这方面的文档《Quartus Ⅱ Incremental compilation for hierarchical and team-based design》好像是Quartus手册中的某一章。

因为现在其中大部分我都用不到,并没有做仔细研究,只是看了其中的<Debugging Incrementally With the SignalTap ⅡLogic Analyzer>这一小节。

总结一下,使用增量编译SignalTap ⅡLogic Analyzer的步骤,即在加入并编译SignalTap ⅡLogic Analyzer时保持原来综合的布局布线结果不变的方法。

这有几个处:1、SignalT ap ⅡLogic Analy观察信号进行调试时,和不使用SignalTap ⅡLogic Analyzer时的逻辑是一样的,即你调试的逻辑和最终使用的逻辑的一样的。

2、当设计较大时,在需要改变SignalTap ⅡLogic Analyzer的设置时,可只编译SignalTap Ⅱ这样就节约了时间。

步骤:1、在assign->design partitions window中将当前工程的netlist type 设置为post-fit.2、全编译。

Altera 28nm FPGA突破带宽瓶颈应对云计算时代

标 准 , 足 兼 容 性 要 求 , 如 , 0 G/ 满 例 1

4 /0 I tr k n和 P I x rs  ̄ O G 1 0 G、 el e n a C pes E ( C e ) e 、 e 2、 e 。V n e P I@ G n 3 G n G n l ic Hu

收发器 性能 。Байду номын сангаас

G 还包 括 一 个 7 7 A x 2位 16 0 Mb s 0 /

DD 3存 储 器 接 口 , 及 所 有 IO 上 R 以 /

的 16G / V . b s L DS通 道 。

高 性 能 内 核

Ah r ea对 Srt P A 内 核 体 t i V FG ax 系 结 构 进 行 了 改 进 , 提 高 了 面 积 和 逻 辑 效 率 以 及 系 统 性 能 。包 括 :1新 () 的 自适 应 逻 辑 模 块 ( L 体 系 结 构 , A M)

本 要 求 呢 ? 在 4月 2 日 的 Srt 0 t iV ax

创 新 使 其 能 够 面 向 特 定 市 场 迅 速 开

发 不 同型号 的产 品。 ” Srt P A还 支 持 与 1 背 t i VF G ax 0G 板 (0 AS KR 和 光 模 块 的 直 接 1 GB E— )

ASC可 以实 现 5 %的 功耗 降 低 。 I 0 Ah r 于 2 1 ea将 0 1年 第 一 季 度 开始

发 售 Srt P A 样 片 ,并 采 取 和 t i VF G ax 4 l 一 样 的激 进 营销 策 略 ,以争 取 0I m 客 户 , 占市 场 。V n e 抢 icHu这 样 解 释 :

链 接 。Srt T F GA 的 2 b s t i V G P ax 8G /

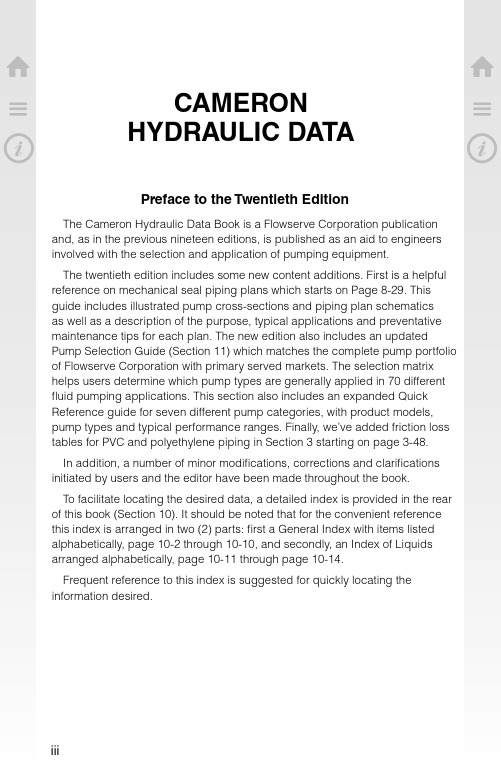

卡梅伦液压数据手册(第 20 版)说明书

iv

⌂

CONTENTS OF SECTION 1

☰ Hydraulics

⌂ Cameron Hydraulic Data ☰

Introduction. . . . . . . . . . . . . ................................................................ 1-3 Liquids. . . . . . . . . . . . . . . . . . . ...................................... .......................... 1-3

4

Viscosity etc.

Steam data....................................................................................................................................................................................... 6

1 Liquid Flow.............................................................................. 1-4

Viscosity. . . . . . . . . . . . . . . . . ...................................... .......................... 1-5 Pumping. . . . . . . . . . . . . . . . . ...................................... .......................... 1-6 Volume-System Head Calculations-Suction Head. ........................... 1-6, 1-7 Suction Lift-Total Discharge Head-Velocity Head............................. 1-7, 1-8 Total Sys. Head-Pump Head-Pressure-Spec. Gravity. ...................... 1-9, 1-10 Net Positive Suction Head. .......................................................... 1-11 NPSH-Suction Head-Life; Examples:....................... ............... 1-11 to 1-16 NPSH-Hydrocarbon Corrections.................................................... 1-16 NPSH-Reciprocating Pumps. ....................................................... 1-17 Acceleration Head-Reciprocating Pumps. ........................................ 1-18 Entrance Losses-Specific Speed. .................................................. 1-19 Specific Speed-Impeller. .................................... ........................ 1-19 Specific Speed-Suction...................................... ................. 1-20, 1-21 Submergence.. . . . . . . . . ....................................... ................. 1-21, 1-22 Intake Design-Vertical Wet Pit Pumps....................................... 1-22, 1-27 Work Performed in Pumping. ............................... ........................ 1-27 Temperature Rise. . . . . . . ...................................... ........................ 1-28 Characteristic Curves. . ...................................... ........................ 1-29 Affinity Laws-Stepping Curves. ..................................................... 1-30 System Curves.. . . . . . . . ....................................... ........................ 1-31 Parallel and Series Operation. .............................. ................. 1-32, 1-33 Water Hammer. . . . . . . . . . ...................................... ........................ 1-34 Reciprocating Pumps-Performance. ............................................... 1-35 Recip. Pumps-Pulsation Analysis & System Piping...................... 1-36 to 1-45 Pump Drivers-Speed Torque Curves. ....................................... 1-45, 1-46 Engine Drivers-Impeller Profiles. ................................................... 1-47 Hydraulic Institute Charts.................................... ............... 1-48 to 1-52 Bibliography.. . . . . . . . . . . . ...................................... ........................ 1-53

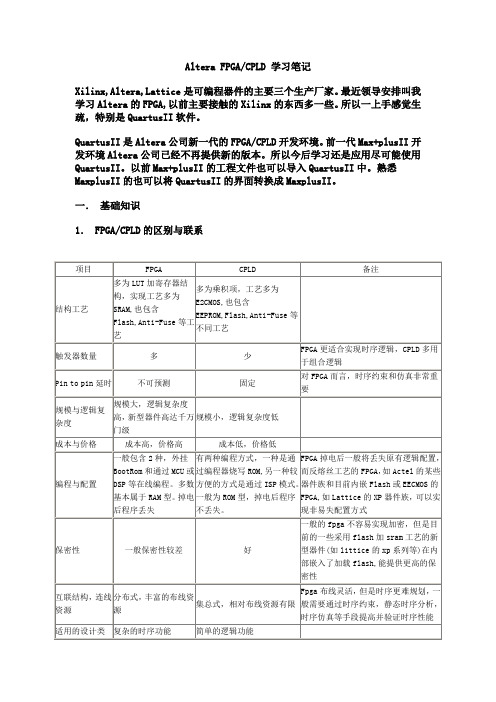

Altera FPGACPLD 学习笔记

Altera FPGA/CPLD 学习笔记Xilinx,Altera,Lattice是可编程器件的主要三个生产厂家。

最近领导安排叫我学习Altera的FPGA,以前主要接触的Xilinx的东西多一些。

所以一上手感觉生疏,特别是QuartusII软件。

QuartusII是Altera公司新一代的FPGA/CPLD开发环境。

前一代Max+plusII开发环境Altera公司已经不再提供新的版本。

所以今后学习还是应用尽可能使用QuartusII。

以前Max+plusII的工程文件也可以导入QuartusII中。

熟悉MaxplusII的也可以将QuartusII的界面转换成MaxplusII。

一.基础知识1. FPGA/CPLD的区别与联系表1-12.逻辑电路概念① 组合逻辑电路的输出信号只与该时刻的输入信号有关,而与电路原来所处的状态无关。

② 时序逻辑任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关。

时序电路的特点是具有记忆元件(最常见的是触发器),具有反馈通道。

包括各类触发器、寄存器、各类计数器和顺序脉冲发生器,各类存储器。

二. Quartus II安装破解这里以Quartus II5.1为例。

QuartusII对PC机硬件要求较高,尽可能采用高配置的PC机。

安装一路next就可以了。

主要是破解,一般的配套光盘都有license文件,但需要自己修改HOSTID,也就是你的网卡的物理地址,介绍一下流程。

1.安装完毕QuartusII后,将sys_cpy.dll文件复制copy到C:\altera\quartus50\bin,将原来的文件覆盖。

2.在C盘新建文件夹flexlm,将光盘中的license.dat拷贝到c:\flexlm中。

同时将只读属性去掉。

3.打开“开始”->运行输入cmd 进入dos模式。

然后输入ipconfig/all 然后记下physical address,也就是hostid。

第二章 ALTERA可编程逻辑器件

第二章 ALTERA 可编程逻辑器件

本章主要讲述了 ALTERA 公司 PLD 芯片的特点和性能,初学者可以跳过,等你需 要考虑设计的效率和可靠性时,需要仔细了解,并且那时候你最好参考相关的英

文手册原文。

ALTERA 在 20 世界 90 年代以后发展很快,是最大的可编程逻辑器件供应商 之一,总部设在位于硅谷圣侯塞,其主要产品有:属于 CPLD 的 MAX3000/5000/7000/9000 和 CLASSIC 系列;属于 FPGA 的 FLEX6K/8K/10K、 APEX20K/ACE1K/APEXII/MERCURY/EXCALICUR 和 STRATIC 系列。ALTERA 公司的开 发软件 MAX+PLUSII 被普遍认为是最优秀的 PLD 开发平台之一,适合开发中小规 模 PLD/FPGA;软件 QuartusII 是新一代 FPGA/PLD 开发软件,适合新器件和大规 模 FPGA 的开发,将逐步取代 MaxplusII。目前 MAXPLUS 软件的资料比较多,但 QUARTUS 软件讲的很少,我们的教程上两种都讲了,但我们强烈建议使用 QUARTUS,我们的例子也基本以 QUARTUS 为主,为什么呢?因为现在单位开发项目 基本都用 QUARTUS 软件,你直接学习 QUARTUS 以后就可以直接使用上了;另外 QUARTUS 性能远比 MAXPLUS 好。

5v

3.3v

3.3v

2.5v

宏单元 备注

EPM7032S EPM7032AE EPM3032A EPM7032B 32

EPM7064S EPM7064AE EPM3064A EPM7064B 64

EPM7128S EPM7128AE EPM3128A EPM7128B 128

第1章-Altera新型系列器件简介

1. 成本优化的架构

传统上,CPLD由基于宏单元的逻辑阵列块(LAB)和特定 的全局布线矩阵组成。这种基于宏单元的构架,随着逻辑密 度的增加,布线区域呈指数性增长,因此当密度大于512宏 单元时,不具有高效的可升级性(见图1.1)。

第1章 Altera新型系列器件简介 图1.1 低成本的MAXⅡ架构占用更小的裸片面积

第1章 Altera新型系列器件简介 图1.2 MAX Ⅱ器件平面图

第1章 Altera新型系列器件简介

2. 低功耗 MAXⅡ器件是动态功耗较低的CPLD。图1.3给出 了MAXⅡ和上一代MAX器件之间的功耗对比。

第1章 Altera新型系列器件简介 图1.3 MAXⅡ器件与MAX器件的功耗对比

接口 SPI 从设备接口

并口 无接口

数据宽度 串行 3~16 串行

占用逻辑单元数 42~97 45~140 0

I/O 引脚数 4

14~46 7~13

第1章 Altera新型系列器件简介 5. 实时在系统可编程能力(ISP)

MAX Ⅱ器件支持实时在系统可编程(ISP),允许用户编 程正在工作的器件。这个功能使得用户可以快速地进行现场 产品升级,而无须将设备断电之后再重新进行初始化配置。

第1章 Altera新型系列器件简介 图1.5 使用独立的串行EEPROM

第1章 Altera新型系列器件简介 图1.6 使用MAXⅡ器件中的用户Flash存储器

第1章 Altera新型系列器件简介

用户Flash存储器与JTAG电路及内核逻辑之间都有 接口,用户可以灵活地采用各种方法对存储器进行读 写操作。如果想把用户Flash存储器连接到一个标准总 线,如串行外设接口(SPI)、并口等,可在Quartus Ⅱ软 件中通过一个基于GUI的宏功能(Megafunction)自动创 建相应的接口(见图1.7)。

altera signaltap核例化与使用 -回复

altera signaltap核例化与使用-回复信号Tap是一款由Altera公司开发的逻辑分析仪软件,用于对FPGA设计进行调试、验证和分析。

它提供了一种非常方便的方法来检查和监视FPGA内部信号的变化。

本文将详细介绍如何对SignalTap进行核例化并使用。

一、SignalTap的核例化1. SignalTap的引入和工具链Altera的Quartus Prime软件套件提供了SignalTap的设计和核例化。

在开始使用SignalTap之前,首先需要下载并安装Quartus Prime软件,并验证其正确安装。

2. 设计工程和工程设置在Quartus Prime中创建一个新的项目,并导入FPGA设计文件。

确保你的设计文件已经被编译并在FPGA上烧录。

3. 添加SignalTap IP核在Quartus Prime的项目菜单中,选择"Add/Remove MegaWizard"选项。

在弹出的对话框中,在左侧的IP Catalog窗口中选择"SignalTap II"核,在右侧的"Selected"窗口中点击"Add"按钮。

然后点击"OK"按钮关闭对话框。

4. 配置SignalTap IP核双击添加的SignalTap II核来打开其配置对话框。

在弹出的对话框中可以配置SignalTap II IP核的各种参数,包括采样时钟、采样触发条件等。

根据设计需求进行相应的配置,并点击"OK"按钮保存配置并关闭对话框。

5. 生成新的设计文件在Quartus Prime的菜单中选择"Processing"和"Start SignalTap II HDL design analysis"选项。

然后选择在第3步添加的SignalTap II IP核作为要分析的目标。

安可与TI共同开发出采用铜柱凸点的倒装芯片封装

范 20 0 3年 5月第 1版. 2 航 天 专项 工 程 电 子 元 器件 标 准 要 求 ( 试

KK) ( 1级和航天专项要求不是只针对一种或

几种特定 产 品的要 求 , 而是 一套 关 于混 合集 成 电 路高质量 高可靠 等级 的标 准要求 。为持续 有效地 研 制 、 产 出满 足 K( ) 和航 天专项 要 求 的产 生 K1级

焊接帽在内的凸点整体高度为 3 — 5 x。设想用于 C P及 PP Pcae iPcae 。 0 4l a n S o ( akg l akg) O

《 集成 电路通讯 编辑部 摘

炼等试验条件均有加严。质量一致性检验则增加

了 x射线 检查 、 热性 能试验 、 频振 动 、 态 寿命 扫 稳 试验装 置监测 、 除水汽外 的其它气 体检测 、 抗辐照 和热真 空试验 等 ; 键合强 度 、 S 温 度循 环 、 E D、 抗盐 雾等试验 条件亦 有加严 。 因此 , 筛选 和质 量一 致 性检 验要 做 的主要 工 作是按照 新增 的试 验项 目、 加严 的试验 条 件进 行

5 结束语

从 H级 向 K级 发展 , 混合集成 电路技 术 和 是 可靠性 发展 的 内在需 求 。客 观上 , 是一 个 必然 这 趋势 。另一方 面 , 相关 产 品 和市 场 的需 求 呼 声也 越来 越பைடு நூலகம் , 天系统 有 关 院所 对 在研 电路 已明确 航 提 出了 K( 1 级 要求 和航 天专项 要求 。 因此 , K) 无

论是从技术发展趋势还是从产品和市场需求来

看 , 时 机 地 发 展 K( 1 级 和航 天 高 可 靠 电 不失 K)

路 , 十分必要 的 。 都是 参 考文献

全面降低系统功耗 Altera推业界首款低功耗28nm FPGA

全面降低系统功耗Altera推业界首款低功耗28nm

FPGA

业界唯一投产的低功耗28 nm FPGA,帮助开发人员降低了PCIe Gen2应用的系统总成本

2013年3月19号Altera公司(NASDAQ:ALTR)今天宣布,其28 nm Cyclone® V GT FPGA全面通过了PCI Express® (PCIe®)2.0规范的兼容性测试。

Cyclone V GT FPGA目前已经投产,是业界第一款实现了5 Gbps数据速率并支持PCIe 2.0互操作性的低成本、低功耗FPGA。

在最近的PCI-SIG实验室测试中,Cyclone V GT FPGA成功通过了所有PCI-SIG®兼容性和互操作性测试,目前已经收录到PCI-SIG Integrators名录中。

与以前的FPGA相比,在开发基于PCIe Gen2的应用时,Cyclone V GT FPGA帮助开发人员大幅度降低了系统成本和系统功耗。

Altera资深产品市场经理Sabrina Raza评论说:我们的Cyclone V GT FPGA实现了与PCIe Gen2的兼容,这是我们28 nm Cyclone V FPGA 系列成功推出的另一里程碑。

对PCIe Gen2系统性能有要求的客户现在可以使用低功耗FPGA,降低其系统总成本,。

发挥我们在收发器技术上的专业优势,以及在开发PCIe设计解决方案方面的专长。

,我们帮助客户显着降低了系统成本,而且不以牺牲性能为代价。

altera存储器的解决方案1

■ 全速率模式来减少延迟并使内核数据总线宽度最 小。

■ 简化 Arria V 和 Cyclone V 器件的总体储存器设 计,并且为每位设计师提供一种真实的即用 (out-of-the-box) 经验。

图 1-1 显示了 Stratix V 器件的软核储存器 IP 中的固定电路。

图 1-1. 软核储存器 IP 中的固定电路

Address/Command Path

Hard IP Soft IP

储存器解决方案

Altera FPGA 通过外部储存器 IP 实现最佳的储存器接口性能。此 IP 提供了以下组件:

■ 物理层接口 (PHY) - 它处理数据路径自身的时序。 ■ 存储控制器模块 - 它实现所有储存命令和地址。 ■ 多端口前端(MPFE)模块化- 它支持FPGA器件内部的多种操作来共享一个公共储存器

软核储存器 IP

硬核储存器 IP

■ 包含一个具有 UniPHY IP 的 DDR2、DDR3 或者 LPDDR2 SDRAM 高性能储存控制器。

■ 读和写的数据通路,是固定电路,来确保设计满 足最快速度的时序。数据路径包括 I/O、锁相环 (PLL)、延迟锁相环 (DLL) 以及读写 FIFO 缓冲 器。

f

要了解关于含有 UniPHY 的控制器或者 ALTMEMPHY IP 的详细信息,请参考外部储存器接 口手册 卷 3 中的 Functional Descriptions 部分。 要了解关于 ALTDQ_DQS 宏功能的详细信息,请参考 ALTDLL and ALTDQ_DQS Megafunctions User Guide。 要了解关于 ALTDQ_DQS2 宏功能的详细信息,请参考 ALTDQ_DQS2 Megafunction User Guide。

非易失性存储器的变革

当务之急在易失性存储器中,DRAM从EDO、SDRAM进化到了DDR SDRAM, DDR-II也即将来临,后面还有DDR-Ⅲ。

SRAM方面也迎来DDR、QDR时代,那么同为电子存储元件的非易失性存储器呢?在技术日新月异的今天,我们也不能忽视它的存在与进步……就目前而言,我们最为熟悉的非易失性存储器就是闪存了,不久前我撰文讲述了闪存在移动存储市场之外的另一个重要天地,但对其在技术上的进步着墨不多,今天我们就着重谈谈闪存近年的发展情况,从中大家能看到这里别有洞天,与我们熟悉的DRAM的发展大不一样。

由于掌上设备对闪存的要求远比移动存储高得多,因此它成为了闪存未来发展的主要动力,而由此带来的发展也会带动闪存的整体进步。

所以,通过闪存在掌上世界中的努力,我们就能体会到闪存的变革……一、高速度闪存在掌上设备中的作用与硬盘相同,但与硬盘相比,访问速度要快得多,并且还在进一步提速。

NAND型闪存的随机访问时间通常在25-50μs左右,而NOR型则是约90ns,不过两者作持续传输时的访问时间则是差不多的。

这就有点像RDRAM与DDR SDRAM的对比。

也因此,NOR型闪存可以达到所谓的XIP的要求(eXecute In Place,本地执行)。

由于90ns 已经与普通的DRAM的速度相差不多,所以,闪存中存放在代码不必先调入DRAM或SRAM中然后再由相关的处理单元调用(这是以往的作法),而是可直接在本地调用/执行,即具备了代码执行(Code Execute)能力。

所以,为什么说NOR是以代码存储为导向,原因也在于此。

在另一方面,为了应付网络数据的传输,目前的NOR闪存都在提倡的能力就是RWW/E ( Read-While-Write / Erase,写或擦除的同时读)。

而由于设计上的限制,NAND闪存是不可能具备这种能力的。

其在内部数据则进行所谓的分区(Partition)管理,一般是4Mb 或8Mb,在对一个分区进行读(执行代码)时,可对其他分区进行写或擦除操作,数据总线则在输入与输出之间根据需要调转。

cpld的若干问题

ALTERA公司CPLD的几个常见问题2007-10-12 16:001、不用的管脚如何处理?不用的全局信号和专用输入管脚,应接地,如:Global clk,Global clear ,Ded input. 其他不用的管脚一般悬空. Maxplus2 中的报告文件(*.rpt)或者QuartusII中的*.pin文件详细说明了管脚的接法. 如不用的管脚与外电路相连,为保证不影响外电路,应将此管脚定义为输入脚,但不接逻辑.2、EPM7000/3000的几个全局输入脚GCLK1,OE2(GCLK2),OE1,GLCRn都是干什么的?怎么在编程中使用?GCLK:全局时钟脚,这个脚的驱动能力最强,到所有逻辑单元的延时基本相同,所以如系统有外部时钟输入,建议定义此脚为时钟脚。

如想用其他脚为时钟输入,必须在在菜单:Assign>Global project logic synthesis>Automatic global>把GCLK前面的勾去掉。

这样任意一个I/O脚均可做时钟输入脚。

OE1:全局输出使能,如有三态输出,建议由此脚来控制(也可由内部逻辑产生输出使能信号),优点和用法同上。

OE2/GCLK2:全局输出使能/全局时钟脚,两者皆可。

GCLRn:全局清零,如有寄存器清零,建议由此脚来控制(也可由内部逻辑产生清零信号),优点和用法同上。

分配这些脚和分配普通I/O脚是一样的,先在Assign>device中选好器件型号,再在Assign>pin中填入你想分配的管脚号和类型,或直接在原理图中选中input 或output,点鼠标右键,选>assign pin,填入你想分配的管脚号,编译一遍即可。

但要注意菜单:Assign>Global project logic synthesis>Automatic global>中的设置。

其他芯片的全局脚的意义与此相同。

Altera帮助ZAPiT Games实现了在交互式控制台家庭游戏产品上的突破

Altera帮助ZAPiT Games实现了在交互式控制台家庭游戏

产品上的突破

佚名

【期刊名称】《《电子与电脑》》

【年(卷),期】2006(000)006

【摘要】Altera公司、ZAPiT Games公司及其研究开发合作伙伴Nytric宣布选用Altera的MAX Ⅱ CPLD来生产其第一款定位于家庭游戏的低价格交互式娱乐产品——Game Wave游戏控制台。

【总页数】1页(P150)

【正文语种】中文

【中图分类】TP391

【相关文献】

1.以英语为突破口,帮助差生实现突破 [J], 王静

2.Altera10代FPGA和SoC:架构和工艺上的双重突破 [J], 胥京宇

3.Altera宣布10代FPGA和SoC实现了突破性优势 [J],

4.以英语为突破口,帮助差生实现突破 [J], 王静

5.Altera10代FPGA和SoC实现突破性优势 [J],

因版权原因,仅展示原文概要,查看原文内容请购买。

反击Altera 赛灵思2014量产16纳米FPGA

反击Altera 赛灵思2014量产16纳米FPGA

赛灵思(Xilinx)将抢先在竞争对手Altera之前,发表16纳米鳍式场效电晶体(FinFET)现场可编程门阵列(FPGA)。

面对Altera采用英特尔(Intel)14纳米三门极电晶体(Tri-gate Transistor)制程,并将于2016年量产14纳米FPGA的攻势,赛灵思于日前发动反击,将携手台积电采用16纳米FinFET制程,抢先于2014年推出新一代FPGA。

赛灵思总裁暨执行长Moshe Gavrielov表示,16纳米先进制程中的三维(3D)电晶体将能够让客户拥有更高效能、更低耗电的产品。

赛灵思与台积电于16纳米制程的合作将延续双方过去在各项先进制程上所获得的成果。

值得一提的是,因着与赛灵思的合作,台积电也宣布将16纳米FinFET制程技术的生产时程提前,将于今年发布16纳米FinFET制程测试芯片,而首批FPGA产品将于2014年问世。

反观英特尔则预计在2014年将第二代三门极电晶体技术导入14纳米制程,并用以量产新中央处理器(CPU)。

据了解,赛灵思与台积电将共同推动一项名为FinFast的专案计划,以台积电16纳米FinFET制程技术打造高速、低耗电、高效能的FPGA元。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

*: Other Alternative solutions include glass or organic interposer, wafer-level fan-out, etc.

11

Design and Architectural Consideration System-level Partitioning and Feasibility

IC2

Chip-to-chip bonding Thorough silicon via (10-100 um pitch ) Thin wafer handling & processing (25-100um thick) C4 Interconnect (100-250 um pitch)

IC1 IC2

2

Agenda

Background Technology Trends 3D FPGA and Application Space Exploration Die Stacking Initiatives at Altera Summary

3

What’s Driving the Need for 3D? Enhanced Capabilities Bandwidth expansion

Technology*

Die Size Number of Interconnects Int. Power Aggregate BW/W Tech. Availability

Wire Bonding

Small A few 100’s 1X 1X In volume production

2.5D (Silicon Interposer)

− High-bandwidth chip-to-chip interface (wide IO interface) − Opticanal processing capabilities

− Memory enhancement

Product feature set expansion

300-500X

IC2

100-1KX

Chip-to-chip bonding Thorough silicon via (10-100 um pitch ) Thin wafer handling & processing (25-100um thick) C4 Interconnect (100-250 um pitch)

Back End Centric Front End Centric

3D Integration (HMC, HBM, etc.) Silicon Interposer (FPGA, mixed signal, - Face-to-Face Stacking SoC, Proc + Memory) (Sony PSP) - Wire bond stacking Glass interposer - Organic Interposer - Fine-Pitch Substrate - Wafer level FO - Multi-Chip Package Cost Driven Performance Driven

Application requirements and product realization

− − − −

Partitioning of functions in different die Chip-to-chip interface Manufacturing aspects (KGD, test) Thermal and thermo-mechanical co-design Relative dimensions of on-chip and chip-chip features, design rules and impact to floorplan Keep out zone for TSVs Design trade-off High-frequency signaling through TSV and u-bump Signal isolation between stacked components

FPGAs FPGAs Cost/Power Balance Mid-range FPGAs SoC & Transceivers SoC & Transceivers

FPGAs Optimized for High Bandwidth

PowerSoCs High-efficiency Power Management

Today’s Remote Radio Units

7

Energy Efficiency Normalized Energy Operation

Write 64b DFF 64b Integer Add Read 64b Register (64 x 32 bank) 8192-point FFT (per transform) Read 64b from DRAM

− Major semi companies across the supply chain have programs in place − High-volume application driver is needed for broader adoption

Next generation high-end FPGA applications require 2.5D/3D integrated memory

Recent Advances in Die Stacking and 3D FPGA

Arif Rahman, Program Director & Architect December 9th 2013

Summary

Early adoption of die stacking technology is underway in logic and logic-memory applications

− Derivative products

Energy efficiency Integration

− Fewer components

4

Enhanced Memory Capability

6

Integration and Form Factor Reduction

Yesterday’s Cell Towers

Implementation strategy

− − −

Other considerations

− −

Traditional system and board level design considerations are now part of 2.5D/3D integration

12

Design Consideration Manufacturing Aspects

16

Altera’s 3D Silicon Vision

Customer & application driven heterogeneous system integration in package

− Mix and match silicon IP − Integrated design flow − Integrated system test methodology

Testability and KGD

Design and technology interaction has to be considered much earlier in product planning process

14

Altera’s Product Portfolio

CPLDs Lowest Cost, Lowest Power

FPGA

HardCopy ASIC ASSP

+

Memory ASIC CPU SoC FPGA

Maximum system performance Minimum system power Smallest form factor Reduced system cost

Package Substrate

Solder Balls (0.5-1 mm pitch)

Enabling Technologies for 3D Integration

Relative Scale 1-10X

IC1

On-chip interconnect (<0.1- 0.8 um pitch) Micro-bump (30-55 um pitch)

Scalability of 2.5D/3D interconnect vs. traditional interconnects Thermal budget and heat removal

− Thermally aware design

Component reliability

− Effects on die size, structural attributes, and material properties − FPGA specific requirements

IC1 IC2

1K-2.5KX

Package Substrate

Solder Balls (0.5-1 mm pitch)

5K-10KX

Comparison of 3D Integration Schemes

Courtesy: Chipworks

Intel: 4Mb Stacked SRAM in 65nm

− Driven by application requirements − Addresses pin bandwidth limitations