《集成电路测试》 实验指导书

集成电路检验规范

管脚数20P生产厂家1National SemiconductorDAC0832LCN(美国国家半导体)管脚数 封装8P DIP-8(插件)芯片丝印 2管装(每管 50)TexasInstruments(TI) (德州仪器)管脚数 封装8 PDIP(插件)芯片丝印 3ONSemiconductor管装(每管 50) PB-FREE规格型号DAC0832LCN厂家图示 规格型号UC3844BN厂家图示 物料编码11XP01003生产厂家尺寸25*7.8mm备注尺寸9.5*6mm备注封装MDIP-20(插件)(ON) (安森美半导体)尺寸9*6mm备注物料编码11XP01001 LM358P厂家图示 11XP01002生产厂家规格型号物料编码芯片丝印 UC3844BN序号LM358P管脚数 封装16 PDIP(插件)芯片丝印4△UNITRODE物料编码 规格型号 管脚数 封装 尺寸11XP01005 TC4424CPA 8 PDIP(插件) 9.5*6mm生产厂家 厂家图示 芯片丝印 备注5MICROCHIPTC4424CPA物料编码11XP01006生产厂家6VISHAY (威士飞兆半 导体公司)规格型号MOC8112厂家图示管脚数 封装 尺寸6 PDIP(插件) 8.7*6.5备注MOC8112尺寸18 .5*6 .7mm备注 (被 TI 收购)管装(每管 25)规格型号UC3854BN厂家图示 物料编码11XP01004生产厂家芯片丝印 UC3854BN序号管脚数 封装8 PDIP(插件)芯片丝印7管装(每管 50)TexasInstruments(TI) (德州仪器)管脚数 封装14 PDIP(插件)芯片丝印 8管装(每管 25)TexasInstruments(TI) (德州仪器)管脚数 封装14 PDIP(插件)芯片丝印 9管装(每管 25)TexasInstruments(TI) (德州仪器)规格型号CD4069UBE厂家图示 物料编码11XP01007生产厂家物料编码11XP01009生产厂家规格型号LM339N厂家图示 规格型号LM393P厂家图示 尺寸19*6mm备注尺寸19*6mm备注尺寸9*6mm备注11XP01008生产厂家物料编码CD4069UBELM339NLM393P序号Texas Instruments(TI) (德州仪器)物料编码11XP01013生产厂家12RENESAS(瑞萨)规格型号HD74LS06P厂家图示SN74HC132N管脚数封装14 PDIP(插件)芯片丝印HD74LS06N(停用)信息传输不稳定HD74S06P管装(每管25)尺寸19*6mm备注被日立收购(HitachiSemiconductor)管脚数封装14 PDIP(插件)芯片丝印CD4093BE管脚数封装14 PDIP(插件)芯片丝印尺寸19*6mm备注管装(每管25)尺寸19*6mm备注物料编码11XP01010 生产厂家Texas Instruments(TI) (德州仪器)物料编码11XP01011 生产厂家规格型号CD4093BE 厂家图示规格型号SN74HC132N 厂家图示序号1011管脚数封装8 PDIP(插件)芯片丝印13X5045P 或者X504P Z品牌Intersil 可用(Z 表示无铅)物料编码规格型号管脚数封装尺寸11XP01016 SG3525AN 16 PDIP(插件) 19*6.5mm生产厂家厂家图示芯片丝印备注14ONSemiconductor(ON)(安森美半导体) 管装(每管25) SG3525ANG 即代表Pb Free ST3525AN 可代物料编码11XP01019生产厂家15TexasInstruments(TI)(德州仪器)规格型号LM324N厂家图示管脚数封装14 PDIP(插件)芯片丝印LM324N尺寸19*6.5mm备注管装(每管25) 规格型号X5045P-4.5A厂家图示物料编码11XP01014 生产厂家尺寸9*6mm 备注XICOR\Intersil 序号Texas Instruments(TI) (德州仪器)物料编码11XP01022生产厂家 18规格型号DS80C320MCG厂家图示管装(每管 25)CD74HC4052E管脚数40芯片丝印Maxim-Dallas Semiconductor (美信- 达拉斯)DS80C320MCG芯片丝印 无厂家图示 检验包装袋丝印 DS80C320MCG+ 即代表 Pb Free管脚数 封装16 PDIP(插件)芯片丝印CD74HC4051E管脚数 封装16 PDIP(插件)芯片丝印 尺寸19*6.5mm备注管装(每管 25)尺寸19*6.5mm备注规格型号CD74HC4051E厂家图示规格型号CD74HC4052E厂家图示 物料编码11XP01020生产厂家Texas Instruments(TI) (德州仪器)物料编码11XP01021生产厂家 序号1617封装40 Plastic DIP备注尺寸序号19 物料编码11XP01023生产厂家INTEL(英特尔)规格型号EE80C196KC20厂家图示管脚数68 PLCC 23.5*23.5mm芯片丝印备注EE80C196KC20 20-20MHZ物料编码规格型号管脚数封装尺寸11XP01024 W27C512-45Z 28 DIP(cpu 类) 37*13.8mm 生产厂家厂家图示芯片丝印备注20WINBOND(华邦)W27C512-45Z Pb Free物料编码11XP01025生产厂家21TexasInstruments(TI)(德州仪器)规格型号SN75176BP厂家图示管脚数封装8 PDIP(插件)芯片丝印SN75176BP尺寸9*6mm备注管装(每管50)封装尺寸序号 物料编码 规格型号 管脚数 封装 尺寸11XP01026 IMP690ACPA 8 PDIP(插件) 9.5*6.5mm生产厂家 厂家图示 芯片丝印 备注22已被香港日银 集团收购管脚数 封装 尺寸28 PDIP(插件) 36.5*13.5mm芯片丝印 备注ATMEL AT28C64B- 15PU (15PC ) PB-FREE物料编码 规格型号 管脚数 封装 尺寸11XP01028 AT28C256- 15PU 28 PDIP(插件) 36.5*13.5mm生产厂家 厂家图示 芯片丝印 备注24ATMEL (爱特梅尔公司)AT28C256- 15PU PB-FREE11XP01027生产厂家23AT28C64B- 15PU厂家图示 (爱特梅尔公司)IMP (安普)IMP690 ACPA规格型号物料编码管脚数 封装28 PDIP(插件)芯片丝印25WS62256LLPG-70或者WS62256LLP-70管脚数 封装20 PDIP(插件)芯片丝印管装(每管 20)TexasInstruments(TI) (德州仪器)管脚数 封装20 PDIP(插件)芯片丝印Lattice (莱迪思半导 体公司)GAL16V8D- 15LPN或者GAL16V8D- 15LPGAL16V8D- 15LPN 即为 PB FREE物料编码11XP01031生产厂家27规格型号GAL16V8D- 15LP厂家图示 11XP01030生产厂家26规格型号WS62256LLP-70厂家图示 规格型号SN74HC573AN厂家图示 70-70nsWS62256LLPG-70 即为 PB-FREE尺寸25.5*6.3mm备注尺寸36..5*12mm备注尺寸25.5*11mm备注物料编码11XP01029生产厂家Wing Shing (永胜实业(远东) )SN74HC573AN物料编码序号管脚数 封装20 PDIP(插件)芯片丝印28管装(每管 20)TexasInstruments(TI) (德州仪器)管脚数 封装16 PDIP(插件)芯片丝印 29MAXIMMZX232CPEMAX232CPE+表示 PB FREE物料编码11XP01034生产厂家30规格型号ULN2803APG厂家图示 管脚数 封装18 DIP(插件)芯片丝印 尺寸26*6.4mm备注TOSHIBA ULN2803APG规格型号SN74HC245N厂家图示 尺寸25.5*6.3mm备注尺寸19*7.5mm备注MAX232CPE厂家图示 11XP01033生产厂家11XP01032生产厂家规格型号物料编码物料编码SN74HC245N序号序号31物料编码11XP01035生产厂家VISHAY(威士飞兆半导体公司)规格型号DG508ACJ厂家图示管脚数封装16 PDIP(插件)芯片丝印DG508ACJ尺寸19*8mm备注可用intersil或者MAXIM物料编码11XP01036生产厂家32Maxim-DallasSemiconductor 管脚数封装24 EDIP (插件)芯片丝印“DS12C887+”表示PB FREE物料编码规格型号管脚数封装尺寸11XP01039 SG2525AN 16 PDIP(插件) 20*8.5mm生产厂家厂家图示芯片丝印备注33STMicroelectronics (意法半导体)SG2525AN尺寸32 .5*16.5mm备注DS12C887厂家图示规格型号DS12C887序号34物料编码11XP01040生产厂家ON Semiconductor(ON)(安森美半导体)规格型号UC2844BN厂家图示管脚数封装8 PDIP(插件)芯片丝印UC2844BN尺寸10*6mm备注管装(每管50)PB-FREE物料编码11XP01048生产厂家35Texas Instruments(TI)(德州仪器)规格型号SN74LS06N厂家图示管脚数封装14 PDIP(插件)芯片丝印SN74LS06N尺寸19*6.5mm备注管装(每管25)物料编码11XP01050生产厂家36规格型号AT89S52-24PU厂家图示管脚数封装40 PDIP(插件)芯片丝印尺寸51.8*13.5mm备注ATMEL(爱特梅尔公司)AT89S52-24PU PB-FREEATMEL(爱特梅尔公司)AT89C2051-24PU PB-FREE物料编码11XP01053生产厂家39ONSemiconductor(ON)(安森美半导体)规格型号UC3843BN厂家图示管脚数 封装8 PDIP(插件)芯片丝印UC3843BN尺寸9.5*6mm备注管装(每管 50)PB-FREE TL3843P(TI)可代用管脚数 封装14 PDIP(插件)芯片丝印37PHILIPS(NXPSemiconductors;Philips )物料编码 规格型号 管脚数 封装 尺寸11XP01052 AT89C2051-24PU 20 PDIP(插件) 25.5*8mm生产厂家 厂家图示 芯片丝印 备注38物料编码11XP01051生产厂家规格型号74HC04N厂家图示 尺寸19*6.3mm备注74HC04N序号PHILIPS (NXPSemiconductors;Philips )74HC00N物料编码 规格型号 管脚数 封装 尺寸11XP01056 SP485ES生产厂家 厂家图示 芯片丝印 备注SIPEX SP485ES被 EXAR 收购规格型号 管脚数 封装 尺寸ULN2803 18 PDIP(插件) 23*6.5mm厂家图示 芯片丝印 备注ULN2803规格型号 管脚数 封装 尺寸74HC00N 14 DIP厂家图示 芯片丝印 备注物料编码11XP01054生产厂家ONSemiconductor(ON)(安森美半导体)物料编码11XP01055生产厂家序号40序号物料编码11XP02001生产厂家规格型号L7805CV(集成稳压块)厂家图示管脚数封装3 TO-220芯片丝印尺寸10*1.25mm(顶部金属宽*厚)备注40STMicroelectronicsL7805 (意法半导体)物料编码11XP02002生产厂家41规格型号L7812CV厂家图示管脚数封装3 TO-220芯片丝印尺寸10*1.25mm(顶部金属宽*厚)备注STMicroelectronicsL7812 (意法半导体)物料编码11XP02003生产厂家42规格型号L7808CV厂家图示管脚数封装3 TO-220芯片丝印尺寸10*1.25mm(顶部金属宽*厚)备注STMicroelectronicsL7808 (意法半导体)序号43物料编码11XP02004生产厂家FARLCHILD(飞兆半导体公司)规格型号LM7912CT厂家图示管脚数封装3 TO-220芯片丝印LM7912CT 可代L7912CV (ST公司)尺寸10*1.25mm备注1 行:仙童标志 (FS or ) +Z+&3 (XYY) +KK2 行: LM7912C物料编码11XP03001生产厂家44TexasInstruments(TI)(德州仪器) 规格型号TL431ACLP厂家图示管脚数3 TO-92芯片丝印TL431AC袋装 1000 只45物料编码11XP04001生产厂家TexasInstruments(TI)(德州仪器)规格型号OP07CD(R)厂家图示管脚数8封装SOIC(贴片)芯片丝印OP70C尺寸备注管装(75)(R) 盘装2500封装尺寸备注11XP04002TL431IPK4SOT-89 贴片464748生产厂家Texas Instruments(TI) (德州仪器)物料编码11XP04003生产厂家Texas Instruments(TI) (德州仪器)物料编码11XP04004生产厂家Texas Instruments(TI) (德州仪器)厂家图示规格型号TL082ACD (管装) TL082CDR(盘装)厂家图示规格型号LM393DR厂家图示芯片丝印顶端标记为 3I管脚数8芯片丝印082AC管脚数8芯片丝印LM393备注袋装(1000 只)尺寸备注管装(75)尺寸备注盘装(2500 只)规格型号 物料编码 管脚数 尺寸序号封装 封装SOIC 贴片SOIC 贴片封装Texas Instruments(TI) (德州仪器)管装(每管 75)LM311物料编码11XP04007生产厂家51Texas Instruments(TI) (德州仪器)规格型号CD4013BM厂家图示管脚数14芯片丝印CD4013BM尺寸备注管装(每管 50)规格型号SN74HC4040DR厂家图示49盘装(2500 只)TexasInstruments(TI) (德州仪器)规格型号11XP04006生产厂家50物料编码11XP04005生产厂家LM311D厂家图示 SOIC 贴片SOIC 贴片物料编码芯片丝印 芯片丝印 管脚数管脚数HC4040序 号尺寸尺寸封装封装备注备注168封装SOIC 贴片Texas Instruments(TI) (德州仪器)管装(每管 75)UC3902D物料编码11XP04010生产厂家54Texas Instruments(TI) (德州仪器)规格型号LF353D厂家图示管脚数8芯片丝印LF353尺寸备注管装(每管 75)规格型号SN74HC393DR厂家图示52卷装(2500)TexasInstruments(TI) (德州仪器)规格型号11XP04009生产厂家53物料编码11XP04008生产厂家UC3902D厂家图示 SOIC 贴片SOIC 贴片物料编码芯片丝印 芯片丝印 管脚数管脚数序 号HC393尺寸尺寸封装封装备注备注148封装SOIC 贴片Texas Instruments(TI) (德州仪器)盘装(每盘 2500)LM358物料编码11XP04018生产厂家57规格型号DG508ADY厂家图示管脚数16封装Narrow Soic(窄体)芯片丝印 尺寸备注VISHAY (威世)根据芯片实际丝 印完善数据物料编码11XP04011生产厂家55管装(每管 50)TexasInstruments(TI) (德州仪器)物料编码11XP04015生产厂家56规格型号LM358DR厂家图示 规格型号LM324D厂家图示 SOIC 贴片SOIC 贴片芯片丝印 芯片丝印 管脚数管脚数序 号LM324封装尺寸封装尺寸备注备注148Texas Instruments(TI) (德州仪器)盘装(每盘 2500)LM339物料编码11XP0402260生产厂家Maxim-Dallas Semiconductor (美信-达拉斯)规格型号DS80C320-ECG厂家图示管脚数44 TQFP芯片丝印DALLASDS80C320规格型号AMS1117-3.3 (三端稳压器)厂家图示 58AMS1117 ADMOS3.3规格型号11XP04020生产厂家59物料编码11XP04019生产厂家 LM339DR厂家图示 SOT-223 (贴片)SOIC 贴片物料编码芯片丝印 芯片丝印管脚数管脚数序 号尺寸尺寸封装封装备注备注144备注尺寸封装序号61物料编码11XP04024生产厂家TexasInstruments(TI)(德州仪器)规格型号CD74HC4051M厂家图示管脚数16芯片丝印HC4051M尺寸备注管装(每管40)物料编码11XP04025生产厂家62TexasInstruments(TI)(德州仪器)规格型号SN74HC245DW厂家图示管脚数20芯片丝印HC245尺寸备注管装(每管25)63物料编码11XP04026生产厂家TexasInstruments(TI)(德州仪器)规格型号SN74LS06D厂家图示管脚数14芯片丝印LS06尺寸备注管装(每管50)封装SOIC贴片SOIC贴片SOIC贴片封装封装。

集成电路设计硬件描述语言实验指导书

集成电路设计硬件描述语言实验指导书实验一Verilog HDL程序结构与ModelSim、Quartus II软件的使用一、实验目的初步掌握Verilog HDL程序基本结构,编制简单的Verilog程序,掌握ModelSim、Quartus II软件的使用,掌握用Quartus II软件对Verilog程序进行编译仿真下载的基本方法。

二、实验内容1、编写Verilog程序描述一个电路,实现以下功能:该电路具有一个输入端口a,一个输出端口b,电路的作用是把输入到a的信号传送给b。

2、编写Verilog程序描述一个电路,实现以下功能:该电路具有两个输入端口a,b一个输出端口c,电路的作用是:c的输出是a 和b的“与”。

三、实验步骤1、编写Verilog程序,两个文件名分别为ex1.v和ex2.v,使用ModelSim的force命令进行仿真。

2、编写测试平台(testbench),对程序进行仿真。

3、启动Quartus II软件,建立工程(第一个工程名为ex1,顶层文件名为ex1.v;第二个工程名为ex2,顶层文件名为ex2.v)。

器件选择Cyclone系列中的EP1C3T144C8。

4、编写Verilog程序,存盘编译。

5、通过编译后,建立波形文件,设置仿真输入信号,存盘。

6、进行仿真,分析结果。

7、进行引脚锁定,重新编译。

对于ex1:a 对应引脚号1(PIO0)b 对应引脚号11(PIO8)对于ex2:a 对应引脚号1(PIO0)b 对应引脚号2(PIO1)c 对应引脚号11(PIO8)8、下载到EDA实验系统上的FPGA中,进行实际测试。

选用实验电路结构图NO.5。

四、实验报告要求实验目的,实验内容,设计的Verilog程序,实验结果,结果分析,心得与体会。

实验二异步清零十进制计数器的设计一、实验目的熟悉时序逻辑电路Verilog程序的设计,掌握计数器的设计方法。

二、实验内容编写Verilog程序描述一个电路,实现以下功能:具有2个输入端口clk和clr,clk输入时钟信号,clr起异步清零作用,‘1’有效,两个输出端口,c和q,q的位宽为4,输出计数值,从0到9,c的位宽为1,每当q为9时输出一个高电平脉冲。

集成电路分析与设计实验指导书

集成电路分析与设计实验指导书电子科学与技术实验中心2015.2本课程实验分为数字集成电路设计实验与全定制设计实验两部分。

实验1—4为基于Cadence的数字集成电路设计实验部分,主要内容为通过一个简单数字低通滤波器的设计、综合、仿真,让学生熟悉数字集成电路前段实际设计流程,以培养学生实际设计集成电路的能力。

具体为:实验1Matlab 实现数字低通滤波器算法设计。

实验2Linux 环境下基本操作。

实验 3 RTL Compiler 对数字低通滤波器电路的综合。

实验4NC 对数字低通滤波器电路的仿真。

其中,实验 1 主要目的是为了展示算法分析的方法和重要性。

使用Matlab 实现数字滤波器的算法设计和HDL 代码生成。

由于Matlab 工具可以在Windows 环境下工作,而其他集成电路EDA 工具均需要在linux 下工作,故建议本实验在课堂演示和讲述,学生课下练习。

实验2 的主要目的是学习linux 下的基本操作。

包括目录管理、文件管理、文件编辑以及文件压缩等在使用集成电路EDA 工具时所需要的操作。

本实验是实验3 和实验4 的基础,建议在实验室完成。

实验3 的主要目的是学习综合工具RTL Compiler 的使用。

其中包括RTL Compiler 命令行模式启动,设计读入,IP 库引入,设计约束设定,设计综合,综合结果报表及分析,综合结果输出等完整综合过程。

通过实验学习利用综合工具对设计(本实验中为数字滤波器)时序、面积、功耗的权衡及优化。

实验 4 的主要目的是学习仿真工具NClaunch 的使用。

主要完成目标滤波器功能仿真(RTL 级,即仿真HDL 代码)、综合后仿真(门级,即仿真门级网表,由sdf 文件反标电路延迟信息)。

通过实验学习数字电路的仿真方法。

实验5—6为基于Empyrean的全定制集成电路设计实验。

实验5为基础设计实验,以反相器设计为例学习由电路设计——仿真——版图设计——电路与版图一致性验证的整个全定制集成电路设计流程。

《集成电路设计实践》指导书(精)

《集成电路设计实践》指导书一、设计目的与要求1、全面掌握《半导体集成电路》、《集成电路工艺原理》与《集成电路设计技术》等课程的内容,加深对 CMOS 集成电路的设计及其制造工艺的理解,学会利用专业理论知识,实现半定制集成电路设计。

2、学会利用 Tanner 软件完成给定功能的集成电路原理设计与特性模拟,按版图规则完成版图设计, 并确定相应的制造工艺流程; 掌握版图布局规划、单元设计和布线规划的知识。

3、培养学生独立分析和设计的在综合实践能力。

4、培养学生的创新意识、严肃认真的治学态度和求真务实的工作作风。

二、设计任务要求根据给定集成电路的功能要求, 确定设计方法和电路基本单元类型, 完成逻辑电路原理设计,模拟分析电路特性,根据版图规则完成光刻版图设计,确定工艺流程,完成版图参数提取与 LVS 分析。

具体设计任务详见《集成电路设计实践任务书》。

三、基本格式规范要求1、设计报告可采用统一规范的稿纸书写,也可以用 16k 纸按照撰写规范单面打印,并装订成册(顶部装订。

内容包括:1 封面(包括题目、院系、专业班级、学生学号、学生姓名、指导教师姓名、职称、起止时间等2 报告正文(即设计过程说明书2、封面格式(第一页2、正文格式 *版图信息表格电路单元类型晶体管数目版图尺寸(不含 PAD版图尺寸(含 PAD设计结构 (层次化 or Flatten备注四、考核考核方法与评分标准按以下三个方面要求 (评分标准按 5分制或百分制记, 总分 5分制 : 1、设计报告(30分 ,分值分布参考如下:1 电路设计方案 (5分2 电路特性仿真及分析(5分3 版图布局及单元设计、工艺流程图(15分 ;4 总结、设计汇总(5分。

2、验收答辩、特性模拟结果、版图检查与回答问题(60分。

3、平时考勤和答疑时的提问情况(10分。

附录:一、0.35μm CMOS工艺版图设计规则说明Tanner 软件使用简介 Tanner 软件含 Ledit 版图编辑工具、Sedit 原理图编辑工具和 Tspice 电路特性模拟工具,LVS 版图原理图验证工具和版图参数提取工具都在 Ledit 文件夹中。

集成电路测试指南

第2章集成电路测试系统

2.1模拟IC测试系统 2.2数字IC测试系统 2.3混合IC测试系统 2.4 ST2500高性能数模混合测试系统 2.5 ST-IDE软件系统 2.6集成电路测试工程师实训平台

第4章数字电路功 能及交流参数测试

第3章直流及参数 测试

第5章混合信号测 试基础

第3章直流及参数测试

集成电路测试指南

读书笔记模板

01 思维导图

03 读书笔记 05 作者介绍

目录

02 内容摘要 04 目录分析 06 精彩摘录

思维导图

本书关键字分析思维导图

测试

电源

集成电路

第章

测试

混合

测试计划

指南

读者芯片 集成电路故障 Nhomakorabea测试

参数

实践

程序

程序调试

原理

第章

内容摘要

内容摘要

作者通过分享自身经验,为读者提供一本以工程实践为主的集成电路测试参考书。本书分为五篇共10章节来 介绍实际芯片验证及量产中半导体集成电路测试的概念和知识。第1篇由第1章和第2章组成,从测试流程和测试 相关设备开始,力图使读者对于集成电路测试有一个整体的概念。第二篇由第3~5章组成,主要讲解半导体集成 电路的自动测试原理。第三篇开始进入工程实践部分,本篇由第6章的集成运算放大器芯片和第7章的电源管理芯 片测试原理及实现方法等内容构成。通过本篇的学习,读者可以掌握一般模拟芯片的测试方法。第四篇为数字集 成电路的具体实践。我们选取了市场上应用需求量大的存储芯片(第8章)和微控制器芯片(第9章),为读者讲 述其测试项目和相关测试资源的使用方法。第五篇即第10章节,使读者了解混合信号测试的实现方式,为后续的 进阶打下一个坚实的基础。本书主要的受众是想要或即将成为集成电路测试工程师的读者,我们假设读者已经学 习过相应的基础课程,主要包括电路分析、模拟电子技术、数字电子技术、信号与系统、数字信号处理以及计算 机程序设计语言。通过本书的学习,读者将对半导体集成电路测试有一个总体的概念,并可以掌握能直接应用到 工作中的实战技术,并借此以“术”入“道”。对于已经从事半导体集成电路测试的工程技术人员、集成电路产 品工程师、设计工程师,本书也具有一定的参考意义。

《集成电路测试》 实验指导书

《集成电路测试》实验指导书南通大学集成电路重点实验室2009年6月实验一 测试图形生成及验证一、实验目的熟悉对被测电路给定故障生成测试图形的过程,掌握异或法和D 算法的具体运用。

二、实验原理参考教材P74 4.2.1 异或法, P82 4.4 D 算法三、实验内容abcd(1) 用异或法对5/0故障生成测试图形;(2) 用D 算法对6/0故障生成测试图形;(3) 对以上所产生的测试图形进行验证;(在Quartus II 中进行验证)四、实验报告写出测试图形生成的具体过程,给出整个实验的原理图和运行结果,分析实验结果的正确性。

f实验二伪随机序列生成一、实验目的了解随机测试和伪随机测试的基本概念;掌握LFSR的基本结构和M序列的基本特性。

二、实验原理基于故障的确定性测试方法是指用专门的算法对给定的故障生成测试图形,优点是生成的测试图形长度短,但生成过程比较复杂,测试施加比较困难。

由微处理器的测试软件算法或者专用的测试电路可容易生成随机的或伪随机的测试图形,并具有较高的故障覆盖率,因此在集成电路测试中得以广泛应用。

如果一个序列,一方面它是可以预先确定的,并且是可以重复地生产和复制的;一方面它又具有某种随机序列的随机特性(即统计特性),我们便称这种序列为伪随机序列。

因此可以说,伪随机序列是具有某种随机特性的确定的序列。

它们是由移位寄存器产生确定序列,然而他们却具有某种随机序列的随机特性。

因为同样具有随机特性,无法从一个已经产生的序列的特性中判断是真随机序列还是伪随机序列,只能根据序列的产生办法来判断。

伪随机序列系列具有良好的随机性和接近于白噪声的相关函数,并且有预先的可确定性和可重复性。

伪随机序列的电路为一个反馈移位寄存器,它可分为线性反馈移位寄存器(简称LFSR 计数器)和非线性反馈移位寄存器,由线性反馈移位寄存器(LFSR)产生的周期最长的二进制数字序列称为最大长度线性反馈移位寄存器序列,通常简称为M序列。

数字集成电路实验指导书

数字集成电路实验指导书2012年10月实验1 :创建工艺库和Virtuoso原理图编辑及仿真一、实验目的:1.创建一个工艺库。

2.掌握电原理图(schematic)设计输入方法。

3.熟悉仿真设置。

二、实验器材:PC机一台,CADENCE的IC5141软件一套。

三、实验步骤:(一):创建SMIC18工艺库过程1.在当前目录下创建一个目录,目录名为:12WDZXXX(学号后三位)2.将smicmmrf_1p6M_200706091815.tar拷贝到11WDXXX目录并解压。

解压命令:tar –xvf smicmmrf_1p6M_200706091815.tarls时会有一个目录smicmmrf_1p6M_200706091815根据该目录下的docs目录下,打开内容SMIC_0.18MMRF_Reference_Manual.pdf(转到第6页)看相当文档。

3.输入cd回到用户根目录,执行环境变量配置souece cad.cshrc4、cd 11WDXXX 进入11WDXXX目录5、输入icfb & 进入IC5141软件6、执行菜单:Tools/library manager在打开的窗口中: Edit/library path…在library中输入: smic18mmrf在path中输入:前面的路径/smicmmrf_1p6M_200706091815/smic18mmrf然后:file/save as …弹出对话框点击yes(二):Virtuoso原理图编辑和仿真1、打开Tools/library manager,查看里面是否有:analoglib、basic和smic18mmrf 等相应的库。

若没有这些库要进行另外处理。

2、建立自己的设计库Design Lib。

File->New->Library,弹出“New Library”对话框,在name输入自己定义的名字如:INVlib在Technology File中选:Attach to an existing techfile后点击OK,在弹出的对话框中Technology File选:smic18mmrf后点击OK。

专用集成电路试验指导书-32页word资料

实验一EDA软件实验实验性质:验证性实验级别:必做开课单位:信息与通信工程学院通信工程系学时:4学时一、实验目的:1、了解Xilinx ISE 6.2软件的功能。

2、掌握Xilinx ISE 6.2的VHDL输入方法。

3、掌握Xilinx ISE 6.2的原理图文件输入和元件库的调用方法。

4、掌握Xilinx ISE 6.2软件元件的生成方法和调用方法。

5、掌握Xilinx ISE 6.2编译、功能仿真和时序仿真。

6、掌握Xilinx ISE 6.2原理图设计、管脚分配、综合与实现、数据流下载方法。

7、了解所编电路器件资源的消耗情况。

二、实验器材:计算机、Quartus II软件或xilinx ISE三、实验内容:1、本实验以三线八线译码器(LS74138)为例,在Xilinx ISE 6.2软件平台上完成设计电路的VHDL文本输入、语法检查、编译、仿真、管脚分配和编程下载等操作。

下载芯片选择Xilinx公司的CoolRunner II系列XC2C256-7PQ208作为目标仿真芯片。

2、用1中所设计的的三线八线译码器(LS74138)生成一个LS74138元件,在Xilinx ISE 6.2软件原理图设计平台上完成LS74138元件的调用,用原理图的方法设计三线八线译码器(LS74138),实现编译,仿真,管脚分配和编程下载等操作。

四、实验步骤:4.1 Xilinx ISE 6.2环境1、三线八线译码器(74LS138)VHDL电路设计(1)、三线八线译码器(74LS138)的VHDL源程序的输入打开Xilinx ISE 6.2编程环境软件Project Navigator,执行“file”菜单中的【New Project】命令,为三线八线译码器(74LS138)建立设计项目。

项目名称【Project Name】为“Shiyan”,工程建立路径为“C:\Xilinx\bin\Shiyan”,其中“顶层模块类型(Top-Level Module Type)”为硬件描述语言(HDL),如图1所示。

集成电路设计实验

集成电路原理及应用班级:组员名单:学号:实验报告实验一芯片基本结构测试实验目的:1、了解芯片的基本结构2、掌握微分析设备显微镜的使用3、掌握集成电路反向设计中的图片提取实验内容:观察芯片的表面结构。

实验要求:(1)装好的芯片,并用在显微镜下观察记录芯片形貌。

(2)拼合拍摄下来的芯片表面图,还原原始芯片整体图。

实验原理:参照显微镜结构,利用CCD数字图像系统显示微观图形。

实验仪器:VM3000显微镜、IBM服务器计算机、晶圆样品、镊子等常用工具实验步骤:(1)连接好显微镜系统。

(2)打开电源启动计算机、显示仪和显微仪。

(3)放置好晶圆样品。

(4)显微镜粗调焦距。

(5)显微镜细调焦距。

(6)控制显微镜载物台,进行扫描观察芯片表面结构,并用计算机保存各块图像(7)打印所有图片并拼合。

实验报告:( 1 )实验目的;(2)实验内容;(3)所用仪器设备;(4)实验步骤;(5)图片拼合总体图;(6)小结。

(每个小组交一份报告)实验二 CMOS电路版图设计实验目的:1、学习CMOS电路的版图设计方法和设计流程。

2、学习版图设计软件L-edit使用。

3、理解CMOS电路中MOS器件的纵向结构和工艺流程。

4、掌握P阱CMOS工艺下的设计规则。

5、设计CMOS电路中异或门的逻辑结构和版图。

实验内容:1、设计CMOS电路中异或门的电路能够实现同或逻辑功能,2、设计的版图满足P阱CMOS电路的λ版图设计规则。

实验原理:1、异或门逻辑功能:Y=A⊕B2、P阱CMOS工艺下CMOS电路版图结构(反相器为例)3、P阱CMOS工艺的λ设计规则实验仪器与器件:微型计算机版图设计软件L-edit。

实验步骤:1、学习P阱CMOS工艺的λ设计规则2、在L-edit环境下设置图层结构、栅格尺寸和设计规则。

3、设计异或门逻辑结构和版图草图;4、设计编辑出异或门的版图文件。

思考题:(1)CMOS电路结构有何特点;(2)MOS管级联在版图中如何实现。

集成电路原理实验指导书

电子科技大学微电子与固体电子学院实验指导书课程名称:集成电路原理电子科技大学教务处制表实验一集成运算放大器参数的测试一、实验目的与意义运算放大器是一种直接耦合的高增益放大器,在外接不同反馈网络后,就组成不同的运算功能。

运算放大器除了可对输入信号进行加、减、乘、除、微分、等数学运算外,还在自动控制、测量技术、仪器仪表等各个领域得到广泛应用。

为了更好地使用运算放大器,必须对它的各种参数有一个较为全面的了解。

运算放大器结构十分复杂,参数很多,测试方法各异,需要分别进行测量。

本实验正是基于如上的技术应用背景和《集成电路原理与设计》课程设置及其特点而设置,目的在于:(1)了解集成电路测试的常用仪器仪表使用方法及注意事项。

(2)学习集成运算放大器主要参数的测试原理,掌握这些主要参数的测试方法。

通过该实验,使学生了解运算放大器测试结构和方法,加深感性认识,增强学生的实验与综合分析能力,进而为今后从事科研、开发工作打下良好基础。

二、实验原理运算放大器符号如图1所示,有两个输入端。

一个是反相输入端用“-”表示,另一个是同相输入端用“+”表示。

可以是单端输入,也可是双端输入。

若把输入信号接在“-”输入端,而“+”端接地,或通过电阻接地,则输出信号与输入信号反相,反之则同相。

若两个输入端同时输入信号电压为V- 和V+时,其差动输入信号为VID = V-- V+。

开环输出电压V=AVOVID。

AVO为开环电压放大倍数。

运算放大器在实际使用中,为了改善电路的性能,在输入端和输出端之间总是接有不同的反馈网络。

通常是接在输出端和反相输入端之间。

图1 运算放大器符号1、开环电压增益开环电压增益是指放大器在无反馈时的差模电压增益,其值为输出端电压变化量∆V 0和输入电压变化量o oV IV A V ∆=∆ (1) 由于A V 0很大,输入信号V I 很小,加之输入电压与输出电压之间有相位差,从而引人了较大的测试误差,实际测试中难以实现。

集成电路实验指导书

Henan University of Science and T echnology集成电路实验指导书河南科技大学电子信息工程学院集成电路实验指导书王丽萍、徐丹旸 主 编齐晶晶 副主编电工电子实验教学中心2007年9月前言随着微电子技术的不断发展和半导体工艺水平的不断提高,电子产品始终朝着速度快、体积小、重量轻的方向发展,近年来电子产品的更新换代速度更可谓日新月异。

为适应这种现状,进一步缩短电子产品的设计研发周期、降低开发成本,日趋进步和完善的EDA/ASIC 技术正在逐步取代传统的电子设计方法而成为现代电子设计技术的核心;而掌握与可编程逻辑器件、大规模集成电路(VLSI)、专用集成电路(ASIC)及电子设计自动化紧密结合的EDA/SOPC设计技术也已成为现代电子信息系统设计工程师的必备技能。

本实验指导书分为大规模集成电路实验、专用集成电路实验两大部分,围绕课程的主要内容使学生对当前集成电路设计技术以及EDA/SOPC技术有一个比较全面和准确的掌握和认识。

目录第一部分 大规模集成电路实验 (1)实验一EDA工具(Tanner Pro)的使用 (2)实验二四位加法器电路的设计与SPICE模拟 (14)实验三CMOS反相器的版图设计及其功能验证 (24)附录Tanner Pro简介 (39)第二部分 专用集成电路实验 (44)实验一 用OrCAD软件进行电路原理图的设计输入 (45)实验二 用PSpice软件进行电路模拟 (56)实验三 数字电路的FPGA实现 (66)第一部分大规模集成电路实验实验一EDA工具(Tanner Pro)的使用一、实验目的1、初步了解VLSI设计过程;2、了解VLSI设计软件系统Tanner Pro的运行;3、掌握系统基本操作方法。

二、实验环境本指导书中的所有实验均在Tanner Pro系统中完成。

三、预习要求初步了解VLSI设计过程,了解Tanner Pro系统所集成软件S-Edit,T-Spice,L-Edit与LVS的作用及相互关系。

集成电路测试指南目录

集成电路测试指南目录下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!集成电路测试指南目录一、引言1.1 集成电路测试的重要性1.2 集成电路测试的基本概念1.3 测试指南的目的和适用范围二、集成电路测试基础2.1 集成电路的分类2.2 集成电路的工作原理2.3 集成电路的主要性能指标三、集成电路测试设备与工具3.1 测试平台介绍3.2 逻辑分析仪3.3 示波器3.4 数字信号发生器3.5 集成电路测试夹具四、集成电路功能测试4.1 功能测试概述4.2 功能测试步骤4.3 常见功能测试方法4.4 功能故障诊断五、集成电路参数测试5.1 参数测试的重要性5.2 主要参数测试项目5.3 参数测试的实施5.4 参数异常的分析与处理六、集成电路可靠性测试6.1 可靠性测试的目标6.2 温度循环测试6.3 老化测试6.4 冲击和振动测试6.5 快速功率周期测试七、集成电路故障定位与修复7.1 故障模式和效应分析7.2 故障定位技术7.3 非破坏性测试方法7.4 破坏性物理分析7.5 故障修复策略八、集成电路测试优化8.1 测试时间优化8.2 测试成本控制8.3 测试覆盖率提升8.4 自动化测试系统九、集成电路测试标准与规范9.1 国际集成电路测试标准9.2 行业测试规范9.3 测试报告的编写要求十、结论与展望10.1 当前集成电路测试面临的挑战10.2 未来发展趋势10.3 对读者的建议这只是一个基本的集成电路测试指南的大纲,具体内容可能需要根据实际的集成电路类型、应用领域以及读者群体进行调整和深化。

集成电路设计课程设计实验指导书3

《集成电路设计》课程设计实验指导书西安邮电大学微电子学系目录目录 (2)1 设计流程及主要文档要求 (3)1.1 课程设计采用设计流程 (3)1.1.1 功能定义 (3)1.1.2 系统设计 (3)1.3 电路设计 (4)1.4 功能仿真验证 (4)1.5 综合 (4)1.6 静态时序分析 (4)1.7 时序仿真 (4)1.2 主要文档要求 (4)1.2.1 技术规范 (4)1.2.2 总体设计方案 (5)1.2.3 验证方案 (5)1.2.4 综合报告 (5)1.2.5 功能仿真报告、时序仿真报告 (5)1.2.6 静态时序分析报告 (6)2 可选题目 (7)1 设计流程及主要文档要求1.1 课程设计采用设计流程本课程设计采用图1.1所示设计流程。

图1.1 集成电路设计流程1.1.1 功能定义根据题目要求定义所设计电路的功能、接口和指标。

编写技术规范。

1.1.2 系统设计根据技术规范进行系统划分。

编写总体设计方案根据技术规范规划整体验证并设计验证激励的Verilog HDL代码。

验证方案。

1.3 电路设计根据总体设计方案设计完成电路设计。

用Verilog HDL描述设计结果。

1.4 功能仿真验证根据验证方案对完成的电路设计进行功能仿真—(验证)。

编写功能仿真报告。

1.5 综合用综合工具对电路设计结果进行综合。

提交综合报告。

1.6 静态时序分析对综合后的网表和延时文件,使用静态时序分析工具对电路进行静态时序分析。

提交静态时序分析报告。

1.7 时序仿真对综合后的网表和延时文件,根据验证方案对电路进行时序仿真。

提交时序仿真报告。

1.2 主要文档要求1.2.1 技术规范技术规范描述电路的功能、性能指标。

至少包括以下内容:1 概述描述文档目标;简单描述电路主要功能。

2 接口定义详细描述电路的引脚,包括名称、宽度、方向、有效电平(边沿)等3 功能说明逐条详细说明电路的功能。

4 关键接口时序描述电路接口关键时序。

实验指导书

《集成电路原理》课程实验指导书目录目录 (1)实验一集成电路基本单元反相器的仿真 (2)一、目的与要求 (2)二、实验内容 (2)三、实验步骤 (2)实验二基本集成电路的功能仿真 (4)一、目的与要求 (4)二、实验内容 (4)三、实验步骤 (5)实验三基本集成电路的时序和驱动特性仿真 (6)一、目的与要求 (6)二、实验内容 (7)三、实验步骤 (7)实验四基本集成电路的参数确定和温度、功耗特性仿真 (10)一、目的与要求 (10)二、实验内容 (10)三、实验步骤 (10)实验一集成电路基本单元反相器的仿真一、目的与要求1.学习设置和运行Hspice。

2.学习使用Hspice进行功能仿真。

3.熟悉Hspice软件,使用MetaWaves 浏览波形。

二、实验内容本实验通过设计一个四个反相器构成的输出电路,学习设置和运行Hspice,学习使用Hspice进行功能仿真,熟悉Hspice软件,使用MetaWaves 浏览波形。

三、实验步骤写出反相器构成的输出电路Hspice仿真的详细步骤1.选用1.2um CMOS工艺level II模型(Models.sp)MODEL NMOS NMOS LEVEL=2 LD=0.15U TOX=200.0E-10 VTO=0.74 KP=8.0E-05+NSUB=5.37E+15 GAMMA=0.54 PHI=0.6 U0=656 UEXP=0.157 UCRIT=31444+DELTA=2.34 VMAX=55261 XJ=0.25U LAMBDA=0.037 NFS=1E+12 NEFF=1.001+NSS=1E+11 TPG=1.0 RSH=70.00 PB=0.58+CGDO=4.3E-10 CGSO=4.3E-10 CJ=0.0003 MJ=0.66 CJSW=8.0E-10 MJSW=0.24 .MODEL PMOS PMOS LEVEL=2 LD=0.15U TOX=200.0E-10 VTO=-0.74 KP=2.70E-05 +NSUB=4.33E+15 GAMMA=0.58 PHI=0.6 U0=262 UEXP=0.324 UCRIT=65720+DELTA=1.79 VMAX=25694 XJ=0.25U LAMBDA=0.061 NFS=1E+12 NEFF=1.001+NSS=1E+11 TPG=-1.0 RSH=121.00 PB=0.64+CGDO=4.3E-10 CGSO=4.3E-10 CJ=0.0005 MJ=0.51 CJSW=1.35E-10 MJSW=0.242.设计基本反相器单元根据模型参数、设计要求设定管子尺寸写出反相器网单。

集成电路原理与设计实验指导书

《集成电路原理与设计》实验指导书河北工业大学信息工程学院集成电路原理与设计课程组0000 年00月随着微电子的迅速发展,集成电路作为微电子的核心已经发展到65nm技术,单个芯片上能够集成多达七十亿个元器件,半导体技术正在进入将整个系统整合在单一晶片上的时代。

目前各种电子产品的极大丰富使得集成电路的设计和制造成为研究的重点,因此了解集成电路的原理与设计也就成为大学生学习的关键。

集成电路原理与设计课程主要介绍双极性集成电路(包括TTL电路、ECL电路、I2L电路)和MOS集成电路(包括NMOS、PMOS、CMOS)的组成特点、工作原理以及逻辑扩展方面的知识,借助计算机辅助设计软件,并遵循各项流程规则及参数规定进行仿真练习。

Tanner Tools Pro提供完整的集成电路设计环境,可在PC 机上运行,能够帮助学生进入VLSI设计领域。

它从电路图设计、电路分析与仿真到电路布局环境一应俱全。

学生通过仿真实验能够进一步深化对集成电路原理、半导体工艺等方面知识的理解和掌握,将电子科学与技术专业的基础知识融会贯通。

实验一使用S—Edit设计简单逻辑电路----------------------------------------------------------------4 实验二简单逻辑电路的瞬时分析和直流分析----------------------------------------------------------10 实验三全加器电路设计与瞬时分析----------------------------------------------------------------------23 实验四四位加法器电路设计与仿真----------------------------------------------------------------------28 实验五使用L—Edit画PMOS布局图-------------------------------------------------------------------33 实验六使用L—Edit画反相器布局图------------------------------------------------------------------43 实验七四位加法器标准原件自动配置与绕线--------------------------------------------------------55实验一使用S—Edit设计简单逻辑电路(2学时)一、实验目的1.熟悉S—Edit电路图编辑环境2.熟悉S—Edit中模块的编辑和引用3.掌握S—Edit菜单中各项的意义和使用方法4.掌握反相器和与非门两种电路图的编辑方法二、实验内容实验内容包括两个部分,首先利用S—Edit编辑反相器和与非门。

集成运算电路实验指导书

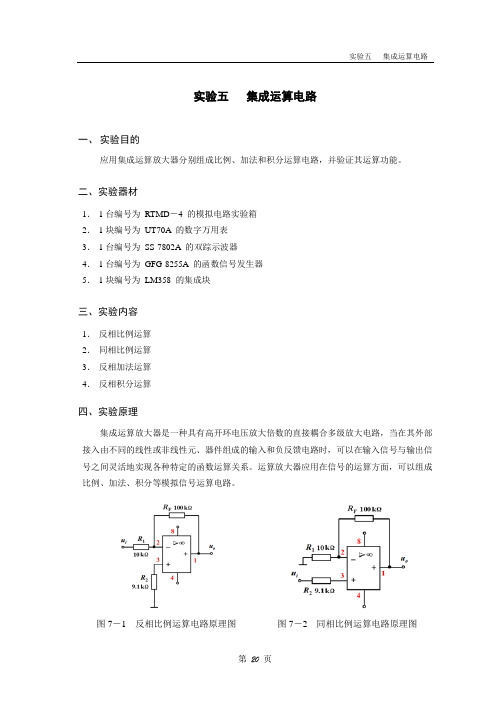

实验五集成运算电路一、实验目的应用集成运算放大器分别组成比例、加法和积分运算电路,并验证其运算功能。

二、实验器材1.1台编号为RTMD-4 的模拟电路实验箱2.1块编号为UT70A 的数字万用表3.1台编号为SS-7802A 的双踪示波器4.1台编号为GFG-8255A 的函数信号发生器5.1块编号为LM358 的集成块三、实验内容1.反相比例运算2.同相比例运算3.反相加法运算4.反相积分运算四、实验原理集成运算放大器是一种具有高开环电压放大倍数的直接耦合多级放大电路,当在其外部接入由不同的线性或非线性元、器件组成的输入和负反馈电路时,可以在输入信号与输出信号之间灵活地实现各种特定的函数运算关系。

运算放大器应用在信号的运算方面,可以组成比例、加法、积分等模拟信号运算电路。

图7-1反相比例运算电路原理图图7-2同相比例运算电路原理图图7-3 反相加法运算电路原理图 图7-4 反相积分运算电路原理图五、实验过程1. 实验准备(a) 熟悉编号为LM358 的集成块: LM358内部含有两个运算放大器,其管脚定义如图7-5所示, 第8号管脚是正电源管脚,应连接 +10V 电源;第4 号管脚是负电源管脚,应连接 -10V 电源。

(b) 为了方便电路连线,对原理图中每个信号均进行管脚编号。

例如:在图7-1中,输出信号U o 的编号为1,表示 U o 对应集成块LM358的第1号管脚。

(c) 打开模拟电路实验箱的盖子,接好实验箱的电源线,断开电源开关,在实验箱上放好集成运算电路扩展面板,在扩展面板上配好1片LM358 。

+U CCU OU +–U –图7-5 双运算放大器 LM358 的管脚图2. 反相比例运算的实验过程(1)按照图7-1连线(a) 在图7—1中,用到了1个运算放大器,需要1片编号为LM358的集成块,用导线将LM358的第8 管脚和+10 V 电源相连,第4 管脚和-10 V 电源相连,再用导线将实验箱的地线与实验电路板的地线相连,做到共地连接。

数字集成电路实验指导书

《数字集成电路》实验指导书何爱香信息与电子工程学院2013年1月目录实验1译码器 (3)实验2组合逻辑电路…………………………………………………………6实验3半加器…………………………………………………………………8实验4全加器…………………………………………………………………9实验5三进制计数器 (11)实验6 555多谐振荡器 (13)实验7电压比较器 (15)实验8Pspice最坏情况分析 (16)实验1 译码器一、 实验目的1. 理解译码器逻辑功能。

2. 掌握译码器电路设计方法。

二、 实验内容译码器74155的芯片如下图所示,76549101112逻辑函数式:B A Y +=三、 实验步骤(1) 在pspice 中,启动Place/Part 命令,出现下图所示的选择框,输入74155,点击OK 。

(2)控制端1C设置为高电平,使能端G在pspice中,高低电平要用专门的符号来设置,启动Place/Ground 命令,出现下图所示的选择框,在SOURE库中取“$D_HI”符号,即为接入高电平,取“$D_LO”符号,接到电路的输入端,即为接入低电平。

(2)设置输入信号AB启动Place/Part命令,出现下图所示的选择框,输入DigClock。

通过设置时钟信号源参数调整方波的周期可占空比。

设置输入信号A的ONTIME和OFFTIME为0.5ms。

设置输入信号B的ONTIME和OFFTIME为1ms时钟信号源有5个周期参数要设置:在一个周期内,低电平状态的持续时间:在一个周期内,低电平状态的持续时间。

ONTIME: 在一个周期内,高电平状态的持续时间OFFTIME: 在一个周期内,低电平状态的持续时间DELAY:延时STARTVAL:时钟信号的初值,在时间延时范围内,信号值由初值决定。

OPPVAL:时钟高电平状态在设置时钟信号时,一般只需要设置OFFTIME和ONTIME方法:双击ONTIME出现下图对话框,设置为0.5ms.同理,设置OFFTIME为0.5ms。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《集成电路测试》实验指导书

南通大学集成电路重点实验室

2009年6月

实验一 测试图形生成及验证

一、实验目的

熟悉对被测电路给定故障生成测试图形的过程,掌握异或法和D 算法的具体运用。

二、实验原理

参考教材P74 4.2.1 异或法, P82 4.4 D 算法

三、实验内容

a

b

c

d

(1) 用异或法对5/0故障生成测试图形;

(2) 用D 算法对6/0故障生成测试图形;

(3) 对以上所产生的测试图形进行验证;(在Quartus II 中进行验证)

四、实验报告

写出测试图形生成的具体过程,给出整个实验的原理图和运行结果,分析实验结果的正确性。

f

实验二伪随机序列生成

一、实验目的

了解随机测试和伪随机测试的基本概念;掌握LFSR的基本结构和M序列的基本特性。

二、实验原理

基于故障的确定性测试方法是指用专门的算法对给定的故障生成测试图形,优点是生成的测试图形长度短,但生成过程比较复杂,测试施加比较困难。

由微处理器的测试软件算法或者专用的测试电路可容易生成随机的或伪随机的测试图形,并具有较高的故障覆盖率,因此在集成电路测试中得以广泛应用。

如果一个序列,一方面它是可以预先确定的,并且是可以重复地生产和复制的;一方面它又具有某种随机序列的随机特性(即统计特性),我们便称这种序列为伪随机序列。

因此可以说,伪随机序列是具有某种随机特性的确定的序列。

它们是由移位寄存器产生确定序列,然而他们却具有某种随机序列的随机特性。

因为同样具有随机特性,无法从一个已经产生的序列的特性中判断是真随机序列还是伪随机序列,只能根据序列的产生办法来判断。

伪随机序列系列具有良好的随机性和接近于白噪声的相关函数,并且有预先的可确定性和可重复性。

伪随机序列的电路为一个反馈移位寄存器,它可分为线性反馈移位寄存器(简称LFSR 计数器)和非线性反馈移位寄存器,由线性反馈移位寄存器(LFSR)产生的周期最长的二进制数字序列称为最大长度线性反馈移位寄存器序列,通常简称为M序列。

关于LFSR构造及M序列的相关特性,请参阅教材p205-212的相关内容。

三、实验内容

下图为4位完全LFSR结构图,试分析其自动生成的序列。

(在Quartus II中运行、分析)

四、实验报告

对伪随机序列,LFSR,M序列等相关概念进行综述。

对上图进行分析。

实验三组合电路测试生成与故障模拟

一、实验目的

了解FAN算法的基本概念;掌握组合电路标准被测电路的基本结构和测试工具使用方法。

二、实验原理

基于故障的确定性测试方法(A TPG)是指用专门的算法对给定的故障生成测试图形,FAN算法是一种比较优秀的的测试图形生成算法,但生成过程比较复杂,由其生成的测试图形具有有较高的故障覆盖率,因此在集成电路测试中得以广泛应用。

FAN算法的基本思路见书本,其算法采用了四个独特的概念来加速测试生成的过程。

故障模拟采用故障模拟器,对故障出现的设计模型施加测试集,进行模拟,然后分析有故障和无故障设计模型的响应,达到以下目的:

测试给定的故障出现的条件;

测试图形生成;

衡量给定测试图形的效率;

生成故障表。

主要的故障模拟方法包括有串行、并行、演绎以及并发性故障模拟四个,其基本模拟方法及原理见书本。

三、实验内容

掌握组合电路故障测试图形生成工具atalanta和组合电路故障模拟工具FSIM的使用方法,能够基于ISCAS85标准电路,进行故障测试图形生成,同时将生成的故障测试图形文件导入故障模拟器,进行故障模拟分析,掌握ISCAS85标准电路结构

四、实验报告

简述FAN算法的主要思想,画出ISCAS85标准电路c17.bench电路结构,并对atalanta 对c17.bench所生成的报告指标进行简要阐述。

实验四时序电路故障模拟

一、实验目的

了解时序电路的基本概念;掌握时序电路故障仿真工具hope以及时序电路ISCA’89。

二、实验原理

时序电路由存储元件(如触发器)和组合逻辑电路组成,电路的输出不仅与电路的当前输入有关,还与电路的历史状态有关。

时序电路测试的可以归纳为4点:大多数电路是时序电路。

时序电路输出不仅与电路当前输入有关,还与内部状态有关。

时序电路的初始化问题。

时序是导致时序电路测试生成困难的一个因素。

故障模拟采用故障模拟器,对故障出现的设计模型施加测试集,进行模拟,然后分析有故障和无故障设计模型的响应,达到以下目的:

测试给定的故障出现的条件;

测试图形生成;

衡量给定测试图形的效率;

生成故障表。

主要的故障模拟方法包括有串行、并行、演绎以及并发性故障模拟四个,其基本模拟方法及原理见书本。

三、实验内容

掌握时序电路故障模拟工具hope的使用方法,能够基于ISCAS89标准电路,将已有的故障测试图形文件导入故障模拟器,进行故障模拟分析,掌握ISCAS89标准电路结构,在quartusii中画出电路s27.bench,并按照测试激励进行仿真。

四、实验报告

简述时序电路基本概念,画出ISCAS89标准电路s27.bench电路结构,并对hope基于s27.bench所生成的报告指标进行简要阐述。