实验报告一多路选择器

实验七数据选择器及应用

数据选择器实验报告一、实验目的1. 熟悉集成据选择器的逻辑功能和扩展。

2. 学习利用数据选择器产生逻辑函数。

二、实验原理数据选择器又称多路选择器、多路开关。

它是一个多输入、单输出电路。

数据选择器在地址码(或叫选择控制)电平的控制下,从几个数据输入中选择一个,并将其送到输出端。

常见的数据选择器有2选1、4选1、8选1和16选1等数据选择器。

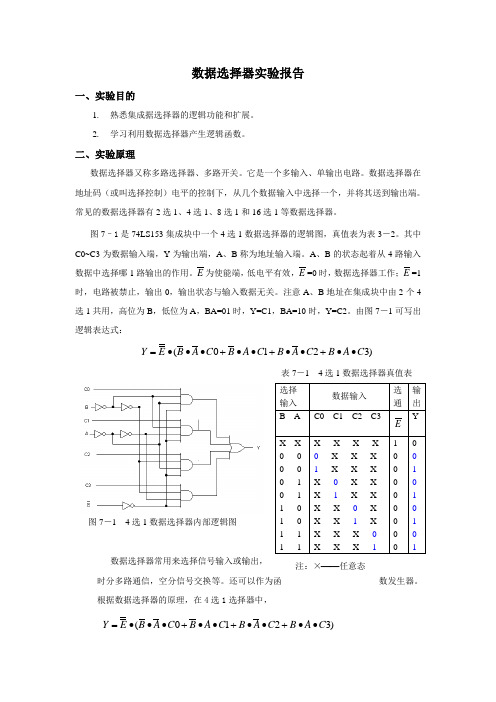

图7–1是74LS153集成块中一个4选1数据选择器的逻辑图,真值表为表3-2。

其中C0~C3为数据输入端,Y 为输出端,A 、B 称为地址输入端。

A 、B 的状态起着从4路输入数据中选择哪1路输出的作用。

E 为使能端,低电平有效,E =0时,数据选择器工作;E =1时,电路被禁止,输出0,输出状态与输入数据无关。

注意A 、B 地址在集成块中由2个4选1共用,高位为B ,低位为A ,BA=01时,Y=C1,BA=10时,Y=C2。

由图7-1可写出逻辑表达式:)3210(C A B C A B C A B C A B E Y ••+••+••+•••=表7-1 4选1数据选择器真值表图7-1 4选1数据选择器内部逻辑图数据选择器常用来选择信号输入或输出,时分多路通信,空分信号交换等。

还可以作为函数发生器。

根据数据选择器的原理,在4选1选择器中,)3210(C A B C A B C A B C A B E Y ••+••+••+•••=选择输入 数据输入 选通 输出B A C0 C1 C2 C3 EY X X 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1X X X X 0 X X X 1 X X X X 0 X X X 1 X X X X 0 X X X 1 X X X X 0 X X X 11 0 0 0 0 0 0 0 00 0 1 0 1 0 1 0 1注:×−−任意态我们可以利用它实现逻辑函数:如A B A B A B A B A B A B Y •+•=••+••+••+•••=)1001(0 通过在E 、C0~C3处输入相应的值,A 、B 和Y 之间构成了同或门逻辑。

数字逻辑实验报告

数字逻辑实验报告数字逻辑实验报告引言数字逻辑是计算机科学中的重要基础知识,通过对数字信号的处理和转换,实现了计算机的高效运算和各种复杂功能。

本实验旨在通过实际操作,加深对数字逻辑电路的理解和应用。

实验一:二进制加法器设计与实现在这个实验中,我们需要设计一个二进制加法器,实现两个二进制数的加法运算。

通过对二进制数的逐位相加,我们可以得到正确的结果。

首先,我们需要将两个二进制数输入到加法器中,然后通过逻辑门的组合,实现逐位相加的操作。

最后,将得到的结果输出。

实验二:数字比较器的应用在这个实验中,我们将学习数字比较器的应用。

数字比较器可以比较两个数字的大小,并输出比较结果。

通过使用数字比较器,我们可以实现各种判断和选择的功能。

比如,在一个电子秤中,通过将待测物品的重量与设定的标准重量进行比较,可以判断物品是否符合要求。

实验三:多路选择器的设计与实现在这个实验中,我们需要设计一个多路选择器,实现多个输入信号中的一路信号的选择输出。

通过使用多路选择器,我们可以实现多种条件下的信号选择,从而实现复杂的逻辑控制。

比如,在一个多功能遥控器中,通过选择不同的按钮,可以控制不同的家电设备。

实验四:时序电路的设计与实现在这个实验中,我们将学习时序电路的设计与实现。

时序电路是数字逻辑电路中的一种重要类型,通过控制时钟信号的输入和输出,实现对数据的存储和处理。

比如,在计数器中,通过时序电路的设计,可以实现对数字的逐位计数和显示。

实验五:状态机的设计与实现在这个实验中,我们将学习状态机的设计与实现。

状态机是一种特殊的时序电路,通过对输入信号和当前状态的判断,实现对输出信号和下一个状态的控制。

状态机广泛应用于各种自动控制系统中,比如电梯控制系统、交通信号灯控制系统等。

实验六:逻辑门电路的优化与设计在这个实验中,我们将学习逻辑门电路的优化与设计。

通过对逻辑门电路的布局和连接方式进行优化,可以减少电路的复杂性和功耗,提高电路的性能和可靠性。

北邮 ASIC实验报告

ASIC设计实验报告学院:电子工程学院班级:2011211204 指导老师:韩可2014年6月实验一:多路选择器的设计一.实验目的:1.掌握门级电路与行为级电路设计的区别;2.掌握逻辑电路的设计方法;3.熟悉测试程序的编写。

4.注意代码规范性要求。

二.实验内容:1.设计一个有两位选择信号的四选一多路选择器,可以根据控制信号从两位或多个输入源中选择一个予以输出。

I0I1 outI2 I3S1 s02.用基本逻辑门来实现多路选择器,即门级语言进行描述。

参考门级电路如下。

四选一 多路选择器3.用行为级语言进行描述,通过case语句重新设计仿真。

4.编写多路选择器的测试激励模块,并通过Synopsys工具进行仿真。

三.实验代码:mux1.vmodule mux1(s,i0,i1,i2,i3,out);input [1:0] s;input i0,i1,i2,i3;output out;wire s1,s0,s1_n,s2_n;wire y0,y1,y2,y3;assign s1 = s[1];assign s0 = s[0];assign s1_n = ~s[1];assign s0_n = ~s[0];assign y0 = i0 & s1_n & s0_n;assign y1 = i1 & s1_n & s0;assign y2 = i2 & s1 & s0_n;assign y3 = i3 & s1 & s0;assign out = y0 | y1 | y2 | y3;endmodulemux1_test.v`timescale 1ns/1usmodule mux1_test();reg [1:0] s;reg i0,i1,i2,i3;wire out;mux1(.s(s),.i0(i0),.i1(i1),.i2(i2),.i3(i3),.out(out));initialbegini2 = 1'b0;forever #2 i2 = ~i2;endinitialbegini3 = 1'b0;forever #4 i3 = ~ i3;endinitialbegin$dumpvars(2,mux1_test);i0 = 1'b0;i1 = 1'b1;s = 2'b00;#20 s = 2'b01;#20 s = 2'b10;#20 s = 2'b11;#20 s = 2'b00;#20 s = 2'b01;#20 s = 2'b10;#20 s = 2'b11;#20 $finish;endEndmodulemux2.vmodule mux2(s,i0,i1,i2,i3,out);input [1:0] s;input i0,i1,i2,i3;output out;reg out;always @(s,i0,i1,i2,i3)begincase (s)default : out = 1'bx;2'b00 : out = i0;2'b01 : out = i1;2'b10 : out = i2;2'b11 : out = i3;endcaseendEndmodulemux2_test.v`timescale 1us/1usmodule mux2_test();reg [1:0] s;reg i0,i1,i2,i3;wire out;mux2(.s(s),.i0(i0),.i1(i1),.i2(i2),.i3(i3),.out(out));initialbegini2 = 1'b0;forever #2 i2 = ~i2;endinitialbegini3 = 1'b0;forever #4 i3 = ~i3;endinitialbegin$dumpvars(2,mux2_test);i0 = 1'b0;i1 = 1'b1;s = 2'b00;#20 s = 2'b01;#20 s = 2'b10;#20 s = 2'b11;#20 s = 2'b00;#20 s = 2'b01;#20 s = 2'b10;#20 s = 2'b11;#20 $finish;endendmodule四.仿真波形:门级电路波形行为级电路波形不同点:两者都能正确的反映输出与输入的关系且波形一致,但两者的原理是不同的。

东南大学数字系统实验实验一

数字系统实验报告实验一

一、实验目的

熟悉quartus环境下的vhdl电路设计,学习简单组合电路设计。

二、实验内容

设计双二选一多路选择器:

1.设计二选一多路选择器

2.将两个二选一多路选择器连接,完成三选一功能

3.仿真验证及下载测试

三、实验过程

1.设计二选一多路选择器。

在quartus中新建工程,并创建vhdl文件,编写代码如下:

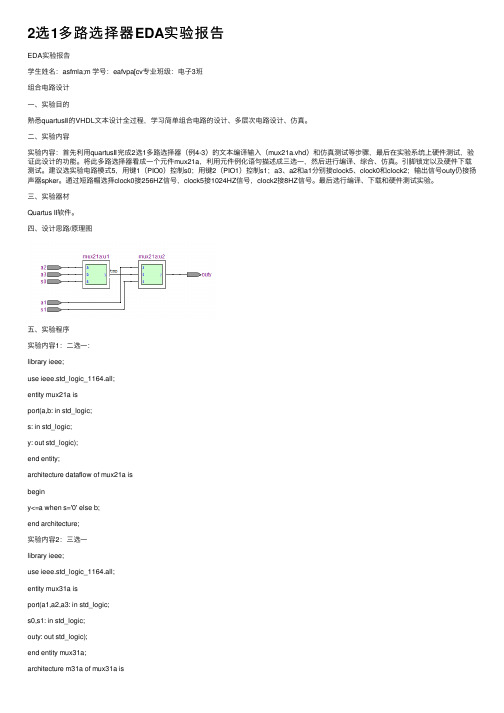

2.将两个二选一选择器连接构成双二选一多路选择器,连接方式如下:

根据连接方式,可以得到输入输出真值表:

3.引脚绑定

按下表进行引脚绑定

四、实验结果及结论

1.时序仿真结果

对双四选一多路选择器进行时序仿真,结果如下:

仿真遍历了所有输入端口的取值,在S1,S2分别取00,01,10,11时,输出分别对应A,B,C,B的值,对比真值表,可以发现仿真结果正确。

2.下载验证

按引脚图绑定端口,其中S1,S2分别由两个键控制,输出口A,B,C连接的是电路板的音调控制,将两个键自由组合按下,可以明显听到发出三种不同的音调。

因此可以验证设计无误。

EDA实验报告8位二选一多路选择器

学号:201400800093 姓名:胡玲专业:电子信息科学与技术科目:电子设计自动化EDA 实验名称:8位二选一多路选择器

一.实验要求

实验要求:1通过有限状态机的VHDL设计初步了解VHDL表达和设计电路的方法2根据学过的一位二选一选择器改进VHDL语言而掌握8位二选一多路选择器

三.RTL图

四.波形仿真图:

由源代码可知a_fin=a_dis,b_fin=b_dis,但由波形仿真图可知在同一时刻它们并不一定相等,而是存在延迟,结果s_fin也是和对应的输入值存在延迟,如果不考虑延迟,结果正确。

例:t=40ns时输入是1010+0001结果是1011,无进位。

五:实验结果

1.用开关sw17-14表示输入的四位二进制A(17-14分别表示A0-A3),并用LEDR17-14显示。

sw13-10表示输入四位二进制B(13-10分别表示B3-B0)并用LEDR13-10显示。

KEY0用于复位KEY1用于做时钟信号LEDR3-0表示输出的四位二进制数LEDG8(绿灯)显示进位输出。

2.按下复位键—用开关确定输入值(例如输入为1111+1000)—按下时钟信号键—可显示红灯为0111以及绿灯亮有进位。

3.可知结果正确。

六.实验体会及心得

1.做实验前先预习实验内容,学以致用和大胆改进很重要。

2.代码写错没关系,几十个错误也没关系,不能复制粘贴那样学不到东西,与同学探讨很有意义,最后结果出来再回过头研究代码会觉得更了解每一步代码。

3.实验过程中切记避免心浮气躁,急于出结果,如果实在没思路可以看同学代码但一定要看懂在之上进行改变看结果。

EDA实验报告

实验一:QUARTUS II 软件使用及组合电路设计仿真实验目的:学习QUARTUS II 软件的使用,掌握软件工程的建立,VHDL 源文件的设计和波形仿真等基本内容。

实验内容:1.四选一多路选择器的设计基本功能及原理:选择器常用于信号的切换,四选一选择器常用于信号的切换,四选一选择器可以用于4路信号的切换。

四选一选择器有四个输入端a,b,c,d,两个信号选择端s(0)和s(1)及一个信号输出端y。

当s输入不同的选择信号时,就可以使a,b,c,d中某一个相应的输入信号与输出y端接通。

逻辑符号如下:程序设计:软件编译:在编辑器中输入并保存了以上四选一选择器的VHDL源程序后就可以对它进行编译了,编译的最终目的是为了生成可以进行仿真、定时分析及下载到可编程器件的相关文件。

仿真分析:仿真结果如下图所示分析:由仿真图可以得到以下结论:当s=0(00)时y=a;当s=1(01)时y=b;当 s=2(10)时y=c;当s=3(11)时y=d。

符合我们最开始设想的功能设计,这说明源程序正确。

2.七段译码器程序设计基本功能及原理:七段译码器是用来显示数字的,7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用VHDL译码程序在FPGA或CPLD中实现。

本项实验很容易实现这一目的。

输出信号的7位分别接到数码管的7个段,本实验中用的数码管为共阳极的,接有低电平的段发亮。

数码管的图形如下七段译码器的逻辑符号:程序设计:软件编译:在编辑器中输入并保存了以上七段译码器的VHDL源程序后就可以对它进行编译了,编译的最终目的是为了生成可以进行仿真、定时分析及下载到可编程器件的相关文件。

仿真分析:仿真结果如下图所示:分析:由仿真的结果可以得到以下结论:当a=0(0000)时led7=1000000 此时数码管显示0;当a=1(0001)时led7=1111001 此时数码管显示1;当a=2(0010)时led7=0100100 此时数码管显示2;当a=3(0011)时led7=0110000 此时数码管显示3;当a=4(0100)时led7=0011001 此时数码管显示4;当a=5(0101)时led7=0010010 此时数码管显示5;当a=6(0110)时led7=0000010 此时数码管显示6;当a=7(0111)时led7=1111000 此时数码管显示7;当a=8(1000)时led7=0000000 此时数码管显示8;当a=9(1001)时led7=0010000 此时数码管显示9;当a=10(1010)时led7=0001000 此时数码管显示A;当a=11(1011)时led7=0000011 此时数码管显示B;当a=12(1100)时led7=1000110 此时数码管显示C;当a=13(1101)时led7=0100001 此时数码管显示D;当a=14(1110)时led7=0000110 此时数码管显示E;当a=15(1111)时led7=0001110 此时数码管显示F;这完全符合我们最开始的功能设计,所以可以说明源VHDL程序是正确的。

数据选择器实验实训报告 .docx

数据选择器实验实训报告 .docx一、实验目的通过本次实习,了解数据选择器的用法,掌握数据选择器基本操作,深入学习数据选择器性能检测和使用方法。

二、实验内容(1)数据选择器的结构及原理数据选择器是一种计算机硬件工具,可用于从计算机中的原始数据中提取数据,从而可缩短报表生成时间,提高系统运行效率,并增强对原始数据的控制及模拟。

它以过滤依赖于特定列,值,范围或者其他条件来筛选数据,以便收集指定的行和列。

数据选择器可以提取当前会话中的数据,或者收集数据源中的原始数据,从而缩小数据的分析范围,减少存储的数据量,提高计算效率。

(2)数据选择器基本操作1、点击 data selector 图标进入数据选择器界面。

2、选择不同的表,点击它以及其中的列,设置条件以筛选出指定的数据集。

3、确定选择的表以及字段,然后点击Save按钮将设置写入Excel文件,以获取满足筛选条件的数据。

4、可以多次进入数据选择器选择不同数据,选择好之后将写入文件,获取满足筛选条件的新数据。

(3)数据选择器的性能检测1、数据检索速度:测试数据选择器在获取原始数据时的耗时,可以得到此工具检索数据的速度。

2、数据滤波频率:测试数据选择器在滤波数据时的耗时,可得到每秒过滤出满足要求的数据的次数。

3、数据存储空间:测试数据选择器存储在文件中的数据大小,可以比较此工具与其他工具使用相同配置时的缩小比例。

三、实验结果实验结果如图1所示:图1:数据选择器的测试结果可以看到,数据检索速度为7.25ms,过滤频率为850次/秒,存储空间比正常节省约50%。

四、总结及建议通过本次实验,我们掌握了数据选择器的用法,了解了数据选择器性能检测和使用方法等。

实验结果表明,数据选择器在检索速度、过滤频率和数据存储空间上都有较好的表现,可以在较短的时间内筛选出满足要求的原始数据,大大节约了空间。

建议:在日常实践中,应当多练习操作数据选择器,认真学习数据选择器的使用方法,进行针对性的性能检测,以便更好地就数据筛选的任务,撰写精确的报表。

[教学]四选一多路选择器

![[教学]四选一多路选择器](https://img.taocdn.com/s3/m/124cbf7eb7360b4c2f3f641f.png)

[教学]四选一多路选择器实验名称:四选一多路选择器一、实验目的及要求通过本次实验进一步掌握 Modelsim SE 6.5c的仿真调试方法及过程思想,并且进一步学习理解语言门级结构建模的原理及方法,通过仿真达到学习知识的目的。

通过反复阅读有关资料,能够熟练掌握四选一多路选择器的程序代码设计及其仿真结果分析。

二、实验程序及仿真结果四选一的verilog代码module mux4_1(out,in0,in1,in2,in3,sel); output out;input in0,in1,in2,in3;input[1:0] sel;reg out;always @(in0 or in1 or in2 or in3 or sel) begincase(sel)2'b00: out=in0;2'b01: out=in1;2'b10: out=in2;2'b11: out=in3;default: out=2'bx;endcaseendendmodule相应测测试代码:`timescale 1ns/100ps module tmux; reg [1:0]sel;reg in0,in1,in2,in3;wire out;mux4_1 mux(out,in0,in1,in2,in3,sel); initialbeginin0 = 1;in1 = 0;in2 = 1;in3 = 0;sel = 00;#30 sel = 10;#30 sel = 11;#30 sel = 01;endendmodule三、实验小结通过这次四选一多路选择器的实验仿真,让我进一步熟练掌握了Modelsim SE 6.5c仿真环境及其使用方法。

EDA技术4选1多路选择器实验报告

0

0

A

0

1

B

1

0

C

1

1

D

(三)实验仪器及器材

PC机一台;Quartus II软件一套;KHF-5型实验开发系统一套

(四)实验方法及步骤

实验方法及步骤与实验一各个步骤一致,按照实验一进行就行。

1,打开Quartus II开发环境;

2,新建项目;

注意:文件夹名不能用中文,也最好不要用数字;不要将文件夹设在计算机已有的安装目录中,更不要将工程文件直接放在安装目录中。

3、完成软件仿真,管脚配置后下载进行硬件测试。3、完成简单与非门电路的VHDL设计或原理图设计,仿真后下载到实验箱上进行硬件测试。

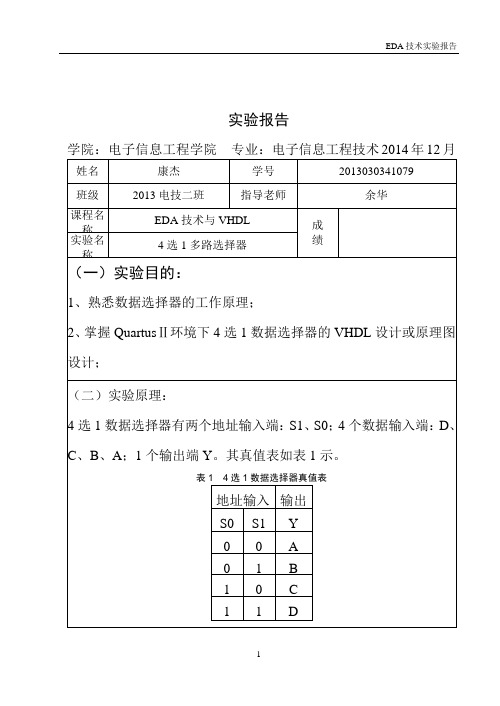

(二)实验原理:

4选1数据选择器有两个地址输入端:S1、S0;4个数据输入端:D、C、B、A;1个输出端Y。其真值表如表1示。

表14选1数据选择器真值表

地址输入

输出

S0

S1

(五)实验数据及分析处理

源程序

4选1数据选择器--用IF-THEN语句

波形仿真结果

RTL电路图

(六)实验结果体会

实验前熟悉数据选择器的工作原理,实验过程中结合理论进行分析;并且初步掌握了QuartusⅡ环境下4选1数据选择器的VHDL设计或原理图设计。波形仿真时仍遇到问题,通过老师指导解决了那个问题,其他方面基本没问题,达到了实验目的。

实验报告

学院:电子信息工程学院专业:dianzi

电子信息工程技术2014年12月20日星期六

姓名

康杰

学号

2013030341079

班级

2013电技二班

指导师

余华

课程名称

EDA技术与VHDL

数字逻辑实验报告 多路选择器

数字逻辑实验实验报告

实验报告说明

数字逻辑课程组

实验名称列入实验指导书相应的实验题目。

实验目的目的要明确,要抓住重点,可以从理论和实践两个方面考虑。

可参考实验指导书的内容。

在理论上,验证所学章节相关的真值表、逻辑表达式或逻辑图的实际应用,以使实验者获得深刻和系统的理解,在实践上,掌握使用软件平台及设计的技能技巧。

一般需说明是验证型实验还是设计型实验,是创新型实验还是综合型实验。

实验环境实验用的软硬件环境(配置)。

实验内容(含电路原理图/Verilog程序、管脚分配、仿真结果等;扩展内容也列入本栏)这是实验报告极其重要的内容。

这部分要写明经过哪几个步骤。

可画出流程图,再配以相应的文字说明,这样既可以节省许多文字说明,又能使实验报告简明扼要,清楚明白。

实验结果分析数字逻辑的设计与实验结果的显示是否吻合,如出现异常,如何修正并得到正确的结果。

实验方案的缺陷及改进意见在实验过程中发现的问题,个人对问题的改进意见。

心得体会、问题讨论对本次实验的体会、思考和建议。

计算机组成原理 多路选择器实验报告

计算机组成原理实验三多路选择器实验...............姓名:陈衍席学号:1205110125 网工1202实验环境】1. Windows 2000 或Windows XP2. QuartusII9.1 sp2、DE2-115计算机组成原理教学实验系统一台,排线若干。

【实验目的】本次实验要求掌握各种多路选择器的设计与实现。

【实验要求】可以利用原理图设计并实现1位、8位和32位2选1多路选择器、32位4选1、32位32选1多路选择器。

其中32位4选1和32位32选1多路选择器,可以借用系统自带的元件库LPM_MUX元件。

【实验原理】多路选择器(Multiplexer)又称数据选择器或多路开关,是一种多个输入、一个输出的器件。

其功能是在选择控制码(地址)电位的控制下从几路数据输入中选择一路并将其送到一个公共输出端,也就是经过多路选择把多个通道的数据传输到唯一的公共数据通道上。

因此,实现数据选择功能的逻辑电路称为多路选择器。

如图所示,为4选1多路选择器示意图:多路选择器的功能类似于一个多掷开关。

如果它有两路数据A0和A1,则选择控制信号S,从两路数据中选中某一路数据送至输出端Y。

此时,其功能相当于多个输入的单刀多掷开关。

2选1多路选择器真值表如下所示;由上表可以推出2选1多路选择器输入、输出逻辑关系式为:【实验步骤】3.1 1位2选1多路选择器的设计由逻辑关系式可知,当S为0时,Y的值由A0确定;当S为1时,Y的值由A1确定,由此可以创建1位2选1多路选择器的原理图。

(1)创建如图所示1位2选1多路选择器的原理图文件:(2)文件编译(3)功能仿真仿真及结果分析:在65s--80ns之间,A0=0,A1=1,当S=1时,Y=1;S=0时,Y(4)生成原理图元器件如图,点击【File】-->【Create/Update】-->【Create Symbol Files for Current File】,完成元件封装。

实验报告一多路选择器Word版

实验报告一多路选择器Word版

实验名称:多路选择器实验

实验目的:

1.了解多路选择器的原理和工作原理。

2.学习如何使用多路选择器。

3.编写多路选择器的真值表和逻辑表达式。

4.掌握多路选择器在数字电路中的应用。

实验器材:

1.实验箱

2.多路选择器IC:74LS153N

3.光电开关:LM228

4.数码开关

5.示波器

实验步骤:

3.将数码开关与多路选择器连接。

实验结果:

输入A 输入B 功能输出Y

0 0 S0输出

逻辑表达式:Y=S0·A·B'+S1·A'·B+S2·A·B+S3·A'·B'

2.按照实验步骤连接电路,开启电源后,将数码开关和光电开关的状态分别作为多路选择器的输入,观察其输出是否符合真值表和逻辑表达式。

1.多路选择器可以实现多输入单输出的功能,根据输入的选择不同,输出不同的信号。

2.制作多路选择器时需要注意电路的连接正确性。

实验报告一多路选择器..

实验报告⼀多路选择器..

计算机组成原理实验报告

——实验⼀多路选择器的设计与实现

专业:计算机科学与技术(师范)

姓名:XXX

学号:

指导⽼师:

完成⽇期:

⼀、实验⽬的

1、回顾多路选择器的原理

2、熟悉Logisim软件的使⽤⽅法

3、熟悉ISE软件的开发过程

4、锻炼使⽤VHDL语⾔⾯熟硬件的能⼒

5、熟悉Digilent Nexy3 FPGA开发板

⼆、实验内容

⽤两种⽅法实现⼀个两位数据的2选1多路选择器

1、⽤Logisim软件设计2选1多路选择器并进⾏仿真

2、使⽤VHDL语⾔设计2选1多路选择器,并在ISE环境下进⾏综合、仿真、调试,并下载到Digilent Nexy3 FPGA开发板进⾏验证

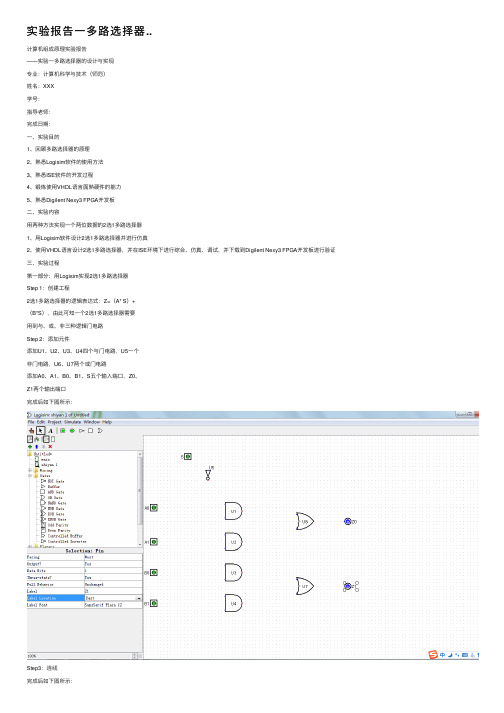

三、实验过程

第⼀部分:⽤Logisim实现2选1多路选择器

Step 1:创建⼯程

2选1多路选择器的逻辑表达式:Z=(A* S)+

(B*S),由此可知⼀个2选1多路选择器需要

⽤到与、或、⾮三种逻辑门电路

Step 2:添加元件

添加U1、U2、U3、U4四个与门电路,U5⼀个

⾮门电路,U6、U7两个或门电路

添加A0、A1、B0、B1、S五个输⼊端⼝,Z0、

Z1两个输出端⼝

完成后如下图所⽰:

Step3:连线

完成后如下图所⽰:

Step 4:仿真

Step 5:编辑电路外观

Step 6: 电路应⽤

四、实验结果

第⼀部分:⽤Logisim实现2选1多路选择器实验结果1、表格:

2、截图

五、实验⼼得

通过实验我熟悉了Logisim 软件的使⽤⽅法,并且掌握了多路选择器的设计与实现。

EDA多路选择器设计实验报告

EDA多路选择器设计实验报告多路选择器设计实验一、实验目的:进一步熟悉Quartus II的Verilog文本设计流程,组合电路的设计仿真和硬件测试。

二、实验内容:1、根据4.1节流程,利用Quartus II完成4选1多路选择器的文本代码编辑输入和仿真测试等步骤,给出仿真波形。

2、在实验系统上硬件测试,验证此设计的功能。

三、实验程序:Quartus II程序:module mux41a(a,b,c,d,s0,s1,y);input a,b,c,d;input s0,s1;output y;reg y;always@(a,b,c,d,s0,s1)begin :mux41case({s0,s1})2'b00:y<=a;2'b01:y<=b;2'b10:y<=c;2'b11:y<=d;default :y<=a;endcaseendendmodulemodelsim程序:// Copyright (C) 1991-2012 Altera Corporation// Your use of Altera Corporation's design tools, logic functions // and other software and tools, and its AMPP partner logic // functions, and any output files from any of the foregoing // (including device programming or simulation files), and any // associated documentation or information are expressly subject // to the terms and conditions of the Altera Program License // Subscription Agreement, Altera MegaCore Function License // Agreement, or other applicable license agreement, including, // without limitation, that your use is for the sole purpose of // programming logic devices manufactured by Altera and sold by // Altera or its authorized distributors. Please refer to the // applicable agreement for further details.//******************************************************************** *********// This file contains a Verilog test bench template that is freely editable to// suit user's needs .Comments are provided in each section to help the user// fill out necessary details.//******************************************************************** *********// Generated on "10/11/2015 21:31:33"// Verilog Test Bench template for design : mux41a//// Simulation tool : ModelSim-Altera (Verilog)//`timescale 1 us/ 1 psmodule mux41a_vlg_tst();// constants // general purpose registers//reg eachvec;// test vector input registersreg a;reg b;reg c;reg d;reg s0;reg s1;// wires wire y;// assign statements (if any) mux41a i1 (// port map - connection between master ports and signals/registers .a(a),.b(b),.c(c),.d(d),.s0(s0),.s1(s1),.y(y));initialbegina=0;b=0;c=0;d=0;s0=0;s1=0;#20 s0=0;s1=1;#20 s0=1;s1=0;#20 s0=1;s1=1;#20 $stop;endalways #2 a=~a;always #4 b=~b;always #6 c=~c;always #8 d=~d;endmodule四、实验步骤:1、打开Quartus II,点击“file”中的“New Project Wizard”,新建工程到指定文件夹中2、点击“New”新建工作簿,写入程序3、点击“compile design”进行编译方法一:联合仿真1、点击“processing”中的“start”2、点击“file”中的“open”,找到“modelsim”,查找“.vt”文件3、打开“mux41a”文件4、修改文件中的程序5、打开“Assignments”,点击“setting”,修改时间6、点击“test benches”后再点击“New”添加“mux41a”文件7、再进行编译8、点击“Tools”,打开“Run Simulation Tool”,再选择“RTL Simulation”方法二:modelsim单独仿真1、在modelsim中新建“sim”文件2、打开“modelsim”,创建工程3、点击“create new file”,新建两个工作簿4、分别添加相应程序进去,进行编译5、选择library,点击work,之后再右击add?to wave?selected signals,最后选择simulate点击run?run all。

2选1多路选择器EDA实验报告

2选1多路选择器EDA实验报告EDA实验报告学⽣姓名:asfmla;m 学号:eafvpa[cv专业班级:电⼦3班组合电路设计⼀、实验⽬的熟悉quartusⅡ的VHDL⽂本设计全过程,学习简单组合电路的设计、多层次电路设计、仿真。

⼆、实验内容实验内容:⾸先利⽤quartusⅡ完成2选1多路选择器(例4-3)的⽂本编译输⼊(mux21a.vhd)和仿真测试等步骤,最后在实验系统上硬件测试,验证此设计的功能。

将此多路选择器看成⼀个元件mux21a,利⽤元件例化语句描述成三选⼀,然后进⾏编译、综合、仿真。

引脚锁定以及硬件下载测试。

建议选实验电路模式5,⽤键1(PIO0)控制s0;⽤键2(PIO1)控制s1;a3、a2和a1分别接clock5、clock0和clock2;输出信号outy仍接扬声器spker。

通过短路帽选择clock0接256HZ信号,clock5接1024HZ信号,clock2接8HZ信号。

最后选⾏编译、下载和硬件测试实验。

三、实验器材Quartus II软件。

四、设计思路/原理图五、实验程序实验内容1:⼆选⼀:library ieee;use ieee.std_logic_1164.all;entity mux21a isport(a,b: in std_logic;s: in std_logic;y: out std_logic);end entity;architecture dataflow of mux21a isbeginy<=a when s='0' else b;end architecture;实验内容2:三选⼀library ieee;use ieee.std_logic_1164.all;entity mux31a isport(a1,a2,a3: in std_logic;s0,s1: in std_logic;outy: out std_logic);end entity mux31a;architecture m31a of mux31a iscomponent mux21aport( a,b: in std_logic;s: in std_logic;y: out std_logic);end component;signal tmp: std_logic;beginu1: mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp);u2: mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy);end architecture;六、实验步骤在E盘新建⼀个⽂件夹,⽤于存放⼯程。

实验一 2选1多路选择器1

本科学生综合性实验报告学号114090317 姓名李明旭学院物电学院专业、班级11电子实验课程名称电子设计自动化(EDA实验)教师及职称罗永道(副教授)开课学期2013 至2014 学年下学期填报时间2014 年05 月06 日实验序号 1 实验名称 2选1多路选择器及其VHDL 描述 实验时间 2014年05月04日实验室同析3栋楼114一.实验预习 1.实验目的:(1) 掌握2选1多路选择器的工作原理;(2) 掌握VHDL 编程语言的使用和设计方法;(3) 掌握Quartus II 软件的使用和工程的开发流程。

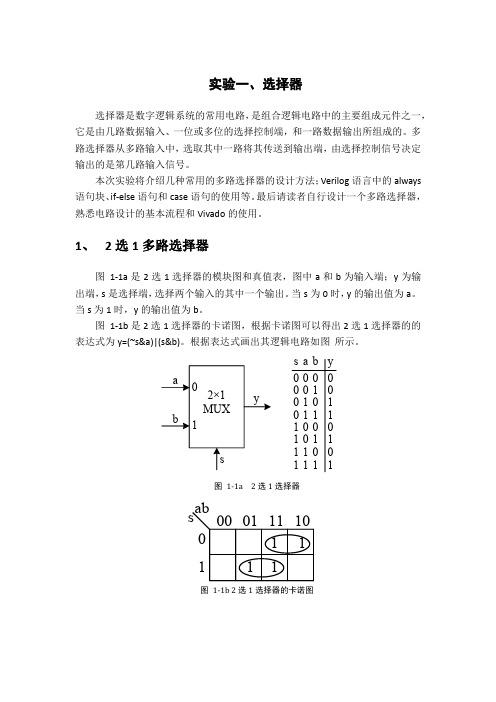

2.实验原理、实验流程或装置示意图:在数字电路中2选1多路选择器具备了组合逻辑电路的简单性和经典性的特征。

本实验以此电路模块来学习对应的VHDL 表达及其设计,同时练习使用Quartus II 软件的开发流程。

2选1多路选择器(假设此模块的器件名是mux21a )的电路模型或元件图如图1所示。

图中,a 、b 是两个数据选择通道输入端口;s 是通道选择控制信号端;y 是数据输出端;当s 取值分别为0和1时,输出端y 将分别输出来自输出口a 和b 的数据。

此选择器对应的逻辑电路图2,可以认为是此多路选择器的内部电路结构。

图1 mux21a 实体NOTinstAND2inst3AND2inst4OR2inst5VCCaINPUTVCCbINPUT VCCsINPUT yOUTPUT图2 mux21a 结构体3.实验设备及材料电脑一台,QuartusII 实验平台4.实验方法步骤及注意事项实验方法步骤:(1)打开计算机;(2)打开Quartur II软件,编写和调试实验代码,然后进行试验仿真。

注意事项:实验过程中认真分析实验原理编写代码,防止书本、书包等物品与实验设备接触,以免造成不必要的麻烦。

二.实验内容1.实验现象与结果2选1多路选择器的VHDL描述1:entity mux21a isport(--定义输入输出端口a:in bit;b:in bit;s:in bit;y:out bit);end entity mux21a;architecture one of mux21a is beginy<=a when s='0'else b;end architecture one;编译报告为:其仿真波形如下所示:其中a,b,s,都分别赋给不同频率的时钟信号RTL图为:符号图为:2选1多路选择器的VHDL描述2:library ieee;use ieee.std_logic_1164.all;entity mux21a isport (a,b,s:in std_logic;y:out std_logic );end entity mux21a;architecture one of mux21a issignal e:std_logic;signal d:std_logic;begind<=a and (not s);e<=b and s ;y<=d or e;end architecture one;编译报告为:其仿真波形如下所示:RTL图为:符号图为:2选1多路选择器的VHDL描述3:library ieee;use ieee.std_logic_1164.all;entity mux21a isport(a,b,s:in std_logic;y:out std_logic);end entity mux21a;architecture one of mux21a isbeginprocess(a,b,s) beginif s='0' then y<=a;else y<=b;end if;end process;end architecture one ;编译报告为:其仿真波形如下所示:RTL图为:符号图为:2.对实验现象、实验结果的分析及其结论从三个仿真波形都可以看出当s=0时y=a,s=1时y=b。

实验1 多路选择器

激励代码解释: `timescale 10 ns/ 1 ps module mux21_vlg_tst();

reg a; reg b; reg s; wire y;

// 设置时间尺度和时间精度 // 测试代码的端口参数列表为空 // 输入变量声明为 reg 型变量

// 输出变量声明为 wire 型变量

always 语句块的使用

always 块的语句格式如下: always @(<敏感事件列表>)

各可执行的语句; …… 其中敏感事件列表中列出了所有影响 always 块中输出的信号清单,也就是 说,如果敏感事件列表中的任何一个变量发生了变化,都要执行 always 语句块 中的语句。如 always @ (a or b or s)表示:只要 a、b、s 中的任何一个变量发生了 变化,就立刻执行 always 语句块中的语句。 为了方便起见,敏感列表也可以用“*”代替,如 always @ (*), (*)号将 自动包含 always 语句块中右边的语句或条件表达式中的所有信号。如程序清单 2, 只要 always 语句块中表达式右边出现的变量 a 和 b,或者条件表达式中出现的变 量 s,这三个变量中的任何一个变量发生了变化,就立刻执行 always 语句块中的 语句。 always 语句还有另外一种形式,即:always 后面不带任何有关敏感事件列表

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

计算机组成原理实验报告

——实验一多路选择器的设计与实现

专业:计算机科学与技术(师范)

姓名:XXX

学号:

指导老师:

完成日期:

实验目的

1、回顾多路选择器的原理

2、熟悉Logisim软件的使用方法

3、熟悉ISE软件的开发过程

4、锻炼使用VHDL语言面熟硬件的能力

5、熟悉Digilent Nexy3 FPGA开发板

一、实验内容

用两种方法实现一个两位数据的2选1多路选择器

1、用Logisim软件设计2选1多路选择器并进行仿真

2、使用VHDL语言设计2选1多路选择器,并在ISE环境下进行综合、仿真、调试,并下载到Digilent Nexy3 FPGA开发板进行验证

二、实验过程

第一部分:用Logisim实现2选1多路选择器

Step 1:创建工程

2选1多路选择器的逻辑表达式:Z=(A* S)+

(B*S),由此可知一个2选1多路选择器需要

用到与、或、非三种逻辑门电路

Step 2:添加元件

添加U1、U2、U3、U4四个与门电路,U5一个

非门电路,U6、U7两个或门电路

添加A0、A1、B0、B1、S五个输入端口,Z0、 Z1两个输出端口

完成后如下图所示:

Step3:连线

完成后如下图所示:

Step 4:仿真

Step 5:编辑电路外观

Step 6: 电路应用

三、实验结果

第一部分:用Logisim实现2选1多路选择器实验结果

1、表格:

序号

输入输出

A1A0B1B0S Z1Z0(预期)Z1Z0(实际)

1000110101 2001011010 3001110011 4010000101 5100001010

6110001111

2、截图

四、实验心得

通过实验我熟悉了Logisim软件的使用方法,并且掌握了多路选择器的设计与实现。

(注:专业文档是经验性极强的领域,无法思考和涵盖全面,素材和资料部分来自网络,供参考。

可复制、编制,期待你的好评与关注)。