数字电子技术基础习题册2010-答案8-11

数字电子技术基础习题及答案

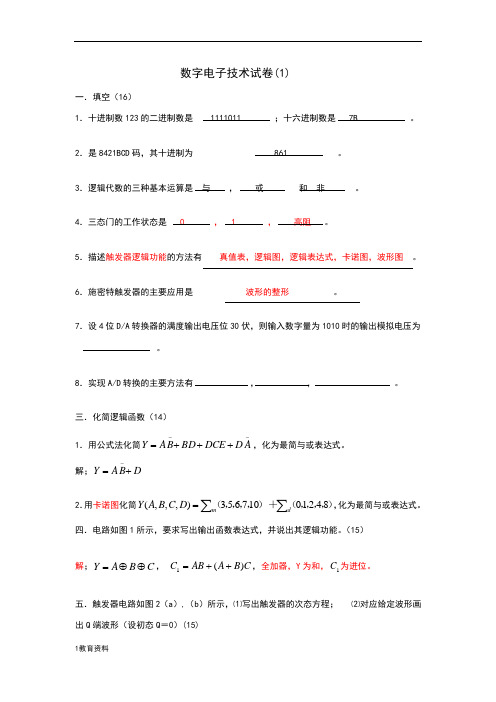

数字电子技术试卷(1)一.填空(16)1.十进制数123的二进制数是 1111011 ;十六进制数是 7B 。

2.是8421BCD 码,其十进制为 861 。

3.逻辑代数的三种基本运算是 与 , 或 和 非 。

4.三态门的工作状态是 0 , 1 , 高阻 。

5.描述触发器逻辑功能的方法有 真值表,逻辑图,逻辑表达式,卡诺图,波形图 。

6.施密特触发器的主要应用是 波形的整形 。

7.设4位D/A 转换器的满度输出电压位30伏,则输入数字量为1010时的输出模拟电压为 。

8.实现A/D 转换的主要方法有 , , 。

三.化简逻辑函数(14)1.用公式法化简--+++=A D DCE BD B A Y ,化为最简与或表达式。

解;D B A Y +=-2.用卡诺图化简∑∑=mdD C B A Y ),,,,()+,,,,(84210107653),,,(,化为最简与或表达式。

四.电路如图1所示,要求写出输出函数表达式,并说出其逻辑功能。

(15)解;C B A Y ⊕⊕=, C B A AB C )(1++=,全加器,Y 为和,1C 为进位。

五.触发器电路如图2(a ),(b )所示,⑴写出触发器的次态方程; ⑵对应给定波形画出Q 端波形(设初态Q =0)(15)解;(1)AQ Q Q n +=-+1,(2)、A Q n =+1六.试用触发器和门电路设计一个同步的五进制计数器。

(15)七.用集成电路定时器555所构成的自激多谐振荡器电路如图3所示,试画出V O ,V C 的工作波形,并求出振荡频率。

(15)数字电子技术试卷(2)二.填空(16)1.十进制数的二进制数是;十六进制数是。

2.逻辑代数中逻辑变量得取值为 0、1 。

3.组合逻辑电路的输出状态只与当前输入有关而与电路原状态无关。

4.三态门的输出有0、1、高阻,三种状态,当多个三态门的输出端连在一根总线上使用时,应注意只能有1个三态门被选通。

5.触发器的基本性质有有两个稳态,在触发信号作用下状态可相互转变,有记忆功能6.单稳态触发器的主要应用是延时。

《数字电子技术》习题及答案

第1章 数制和码制 一、填空题1.数制转换:(011010)2 =( )10 =( )8 =( )16。

2.数制转换:(35)10 =( )2 =( )8 =( )16。

3.数制转换:(251)8 =( )2 =( )16 =( )10。

4.数制转换:(4B )16 =( )2 =( )8 =( )10。

5.数制转换:(69)10 =( )2 =( )16 =( )8。

6.将二进制数转换为等值的八进制和十六进制数 (10011011001)2 =( )8 =( )16。

7.将二进制数转换为等值的八进制和十六进制数 (1001010.011001)2 =( )8 =( )16。

一、填空题答案: 1.26、32、1A ; 2.100011、43、 23; 3.10101001、A9、169; 4.1001011、113、75; 5.1000101、45、105; 6.2331、4D9; 7.112.31、4A.64。

第2章 逻辑代数基础 一、填空题1.逻辑函数Y AB A B ''=+,将其变换为与非-与非形式为 。

2.逻辑函数Y A B AB C ''=+,将其变换为与非-与非形式为 。

3. 将逻辑函数AC BC AB Y ++=化为与非-与非的形式,为 。

4.逻辑函数Y A A BC '''=+,化简后的最简表达式为 。

5.逻辑函数Y A B A B ''=++,化简后的最简表达式为 。

6.逻辑函数()()Y A BC AB ''''=+,化简后的最简表达式为 。

7. 逻辑函数Y AB AB A B ''=++,化简后的最简表达式为 。

一、填空题答案1.()()()Y AB A B '''''= ; 2.()()()Y A B AB C '''''=; 3. ()()()()Y AB BC AC ''''=; 4. Y A '=; 5.1Y =; 6.1Y =; 7.Y A B =+。

《数字电子技术基础》课后习题及参考答案

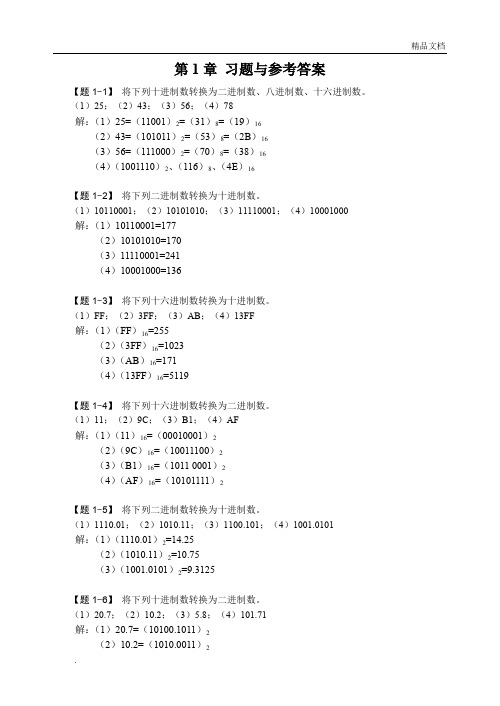

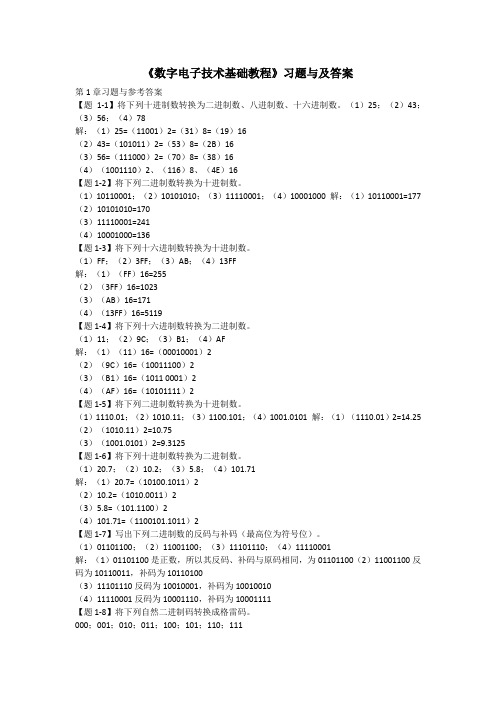

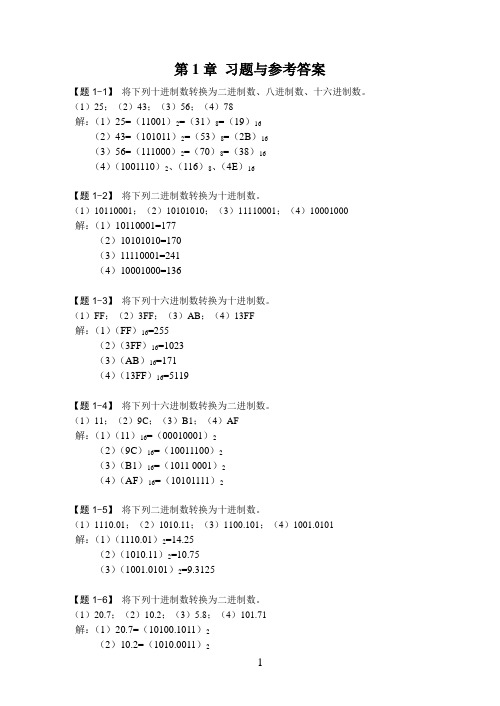

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)=177(2)=170(3)=241(4)=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=()2(3)(B1)16=(1011 0001)2(4)(AF)16=()2【题1-5】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)()2=(2)()2=(3)()2=【题1-6】将下列十进制数转换为二进制数。

(1);(2);(3);(4)解:(1)=()2(2)=()2(3)=()2(4)=()2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(1)01101100;(2);(3);(4)解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100(2)反码为,补码为(3)反码为,补码为(4)反码为,补码为【题1-8】将下列自然二进制码转换成格雷码。

000;001;010;011;100;101;110;111解:格雷码:000、001、011、010、110、111、101、100【题1-9】将下列十进制数转换成BCD码。

《数字电子技术基础》课后习题及参考答案

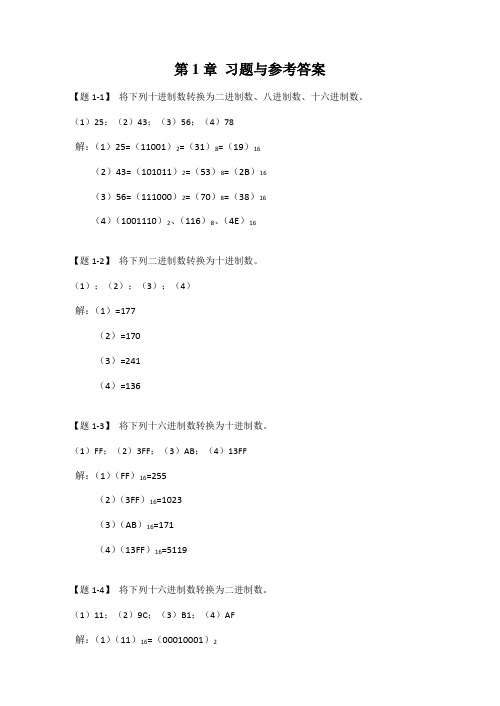

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

《数字电子技术基础》课后习题答案

2、2: (4)解:

(8)解:

2、3:

(2)证明:左边

《数字电子技术基础》课后习题答案

=右式 所以等式成立

(4)证明:左边=

右边= 左边=右边,所以等式成立 2、4

(1) 2、5 (3) 2、6:

(1) 2、7:

(1) 卡诺图如下:

BC A

00

01

11

10

0

1

1

1

1

1

1

所以, 2、8: (2)画卡诺图如下:

(c)

(f)

3、7、解: (a)

《数字电子技术基础》课后习题答案

3、8、解:输出高电平时,带负载的个数

N OH

I OH I IH

400 20

20

G 可带 20 个同类反相器 输出低电平时,带负载的个数

N OL

I OL I IL

8 0.45

17.78

G 反相器可带 17 个同类反相器 3、12

EN=1 时,

11

10

00

0

0

0

0

01

0

0

0

0

11

0

1

1

1

10

0

0

0

0

电路图如下:

第四章:

自测题:

一、 2、输入信号,优先级别最高的输入信号 7、用以比较两组二进制数的大小或相等的电路,A>B 二、 3、√ 4、√ 三、 5、A 7、C

练习题:

4、1;解:(a) (b)

(74)10 =(0111 0100)8421BCD=(1010 0111)余 3BCD (45、36)10 =(0100 0101、0011 0110)8421BCD=(0111 1000、0110 1001 )余 3BCD (136、45)10 =(0001 0011 0110、0100 0101)8421BCD=(0100 0110 1001、0111 1000 )余 3BCD (374、51)10 =(0011 0111 0100、0101 0001)8421BCD=(0110 1010 0111、1000 0100)余 3BCD 1、8、解

《数字电子技术基础》课后习题及参考标准答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)=177(2)=170(3)=241(4)=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=()2(3)(B1)16=(1011 0001)2(4)(AF)16=()2【题1-5】将下列二进制数转换为十进制数。

(1);(2);(3);(4)解:(1)()2=(2)()2=(3)()2=【题1-6】将下列十进制数转换为二进制数。

(1);(2);(3);(4)解:(1)=()2(2)=()2(3)=()2(4)=()2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(1)01101100;(2);(3);(4)解:(1)01101100是正数,所以其反码、补码与原码相同,为01101100(2)反码为,补码为(3)反码为,补码为(4)反码为,补码为【题1-8】将下列自然二进制码转换成格雷码。

000;001;010;011;100;101;110;111解:格雷码:000、001、011、010、110、111、101、100【题1-9】将下列十进制数转换成BCD码。

数字电子技术基础习题册2010-答案8-11

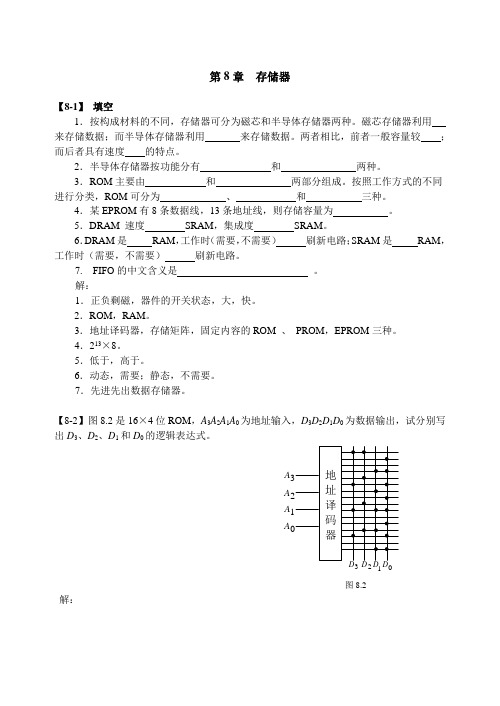

第8章存储器【8-1】填空1.按构成材料的不同,存储器可分为磁芯和半导体存储器两种。

磁芯存储器利用来存储数据;而半导体存储器利用来存储数据。

两者相比,前者一般容量较;而后者具有速度的特点。

2.半导体存储器按功能分有和两种。

3.ROM主要由和两部分组成。

按照工作方式的不同进行分类,ROM可分为、和三种。

4.某EPROM有8条数据线,13条地址线,则存储容量为。

5.DRAM 速度SRAM,集成度SRAM。

6.DRAM是RAM,工作时(需要,不需要)刷新电路;SRAM是RAM,工作时(需要,不需要)刷新电路。

7. FIFO的中文含义是。

解:1.正负剩磁,器件的开关状态,大,快。

2.ROM,RAM。

3.地址译码器,存储矩阵,固定内容的ROM 、PROM,EPROM三种。

4.213×8。

5.低于,高于。

6.动态,需要;静态,不需要。

7.先进先出数据存储器。

【8-2】图8.2是16×4位ROM,A3A2A1A0为地址输入,D3D2D1D0为数据输出,试分别写出D3、D2、D1和D0的逻辑表达式。

AAAA3 2 1 0图8.2解:⎪⎪⎪⎩⎪⎪⎪⎨⎧∑=⋅=∑==)m(0,5,9,13312,15)m(3,6,9,12100D A A D D A D【8-3】用16×4位ROM 做成两个两位二进制数相乘(A 1A 0×B 1B 0)的运算器,列出真值表,画出存储矩阵的阵列图。

解:图8.3【8-4】由一个三位二进制加法计数器和一个ROM 构成的电路如图8.4(a)所示 1.写出输出F 1、F 2和F 3的表达式;2.画出CP 作用下F 1、F 2和F 3的波形(计数器的初态为”0“)F 1F 2F 3CP(a) (b)图8.4解:1. ⎪⎪⎩⎪⎪⎨⎧⋅=⋅⋅+⋅+⋅⋅=⋅+⋅+⋅=013012012012201212011Q Q F Q Q Q Q Q Q Q Q Q F Q Q Q Q Q Q Q F2.CP F1F2F3图8.4(b )【8-5】用ROM 实现全加器。

数字电子技术基础习题答案完整版

数字电子技术基础习题答案HEN system office room 【HEN16H-HENS2AHENS8Q8-HENH1688】数字电子技术基础答案第1章自测题 填空题 1.2. 43. n 24. 逻辑代数 卡诺图5.)(D C B A F )(D C B A F +='6.))((C B D C B A F7. 代数法 卡诺图8. 1 判断题1. √2.√3. × 选择题A F =1⊙B AB F 2 B A F +=3C L =AB C B A BC Y 习题1.1 当000012 A A A ,7A 到3A 有1个不为0时,就可以被十进制8整除 1.2 (a)AC BC AB F ++=1 (b )B A AB F +=2(c)C B A S ⊕⊕= AC BC AB C 0 略(1) )(B A D C F )(1 ))((1B A D C F ++=' (2) )(B A B A F )(2 ))((2B A B A F ++=' (3) E D C B A F 3 DE C AB F ='3(4) )()(4D A B A C E A F )())()((4D A C AB E A F +++='C B A F ⊕⊕=(1) B A C B C A L (2) D B C B D C A L (3) AD L (4) E ABCD L (5) 0 L C B A BC A C AB ABC C B A L ),,((1) ABD D A C F 1 (2) BC AB AC F 2(3) C A B A B A F 3 (有多个答案) (4) C B D C AB C A CD F +++=4 (5) C B A ABD C B A D B A F 5 (6) 16 F (1) AD D C B B A F 1 (2) B A AC F 2(3) D A D B C B F 3 (4) B C F 4 (1) C A B F 1 (2) B C F 2(3) D A B C F 3 (4) C B A D B D C F 4 C A B A D F(1) D B A D C A D C B F 1(多种答案) (2) C B BCD D C D B F 2 (3) C B C A D C F 3 (4) A B F 4 (5) BD D B F 5 (6) C B D A D C A F 6(多种答案) (7) C A D B F 7(多种答案) (8) BC D B F 8(多种答案) (9) B D C F 9 略第2章自测题 判断题1. √2. √3. ×4. √5. √6. √7. ×8. √9. × 10√ 选择题1.A B 2.C D 3.A 4.B 5.B 6.A B D 7.C 8.A C D 9.A C D 习题解:ABC Y =1 解:(a)mA 234.0503.012=-=-=C CES CC BS R U V I β∴三极管处于放大状态,)V (711.05012=⨯⨯-=-=C B CC O R I V u β。

数字电子技术基础课后习题答案第8章习题答案

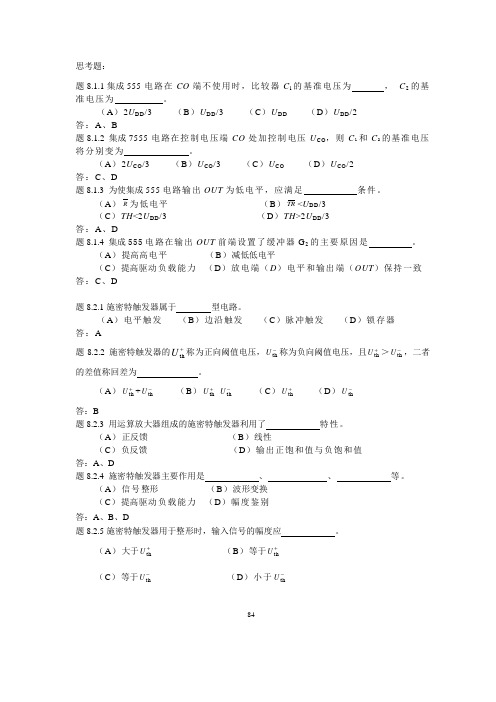

84题8.1.1集成555电路在CO 端不使用时,比较器C l 的基准电压为 , C 2的基准电压为 。

(A )2U DD /3 (B )U DD /3 (C )U DD (D )U DD /2 答:A 、B题8.1.2 集成7555电路在控制电压端CO 处加控制电压U CO ,则C 1和C 2的基准电压将分别变为 。

(A )2U CO /3 (B )U CO /3 (C )U CO (D )U CO /2 答:C 、D题8.1.3 为使集成555电路输出OUT 为低电平,应满足 条件。

(A )R 为低电平 (B )TR <U DD /3 (C )TH <2U DD /3 (D )TH >2U DD /3 答:A 、D题8.1.4 集成555电路在输出OUT 前端设置了缓冲器G 2的主要原因是 。

(A )提高高电平 (B )减低低电平(C )提高驱动负载能力 (D )放电端(D )电平和输出端(OUT )保持一致 答:C 、D题8.2.1施密特触发器属于 型电路。

(A )电平触发 (B )边沿触发 (C )脉冲触发 (D )锁存器 答:A题8.2.2 施密特触发器的+th U 称为正向阈值电压,-th U 称为负向阈值电压,且+th U >-th U ,二者的差值称回差为 。

(A )+th U +-th U (B )+th U --th U (C )+th U (D )-th U答:B题8.2.3 用运算放大器组成的施密特触发器利用了 特性。

(A )正反馈 (B )线性(C )负反馈 (D )输出正饱和值与负饱和值 答:A 、D题8.2.4 施密特触发器主要作用是 、 、 等。

(A )信号整形 (B )波形变换 (C )提高驱动负载能力 (D )幅度鉴别 答:A 、B 、D题8.2.5施密特触发器用于整形时,输入信号的幅度应 。

(A )大于+th U (B )等于+th U (C )等于-th U(D )小于-th U题8.2.6 可将变化缓慢的输入信号变换为矩形脉冲信号。

数字电子技术基础课后习题及参考答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础课后习题及参考答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础课后答案

数字电子技术基础课后答案第一章1.1 选择题答案1.C2.D3.A4.B1.2 填空题答案1.二进制2.163.2^n4.霍尔定律1.3 简答题答案1.数字系统的特征:离散性、离散性变量、离散性元件。

2.多位二进制数的表示:每一位上的位权是2的倍数,从右到左依次是1、2、4、8、16,即从低到高位权递增。

3.数字电路中的常用逻辑门:与门、或门、非门、异或门。

4.二进制加法器:用于实现二进制数的加法操作,可以分为半加器和全加器两种。

第二章2.1 选择题答案1.B2.C3.A4.D2.2 填空题答案1.与非门2.非3.低电平4.与非门2.3 简答题答案1.逻辑代数的基本运算:与运算、或运算、非运算。

2.逻辑门的基本类型:与门、或门、非门。

3.逻辑电位表示:用两个不同的电平来表示逻辑0和逻辑1,常用的是低电平表示逻辑0,高电平表示逻辑1。

4.逻辑门的输入输出关系:根据输入的逻辑电平,逻辑门会产生对应的输出电平。

第三章3.1 选择题答案1.C2.B3.D4.A3.2 填空题答案1.或非门2.与非门3.反相器4.同或门3.3 简答题答案1.反相器的功能:将输入信号的逻辑电平反转。

2.与非门和或非门的功能:与非门将与门的输出进行反向,或非门将或门的输出进行反向。

3.同或门的功能:在输入信号相同的情况下,输出逻辑1;在输入信号不同的情况下,输出逻辑0。

4.逻辑门的级联:逻辑门可以通过级联连接,实现复杂的逻辑功能。

第四章4.1 选择题答案1.C2.D3.A4.B4.2 填空题答案1.半加器2.与非门3.非门4.不可用4.3 简答题答案1.半加器的功能:用于实现两个单独的二进制位的相加操作,产生和位和进位位。

2.全加器的功能:用于实现三个二进制位的相加操作,包括输入的两个二进制位和进位位,产生和位和进位位。

3.二进制加法器的级联:通过将多个全加器级联连接,可以实现多位二进制数的相加操作。

4.数字比较器的功能:用于比较两个多位二进制数的大小,根据比较结果输出大于、小于或等于的信号。

(全)数字电子技术基础课后答案夏路易

《数字电子技术基础教程》习题与参考答案(2010.1)第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(全)数字电子技术基础课后答案

【题

(

解:(1)A=0,B=0

(2)A=0,B=1或C=1

(3)A=1,B=0,C=1

(4)A=0,B=1或C=0

【题

(

解:(1)

A

B

C

Y

0

0

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

1

1

0

1

1

1

1

0

0

1

1

1

1

(2)

当A取1时,输出Y为1,其他情况Y=0。

【题

(

(

解:(1)左边 右边

【题

(1)

解:(1)25=(0010 0101)BCD

(

(

(

【题

解:4位数格雷码;

0000、0001、0011、0010、0110、0111、0101、0100、1100、1101、1111、1010、1011、1001、1000、

第

【题

图题2-1

解:

【题

图题2-2

解:

【题

图题2-3

解:

【题

图题2-4

0

0

0

0

1

0

0

0

1

0

0

0

1

0

0

0

0

1

1

0

0

1

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

1

习题答案(数电)

将各触发器的驱动方程代入特性 方程,即得电路的状态方程:

数字电子技术基础 列状态转换表

* Q0 D * Q1 Q0 * Q2 Q1

西安工程大学

数字电子技术基础 15. 用ROM产生下列一组函数,写出ROM中应存入的数据表。 解:由原式得到最小项之和表达式

Y3 m( 2 ,11 ) Y2 m( 3 ,7 ,8 ,12,14 ) Y1 m( 5 ,10,13 ) Y0 m( 0 ,2 ,4 ,6 )

将各触发器的驱动方程代入特性方程, 即得电路的状态方程: Q1* T1 Q1 X Q0 Q1

* Q0 T0 Q0 1 Q0 Q0 西安工程大学

数字电子技术基础 列状态转换表

画状态转换图和时序波形图

由状态图可以看出, 当输入X =0时,状态变化为: 00→01→10→11→00→…

当X=1时,状态变化为: 00→11→10→01→00→… 可见,该电路既具有递增计数功能,又具有递减计数功能, 是一个2位二进制同步可逆计数器。 西安工程大学

数字电子技术基础 8. 写出下图电路的驱动方程、特性方程和输出方程。

解:驱动方程

J 1 Q3 J 2 Q1 J Q Q 1 2 3

西安工程大学

数字电子技术基础

第六章

时序逻辑电路

西安工程大学

数字电子技术基础 7. 试分析下图所示时序逻辑电路的逻辑功能。

解:属同步时序电路,时钟方程省去。 输出方程: Y XQ1 X Q1 驱动方程: T触发器的特性方程:

《数字电子技术基础教程》习题与及参考答案

《数字电子技术基础教程》习题与及答案第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177 (2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101 解:(1)(1110.01)2=14.25 (2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础课后习题及参考答案

第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

(全)数字电子技术基础课后答案夏路易

《数字电子技术基础教程》习题与参考答案(2010.1)第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101 解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础试卷及答案8套

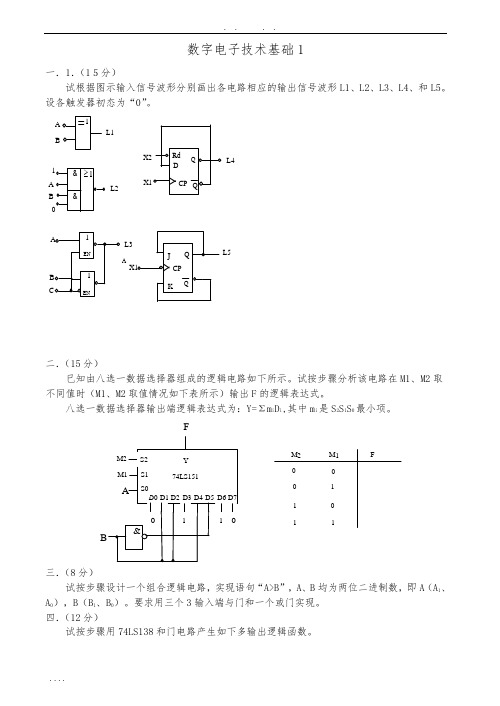

数字电子技术基础1一.1.(15分)试根据图示输入信号波形分别画出各电路相应的输出信号波形L1、L2、L3、L4、和L5。

设各触发器初态为“0”。

AB二.(15分)已知由八选一数据选择器组成的逻辑电路如下所示。

试按步骤分析该电路在M1、M2取不同值时(M1、M2取值情况如下表所示)输出F的逻辑表达式。

八选一数据选择器输出端逻辑表达式为:Y=Σm i D i,其中m i是S2S1S0最小项。

FM2M1 F0 00 1111三.(8分)试按步骤设计一个组合逻辑电路,实现语句“A>B”,A、B均为两位二进制数,即A(A1、A0),B(B1、B0)。

要求用三个3输入端与门和一个或门实现。

四.(12分)试按步骤用74LS138和门电路产生如下多输出逻辑函数。

123Y AC Y ABC ABC BC Y BC ABC=⎧⎪=++⎨⎪=+⎩ 74LS138逻辑表达式和逻辑符号如下所示。

五.(15分)已知同步计数器的时序波形如下图所示。

试用维持-阻塞型D 触发器实现该计数器。

要求按步骤设计。

六.(18分)按步骤完成下列两题1.分析图5-1所示电路的逻辑功能:写出驱动方程,列出状态转换表,画出完全状态转换图和时序波形,说明电路能否自启动。

2.分析图5-2所示的计数器在M=0和M=1时各为几进制计数器,并画出状态转换图。

图5-1BCCP AEpE TLDDQ0Q1Q3Q274LS163Rd1M&1计数脉冲001图5-2七.八.(10分)电路下如图所示,按要求完成下列问题。

1.指出虚线框T1中所示电路名称.2.对应画出V C、V01、A、B、C的波形。

并计算出V01波形的周期T=?。

1576842R1NE5553R2C1Vc+0.01uJK1QQ&&V CCV01ABCC10K10KT1T2数字电子技术基础2一.(20分)电路如图所示,晶体管的β=100,Vbe=0.7v 。

(1)求电路的静态工作点;(2) 画出微变等效电路图, 求Au 、r i 和r o ;(3)若电容Ce 开路,则将引起电路的哪些动态参数发生变化?并定性说明变化趋势.二.(15分)求图示电路中a U 、bU 、b U 、c U 及L I 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第8章存储器【8-1】填空1.按构成材料的不同,存储器可分为磁芯和半导体存储器两种。

磁芯存储器利用来存储数据;而半导体存储器利用来存储数据。

两者相比,前者一般容量较;而后者具有速度的特点。

2.半导体存储器按功能分有和两种。

3.ROM主要由和两部分组成。

按照工作方式的不同进行分类,ROM可分为、和三种。

4.某EPROM有8条数据线,13条地址线,则存储容量为。

5.DRAM 速度SRAM,集成度SRAM。

6.DRAM是RAM,工作时(需要,不需要)刷新电路;SRAM是RAM,工作时(需要,不需要)刷新电路。

7. FIFO的中文含义是。

解:1.正负剩磁,器件的开关状态,大,快。

2.ROM,RAM。

3.地址译码器,存储矩阵,固定内容的ROM 、PROM,EPROM三种。

4.213×8。

5.低于,高于。

6.动态,需要;静态,不需要。

7.先进先出数据存储器。

【8-2】图8.2是16×4位ROM,A3A2A1A0为地址输入,D3D2D1D0为数据输出,试分别写出D3、D2、D1和D0的逻辑表达式。

AAAA3 2 1 0图8.2解:⎪⎪⎪⎩⎪⎪⎪⎨⎧∑=⋅=∑==)m(0,5,9,13312,15)m(3,6,9,12100D A A D D A D【8-3】用16×4位ROM 做成两个两位二进制数相乘(A 1A 0×B 1B 0)的运算器,列出真值表,画出存储矩阵的阵列图。

解:图8.3【8-4】由一个三位二进制加法计数器和一个ROM 构成的电路如图8.4(a)所示 1.写出输出F 1、F 2和F 3的表达式;2.画出CP 作用下F 1、F 2和F 3的波形(计数器的初态为”0“)F 1F 2F 3CP(a) (b)图8.4解:1. ⎪⎪⎩⎪⎪⎨⎧⋅=⋅⋅+⋅+⋅⋅=⋅+⋅+⋅=013012012012201212011Q Q F Q Q Q Q Q Q Q Q Q F Q Q Q Q Q Q Q F2.CP F1F2F3图8.4(b )【8-5】用ROM 实现全加器。

解:0m 1m 2m 3m 4m 5m 6m 7m图8.5第9章 可编程逻辑器件及Verilog 语言【9-1】简述CPLD 与FPGA 的结构特点? 解:CPLD 采用了与或逻辑阵列加上输出逻辑单元的结构形式;而FPGA 的电路结构由若干独立的可编程逻辑模块组成,用户可以通过编程将这些模块连接成所需要的数字系统。

CPLD 属于粗粒结构,FPGA 属于细粒结构。

CPLD 是基于乘积项的可编程结构,而在FPGA 中,其基本逻辑单元LE 是由可编程的查找表(LUT ,Look-Up Table )构成的, LUT 本质上就是一个RAM 。

【9-2】简述手工设计与PLD 设计的流程? 解:答:手工设计:第一步,设计电路,画出逻辑图;第二步,选择逻辑元器件。

第三步,进行正确的连线。

PLD的设计流程:首先根据设计要求写出相应的逻辑表达式,画出设计草图,接着在计算机上利用PLD软件通过原理图输入方式或硬件描述语言(HDL)输入方式输入逻辑设计描述,经计算机仿真验证后,下载到PLD器件中,最后再通过外部实际输入输出对设计进行验证。

【9-3】用PLD器件实现的电路仿真结果如图9.4所示,请指出电路的功能。

(a)(b)(c)图9.4解:图P9.4 (a)为二选一数据选择器,图P9.4 (b) 边沿型D触发器,图P9.4 (c)为电平触发D触发器。

【9-4】Verilog语言程序清单如下,写出电路的逻辑功能,并通过QuartusII进行仿真。

module count(out,data,load,reset,clk);output[7:0] out;input[7:0] data;input load,clk,reset;reg[7:0] out;always @(posedge clk)beginif (!reset) out = 8'h00;else if (load) out = data;else out = out - 1;endendmodule解:Verilog语言程序清单如下,写出电路的逻辑功能,并通过QuartusII进行仿真。

module count(out,data,load,reset,clk);output[7:0] out;input[7:0] data;input load,clk,reset;reg[7:0] out;always @(posedge clk)beginif (!reset) out = 8'h00;else if (load) out = data;else out = out - 1;endendmodule【9-5】Verilog语言程序清单如下,写出电路的逻辑功能表,并通过QuartusII进行仿真。

module yima(A,EN,Y);output [7:0] Y;input [2:0] A;input EN;reg[7:0] Y;wire [3:0] temp={A,EN};alwayscase (temp)4'b0001 : Y=8'b00000001;4'b1001 : Y=8'b00000010;4'b0101 : Y=8'b00000100;4'b1101 : Y=8'b00001000;4'b0011 : Y=8'b00010000;4'b1011 : Y=8'b00100000;4'b0111 : Y=8'b01000000;4'b1111 : Y=8'b10000000;default : Y=8'b11111111;endcaseendmodule解:3输入8输出译码器。

仿真波形图见P9.5(a),仿真电路图见P9.5(b)。

(a)仿真波形图(b) 仿真电路图图9.5【9-6】Verilog语言程序清单如下,写出电路的逻辑功能表,并通过QuartusII进行仿真。

module bianma(Y,A);output [2:0] A;input [7:0] Y;reg [2:0] A;wire [7:0] temp=Y;alwayscase (temp)8'b00000001: A=3'b000;8'b00000010: A=3'b100;8'b00000100: A=3'b010;8'b00001000: A=3'b110;8'b00010000: A=3'b001;8'b00100000: A=3'b101;8'b01000000: A=3'b011;8'b10000000: A=3'b111;default A=3'b000;endcaseendmodule解:8输入3输出编码器。

仿真波形图见P9.6(a),仿真电路图见P9.6(b)。

(a)仿真波形图(b) 仿真电路图图P9.6【9-7】用V erilog 写出60进制计数器的程序,并进行仿真第10章 脉冲产生及变换电路【10-1】试计算图10.1中单稳态触发器74LS122的暂稳态时间,R ext =10k Ω、C ext =100nF 。

图10.1解:根据图中所给参数,暂稳态时间t wt w =0.7R ext C ext =0.7⨯10⨯103⨯100⨯10-9=0.7ms【10-2】图10.2(a )是由555定时器构成的单稳态触发电路。

1.简要说明其工作原理; 2.计算暂稳态维持时间t w3.画出在图10.2(b)所示输入u i 作用下的u C 和u O 的波形。

4.若u i 的低电平维持时间为15ms ,要求暂稳态维持时间t w 不变,应采取什么措施?+5VFμo(a) (b )u t (ms)(ms)(ms)u u图10.2解:1、工作原理(略);2、暂稳态维持时间t w =1.1RC=10ms ;3、u c 和u o 的波形如下图:u ou ct t tu i (ms)(ms)(ms)5 10 25 30 45 503.33V4若u i 的低电平维持时间为15m s ,要求暂稳态维持时间t w 不变,可加入微分电路【10-3】图10.3(a )为由555定时器和D 触发器构成的电路,请问:1.555定时器构成的是那种脉冲电路?2.在图10.3(b )中画出u c 、u 01、u 02的波形; 3.计算u 01和u 02的频率。

0.1 F tu cu u u μ(a ) (b )图10.3解:1、555定时器构成多谐振荡器2、u c, u o 1, u o 2的波形u c u o 1u o 2t t t 1.67V3.33V3、u o 1的频率f 1=1074501316..H z ⨯⨯≈ u o 2的频率f 2=158H z【10-4】由555定时器构成的电路如图10.4 (a)所示,其中CC 5V V =、S 4V U =。

回答下列问题:1. 说明由555定时器构成的电路名称。

2. 如果输入信号u i 如图10.4 (b)所示,画出电路输出u o 的波形。

V CCu o12345678555u i-+Su u o(a)(b)图10.4解:1. 该电路为555定时器构成的施密特触发器。

………………………..................…(3分)2. 由电路图可知,电路的阈值电压为TH1s 4V U U ==TH 2s 12V 2U U ==在给定输入u i 信号条件下,电路输出u o 的波形如图10.4(b)所示。

…………......…(3分)u u o图10.4(b)【10-5】由555定时器构成的施密特触发器如图10.5(a )所示。

1.在图(b )中画出该电路的电压传输特性曲线;2.如果输入u i 为图(c )的波形;所示信号,对应画出输出u O 的波形; 3.为使电路能识别出u i 中的第二个尖峰,应采取什么措施?4.在555定时器的哪个管脚能得到与3脚一样的信号,如何接法?+6Vo5(a )i (V)u o(V)tu u(b ) (c )图10.5+6Vu O5u II u /O u O u I u t(c)(a)(b)V//V/图10.5(b)解:1.见图10.5(b)所示。

2. 见图10.5(c)所示。

3. 为使电路能识别出u I 中的第二个尖峰,应使5脚接3V 左右控制电压,降低阈值。

4. 7脚,在 7脚与电源间接上拉电阻。