8位全加器的设计

8位串行全加器设计

8位串行全加器设计一.实验目的1.掌握ISE开发工具的使用,掌握FPGA开发的基本步骤;2.掌握8位串行全加器电路设计的一般办法;3.掌握程序下载的办法;4.初步了解开发板资源,掌握开发板的使用方法,重点掌握按键,开关,LCD,LED的使用方法。

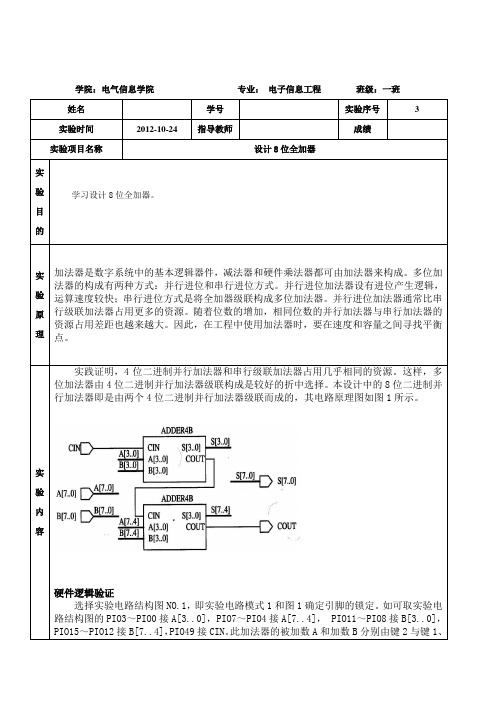

二.实验内容1.用VHDL实现8位串行全加器8位串行全加器顶层模块电路如下图所示。

图 8位串行全加器顶层模块其中a_in,b_in:数据输入,使用板上开关(S0~S15);sum_out:运算结果输出,使用LED显示运算结果。

2.将程序下载到FPGA并进行检验资源使用要求用开关(S0~S15)输入加数,被加数。

用 LED(D8~D15)显示运算结果。

三.实验步骤1.启动ISE,新建工程文件;2.编写8位串行全加器模块Hadder,其原理图如上图所示。

3.编写完加法器模块之后,在顶层文件上实现映射;4.新建UCF文件,输入位置约束;5.完成综合,实现,生成下载文件;6.连接开发板USB下载线,开启开发板电源;7.下载FPGA;8.输入数据,验证结果。

四.关键代码entity add_one isPort ( a_in : in STD_LOGIC;b_in : in STD_LOGIC;cin : in STD_LOGIC;si : out STD_LOGIC;cout : out STD_LOGIC);end add_one;architecture Behavioral of add_one isbeginsi<=(a_in xor b_in)xor cin;cout<=(a_in and b_in)or(cin and a_in)or(cin and b_in); end Behavioral;-- 一位加entity add_eight isPort ( a : in STD_LOGIC_VECTOR (7 downto 0);b : in STD_LOGIC_VECTOR (7 downto 0);sum : out STD_LOGIC_VECTOR (7 downto 0);c_out :out STD_LOGIC);end add_eight;architecture Behavioral of add_eight is component add_oneport( a_in,b_in,cin:in STD_LOGIC;si,cout:out STD_LOGIC);end component;signal c: STD_LOGIC_VECTOR (7 downto 0);signal c_in:STD_LOGIC:='0';beginu0: add_one port map(a(0),b(0),c_in,sum(0),c(0)); u1: add_one port map(a(1),b(1),c(0),sum(1),c(1)); u2: add_one port map(a(2),b(2),c(1),sum(2),c(2)); u3: add_one port map(a(3),b(3),c(2),sum(3),c(3)); u4: add_one port map(a(4),b(4),c(3),sum(4),c(4)); u5: add_one port map(a(5),b(5),c(4),sum(5),c(5)); u6: add_one port map(a(6),b(6),c(5),sum(6),c(6)); u7: add_one port map(a(7),b(7),c(6),sum(7),c_out); end Behavioral;--八位加。

EDA技术实用教程 设计8位全加器

END IF;

END PROCESS;

END BHV;

4. h_adder

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY h_adder IS

PORT ( a , b : IN STD_LOGIC ;

co, so : OUT STD_LOGIC );

component or2a

PORT ( a , b : IN STD_LOGIC ;

c : OUT STDຫໍສະໝຸດ LOGIC );END component ;

component CNT4

PORT ( CLK : IN BIT ;

Q : BUFFER INTEGER RANGE 7 DOWNTO 0);

END component ;

signal d,e,f : std_logic;

begin

u1:h_adder port map (a=>ain, b=>bin, co=>d,so=>e);

u2:h_adder port map (a=>e, b=>cin, co=>f,so=>sum);

u3:or2aport map (a=>d, b=>f, c=>cout);

ENTITY E_adder IS

PORT ( CLK1,LOAD1: IN STD_LOGIC ;

A :IN STD_LOGIC_VECTOR(7 DOWNTO 0):="00000000";

B :IN STD_LOGIC_VECTOR(7 DOWNTO 0);

COUNTOUT,E : OUT STD_LOGIC );

实验六 8位全加器的设计

实验六8位全加器的设计实验报告一、实验要求1、GW48实验箱;2、用原理图输入方式设计8位全加器,并进行编译、仿真、下载;3、总结实验步骤和实验结果。

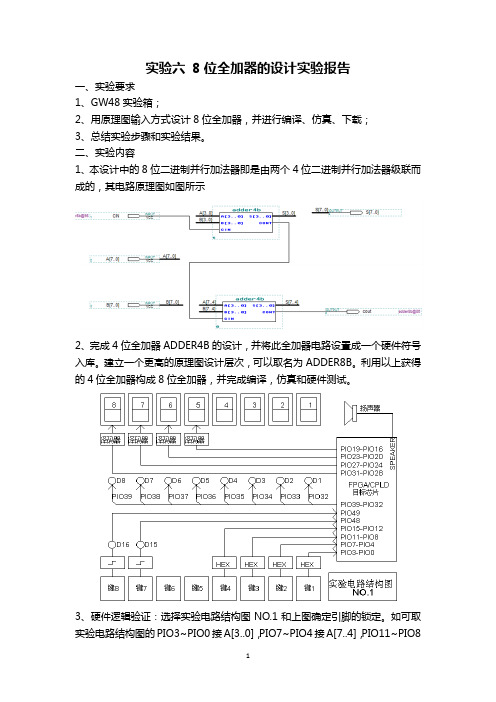

二、实验内容1、本设计中的8位二进制并行加法器即是由两个4位二进制并行加法器级联而成的,其电路原理图如图所示2、完成4位全加器ADDER4B的设计,并将此全加器电路设置成一个硬件符号入库。

建立一个更高的原理图设计层次,可以取名为ADDER8B。

利用以上获得的4位全加器构成8位全加器,并完成编译,仿真和硬件测试。

3、硬件逻辑验证:选择实验电路结构图NO.1和上图确定引脚的锁定。

如可取实验电路结构图的PIO3~PIO0接A[3..0],PIO7~PIO4接A[7..4],PIO11~PIO8接B[3..0],PIO15~PIO12接B[7..4],PIO49接CIN。

此加法器的被加数A和加数B分别由键2与键1、键4与键3输入,加法器的最低位进位CIN由键8输入,计算和S将分别通过PIO23~PIO20,PIO19~PIO16输出并显示于数码管6(高四位)和数码管5(低四位),溢出进位COUT由PIO39输出,当有进位时,结果显示于发光管D8上。

参考源程序:4位二进制并行加法器的源程序ADDER4Bmodule ADDER4B(A,B,CIN,S,CONT);output [3:0]S;output CONT;input [3:0]A,B;input CIN;assign {CONT, S}=A+B+CIN;endmodule三、实验步骤1、创建文件Max-plus->text editor源代码2、创建缺省符号(Creat Default Symbol)然后添加到框图中:3、连线并标注接口4、编译5、仿真6、下载1)引脚锁定2)开始下载四、实验结果选择实验电路结构图NO.1,此加法器的被加数A和加数B分别由键2与键1、键4与键3输入,加法器的最低位进位CIN由键8输入,当有进位时,结果显示于发光管D8上。

8位全加器课程设计报告

8位全加器课程设计报告一、课程目标知识目标:1. 学生理解8位全加器的基本概念,掌握全加器的逻辑结构和工作原理;2. 学生掌握8位全加器的电路图绘制方法,能分析并解释全加器中各个部分的作用;3. 学生了解8位全加器在计算机运算中的应用,理解其重要性。

技能目标:1. 学生能够运用所学知识,独立完成8位全加器的电路图设计;2. 学生能够运用逻辑门电路,搭建8位全加器电路,并进行功能验证;3. 学生能够通过实际操作,提高解决问题的能力和团队协作能力。

情感态度价值观目标:1. 学生培养对电子技术课程的兴趣,激发学习热情;2. 学生在学习过程中,树立正确的科学态度,注重实践,勇于创新;3. 学生通过团队合作,培养沟通与协作能力,增强集体荣誉感。

课程性质分析:本课程为电子技术课程的一部分,重点在于让学生掌握8位全加器的原理和应用,培养实际操作能力。

学生特点分析:八年级学生具有一定的电子技术基础,对电路有一定的了解,但可能对全加器的理解尚浅,需要通过具体实例和操作来加深理解。

教学要求分析:本课程要求教师以理论与实践相结合的方式进行教学,注重培养学生的实际操作能力和团队协作能力。

在教学过程中,关注学生的个体差异,给予个性化指导,确保课程目标的实现。

通过本课程的学习,学生能够达到上述具体的学习成果。

二、教学内容1. 引言:介绍全加器在数字电路中的重要性,回顾一位全加器的基本原理,引出8位全加器的研究意义。

2. 理论知识:a. 8位全加器的定义和功能;b. 8位全加器的逻辑结构,包括加法器、进位发生器和进位传递部分;c. 8位全加器的真值表和逻辑表达式。

3. 实践操作:a. 8位全加器电路图的绘制;b. 利用集成电路芯片搭建8位全加器电路;c. 电路功能测试及故障排查。

4. 应用拓展:a. 8位全加器在计算机运算中的应用案例;b. 探讨8位全加器与其他数字电路模块的组合应用。

教学大纲安排:第一课时:引言及理论知识(1、2a)第二课时:理论知识(2b、2c)第三课时:实践操作(3a、3b)第四课时:实践操作(3c)第五课时:应用拓展(4a、4b)教材章节关联:本教学内容与教材中“第十章 数字电路及其应用”相关,涉及全加器部分的内容,与教材中的理论知识和实践操作相结合,确保学生能够系统地学习和掌握8位全加器的相关知识。

8位全加器的设计

课程设计报告课程名称数字逻辑课程设计课题8位全加器的设计专业计算机科学与技术班级1202学号34姓名贺义君指导教师刘洞波陈淑红陈多2013年12月13日课程设计任务书课程名称数字逻辑课程设计课题8位全加器的设计专业班级计算机科学与技术1202学生姓名贺义君学号34指导老师刘洞波陈淑红陈多审批刘洞波任务书下达日期:2013年12月13日任务完成日期:2014年01月21日一、设计内容与设计要求1.设计内容:本课程是一门专业实践课程,学生必修的课程。

其目的和作用是使学生能将已学过的数字电子系统设计、VHDL程序设计等知识综合运用于电子系统的设计中,掌握运用VHDL或者Verilog HDL 设计电子系统的流程和方法,采用Quartus II等工具独立应该完成1个设计题目的设计、仿真与测试。

加强和培养学生对电子系统的设计能力,培养学生理论联系实际的设计思想,训练学生综合运用数字逻辑课程的理论知识的能力,训练学生应用Quartus II进行实际数字系统设计与验证工作的能力,同时训练学生进行芯片编程和硬件试验的能力。

题目一4线-16线译码器电路设计;题目二16选1选择器电路设计;题目三4位输入数据的一般数值比较器电路设计题目四10线-4线优先编码器的设计题目五8位全加器的设计题目六RS触发器的设计;题目七JK触发器的设计;题目八D触发器的设计;题目九十进制同步计数器的设计;题目十T触发器的设计;每位同学根据自己学号除以10所得的余数加一,选择相应题号的课题。

参考书目1EDA技术与VHDL程序开发基础教程雷伏容,李俊,尹霞清华大学出版社978-7-302-22416-72010TP312VH/362VHDL电路设计雷伏容清华大学出版社7-302-14226-22006TN702/1854VHDL 实用技术潘松,王国栋7-810657-81065-290-72000TP312VH/1北京理工大学7-9006257-900625-02-X1999TP312VH/35VHDL 语言100 例详解ASIC研究所人民邮电出版73.9621/W38V 6VHDL编程与仿真王毅平等7-115-08641-92000社2.设计要求:1) 课程设计报告规范课程设计报告应包含如下几个部分(1)功能描述说明设计器件的功能,包括真值表(功能表),函数表达式,逻辑电路图(2) 详细设计按照VHDL语言开发流程写出整个开发的详细过程,可以根据如下步骤适当导出程序,程序界面截图到课程设计报告对应模块。

原理图输入设计8位全加器

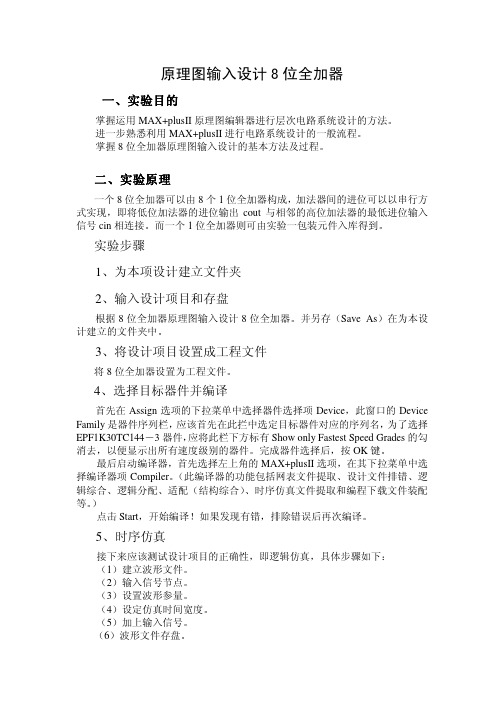

原理图输入设计8位全加器一、实验目的掌握运用MAX+plusII原理图编辑器进行层次电路系统设计的方法。

进一步熟悉利用MAX+plusII进行电路系统设计的一般流程。

掌握8位全加器原理图输入设计的基本方法及过程。

二、实验原理一个8位全加器可以由8个1位全加器构成,加法器间的进位可以以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相连接。

而一个1位全加器则可由实验一包装元件入库得到。

实验步骤1、为本项设计建立文件夹2、输入设计项目和存盘根据8位全加器原理图输入设计8位全加器。

并另存(Save As)在为本设计建立的文件夹中。

3、将设计项目设置成工程文件将8位全加器设置为工程文件。

4、选择目标器件并编译首先在Assign选项的下拉菜单中选择器件选择项Device,此窗口的Device Family是器件序列栏,应该首先在此拦中选定目标器件对应的序列名,为了选择EPF1K30TC144-3器件,应将此栏下方标有Show only Fastest Speed Grades的勾消去,以便显示出所有速度级别的器件。

完成器件选择后,按OK键。

最后启动编译器,首先选择左上角的MAX+plusII选项,在其下拉菜单中选择编译器项Compiler。

(此编译器的功能包括网表文件提取、设计文件排错、逻辑综合、逻辑分配、适配(结构综合)、时序仿真文件提取和编程下载文件装配等。

)点击Start,开始编译!如果发现有错,排除错误后再次编译。

5、时序仿真接下来应该测试设计项目的正确性,即逻辑仿真,具体步骤如下:(1)建立波形文件。

(2)输入信号节点。

(3)设置波形参量。

(4)设定仿真时间宽度。

(5)加上输入信号。

(6)波形文件存盘。

(7)运行仿真器。

选择MAX+plusII项及其中的仿真器Simulator选项,点击跳出的仿真器窗口中的Start键。

(注意,刚进入窗口时,应该将最下方的滑标拖向最左侧,以便可观察到初始波形)。

8位二进制全加器设计实验报告

EDA技术8位二进制全加器设计实验报告班级:学号:姓名:时间:2013-12-06目录方法一:自己写程序 (2)一、设计原理 (2)二、实验程序 (3)程序1:半加器描述 (3)程序2:一位二进制全加器设计顶层描述 (3)程序3:D触发器描述 (4)程序4:8位二进制加法器顶层描述 (4)三、编译及仿真结果 (9)方法二:使用LPM创立元件 (10)一、打开MegaWizard Plug-In Manager (10)二、按照提示,一步步完成全加器/全减器的创建 (10)三、创建成功,生成CMP文件 (10)四、调用CMP文件,例化元件,生成可以使用的元件。

(10)实验总结: (12)摘要我在本实验中用顶层设计思想,用半加器、全加器、D触发器例化出八位全加器,完成了八路加法器、寄存器/锁存器的设计,上升沿触发,使用了6个数码管,分别用于显示输入A,输入B和输出,输出结果也用红灯进行了显示,溢出用绿灯表示。

输入A用0~7号开关完成,输入B用10~17号开关完成,进位C 用8号开关完成。

实验要求完成八路全加器的设计,十六进制输出,上升沿触发,低电平复位,输入输出用数码管显示,用红灯显示输出,绿灯显示溢出。

方法一:自己写程序一、设计原理先写一个半加器,然后用两个半加器例化出一个全加器,再用八个全加器例化出一个八位全加器。

原理如图。

关于上升沿触发,使用D触发器和八位全加器进行例化,D触发器接同一个时钟。

最终完成上升沿触发的八位全加器的设计。

二、实验程序程序1:半加器描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY h_adder ISPORT (A, B : IN STD_LOGIC;CO, SO : OUT STD_LOGIC );END ENTITY h_adder;ARCHITECTURE FH1 OF h_adder ISBEGINSO <= NOT (A XOR (NOT B));CO <= A AND B;END ARCHITECTURE FH1;程序2:一位二进制全加器设计顶层描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY f_adder ISPORT (AIN, BIN, CIN : IN STD_LOGIC;COUT, SUM : OUT STD_LOGIC );END ENTITY f_adder;ARCHITECTURE FD1 OF f_adder ISCOMPONENT h_adder ISPORT (A, B : IN STD_LOGIC;CO, SO : OUT STD_LOGIC );END COMPONENT;SIGNAL D, E, F : STD_LOGIC;3BEGINU1 : h_adder PORT MAP(A => AIN, B => BIN, CO => D, SO => E);U2 : h_adder PORT MAP(A => E, B => CIN, CO => F, SO => SUM);COUT <= D OR F;END ARCHITECTURE FD1;程序3:D触发器描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DEF1 ISPORT (CLK : IN STD_LOGIC;D : IN STD_LOGIC;Q : OUT STD_LOGIC);END;ARCHITECTURE bhv OF DEF1 ISSIGNAL Q1 :STD_LOGIC;BEGINPROCESS (CLK)BEGINIF CLK'EVENT AND CLK = '1'THEN Q1<=D;END IF;Q<=Q1;END PROCESS;END bhv;程序4:8位二进制加法器顶层描述LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY f_adder8 ISPORT ( AIN, BIN : IN STD_LOGIC_VECTOR(7 DOWNTO 0);ASEGIN1,ASEGIN2, BSEGIN1,BSEGIN2 : BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0);CIN : IN STD_LOGIC;CLK : IN STD_LOGIC;SUM : BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0);SEG1 : BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0);SEG2 : BUFFER STD_LOGIC_VECTOR(6 DOWNTO 0);COUT : OUT STD_LOGIC );END f_adder8;ARCHITECTURE ONE OF f_adder8 ISCOMPONENT f_adder ISPORT (AIN, BIN, CIN : IN STD_LOGIC;COUT, SUM : OUT STD_LOGIC );END COMPONENT;COMPONENT DEF1 ISPORT (CLK : IN STD_LOGIC;D : IN STD_LOGIC;Q : OUT STD_LOGIC);END COMPONENT;SIGNAL C,C1, C2, C3,C4,C5,C6,C7: STD_LOGIC;SIGNAL a : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL b : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL s : STD_LOGIC_VECTOR(7 DOWNTO 0);SIGNAL ss : STD_LOGIC_VECTOR(3 DOWNTO 0);SIGNAL sss : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINU1 : f_adder PORT MAP(AIN => a(0), BIN => b(0), CIN => CIN, SUM => s(0),COUT => C1);U2 : f_adder PORT MAP(AIN => a(1), BIN => b(1), CIN => C1, SUM => s(1),COUT => C2);U3 : f_adder PORT MAP(AIN => a(2), BIN => b(2), CIN => C2, SUM => s(2),COUT => C3);U4 : f_adder PORT MAP(AIN => a(3), BIN => b(3), CIN => C3, SUM => s(3),COUT => C4);U5 : f_adder PORT MAP(AIN => a(4), BIN => b(4), CIN => C4, SUM => s(4),COUT => C5);U6 : f_adder PORT MAP(AIN => a(5), BIN => b(5), CIN => C5, SUM => s(5),COUT => C6);U7 : f_adder PORT MAP(AIN => a(6), BIN => b(6), CIN => C6, SUM => s(6),COUT => C7);U8 : f_adder PORT MAP(AIN => a(7), BIN => b(7), CIN => C7, SUM => s(7),COUT => C);U9 : DEF1 PORT MAP(Q=>a(0),D=>AIN(0),CLK=>CLK);U10 : DEF1 PORT MAP(Q=>a(1),D=>AIN(1),CLK=>CLK);U11 : DEF1 PORT MAP(Q=>a(2),D=>AIN(2),CLK=>CLK);U12 : DEF1 PORT MAP(Q=>a(3),D=>AIN(3),CLK=>CLK);U13 : DEF1 PORT MAP(Q=>a(4),D=>AIN(4),CLK=>CLK);U14 : DEF1 PORT MAP(Q=>a(5),D=>AIN(5),CLK=>CLK);U15 : DEF1 PORT MAP(Q=>a(6),D=>AIN(6),CLK=>CLK);U16 : DEF1 PORT MAP(Q=>a(7),D=>AIN(7),CLK=>CLK);5U17 : DEF1 PORT MAP(Q=>b(0),D=>BIN(0),CLK=>CLK); U18 : DEF1 PORT MAP(Q=>b(1),D=>BIN(1),CLK=>CLK); U19 : DEF1 PORT MAP(Q=>b(2),D=>BIN(2),CLK=>CLK); U20 : DEF1 PORT MAP(Q=>b(3),D=>BIN(3),CLK=>CLK); U21 : DEF1 PORT MAP(Q=>b(4),D=>BIN(4),CLK=>CLK); U22 : DEF1 PORT MAP(Q=>b(5),D=>BIN(5),CLK=>CLK); U23 : DEF1 PORT MAP(Q=>b(6),D=>BIN(6),CLK=>CLK); U24 : DEF1 PORT MAP(Q=>b(7),D=>BIN(7),CLK=>CLK);U25 : DEF1 PORT MAP(Q=>SUM(0),D=>s(0),CLK=>CLK); U26 : DEF1 PORT MAP(Q=>SUM(1),D=>s(1),CLK=>CLK); U27 : DEF1 PORT MAP(Q=>SUM(2),D=>s(2),CLK=>CLK); U28 : DEF1 PORT MAP(Q=>SUM(3),D=>s(3),CLK=>CLK); U29 : DEF1 PORT MAP(Q=>SUM(4),D=>s(4),CLK=>CLK); U30 : DEF1 PORT MAP(Q=>SUM(5),D=>s(5),CLK=>CLK); U31 : DEF1 PORT MAP(Q=>SUM(6),D=>s(6),CLK=>CLK); U32 : DEF1 PORT MAP(Q=>SUM(7),D=>s(7),CLK=>CLK);U33 : DEF1 PORT MAP(Q=>COUT,D=>C,CLK=>CLK);PROCESS(CLK,AIN,BIN)VARIABLE sSeg1 : STD_LOGIC_VECTOR(7 DOWNTO 0);VARIABLE sSeg2 : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINss(3 DOWNTO 0)<=SUM(3 DOWNTO 0);sss(3 DOWNTO 0)<=SUM(7 DOWNTO 4);sSeg1(7 DOWNTO 0):= AIN(7 DOWNTO 0);sSeg2(7 DOWNTO 0):= BIN(7 DOWNTO 0);CASE ss ISWHEN "0000" => SEG1 <= "";--0WHEN "0001" => SEG1 <= "";WHEN "0010" => SEG1 <="";WHEN "0011" => SEG1 <="";WHEN "0100" => SEG1 <="";WHEN "0101" => SEG1 <="";WHEN "0110" => SEG1 <="";WHEN "0111" => SEG1 <="";WHEN "1000" => SEG1 <="";WHEN "1001" => SEG1 <=""; --9WHEN "1010" => SEG1 <="";WHEN "1011" => SEG1 <="";WHEN "1100" => SEG1 <="";WHEN "1101" => SEG1 <="";WHEN "1110" => SEG1 <="";WHEN "1111" => SEG1 <="";WHEN OTHERS =>NULL;END CASE;CASE sss ISWHEN "0000" => SEG2 <= "";--0WHEN "0001" => SEG2 <= "";WHEN "0010" => SEG2 <="";WHEN "0011" => SEG2 <="";WHEN "0100" => SEG2 <="";WHEN "0101" => SEG2 <="";WHEN "0110" => SEG2 <="";WHEN "0111" => SEG2 <="";WHEN "1000" => SEG2 <="";WHEN "1001" => SEG2 <=""; --9WHEN "1010" => SEG2 <="";WHEN "1011" => SEG2 <="";WHEN "1100" => SEG2 <="";WHEN "1101" => SEG2 <="";WHEN "1110" => SEG2 <="";WHEN "1111" => SEG2 <="";WHEN OTHERS =>NULL;END CASE;CASE sSeg1(3 DOWNTO 0) ISWHEN "0000" => ASEGIN1 <= "";--0WHEN "0001" => ASEGIN1 <= "";WHEN "0010" => ASEGIN1 <="";WHEN "0011" => ASEGIN1 <="";WHEN "0100" => ASEGIN1 <="";WHEN "0101" => ASEGIN1 <="";WHEN "0110" => ASEGIN1 <="";WHEN "0111" => ASEGIN1<="";WHEN "1000" => ASEGIN1 <="";WHEN "1001" => ASEGIN1 <=""; --9WHEN "1010" => ASEGIN1 <="";WHEN "1011" => ASEGIN1 <="";WHEN "1100" => ASEGIN1 <="";WHEN "1101" => ASEGIN1 <="";WHEN "1110" => ASEGIN1 <="";WHEN "1111" => ASEGIN1 <="";WHEN OTHERS =>NULL;END CASE;7CASE sSeg1(7 DOWNTO 4) ISWHEN "0000" => ASEGIN2 <= "";--0 WHEN "0001" => ASEGIN2 <= "";WHEN "0010" => ASEGIN2 <="";WHEN "0011" => ASEGIN2 <="";WHEN "0100" => ASEGIN2 <="";WHEN "0101" => ASEGIN2 <="";WHEN "0110" => ASEGIN2 <="";WHEN "0111" => ASEGIN2<="";WHEN "1000" => ASEGIN2 <="";WHEN "1001" => ASEGIN2 <=""; --9 WHEN "1010" => ASEGIN2 <="";WHEN "1011" => ASEGIN2 <="";WHEN "1100" => ASEGIN2 <="";WHEN "1101" => ASEGIN2 <="";WHEN "1110" => ASEGIN2 <="";WHEN "1111" => ASEGIN2 <="";WHEN OTHERS =>NULL;END CASE;CASE sSeg2(3 DOWNTO 0) ISWHEN "0000" => BSEGIN1 <= "";--0 WHEN "0001" => BSEGIN1 <= "";WHEN "0010" => BSEGIN1 <="";WHEN "0011" => BSEGIN1 <="";WHEN "0100" => BSEGIN1 <="";WHEN "0101" => BSEGIN1 <="";WHEN "0110" => BSEGIN1 <="";WHEN "0111" => BSEGIN1<="";WHEN "1000" => BSEGIN1 <="";WHEN "1001" => BSEGIN1 <=""; --9 WHEN "1010" => BSEGIN1 <="";WHEN "1011" => BSEGIN1 <="";WHEN "1100" => BSEGIN1 <="";WHEN "1101" => BSEGIN1 <="";WHEN "1110" => BSEGIN1 <="";WHEN "1111" => BSEGIN1 <="";WHEN OTHERS =>NULL;END CASE;CASE sSeg2(7 DOWNTO 4) ISWHEN "0000" => BSEGIN2 <= "";--0 WHEN "0001" => BSEGIN2 <= "";WHEN "0010" => BSEGIN2 <="";WHEN "0011" => BSEGIN2 <="";WHEN "0100" => BSEGIN2 <="";WHEN "0101" => BSEGIN2 <="";WHEN "0110" => BSEGIN2 <="";WHEN "0111" => BSEGIN2<="";WHEN "1000" => BSEGIN2 <="";WHEN "1001" => BSEGIN2 <=""; --9WHEN "1010" => BSEGIN2 <="";WHEN "1011" => BSEGIN2 <="";WHEN "1100" => BSEGIN2 <="";WHEN "1101" => BSEGIN2 <="";WHEN "1110" => BSEGIN2 <="";WHEN "1111" => BSEGIN2 <="";WHEN OTHERS =>NULL;END CASE;END PROCESS;--U1 : f_adder PORT MAP(AIN => AIN(0), BIN => BIN(0), CIN => CIN, SUM => SUM(0), COUT => C1);--U2 : f_adder PORT MAP(AIN => AI N(1), BIN => BIN(1), CIN => C1, SUM => SUM(1), COUT => C2);--U3 : f_adder PORT MAP(AIN => AIN(2), BIN => BIN(2), CIN => C2, SUM => SUM(2), COUT => C3);--U4 : f_adder PORT MAP(AIN => AIN(3), BIN => BIN(3), CIN => C3, SUM => SUM(3), COUT => C4);--U5 : f_adder PORT MAP(AIN => AIN(4), BIN => BIN(4), CIN => C4, SUM => SUM(4), COUT => C5);--U6 : f_adder PORT MAP(AIN => AIN(5), BIN => BIN(5), CIN => C5, SUM => SUM(5), COUT => C6);--U7 : f_adder PORT MAP(AIN => AIN(6), BIN => BIN(6), CIN => C6, SUM => SUM(6), COUT => C7);--U8 : f_adder PORT MAP(AIN => AIN(7), BIN => BIN(7), CIN => C7, SUM => SUM(7), COUT => COUT);END ONE;三、编译及仿真结果程序波形仿真图9时间分析方法二:使用LPM创立元件一、打开MegaWizard Plug-In Manager二、按照提示,一步步完成全加器/全减器的创建三、创建成功,生成CMP文件四、调用CMP文件,例化元件,生成可以使用的元件。

8位串行全加器设计

8位串行全加器设计串行全加器是一种基本的数字电路,用于实现两个二进制数的加法运算。

它可以将两个数位相同的二进制数相加,并将其和以及进位输出。

本文将详细介绍如何设计一个8位串行全加器。

首先,我们需要了解全加器的功能。

全加器由两个输入和两个输出组成。

输入包括两个要相加的二进制数位以及前一位的进位(Carry In),输出包括当前位的和(Sum)和当前位的进位(Carry Out)。

设计一个8位串行全加器时,我们需要将8个全加器连接在一起。

每个全加器的输入为两个二进制数位和前一位的进位,输出为当前位的和和当前位的进位。

具体设计步骤如下:1.首先,我们需要设计一个单个全加器电路。

全加器电路可以通过将两个半加器连在一起来实现。

半加器接收两个输入,并输出当前位的和和当前位的进位。

2.设计一个半加器电路。

半加器电路由两个输入和两个输出组成。

输入包括两个要相加的二进制数位,输出包括当前位的和和当前位的进位。

3.实现半加器电路的真值表。

半加器的真值表如下:输入A,输入B,输出S,进位--------,--------,--------,-------0,0,0,0,1,1,1,0,1,1,1,0,根据真值表可知,半加器的和输出为输入A和输入B的异或运算结果,进位输出为输入A和输入B的与运算结果。

4.通过使用逻辑门来实现半加器电路。

可以使用异或门实现和输出,使用与门实现进位输出。

5.设计一个完整的全加器电路。

一个全加器电路由一个半加器和一个或门构成。

半加器负责计算两个输入位的和和进位,而或门负责计算前一位的进位和当前位的进位的和。

全加器电路的输入为两个要相加的二进制数位和前一位的进位,输出为当前位的和和当前位的进位。

6.将8个全加器连在一起。

将第一个全加器的输入连接到待相加的两个8位二进制数的最低位和前一位的进位,将第二个全加器的输入连接到待相加的两个8位二进制数的次低位和第一个全加器的进位,以此类推。

最后一个全加器的输出即为所求的和。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计报告课程名称数字逻辑课程设计课题8位全加器的设计专业计算机科学与技术班级1202学号34姓名贺义君指导教师刘洞波陈淑红陈多2013年12月13日课程设计任务书课程名称数字逻辑课程设计课题8位全加器的设计专业班级计算机科学与技术1202学生姓名贺义君学号34指导老师刘洞波陈淑红陈多审批刘洞波任务书下达日期:2013年12月13日任务完成日期:2014年01月21日一、设计内容与设计要求1.设计内容:本课程是一门专业实践课程,学生必修的课程。

其目的和作用是使学生能将已学过的数字电子系统设计、VHDL程序设计等知识综合运用于电子系统的设计中,掌握运用VHDL或者Verilog HDL设计电子系统的流程和方法,采用Quartus II等工具独立应该完成1个设计题目的设计、仿真与测试。

加强和培养学生对电子系统的设计能力,培养学生理论联系实际的设计思想,训练学生综合运用数字逻辑课程的理论知识的能力,训练学生应用Quartus II进行实际数字系统设计与验证工作的能力,同时训练学生进行芯片编程和硬件试验的能力。

题目一4线-16线译码器电路设计;题目二16选1选择器电路设计;题目三4位输入数据的一般数值比较器电路设计题目四10线-4线优先编码器的设计题目五8位全加器的设计题目六RS触发器的设计;题目七JK触发器的设计;题目八D触发器的设计;题目九十进制同步计数器的设计;题目十T触发器的设计;每位同学根据自己学号除以10所得的余数加一,选择相应题号的课题。

参考书目1 EDA技术与VHDL程序开发基础教程雷伏容,李俊,尹霞清华大学出版社978-7-302-22416-7201TP312VH/362 VHDL电路设计雷伏容清华大学出版社7-302-14226-2 2006 TN702/1853 VHDL电路设计技术王道宪贺名臣刘伟国防工业出版社7-118-03352-9 2004 TN702/624 VHDL 实用技术潘松,王国栋7-81065 7-81065-290-7 2000 TP312VH/15 VHDL语言100例详解北京理工大学ASIC研究所7-900625 7-900625-02-X1999TP312VH/36 VHDL编程与仿真王毅平等人民邮电出版社7-115-08641-9200073.9621/W38V7 VHDL程序设计教程邢建平曾繁泰清华大学出版社7-302-11652-02005TP312VH/27/32.设计要求:1) 课程设计报告规范课程设计报告应包含如下几个部分(1)功能描述说明设计器件的功能,包括真值表(功能表),函数表达式,逻辑电路图(2) 详细设计按照VHDL语言开发流程写出整个开发的详细过程,可以根据如下步骤适当导出程序,程序界面截图到课程设计报告对应模块。

基本设计流程如下:①工程管理:新建工程,工程管理;②源文件输入:VHDL程序或者原理图的设计,内嵌模块的调用;③综合、编译:检查语法,连接错误,生成综合后网表;④功能仿真:综合后的功能仿真;⑤简单约束:管脚分配,I/O特性约束,简单的时序约束;⑥全编译:软件自动完成布局布线,生成最终编程文件;⑦时序仿真:带延时的和实际情况非常接近的时序仿真;⑧编程:下载到硬件当中。

(3)调试分析以及设计体会①仿真或程序下载调试(附界面截图)。

②设计过程中遇到的问题以及解决问题的方法。

③课程设计过程经验教训、心得体会。

(4)书写格式见附带说明。

(5) 附录①参考书目②源程序清单(带注释)2) 考核方式指导老师负责验收程序的运行结果,并结合学生的工作态度、实际动手能力、创新精神和设计报告等进行综合考评,并按优秀、良好、中等、及格和不及格五个等级给出每位同学的课程设计成绩。

具体考核标准包含以下几个部分:(1)平时出勤 (占10%)(2)系统需求分析、功能设计、数据结构设计及程序总体结构合理与否(占10%)(3)程序能否完整、准确地运行,个人能否独立、熟练地调试程序(占40%)(4)设计报告(占30%)(5)注意:不得抄袭他人的报告(或给他人抄袭),一旦发现,成绩为零分。

(6)独立完成情况(占10%)。

3) 课程设计验收要求(1)运行所设计的系统。

(2)回答有关问题。

(3)提交课程设计报告纸质稿。

(4)提交源程序或设计报告文档电子稿。

(5)依内容的创新程度,完善程序情况及对程序讲解情况打分。

二、进度安排上机时间、地点:16 周周二下午E410/41316 周周二下午E413/41416 周周三下午E414/606附带说明:1.课程设计报告装订顺序:封面、任务书、目录、正文、评分、附件(程序清单)。

2.正文的格式:一级标题用3号黑体,二级标题用四号宋体加粗,正文用小四号宋体;行距为22。

3.正文的内容:一、课题的主要功能;二、详细设计;三、程序调试;四、总结;五、附件(所有程序的原代码,要求对程序写出必要的注释)。

4.正文总字数要求在5000字以上(不含程序原代码)。

目录(1)功能描述……………………………………………………………………………………………………1(2)详细设计……………………………………………………………………………………………………3.(3)调试分析与设计体会………………………………………………………………………………10(4)书写格式……………………………………………………………………………………………………13(5)附录……………………………………………………………………………………………………………14(1)功能描述1.1全加器介绍全加器是能够计算低位进位的二进制加法电路。

一位全加器(FA)的逻辑表达式为:S=A⊕B⊕Cin Co=AB+BCin+ACin其中A,B为要相加的数,Cin为进位输入;S为和,Co是进位输出;ﻫ如果要实现多位加法可以进行级联,就是串起来使用;比如8位全加器,就需要8个全加器;这种级联就是串行结构速度慢,如果要并行快速相加可以用超前进位加法,如果将全加器的输入置换成A和B的组合函数Xi和Y(S0…S3控制),然后再将X,Y和进位数通过全加器进行全加,就是ALU的逻辑结构结构。

即X=f(A,B)Y=f(A,B)不同的控制参数可以得到不同的组合函数,因而能够实现多种算术运算和逻辑运算。

1.2真值表:1.3函数表达式Si=Ai⊕Bi⊕Ci-1Ci=AiBi+Ci-1(Ai⊕Bi)1.4逻辑电路图(2)详细设计按照VHDL语言开发流程写出整个开发过程,可以根据如下步骤适当导出程序,程序界面截图到课程设计报告对应模块。

2.1新建工程管理2.2输入文本语言程序2.3编译2.4选择波形编辑器2.5对应节点2.6形成综合编译后网表2.7进行仿真调试2.8生成波形图2.9配置管脚(3)调试分析与设计体会3.1调试分析在编辑好程序代码完成后,编译结果如图:图3.1编译结果虽然有警告,当时不碍事,继续运行代码,查看表编译分析结果,如图:图3.2 结果分析程序运行正常,没有大的错误。

3.2分析设计过程中遇到的问题以及解决问题的方法。

设计过程中遇到的主要困难就是源程序不会写,因为我们根本没有学过VHDL这门程序语言,即使在网上搜索的或图书馆找的的源程序,一旦出现错误,也很难自己改正。

其次,就是对QuartusII软件应用不熟悉,全英文式的操作界面,让这个英语很菜的我用的很费劲,有有时操作到一半,竟不知下一步该怎么弄,又得去看教材或问同学,花费了很多时间。

对于出现的这些问题,我会先查查资料,理解实验的具体信息,不懂的地方问同学或上网查资料。

看看VHDL,理解源程序的组成,以便出现错误时能够自我改正。

对于软件应用的不熟习,进行反复操作,增加熟练度。

3.3课程设计过程经验教训、心得体会。

通过这次课程设计,加强了我们动手、思考和解决问题的能力。

在整个设计过程中,我设计了数字逻辑中八位全加器的设计。

在设计过程中,经常会遇到这样那样的情况,就是对于VHDL中源代码中出现的错误不会改正,还有就是对Quartus II应用的不熟悉,有时竟忘了下一步该怎么操作,又得去查阅资料或阅读教材,因此耗费在这上面的时间用去很多。

我觉得做课程设计同时也是对课本知识的巩固和加强,由于课本上的知识太多,平时课间的学习并不能很好的理解和运用设计程序的功能,而且我们并没有学习VHDL这门程序语言,因此给课程设计造成了很大的困难。

平时看课本时,有时问题老是弄不懂,做完课程设计,那些问题就迎刃而解了,而且还可以记住很多东西,映象深刻。

经过几天的上机操作,过程曲折可谓一语难尽。

在此期间我们也失落过,也曾一度热情高涨。

从开始时满富盛激情到最后汗水背后的复杂心情,点点滴滴无不令我回味无长。

生活就是这样,汗水预示着结果也见证着收获。

劳动是人类生存生活永恒不变的话题。

通过实习,我才真正领略到“艰苦奋斗”这一词的真正含义,我才意识到老一辈电子设计为我们的社会付出。

我想说,设计确实有些辛苦,但苦中也有乐,在如今单一的理论学习中,很少有机会能有实践的机会,但我们可以在一起讨论、研究,相互帮助,配合默契,多少人间欢乐在这里洒下,大学里一年的相处还赶不上这几天的合作,我感觉我和同学们之间的距离更加近了;我想说,确实很累,但当我们看到自己所做的成果时,心中也不免产生兴奋; 正所谓“三百六十行,行行出状元”。

我们同样可以为社会作出我们应该做的一切,这有什么不好?我们不断的反问自己。

也许有人不喜欢这类的工作,也许有人认为设计的工作有些枯燥,但我们认为无论干什么,只要人生活的有意义就可。

社会需要我们,我们也可以为社会而工作。

既然如此,那还有什么必要失落呢?于是我们决定沿着自己的路,执着的走下去。

同时我认为我们的工作是一个团队的工作,团队需要个人,个人也离不开团队,必须发扬团结协作的精神。

某个人的离群都可能导致导致整项工作的失败。

实习中只有一个人知道原理是远远不够的,必须让每个人都知道,否则一个人的错误,就有可能导致整个工作失败。

团结协作是我们实习成功的一项非常重要的保证。

而这次实习也正好锻炼我们这一点,这也是非常宝贵的。

对我们而言,知识上的收获重要,精神上的丰收更加可喜。

挫折是一份财富,经历是一份拥有。

这次实习必将成为我人生旅途上一个非常美好的回忆。

通过这次课程设计使我懂得了理论与实际相结合是很重要的,只有理论知识是远远不够的,只有把所学的理论知识与实践相结合起来,从理论中得出结论,才能真正为社会服务,从而提高自己的实际动手能力和独立思考的能力。

在设计的过程中遇到问题,可以说得是困难重重,这毕竟第一次做的,难免会遇到过各种各样的问题,同时在设计的过程中发现了自己的不足之处,对以前所学过的知识理解得不够深刻,掌握得不够牢固。