基于FPGA的PS2键盘控制器设计

FPGA实验十一 PS2键盘控制LCD显示实验

高性能软件无线电平台X6-面向高性能SoC验证和科学仿真主要特性支持PCI Express® Gen2 ×8 (但IP另配)搭载DDR3 SDRAM SO-DIMM系统搭载FMC连接器,可使用大部分RocketI/O(GTX)利用FMC可选基板能够对应各种接口提供PCI Express和DMA等参考设计无限扩展行业应用下一代软件无线电平台微软研究院软件无线电(Sora)是一种新型基于PC 的可编程无线电平台架构。

Sora 结合了可编程性和通用处理器(GPP )平台的性能和灵活性,同时使用的硬件和软件技术,以满足高性能的无线通信算法的计算挑战。

Sora 平台提供 Soft WiFi 开源代码。

SoftWiFi 目前支持率的802.11a/b/g 全部协议,无缝地与商业802.11网卡实现互操作,并达到商业网卡相当的性能。

Sora 是第一平台真正的软件无线电平台,支持用户开发的802.11a/b/g ,如物理层和MAC ,软件完全是标准PC 架构。

典型应用: White Spaces Mobile Phones Public Safety Radio Land MobileBroadcast TV and FM Radio Satellite navigationCovers 6 Amateur Radio Bands 射频部分主要特性: Dull-duplex Transceiver50 MHz to 5.8 GHz coverage50-100mW (17-20dBm) from 50 MHz to 1.2 GHz 30-70mW (15-18dBm) from 1.2 GHz to 2.2 GHz25+ dB Output power control range under software control Receive Specs:Noise figure of 5-7 dBIIP3 of 5-10 dBm;IIP2 of 40-55 dBm全频带射频收发模块实验十一 PS/2键盘显示LCD 实验一 实验目的1掌握PS/2键盘控制端口协议;2通过编写程序实现PS/2键盘控制LCD 的显示。

基于FPGA的PS2键盘鼠标控制电子琴

XX制造职业技术学院信息工程系08级毕业论文姓名:江太平班级:08通信电子设计题目:基于FPGA的PS/2键盘鼠标控制电子琴指导教师:**二〇一一年五月目录第一章FPGA简介1.1 FPGA背景1.2 FPGA芯片结构1.3 FPGA的基本特点第二章FPGA工作原理2.1 查找表(Look-Up-Table)的原理与结构2.2FPGA工作原理第三章PS2键盘通信3.1PS2 背景3.2PS2键盘通信3.3VGA原理第四章PS2键盘控制模型电子琴顶层电路的设计4.1 PS2键盘控制电子琴程序结论、参考文献第一章 FPGA简介1.1 FPGA背景FPGA主要生产厂商1、Altera2、Xilinx3、Actel4、Lattice其中Altera作为世界老牌可编程逻辑器件的厂家,是当前世界X围内市场占有率最大的厂家,它和Xilinx主要生产一般用途FPGA,其主要产品采用RAM工艺。

Actel主要提供非易失性FPGA,产品主要基于反熔丝工艺和FLASH工艺。

目前以硬件描述语言(Verilog 或 VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至 FPGA 上进行测试,是现代 IC 设计验证的技术主流。

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。

一个出厂后的成品FPGA 的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

FPGA一般来说比ASIC(专用集成芯片)的速度要慢,无法完成复杂的设计,而且消耗更多的电能。

但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。

FPGA基础设计_PS2键盘控制及短按、长按

FPGA基础设计_PS2键盘控制及短按、长按

PS2键盘也是一个经典的实验,可能很多人接触如何对通信协议、时序编程就是从这个实验开始学习的。

USB键盘已经很普及,现在市场上还是有一些USB转PS2的转接头,还有一些转换芯片。

这个实验虽然简单,不过不知道您有考虑过单按一次输出一个有效脉冲、短按、长按等这些是如何实现的么?这就涉及到一些时钟、边沿检测等设计问题。

PS2协议实现

我们见到的PS2的接口电路应该都是这样的:

一根时钟线、一根数据线完成通信,PS2通信的帧格式如下所示,时钟的下降沿数据有效:

按键在被按下时,会发送一个字节,这个码就是通码;按键在释放时,会发送两个字节,这个码就做断码(当然也有例外)。

每一个按键都有唯一的通码和断码,据此进行判断按下的是哪个键,从而执行对应的功能。

如一部分按键的通码和断码如下所示:

可以看出断码其实就是在通码前加了一个F0,比如A的通码是1C,则它的断码是F01C。

另外一些特殊功能的按键,在通码和断码前都会加个E0。

PS2解码的代码如下所示:

//-----------------ps2_clk下降沿捕获--------------------

//clk相当于中间采样点的作用,第一个下降沿到来说明起始位开始

reg ps2_clk0,ps2_clk1,ps2_clk2;//缓冲寄存器

wire ps2_clk_neg; //1表示检测到下降沿

reg ps2_state;

always @ (posedge clk or negedge rst_n)

if (!rst_n)

{ps2_clk0,ps2_clk1,ps2_clk2} 《= 3‘d0;

else。

基于FPGA的标准PS_2键盘接口电路设计概要

一、引言键盘是嵌入式系统的最重要的输入设备之一,是实现人机交互的重要途径。

设计者除了可以自行设计扫描式矩阵键盘之外,还可以选择标准PS/2键盘实现人机交互。

扫描式矩阵键盘虽然电路简单,但不具有通用性,当需要使用较多的按键输入时,则会占用较多的I /O 端口,在软件上则要进行上电复位、按键扫描及通信的处理,而且还要加上按键的去抖动处理,增大了系统软、硬件的开销,开发周期较长[1]。

标准PS /2键盘由于接口通信协议简单,在系统中占用软硬件资源少,高可靠性,表达信息量大而得到了越来越广泛的应用[2]。

本文根据标准PS/2键盘的通信时序,用硬件描述语言Verilog HDL 设计了基于FPGA 的标准PS/2键盘接口,通过本设计接口,完成把键盘按键扫描码转换成字符ASCII 码过程,成功实现了标准PS/2键盘到NiosII 嵌入式CPU 的数据单向通信。

本设计具有较好的通用性和可移植性,可取代自行设计扫描式矩阵键盘而用于嵌入式系统设计中。

二、标准PS/2键盘物理接口的定义及其连接图1为标准PS/2键盘mini-DIN 连接器,标准PS/2键盘是通此连接器与外设相连接,其中,第1脚为Data(数据,第5脚为Clock(时钟,第3脚接地,第4脚接电源(5伏,第2与6脚保留。

因标准PS/2键盘输出脚是采用集电极开路设计,因此,标准PS/2键盘与接口相连时,输出要接一个上拉电阻方可使用,如图2所示。

脚1Data 脚2保留脚3接地脚4接电源脚5Clock 脚6保留图1标准PS/2键盘mini-DIN 连接器图2标准PS/2键盘与接口的连接三、标准PS/2键盘数据输出通信协议[3]图3为标准PS/2键盘数据输出短帧格式,当PS/2键盘要发数据时,首先要检查Clock 时钟脚的电压情况,如电压为低电平,则表示主机抑制了通信,如电压为高电平,PS/2键盘获得发送数据的控制权。

首先发送短帧数据格式的起始位(低电平,然后才发送数据(低位先发送,跟着发送奇校验位,最后才发送帧数据格式的停止位。

基于VHDL利用PS_2键盘控制的密码锁设计_胡彩霞

《》2011年第5期在传统的数字电路设计实验中,如果要构建一个小型数字系统,通常要在数字电路试验箱中进行繁琐的搭线操作。

由于试验箱资源的限制使得所设计的数字系统功能会受到很大限制。

而FPGA 由于其集成度高和支持可在线编程的特点,修改电路设计变得如同修改程序一样方便[1]。

本文以电子密码锁的设计为实例,介绍了利用硬件编程语言VHDL 自顶向下地进行此系统的行为描述与结构设计,并介绍了PS/2键盘到主机的单向通信过程。

该设计中所用芯片的具体型号是XILINX 公司的具有40万门、208个管脚的SPARTAN XC3S400。

设计过程中下载模式采用主串模式,将程序下载到开发板上的EPROM 中,再由FPGA 将EPROM 中的程序读入片内编程RAM 中。

采用的EDA 开发工具为ISE 6,仿真工具是Modelsim 5.8a 。

1.数字密码锁的基本功能1.1功能描述:密码锁的设计主要达到以下四个功能:(1)密码锁加密:按下F1加密键,再按下0到9中的任四位数字作为密码。

(2)输入码激活:按下F2激活键,将已输入的四位数码作为密码或解锁码。

(3)解锁:按下F5解密键,输入的解锁码会与原密码会进行匹配。

如果成功,则开启密码锁;如果不成功,可继续解码,共有3次解密机会,当3次解密都不成功时,蜂鸣器产生报警信号宣告操作失败。

(4)数码输入:只有在按下F1加密键或F5解密键的前提下,按下0到9的数值才能显示到数码管上。

显示顺序是:随机按下的数码首先显示在四位数码管的最低位上,若确定此数码是想要的数码,再按下ENTER 键,便将此数码向左移动至左边第一个未显示的数码管上。

比如,初始时数码管显示为“XXXX ”(X 表示什么都不显示),按下一个9后,显示的是“XXX9”,再按下ENTER 键后,显示为“9XXX ”。

当输入的数码已达四位数时,按下F2激活键,便可将这四位数作为密码。

由于开发板上只有4个数码管,所以密码设定为4位,在实际中为了增加安全性,可以设置为更多位,还可将字母键扩展为密码。

基于FPGA 的PS2鼠标控制器设计概要

基于FPGA 的PS/2 鼠标控制器设计1 PS/2介绍PS/2 接口作为传统的鼠标键盘接口已经被大部分人所熟知,虽然随着USB 接口键鼠的普及,绝大多数PC用户均选择了USB的键鼠,但目前主流PC中依旧保留了PS/2键鼠的接口,由于PS/2接口实现简单,使用方便的特点,在许多领域如工控机等仍旧采用PS/2接口来完成基本的人机交互。

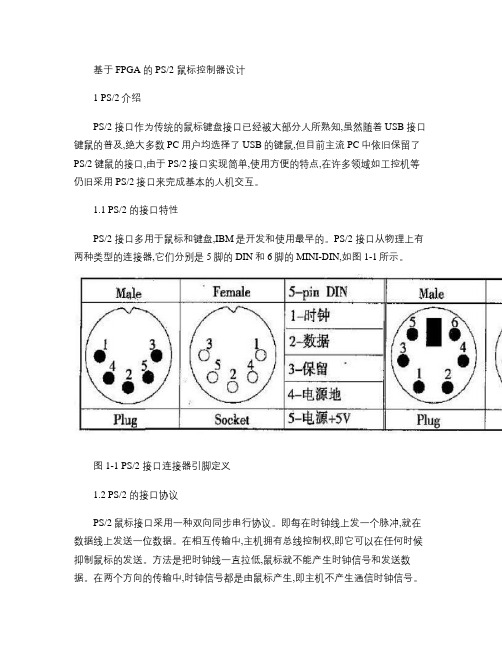

1.1 PS/2 的接口特性PS/2 接口多用于鼠标和键盘,IBM是开发和使用最早的。

PS/2 接口从物理上有两种类型的连接器,它们分别是5脚的DIN和6脚的MINI-DIN,如图1-1所示。

图1-1 PS/2 接口连接器引脚定义1.2 PS/2 的接口协议PS/2鼠标接口采用一种双向同步串行协议。

即每在时钟线上发一个脉冲,就在数据线上发送一位数据。

在相互传输中,主机拥有总线控制权,即它可以在任何时候抑制鼠标的发送。

方法是把时钟线一直拉低,鼠标就不能产生时钟信号和发送数据。

在两个方向的传输中,时钟信号都是由鼠标产生,即主机不产生通信时钟信号。

如果主机要发送数据,它必须控制鼠标产生时钟信号。

方法如下:主机首先下拉时钟线至少100μs抑制通信,然后再下拉数据线,最后释放时钟线。

通过这一时序控制鼠标产生时钟信号。

PS/2接口的鼠标一般工作在10KHz-20KHz时钟频率,不同厂家制造的鼠标工作的时钟频率不同,推荐值在15kHz左右,也就是说,Clock(时钟脚高、低电平的持续时间都为40μs。

PS/2接口分为两种通讯模式:设备到主机的通讯、主机到设备的通讯。

时序如图1-2。

当时钟为高时,设备驱动数据线改变状态,在时钟信号的下降沿数据被控制器锁存。

图1-3为主机到设备的通讯时序。

图1-2鼠标到主机的通信时序图1-3主机到的鼠标通信时序1.3 PS/2 的鼠标工作模式PS/2 鼠标有四种工作模式,它们分别为:Reset 模式:当鼠标上电或主机发复位命令给它时,进入Reset 模式;Stream 模式:这是鼠标的默认模式,当鼠标上电或复位完成后,鼠标自动进Stream 模式,鼠标大部分就是用此模式工作;Remote模式:只有当主机发送了设置命令后,鼠标才进入Remote 模式;Wrap模式:Wrap 模式只用于测试鼠标与主机连接是否正确。

课程设计基于FPGA的VGA图像汉字显示及-PS-2键盘控制设计与应用 精品

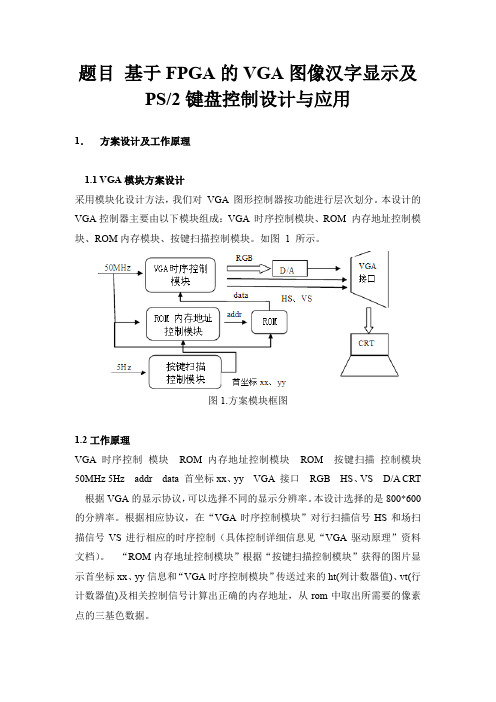

题目基于FPGA的VGA图像汉字显示及PS/2键盘控制设计与应用1.方案设计及工作原理1.1 VGA模块方案设计采用模块化设计方法,我们对VGA 图形控制器按功能进行层次划分。

本设计的VGA控制器主要由以下模块组成:VGA 时序控制模块、ROM 内存地址控制模块、ROM内存模块、按键扫描控制模块。

如图 1 所示。

图1.方案模块框图1.2工作原理VGA时序控制模块ROM内存地址控制模块ROM 按键扫描控制模块50MHz 5Hz addr data 首坐标xx、yy VGA 接口RGB HS、VS D/A CRT 根据VGA的显示协议,可以选择不同的显示分辨率。

本设计选择的是800*600的分辨率。

根据相应协议,在“VGA时序控制模块”对行扫描信号HS和场扫描信号VS进行相应的时序控制(具体控制详细信息见“VGA驱动原理”资料文档)。

“ROM内存地址控制模块”根据“按键扫描控制模块”获得的图片显示首坐标xx、yy信息和“VGA时序控制模块”传送过来的ht(列计数器值)、vt(行计数器值)及相关控制信号计算出正确的内存地址,从rom中取出所需要的像素点的三基色数据。

1.3 PS/2接口电路的工作原理PS/2协议和接口最初是IBM公司开发并推广使用的一种应用于键盘/鼠标的协议和接口,PS/2键盘按键接口是6芯的插头与PC机的键盘相连接,插头、插座定义如图所示。

键盘/鼠标接口的数据线和时钟线采用集电极开路结构,平时都是高电平当这些设备等待发送数据时,它首先检查clock是否为高。

如果为低,则认为PC抑制了通讯,此时它缓冲数据直到获得总线的控制权。

如果clock为高电平,设备则开始向PC发送数据。

一般都是由ps2设备产生时钟信号。

发送按帧格式。

数据位在clock为高电平时准备好,在clock下降沿被PC读入。

图3所示是按下Q 键的时序图“Q”键的扫描码从键盘发送到计算机(通道A是时钟信号,通道B 是数据信号)。

FPGA控制的PS2接口电路设计

FPGA控制的PS/2接口电路设计摘要:作为计算机常用的输入设备键盘,其接口通常是PS/2接口,现在也出现了USB接口的键盘。

本文是根据PS/2接口原理,使用FPGA接收键盘发送的数据,将扫描码转换成ASCII码,最后将扫描码和ASCII码显示出来。

关键词:键盘PS/2FPGA转换显示一、引言PS/2协议和接口最初是有IBM公司开发并推广使用的一种应于键盘/鼠标的协议和接口,直到现在仍被广泛使用。

PS/2键盘接口是6芯的插头与PC机连接,该接口在封装上小巧,并且使用双向串行通信协议,并且提供有可选择的第三套扫描码集,同时支持17个主机到键盘的命令。

利用FPGA和EDA技术可以根据PS/2接口的传输协议,编写VHDL程序来接收键盘发送的扫描码。

本文就是根据此方法来设计电路,将键盘发送的数据转换为ASCII码,并用7段数码管显示键盘的16进制扫描码和其所对应的16进制ASCII码,并且将扫描码和ASCII码显示在1602液晶上。

二、PS/2接口原理1、接口特性在PS/2的的6个引脚中只有4个有实际意义,它们分别是clock 时钟脚,data数据脚,+5V电源脚和Ground电源地。

如图所示:PS/2通讯协议是一种双向同步串行通讯协议。

通讯的两端通过Clock同步,并通过Data交换数据。

2、设备到主机的通信过程键盘接口的数据线和时钟线大多采用集电极开路结构,平常处于高电平。

当键盘像主机发送数据时,首先检查时钟线是否为高。

如果为低,则是主机抑制饿通讯,此时数据必须将数据缓存,直到重新获得总线的控制权(一般PS/2键盘有16个字节的缓冲区)。

如果Clock 为高电平,键盘开始将数据发送到主机。

一般都是有PS/2设备产生时钟信号,发送时按照数据帧格式顺序发送。

其中数据位在Clock 为高时准备好,在Clock的下降沿被PC读入。

下图为数据发送时序图和数据帧格式。

数据发送时序图1个起始位总是逻辑08个数据位(LSB)低位在前1个奇偶校验位奇校验1个停止位总是逻辑11个应答位仅用在主机对设备的通讯中数据帧格式三、硬件电路由于是使用FPGA控制的PS/2接口电路,因此应有一对PS/2接口分别与FPGA和键盘相接,以实现数据的发送和接收。

FPGA控制的PS2接口电路设计 毕业论文 毕业设计

FPGA控制的PS/2接口电路设计摘要:PS2作为键盘接口至今仍在广泛使用。

本论文根据PS2键盘接口的协议,用VHD语言编程,用FPGA控制PS2,使其能够接收从键盘键入的信息,并把它显示在数码管和液晶显示频上。

The Design of PS / 2 Interface Circuit by Control of FPGAAbstract:Today,PS2 keyboard interface is still being used widely.This report is based PS2 keyboard interface protocol, with VHD language programming, using FPGA control PS2, so that it can receive information from the keyboard to type, and display it in the digital frequency of the tube and liquid crystal display.关键词:VHDL,FPGA , PS2, QuartusII引言:PS2是一类应用广泛的键盘接口。

本文论述了用FPGA控制PS2的设计思想及方法,并实现把按键的扫描码及其对应的ASCII码显示在LED及LCD上。

设计原理通过分析,本次设计需要分四部分实现:1.接收从键盘发出的扫描码信息2.把接收到的扫描码转换成ASCII码3.把扫描码和ASCII码显示在数码管上4.把扫描码和ASCII码显示在LED液晶上。

1.PS2键盘接口协议介绍PS2协议和接口最初是由IBM公司开发并广泛使用的应用于键盘/鼠标的协议和接口。

PS2键盘接口是6芯的插头,各插头定义如下:在PS2的6个芯中,2和6未定义,3和4为电源和地,需要用FPGA控制的只有1(数据)和5(时钟)。

2.把从键盘发出的数据转换成扫描码每当有按键按下或弹起时键盘都会发出一帧或几帧数据,每一帧数据一共都12位,其数据格式如下表所示:从键盘发出的数据是在时钟信号的下降沿的时候才被读取,FPGA要想接收到键盘发出的数据就要配合PS2的时序。

基于FPGA的标准PS_2键盘接口电路设计概要

一、引言键盘是嵌入式系统的最重要的输入设备之一,是实现人机交互的重要途径。

设计者除了可以自行设计扫描式矩阵键盘之外,还可以选择标准PS/2键盘实现人机交互。

扫描式矩阵键盘虽然电路简单,但不具有通用性,当需要使用较多的按键输入时,则会占用较多的I /O 端口,在软件上则要进行上电复位、按键扫描及通信的处理,而且还要加上按键的去抖动处理,增大了系统软、硬件的开销,开发周期较长[1]。

标准PS /2键盘由于接口通信协议简单,在系统中占用软硬件资源少,高可靠性,表达信息量大而得到了越来越广泛的应用[2]。

本文根据标准PS/2键盘的通信时序,用硬件描述语言Verilog HDL 设计了基于FPGA 的标准PS/2键盘接口,通过本设计接口,完成把键盘按键扫描码转换成字符ASCII 码过程,成功实现了标准PS/2键盘到NiosII 嵌入式CPU 的数据单向通信。

本设计具有较好的通用性和可移植性,可取代自行设计扫描式矩阵键盘而用于嵌入式系统设计中。

二、标准PS/2键盘物理接口的定义及其连接图1为标准PS/2键盘mini-DIN 连接器,标准PS/2键盘是通此连接器与外设相连接,其中,第1脚为Data(数据,第5脚为Clock(时钟,第3脚接地,第4脚接电源(5伏,第2与6脚保留。

因标准PS/2键盘输出脚是采用集电极开路设计,因此,标准PS/2键盘与接口相连时,输出要接一个上拉电阻方可使用,如图2所示。

脚1Data 脚2保留脚3接地脚4接电源脚5Clock 脚6保留图1标准PS/2键盘mini-DIN 连接器图2标准PS/2键盘与接口的连接三、标准PS/2键盘数据输出通信协议[3]图3为标准PS/2键盘数据输出短帧格式,当PS/2键盘要发数据时,首先要检查Clock 时钟脚的电压情况,如电压为低电平,则表示主机抑制了通信,如电压为高电平,PS/2键盘获得发送数据的控制权。

首先发送短帧数据格式的起始位(低电平,然后才发送数据(低位先发送,跟着发送奇校验位,最后才发送帧数据格式的停止位。

基于FPGA多功能键盘显示控制器的设计与研究

基于FPGA多功能键盘显示控制器的设计与研究引言FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,被广泛应用于数字电路设计。

多功能键盘显示控制器是一种可以实现多种功能的键盘,通过FPGA来实现控制和显示功能的设计与研究是目前的热点之一、本文将介绍基于FPGA的多功能键盘显示控制器的设计原理、功能和性能。

一、设计原理多功能键盘显示控制器的设计原理主要包括两个方面,即键盘控制和显示控制。

键盘控制主要是指通过按键输入来实现功能的切换和控制,而显示控制则是指通过控制显示屏来显示相应的信息。

在FPGA中设计键盘控制功能的原理是将键盘的每一个按键与FPGA内部的一个输入端口相连,然后通过FPGA的逻辑电路进行处理,将按键输入转化为相应的控制信号。

具体的实现方法可以采用状态机的设计思路,通过对按键输入的状态进行判断,确定相应的功能和控制信号。

显示控制的原理是将FPGA的输出端口与显示屏的输入端口相连,然后通过FPGA内部的逻辑电路将控制信号转化为对显示屏的输出信号,从而实现信息的显示。

通常情况下,可以使用七段数码管或者LCD屏来实现信息的显示。

二、功能设计多功能键盘显示控制器的功能设计可以根据实际需求进行扩展。

一般而言,它应该包括以下基本功能:1.多键切换功能:通过按键输入来实现多种功能的切换,可以根据用户的需求进行自定义设置。

2.多种显示方式:可以支持不同的显示方式,例如数码管显示、LCD显示等。

3.显示内容自定义:可以根据用户的需要自定义显示内容,例如显示时间、温度、电压等信息。

4.LED指示功能:通过LED灯来指示当前的工作状态,例如电源状态、工作模式等。

5.反馈功能:在按键输入或者功能切换时可以通过蜂鸣器或者震动马达来给用户一个反馈。

三、性能分析多功能键盘显示控制器的性能分析主要包括以下几个方面:1.响应速度:控制器对按键输入的响应速度应尽可能快,可以通过优化逻辑电路的设计来提高响应速度。

基于FPGA的PS键盘鼠标控制电子琴

基于FPGA的PS键盘鼠标控制电子琴基于FPGA的PS键盘鼠标控制电子琴随着计算机和数字技术的飞速发展,电子琴的应用在音乐行业和娱乐领域得到了广泛的应用。

而FPGA(即“现场可编程门阵列”)技术则为音乐技术的发展带来了新的希望。

本文将介绍基于FPGA的PS键盘鼠标控制电子琴的原理、开发过程和功能实现。

1. 基于FPGA的PS键盘鼠标控制电子琴的原理基于FPGA的PS键盘鼠标控制电子琴,是利用FPGA技术实现的。

FPGA 可以通过构建复杂的数字电路和逻辑系统来替代传统的硬件设计,实现高度集成的运算和逻辑控制。

在电子琴的功能实现中,我们主要是通过PS键盘和鼠标进行控制,FPGA则起到中间件的作用,在过程中实现模拟音乐输出。

2. 开发过程在整个开发过程中,我们需要申明使用的硬件平台(例如DE0-nano板卡)、使用的开发工具(例如Quartus II)、利用硬件系统和电子电路原理实现硬件电路的设计、开发板的测试以及代码的上载:第一步:准备硬件平台选用基于FPGA的DE0-nano开发板卡,需要在开发前熟知该硬件平台及实现方案。

关于DE0-nano的介绍,可以在手册或者网上自行查阅获得。

第二步:准备开发工具Quartus II是一款基于Windows环境的集成开发工具,可以代码规划、模拟仿真、调试以及实现真实硬件系统部署等功能。

第三步:实现硬件电路的设计在根据用户所期望实现的功能时,需要对硬件电路进行分析,确定实现的方案,并在Quartus II开发软件平台中实现代码规划。

第四步:开发板的测试在实现硬件电路设计后,需要对其进行测试。

利用DE0-nano开发板卡进行测试,检测电路效能和运行输出等测试等。

第五步:代码上载程序源文件编写完成后,需要将代码上载到DE0-nano开发板中,通过开发板输出运算结果。

3. 功能实现在基于FPGA的PS键盘鼠标控制电子琴中,我们主要需要实现一下几个功能:1. 利用PS2键盘控制矩阵键盘;2. 利用TFT显示屏显示正在按下的琴键;3. 利用鼠标实现电子琴的调音功能,并在TFT屏幕上显示当前的调音频率;4. 实现模拟音乐输出。

基于FPGA的PS键盘接口设计

基于FPGA的PS/2键盘接口的设计The design of PS/2 keyboard interface based on FPGA Wei,Junhui W ang ,Fuyuan Zhou, Ziang Hou,WeiyanAbstract:PS/2 keyboard is a general input of compute system. It can be easily equipped with various embedded systems. This paper describ es a new method to design PS/2 interface with FPGA. The result indi cates that the design has the features of easy modularization and powerful transplantable capability.Keywords: PS/2 interface; embedded system ; FPGA;摘要:PS/2键盘是一种常用的计算机输入设备,只需稍加改动,便可很方便的应用在各种嵌入式系统中。

本文提出了一种利用FPGA来设计PS/2接口的方法,结果表明此方法有容易实现模块化和移植性强的特点。

关键词:PS/2接口;嵌入式系统;FPGA键盘作为嵌入式系统的一种最常用人机接口设备,在嵌入式系统中有着相当广泛的应用。

但开发者一般均采用自行设计的简易矩阵键盘,这类键盘仅仅是按行、列排列起来的矩阵开关,往往需要单独设计并制作,通用性不强。

当需要较多的按键时,则会占用较多的I/O端口,在软件上则要进行上电复位按键扫描及通信处理,而且还要加上按键的去抖动处理,增大了系统的软硬件开销。

而PS/2键盘,内嵌自动去除按键抖动的设计,自动地识别键的按下与释放,软硬件可发简便,价格便宜,稳定可靠,将PS/2键盘作为嵌入式系统的输入设备已经成为可行的方案。

基于FPGA的PS2键盘控制设计及仿真实现

本科毕业论文(设计)论文题目:基于FPGA的PS2键盘控制设计及仿真实现作者声明本毕业论文(设计)是在导师的指导下由本人独立撰写完成的,没有剽窃、抄袭、造假等违反道德、学术规范和其他侵权行为。

对本论文(设计)的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

因本毕业论文(设计)引起的法律结果完全由本人承担。

特此声明作者专业:通信工程作者学号:作者签名:年月日基于FPGA的PS2键盘控制设计及仿真实现The Design and Simulation Implementation of the PS2 Keyboard Control based on FPGA2013年5月10日摘要本文简述了PS2键盘的特点和工作原理,重点介绍了在FPGA 上实现PS2键盘的结构设计和VHDL代码设计。

PS2键盘具有价格低、通用可靠,且连接线少(仅使用2根信号线)的特点。

并可满足多种系统的要求。

FPGA(Field Programmable Gate Array)是一类高集成度的可编程逻辑器件,它结合EDA技术以硬件描述语言、电路原理图、状机等形式输入设计逻辑;并提供功能模拟、时序仿真等模拟手段,再经过一系列的变换,将输入逻辑转换成FPGA器件所需的编程文件,以实现专用集成电路ASIC。

应用FPGA设计PS2键盘控制器,不仅有硬件电路简单,更具灵活性,集成度高更容易移植等特点,更重要的是现代EDA(电子设计自动化)技术提供了一种很好的途径,利用VHDL硬件描述语言和FPGA器件可以很方便地构建键盘扫描模块。

设计使得使用VHDL语言基于FPGA芯片实现PS2键盘成为研究的方向。

本文对基于VHDL的PS2键盘实现进行了研究,并设计了PS2键盘。

所做的主要工作为:(1)以PS2键盘控制的基本理论为依据,对其进行了详细的讨论。

(2)本设计中采用了自上而下的层次化、模块化的设计思想,将整个接口划分为多个模块,同时利用VHDL语言的描述方法对各个功能模块进行了设计,最终完成了PS2键盘的系统设计。

PS2键盘接口设计

研究生课程设计报告课程名称:基于FPGA的现代数字系统设计设计名称: PS/2键盘接口设计姓名:学号:课程教师:起止日期: 2016,西南科技大学信息工程学院制设计任务书学生班级:学生姓名:学号:设计名称:PS/2键盘接口设计起止日期: 2016,12,21至2016,12,28 课程教师:设计题目一、设计目的和意义键盘是嵌入式系统的最重要的输入设备之一,是实现人机交互的重要途径。

除了可以自行设计扫描式矩阵键盘之外,还可以选择标准 PS/2键盘实现人机交互。

扫描式矩阵键盘虽然电路简单,但不具有通用性,当需要使用较多的按键输入时,则会占用较多的I/O 端口,在软件上则要进行上电复位、按键扫描及通信的处理,而且还要加上按键的去抖动处理,增大了系统软、硬件的开销,开发周期较长。

标准PS/2 键盘由于接口通信协议简单,在系统中占用软硬件资源少,高可靠性,表达信息量大而得到了越来越广泛的应用本设计根据PS/2键盘的通信时序,利用Verilog HDL硬件描述语言来设计PS/2接口键盘的输入识别电路,并在CPLD/FPGA上实现,避免了硬件电路的焊接与测试。

Verilog HDL语言满足数字系统设计和综合的所有要求,设计中充分运用Verilog HDL层次化与模块化的思想,使整个设计过程简单、灵活。

同时运用EDA工具ISE Design Suite10.1验证设计。

经过对系统进行编译、仿真、测试,完成把键盘按键扫描码转的通码的显示,成功实现PS/2接口键盘的输入识别及显示的功能。

本设计具有较好的通用性和可移植性,可取代自行设计扫描式矩阵键盘而用于许多嵌入式系统设计中。

二、设计原理1 PS/2模块1.1、SP/2键盘接口PS/2通信协议是一种双向同步串行通迅协议。

通迅的两端通过CLOCK(时钟信号端)同步,并通过DATA(数据端口)交换数据。

任何一方如果想要抑制另外一方的通迅时,只需要把CLOCK 拉到低电平。

HDL-PS2接口键盘课程设计

课程设计报告题目HDL项目设计摘要:键盘是最常用人机接口设备之一,在嵌入式系统中有着相当广泛的应用。

一般自行设计的简易矩阵键盘仅仅是按行、列排列起来的矩阵开关。

当需要较多的按键时,则会占用较多的I/O 端口,在软件上则要进行上电复位按键扫描及通信处理,而且还要加上按键的去抖动处理,增大了软硬件开销。

而PS/2 键盘,内嵌自动去除按键抖动设计,自动地识别键的按下与释放,软硬件开发简便,价格便宜,稳定可靠,将PS/2 键盘作为嵌入式系统的输入设备已经成为可行的方案。

本设计是以现场可编程逻辑器件(FPGA)为核心的PS/2接口键盘的输入识别电路。

利用QuartusⅡ软件编写verilog HDL硬件描述语言程序以实现键盘部分简单键值的识别与输出。

本设计主要以程序为核心,硬件电路的搭建使用FPGA实验箱,将程序顶层文件里定义的输入输出端口与实验箱管脚进行相应的配置,除实验箱上的reset键以外,外设是一个与实验箱通过PS/2接口相连的键盘。

当系统上电后,实验箱上的数码管可以依次显示从键盘上输入的键值,并具有数码管清零功能。

关键词:Ps/2接口键盘、输入识别、FPGA 、Quartus Ⅱ、Verilog HDLAbstractThe keyboard, as one of the most commonly used man-machine interface equipment, has a wide application in embedded systems. General to design simple matrix keyboard is only per row, column arrangement up matrix switch. When need more button, will occupy more I/O port, in software, must carry on the power on the reset button scanning and communication processing, but also add buttons to jitter processing, increases the software and hardware cost. And PS / 2 keyboard, inline automatic remove key jitter design, automatically identify key press and release, software and hardware development is simple, cheap, stable and reliable, the PS / 2 keyboard as embedded system input device has become feasible scheme.This design based on field programmable logic devices (FPGA) is the core of the PS / 2 interface keyboard input identification circuit. Use verilog HDL Quartus Ⅱwriting software hardware description language program to realize the keyboard part simple key value of the recognition and output. This design mainly program as the core, the construction of the hardware circuit using FPGA experimental box, will be the top procedure defined in the file input/output port and experimental XiangGuan foot carries on the corresponding configuration, in addition to the experiment box on the reset button beyond, peripheral is a and experimental box through the PS / 2 interface connected keyboard. When the system is powered on, experiment box on the digital tube display can in turn from the keyboard input key value, and has the digital tube reset function.Keywords: Ps / 2 interface keyboard input identification FPGA,QuartusⅡVerilog HDL目录摘要2一.系统设计 51.1设计目标 51.2方案对比与确定 51.3总体设计框图及说明 61.3.1 总体设计框图 61.3.2总体设计端口说明 6 1.4模块电路设计及说明 7 1.4.1键盘数据接收部分 71.4.2数码管显示部分 8二.结果与讨论92.1调试步骤 9 2.2调试现象 92.3问题与分析 9三.软件设计103.1程序流程图 103.2程序设计 11四.心得体会17五.参考文献17六.附录18第一章系统设计1.1系统设计目标(1)以通用的PS2键盘为输入,设计一个能够识别PS2键盘输入编码的电路,并把键值通过数码管显示;(2)至少能够识别0~9的数字键。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

P/ S2键盘 间的通讯 , P 则 c机必须做 主机 , 也就是说 ,c机可 以 P 抑制 P / S 2键盘发送 数据 , P / 而 S2键盘则不会抑制 P C机发送数 据 。数据传 输的最大 时钟频率是 3 K z大 多数 P I 3H , S2设备工作 在 1 —0 H , 0 2 K z一般采 用 1 K zCok高 、 电平 的持 续时 间 5 H ,lc 低 都为 4 1 。每一数据帧包含 1— 2 0s x 1位 1 。

另 外 一 方通 讯 时 , 需 要 把 Cok 到低 电平 。如 果 是 P 只 lc 拉 C机 和

a as p sd e e — u / l y@(oe g l ot/ w k )采样十一位数据

be i gn

ia= "l) a4d ; f = 4d 0 = "0 (

e s a + 1 le =a 4 :

F GA独特器件 架构 , 用 F G P 利 P A设计键盘控制器, 不仅硬件 电路 简单, 而且编程过程 比通用 MC 比, U 简单易行 。

关键 词 : 制 器 ; 盘 ; P A; 控 键 F G 电路 中 图分 类 号 : P 7 + 8 T 21. 2 文 献 标 识码 : A

ed n

as n c ( = )1 11 O/ 动解 码 模 块 和 验 证模 块 si =a 9? , : d ;启 g = d /

as n a 1 ( = ,1 dt : ;数据采样结束 , 出数据 si dt =c 1d) a 28 , g a = ? a 0 / 输 aw y@ psd e c i) ̄: las (oe g l n 样数据端 k /

・

计算技术与 自动化 ・

基 于 F GA的 P 2键 盘 控 制 器设 计 P S

郭玉峰 , 昌 霞 孙

( 河南农业大学信息与管理科学学院 , 河南 摘 郑州 4 00 ) 5 0 2 要 : -k 在x _ 电子设备的智 能化和升级换代 以及 电路 的设计 中 , 需要使 用键盘 , , l 常 而使 用标 准 P 2 盘则可 简化设计 。由于 S键

方案。

4d : g id = 1 O d t[ = ;l 1d; ed d 止 "1 ei f l = " ) a 0 Ⅸd = ,1 n/ nl b n ( d a】 d /

重 复采样 出错

4d :ei id = l 0dt[ :x; d = ,1 ed "2 gn f 2 = )aa1 rd 2 l : n b ( d ] d 4d :ei id = l 0dt[ =x; d = 'l ed "3 g f 3 = )aa lrd 3 l ; n b n ( d 2 d 4d :ei id = 1 0dt[]rd d = 'l ed "4 g f 4 = " )aa =x; 4 l ; n b n ( d 3 d 4d :ei id= 1 0dt[ =x; d = 'l ed "5 g f 5 = " )aa ]rd 5 l ; n b n ( d 4 d 4d : g id= 1 Odt[]rd d = 'l ed " b i f 6 = " )a 5=x; 6 l ; n 6 en ( d a d 4 7bg id = l 0dt[lrd d = 'l ed d en ( " : i f 7 = ' )a 6=x; 7 l ; n d a d 4d : g id= l Odt[]rd d = 'l ed " b i f 8 = ' )a 7=x; 8 l n 8 en ( d a d;

D es gn i of C ont oler r l of PS2 key boa rd a d B se on FPGA

GUO Yu fn ,S h n — i — e g UN C a g xa

(nom t n a d Ma a e e t c n e C l g , n n A r ut a U i r t H n n Z e gh u 4 0 0 ) I f ai n n g m n i c o e e He a g c l rl nv s y e a h n z o 5 0 2 r o S e l i u e i,

Ke y wo d :c nr l r e b a d F GA; i u t rs 0 t l ; yor;P oek cr i c

FG P A利用 E A技术 , D 以电路原理 图 、 硬件描 述语 言 、 状态

P 2的时钟线发送时钟 的频率在 1~ 0 H 之 间 ,本文用 S 02K z 10 Hz 0 K 的信号对 P 2 S 键盘 的时钟信号进行采样 , 用这个采样到 的信号作为数据 时钟 的接手控制线 , 完成数据的采样。根据 P 2 S 键盘发送信号时序 , 键盘控制器的部分 V ro 代码为 : el ig

be i gn

2 器 件 选 择

A ea yln 系列 F G h r C coe P A是基于成本优化的 , 工艺 的 全铜

cs( ae ) a

1 V S A 工 艺 ,最 高 达 2 00个 逻 辑单 元 和 2 8 . RM 5 06 8 K位 的

R M,内部还集 成 了许 多复杂 的功能 。提供 全功能 的锁相环 A ( L )用于板级 的时钟 网络管理 和专用 I PL , / O接 口, 这些 接 口用 于 连接业 界标 准 的外 部存 储 器 器件 。低 成 本结 构 和 C coe yln FG P A丰富的器件资源相结合 , 能够实现完整的可编程芯片系统

1 PS 2

ick = O c — u= O f l= l 1 l ot1 ; ( d k d

e s ek o t d1 le l u =1, :

_

P / 通 讯 协 议 是 一 种 双 向 同 步 串行 通 讯 协 议 。P / 盘 连 S2 S 2键

ed n

接端 口有 四个有意义的引脚 , 分别是 Cok D t、 lc 、 aa 电源 、 。通讯 地 的两端通过 Cok同步 , 通过 D t 交换数据 。 l c 并 aa 一方如果想抑制

a as p sd e ckn / 样 时 钟 l y@(oe g li)采 w /

b gn e i

机等形 式输入设 计逻辑 ; 提供功能模拟 、 时序仿 真等模拟手段 ,

经过一 系列 的变பைடு நூலகம் , 将输入逻辑转换成 F G P A器件 的编程文件 , 以实现专用集成电路。 随着大规模逻辑器件 F G /P D大量应 P AC L 用 在电子设 计领域 ,很多通用 的电路控制模块都 集 中到 F G PA 里面以便简化 电路 。应用 F G P A设计 P 2键盘控制器 ,设计量 S 小, 简单方便 。