数电研讨-用CMOS传输门和CMOS非门设计边沿D触发器

数字电子技术基础(第四版)阎石第4章

CP S R Qn Qn1

0 t

0

0 1 1

X

X 0 0

X

X 0 0

0

1 0 1

0

1 0 1

RD

0 S 0 R 0 Q 0 t t

1

1 1 1 1 1

1

1 0 0 1 1

0

0 1 1 1 1

0

1 0 1 0 1

1

1 0 0 1* 1*

t

Q

0

t

在CLK

1期间,Q和Q可能随S、R潍坊学院 信息与控制工程学院 变化多次翻转

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

主从SR触发器的 表4.2.4 特性表如表4.2.4所示, CP S R 和电平触发的SR触发 × × × 器相同,只是CP作用 0 0 的时间不同

0 0 0 1 0 1 1 0 0 1 1

Q × 0 1 0 1 0 1 0 1

Q* Q 0 1 0 0 1 1 1* 1*

0

1 1 1 0 0 0* 0*

S D和R D同时为0 Q ,Q同为 1

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

4.2.2 同步RS触发器的电路结构与动作特点

在数字系统中,常常要求某些触发器在同一时刻动作,这 就要求有一个同步信号来控制,这个控制信号叫做时钟信号 (Clock pulse),简称时钟,用CP表示。这种受时钟控制的 触发器统称为时钟触发器。 一、电路结构与工作原理 图5.3.1所示为电平触发SR触发器(同步SR触发器)的基 本电路结构及图形符号。

潍坊学院 信息与控制工程学院

《数字电子技术基础》第四版

2. 主从 JK触发器 为解除约束 即使出现 S R 1的情况下, Q n 1也是确定的

基于CMOS传输门结构的基本D触发器详解

集成电路版图课程设计设计项目:基于CMOS传输门结构的基本D触发器版图设计学院:电子科学与应用物理学院班级:姓名:合作者:目录一、设计的目的和意义 (3)二、设计的主要内容和要求 (4)三、设计采用的硬件和软件环境和条件 (4)四、实验原理 (4)五、设计步骤 (8)六、设计心得 (10)七、参考文献 (10)一、设计的目的和意义设计目的:1.熟悉L-Edit电路图编辑环境、模块的编辑和引用;2.掌握L-Edit菜单使用方法3.掌握并认识版图设计规则检测;4.了解如何分析所绘制的电路图的功能能够达到原来预计的效果;5.熟悉IC制造工艺文件;6.熟练运用软件设计电路和版图。

设计意义:1.配合CMOS数字集成电路设计基础、集成电路设计硬件描述语言、超大规模集成电路CAD、器件模型CAD、集成电路版图设计,培养IC设计的实践能力;2.进一步掌握基本的数字集成电路与器件设计和调试的方法与步骤;3.掌握设计输入、编译、模拟、仿真等IC设计的基本过程;4.进一步巩固所学IC设计相关的理论知识,提高运用所学知识分析和解决实际集成电路工程设计问题的能力;5.经过查找资料、方案的设计与选择、设计仿真器件或电路、检查版图设计、撰写设计报告等一系列实践过程,实现一次较全面的IC版图设计工程实践训练6.通过理论与实际相结合初步感悟工程设计与理论设计的不同点,提高和培养创新和实践能力,为后续课程的学习打下坚实基础。

7.提高团队合作能力。

二、设计的主要内容和要求利用S-Edit软件画出传输门结构的D触发器,然后用L-Edit画出其版图,并作DRC验证。

三、设计采用的硬件和软件环境和条件1.主要设备是电脑2.软件环境:Tanner Pro 13.1四、实验原理触发器是具有记忆功能的基本存储单元,有静态和动态两种实现方法,静态主要是利用双稳态原理:一对交叉耦合的反相器形成一个双稳态元件并且因此可以用来记忆二进制值。

这种方法的优点是只要电源电压加在该电路上,他所保持得值就一直有效,因此称为静态电路。

基于CMOS传输门和CMOS非门设计边沿D触发器实验报告..

数字电子技术研讨报告实验题目:基于CMOS传输门和CMOS非门设计边沿D触发器THE D FLIP-FLOP BASED ON THE CMOS TRANSMISSION DOORAND CMOS GATE学院:电子信息工程学院专业:学生姓名:学号:任课教师:侯建军2013 年12 月 3 日绪论一、概述------------------------------------------------------------31.触发器简介--------------------------------------------------32.D触发器-----------------------------------------------------43.CMOS边沿D触发器------------------------------------5二、设计目的及要求---------------------------------------------61.设计目的-----------------------------------------------------62.设计任务及要求--------------------------------------------6三、设计电路------------------------------------------------------61.电路结构设计-----------------------------------------------72.电路工作原理-----------------------------------------------83.特征方程、表、图-----------------------------------------84.脉冲设计-----------------------------------------------------95.异步置位、复位设计---------------------------------------11四、总结与感想---------------------------------------------------12 参考文献-------------------------------------------------------------13 致谢附录本文主要研究了用CMOS传输门和CMOS非门设计边沿D触发器。

数电研讨——用CMOS传输门和CMOS非门设计边沿D触发器

目录摘要 (2)关键字 (2)正文 (2)1 电路结构图及其原理 (3)1.1传输门 (3)1.2 与非门 (3)1.3 D触发器电路 (4)2 电路工作原理仿真 (5)3 特征方程、特征表、激励表与状态图 (5)3.1特征方程 (5)3.2 特征表 (5)3.3 激励表 (6)3.4 状态图 (6)4 激励信号D的保持时间和时钟CP的最大频率 (6)5 设计的D触发器转换成JK触发器和T触发器 (8)5.1D触发器转换为JK触发器 (8)5.2D触发器转换为T触发器 (9)6基于CMOS的D触发器芯片与基于TTL的D触发器芯片外特性比较分析 (9)7 总结与感想 (11)7.1 总结 (11)7.2 感想 (11)参考文献 (1)用CMOS传输门和CMOS非门设计边沿D触发器摘要:本文主要研究了用CMOS传输门和CMOS非门设计边沿D触发器。

首先分析CMOS传输门和CMOS与非门原理;然后设计出CMOS传输门和CMOS非门设计边沿D触发器;阐述电路工作原理;写出特征方程,画出特征表,激励表与状态图;计算出激励信号D的保持时间和时钟CP的最大频率;将设计的D触发器转换成JK触发器和T触发器,最后对CMOS构成的D触发器进行辨证分析。

关键词:CMOS传输门;CMOS非门;边沿D触发器;最大频率;辨证思想Use CMOS transmission door and CMOS gate design edge D flip-flopAbstract:This paper mainly studied how to use CMOS transmission door and CMOS gatedesign edge D flip-flop. Firstly analyzes CMOS transmission door and CMOS nand gate principle;Then design a CMOS transmission door and CMOS gate design edge D flip-flop; This circuitprinciple of work, Write characteristic equation, draw the feature list, incentive table and statediagram; To calculate the excitation signal D retention time and clock CP's maximum frequency;The design of the D flip-flop into JK flip-flop and T trigger, the CMOS a D flip-flop syndromedifferentiation and analysisKey words:CMOS transmission door;CMOS gate edge ;D flip-flop;maximum frequency;dialectic thought1.结构图以及功能1.1CMOS传输门图1传输门的结构图原理:所谓传输门(TG)就是一种传输模拟信号的模拟开关。

数电研讨——用CMOS传输门和CMOS非门设计边沿D触发器

用CMOS传输门和CMOS非门设计边沿D触发器Design Edge D Flip-flop with CMOS Transmission Gate and CMOS NAND Gate摘要本文主要研究了用CMOS传输门和CMOS非门设计边沿D触发器,并将其进行了拓展分析与研究。

本文首先从CMOS传输门和CMOS非门组成的边沿D触发器的电路工作原理、特征方程、特征表、激励表、状态图进行了阐述,计算出激励信号D的保持时间和时钟CP的最大频率,并与TTL组成的D触发器进行了对比和应用分析。

接着还将D触发器转换成JK触发器和T触发器,并分别设计了并行数据存储电路、倍频电路、单稳态电路以及脉冲震荡器这四个功能电路,在实际生活中有着重要的应用。

关键词边沿D触发器 CMOS传输门 CMOS非门 JK触发器 D触发器AbstractThis paper studies the use of non-CMOS and CMOS transmission gate door design edge D flip-flop, and Analysis and research conducted to expand. Edge D flip-flop circuit works from the paper first and CMOS transmission gate CMOS NAND gate composed of the characteristic equation, characteristic form, motivate table, state diagram are described, D calculate the excitation signal hold time and the maximum clock frequency of CP and the composition of the D flip-flop TTL were compared and applied analysis. Then will be converted into a JK flip-flop D flip-flop and Tflip-flops, and were designed to parallel data storage circuit, multiplier circuits,one-shot pulse oscillator circuit and four functional circuit, has important in real life application.Key Words:edge D flip-flop; CMOS transmission gate; CMOS NAND gate; JKflip-flop; T flip-flop目录第1章用CMOS传输门和CMOS非门设计边沿D触发器 (5)1.1 CMOS传输门 (5)1.1.1组成 (5)1.1.2 原理 (5)1.1.3 结论 (5)1.2 CMOS非门 (6)1.2.1 CMOS非门的组成 (6)1.2.2 CMOS非门的原理 (6)1.2.3 CMOS非门的传输延迟时间 (7)1.3用CMOS传输门和CMOS非门设计边沿D触发器 (7)1.3.1 电路组成 (7)1.3.2 电路原理 (7)1.3.3 特征方程,特征表,激励表与状态图 (8)1.3.4激励信号D的保持时间和时钟CP的最大频率 (9)1.4 CMOS构成的D触发器与TTL构成的D触发器比较 (10)1.5 CMOS D触发器的应用——CD4013触摸开关 (12)第二章将设计的边沿D触发器改成其他类型触发器 (13)2.1将设计的D触发器转换成JK触发器 (13)2.2将设计的D触发器转换成T触发器 (13)第三章基于D触发器的应用拓展电路设计 (15)3.1 并行数据存储电路 (15)3.2 倍频电路 (16)3.3 单稳态电路 (18)第四章总结 (26)致谢 (27)参考文献 (27)第1章用CMOS传输门和CMOS非门设计边沿D触发器1.1 CMOS传输门1.1.1组成CMOS传输门的电路如图1-1(a),逻辑符号如图1-1(b)所示。

用CMOS传输门和CMOS非门设计边沿D触发器-北京交通大学

数字电子技术研究性课题数字电子技术研究性课题用CMOS传输门和CMOS非门设计边沿D触发器姓名:学号:学院:电子信息工程学院班级:********日期:2013/11/25摘要本文用CMOS传输门和非门设计边沿D触发器。

首先说明了电路原理,阐明电路的组成结构。

写出特征方程,画出特征表,激励表与状态图。

计算出激励信号D的保持时间和时钟CP的最大频率。

并将设计的D触发器转换成JK触发器和T触发器。

还研究了CMOS触发器在时钟边沿的工作特性及总结,分析了CMOS触发器的功耗情况,阐述了双边沿触发器的工作原理,最后阐述了自己的感想。

关键词:D触发器边沿触发 CMOS传输门 CMOS非门AbstractThis paper mainly discusses the edge D flip-flop using CMOS transmission gate and gate design. The edge D trigger in teaching material is maintaining block edge D flip-flop, use TTL controls into, and this practice is used in innovative ways: with the use of CMOS transmission gate and the gate to the edge D flip-flop. At the same time also analyzed the setup time, hold time, and delay time, the highest frequency analysis method. Also focused on CMOS trigger clock edge characteristics. And has carried on the summary. As well as the contrast between the chip, in practical application are presented. Suggestions.Keywords: D trigger; trigger edge; CMOS transmission gate; CMOS gate目录摘要.............................................................................................................. - 1 -Abstract.......................................................................................................... - 1 -绪论.............................................................................................................. - 3 -第1章电路组成结构及其原理 ........................................................................ - 4 -1.1 边沿D触发器 ......................................................................................................... - 4 -1.2 CMOS门电路 ............................................................................................................ - 4 -1.3 电路组成结构图 ..................................................................................................... - 5 -1.4 电路工作原理 ......................................................................................................... - 6 -第2章特征方程、特征表、激励表及状态图..................................................... - 7 -第3章激励信号D的保持时间和时钟CP的最大频率 ......................................... - 8 -3.1 平均传输延迟时间 ................................................................................................. - 8 -3.2 保持时间 ................................................................................................................. - 8 -3.3 时钟CP最大频率 ................................................................................................... - 9 -第4章复位、置位电路 ................................................................................ - 11 -第5章触发器逻辑功能的转换 ...................................................................... - 13 -5.1 D触发器转换成JK触发器 .................................................................................. - 13 -5.2 D触发器转换成T触发器 .................................................................................... - 14 -第6章 CMOS双边沿D触发器......................................................................... - 15 -6.1 CMOS集成电路功耗分析 ...................................................................................... - 15 -6.2 CMOS双边D沿触发器工作原理 .......................................................................... - 15 -第7章 D触发器常用芯片 ............................................................................ - 18 -7.1 74HC273芯片资料 .................................................................................................. - 18 -7.2 74LS273芯片资料 .................................................................................................. - 19 -7.3 芯片性能比较 ......................................................................................................... - 20 -感想与总结 .................................................................................................. - 22 -绪论触发器按触发方式的不同,可分为电平触发器、主从触发器和边沿触发器。

用CMOS传输门和CMOS非门设计D触发器解读

用CMOS传输门和CMOS非门设计边沿D触发器姓名单赟吉所在学院电子信息工程专业班级通信1109学号 11211105指导教师白双日期 __2013.12月_____目录摘要 (2)第一章绪论 (2)1.1 CMOS D触发器与TTL D触发器的比较 (3)1.2 触发器 (4)1.3 边沿触发器 (4)第二章D触发器电路组成结构 (6)2.1 CMOS反向器 (6)2.2 CMOS传输门 (6)2.3 D触发器 (7)2.4 第一种设计方案 (8)2.5 第二种设计方案 (9)2.6 两种设计方案比较 (10)第三章置位、复位电路 (12)第四章特征方程,特征表,激励表,状态图 (14)4.1 特征方程和特征表 (14)4.2 激励表 (14)4.3 状态图 (14)第五章激励信号D的保持时间和时钟CP的最大频率 (16)5.1 平均传输延迟时间 (16)5.2 建立时间和保持时间 (16)5.3 CP时钟周期 (17)第六章设计的D触发器转换成JK触发器和T触发器 (18)6.1 设计的D触发器转换成JK触发器 (18)6.2 D触发器转换成T触发器 (19)第七章CMOS D触发器在CP边沿的工作特性研究 (21)第八章CMOS D触发器的应用—CD4013触摸开关 (24)第九章总结以及感想 (25)参考文献 (26)摘要:本文用CMOS传输门和CMOS非门设计边沿D触发器。

说明电路组成结构;阐述电路工作原理;写出特征方程,画出特征表,激励表与状态图;计算出激励信号D的保持时间和时钟CP 的最大频率;将设计的D触发器转换成JK触发器和T触发器。

关键词:边沿触发 CMOS非门,CMOS传输门,D触发器。

Abstract:This paper mainly studied how to use CMOS transmission door and CMOS gate design edge D flip-flop. Firstly analyzes CMOS transmission door and CMOS gate principle; Then use the CMOS transmission door and CMOS gate design the edge D flip-flop; Also this paper tells us how this circuit work, Then write characteristic equation, draw the feature list, incentive table and state diagram; Next calculate the excitation signal D retention time and clock CP's maximum frequency; Finally put The design of the D flip-flop into JK flip-flop and T trigger.Keywords: trigger edge; CMOS gate;CMOS transmission gate; D trigger;一、绪论1.1 CMOS D触发器与TTL D触发器的比较TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。

用CMOS传输门和CMOS非门设计D触发器

用CMOS传输门和CMOS非门设计边沿D触发器姓名周路所在学院电子信息工程专业班级通信1002学号 10211061指导教师侯建军日期 __2012.12月_____目录第一章电路组成结构 (1)第二章电路工作原理 (2)第三章特征方程,特征表,激励表,状态图 (2)第四章激励信号D的保持时间和时钟CP的最大频率 (3)第五章设计的D触发器转换成JK触发器和T触发器 (4)5.1 设计的D触发器转换成JK触发器 (4)5.2 D触发器转换成T触发器 (4)第六章CMOS D触发器CD4013和TTL D触发器74LS74区别 (5)第七章CMOS D触发器的应用——CC4013触摸开关 (7)第八章感想以及总结 (8)参考文献 (9)摘要:本文用CMOS 传输门和CMOS 非门设计边沿D 触发器。

说明电路组成结构;阐述电路工作原理;写出特征方程,画出特征表,激励表与状态图;计算出激励信号D 的保持时间和时钟CP 的最大频率;将设计的D 触发器转换成JK 触发器和T 触发器。

比较C4013和74LS74的区别,简述CD4013的一个应用。

最后阐述自己的感想和对未来电子技术发展的一些展望设想。

关键词: CMOS 非门,CMOS 传输门,TTL 与CMOS ,展望未来。

一、电路组成结构传统的边沿D 触发器电路已为大家熟知,在此基础上,用CMOS 传输门(TG )和CMOS 非门(G)设计;由此该电路的整体构造如下图所示.图1 D 触发器原理图图2 仿真CMOS传输门和非门构成的D触发器,非门G1、G2和传输门TG1、TG2组成了主触发器;非门G3、G4和传输门TG3、TG4组成了从触发器。

TG1和TG3分别为主触发器和从触发器的输入控制门。

根据CMOS传输门的工作原理和图中控制信号的极性标注可知,当传输门TG1、TG4导通时,TG2、TG3截止;反之,当TG1、TG4截止时,TG2、TG3导通二、电路工作原理1.CP=0,TG1导通,TG2截止,D端输入信号送人主触发器中,G1=D,G2=D此时触发器尚未形成反馈连接,不能自行保持。

d触发器与非门设计模10

d触发器与非门设计模拟1. 引言在数字电子技术中,触发器是一种重要的电子元件,用于存储和处理信息。

d触发器作为最简单且常用的一种触发器,具有广泛的应用。

本文将介绍d触发器的原理和设计模拟,并讨论非门的实现方法。

2. d触发器的原理d触发器是一种存储器件,用于存储和传输数字信息。

它具有一个输入端d和两个输出端q和q’。

d触发器的状态取决于输入信号d和时钟信号的变化。

在上升沿或下降沿时,输入端d的值被传递到输出端q,使得q的值与d相等。

d触发器可以分为边沿触发器和级沿触发器。

2.1 边沿触发器边沿触发器在时钟信号的上升沿或下降沿时更新其状态。

常见的边沿触发器包括d 触发器、JK触发器和T触发器。

根据时钟信号的上升沿或下降沿更新状态的性质,d触发器可以进一步分为正边沿触发器和负边沿触发器。

在正边沿触发器中,输入信号d在上升沿时被传递到输出端q;在负边沿触发器中,输入信号d在下降沿时被传递到输出端q。

2.2 级沿触发器级沿触发器根据时钟信号的边沿更新其状态。

常见的级沿触发器包括D触发器、JK 触发器和T触发器。

d触发器是最简单且常用的级沿触发器。

它通过给定的时钟信号来将输入信号d传输到输出端q。

d触发器有两个稳定状态,它的输出保持不变,直到时钟信号发生变化。

3. d触发器的设计模拟为了实现d触发器的功能,我们可以使用基本逻辑门来构建它。

常用的逻辑门包括与门、或门、非门和异或门。

3.1 与门与门是基本的逻辑门之一。

它有两个输入端和一个输出端。

当且仅当所有输入端都为高电平时,输出端才为高电平。

我们可以使用与门来实现d触发器的布尔表达式。

d触发器的布尔表达式为:q(t+1) = d可以使用与门来实现该布尔表达式。

将输入端d和时钟信号连接到与门的输入端,并将与门的输出端连接到输出端q。

这样,在时钟信号的边沿触发下,输入信号d的值将被传输到输出端q。

3.2 非门非门是基本的逻辑门之一。

它有一个输入端和一个输出端。

用CMOS传输门和CMOS非门设计边沿D触发器汇总

《数字电子技术》研究性学习用CMOS传输门和CMOS非门设计边沿D触发器*名:***学号: ********班级:通信1307指导老师:***时间: 2015年12月1日目录摘要 3关键字 3正文 31 电路结构图及其原理 31.1传输门31.2 与非门 31.3 D触发器电路 42 电路工作原理仿真53 特征方程、特征表、激励表与状态图53.1特征方程 53.2 特征表 53.3 激励表 63.4 状态图 64 激励信号D的保持时间和时钟CP的最大频率 65 设计的D触发器转换成JK触发器和T触发器85.1 D触发器转换为JK触发器85.2 D触发器转换为T触发器96基于CMOS的D触发器芯片与基于TTL的D触发器芯片外特性比较分析117 CMOS D触发器的应用——CD4013触摸开关 138 总结148.1 总结 148.2 感想 14参考文献15摘要:本文主要研究了用CMOS传输门和CMOS非门设计边沿D触发器。

首先分析CMOS传输门和CMOS与非门原理;然后设计出CMOS传输门和CMOS非门设计边沿D触发器;阐述电路工作原理;写出特征方程,画出特征表,激励表与状态图;计算出激励信号D的保持时间和时钟CP的最大频率;将设计的D触发器转换成JK触发器和T触发器,最后对CMOS构成的D触发器进行辨证分析。

关键词:CMOS传输门;CMOS非门;边沿D触发器;1.结构图以及功能1.1CMOS传输门图1传输门的结构图原理:所谓传输门(TG)就是一种传输模拟信号的模拟开关。

CMOS传输门由一个P沟道和一个N沟道增强型MOS管并联而成,如上图所示。

设它们的开启电压|VT|=2V且输入模拟信号的变化范围为0V到+5V。

为使衬底与漏源极之间的PN结任何时刻都不致正偏,故T2的衬底接+5V电压,而T1的衬底接地。

传输门的工作情况如下:当C端接低电压0V时T1的栅压即为0V,vI取0V到+5V范围内的任意值时,TN均不导通。

用CMOS传输门和CMOS非门设计D触发器资料

用CMOS传输门和CMOS非门设计边沿D触发器姓名单赟吉所在学院电子信息工程专业班级通信1109学号 11211105指导教师白双日期 __2013.12月_____目录摘要 (2)第一章绪论 (2)1.1 CMOS D触发器与TTL D触发器的比较 (3)1.2 触发器 (4)1.3 边沿触发器 (4)第二章D触发器电路组成结构 (6)2.1 CMOS反向器 (6)2.2 CMOS传输门 (6)2.3 D触发器 (7)2.4 第一种设计方案 (8)2.5 第二种设计方案 (9)2.6 两种设计方案比较 (10)第三章置位、复位电路 (12)第四章特征方程,特征表,激励表,状态图 (14)4.1 特征方程和特征表 (14)4.2 激励表 (14)4.3 状态图 (14)第五章激励信号D的保持时间和时钟CP的最大频率 (16)5.1 平均传输延迟时间 (16)5.2 建立时间和保持时间 (16)5.3 CP时钟周期 (17)第六章设计的D触发器转换成JK触发器和T触发器 (18)6.1 设计的D触发器转换成JK触发器 (18)6.2 D触发器转换成T触发器 (19)第七章CMOS D触发器在CP边沿的工作特性研究 (21)第八章CMOS D触发器的应用—CD4013触摸开关 (24)第九章总结以及感想 (25)参考文献 (26)摘要:本文用CMOS传输门和CMOS非门设计边沿D触发器。

说明电路组成结构;阐述电路工作原理;写出特征方程,画出特征表,激励表与状态图;计算出激励信号D的保持时间和时钟CP 的最大频率;将设计的D触发器转换成JK触发器和T触发器。

关键词:边沿触发 CMOS非门,CMOS传输门,D触发器。

Abstract:This paper mainly studied how to use CMOS transmission door and CMOS gate design edge D flip-flop. Firstly analyzes CMOS transmission door and CMOS gate principle; Then use the CMOS transmission door and CMOS gate design the edge D flip-flop; Also this paper tells us how this circuit work, Then write characteristic equation, draw the feature list, incentive table and state diagram; Next calculate the excitation signal D retention time and clock CP's maximum frequency; Finally put The design of the D flip-flop into JK flip-flop and T trigger.Keywords: trigger edge; CMOS gate;CMOS transmission gate; D trigger;一、绪论1.1 CMOS D触发器与TTL D触发器的比较TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。

(Multisim数电仿真)D触发器及应用

实验3.9 D 触发器及应用一、实验目的:1.了解边沿D 触发器的逻辑功能和特点。

2.掌握D 触发器的异步置0和异步置1端的作用。

3.了解用D 触发器组成智力抢答器的工作原理。

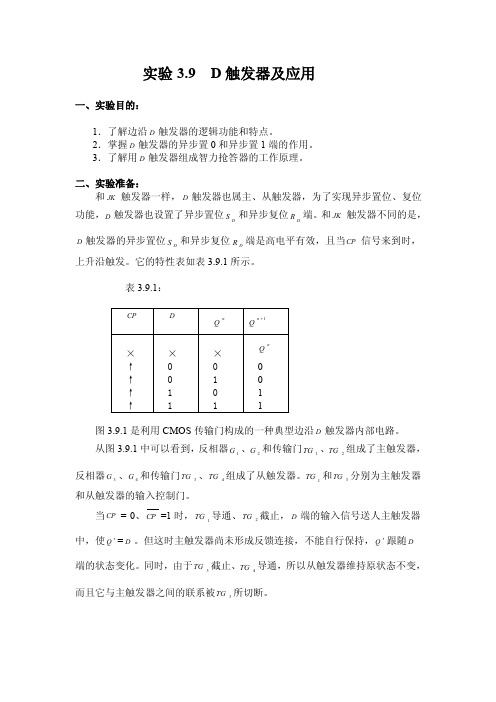

二、实验准备:和JK 触发器一样,D 触发器也属主、从触发器,为了实现异步置位、复位功能,D 触发器也设置了异步置位D S 和异步复位D R 端。

和JK 触发器不同的是,D触发器的异步置位D S 和异步复位D R 端是高电平有效,且当CP 信号来到时,上升沿触发。

它的特性表如表3.9.1所示。

表3.9.1:图3.9.1是利用CMOS 传输门构成的一种典型边沿D 触发器内部电路。

从图3.9.1中可以看到,反相器1G 、2G 和传输门1TG 、2TG 组成了主触发器,反相器3G 、4G 和传输门3TG 、4TG 组成了从触发器。

1TG 和3TG 分别为主触发器和从触发器的输入控制门。

当CP = 0、CP =1时,1TG 导通、2TG 截止,D 端的输入信号送人主触发器中,使Q '=D 。

但这时主触发器尚未形成反馈连接,不能自行保持,Q '跟随D 端的状态变化。

同时,由于3TG 截止、4TG 导通,所以从触发器维持原状态不变,而且它与主触发器之间的联系被3TG 所切断。

图3.9.1当CP 的上升沿到达时(即CP 跳变为1、CP 跳变为0),1TG 截止、2TG 导通。

由于门1G 的输入电容存储效应,1G 输入端的电压不会立刻消失,于是Q '在1TG 切断前的状态被保存下来。

同时,由于3TG 导通、4TG 截止,主触发器的状态通过3TG和3G 送到了输出端,使=QQ '=D (CP 上升沿到达时D 的状态)。

可见,这种触发器的动作特点是输出端状态的转换发生在CP 的上升沿,而且触发器所保存下来的状态仅仅取决于CP 上升沿到达时的输入状态。

因为触发器输出端状态的转换发生在CP 的上升沿,所以这是一个上升沿触发边沿触发器。

cmos边沿d触发器真值表

cmos边沿d触发器真值表

CMOS边沿D触发器的真值表如下:

1.当输入信号D为0时,触发器保持原状态不变。

2.当输入信号D为1时,触发器翻转至0状态。

3.当输入信号D为X(不确定)时,触发器状态不确定。

4.当输入信号D为Z(高阻态)时,触发器输出状态为0。

需要注意的是,CMOS边沿D触发器的真值表与具体的电路实现有关,上述真值表仅供参考,具体的真值表应根据电路设计而定。

CMOS边沿D触发器和边沿A、B触发器的主要区别在于触发方式和输入信号的处理方式。

1.触发方式:边沿D触发器是一种最简单的触发器,在触发边沿到来时,将输入端的值存入其中,并且这个值与当前存储的值无关。

在两个有效的脉冲边沿之间,D的跳转不会影响触发器存储的值,但是在脉冲边沿到来之前,输入端D必须有足够的建立时间,保证信号稳定。

而边沿A、B触发器则具有不同的触发方式,对输入信号的处理也有所不同。

2.输入信号处理:CMOS边沿D触发器主要通过D端输入信号来控制触发器的状态,当D端输入为1时,触发器翻转至0状态;当D端输入为0时,触发器保持原状态不变。

而边沿

A、B触发器则可能根据A、B端的输入信号来控制触发器的状态。

综上所述,CMOS边沿D触发器和边沿A、B触发器的主要区别在于触发方式和输入信号的处理方式,具体选择哪种触发器需要根据实际应用需求来决定。

边沿d触发器的逻辑功能

边沿d触发器的逻辑功能边沿D触发器是一种常用的数字电路元件,用于存储和传输数据。

它由一个D输入端、一个时钟输入端和两个输出端(Q和Q')组成。

边沿D触发器根据时钟信号的上升沿或下降沿来决定是否将D输入的数据传输到输出端。

1. 工作原理边沿D触发器的工作原理可以分为以下几个步骤:(1) 当时钟信号为低电平时,边沿D触发器处于保持状态,即不对D输入进行任何操作。

(2) 当时钟信号上升沿到来时,边沿D触发器会将此刻的D输入值传输到输出端,并在之后的时钟周期内保持该值。

(3) 当时钟信号下降沿到来时,边沿D触发器继续保持上一个状态,并在之后的时钟周期内保持不变。

2. 逻辑功能边沿D触发器具有以下几种逻辑功能:(1) 存储功能:当时钟信号为低电平时,边沿D触发器会将当前的输入值存储在输出端,并在之后的周期内一直保持该值。

(2) 数据传输功能:当时钟信号上升沿到来时,边沿D触发器会将此刻的D输入值传输到输出端,并在之后的周期内保持该值。

这种功能可以用于数据的传输和暂存。

(3) 边沿检测功能:边沿D触发器能够检测时钟信号的上升沿或下降沿,并根据边沿的到来来执行相应的操作。

3. 应用场景边沿D触发器在数字电路中有广泛的应用,以下是一些常见的应用场景:(1) 时序电路设计:边沿D触发器可以用于设计各种时序电路,如计数器、移位寄存器等。

通过合理地连接多个边沿D触发器,可以实现复杂的时序逻辑功能。

(2) 存储单元:由于边沿D触发器具有存储功能,因此可以作为存储单元使用。

多个边沿D触发器可以组成一个寄存器,用于存储和传输数据。

(3) 状态机设计:状态机是一种常见的逻辑电路,在许多数字系统中都有应用。

边沿D触发器可以作为状态机中状态转换的触发器使用,实现状态转换和状态保持功能。

4. 性能特点边沿D触发器具有以下几个性能特点:(1) 同步性:边沿D触发器具有同步性,即输出值的变化与时钟信号的边沿到来同步。

这样可以确保在时钟信号稳定之后再进行数据传输,避免了由于时钟抖动等原因引起的数据错误。

数电研讨-用CMOS传输门和CMOS非门设计边沿D触发器

数字电子技术研究性学习报告用CMOS传输门和CMOS非门设计边沿D触发器学院:电子信息工程学院指导教师:侯建军本文主要研究了用CMOS传输门和CMOS非门设计边沿D触发器。

首先分析CMOS传输门和CMOS与非门原理;然后设计出CMOS传输门和CMOS非门设计边沿D触发器;阐述电路工作原理;写出特征方程,画出特征表,激励表与状态图;计算出激励信号D的保持时间和时钟CP的最大频率;将设计的D触发器转换成JK触发器和T触发器,最后对CMOS构成的D触发器进行辨证分析。

关键词CMOS传输门 CMOS非门边沿D触发器最大频率辨证思想AbstractThis paper mainly studied how to use CMOS transmission door and CMOS gate design edge D flip-flop. Firstly analyzes CMOS transmission door and CMOS nand gate principle; Then design a CMOS transmission door and CMOS gate design edge D flip-flop; This circuit principle of work, Write characteristic equation, draw the feature list, incentive table and state diagram; To calculate the excitation signal D retention time and clock CP's maximum frequency; The design of the D flip-flop into JK flip-flop and T trigger, the CMOS a D flip-flop syndrome differentiation and analysis.Key words: CMOS transmission door;CMOS gate edge;D flip-flop; maximum frequency dialectic thought摘要 (2)Abstract (2)第一章基本器件结构图以及功能 (5)1.1 CMOS传输门 (5)1.2 CMOS反相器 (5)1.2.1电压传输特性和电流传输特性 (5)1.2.2 CMOS反相器特点 (6)第二章设计方案一 (7)2.1设计思路 (7)2.2性能评估 (7)第三章设计方案二 (8)3.1 电路结构图 (8)3.2工作原理 (8)3.3 性能评估 (9)第四章设计方案三 (9)4.1电路结构图 (9)4.2工作原理 (10)4.3性能评估 (10)4.4 方案对比 (10)第五章激励信号D的保持时间和时钟CP的最大频率 (11)5.1分析与结论 (11)第六章写出特征方程,画出特征表,激励表与状态图 (11)6.1特征方程 (11)6.2特征表(如表5-1) (11)6.3激励表(如表5-2) (11)6.4状态转换图(如图8) (12)第七章设计拓展 (12)7.1思想启发 (12)7.2功能简述 (12)7.3电路结构 (12)7.3.1 由CMOS传输门和CMOS反相器构成的异或门 (12)7.3.2 抢答器结构图如图10 (13)7.3.3 工作原理 (14)7.4 电路的改进 (15)7.4.1 改进的原因 (15)第八章将设计的D触发器转换成JK触发器和T触发器 (15)8.1 D触发器转换成JK触发器(如图14) (15)8.2 D触发器转成T触发器(如图15) (16)第九章收获与感想 (16)致谢 (17)参考文献 (17)第一章基本器件结构图以及功能1.1 CMOS传输门图1原理:所谓传输门(TG)就是一种传输模拟信号的模拟开关。

基于CMOS传输门CMOS非门设计边沿D触发器的研究

目录摘要、前言---------------------------------------------------------------------3 一概述---------------------------------------------------------------------------4 二CMOS边沿D触发器---------------------------------------------------5 三设计目的及要求----------------------------------------------------------5 四电路组成结构-------------------------------------------------------------8 五电路工作原理-------------------------------------------------------------9 六特征方程、表、图-------------------------------------------------------9 七脉冲特性------------------------------------------------------------------10 八集成触发器---------------------------------------------------------------10 九异步置位、复位设计---------------------------------------------------11 十触发器转换---------------------------------------------------------------12 十一CMOS触发器在时钟边沿工作特性研究-----------------------14 十二CMOS D触发器CD4013的脉冲宽度检测电路--------------20 十三芯片对比---------------------------------------------------------------22 十四总结与感想------------------------------------------------------------25 参考文献---------------------------------------------------------------------26摘要:边沿D触发器在教材里的是维持阻塞边沿D触发器,使用TTL管制成的,而本文的作法是采用了创新手法:即用CMOS传输门和非门来做边沿D触发器。

经常利用CMOS传输门组成电平触发D触发器

CLK = 1时,与SR锁存器工作原理相同。

上页

2

下页

返回

第二节 电平触发的触发器

同步RS触发器的特性表

S

CLK

G3

CLK

G1

Q

R

G4

G2

Q

电路结构

0 0 1 1 1 1 1 1 1 1

0 0 1 1 0 0 1 1

S

0 0 0 0 1 1 1 1

R

Q

0 1 0 1 0 1 0 1 0 1

CLK

[例5.2.2] 若用 CMOS传输门组成 的电平触发D触发 器的CLK和输入端 D的电压波形如右 图中所给出,画出 Q和Q'端的电压波 形。假定触发器的 初始状态为Q=0

O

D

O

Q

t t

O Q O

t t

上页 返回

9

在CMOS电路中,经常利用CMOS传输门组成电平 触发D触发器。

C

D

TG1

Q

C C C

CLK

C

TG2

Q

C

利用CMOS传输门组成的电平触发D触发器

因为在CLK的有效电平期间输出状态始终跟随输入状 态变化,输出与输入的状态相同,所以又将这个电 路称为“透明的D型锁存器”。

上页

8

下页

返回

第二节 电平触发的触发器

第二节 电平触发的触发器

第二节 电平触发的触发器

电路结构与工作原理

电平触发方式的动作特点

推出 下页 总目录

1

第二节 电平触发的触发器

一、电路结构与工作原理

S

CLK

G3

G1

Q

CLK

CMOS锁存器 D触发器

2021/7/5

CMOS 锁存器

CMOS锁存器的瞬态仿真波形

2021/7/5

2021/7/5

任务要求

• 画出D latch的线路图,并设计尺寸为 :PMOS(10u/2u),NMOS(5u/2u)

• 验证DRC,LVS。---以上为选做 • 撰写项目单7

2021/7/5

作业(最后一次)

• D-latch由几个晶体管构成,分别是什么 作用?简述D-latch的工作原理?

• 如果输入信号在D-latch锁存的瞬间发生 变化, D-latch会出现什么状况?

• 主从式DFF是什么结构,每一级D-latch 结构的作用是什么?

数字集成电路设计基础

CMOS锁存器与 CMOS主从D型触发器

2021/7/5

CMOS 锁存器

CMOS琐存器线路模块

C

TG1

D

INV1

2021/7/5

C

TG2

C

Q

锁存器的线路图

2021/7/5

CMOS 锁存器

CMOS锁存器的工作原理: CMOS锁存器有两种状态:传输或保持。 传输:

• 请画出DFF工作的输入信号,输出信号 ,时钟信号的波形图。

2021/7/5

后面任务:

• 先下发课程设计的选题资料,下周正式 开始课程设计。

2021/7/5

的输出端tq,这时将主触发器与从触发器连接的传输门 是截止的,传送进从触发器的d信号并不能送入主触发 器,主触发器中的另一个传输门导通,主触发器处于保 持状态,输出保持为原来的输出不变.

边沿D 触发器介绍

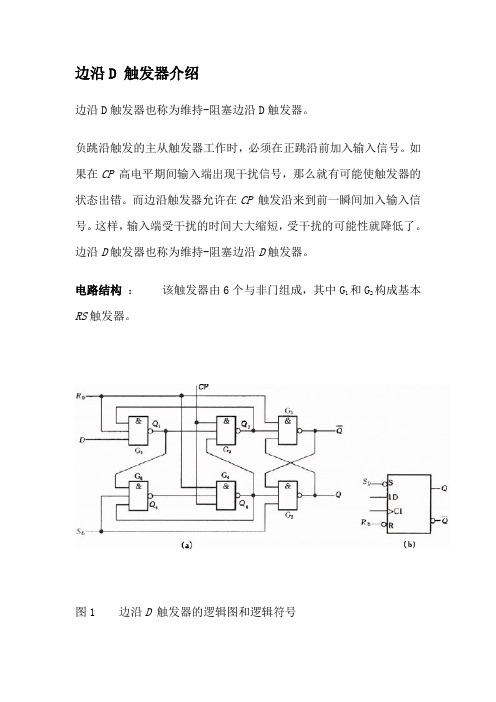

边沿D 触发器介绍边沿D触发器也称为维持-阻塞边沿D触发器。

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。

如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。

而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。

这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。

边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构:该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

图1 边沿D 触发器的逻辑图和逻辑符号工作原理:S D 和R D 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。

当S D=0且R D=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当S D=1且R D=0时,触发器的状态为0,S D和R D通常又称为直接置1和置0端。

我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。

同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。

这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。

Q3=Q5=D,Q4=Q6=D。

由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。

这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。

Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。

Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字电子技术研究性学习报告用CMOS传输门和CMOS非门设计边沿D触发器学院:电子信息工程学院指导教师:侯建军本文主要研究了用CMOS传输门和CMOS非门设计边沿D触发器。

首先分析CMOS传输门和CMOS与非门原理;然后设计出CMOS传输门和CMOS非门设计边沿D触发器;阐述电路工作原理;写出特征方程,画出特征表,激励表与状态图;计算出激励信号D的保持时间和时钟CP的最大频率;将设计的D触发器转换成JK触发器和T触发器,最后对CMOS构成的D触发器进行辨证分析。

关键词CMOS传输门 CMOS非门边沿D触发器最大频率辨证思想AbstractThis paper mainly studied how to use CMOS transmission door and CMOS gate design edge D flip-flop. Firstly analyzes CMOS transmission door and CMOS nand gate principle; Then design a CMOS transmission door and CMOS gate design edge D flip-flop; This circuit principle of work, Write characteristic equation, draw the feature list, incentive table and state diagram; To calculate the excitation signal D retention time and clock CP's maximum frequency; The design of the D flip-flop into JK flip-flop and T trigger, the CMOS a D flip-flop syndrome differentiation and analysis.Key words: CMOS transmission door;CMOS gate edge;D flip-flop; maximum frequency dialectic thought摘要 (2)Abstract (2)第一章基本器件结构图以及功能 (5)1.1 CMOS传输门 (5)1.2 CMOS反相器 (5)1.2.1电压传输特性和电流传输特性 (5)1.2.2 CMOS反相器特点 (6)第二章设计方案一 (7)2.1设计思路 (7)2.2性能评估 (7)第三章设计方案二 (8)3.1 电路结构图 (8)3.2工作原理 (8)3.3 性能评估 (9)第四章设计方案三 (9)4.1电路结构图 (9)4.2工作原理 (10)4.3性能评估 (10)4.4 方案对比 (10)第五章激励信号D的保持时间和时钟CP的最大频率 (11)5.1分析与结论 (11)第六章写出特征方程,画出特征表,激励表与状态图 (11)6.1特征方程 (11)6.2特征表(如表5-1) (11)6.3激励表(如表5-2) (11)6.4状态转换图(如图8) (12)第七章设计拓展 (12)7.1思想启发 (12)7.2功能简述 (12)7.3电路结构 (12)7.3.1 由CMOS传输门和CMOS反相器构成的异或门 (12)7.3.2 抢答器结构图如图10 (13)7.3.3 工作原理 (14)7.4 电路的改进 (15)7.4.1 改进的原因 (15)第八章将设计的D触发器转换成JK触发器和T触发器 (15)8.1 D触发器转换成JK触发器(如图14) (15)8.2 D触发器转成T触发器(如图15) (16)第九章收获与感想 (16)致谢 (17)参考文献 (17)第一章基本器件结构图以及功能1.1 CMOS传输门图1原理:所谓传输门(TG)就是一种传输模拟信号的模拟开关。

CMOS传输门(如图1)由一个P沟道和一个N沟道增强型MOS管并联而成,如上图所示。

设它们的开启电压|VT|=2V且输入模拟信号的变化范围为0V到+5V。

为使衬底与漏源极之间的PN结任何时刻都不致正偏,故T2的衬底接+5V电压,而T1的衬底接地。

传输门的工作情况如下:当C端接低电压0V时T1的栅压即为0V,vI取0V 到+5V范围内的任意值时,TN均不导通。

同时,TP的栅压为+5V,TP亦不导通。

可见,当C端接低电压时,开关是断开的。

为使开关接通,可将C端接高电压+5V。

此时T1的栅压为+5V,vI在0V到+3V的范围内,TN导通。

同时T2的棚压为-5V,vI在2V到+5V的范围内T2将导通。

由上分析可知,当vI<+3V时,仅有T1导通,而当vI>+3V时,仅有T2导通当vI在2V到+3V的范围内,T1和T2两管均导通。

进一步分析还可看到,一管导通的程度愈深,另一管的导通程度则相应地减小。

换句话说,当一管的导通电阻减小,则另一管的导通电阻就增加。

由于两管系并联运行,可近似地认为开关的导通电阻近似为一常数。

这是CMOS传输出门的优点。

1.2 CMOS反相器1.2.1电压传输特性和电流传输特性CMOS反相器的电压传输特性曲线可分为五个工作区。

(如图2)图2工作区Ⅰ:由于输入管截止,故vO=VDD,处于稳定关态。

工作区Ⅲ:PMOS和NMOS均处于饱和状态,特性曲线急剧变化,vI值等于阈值电压Vth。

工作区Ⅴ:负载管截止,输入管处于非饱和状态,所以vO≈0V,处于稳定的开态。

CMOS反相器的电流传输特性曲线如图3,只在工作区Ⅲ时,由于负载管和输入管都处于饱和导通状态,会产生一个较大的电流。

其余情况下,电流都极小。

图31.2.2 CMOS反相器特点静态功耗极低。

在稳定时,CMOS反相器工作在工作区Ⅰ和工作区Ⅴ,总有一个MOS管处于截止状态,流过的电流为极小的漏电流。

抗干扰能力较强。

由于其阈值电平近似为0.5VDD,输入信号变化时,过渡变化陡峭,所以低电平噪声容限和高电平噪声容限近似相等,且随电源电压升高,抗干扰能力增强。

电源利用率高。

VOH=VDD,同时由于阈值电压随VDD变化而变化,所以允许VDD有较宽的变化范围,一般为+3~+18V。

输入阻抗高,带负载能力强。

第二章设计方案一2.1设计思路最初拿到这个题,感觉有些难度,相比直接由CMOS传输门和COMS反相器设计出D触发器,我感觉由以上两种器件设计出与非门较简单。

设计出的与非门如图4。

2.2性能评估1. 构成较复杂:由于一个两输入的与非门就需要8个传输门以及10个非门,若需要三输入的与非门则需要更多的传输门以及与非门,所以电路构成复杂。

2.电路利用率较低:当一条支路通路时,其他之图4路处于闲置状态,所以电路的利用率低。

第三章设计方案二3.1 电路结构图图53.2工作原理如图5。

当cp低电平时,TG1导通、TG2截止,D信号经过传输门输入,=、Q=D,电路输出Q跟随D信号变化。

当cp上升沿时,TG1截止、TG2导通,D信号不能传输,D信号的改变对输出不会产生影响,输出端的两个非门首尾相连,保持上升沿时刻的状态不变。

此方案由手动开启和关闭传输门来体现D触发器的特性。

波形如图6。

由图6可知,若CP上升前,即D触发器关闭前,输入D发生突变,输出会有影响。

3.3 性能评估1.元件数量少:整个电路只需要5个元件,包括两个传输门以及三个非门。

2.传输时间短:信号经过电路时,只需要通过三个非门和一个传输门即可输出。

传输时间大概为40ns。

3.功耗小:组成电路的元器件都为CMOS元器件,功耗小。

4.人性化:可人为手动控制。

若输入了错误信号,则可在时钟上升沿到来前进行改正。

5.抗干扰能力不强:在时钟上升沿到来之前,传输门一直处于开启状态。

如果在时钟上升沿到来前,信号发生了突变,则导致输出了错误的信号,所以抗干扰能力有待提高。

图6第四章设计方案三4.1电路结构图图74.2工作原理如图7。

当CP的上升沿到达时,TG1截止,TG2导通,切断了D信号的输入,由于G1的输入电容存储效应,G1输入端电压不会立即消失,于是Q、在TG1截止前的状态被保存下来;同时由于TG3导通、TG4截止,主触发器的状态通过TG3和G3送到了输出端,使Q=D(CP上升沿到达时D的状态),而=。

在CP高电平期间, Q=D, =的状态一直不会改变,直到CP下降沿到达时,TG2、TG3又截止,TG1、TG4又导通,主触发器又开始接收D端新数据,从触发器维持已转换后的状态。

可见,这种触发器的动作特点是输出端的状态转换发生在CP的上升沿,而且触发器所保持的状态仅仅取决于CP上升沿到达时的输入状态。

正因为触发器输出端状态的转换发生在CP的上升沿(即CP的上升沿),所以这是一个CP 上升沿触发的边沿触发器,CP上升沿为有效触发沿,或称CP上升沿为有效沿(下降沿为无效沿)。

4.3性能评估1.传输时间较短:信号经过电路时,需要通过三个非门和三个传输门即可输出。

传输时间大概为60ns。

2.功耗较小:组成电路的元器件都为CMOS元器件,功耗小。

3.抗干扰能力强:传输门只于上升沿到来前后几十纳秒内处于开启状态,其他时间都处于关闭状态,此时信号无法输入。

因此只要保证信号在上升沿到来前后20ns内保持不变即可将信号准确地传输。

所以抗干扰能力强。

4.电子元器件较多,成本略高:一个触发器需要9个原件,其中包括4个传输门以及5个非门。

所以成本略高。

4.4 方案对比表4-1通过两种方案(表4-1)的对比可以根据其性能以及自身需求对此两种方案进行合理选择。

第五章激励信号D的保持时间和时钟CP的最大频率5.1分析与结论假设,信号通过传输门及反相器的时间为t1。

D信号的保持时间需大于3t1,才能保证D信号能够存储下来。

如果CP下降沿后,D信号才被锁存,在此期间如果D信号有突变,将影响输出结果,所以电路需保证D信号存储后CP再变为低电平,也就是说CP高电平的时间需大于3t1,设CP周期为TCP,则推出的解释即为CP需满足0.5TCP大于3t1,即fCP 小于1/6t1。

第六章写出特征方程,画出特征表,激励表与状态图6.1特征方程6.2特征表(如表5-1)n+1X X Q n0011表5-1 特征表6.3激励表(如表5-2)Q n Q n+1D000011100111表5-2 激励表6.4状态转换图(如图8)图8第七章设计拓展7.1思想启发本次研究性学习主要是使用CMOS传输门和CMOS反相器设计D触发器。

但为了加深我对电子元器件的理解并充分锻炼我的设计能力,我想到用CMOS传输门和CMOS反相器设计一个抢答器。

7.2功能简述此电路中有N个输入和N个输出,每个人对应各自的一个输出,每个输出端各连接一个灯。