FIFO Verilog

FIFO缓存,Verilog

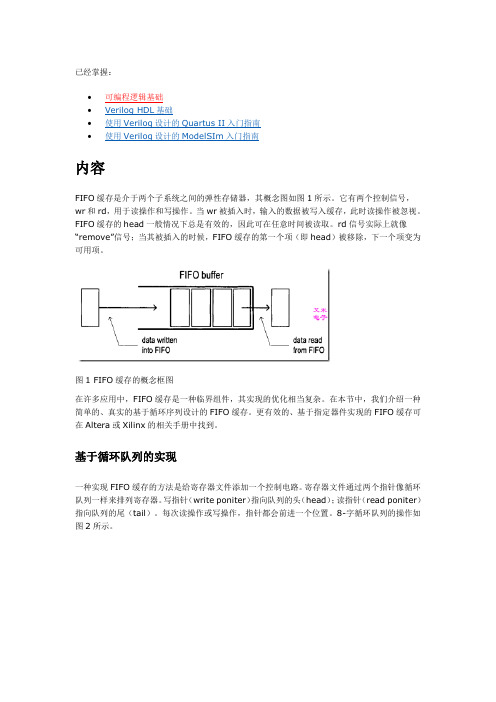

已经掌握:∙可编程逻辑基础∙Verilog HDL基础∙使用Verilog设计的Quartus II入门指南∙使用Verilog设计的ModelSIm入门指南内容FIFO缓存是介于两个子系统之间的弹性存储器,其概念图如图1所示。

它有两个控制信号,wr和rd,用于读操作和写操作。

当wr被插入时,输入的数据被写入缓存,此时读操作被忽视。

FIFO缓存的head一般情况下总是有效的,因此可在任意时间被读取。

rd信号实际上就像“remove”信号;当其被插入的时候,FIFO缓存的第一个项(即head)被移除,下一个项变为可用项。

图1 FIFO缓存的概念框图在许多应用中,FIFO缓存是一种临界组件,其实现的优化相当复杂。

在本节中,我们介绍一种简单的、真实的基于循环序列设计的FIFO缓存。

更有效的、基于指定器件实现的FIFO缓存可在Altera或Xilinx的相关手册中找到。

基于循环队列的实现一种实现FIFO缓存的方法是给寄存器文件添加一个控制电路。

寄存器文件通过两个指针像循环队列一样来排列寄存器。

写指针(write poniter)指向队列的头(head);读指针(read poniter)指向队列的尾(tail)。

每次读操作或写操作,指针都会前进一个位置。

8-字循环队列的操作如图2所示。

图2 基于循环队列的FIFO缓存FIFO缓存通常包括两个标志信号,full和empty,相应地来指示FIFO满(即不可写)或FIFO 空(即不可读)。

这两种情况发生在读指针和写指针相等的时候,如图2(a)、(f)和(i)所示的情况。

控制器最难的设计任务是获取一种分辨这两种情形的机制。

一种方案是使用触发器来跟踪empty和full标志。

当系统被初始化时,触发器被设置为1和0;然后在每一个时钟周期根据wr和rd的值来修改。

代码FIFO缓存代码被分为寄存器文件和FIFO控制器两部分。

控制器由两个指针和两个标志触发器组成,它们的次态逻辑会检测wr和rd信号,以采取相应的动作。

verilogfifo读写详细讲解

verilogfifo读写详细讲解FIFO是一种先进先出的数据结构,其全称为First-In-First-Out。

在Verilog中,可以使用以下代码实现FIFO的读写操作。

首先,我们需要定义FIFO的模块。

如下所示:```verilogmodule fifo #(parameter DATA_WIDTH = 8) (input clk, // 时钟信号input reset, // 复位信号input read, // 读使能信号input write, // 写使能信号input [DATA_WIDTH-1:0] data_in, // 输入数据output reg [DATA_WIDTH-1:0] data_out, // 输出数据output reg empty, // FIFO为空信号output reg full // FIFO为满信号);```在FIFO的模块中,我们定义了以下信号:clk表示时钟信号,reset表示复位信号,read表示读使能信号,write表示写使能信号,data_in表示输入数据,data_out表示输出数据,empty表示FIFO为空信号,full表示FIFO为满信号。

在模块的内部,我们可以使用一个或多个寄存器来实现FIFO的功能。

在这里,我们使用两个寄存器data_reg和next_data_reg来存储数据,使用两个计数器empty_count和full_count来记录FIFO的空和满状态。

```verilogreg [DATA_WIDTH-1:0] data_reg; // 数据寄存器reg [DATA_WIDTH-1:0] next_data_reg; // 下一个数据寄存器reg [DATA_WIDTH-1:0] data_out_reg; // 输出数据寄存器reg empty_count; // 空计数器reg full_count; // 满计数器```接下来,我们定义FIFO的行为。

verilog hdl语言100例详解

verilog hdl语言100例详解Verilog HDL语言是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

它是硬件设计工程师在数字电路设计中的重要工具。

本文将介绍100个例子,详细解释Verilog HDL语言的应用。

1. 基本门电路:Verilog HDL可以用于描述基本门电路,如与门、或门、非门等。

例如,下面是一个描述与门电路的Verilog HDL代码:```verilogmodule and_gate(input a, input b, output y);assign y = a & b;endmodule```2. 多路选择器:Verilog HDL也可以用于描述多路选择器。

例如,下面是一个描述2:1多路选择器的Verilog HDL代码:```verilogmodule mux_2to1(input a, input b, input sel, output y);assign y = sel ? b : a;endmodule```3. 寄存器:Verilog HDL可以用于描述寄存器。

例如,下面是一个描述8位寄存器的Verilog HDL代码:```verilogmodule register_8bit(input [7:0] d, input clk, input reset, output reg [7:0] q);always @(posedge clk or posedge reset)if (reset)q <= 0;elseq <= d;endmodule```4. 计数器:Verilog HDL可以用于描述计数器。

例如,下面是一个描述8位计数器的Verilog HDL代码:```verilogmodule counter_8bit(input clk, input reset, output reg [7:0] count);always @(posedge clk or posedge reset)if (reset)count <= 0;elsecount <= count + 1;endmodule```5. 加法器:Verilog HDL可以用于描述加法器。

alterafifoIP核使用verilog代码

ALTERA FIFO IP 核使用verilog 代码FIFO ,在FPGA 中是一种非常基本,使用非常广泛的模块。

FPGA 高手可能觉得不值一提,但对于像我这样的新手,但对于像我这样的新手,有时却是个大问题,有时却是个大问题,有时却是个大问题,弄了一个多月,弄了一个多月,弄了一个多月,总算有所进展,希望把自己的总算有所进展,希望把自己的一些总结写下来,一方面希望对其他入门者有所帮助,另一方面希望看到的高手们批评指正。

另外得特别感谢特权同学的教程,没有大神的指导,他的教程确实不错。

另外得特别感谢特权同学的教程,没有大神的指导,他的教程确实不错。

在大学中编了两年单片机(断断续续),C 语言的串行思维深入人心,一下子转换到FPGA并行的工作方式和有些奇异的编程风格,一开始还真有点处理不好。

另一方面,对FPGA 各种延迟非常困惑,比如RAM 模块读取延迟,FIFO 读取数据延迟等,常常不知道如何处理。

下面说说我现在的理解和解决办法。

下面说说我现在的理解和解决办法。

FPGA 写入数据写入相对简单,只需要在时钟上升沿来临之时使能wrreq 和写入data ,当然还需要判断FIFO full 信号。

时序图如下,在第一个时钟之前使能wrreq 信号,在第一个时钟及以后的几个时钟上升沿FIFO 判断wrreq 有效并且读入数据。

有效并且读入数据。

一份参考的代码如下一份参考的代码如下reg [7:0] fifo_wcnt; always @(posedge led or negedge rst) begin if (~rst) begin fifo_wreq<=1'b0; fifo_wdat<=0; fifo_wcnt<=0;//测试数据测试数据endelsebegin if(~fifo_wfull)begin//FIFO 没有写满的时候就写入数据没有写满的时候就写入数据fifo_wcnt<=fifo_wcnt+1'b1; fifo_wreq<=1'b1; fifo_wdat<=fifo_wcnt+8'd2; end else begin fifo_wreq<=1'b0; end end end 这里fifo_wfull 值得注意,在没有延迟的时候这个信号可以直接为FIFO 直接输出的full 信号,但实际中通常都会有一个或者多个时钟的延迟。

verilog fifo原理

verilog fifo原理FIFO(FirstInFirstOut)是一种常用的存储器结构,用于在数据传输过程中暂存数据。

在数字电路和系统设计中,FIFO被广泛应用于数据缓存、接口通信等领域。

本文将介绍VerilogFIFO的基本原理和设计方法。

一、FIFO的结构FIFO通常由输入端、输出端和存储器组成。

输入端和输出端分别对应数据的输入和输出,而存储器则用于暂存数据。

FIFO的读写操作遵循FIFO的先进先出(FIFO)原则,即最早进入FIFO的数据最先被读取。

在Verilog中,可以使用模块(module)和语句(statement)来实现FIFO。

常见的VerilogFIFO结构包括数据寄存器(dataregister)、读写指针(read/writepointer)、存储器单元(memorycell)和控制逻辑(controllogic)等部分。

二、FIFO的工作原理1.读写操作FIFO的读写操作遵循FIFO的基本原则。

在写操作时,新数据被写入存储器;在读操作时,最早进入FIFO的数据最先被读取。

控制逻辑负责管理读写指针,以确保正确的读写操作顺序。

2.缓冲作用FIFO的主要作用是缓冲数据,即在数据传输过程中,将输入端的数据存储到FIFO中,待FIFO满后再从输出端输出数据。

这样可以在一定程度上缓解数据传输的时序问题,提高数据传输的可靠性和效率。

3.溢出和欠流控制当FIFO满时,控制逻辑会停止新的写操作,以避免数据溢出。

同样地,当FIFO空时,控制逻辑会暂停新的读操作,以防止欠流(underflow)现象的发生。

这些控制逻辑的实现通常需要借助状态机(statemachine)和条件语句(conditionstatement)等Verilog语言特性。

以下是一个简单的VerilogFIFO设计示例:modulefifo(inputwireclk,reset,en_write,en_read,outputwire [7:0]data_out);reg[7:0]data_reg[15:0];//数据寄存器regread_pointer,write_pointer;//读写指针integeri;parameterSIZE=16;//FIFO容量//控制逻辑和状态机always@(posedgeclkorposedgereset)beginif(reset)beginread_pointer<=0;//复位时读写指针都归零write_pointer<=0;for(i=0;i<SIZE;i=i+1)begindata_reg[i]<=8'h00;//清空FIFOendendelseif(en_write)begindata_reg[write_pointer]<={data_reg[write_pointer],data_in };//新数据写入FIFOwrite_pointer<=write_pointer+1;//写指针加一if(write_pointer==SIZE)write_pointer<=0;//FIFO满时归零写指针endelseif(en_read)begindata_out<=data_reg[read_pointer];//读出最早进入FIFO的数据read_pointer<=read_pointer+1;//读指针加一if(read_pointer==SIZE)read_pointer<=0;//FIFO空时归零读指针endelsebegin//其他情况不做处理endendendmodule以上示例中,我们使用了一个16位的数据寄存器和两个指针(read_pointer和write_pointer)来管理FIFO的读写操作。

system verilog 中进程间通讯的常用机制

system verilog 中进程间通讯的常用机制SystemVerilog是一种硬件描述语言,用于设计和验证复杂的数字系统。

在SystemVerilog中,进程间通信是设计和验证中一个重要的方面。

本文将介绍SystemVerilog中进程间通信的常用机制。

一、FIFO队列FIFO(First In, First Out)队列是SystemVerilog中最常用的进程间通信机制之一。

它可以实现单个或多个生产者与单个或多个消费者之间的数据传输。

FIFO队列由一组寄存器组成,其中包含用于存储和传输数据的缓冲区。

FIFO队列通常具有读指针和写指针,用于指示下一个要读取的数据和下一个要写入的数据的位置。

当生产者向队列中写入数据时,写指针递增,当消费者从队列中读取数据时,读指针递增。

通过读取和写入指针的比较,可以确定队列是否为空或已满。

二、信号量信号量是另一种常见的进程间通信机制。

它用于控制共享资源的访问。

信号量有一个计数器,在资源被占用时递减,在资源释放时递增。

当计数器为零时,其他进程需要等待资源可用。

在SystemVerilog中,可以使用`semaphore`关键字定义信号量。

通过使用`wait()`和`signal()`方法,进程可以申请和释放信号量。

三、事件事件是SystemVerilog中用于进程同步的常见机制之一。

事件表示某个特定条件是否满足。

当事件发生时,其他进程可以通过等待该事件来进行进一步操作。

SystemVerilog中,可以使用`event`关键字定义事件。

通过使用`->`操作符,可以将事件关联到条件或表达式上。

四、互斥锁互斥锁是用于保护共享资源的进程同步机制。

只有一个进程可以获得互斥锁,并访问被保护的资源。

其他进程需要等待互斥锁被释放后才能访问资源。

在SystemVerilog中,可以使用`lock()`和`trylock()`方法获取互斥锁,并使用`unlock()`方法释放互斥锁。

verilog基本电路设计(包括:时钟域同步、无缝切换、异步fifo、去抖滤波))

Verilog基本电路设计(包括:时钟域同步、无缝切换、异步FIFO、去抖滤波))Verilog基本电路设计共包括四部分:单bit跨时钟域同步时钟无缝切换异步FIFO去抖滤波Verilog基本电路设计之一: 单bit跨时钟域同步(帖子链接:/thread-605419-1-1.html)看到坛子里不少朋友,对于基本数字电路存在这样那样的疑惑,本人决定开贴,介绍数字电路最常见的模块单元,希望给初学者带来帮助,也欢迎大佬们前来拍砖。

如果想要做数字设计,下面这些电路是一定会碰到的,也是所有大型IP,SOC设计必不可少的基础,主要包括异步信号的同步处理,同步FIFO,异步FIFO,时钟无缝切换,信号滤波debounce等等,后面会根据大家反馈情况再介绍新电路。

首先介绍异步信号的跨时钟域同步问题。

一般分为单bit的控制信号同步,以及多bit的数据信号同步。

多bit的信号同步会使用异步FIFO完成,而单bit的信号同步,又是时钟无缝切换电路以及异步FIFO电路的设计基础,这里先介绍单bit信号同步处理。

clka域下的信号signal_a,向异步的clkb域传递时,会产生亚稳态问题。

所有的亚稳态,归根结底就是setup/hold时间不满足导致。

在同一个时钟域下的信号,综合以及布线工具可以在data路径或者clock路径上插入buffer使得每一个DFF的setup/hold时间都满足;但是当signal_a在clkb域下使用时,由于clka与clkb异步,它们的相位关系不确定,那么在clkb的时钟沿到来时,无法确定signal_a此时是否处于稳定无变化状态,也即setup/hold时间无法确定,从而产生亚稳态。

这种异步信号在前后端流程里面是无法做时序分析的,也就是静态时序分析里常说的false_path。

消除亚稳态,就是采用多级DFF来采样来自另一个时钟域的信号,级数越多,同步过来的信号越稳定。

对于频率很高的设计,建议至少用三级DFF,而两级DFF同步则是所有异步信号处理的最基本要求。

verilog同步和异步FIFO,可直接仿真和综合解读

EDA/SOPC课程设计报告题目:同异步FIFO模块的设计与验证姓名:xxx学号:120260320同组人:xxx指导教师:xxx成绩:目录目录 (II)第1章课程设计的要求 (1)1.1 课程设计的目的 (1)1.2 课程设计的条件 (1)1.3 课程设计的要求 (1)第2章课程设计的内容 (2)2.1 设计思路 (2)2.2 软件流程图 (2)2.3 HDL代码阐述 (2)2.4 ModelSim验证 (2)第3章课程设计的心得 (3)第1章课程设计的要求1.1 课程设计的目的●掌握FIFO设计的基本原理与方法●培养Verilog语言模块化设计的思想意识●完成一个FIFO的设计与验证●掌握较大工程的基本开发技能●培养综合运用Modelsim工具进行硬件开发的能力●培养数字系统设计的基本能力●加强对课堂Verilog语言学习的理解与升华1.2 课程设计的条件●设计条件ISE、Modelsim等开发软件的使用1.3 课程设计的要求●设计要求1 设计同步FIFO并验证(包括仿真验证、FPGA验证)●设计要求2 设计异步FIFO并验证(包括仿真验证、FPGA验证)●设计要求3 采用Design Compiler完成其逻辑综合,评估其面积和时序●设计要求4 完成综合后的SDF反标仿真第2章课程设计的内容2.1 设计思路FIFO(First Input First Output),即先进先出队列。

在计算机中,先入先出队列是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令(指令就是计算机在响应用户操作的程序代码,对用户而言是透明的)。

如下图所示,当CPU在某一时段来不及响应所有的指令时,指令就会被安排在FIFO队列中,比如0号指令先进入队列,接着是1号指令、2号指令……当CPU完成当前指令以后就会从队列中取出0号指令先行执行,此时1号指令就会接替0号指令的位置,同样,2号指令、3号指令……都会向前挪一个位置,这样解释大家清楚了吧?在设计之初,我们只对FIFO有一个模糊的了解,只知道它是一个先入先出的队列,但是对于它是如何组成和如何工作并不了解,于是我们设计的首要任务就是查阅资料,逐步完善我们对于同步FIFO和异步FIFO的了解。

FIFO的verilog语言代码(含测试代码)

fullp <= 1'b0;

end

endmodule

/*******************************************************************************************/

测试程序:

module test_fifo;

count <= count - 1; //为读状态计数器进行减法计数

2'b11:

count <= count;

endcase

end

end

always @(count) begin

if (count == 2'b00)

tail <= 2‘b00; //复位

end

else begin

if (readp == 1'b1 && emptyp == 1'b0) begin

tail <= tail + 1;

end

end

FIFO存储器的设计(后面是测试程序的部分)

module fifo (clk, rstp, din, writep, readp, dout, emptyp, fullp);

input clk;

input rstp; //复位信号

input [15:0] din;

input readp; //读信号

read_word;

end

#50;

end

end

join

end

endtask

endmodule

end

实现fifo的关键代码

实现FIFO的关键代码实现该FIFO的关键部分verilog代码如下:(1)将指向下一个读地址的读指针转为格雷码表示:assign rgraynext = (rbinnext >> 1)^rbinnext。

(2)将指向下一个写地址的写指针转为格雷码表示:assign wgraynext = (wbinnext >> 1)^wbinnext。

(3)将读指针用两级触发器与写时钟同步:always @(posedge wclk or negedge wrst_n)if(!wrst_n) {wq2_rptr,wq1_rptr} <= 0;else {wq2_rptr,wq1_rptr} <= {wq1_rptr,rptr};(4)将写指针用两级触发器与读时钟同步:always @(posedge rclk or negedge rrst_n)if(!rrst_n) {rq2_wptr,rq1_wptr} <= 0;else {rq2_wptr,rq1_wptr} <= {rq1_wptr,wptr};(5)产生写满标志:assignwfull_val = (wgraynext == {~wq2_rptr[ADDRSIZE:ADDRSIZE-1],wq2_rptr[ADDRSIZE-2:0]});always @ (posedge wclk or negedge wrst_n)if(!wrst_n) wfull <= 1’b0;else wfull<= wfull_val;(6)产生读空标志:assign rempty_val = (rgraynext == rq2_wptr);always @ (posedge rclk or negedge rrst_n)if(!rrst_n) rempty <= 1’b1;else rempty<= rempty_val;(7)产生FIFO存储单元,并写入、读出数据:always@ (posedge wclk)if(winc&&!wfull) mem[waddr] <= wdataassign rdata = gp15?mem[raddr] : 16’bzzzzzzzzzzzzzzzz;。

同步FIFO的Verilog代码

ÍFIFOµÄVerilog?úÂëmodule fifo_syn(datain,rd,wr,rst,clk,dataout,full,empty);input [7:0] datain;input rd, wr, rst, clk;output [7:0] dataout;output full, empty;reg [7:0] dataout;reg full_in, empty_in;reg [7:0] mem [15:0];reg [3:0] rp, wp;assign full = full_in;assign empty = empty_in;// memory read out ÉÔ×?ÐÞ?Äalways@(posedge clk) beginif(rd && ~empty_in) dataout = mem[rp];end// memory write inalways@(posedge clk) beginif(wr && ~full_in) mem[wp]<=datain;end// memory write pointer incrementalways@(posedge clk or negedge rst)if(!rst)wp<=0;else wp <= (wr && ~full_in) ? (wp + 1'b1) : wp;// memory read pointer incrementalways@(posedge clk or negedge rst)if(!rst)rp <= 0;else rp <= (rd && ~empty_in)? (rp + 1'b1): rp;// Full signal generatealways@(posedge clk or negedge rst) beginif(!rst) full_in <= 1'b0;else beginif( (~rd && wr)&&((wp==rp-1) | | (rp==4'h0&&wp==4'hf))) full_in <= 1'b1;else if(full_in && rd) full_in <= 1'b0;endend// Empty signal generatealways@(posedge clk or negedge rst) beginif(!rst) empty_in <= 1'b1;else beginif((rd&&~wr)&&(rp==wp-1 || (rp==4'hf&&wp==4'h0)))empty_in<=1'b1;else if(empty_in && wr) empty_in<=1'b0;endendendmodule******************************************************************** ***********ÍøÉϵÄ?úÂë?ÁÊý?ÝÊä?ö(dataout)Ö??ÊÜ?ÁÊ?ÄÜ(rd)?ØÖÆ??ÏÔÈ?Ô??ËùÒÔÉ Ô×?ÐÞ?ÄÓ,ÅúÆÀ******************************************************************** ******************ÁíÒ?ÖÖ?ç?ñµÄÍFIFOmodule FIFO_Buffer(Data_out,stack_full,stack_almost_full,stack_half_full,stack_almost_empty,stack_empty,Data_in,write_to_stack,read_from_stack,clk,rst);parameter stack_width=32;parameter stack_height=8;parameter stack_ptr_width=3;parameter AE_level=2;parameter AF_level=6;parameter HF_level=4;output [stack_width-1:0] Data_out;output stack_full,stack_almost_full,stack_half_full; output stack_almost_empty,stack_empty;input[stack_width-1:0] Data_in;input write_to_stack,read_from_stack;input clk,rst;reg[stack_ptr_width-1:0] read_ptr,write_ptr;reg[stack_ptr_width:0] ptr_gap;reg[stack_width-1:0] Data_out;reg[stack_width-1:0] stack[stack_height-1:0]; assign stack_full=(ptr_gap==stack_height);assign stack_almost_full=(ptr_gap==AF_level);assign stack_half_full=(ptr_gap==HF_level);assign stack_almost_empty=(ptr_gap==AE_level);assign stack_empty=(ptr_gap==0);always @(posedge clk or posedge rst)if(rst)beginData_out<=0;read_ptr<=0;write_ptr<=0;ptr_gap<=0;endelse if(write_to_stack &&(!stack_full)&&(!read_from_stack))begin stack[write_ptr]<=Data_in;write_ptr<=write_ptr+1;ptr_gap<=ptr_gap+1;endelse if((!write_to_stack)&&(!stack_empty)&&read_from_stack)begin Data_out<=stack[read_ptr];read_ptr<=read_ptr+1;ptr_gap<=ptr_gap-1;endelse if(write_to_stack &&read_from_stack&&stack_empty)begin stack[write_ptr]<=Data_in;write_ptr<=write_ptr+1;ptr_gap<=ptr_gap+1;endelse if(write_to_stack &&read_from_stack&&stack_full)beginData_out<=stack[read_ptr];read_ptr<=read_ptr+1;ptr_gap<=ptr_gap-1;endelseif(write_to_stack&&read_from_stack&&(!stack_full)&&(!stack_empty)) beginData_out<=stack[read_ptr];stack[write_ptr]<=Data_in;read_ptr<=read_ptr+1;write_ptr<=write_ptr+1;endendmoduleÏÔÈ?Õâ?ö?È?ÏÈÝÒ×Àí?â。

使用VerilogHDL实现异步FIFO设计与实现FIFO读写时序[试题]

![使用VerilogHDL实现异步FIFO设计与实现FIFO读写时序[试题]](https://img.taocdn.com/s3/m/32358ffe846a561252d380eb6294dd88d0d23d78.png)

使用Verilog HDL实现异步FIFO设计与实现FIFO 读写时序在现代IC设计中,特别是在模块与外围芯片的通信设计中,多时钟域的情况不可避免。

当数据从一个时钟域传递到另一个域,并且目标时钟域与源时钟域不相关时,这些域中的动作是不相关的,从而消除了同步操作的可能性,并使系统重复地进入亚稳定状态[1]。

在有大量的数据需要进行跨时钟域传输且对数据传输速度要求比较高的场合,异步FIFO 是一种简单、快捷的解决方案。

异步FIFO用一种时钟写入数据,而用另外一种时钟读出数据。

读写指针的变化动作由不同的时钟产生。

因此,对FIFO空或满的判断是跨时钟域的。

如何根据异步的指针信号产生正确的空、满标志,是异步FIFO设计成败的关键。

本文提出一种新颖的异步FIFO设计方案,它通过先比较读写地址并结合象限检测法产生异步的空/满标志,再把异步的空/满标志同步到相应的时钟域。

通过仿真验证,该方法是稳定有效的。

1异步信号传输问题的分析在一个AS IC或FPGA库中,每种触发器都有时序要求。

对于使用上升沿触发的触发器来说,建立时间(Setup Time)是在时钟上升沿到来之前,触发器数据保持稳定的最小时间;而保持时间(Hold Time)是在时钟上升沿到来之后,触发器数据还应该保持的最小时间[2]。

如图1所示,在时钟上升沿前后的这个窗口内数据应该保持不变,否则会使触发器工作在一个不确定的状态,即亚稳态。

当触发器处于亚稳态,且处于亚稳态的时间超过了一个时钟周期时,这种不确定的状态将会影响到下一级的触发器,最终导致连锁反应,从而使整个系统功能失常。

当一个信号跨越某个时钟域时,对新时钟域的电路来说它就是一个异步信号。

由于异步信号之间的时序是毫无关系的,因此必然存在SetupTime/Hold Time冲突。

为了避免亚稳态问题,采用如图2所示的双锁存器法[3],即在一个信号进入另一个时钟域前,将该信号用两个锁存器连续锁存两次,最后得到的采样结果就可以消除亚稳态。

基于verilog hdl的异步FIFO设计

基于verilog hdl的异步FIFO设计陕西理工学院毕业设计题目基于verilog hdl的异步FIFO设计学生姓名薛博阳学号 1113014175所在学院物理与电信工程学院专业班级电子1105 指导教师吴燕 __ ____ __完成地点博远楼实验室年月日第 1 页共 36 页陕西理工学院毕业设计基于Verilog HDL的异步FIFO设计与实现摘要在现代IC设计中,特别是在模块与外围芯片的通信设计中,多时钟域的情况不可避免。

当数据从一个时钟域传递到另一个域,并且目标时钟域与源时钟域不相关时,这些域中的动作是不相关的,从而消除了同步操作的可能性,并使系统重复地进入亚稳定状态,出)存储器来实现。

本文提出一种新颖的异步FIFO设计方案,它通过先比较读写地址并结合象限检测法产生异步的空/满标志,再把异步的空/满标志同步到相应的时钟域。

通过仿真验证,该方法是稳定有效的。

关键词:异步;FIFO;亚稳态;格雷码;结绳法第 2 页共 36 页造成系统时钟时序上的紊乱。

为了有效的解决这个问题,我们采用一种异步FIFO(先进先陕西理工学院毕业设计Design and accomplish asynchronousFIFO based on Verilog HDLAbstractIn modern IC design, particularly in the communications module and peripheral chip design, multiple clock domains of the inevitable. When data passes from one clock domain to another domain, and the target clock domains are not associated with the source clock domain, these domains are not related movements, thus eliminating the possibility of simultaneous operation and allows the system to enter the sub-repeat steady-state, causing disorder on the system clock timing. In order to effectively solve this problem, we use a asynchronous FIFO (FIFO) memory to achieve. This paper proposes a novel asynchronous FIFO design, which compared reading and writing through the first address and generate an asynchronous combination of quadrant detection empty / full flag, then asynchronous empty / full flag synchronized to the corresponding clock domain. The simulation results that the method is stable and effective.Key Words: asynchronous; FIFO; metastable state; Gray code; tie knots France第 3 页共 36 页陕西理工学院毕业设计目录1 引言 (6)1.1 FIFO研究意义 ........................................................6 1.2 生产需求状况 (6)1.3 存储器外发展状况 (7)1.4 FIFO设计技术简介 (9)1.4.1 基于信元的FIFO设计方法 (9)1.4.2 基于SRAM/DRAM的大容量FIFO的设计与实现 ........................ 9 1.5 异步FIFO设计中存在的问题及解决办法 .. (10)1.5.1 亚稳态 (10)1.5.2 空/满指针的解决方法 ........................................... 11 1.6 论文主要内容 ....................................................... 11 2 异步FIFO工作原理简介 . (12)2.1 关于异步信号 ....................................................... 12 2.2 异步FIFO芯片简介 .. (13)2.3 FIFO的一些重要参数 (14)2.4 异步FIFO设计的难点 (15)2.4.1 异步FIFO设计难点概述 (15)2.4.1.1 解决FIFO的满/空技术方法概述和特点 (15)2.4.1.2 亚稳态问题的产生及解决 (15)2.5 FIFO的功能简介 .....................................................16 2.6 Modelsim仿真工具简介 (16)2.6.1 主要特点 (16)2.7 Verilog HDL语言的简介 (17)2.8 HDL语言 (17)2.8.1 HDL与原理图输入法的关系 (17)2.8.2 HDL开发流程 (17)3 异步FIFO实现的技所涉及的技术及其解决方法 (18)3.1格雷码 ..............................................................18 3.2结绳法 (19)4 异步FIFO具体实现方法 ....................................................204.1 亚稳态问题的解决方案 ...............................................204.1.1 问题的产生 (20)4.1.2 常见的解决方法 (21)4.1.2.1 格雷码编码法 (21)4.1.2.2 双触发器法 .............................................. 22 4.1.2.3结绳法 (22)4.2 基于异步比较FIFO逻辑标志的产生 ....................................234.2.1 设计思想 (23)4.2.2 标志位的产生 (24)4.2.2.1 异步比较FI FO逻辑标志与时钟的同步 (24)4.2.2.2 保守的空/满标志 ......................................... 26 4.2.2.3半满、将近满、将近空的产生 (27)第 4 页共 36 页陕西理工学院毕业设计4.2.2.4 FIFO异步空/满信号的同步 (28)4.3 仿真验证和综合 .....................................................28 5 总结 (29)5.1 异步FIFO设计的总结 ................................................29 5.2 设计方法的不足之处 (29)附录一 .....................................................................30 参考文献 (35)第 5 页共 36 页感谢您的阅读,祝您生活愉快。

FIFO同步、异步以及Verilog代码实现

FIFO同步、异步以及Verilog代码实现FIFO 很重要,之前参加的各类电⼦公司的逻辑设计的笔试⼏乎都会考到。

FIFO是英⽂First In First Out 的缩写,是⼀种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使⽤起来⾮常简单,但缺点就是只能顺序写⼊数据,顺序的读出数据, 其数据地址由内部读写指针⾃动加1完成,不能像普通存储器那样可以由地址线决定读取或写⼊某个指定的地址。

FIFO⼀般⽤于不同时钟域之间的数据传输,⽐如FIFO的⼀端是AD数据采集, 另⼀端是计算机的PCI总线,假设其AD采集的速率为16位 100K SPS,那么每秒的数据量为100K×16bit=1.6Mbps,⽽PCI总线的速度为33MHz,总线宽度32bit,其最⼤传输速率为 1056Mbps,在两个不同的时钟域间就可以采⽤FIFO来作为数据缓冲。

另外对于不同宽度的数据接⼝也可以⽤FIFO,例如单⽚机位8位数据输出,⽽ DSP可能是16位数据输⼊,在单⽚机与DSP连接时就可以使⽤FIFO来达到数据匹配的⽬的。

FIFO的分类根均FIFO⼯作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。

同步FIFO是指读时钟和写时钟为同⼀个时钟。

在时钟沿来临时同时发⽣读写操作。

异步FIFO是指读写时钟不⼀致,读写时钟是互相独⽴的。

FIFO设计的难点 FIFO设计的难点在于怎样判断FIFO的空/满状态。

为了保证数据正确的写⼊或读出,⽽不发⽣益处或读空的状态出现,必须保证FIFO在满的情况下,不 能进⾏写操作。

在空的状态下不能进⾏读操作。

怎样判断FIFO的满/空就成了FIFO设计的核⼼问题。

.........................................................................................................................................同步FIFO的Verilog代码之⼀在modlesim中验证过。

verilog FIFO序列(深度可调)

公司招聘时给大家出的题目,我自己也给做了一下,帮助大家学习。

主程序和tb文件都在。

可用modelsim直接仿真。

主程序:module fifo(datain,clk,reset,dataout,wr,rd,full,empty);input[7:0]datain;input clk,reset,rd,wr;output[7:0]dataout;output full,empty;reg[7:0]dataout;reg rp,wp;reg[3:0]counter;reg[7:0]ram[15:0];wire full,empty;always@(posedge clk)if(!reset)beginrp=0;wp=0;counter=0;dataout=0;endelsecase({rd,wr})2'b00:counter=counter;2'b01:beginif(!full)beginram[wp]=datain;counter=counter+1;wp=(wp==15)?0:wp+1;endendif(!empty)begindataout=ram[rp];counter=counter-1;rp=(rp==15)?0:rp+1;endend2'b11:beginif(counter==0)dataout=datain;elsebeginram[wp]=datain;wp=(wp==15)?0:wr+1;dataout=ram[rp];rp=(rp==15)?0:rp+1;endendendcaseassign full=(counter==5);assign empty=(counter==0); endmodule测试文件(testbench):`timescale1ns/1nsmodule fifo_tb;reg reset,clk,wr,rd;reg[7:0]datain;wire[7:0]dataout;wire full,empty;always#50beginclk=~clk;datain={$random}%256;endinitialbeginreset=0;clk=0;{rd,wr}=2'b00;#100reset=1;{rd,wr}=2'b01;#2000{rd,wr}=2'b10;#2000{rd,wr}=2'b11;#500$stop;endfifom0(.datain(datain),.clk(clk),.reset(reset),.dataout(dataout),.wr(wr),.rd(rd),.full(full),.empty(empty)) ;endmodule。

异步FIFO的verilog代码实现(包含将满和将空逻辑)

异步FIFO的verilog代码实现(包含将满和将空逻辑)异步FIFO的verilog代码实现(包含将满和将空逻辑)代码参考来源:1. Clifford E. Cummings, "Simulation and Synthesis Techniques for Asynchronous FIFO Design".2.⽬录异步FIFO简介使⽤场景:在有⼤量的数据需要进⾏跨时钟域传输,并且对数据传输速度要求⽐较⾼的场合。

⼀个异步 FIFO ⼀般由如下部分组成:1. Memory, 作为数据的存储器;2.写逻辑部分,主要负责产⽣写信号和地址;3.读逻辑部分,主要负责产⽣读信号和地址;4.地址⽐较部分,主要负责产⽣ FIFO 空、满的标志。

跟普通的FIFO相⽐,异步FIFO实际上多了读写地址的跨时钟域同步的逻辑,以及两个时钟域中读写信号的⽐较逻辑。

异步FIFO关键技术1 -- 读写信号跨时钟域同步⾸先,FIFO的关键是需要判断读空和写满,⽽这两个信号的产⽣依赖读地址和写地址。

在异步FIFO中,读和写是分在两个时钟域中的,在写时钟域,需要得到读地址的信息进⽽判断是否写满(写指针是否追上读指针),同理,在读时钟域,也需要写地址的信息。

我们知道跨时钟域的单⽐特数据⼀般可以⽤双寄存器法进⾏同步,但读写地址通常都是多⽐特的信号,此时如何进⾏同步呢?当然,多⽐特的同步肯定可以通过增加握⼿信号来解决,但实际上对于数值上连续的信号,可以采⽤格雷码进⾏多⽐特到单⽐特的传输。

格雷码再次不做介绍,具体原理可以参考:有了格雷码,就可以将读写地址同步到各⾃的时钟域了。

异步FIFO关键技术2 -- 读写地址的⽐较跟普通fifo⼀样,异步fifo也是通过⽐较读写地址是否相同来判断当前fifo是否空满。

区别在于,异步FIFO因为使⽤了格雷码对地址进⾏编码传输。

⽐如读信号通过格雷码编码后同步到写时钟域,此时需要只需要写信号对应的格雷码和读信号格雷码是否相同(有效位相同)。

systemverilog 队列

systemverilog 队列SystemVerilog是一种用于硬件设计和验证的编程语言,它是Verilog HDL 的扩展。

SystemVerilog 提供了一些新的特性,如对象导向编程、泛型和队列等,使得它更适合于设计和验证复杂的硬件系统。

在本文中,我们将重点介绍 SystemVerilog 中的队列。

队列是一种数据结构,它可以在一端添加元素,在另一端删除元素。

队列通常是先进先出 (FIFO) 的,这意味着先添加的元素将首先被删除。

在硬件设计中,队列通常用于存储和传输数据,如缓冲区或FIFO。

SystemVerilog 中的队列是一种动态数组类型,它可以自动调整大小以适应添加或删除元素。

队列也可以是多维的,例如一个二维队列可以表示一个矩阵。

以下是一个简单的 SystemVerilog 队列定义: ```queue # (int) my_queue;```这个定义创建了一个名为 my_queue 的整数队列。

队列的大小可以在运行时动态调整,例如:```my_queue.push_back(10);my_queue.push_back(20);my_queue.push_back(30);```这个代码将三个整数添加到 my_queue 中。

push_back() 函数将元素添加到队列的末尾。

可以使用 pop_front() 函数从队列的前端删除元素,例如:```my_queue.pop_front();```这个代码将从 my_queue 中删除第一个元素。

队列还提供了其他的函数,如 size() 函数返回队列的大小,empty() 函数检查队列是否为空,front() 函数返回队列的第一个元素,back() 函数返回队列的最后一个元素。

队列还支持迭代器,可以使用 for-each 循环遍历队列中的元素。

以下是一个使用 for-each 循环遍历队列的例子:```foreach (my_queue[i]) begin$display('Element %0d: %0d', i, my_queue[i]);end```这个代码将打印队列中每个元素的值和索引。

system verilog 中进程间通讯的常用机制 -回复

system verilog 中进程间通讯的常用机制-回复系统Verilog是一种硬件描述语言,常用于设计和验证数字集成电路。

在复杂的设计中,可能会涉及到多个进程间的通讯。

本文将详细介绍系统Verilog中的常用进程间通讯机制。

一、进程间通讯的概念进程间通讯(IPC)是指两个或多个并行运行的进程之间的数据交换。

在系统Verilog中,可以使用多种机制实现进程间通讯,包括mailbox、fifo、semaphore等。

二、MailboxMailbox是系统Verilog中最基本的进程间通讯机制之一。

它是一个FIFO (First-In-First-Out)队列,可以存储一定数量的数据。

一个进程可以把数据放入mailbox,另一个进程可以从mailbox取出数据。

创建mailbox的基本语法如下:mailbox m = new [size];其中,`m`是mailbox的名字,`size`是mailbox的大小,即它可以存储的最大数据量。

向mailbox发送数据的基本语法如下:m.put(data);从mailbox接收数据的基本语法如下:data = m.get();三、FIFOFIFO也是一种常用的进程间通讯机制。

与mailbox不同的是,FIFO不仅可以存储数据,还可以存储任务或者函数的调用请求。

创建FIFO的基本语法如下:FIFO#(type) f = new [size];其中,`f`是FIFO的名字,`type`是要存储的数据类型,`size`是FIFO的大小。

向FIFO发送数据的基本语法如下:f.put(data);从FIFO接收数据的基本语法如下:data = f.get();四、SemaphoreSemaphore是一种同步机制,用于控制对共享资源的访问。

在系统Verilog中,可以使用semaphore来实现进程间的同步。

创建semaphore的基本语法如下:semaphore s = new [count];其中,`s`是semaphore的名字,`count`是初始的计数值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

// word in FIFO.

reg F_FullN;

reg F_EmptyN;

reg F_LastN;

reg F_SLastN;

wire ReadN = FOutN;

wire WriteN = FInN;

assign F_Data = FIFODataOut;

assign FIFODataIn = Data_In;

FIFO_MEM_BLK memblk(.clk(Clk),

.writeN(WriteN),

.rd_addr(rd_ptr),

.wr_addr(wr_ptr),

.data_in(FIFODataIn),

.data_out(FIFODataOut)

// is incremented else if read only read counter is incremented

// else if both, read and write counters are incremented.

// fcounter indicates the num of items in the FIFO. Write only

FOutN,

F_Data,

F_FullN,

F_LastN,

F_SLastN,

F_FirstN,

F_EmptyN

// increments the fcounter, read only decrements the counter, and

// read && write doesn't change the counter value.

always @(posedge Clk or negedge RstN)

// If the fcounter is equal to zero, indicates the FIFO is empty.

// F_EmptyN signal indicates FIFO Empty Status. By default it is

// asserted, indicating the FIFO is empty. After the First Data is

// put into the FIFO the signal is deasserted.

always @(posedge Clk or negedge RstN)

begin

if(!RstN)

F_EmptyN <= 1'b0;

reg [(`FCWIDTH-1):0] wr_ptr; // Current write pointer.

wire [(`FWIDTH-1):0] FIFODataOut; // Data out from FIFO MemBlk

wire [(`FWIDTH-1):0] FIFODataIn; // Data into FIFO MemBlk

input FInN; // Write into FIFO Signal.

input FClrN; // Clear signal to FIFO.

input FOutN; // Read from FIFO signal.

// in the FIFO. When the FIFO is empty and a write to FIFO occurs,

// this signal gets asserted.

always @(posedge Clk or negedge RstN)

F_FirstN <= 1'b1;

end

else begin

F_FirstN <= 1'b1;

end

end

end

// F_SLastN indicates that there is space for only two data words

output F_LastN; // FIFO Last but one signal.

output F_SLastN; // FIFO SLast but one signal.

output F_FirstN; // Signal indicating only one

begin

if(!RstN)

F_FirstN <= 1'b1;

else begin

if(FClrN==1'b1) begin

if((F_EmptyN==1'b0 && WriteN==1'b0) ||

);

input Clk; // CLK signal.

input RstN; // Low Asserted Reset signal.

input [(`FWIDTH-1):0] Data_In; // Data into FIFO.

if(!FClrN ) begin

fcounter <= 0;

rd_ptr <= 0;

wr_ptr <= 0;

end

else begin

if(!WriteN && ReadN && F_FullN)

fcounter <= fcounter + 1;

else if(WriteN && !ReadN && F_EmptyN)

fcounter <= fcounter - 1;

);

// Control circuitry for FIFO. If reset or clr signal is asserted,

// all the counters are set to 0. If write only the write counter

`define FWIDTH 32 // Width of the FIFO.

`define FDEPTH 4 // Depth of the FIFO.

`define FCWIDTH 2 // Counter Width of the FIFO 2 to power

else begin

if(FClrN==1'b1) begin

if(F_EmptyN==1'b0 && WriteN==1'b0)

F_EmptyN <= 1'b1;

else if(F_FirstN==1'b0 && ReadN==1'b0 && WriteN==1'b1)

output [(`FWIDTH-1):0] F_Data; // FIFO data out.

output F_FullN; // FIFO full indicating signal.

output F_EmptyN; // FIFO empty indicating signal.

reg F_FirstN;

reg [`FCWIDTH:0] fcounter; //counter indicates num of data in FIFO

reg [(`FCWIDTH-1):0] rd_ptr; // Current read pointer.

begin

if(!RstN) begin

fcounter <= 0;

rd_ptr <= 0;

wr_ptr <= 0;

end

else begin

if(!WriteN &&r_ptr + 1;

if(!ReadN && F_EmptyN)

rd_ptr <= rd_ptr + 1;

end

end

end

// All the FIFO status signals depends on the value of fcounter.

// If the fcounter is equal to fdepth, indicates FIFO is full.

(fcounter==2 && ReadN==1'b0 && WriteN==1'b1))

F_FirstN <= 1'b0;

else if (F_FirstN==1'b0 && (WriteN ^ ReadN))

F_EmptyN <= 1'b0;

end

else

F_EmptyN <= 1'b0;

end

end

// F_FirstN signal indicates that there is only one datum sitting

// FCWIDTH = FDEPTH.

module FIFO( Clk,

RstN,

Data_In,

FClrN,

FInN,