实验三 verilog HDL中任务与函数的数字系统设计

EDA实验06—Verilog HDL中使用函数和任务

电子信息工程学系实验报告课程名称:EDA技术与实验在实验项目名称:Verilog HDL中使用函数和任务实验时间:班级:通信091 姓名:Jxairy 学号:实验目的:1.了解函数的定义和在模块设计中的使用。

2.了解函数的可综合性问题。

3.了解许多综合器不能综合复杂的算术运算。

4.掌握任务在Verilog模块设计中的应用。

5.学会在电平敏感列表的always中使用拼接操作、任务和阻塞赋值等语句,并生成复杂组合逻辑的高级方法。

实验环境:Windows 7、MAX+PlusⅡ10、QuartusⅡ等。

实验内容:1.用函数定义8—3编码器的文本设计及仿真。

2.用任务模块进行alutask的文本设计及仿真。

实验过程:一、用函数定义8—3编码器的文本设计及仿真:(试验环境:MAX+PlusⅡ10)(1)新建文本:选择菜单File下的New,出现如图5.1所示的对话框,在框中选中“Text Editor file”,按“OK”按钮,即选中了文本编辑方式。

图6.1 新建文本(2)另存为Verilog编辑文件,命名为“code_83.v”如图5.2所示。

(3)在编辑窗口中输入程序,如图6.3所示。

图6.2 另存为.V编辑文件图6.3 8—3编码器的源程序(4)设置当前文本:在MAX+PLUS II中,在编译一个项目前,必须确定一个设计文件作为当前项目。

按下列步骤确定项目名:在File菜单中选择Project 中的Name选项,将出现Project Name 对话框:在Files 框内,选择当前的设计文件。

选择“OK”。

如图6.4所示。

(5)打开编译器窗口:在MAX—plusⅡ菜单内选择Compiler 项,即出现如图6.5的编译器窗口。

图6.4 设置当前仿真的文本设计图6.5 编译器窗口选择Start即可开始编译,MAX+PLUS II编译器将检查项目是否有错,并对项目进行逻辑综合,然后配置到一个Altera 器件中,同时将产生报告文件、编程文件和用于时间仿真用的输出文件。

Verilog HDL数字设计实训教程第1章 Verilog HDL数字设计实训基础

图1-2 按键电路连接图和管脚对应图

1.1 实训平台

4个LED灯:

图1-3 LED电路连接图和管脚对应图

1.1 实训平台

2个数码管:

图1-4 数码管电路连接图和管脚对应图

1块液晶:

1.1 实训平台

图1-5 液晶电路连接图和管脚对应图

1个UART:

1.1 实训平台

图1-6 UART电路连接图和管脚对应图

if(p==N-1) begin p=0; clk_p=~clk_p; end else p=p+1; end always @(negedge clk) begin

if(q==N-1) q=0; else q=q+1;

if(p==(N-1)/2) clk_q=~clk_q; end assign clk_N=clk_p^clk_q; endmodule

图1-39 设置USB硬件端口

QuartusII设计流程

5.引脚锁定和硬件验证

图1-40 下载界面

QuartusII设计流程

5.引脚锁定和硬件验证

图1-41 选择下载文件

QuartusII设计流程

5.引脚锁定和硬件验证

图1-42 led灯闪烁的效果

1.3 分频器设计

分频器电路是非常有用的一种电路, 分频的方法很多,最常见的是利用加 法计数器对时钟信号进行分频。

begin if(p==N/2-1) begin p=0; clk_N=~clk_N; end else p=p+1;

end endmodule

图1-44 任意偶数分频仿真波形

1.3 分频器设计

【例1-5】 可设置参数的任意整数分频器:占空比可变。 module divf_parameter(rst,clk,en,clkout); input rst,clk,en; output clkout; integer temp; //最大值为2的32次方 parameter N=7,M=3; //N为分频系数,M/N为占空比 always @(posedge clk)

使用Verilog HDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明

使用Verilog HDL进行数字逻辑设计、综合、仿真的步骤及工具软件使用简要说明综合工具使用synplify pro 7.0仿真工具使用modelsim 5.5e (几个菜单排列与5.6有不同,文中有介绍)布局布线工具及时序仿真模型生成使用maxplusII 10.0一.写在开干之前1.涉及到的文件a.源程序(*.v)用户编写的用于描述所需电路的module (可能有多个文件,多个module相互调用)如果用于综合,则源程序内用于描述的V erilog语言必须是可综合风格的。

否则将只能做功能仿真(前仿真),而不能做综合后的仿真和时序仿真(后仿真)。

b.综合后的V erilog HDL 模型(网表) (*.vm)用综合工具synplify对a 进行综合后生成的电路的V erilog HDL 描述。

由synplify自动生成(必须在Implementation Option —Implementation results选项中选中write mapped verilog netlist后才会生成vm文件)。

此文件用于作综合后的仿真c.布局布线后生成的时序仿真模型(网表) (*.vo)文件使用maxplusII对设计进行布局布线之后,生成的带有布局布线及具体器件延迟特性等参数的电路模型的V erilog HDL描述。

要让maxplusII生成vo文件,必须在maxplusII的compile interface中选中verilog netlist writer。

此文件用于作时序仿真(后仿真)d.测试文件(*.v或*.tf)用户编写的V erilog HDL源程序。

用于测试源程序(a,b,c)中所描述电路。

在测试文件中调用被测试的module,生成被测点路所需的输入信号。

所用V erilog HDL语句不需要是可以综合的,只需语法正确。

如果被测试的模型为a,则对应的仿真为前仿真(功能仿真)如果被测试的模型为b, 则对应的仿真为综合后仿真如果被测试的模型为c, 则对应的仿真为后仿真2.强烈建议a.在写用于综合的源程序时,一个源程序文件里只写一个moduleb.源程序文件名与其内所描述的module名相同(如module myadder 文件名myadder.v)c.为了方便管理文件,为每一个设计都单独创建一个目录,目录内创建source, test子目录分别用于存放源程序(用于综合的)和测试文件。

数字系统设计与Verilog HDL

数字系统设计与Verilog HDL(复习)EDA(Electronic Design Automation)就是以计算机为工作平台,以EDA软件工具为开发环境,以PLD器件或者ASIC专用集成电路为目标器件设计实现电路系统的一种技术。

1.电子CAD(Computer Aided Design)2.电子CAE(Computer Aided Engineering)3.EDA(Electronic Design Automation)EDA技术及其发展p2EDA技术的应用范畴1.3 数字系统设计的流程基于FPGA/CPLD的数字系统设计流程1. 原理图输入(Schematic diagrams )2、硬件描述语言 (HDL文本输入)设计输入硬件描述语言与软件编程语言有本质的区别综合(Synthesis)将较高层次的设计描述自动转化为较低层次描述的过程◆行为综合:从算法表示、行为描述转换到寄存器传输级(RTL)◆逻辑综合:RTL级描述转换到逻辑门级(包括触发器)◆版图综合或结构综合:从逻辑门表示转换到版图表示,或转换到PLD器件的配置网表表示综合器是能自动实现上述转换的软件工具,是能将原理图或HDL语言描述的电路功能转化为具体电路网表的工具适配适配器也称为结构综合器,它的功能是将由综合器产生的网表文件配置于指定的目标器件中,并产生最终的可下载文件对CPLD器件而言,产生熔丝图文件,即JEDEC文件;对FPGA器件则产生Bitstream 位流数据文件p8仿真(Simulation)功能仿真(Function Simulation)时序仿真(Timing Simulation)仿真是对所设计电路的功能的验证p9编程(Program)把适配后生成的编程文件装入到PLD器件中的过程,或称为下载。

通常将对基于EEPROM工艺的非易失结构PLD器件的下载称为编程(Program),将基于SRAM 工艺结构的PLD器件的下载称为配置(Configure)。

Verilog数字系统设计-课程设计报告

Verilog HDL数字系统设计课程设计课题:RISC_CPU设计与验证第一章:RISC_CPU概述(51.1课题的由来和设计环境介绍(5 1.2什么是CPU (5第二章:RISC_CPU结构(62.1 RISC_CPU整体结构(62.2 时钟发生器(72.2.1 时钟发生器的介绍(72.2.2 时钟发生器symbol(82.2.3 时钟发生器RTL(82.2.4 时钟发生器源代码(82.2.5 时钟发生器测试代码(92.2.6 时钟发生器仿真波形(10 2.3指令寄存器(102.3.1 指令寄存器介绍(102.3.2 指令寄存器symbol(112.3.3 指令寄存器RTL(112.3.4 指令寄存器源代码(11 2.3.5 指令寄存器测试代码(122.3.6指令寄存器仿真波形(13 2.4 累加器(132.4.1 累加器介绍(132.4.2 累加器symbol(132.4.3 累加器RTL(142.4.4 累加器源代码(142.4.5 累加器仿真代码(142.4.6 累加器仿真波形(152.5 算术运算器(152.5.1 算术运算器介绍(152.5.2 算术运算器symbol(162.5.3 算术运算器RTL(172.5.4 算术运算器源代码(182.5.5 算术元算器测试代码(192.5.6 算术运算器仿真波形(20 2.6数据控制器(202.6.1 数据控制器介绍(202.6.2 数据控制器smybol(20 2.6.3 数据控制器RTL(212.6.4 数据控制器源代码(21 2.6.5 数据控制器测试代码(222.6.6 数据控制器仿真波形(22 2.7 地址多路器(222.7.1地址多路器介绍(222.7.2 地址多路器smybol(232.7.3 地址多路器RTL(232.7.5 地址多路器测试代码(232.7.6 地址多路器仿真波形(24 2.8程序计数器(242.8.1 程序计数器介绍(242.8.2 程序计数器symbol(25 2.8.3 程序计数器RTL(252.8.4 程序计数器源代码(25 2.8.5 程序计数器测试代码(262.8.6 程序计数器仿真波形(26 2.9 状态控制器(272.9.1 状态控制器介器(272.9.2 状态控制器smybol(272.9.3 状态控制器RTL(272.9.4 状态控制器源代码(272.9.5 状态控制器测试代码(282.9.6 状态控制器仿真波形(29 2.10状态机(292.10.1状态机的介绍(292.10.2 状态机symbol(302.10.3 状态机RTL(302.10.4状态机源代码(312.10.5 状态机测试代码(352.10.6 状态机仿真波形(362.11 CPU内核模块的整合(362.11.1 CPU内核原理图(362.11.2 CPU内核smybol (37第三章:CPU外围模块的设计(37 3.1 地址译码器(373.1.1 地址译码器介绍(373.1.2 地址译码器smybol(373.1.3 地址译码器RTL(383.1.4 地址译码器源代码(383.1.5 地址译码器测试代码(383.1.6 地址译码器仿真波形(393.2 RAM (393.2.1 RAM的介绍(393.2.2 RAM smybol(393.2.3 RAM RTL(403.2.4 RAM 源代码(403.2.5 RAM 测试代码(403.2.6 RAM 仿真波形(423.3 ROM (423.3.1 ROM的介绍(423.3.3 ROM的高阻化处理(423.4 I/O模块(433.4.1 I/O模块源代码(433.4.2 I/O模块smybol(443.5 CPU外围模块连接电路原理图(443.6 烧录到FPGA上(45第四章:CPU功能验证(454.1 CPU寻址方式和指令系统(454.2 HLT指令验证(464.3 SKZ指令验证(464.4 ADD指令验证(474.5 AND指令验证(474.6 LDA、STO、JMP指令验证(47第五章:总结(48参考文献: (48第一章:RISC_CPU概述1.1课题的由来和设计环境介绍在本设计课程中,我们通过自己动脑筋,设计出CPU的软核和固核。

VerilogHDL数字系统设计技巧精品PPT课件

output o_clk; input i_clk; input rst_n; parameter N = N_even; // 设置偶数倍分频 parameter M = ?; // M="N/2-1" // bit_of_N: N_even的二进制位宽 reg [(bit_of_N - 1):0] cnt; // 计数器单元 reg o_clk;

cnt <= cnt + 1'b1; end end

恰恰分频:任意整数和小数分频的Verilog实现

// 生成上升沿时钟 // 0~(N/2-1) ↑ -> 1; (N/2)~(N-1) ↑ -> 0 always @ (posedge i_clk, negedge rst_n) begin

if (!rst_n) o_clk <= 0;

偶数分频器的实现非常简单,通过计数器计数 就完全可以实现。 如进行N倍偶数分频,就可以通过由待分频的 时钟触发计数器计数。 当计数器从0计数到N/2-1时,输出时钟进行翻 转,并给计数器一个复位信号,以使下一个时 钟从零开始计数。 以此循环,就可以实现任意的偶数分频。

恰恰分频:任意整数和小数分频的Verilog实现

恰恰分频:任意整数和小数分频的Verilog实现

always@(negedge clk or negedge rst_n) begin if(!rst_n) begin cnt2<=0; end else if(cnt2==2'b10) begin cnt2<=0; end else begin cnt2<=cnt2+1; end end

veriloghdl课程设计

veriloghdl课程设计一、课程目标知识目标:1. 理解Verilog HDL的基本语法和结构,掌握数字电路设计的基本原理;2. 学会使用Verilog HDL进行简单的数字电路设计和仿真;3. 掌握Verilog HDL中的模块化设计方法,能够阅读和分析中等难度的Verilog代码;4. 了解FPGA的基本原理,能够将Verilog HDL代码在FPGA开发板上实现硬件编程。

技能目标:1. 能够运用Verilog HDL编写基本的组合逻辑和时序逻辑电路;2. 独立完成简单的数字信号处理系统的设计、仿真和硬件测试;3. 掌握使用Verilog HDL进行代码调试和优化的基本技巧;4. 培养学生的团队合作能力和问题解决能力,能够在项目中进行有效的沟通与协作。

情感态度价值观目标:1. 培养学生对数字电路设计的兴趣,激发学生的创新意识和探索精神;2. 培养学生严谨、细致的学习态度,树立良好的工程伦理观念;3. 增强学生的国家意识,认识到我国在集成电路领域的发展现状和重要性,激发学生的爱国情怀;4. 引导学生树立正确的价值观,认识到科技进步对国家和社会发展的贡献。

本课程针对高年级学生,以项目为导向,注重理论与实践相结合。

在教学过程中,教师需关注学生的学习特点,充分调动学生的主观能动性,培养学生的实际操作能力和创新能力。

课程目标旨在使学生能够掌握Verilog HDL的基本知识和技能,为今后在集成电路设计和开发领域的发展奠定基础。

通过本课程的学习,学生将能够独立完成数字电路的设计和实现,为我国集成电路产业的发展贡献自己的力量。

二、教学内容1. Verilog HDL基础语法:包括数据类型、运算符、赋值语句、控制结构等,对应教材第一章内容;2. 数字电路设计原理:介绍组合逻辑电路和时序逻辑电路设计方法,对应教材第二章内容;3. Verilog HDL模块化设计:学习模块定义、端口声明、模块调用等,对应教材第三章内容;4. 常用数字电路设计实例:分析并实践触发器、计数器、状态机等设计,对应教材第四章内容;5. 仿真与调试技巧:掌握ModelSim仿真工具的使用,学习代码调试和优化方法,对应教材第五章内容;6. FPGA硬件编程:了解FPGA基本原理,学习将Verilog HDL代码烧写到FPGA开发板,对应教材第六章内容;7. 项目实践:分组进行项目设计,包括数字信号处理系统、通信系统等,综合运用所学知识,对应教材第七章内容。

精品课件-Verilog HDL数字系统设计-Verilog HDL数字系统设计-第6章

第6章 任务、函数及其他

13

6.2.1 函数的定义 函数的目的是返回一个值,以用于表达式的计算。函数的

语法格式如下:

function <返回值位宽或类型说明> 函数名; 输入端口与类型说明; 局部变量说明; 块语句

endfunction 其中,<返回值位宽或类型说明>是一个可选项,如果缺省,则返回值为一位寄存器类型的 数据。

24

【例6.6】 条件编译举例。

module compile(out,a,b); output out; input a,b; `ifdef add assign out=a+b; `else assign out=a-b; `endif

endmodule

//宏名为 add

第6章 任务、函数及其他

第6章 任务、函数及其他

9

【例6.3】 任务参数传递示例。

module mult(clk, a, b, out, en_mult);

input clk, en_mult;

input [3:0] a, b;

output [7:0] out; reg [7:0] out;

task muotme;

//任务定义

第6章 任务、函数及其他

6

【例6.2】 定义一个完成两个操作数按位与操作的任务, 然后在后面的算术逻辑单元的描述中调用该任务完成与操作。

module alutask(code,a,b,c); input[1:0] code; input[3:0] a,b; output[4:0] c; reg[4:0] c; task my_and;

8'b1xxx_xxxx:code = 3'h7;

Verilog HDL数字系统设计 原理 实例及仿真 第3章

类型 wire, tri supply1, supply0 wor, trior wand, triand trireg tri1, tri0

表 3.1

线网型变量的类型和功能

功能 对应于标准的互连线(可缺省) 对应于电源线或接地线 对应于有多个驱动源的线或逻辑连接 对应于有多个驱动源的线与逻辑连接 对应于有电容存在且能暂时存储电平的连接 对应于需要上拉或下拉的连接

wire a; wire [7:0] b; wire [4:1] c, d;

//定义了 1 个 1 位的 wire 型数据 //定义了 1 个 8 位的 wire 型数据 //定义了 2 个 4 位的 wire 型数据

பைடு நூலகம்

2.寄存器型变量 寄存器是数据存储单元的抽象,通过赋值语句可以改变 寄存器内存储的值,其作用与改变触发器存储的值相当。在 设计中必须将寄存器变量放在过程语句(如initial、always)中, 通过过程赋值语句赋值。在未被赋值时,寄存器的缺省值为x。 寄存器型信号或变量共有五种数据类型,见表3.3。

wire start,do;

//声明 2 个 1 位的连线型信号

wand [4:0] addr;

//声明 1 个 5 位的线与型信号

tri [MSB-1:LSB+1] addr1; //声明三态线 addr1,位宽由表达式确定

wire和tri是最常用的线网类型,它们具有相同的语法格式 和功能。wire型变量通常用来表示单个门驱动或连续赋值语 句驱动的网络型数据,tri型变量则用来表示多驱动器驱动的 网络型数据。如果wire型或tri型变量没有定义逻辑强度(logic strength),在多个驱动源的情况下,逻辑值会发生冲突从而产 生不确定值。如果多个驱动源驱动同一个连线(或三态线网), 则这个线网的有效值可由表3.2来决定。

Verilog HDL与FPGA数字系统设计ch05_FSM

5.2.2 推荐的状态图描述方法

利用Verilog HDL语言描述状态图主要包含四部分内容: 1,利用参数定义语句parameter描述状态机中各个状态 的名称,并指定状态编码。例如,对序列检测器的状态分配 可以使用最简单的自然二进制码,其描述如下: parameter S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11; 或者,parameter [1:0] S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11; 2,用时序的always 块描述状态触发器实现的状态存储。 3,使用敏感表和case语句(也可以采用if-else等价语句)描 述的状态转换逻辑。 4,描述状态机的输出逻辑。

一般来说,状态机的基本操作主要有以下两种: (1) 状态机的内部状态转换。 (2) 产生输出信号序。

根据电路的输出信号是否与电路的输入有关,可以将状态 机分为两种类型:一类是米利型(Mealy)状态机,电路的输 出信号不仅与电路当前的状态有关,还与电路的输入有关;另 一类是穆尔型(Moore)状态机,电路输出仅仅取决于各触发 器的状态,而不受电路当时的输入信号影响或没有输入变量。

5.2.2 推荐的状态图描述方法

state <= S0; //在nCR跳变为0时,异步清零 Else case(State)

S0: begin Out =1’b0; State = (Sin==1)? S0 : S1; end S1: begin Out = 1’b0; State = (Sin==1)? S2 : S1; end S2: begin Out = 1’b0; State = (Sin==1)? S0 : S3; end

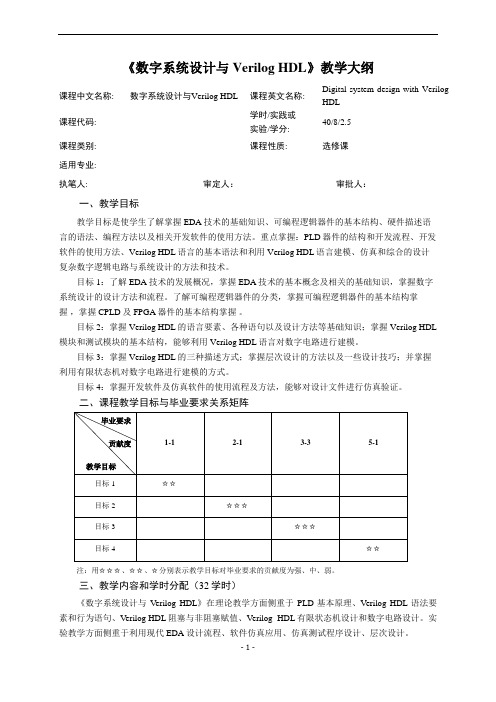

《数字系统设计与Verilog HDL》教学大纲

《数字系统设计与Verilog HDL》教学大纲课程中文名称: 数字系统设计与Verilog HDL 课程英文名称: Digital system design with Verilog HDL课程代码: 学时/实践或实验/学分:40/8/2.5课程类别: 课程性质: 选修课适用专业:执笔人: 审定人:审批人:一、教学目标教学目标是使学生了解掌握EDA技术的基础知识、可编程逻辑器件的基本结构、硬件描述语言的语法、编程方法以及相关开发软件的使用方法。

重点掌握:PLD器件的结构和开发流程、开发软件的使用方法、Verilog HDL语言的基本语法和利用Verilog HDL语言建模、仿真和综合的设计复杂数字逻辑电路与系统设计的方法和技术。

目标1:了解EDA技术的发展概况,掌握EDA技术的基本概念及相关的基础知识,掌握数字系统设计的设计方法和流程。

了解可编程逻辑器件的分类,掌握可编程逻辑器件的基本结构掌握,掌握CPLD及FPGA器件的基本结构掌握。

目标2:掌握Verilog HDL的语言要素、各种语句以及设计方法等基础知识;掌握Verilog HDL 模块和测试模块的基本结构,能够利用Verilog HDL语言对数字电路进行建模。

目标3:掌握Verilog HDL的三种描述方式;掌握层次设计的方法以及一些设计技巧;并掌握利用有限状态机对数字电路进行建模的方式。

目标4:掌握开发软件及仿真软件的使用流程及方法,能够对设计文件进行仿真验证。

二、课程教学目标与毕业要求关系矩阵注:用☆☆☆、☆☆、☆分别表示教学目标对毕业要求的贡献度为强、中、弱。

三、教学内容和学时分配(32学时)《数字系统设计与Verilog HDL》在理论教学方面侧重于PLD基本原理、Verilog HDL语法要素和行为语句、Verilog HDL阻塞与非阻塞赋值、Verilog HDL有限状态机设计和数字电路设计。

实验教学方面侧重于利用现代 EDA设计流程、软件仿真应用、仿真测试程序设计、层次设计。

实验三 verilog HDL中任务与函数的数字系统设计

实验三:verilog HDL中任务与函数的数字系统设计班级:通信二班姓名:孔晓悦学号:10082207作业完成后,以班级为单位,班长或课代表收集齐电子版实验报告,统一提交.文件命名规则如“通1_王五_学号”一、实验目的1、了解verilog HDL任务与函数的定义及格式2、掌握函数与任务的定义与调用3、掌握函数与任务在使用时的区别4、掌握任务与函数的具体应用二、预习要求1.复习veirlogHDL行为语句。

2. 预习任务与函数的相关定义和格式要求。

3.简单电路系统设计的流程和方法。

三、实验基本概念1、任务定义☐任务定义格式:task <任务名>;//注意无端口列表端口及数据类型声明语句;其它语句;endtask☐任务调用的格式为:<任务名>(端口1,端口2,……);☐需要注意的是:任务调用时和定义时的端口变量应是一一对应的。

☐注意事项:●任务的定义与调用须在一个module模块内。

●定义任务时,没有端口名列表,但需要紧接着进行输入输出端口和数据类型的说明。

●当任务被调用时,任务被激活。

任务的调用与模块调用一样通过任务名调用实现,调用时,需列出端口名列表,端口名的排序和类型必须与任务定义中的相一致。

●一个任务可以调用别的任务和函数,可以调用的任务和函数个数不限。

2、函数定义☐函数的目的是返回一个值,以用于表达式计算☐函数的定义格式:function <返回值位宽或类型说明> 函数名;端口声明;局部变量定义;其它语句;endfunction☐<返回值位宽或类型说明>是一个可选项,如果缺省,则返回值为1位寄存器类型的数据。

☐注意事项:●函数的定义与调用须在一个module模块内。

●函数只允许有输入变量且必须至少有一个输入变量,输出变量由函数名本身担任,在定义函数时,需对函数名说明其类型和位宽。

●定义函数时,没有端口名列表,但调用函数时,需列出端口名列表,端口名的排序和类型必须与定义时的相一致。

VerilogHDL数字系统设计教程

1,组合逻辑、时序逻辑的Verilog语言描 述

2,锁存器与 D触发器及其Verilog语言描 述

3,设计实例讲解

2020/6/24

本次课主要内容

1,组合逻辑、时序逻辑的Verilog语言描 述

2,锁存器与 D触发器及其Verilog语言描 述

3,Verilog设计电路实例讲解

2020/6/24

CLK

D触发器符号

D触发器电路图

说明:复位信号rst为高电平时复位,输出Q为0; 在复位信号变为低电平后不工作后, 红色标示的或非门对数据输入端D而言,等效于反相器,如下

页2020/6/24

CMOS工艺下D触发器的电路结构(cont.)

CLK

. .CLK

QM

T3

CLK CLK T4

.

2020/6/24

时m序od逻ule辑DFF电(clk路, rs的t, da,ql)w; ays过程块实现

input clk, rst ,d; output q; reg q; always @( posedge clk)

if (rst) q <= 1'b0;

else q <= d;

endmodule

2020/6/24

锁存器与D触发器

问题:锁存器与D触发器的区别? 答案要点:从触发方式和电路结构两方面说明。

2020/6/24

Verilog语法下的锁存器与D触发器

module LATCHorDFF (q, data, enable); input clk,data, enable; output q; reg q;

always @( enable or data) if (enable) q <= data; // enable为低电平的情况

VerilogHDL基础实验可编程实验报告

可编程逻辑器件设计实验报告实验名称:第二部分:VerilogHDL基础实验实验目的:掌握Quartus II 软件的基本使用方法,完成基本时序电路设计实验时间: 2014 年 06 月 19 日地点: 803实验室学生姓名:学号:实验名称:简单D触发器实验一简单D触发器1、实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

(2)创建文件选择菜单File—>New—>Verilog HDL File,创建一个Verilog HDL文件,在Verilog HDL文件中编写能够完成实验功能的Verilog HDL代码。

(3)编译工程选择菜单Processing —>Start Compilation,或者单击按钮。

(4)观察RTL视图选择菜单Tools—>Netlist Viewers—>RTL Viewer即可生成RTL视图。

(5)仿真1).创建VWF文件选择菜单File—>New—>Vector Waveform File2). 设定“End Time”选择菜单Edit File—> End Time,在弹出的对话框中将Time设置为20us。

3).在VWF文件中输入信号节点选择菜单View—>Utility Windows—>Node Finder,在出现的对话框中将Filter框中设置为Pins:all,再单击List按钮,从端口列表中选择需要观察的并拖到波形编辑窗口中。

4).编辑输入信号波形5).观察仿真结果选择菜单Processing—>Start Simulation,或者单击按钮,观察输出波形。

2. VerilogHDL代码module _DFF (clk,d,q);input clk,d;output q;reg q;always@ (posedge clk)beginq<=d;endendmodule3. RTL 视图4.仿真波形实验二同步置数的D触发器1.实验步骤(1)创建工程启动New Project Wizard,创建一个工程。

Verilog HDL数字设计实训教程第3章 数字系统应用类实训项目[精]

![Verilog HDL数字设计实训教程第3章 数字系统应用类实训项目[精]](https://img.taocdn.com/s3/m/bb5354930029bd64783e2cb7.png)

3.4 多功能数字钟设计

1. 设计要求

实现一个多功能数字钟(含跑表功能),如图3-14所示,具体要求如下: (1)计时功能:包括时、分、秒、百分秒的计时,可以实现一天以内精确至百

分之一秒的计时,并将结果显示在液晶上。 (2)定时功能:可设定闹钟定时的小时和分钟值。 (3)校时功能:根据当前准确时间对小时、分钟能手动调整以校准时间。通过

Verilog HDL数字设计实训教程

西安电子科技大学出版社

第1章 Verilog HDL数字设计实训基础 第2章 接口类实训项目 第3章 数字系统应用类实训项目 第4章 NiosII处理器实训项目

第3章 数字系统应用类实训项目

3.1 序列检测器设计 3.2 多功能计算器设计 3.3 求最大公因数设计 3.4 多功能数字钟设计 3.5 音乐播放器设计 3.6 小结

3.3 求最大公因数设计

1. 设计要求 实现求最大公因数,具体要求如下: 对任意输入的两个正整数,能够得到它们的

最大公因数,2个数由键1和键2产生,键4则 启动求最大公因数并将结果显示液晶上,显示 格式分别为“8G4=4”,要求输入的2个数均为 9以内的整数。

2. 设计说明

图3-8 GCD系统框图

按键来修改小时、分钟值,完成对小时、分钟的校准。 (4)复位和暂停功能:这一功能是针对数字跑表的,数字钟不需要这个功能。

hour counter

minute counter

second counter

millisecond counter

图3-14 多功能数字钟

millisecond pusle

clk

基于Verilog HDL的数字系统设计入门教程(CPLD篇)——第三天

【线路人生】手把手系列入门教程 基于 Verilog HDL 的数字系统设计 入门教程(CPLD 篇) 第三天 Version 1.0 Copyright © 线路人生|Circuitry Life 基于 Verilog HDL 的数字系统设计入门教程(CPLD 篇)——第三天 版本修订记录 Version 1.0 Author zhiyuh Data 2009‐8‐5 Description First draft. ~ 2 ~ 线路人生|Circuitry 基于 Verilog HDL 的数字系统设计入门教程(CPLD 篇)——第三天 目录 1. 2. 3. 简介........................................................................................................................................... 4 实验环境 .................................................................................................................................. 4 . 轻触开关(按钮)原理 ........................................................................................................... 4 3.1 轻触开关(按钮)介绍 ............................................................................................... 4 3.2 接口原理 ....................................................................................................................... 5 3.3 实验扩展板上的独立式轻触开关原理图 ................................................................... 6 实验一(基本输入输出) ....................................................................................................... 7 4.1 实验要求 ....................................................................................................................... 7 4.2 实验目标 ....................................................................................................................... 7 4.3 源代码 .......................................................................................................................... 7 . 4.4 实验步骤 ....................................................................................................................... 8 4.5 利用 RTL 电路图观察器 ............................................................................................. 10 4.6 思考 ............................................................................................................................ 11 . 实验二(基本逻辑门实验) ................................................................................................. 11 5.1 实验要求 ..................................................................................................................... 11 5.2 实验目标 ..................................................................................................................... 11 5.3 原理分析 ..................................................................................................................... 11 5.4 实验步骤 ..................................................................................................................... 12 5.5 思考 ............................................................................................................................ 15 . 作业......................................................................................................................................... 16 后记......................................................................................................................................... 16 其它信息 ................................................................................................................................ 16 .4. 5. 6. 7. 8. ~ 3 ~ 线路人生|Circuitry 基于 Verilog HDL 的数字系统设计入门教程(CPLD 篇)——第三天 1. 简介 希望通过今天的学习和实验,大家能掌握以下要点: 轻触开关(按键)的基本工作原理; 利用 RTL 电路图观察器观察电路结构; 基于原理图方式的 Quartus II 输入设计方法。

Verilog HDL 数字系统设计及实践 第8章 任务和函数

8.2 函数(Function)说明语句 函数( )

章例4.8所示的 二进制译码器。 【例8.2】利用函数定义本书第 章例 所示的 二进制译码器。 】利用函数定义本书第4章例 所示的2-4二进制译码器 // example_8_2: 2-4 Binary Decoder defined as function. module binary_decoder_2_4_func(); // 以各种参数调用函数 以各种参数调用函数dec_2_4,并且用 打印解码结果。 ,并且用$display打印解码结果。 打印解码结果 initial begin $display("dec = %b", dec_2_4(1'b1, 2'b00)); $display("dec = %b", dec_2_4(1'b1, 2'b01)); $display("dec = %b", dec_2_4(1'b1, 2'b10)); $display("dec = %b", dec_2_4(1'b1, 2'b11)); $display("dec = %b", dec_2_4(1'b0, 2'b11)); $finish; end // 定义函数,该函数实现 二进制译码的功能。 定义函数,该函数实现2-4二进制译码的功能 二进制译码的功能。 function [3:0] dec_2_4; input i_en; input [1:0] i_dec; begin

8.1 任务(Task)说明语句 任务( )

任务可以在always或者 或者initial模块中的任何过程语句中调用。任务的调用可以 模块中的任何过程语句中调用。 任务可以在 或者 模块中的任何过程语句中调用 包含一个参数列表,参数列表中的各个参数将按照其在任务中的定义顺序,依 包含一个参数列表, 参数列表中的各个参数将按照其在任务中的定义顺序, 次传递给任务中相对应的端口变量。 次传递给任务中相对应的端口变量 。 其传递规则类似于用顺序端口连接方式来 实例化子模块,任务调用时,仿真的运行控制转移到任务模块中。 实例化子模块 , 任务调用时 , 仿真的运行控制转移到任务模块中 。 当任务结束 仿真控制权才回归到任务调用之后的下一条语句。在一个任务中, 后 , 仿真控制权才回归到任务调用之后的下一条语句 。 在一个任务中 , 可以启 动另外一个任务,而新启动的任务又可以再次启动新的任务。 动另外一个任务 , 而新启动的任务又可以再次启动新的任务 。 当所有的任务在 该仿真时刻运行完毕时,仿真运行控制权才转移回来。 该仿真时刻运行完毕时,仿真运行控制权才转移回来。 定义任务的语法如下所示: 定义任务的语法如下所示: task 任务名 任务名; 端口声明和变量定义; 端口声明和变量定义; 一个或多个过程语句; 一个或多个过程语句 endtask

Verilog HDL 数字系统设计及实践 第3章 Verilog行为描述

Verilog HDL 数字系统设计及实践

第3章 Verilog行为描述

学习指南

•【知识目标】 •(1) 了解initial和always语句的概念; •(2) 了解块语句及过程赋值语句的概念和形式; •(3) 理解条件语句,多路分支语句和循环语句的功能特点; •(4) 理解各种时序控制的机制及形式。 •【技能目标】 •(1) 能够建立各种基本的行为模型。 •【重点难点】 •(1) 非阻塞赋值与阻塞赋值的区别; •(2) 各种时序控制机制的特点及应用。

并行块: 并行块中的语句是并行执行的,一旦仿真进入到并行。若使用延迟语句,则每条语句的延迟值是 都是相对于并行块开始执行的仿真时刻而言的,与前后语句的执行顺序无关。 块语句的其他特点: 块语句可以嵌套,顺序块与并行块可以混合使用 。 块语句可以被命名,称为命名块。在命名块中我们可以声明局部变量,但只 能在块内使用。

思考与练习

6. 上题的代码改写如下 initial begin a = 1’b0; b = 1’b0; c = 1’b1; b <= #10 1’b1; c <= #5 1’b0; d <= #15 {a,b,c}; end 请问每条语句执行的仿真时刻是多少?仿真结束后,各变量值是多少? 7. 请设计一个可选择的计算单元,输入a,b位宽为8,输出结果ret为9位,如下图

3.5 条件语句

条件语句可以根据某个判定条件来确定后面的语句是否执行。条件语句使用的关 键字为“if”和“else” if (条件表达式) 条件为真执行的语句; 或: if (条件表达式) 条件为真执行的语句; else 条件为假执行的语句;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验三:verilog HDL中任务与函数的数字系统设计班级:通信二班姓名:孔晓悦学号:10082207

作业完成后,以班级为单位,班长或课代表收集齐电子版实验报告,统一提交.

文件命名规则如“通1_王五_学号”

一、实验目的

1、了解verilog HDL任务与函数的定义及格式

2、掌握函数与任务的定义与调用

3、掌握函数与任务在使用时的区别

4、掌握任务与函数的具体应用

二、预习要求

1.复习veirlogHDL行为语句。

2. 预习任务与函数的相关定义和格式要求。

3.简单电路系统设计的流程和方法。

三、实验基本概念

1、任务定义

☐任务定义格式:

task <任务名>;//注意无端口列表

端口及数据类型声明语句;

其它语句;

endtask

☐任务调用的格式为:

<任务名>(端口1,端口2,……);

☐需要注意的是:任务调用时和定义时的端口变量应是一一对应的。

☐注意事项:

●任务的定义与调用须在一个module模块内。

●定义任务时,没有端口名列表,但需要紧接着进行输入输出端口

和数据类型的说明。

●当任务被调用时,任务被激活。

任务的调用与模块调用一样通过

任务名调用实现,调用时,需列出端口名列表,端口名的排序和类

型必须与任务定义中的相一致。

●一个任务可以调用别的任务和函数,可以调用的任务和函数个数

不限。

2、函数定义

☐函数的目的是返回一个值,以用于表达式计算

☐函数的定义格式:

function <返回值位宽或类型说明> 函数名;

端口声明;

局部变量定义;

其它语句;

endfunction

☐<返回值位宽或类型说明>是一个可选项,如果缺省,则返回值为1位寄存器类型的数据。

☐注意事项:

●函数的定义与调用须在一个module模块内。

●函数只允许有输入变量且必须至少有一个输入变量,输出变量由

函数名本身担任,在定义函数时,需对函数名说明其类型和位宽。

●定义函数时,没有端口名列表,但调用函数时,需列出端口名列

表,端口名的排序和类型必须与定义时的相一致。

这一点与任务相

同

●函数可以出现在持续赋值assign的右端表达式中。

●函数不能调用任务,而任务可以调用别的任务和函数,且调用任

务和函数个数不受限制。

3、例题1 alutask

4、例题2 code_83

4、例题3 funct

四、实验内容

(一)典型习题的验证与仿真

设计要求:

1、指令译码器电路alutask进行调试和仿真。

2、将函数的两个例题83译码器和斐波拉切数计算的例题进行调试和仿真。

3、通过三个例题,掌握任务和函数的定义格式,使用的方法。

代码:

module alutask(opcode,a,b,c);

input [1:0] opcode;

input [7:0] a,b;

output reg [8:0] c;

always @(a or b or opcode)

begin

case(opcode)

2'b00:my_and(a,b,c);

2'b01:c=a|b;

2'b10:c=a-b;

2'b11:c=a+b;

default :c=9'bx;

endcase

end

task my_and;

input [7:0] my_a,my_b;

output [7:0] my_c;

integer i;

for(i=0;i<=7;i=i+1)

my_c[i]=my_a[i]&my_b[i];

endtask

endmodule

仿真结果:

(二)函数与任务练习1---指令译码电路设计

设计要求:

1、在“三、实验基本概念”中例题1,进行改进。

在目前4个分支的基础上增加两个分支,完成a*b的功能,利用移位相加的形式计算,两个分支分别用任务和函数设计。

2.QuartusII进行功能仿真,验证设计的正确性。

4、过程和结果(后面继续添加)

将在程序编辑、编译过程中的错误进行记录(截图或者文本),并错误指出来

(1)编译过程出现的问题总结

错误提示(系统提示)解决方法

错误1

错误2

……..

(2)代码与仿真结果(结果截图)

代码:

module code_83(din,dout);

input[7:0] din;

output [7:0] dout;

function [2:0] code;

input [7:0] din;

casex (din)

8'b1xxx_xxxx : code = 3'h7;

8'b01xx_xxxx : code = 3'h6;

8'b001x_xxxx : code = 3'h5;

8'b0001_xxxx : code = 3'h4;

8'b0000_1xxx : code = 3'h3;

8'b0000_01xx : code = 3'h2;

8'b0000_001x : code = 3'h1;

8'b0000_000x : code = 3'h0;

default :code = 3'hx;

endcase

endfunction

assign dout = code(din);

endmodule

仿真结果:

(三)任务与函数练习2---带7段管输出1位bcd码加法电路

设计要求:

1、参考例题2,设计一个数字电路完成2个1位bcd码加法,输出为七段管。

2、参考例题2和上次试验的7段管译码电路,分别用任务和函数定义7段管的译码电路实

现电路设计。

3.QuartusII进行功能仿真,验证设计的正确性。

4、过程和结果(后面继续添加)

将在程序编辑、编译过程中的错误进行记录(截图或者文本),并错误指出来

(1)编译过程出现的问题总结

错误提示(系统提示)解决方法

错误1

错误2

……..

(2)代码与仿真结果(结果截图)

代码:

module funct(clk,n,result,reset);

output [31:0] result;

input [3:0] n;

input clk,reset;

reg [31:0] result;

always @(posedge clk)

begin

if(!reset) result <=0;

else begin

result <= 2 * factorial(n);

end

end

function [31:0] factorial;

input [3:0] opa;

reg [3:0] i;

begin

factorial = opa ? 1:0;

for(i=2;i<=9;i=i+1)

factorial = i * factorial;

end

endfunction

endmodule

仿真结果:

不是很全的结果

实验要求

1、按照上面的提示完善报告

2、将程序编译过程中出现的主要错误及解决方案进行总结

3、掌握和练习数字系统的分析步骤,并将一些核心步骤进行记录

4、将编写的程序与仿真结果进行记录。