第8章 设计综合与行为仿真

CPLD1

第 8 章 仿真 158第 8 章 仿真仿真也称模拟Simulation 是对电路设计的一种间接的检测方法 对电路设 计的逻辑行为和运行功能进行模拟测试 可以获得许多对原设计进行排错 改进的信息 对于利用 V HDL 设计的大型系统 进行可靠 快速 全面的仿真测试尤为重要 对于纯硬件的电路系统 如纯模拟或数字电路系统 就无所谓仿真了设计者对于它 们只能作直接的硬件系统测试 如果发现有问题 特别是当问题比较大或根本无法运行时 就只能全部推翻 从头开始设计 对于具有微处理器的系统 如单片机系统 可以在一定 程度上进行仿真测试如果希望得到可靠的仿真结果 通常必须利用单片机仿真器进行硬 件仿真 以便了解软件程序对外围接口的操作情况 这类仿真耗时长 成本高 而且获得 的仿真信息不全面 因为单片机仿真主要是对软件程序的检测和排错 对于硬件系统中的 问题则难以有所作为并且这种方法只适用于小系统的设计调试 利用 V HDL 完成的系统设计的电路规模往往达到数万 数十万 乃至数百万个等效逻 辑门构成的规模 显然 必须利用先进的仿真工具才能快速 有效地完成所必需的测试工 作 如前所述 基于 EDA 工具和 FPGA 的关于 VHDL 设计的仿真形式有多种形式 如 VHDL 行为仿真 或称 V HDL 仿真 是进行系统级仿真的有效武器 它既可以在早期对系统的设 计可行性进行评估和测试 也可以在短时间内以极低的代价对多种方案进行测试比较 系统模拟和方案论证 以获得最佳系统设计方案 而时序仿真则可获得与实际目标器件电气 性能最为接近的设计模拟结果 但由于针对具体器件的逻辑分割和布局布线的适配过程耗时过大 不适合大系统进行 仿真 此外 硬件仿真在 V HDL 设计中也有其重要地位 因为 毕竟最后的设计必须落实 在硬件电路上 硬件仿真的工具除必须依赖 EDA 软件外 还有赖于良好的开发模型系统 和规模比较大的 S RAM 型 F PGA 器件 一项较大规模的 V HDL 系统设计的最后完成必须经历多层次的仿真测试过程 其中将包括针对系统的 V HDL 行为仿真 分模块的时序仿真和硬件仿真 直至最后系统级的硬件 仿真 本章主要简要介绍 V HDL 仿真的基本方式和方法 时序仿真和硬件仿真可参考第 12 13 章和附录§ 8.1 VHDL 仿真VHDL 源程序可以直接用于仿真 许多E DA 工具还能将各种不同表述方法包括图形第 8 章仿真 159的或用 V HDL 本身表述的设计文件在综合后输出以 V HDL 表述的可用于时序仿真的文 件这是 V HDL 的重要特性完成 V HDL 仿真功能的软件工具称为 VHDL 仿真器 VHDL 仿真器有不同的实现方法 大致有以下两种方式 (1) 解释型仿真方式经过编译之后 在基本保持原有描述风格的基础上生成仿真数据 在仿真时 对这些 数据进行分析 解释和执行 这种方式基本保持描述中原有的信息 便于做成交互式的 有DEBUG 功能的模拟系统 这对用户检查 调试和修改其源程序描述提供了最大的便利 ModelSim 及 A ctive-VHDL 均采用这种方式 它们都可以以断点 单步等方式调试 V HDL 程序 (2) 编译型模拟方式将源程序结构描述展开成纯行为模型 并编译成目标语言的程序设计语言如 C 语 言然后通过语言编译器编译成机器码形式的可执行文件 然后运行此执行文件实现模 拟 这种方式以最终验证一个完整电路系统的全部功能为目的 采用详细的 功能齐全的 输入激励波形 用较多的模拟周期进行模拟 VHDL 仿真的一般过程如图 8-1 所示数据和波形图 8-1 VHDL 仿真流程为了实现 V HDL 仿真 首先可用文本编辑器完成 V HDL 源程序的设计 但也可以利用 相应的工具以图形方式完成 近年来出现的图形化 V HDL 设计工具 可以接受逻辑结构图 状态转换图 数据流图 控制流程图及真值表等输入形式 通过配置的翻译器将这些图形 格式转换成可用于仿真的 VHDL 文本 Mentor Graphics 的 Renoir Xilinx 的 Foundation Series 以及其它一些 EDA 公司都含有将状态转换图翻译成 VHDL 文本 的设计工具 可以由图文编辑器产生的或直接由用户编辑输入的 V HDL 文本送入 V HDL 编译器进行 编译VHDL 编译器首先对 VHDL 源文件进行语法及语义检查 然后将其转换为中间数据第 8 章 仿真 160格式 中间数据格式是 V HDL 源程序描述的一种内部表达形式 能够保存完整的语义信息 以及仿真器调试功能所需的各种附加信息 中间数据结果将送给设计数据库保存 设计者 可以在 V HDL 源程序中使用 L IBRARY 语句打开相应的设计库 以便使用 U SE 语句来引用 库中的程序包 在工程上 VHDL 仿真类型可分为行为仿真 功能仿真和时序仿真 所谓功能仿真 是不考虑延时情况下利用门级仿真器获得仿真结果 即在未经布线和适配之前 使用VHDL 源程序综合后的文件进行的仿真 时序仿真则是将 VHDL 设计综合之后 再由FPGA/CPLD适配器完成芯片内自动布线等功能映射于具体芯片后得到的文件进行仿真 行为仿真是对未经综合的文件进行仿真 目前大规模 PLD 器件供应商提供的大多数 适配器都配有一个输出选项功能 可以生成 V HDL 网表文件 用户可用 V HDL 仿真器针对 网表文件进行仿真 其方式类似于行为仿真 但所获得的却是时序仿真的结果 VHDL 网表文件实际上也是 VHDL 程序 不过程序中只使用门级元件进行低级结构描 述 门级电路网络完全根据适配器布线的结果生成 因此 VHDL 网表文件中包含了精确 的仿真延时信息 因而仿真的结果将非常接近实际 一般地 在 VHDL 的设计文件中 利用一些 VHDL 中的行为仿真语句 加以一些 控制参数 如人为设定的延时量 和一些报告语句 如 REPORT 语句和 ASSERT 语 句等 将未经综合的文件通过 VHDL 仿真器的仿真 称为行为仿真 而若将 E DA 工 具通过综合与适配后输出的仿真用 V HDL 文件 在同样的 V HDL 仿真器中仿真 或者将综合与适配后输出的门级仿真文件如 M AX+PLUSII 的 S NF 文件经门级仿真器的仿真 都称为时序仿真 目前 P C 机上流行的 V HDL 仿真器有 Model Technology 公司的ModelSim 和 A ldec 公司的 A ctive-VHDL 等 ModelSim 的早期版本称为 V -System/Windows 这些软件都可以在 W indows 上运行 以下的示例可以对上述文字作一些说明 程序 8-1 是一个可综合的普通 V HDL 文件 描述的是一个与门 当在 EDA 工具 MAX+PLUSII中进行综合和适配后设置目标器件为EPF10K10LC84产生了两个可用于仿真的文件 一个是可直接在 MAX+PLUSII 中的门 级仿真器上仿真的 SNF 文件仿真网表文件另一个是可选的用于第三方的 VHDL 仿真 器中仿真的文件 程序8-2程序中的所有语句和表达格式都是自动产生的由此程序可见 程序中已加入了许多用于仿真的语句和参数 由于这些延时参数不是人为加入的 而是根据器件 E PF10K10LC84 的硬件延时特性设置的 因此 利用程序 8-2 在 V HDL 仿 真器中产生的仿真结果是真实的时序仿真 决非行为仿真 程序8-1 LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL; ENTITY and1 ISPORT(aaa,bbb : IN STD_LOGIC; ccc: OUT STD_LOGIC); END and1;ARCHITECTURE one OF and1 IS BEGINccc <= aaa AND bbb; END;真161第8章仿程序8-2LIBRARY IEEE;USE IEEE.std_logic_1164.all;ENTITY TRIBUF_and1 ISGENERIC (ttri: TIME := 1 ns;ttxz: TIME := 1 ns;ttzx: TIME := 1 ns);PORT (in1 : IN std_logic;oe : IN std_logic;y : OUT std_logic);END TRIBUF_and1;ARCHITECTURE behavior OF TRIBUF_and1 ISBEGINPROCESS (in1, oe)BEGINIF oe'EVENT THENIF oe = '0' THENy <= TRANSPORT 'Z' AFTER ttxz;ELSIF oe = '1' THENy <= TRANSPORT in1 AFTER ttzx; ENDIF;ELSIF oe = '1' THENy <= TRANSPORT in1 AFTER ttri;ELSIF oe = '0' THENy <= TRANSPORT 'Z' AFTER ttxz;END IF;END PROCESS;END behavior;LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE work.tribuf_and1;ENTITY and1 ISPORT (aaa : IN std_logic;bbb : IN std_logic;ccc : OUT std_logic);END and1;ARCHITECTURE EPF10K10LC84_a3 OF and1 ISSIGNAL gnd : std_logic;SIGNAL vcc : std_logic;SIGNALn_8, n_9, n_10, n_11, n_12, a_a4_aOUT, n_14, n_15, n_16, n_17, n_18, n_20,n_22 : std_logic;COMPONENT TRIBUF_and1GENERIC (ttri, ttxz, ttzx: TIME);PORT (in1, oe : IN std_logic; y : OUT std_logic); END COMPONENT;BEGIN真162第8章仿gnd <= '0'; vcc <='1'; PROCESS(aaa,bbb) BEGINASSERT aaa /= 'X' OR Now = 0 ns REPORT"Unknown value on aaa" SEVERITYWarning;ASSERT bbb /= 'X' OR Now = 0 ns REPORT"Unknown value on bbb" SEVERITYWarning;END PROCESS;TRIBUF_2: TRIBUF_and1GENERIC MAP (ttri => 2600 ps, ttxz => 4500 ps, ttzx => 4500 ps)PORT MAP (IN1 => n_8, OE => vcc, Y => ccc);DELAY_3: n_8 <= TRANSPORT n_9;XOR2_4: n_9 <= n_10 XOR n_14;OR1_5: n_10 <= n_11;AND1_6: n_11 <= n_12;DELAY_7: n_12 <= TRANSPORT a_a4_aOUT AFTER 2500 ps;AND1_8: n_14 <=gnd;DELAY_9: a_a4_aOUT <= TRANSPORT n_15 AFTER 500 ps;XOR2_10: n_15 <= n_16 XOR n_22;OR1_11: n_16 <= n_17;AND2_12: n_17 <= n_18 AND n_20;DELAY_13: n_18 <= TRANSPORT bbb AFTER 4800 ps;DELAY_14: n_20 <= TRANSPORT aaa AFTER 4300 ps;AND1_15: n_22 <= gnd;END EPF10K10LC84_a3;对于大型设计采用V HDL 仿真器对源代码进行仿真可以节省大量时间因为大型设计的综合布局布线要花费计算机很长的时间不可能针对某个具体器件内部的结构特点和参数在有限的时间内进行许多次的综合适配和时序仿真而且大型设计一般都是模块化设计在设计完成之前即可进行分模块的VHDL 源代码仿真模拟VHDL 仿真使得在设计的早期阶段即可以检测到设计中的错误从而进行修正§ 8.2 延时模型延时是V HDL 仿真需要的重要特性设置为设计建立精确的延时模型可以使用V HDL 仿真器得到接近实际的精确结果在F PGA/CPLD 设计过程中源设计文件一般不需要建立延时模型因为源设计采用许多V HDL 高级行为描述即使采用延时模型也与经FPGA/CPLD 适配器布线后的结果有很大差异一般是通过设置F PGA/CPLD 适配器使其生成VHDL 网表文件的方法来获得仿真文件如程序8-2VHDL 中有两类延时模型能用于行为仿真建模即固有延时和传输延时真163第8章仿8.2.1 固有延时固有延时也称为惯性延时是任何电子器件都存在的一种延时特性固有延时的主要物理机制是分布电容效应分布电容产生的因素很多分布电容具有吸收脉冲能量的效应当输入器件的信号脉冲宽度小于器件输入端的分布电容对应的时间常数时或者说小于器件的惯性延时宽度时脉冲将无法突破数字器件的阈值电平从而在输出端不会产生任何变化这就类似于用一外力推动一静止物体时如果此外力持续的时间过短将无法克服物体的静止惯性而将其推动由此不难理解在惯性延时模型中器件的输出确实都有一个固有的延时当信号的脉宽或者说信号的持续时间小于器件的固有延时时器件将对输入的信号不作任何反应也就是说有输入而无输出为了使器件对输入信号的变化产生响应就必须使信号维持的时间足够长即信号的脉冲宽度必须大于器件的固有延时在V HDL 仿真和综合器中固有延时是默认的延时是一个无穷小量称为延时或称仿真这个延时小量的设置仅为了仿真它是VHDL 仿真器的最小分辩时间并不能完全代表器件实际的惯性延时情况在V HDL 程序的语句中如果没有指明延时的类型与延时量就意味着默认采用了这个固有延时量延时在大多数情况下这一固有延时量近似地反映了实际器件的行为在所有当前可用的仿真器中固有模式是最通用的一种为了在行为仿真中比较逼真地模仿电路的这种延时特性VHDL 提供了有关的语句如z <= x XOR y AFTER 5ns表示此赋值电路的惯性延时为5ns 即要求信号值x XOR y 变化的稳定时间不能少于5ns 换句话说x XOR y 的值在发生变化5ns 后才被赋给z此前x 或y 的任何变化都是无效的若对于下句z <= x XOR y则表明x XOR y 的值在时间段后才被赋给z对于F PGA/CPLD 来说适配器生成的V HDL 网表中一般只使用固有延时模式8.2.2 传输延时另一种延时模型是传输模型传输延时与固有延时相比其不同之处在于传输延时表达的是输入与输出之间的一种绝对延时传输延时并不考虑信号持续的时间它仅仅表示信号传输推迟或延迟了一个时间段这个时间段即为传输延时VHDL 中传输延时表示连线的延时传输延时对延时器件PCB 板上的连线延时和ASIC 上的通道延时的建模特别有用表达传输延时的语句如以下例句所示z <= TRANSPORT x AFTER 10 ns;其中关键词TRANSPORT 表示语句后的延时量为传输延时量虽然产生传输延时与真164第8章仿固有延时的物理机制不一样但在行为仿真中传输延时与固有延时造成的延时效应是一样的在综合过程中综合器将忽略A FTER 后的所有延时设置§ 8.3 仿真d前面曾提到过功能仿真的概念由于综合器不支持延时语句在综合后的功能仿真中仿真器仅对设计的逻辑行为进行了模拟测定而没有把器件的延时特性考虑进去仿真器给出的结果也仅仅是逻辑功能按理说功能仿真就是假设器件间的延迟时间为零的仿真然而事实并非如此由于无论是行为仿真还是功能仿真都是利用计算机进行软件仿真即使在并行语句的仿真执行上也是有先后的在零延时条件下当作为敏感量的输入信号发生变化时并行语句执行的先后次序无法确定而不同的执行次序会得出不同的仿真结果最后将导致矛盾的和错误的仿真结果这种错误仿真的根本原因在于零延时假设在客观世界中是不可能存在的为了解决这一矛盾VHDL 仿真器将自动为系统中的信号赋值配置一足够小而又能满足逻辑排序的延时量即仿真软件的最小分辩时间这个延时量就称为仿真或称延时由此可见在行为仿真和功能仿真中引入延时是必需的仿真中延时的引入由仿真器自动完成无需设计者介入§ 8.4 仿真激励信号的产生在进行仿真时需要在输入端加激励信号有多种方法可以产生仿真驱动信号如可以用VHDL 设计一个波形发生器模块也可以将波形数据或其它数据放在文件中用TEXTIO 程序包中提供的类型和子程序可以读取文本文件当然也可以将仿真的一些中间结果写到文件中VHDL 仿真器本身也提供了设置输入波形的命令下面通过一个4位二进制加法器的仿真示例介绍两种激励信号的产生方法简单的4位二进制加法器的设计如下LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ADDER4 ISPORT ( a, b : IN INTEGER RANGE 0 TO 15;c : OUT INTEGER RANGE 0 TO 15 );END ADDER4;ARCHITECTURE one OF ADDER4 ISBEGINc <= a + b;END one;真165第8章仿第一种方法用V HDL 写一个波形信号发生器源程序如下ENTITY SIGGEN ISPORT ( sig1 : OUT INTEGER RANGE 0 TO 15;sig2 : OUT INTEGER RANGE 0 TO 15 );END;ARCHITECTURE Sim OF SIGGEN ISBEGINsig1 <= 10, 5 AFTER 200 ns, 8 AFTER 400 ns;sig2 <= 3, 4 AFTER 100 ns, 6 AFTER 300 ns;END;图8-2 是由M odelSim 生成的S IGGEN 波形信号发生器的仿真输出波形然后将此波形发生器与A DDER4 组装设计一个V HDL 仿真测试模块示范程序如下图8-2 SIGGEN 的仿真输出波形ENTITY BENCH ISEND;ARCHITECTURE one OF BENCH ISCOMPONENT ADDER4PORT ( a, b : integer range 0 to 15;c : OUT INTEGER RANGE 0 TO 15 ); ENDCOMPONENT;COMPONENT SIGGENPORT ( sig1 : OUT INTEGER RANGE 0 TO 15;sig2 : OUT INTEGER RANGE 0 TO 15 );END COMPONENT;SIGNAL a, b, c : INTEGER RANGE 0 TO 15; BEGINU1 : ADDER4 PORT MAP (a, b, c);U2 : SIGGEN PORT MAP (sig1=>a, sig2=>b);END;在仿真器的波形图上加入a b c 三个内部信号然后运行仿真过程在M odelSim中得到如图8-3 所示的波形图第二种方法利用仿真器的波形设置命令施加激励信号第 8 章 仿真 166准在 M odelSim 中使用 f orce 命令可以交互地施加激励 force 命令的格式如下 force <信号名> <值> [<时间>][, <值> <时间> ] [-repeat <周期>]图 8-3 BENCH 仿真波形图例如force a 0 强制信号的当前值为 0force b 0 0, 1 10 强制信号 b 在时刻 0 的值为 0 在时刻 10 的值为 1 force clk 0 0, 1 15 –repeat 20 clk 为周期信号 周期为 20 可以直接用实体 ADDER4 的结构体进行仿真 在初始化仿真过程后 在ModelSim 的命令行中输入以下命令 force a 10 0, 5 200, 8 400force b 3 0, 4 100, 6 300然后连续执行 R un 命令或执行 R un 500 命令 也可以得到如图 8-3 所示的波形利用 M odelSim 进行仿真的具体操作方法请参考第 12 章 VHDL 各仿真器的命令及操作方式有所不同 请参考相关资料§ 8.5 VHDL 测试基准VHDL测试基准Test Bench 是指用来测试一个 VHDL 实体的程序 VHDL 测试 基准本身也是 V HDL 程序 它用各种方法产生激励信号 通过元件例化语句以及端口映射 将激励信号传给被测试的 V HDL 实体 然后将输出信号波形写到文件中 或直接用波形浏览器观察输出波形在对一个实体进行仿真的时候 编写一个 V HDL 程序 在程序中将这个实体进行元件 例化 对这个实体的输入信号用 V HDL 程序加上激励波形 在VHDL 仿真器中编译运行这 个新建的 V HDL 程序即可对前面的实体进行仿真测试 这个 V HDL 程序称为测试基TestBench 一般情况下 VHDL 测试基准程序不需要定义输入/输出端口 测试结果全部通过内 部信号或变量来观察和分析真167第8章仿事实上8.4 节中已经使用了测试基准其中的第一种方法就是使用的基准文件大部分V HDL 仿真器一般都可以根据被测试的实体自动生成一个测试基准文件框架然后设计者可以在此基础上加入自己的激励波形产生方法及其它各种测试手段注意测试基准通常不能被V HDL 综合器所综合以下是一个8位计数器的设计实体Library IEEE;use IEEE.std_logic_1164.all;entity counter8 isportCLK CE LOAD DIR RESET: in STD_LOGIC;DIN: in INTEGER range 0 to 255;COUNT: out INTEGER range 0 to 255 );end counter8;architecture counter8_arch of counter8 isbeginprocess (CLK, RESET)variable COUNTER: INTEGER range 0 to 255;beginif RESET='1' then COUNTER := 0;elsif CLK='1' and CLK'event thenif LOAD='1' then COUNTER := DIN;Elseif CE='1' thenif DIR='1' thenif COUNTER =255 then COUNTER := 0;Else COUNTER := COUNTER + 1;end if;elseif COUNTER =0 then COUNTER := 255;Else COUNTER := COUNTER - 1;end if;end if;end if;end if;end if;COUNT <= COUNTER;end process;end counter8_arch;这个计数器的测试基准文件示例如下Entity testbench is end testbench;Architecture testbench_arch of testbench isFile RESULTS: TEXT open WRITE_MODE is "results.txt";Component counter8port ( CLK: in STD_LOGIC;RESET: in STD_LOGIC;CE, LOAD, DIR: in STD_LOGIC;DIN: in INTEGER range 0 to 255; COUNT:out INTEGER range 0 to 255 );真168第8章仿end component;shared variable end_sim : BOOLEAN := false;signal CLK, RESET, CE, LOAD, DIR: STD_LOGIC;signal DIN: INTEGER range 0 to 255;signal COUNT: INTEGER range 0 to 255;procedure WRITE_RESULTS (CLK CE LOAD LOAD RESET : STD_LOGIC; DINCOUNT : INTEGER ) isVariable V_OUT : LINE;Beginwrite(V_OUT, now, right, 16, ps); -- 输入时间write(V_OUT, CLK, right, 2);write(V_OUT, RESET, right, 2);write(V_OUT, CE, right, 2);write(V_OUT, LOAD, right, 2);write(V_OUT, DIR, right, 2);write(V_OUT, DIN, right, 257);--write outputswrite(V_OUT, COUNT, right, 257);writeline(RESULTS,V_OUT);end WRITE_RESULTS;beginUUT: COUNTER8port map (CLK => CLK,RESET => RESET,CE => CE, LOAD => LOAD,DIR => DIR, DIN => DIN,COUNT => COUNT );CLK_IN: processBeginif end_sim = false then CLK <= '0';Wait for 15 ns;CLk <='1';Wait for 15 ns;ElseWait;end if;end process;STIMULUS: processBeginRESET <= '1';CE <= '1'; -- 计数使能DIR <= '1'; -- 加法计数DIN <= 250; -- 输入数据LOAD <= '0'; -- 禁止加载输入的数据wait for 15 ns;RESET <= '0';wait for 1 us;CE <= '0'; -- 禁止计数脉冲信号进入wait for 200 ns;CE <= '1';第 8 章 仿真 169wait for 200 ns; DIR <= '0'; wait for 500 ns; LOAD <= '1';wait for 60 ns; LOAD <= '0'; wait for 500 ns; DIN <= 60; DIR <= '1'; LOAD <= '1'; wait for 60 ns; LOAD <= '0'; wait for 1 us; CE <= '0'; wait for 500 ns; CE <= '1'; wait for 500 ns; end_sim :=true; wait;end process; WRITE_TO_FILE: WRITE_RESULTS(CLK,RESET,CE,LOAD,DIR,DIN,COUNT); End testbench_arch;图 8-4 8 位计数器测试基准仿真部分波形图这个例子综合性地使用了一些测试方法 请参照以上几节 仔细阅读本例 图 8-4 为该测试基准在仿真器 A ctive-VHDL 中仿真运行时产生的波形图的一部分§ 8.6 VHDL 系统级仿真VHDL 设计通常要通过各种软件仿真器进行功能和时序模拟 在设计初期一般也采用 行为级模拟 目前 由于大多数 VHDL 仿真器支持标准的接口如 PLI 接口以方便制 作通用的仿真模块及支持系统级仿真 所谓仿真模块 是指许多公司为某种器件制作的第8章仿真170VHDL仿真模型这些模型一般是经过预编译的也有提供源代码的然后在仿真的时候将各种器件的仿真模型用V HDL 程序组装起来成为一个完整的电路系统设计者的设计文件成为这个电路系统的一部分这样在V HDL 仿真器中可以得到较为真实的系统级的仿真结果支持系统仿真已经成为目前V HDL 应用技术发展的一个重要趋势当然这里所谈的还只是在单一目标器件中的一个完整的设计对于一个可应用于实际环境的完整的电子系统来说用于实现VHDL 设计的目标器件常常只是整个系统的一部分对芯片进行单独仿真仅得到针对该芯片的仿真结果但对于整个较复杂的系统来说仅对某一目标芯片的仿真往往有许多实际的情况不能考虑进去如果对整个电路系统都能进行仿真可以使芯片设计风险减少找出一些整个电路系统一起工作才会出现的问题由于VHDL 是一种描述能力强描述范围广的语言完全可以将整个数字系统用VHDL 来描述然后进行整体仿真即使没有使用V HDL 设计的数字集成电路同样可以设计出VHDL 仿真模型现在有许多公司可提供许多流行器件的VHDL 模型如8051 单片机模型PIC16C5X 模型80386 模型等利用这些模型可以将整个电路系统组装起来许多公司提供的某些器件的V HDL 模型甚至可以进行综合这些模型有双重用途既可用来仿真也可作为实际电路的一部分即IP 核例如现有的PCI 总线模型大多是既可仿真又可综合的图8-5 即为由89C51 单片机的VHDL 模型与V HDL 专用系统模型联合进行更高层次系统仿真的示意图虽然用于描述模拟电路的V HDL 语言尚未进入实用阶段但有些软件仍可以完成具有部分模拟电路的支持V HDL 的电路系统级仿真器PSPICE 是一个典型的系统级电路仿真软件其新版本扩展了VHDL 仿真功能PSPICE 本来就可以进行模拟电路数字电路混合仿真因此P SPICE 扩展了V HDL 仿真功能之后理所当然也能进行VHDL 描述的数字电路和模拟电路的混合仿真即能够仿真几乎所有的电路系统所谓的V HDL 器件模型实际上是用V HDL语言对某种器件设计的实体不过这些模型提供给用户的时候一般是经过预编译的用户需支付一定的费用才能得到源代码通过Internet 也可寻到FSF 免费的VHDL 模型及其源码习题图8-5 VHDL 系统仿真模型示意图杭州康芯电子有限公司171KONXINKONXIN第 9 章综合8-1 叙述惯性延迟与传输延迟的异同点 以及惯性延迟的物理机制 8-2 功能仿真中 引进仿真 的意义是什么 试举例说明 8-3 综合前的 V HDL 行为仿真 综合后的 VHDL 行为仿真 功能仿真 时序仿真和 硬件仿真的特点和适用范围是什么 8-4 为什么要进行系统仿真 怎样实现 V HDL 系统仿真第 9 章 综合在利用 V HDL 设计过程中 综合Synthesis是将软件描述VHDL 就其描述方式 来说 仍属软件描述与硬件结构相联系的关键步骤 是文字描述与硬件实现的一座桥梁 是突破软硬件屏障的有利武器 综合就是将电路的高级语言如行为描述 转换成低级的 可与 F PGA/CPLD 或构成 A SIC 的门阵列基本结构相映射的网表文件或程序 EDA的实现 在很大程度上依赖于性能良好的综合器 因此 VHDL 程序设计必须完全适应 VHDL综合 器的要求 使软件设计牢固植根于可行的硬件实现中 当然 另一方面 也应注意到 并非所有可综合的 V HDL 程序都能在硬件中实现 这涉及到两方面的问题 首先要看此程序 将对哪一系列的目标器件进行综合 例如 含有内部三态门描述的 V HDL 程序 原则上是 可综合的 但对于特定的目标器件系列却不一定支持 即无法在硬件中实现 其次是资源问题 这是实用 V HDL 面临的最尖锐的问题 例如在 V HDL 程序中 直接使用乘法运算符尽管综合器和绝大多数目标器件都是支持的 但即使是一个 16 位乘 16 位的组合逻辑乘 法器在普通规模的 PLD 器件 1 万门左右中也是难以实现的 因此 实用的 VHDL 程 序设计中必须注意硬件资源的占用问题 本章首先介绍一般的综合原理 以及可综合的 V HDL 程序设计所涉及的问题 然后介 绍一些通过 V HDL 合理的程序设计来达到正确的综合结果的技术§ 9.1 VHDL 综合由设计要求到设计实现的整个过程 如果是靠人工完成 通常简单地称之为设计 如果依靠 EDA 工具软件自动生成 则通常称之为综合 综合 就是针对给定电路应实现的 功能和实现此电路的约束条件 如速度 功耗成本及电路类型等 通过计算机的优化处 理 获得一个满足上述要求的电路设计方案 这就是说 被综合的文件是 V HDL 程序 综 合的依据是逻辑设计的描述和上述各种约束条件 综合的结果则是一个硬件电路的实现方 案 该方案必须同时满足预期的功能和约束条件的要求 对于综合来说 满足要求的方案 可能有多个综合器将产生一个最优的或接近最优的结果 因此 综合的过程同时也是设 计目标的优化过程 最后获得的结果与综合器的工作性能有关现代的逻辑综合技术主要是基于寄存器传输级的优化技术VHDL 的行为描述被综合 为寄存器/触发器及他们之间的组合逻辑电路的合理连接 优化技术即包括参与逻辑描述 的寄存器/触发器设置的优化和相应的组合逻辑的优化 优化的目标主要有两个 即速度优化和资源优化 前者以提高目标器件的工作速度为优化综合目标 而后者以节省目标器。

第八章Synplify综合讲课文档

–逻辑描述:对设计进行RTL级描述,导出逻辑表达式,并用功

能仿真工具进行仿真

–门级描述:设计的门级实现,相当于系统的逻辑原理图

–物理描述:或称版图描述,ASIC设计中表现为GDSII 文件

•综合指不同设计描述之间的转换

第三页,共53页。

IC设计中的综合

第四页,共53页。

Pipelining

第三十七页,共53页。

Retiming和Pipelining

第三十八页,共53页。

(3)综合约束文件选项

第三十九页,共53页。

(4)综合结果存储

必须选中此项

第四十页,共53页。

(5)时序报告选项

第四十一页,共53页。

(6)语言参数选项

Synplify把最后编译的module作为顶层设计故把你所

Type 说明端口类型Input 或 Output

Value Improve Route等与前面的相同或类似

4) Registers

这个约束的目的是按照给定的时间缩短进入一个寄存器或由其

输出的路径延迟

Type 说明是输入路径还是输出路径

Object 说明指定寄存器的名字

其他如Improve Route Units等与前相同或类似

1 创建工程---使用工具栏快捷按钮

1)方法一、点击File->New

第十八页,共53页。

方法二

第十九页,共53页。

方法三

第二十页,共53页。

2)添加文件

第二十一页,共53页。

2 源代码错误检查

•包括两个层次

–语法错误检查

–综合错误检查

•推荐在代码调试

阶段使用代码错

第8章VHDL顺序和并行语句归纳

VHDL常用顺序语句、并行语句归纳

常用的并行语句有: (1) 并行信号赋值语句,用 “<=” 运算符 (2) 条件赋值语句,WHEN-ELSE (3) 选择信号赋值语句,WITH-SELECT (4) 进程语句,PROCESS 常用的顺序语句有: (1) 信号赋值语句和变量赋值语句 (2) IF- ELSE语句 (3) CASE-WHEN语句 (4) FOR-LOOP

VHDL中描述时序逻辑时必须使用进程语句。

PROCESS语句结构的一般表达格式如下

[进程标号: ] PROCESS [ ( 敏感信号参数表 [进程说明部分]

BEGIN 顺序描述语句

END PROCESS [进程标号];

) ] [IS]

8.3 进程语句归纳

8.3.2 进程结构组成

进程说明部分 数据类型、常数、变量、属性、子程序

1 WHEN s0=’1’ AND s1=’0’ ELSE 2 WHEN s0=’0’ AND s1=’1’ ELSE 3; x <= a WHEN select=0 ELSE b WHEN select=1 ELSE c WHEN select=2 ELSE d; ...

8.5 IF语句概述

(1) IF

条件句 Then 顺序语句

END IF ;

(3) IF 条件句 Then IF 条件句 Then ... END IF

END IF

(2) IF 条件句 Then 顺序语句

ELSE 顺序语句

END IF ; (4) IF 条件句 Then

顺序语句 ELSIF 条件句 Then 顺序语句 ... ELSE

图8-9 固有延时输入输出波形

A

第8章_仿真模型的检验和验证

观测到的平均延迟μ0=4.3分钟

进行原假设统计检验:

H0 : Y 4.3分钟 H1 : Y 4.3分钟

统计术语

建模术语 相关风险

拒绝

类型Ⅰ:当H0为真时拒绝H0 有效模型

α

不拒绝

类型Ⅱ:当H1为真时不拒绝H0 无效模型

β

选择置信水平α=0.05和样本量n=6

计算

t0

Y S

0

/n

2.51 4.3 0.82 / 6

灵敏度分析也可以用来检查模型的表 面效度。

在进行灵敏度分析时,要注意选择最 关键的输入变量进行检验。

§8.3.2模型假设的验证 模型的假设一般分为两类:结构假设

和数据假设。 结构假设包括系统如何运行的问题,

通常涉及实际系统的简化和抽象。 数据假设应该以可靠数据的采集和对

数据正确的统计分析为基础。

§8.3.3输入—输出变换的验证 模型在验证阶段可视为一个输入—输

另一个对模型检验有帮助的重要方 法是文档说明。

更为复杂的有助于模型检验的方法 是跟踪。

§8.3 模型的校验和验证

校验和验证尽管在概念上有区别, 但建模者通常同时进行两方面的工作。

验证是模型及其特性与现实系统及 其特性进行比较的全过程。

校验是一个迭代过程,即把模型和 现实系统进行比较、调整,再比较、再 调整……

1.66

选择置信水平α=0.05和样本量n=6 计算

t0

Y S

0

/n

4.78 4.3 1.66 / 6

0.710

查表得tα/2,n-1=2.571,因此不能拒绝H0。 不拒绝H0必须被认为是弱结论。

§8.3.4利用历史输入数据 使用历史数据进行模型验证时,这些

第8章 自动化制造系统的总体设计 ppt课件

PPT课件

25

(2)控制方便

柔性制造系统所采用机床的控制系统不 仅要能够实现自动加工循环,还要能够适应 加工对象的改变,易于重新调整,也就是说 要具有“柔性”。

PPT课件

5

8.1 总体设计的步骤及内容

(2)选择加工零件类型和范围,并进行工 艺分析,制定工艺方案,确定设备选型。

(3)按功能划分设计模块,初步制定技术 指标和各自的接口,同时进行概要设计和初步 设计。

(4)总体方案初步设计,这一阶段包括总 体布局和各分系统的概要设计。

PPT课件

6

8.1 总体设计的步骤及内容

PPT课件

11

成组技术

成组技术(GT-Group Technology)揭示和 利用事物间的相似性,按照一定的准则分类成 组,同组事物能够采用同一方法进行处理,以 便提高效益的技术,称为成组技术。

日本、美国、前苏联和德国等许多国家把 成组技术与计算机技术、自动化技术结合起来 发展成柔性制造系统,使多品种、中小批量生

另外,柔性制造系统中的所有装备受到本身数 控系统和柔性制造系统中央计算机控制系统的调度 和指挥,要能实现动态调度、资源共享、提高效率 ,就必须在各机床之间建立必要的接口和标准,以 便准确及时地实现数据通信与交换,使各个生产装 备、储运系统、控制系统等协调地工作。

PPT课件

27

2)选择机床的原则

对于箱体类工件,通常选择立式和卧式加 工中心,以及有一定柔性的专用机床,如可换 主轴箱的组合机床,带有转位主轴箱的专用机 床等。

信号与系统-第8章

1/T2称为交接频率(断点)。

G2 ( )

40

20 1 -20 -40 10 102 103

1.系统函数的极点与时域特性的关系 (1) 若一阶极点位于s平面的坐标原点

(2) 若一阶极点位于s平面的实轴上 , 且极点为负实数,p=-a<0

(3) 若一阶极点位于s平面的实轴, 且极点为正实数,p1=a>0

(4) 若有一对共轭极点位于虚轴, p1=jω0及p2=-jω0

(5) 若有一对共轭极点位于s左半平 面,即p1=-a+jω0,p2=-a-jω0,-a<0

应用拉普拉斯变换求解微分方程

• 当电路或系统的输入输出微分方程 已知时,可直接对微分方程应用单边拉 普拉斯变换,利用时域微分性质求出s域 输出 Y(s) ,对其取逆变换得到时域解 y(t) 。

从该例可看出,用拉普拉斯变换法求 解微分方程不需要专门求解t=0+时刻的输 出及其导数,并且可直接得到全响应。 通过上例可以看到,利用拉普拉斯变换 可以避开烦琐的求解微分方程的过程。 特别是对于高阶微分方程,拉氏变换法 可以使计算量大大减小。

1 2 2 H ( ) 2 1 T2 j 2T2 T2

1 2 2 H ( ) 2 1 T2 j 2T2 T2

二次因式的幅频特性的对数增益为

1 2 2 2 2 G 20lg 2 20lg 1 T2 2T2 T2

1 1 G 20lg j 20lg 1 2T12 T1 T1

1 2 2 20lg 10lg(1 T1 ) T1

1 G( ) 20 lg 10 lg(1 2T12 ) T1

精通matlab6.5版 8. SIMULINK交互式仿真集成环境

第八第八章章 SIMULINK SIMULINK 交互式仿真集成环境交互式仿真集成环境8.1 引导SIMULINK 是一个进行动态系统建模、仿真和综合分析的集成软件包。

它可以处理的系统包括:线性、非线性系统;离散、连续及混合系统;单任务、多任务离散事件系统。

在SIMULINK 提供的图形用户界面GUI 上,只要进行鼠标的简单拖拉操作就可构造出复杂的仿真模型。

它外表以方块图形式呈现,且采用分层结构。

从建模角度讲,这既适于自上而下(Top-down )的设计流程(概念、功能、系统、子系统、直至器件),又适于自下而上(Bottum-up ) 逆程设计。

从分析研究角度讲,这种SIMULINK 模型不仅能让用户知道具体环节的动态细节,而且能让用户清晰地了解各器件、各子系统、各系统间的信息交换,掌握各部分之间的交互影响。

在SIMULINK 环境中,用户将摆脱理论演绎时需做理想化假设的无奈,观察到现实世界中摩擦、风阻、齿隙、饱和、死区等非线性因素和各种随机因素对系统行为的影响。

在SIMULINK 环境中,用户可以在仿真进程中改变感兴趣的参数,实时地观察系统行为的变化。

由于SIMULINK 环境使用户摆脱了深奥数学推演的压力和烦琐编程的困扰,因此用户在此环境中会产生浓厚的探索兴趣,引发活跃的思维,感悟出新的真谛。

在MATLAB6.x 版中,可直接在SIMULINK 环境中运作的工具包很多,已覆盖通信、控制、信号处理、DSP 、电力系统等诸多领域,所涉内容专业性极强。

本书无意论述涉及工具包的专业内容,而只是集中阐述:SIMULINK 的基本使用技法和相关的数值考虑。

节8.1虽是专为SIMULINK 初学者写的,但即便是熟悉SIMULINK 以前版本的读者也值得快速浏览这部分内容,因为新版的界面、菜单、工具条、模块库都有较大的变化。

第8.2节比较详细地阐述建模的基本操作:通用模块的具体化设置、信号线勾画、标识、模型窗参数设置。

8章9.4-物流系统仿真软件介绍

4.Extend

特点: 交互性 可扩展性 可重复使用性 规模性 连续性 第三方开发支持

4.Extend

5.arena

Arena不象Flexsim、RaLc等软件建模非常直观和方便,但 Arena一直在仿真学术界有着很高的声誉。2006年的美国 冬季仿真会议上,48%的论文引用到了该软件,Arena是 一个适于学习和研究的仿真软件。

AutoMod 在生产系统中的应用 AutoMod 的分析与优化

1.automod

1.1 AutoMod仿真软件的结构和功能 4)AutoView模块

-显示3D运行画面或影像

AutoView可以允许用户通AutoMod 模型定义场景和摄像机的移动,产 生高质量的AVI格式的动画。用户可 以缩放或者平移视图,或View可以提供动态 的场景描述和灵活的显示方式。

Arena也使用很多基本的构件来建立仿真模型,Arena把这 些基本构件叫做模块,用户可以利用这些模块定义仿真流 程和数据。

5.arena

5.arena

Arena中的模块分为两种, 流程图模块和数据模块, 流程图模块在模型中用于 描述动态过程,可以看成 实体流经的结点或模型起 止的过程。

Flexsim是集成C++的3D仿真软件,是工程师、管理者和决策人对提 出的“关于操作、流程、动态系统的方案”进行试验、评估、视觉化的 工具。它具有完全的C++面向对象性,超强的3D虚拟现实(3D动画), 直观的、易懂的用户接口,卓越的柔韧性。Flexsim是世界唯一的在图形 的模型环境中应用C++ IDE(集成设备)和编译程序的仿真软件。定义 模型逻辑时,可直接使用C++,而且可立刻编译到 Flexsim 中。因为 Flexsim 具有高度的开放性和柔韧性,所以能为几乎所有产业定制特定的 模型。

计算机测控技术与系统第8章 计算机测控系统的设计与实现

8.2 计算机测控系统设计方法

1. 测控系统总体方案设计

(1)确定系统的结构和类型

测控系统类型多、选型范围广,可根据主要功能要求、技术指标进行 系统结构和类型的选择。选型要保证性能指标与技术措施,达到或超过 技术指标要求,在满足需求的前提下,选择性价比高的系统。

(2)确定系统的构成方式

① 专用测控系统

2020/2/21

2

(2)可靠性要高

系统的可靠性是指系统在规定的条件下和规定的时间内完成规定功能 的能力。

可靠性的指标一般采用平均无故障工作时间(MTBF)和故障修复时 间(MTTR)表示。MTBF反映了系统可靠工作的能力,MTTR则反映了 系统出现故障后恢复工作的能力。通常要求MTBF有较高的数值,如达到 几万小时,同时尽量缩短MTTR,以达到很高的运行效率。

这种方式可提高研制和开发速度,提高系统的技术水平和性能,增 加可靠性,容易实现各种复杂的控制功能。

对于大中型规模的测控系统设计,要求设计者具有丰富的专用理论 和实际工程设计能力与经验,系统设计工作量大,过程复杂,通用测控 系统方式是理想的选择。

2020/2/21

13

(3)测控系统主机的选择

主机是整个测控系统的核心,它的选择将对整个系统产生决定性的影 响。目前,可担当测控系统主机的机型很多,如IPC、PLC、PAC、各类 嵌入式微控制器等。在具体选型时,可以选择IPC、PLC、智能仪表等现 有测控硬件设备,设计者只需要根据测控任务选择相应的硬件配置,再 配以软件设计,即可完成测控任务。

可以根据以下几点选用传感器。

•根据测量对象与测量环境确定传感器的类型

•灵敏度的选择

•频率响应特性

•线性范围

•稳定性

•精度

EDA教程第一章

课程所要解决的问题?

当你们经历了以上的痛苦后,不知道你们想过下 面的问题没有? 能不能让计算机帮助化简卡诺图?而且是多个 变量? 能不能用一种芯片实现多个分离小规模数字IC 能不能用一种芯片实现多个分离小规模数字IC 的功能,并且在芯片内部将这些功能连接? 设计数字系统能不能象C 设计数字系统能不能象C语言那样,只关心“如 何描述”一个数字系统,而不是“如何具体实 现”数字系统。

数字系统EDA技术发展概述 数字系统EDA技术发展概述

EDA技术所涉及的领域相当广泛,业界一般将 EDA技术所涉及的领域相当广泛,业界一般将 EDA技术分成: EDA技术分成: 狭义EDA技术 狭义EDA技术 广义EDA技术 广义EDA技术

数字系统EDA技术发展概述 数字系统EDA技术发展概述

狭义EDA技术 狭义EDA技术,就是指以大规模可编程逻辑器件为 技术,就是指以大规模可编程逻辑器件为 设计载体,以 设计载体,以硬件描述语言为系统逻辑描述的主要表达方 式,以 式,以计算机、大规模可编程逻辑器件的开发软件及实验 开发系统为设计工具,通过有关的开发软件,自动完成用 开发系统为设计工具,通过有关的开发软件,自动完成用 软件方式设计的电子系统到硬件系统的: 软件方式设计的电子系统到硬件系统的: 逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、 逻辑编译、逻辑化简、逻辑分割、逻辑综合及优化、 逻辑布局布线、逻辑仿真, 逻辑布局布线、逻辑仿真,直至对于特定目标芯片的适配 编译、逻辑映射、 编译、逻辑映射、编程下载等工作 最终形成集成电子系统或专用集成芯片的一门新技 术,或称为IES/ASIC自动设计技术。 术,或称为IES/ASIC自动设计技术。

数字系统设计技术发展历史

年代 事件

公元前3000年 公元前 年 1614-1617

现代设计理论与方法 第8章绿色设计

• 在国与国之间进行贸易时,有些工业发达国家 会利用其先进技术和环境优势、实行他们的所 谓“环境标志”或“绿色标志”,制造一种最 大的非关税贸易壁垒,即“绿色贸易壁垒”, 使发展中国家面临不利的贸易态势。 • 没有绿色标志的产品,一些发达国家就会拒绝 进口,在价格和关税方面也不给予优惠,并采 取歧视性待遇从而使发展中国家蒙受巨大的经 济损失。 • 为了克服这种绿色贸易壁垒,我们所能做的就 是大力提倡绿色设计,从根本上实现产品的绿 色性。

(3)面向拆卸的设计

表8-2可拆卸性设计准则

目标 设计准则

减少所用材料的种类、采用互相兼容的材料、尽 减少拆卸的工作 量将各部件结合成模块、将有害材料组装成特定 量 模块、有价值及可重复使用的零件应容易拆卸 产品可预见性 易于拆卸 易于分离 减少多样性 避免易老化及腐蚀材料的连接、避免零部件被污 染和腐蚀 减少紧固件数量、尽量采用相同的紧固方法、易 于接近拆卸点、避免在塑料部件中嵌入金属件 尽量避免二次处理(油漆、涂层、电镀等)、对 不同材料进行标识或用颜色加以识别 利用标准零部件、最大程度的减少紧固件类型

第8章 绿色设计

张东编写

§8.1 概述

• 绿色设计 (Green Design)是20世纪80末出现 的一股国际设计潮流,绿色设计反映了人们对 于现代科技文化所引起的环境及生态破坏的反 思,同时也体现了设计师道德和社会责任心的 回归。 • 绿色设计的兴起和广泛应用正逐步改变着一贯 以来以大量消耗资源为主的经济增长方式,改 变着人们的生活方式和消费观念,它为人们提 供了一种解决人-机-环境关系协调的系统设计 方法,是可持续发展的必然要求。

§8.3 绿色设计的原则与方法 §8.3.1 绿色设计与传统产品设计

• 绿色设计是这样一种设计,即在产品整个生命周 期内,着重考虑产品环境属性(可拆卸性、可回 收性、可维护性、可重复利用性等),并将其作 为设计目标,在满足环境目标要求的同时,保证 产品应有的基本功能、使用寿命、质量等。 • 绿色设计要求在设计产品时必须按环境保护的指 标选用合理的原材料、结构和工艺,在制造和使 用过程中降低能耗、不产生毒副作用,其产品易 于拆卸和回收,回收的材料可用于再生产。

(完整word版)自动控制原理(第2版)(余成波_张莲_胡晓倩)习题全解及MATLAB实验第8章

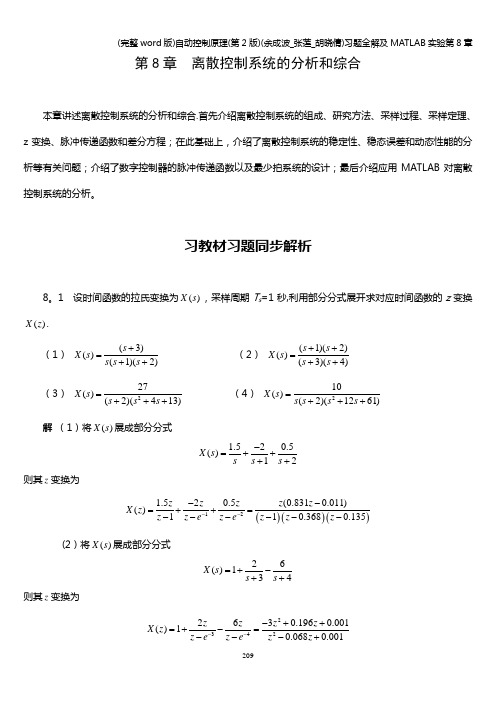

209第8章 离散控制系统的分析和综合本章讲述离散控制系统的分析和综合.首先介绍离散控制系统的组成、研究方法、采样过程、采样定理、z 变换、脉冲传递函数和差分方程;在此基础上,介绍了离散控制系统的稳定性、稳态误差和动态性能的分析等有关问题;介绍了数字控制器的脉冲传递函数以及最少拍系统的设计;最后介绍应用MATLAB 对离散控制系统的分析。

习教材习题同步解析8。

1 设时间函数的拉氏变换为()X s ,采样周期T s =1秒,利用部分分式展开求对应时间函数的z 变换()X z .(1) (3)()(1)(2)s X s s s s +=++ (2) (1)(2)()(3)(4)s s X s s s ++=++(3) 227()(2)(413)X s s s s =+++ (4) 210()(2)(1261)X s s s s s =+++ 解 (1)将()X s 展成部分分式1.520.5()12X s s s s -=++++ 则其z 变换为()()()121.520.5(0.8310.011)()110.3680.135z z z z z X z z z e z e z z z ----=++=------ (2)将()X s 展成部分分式26()134X s s s =+-++ 则其z 变换为23422630.1960.001()10.0680.001z z z z X z z e z e z z ---++=+-=---+210(3)将()X s 展成部分分式22233633(2)()24132(2)3s s X s s s s s s ++=-=-++++++ 则其z 变换为22222433(cos3)()2cos3z z ze X z z e z ze e -----=---+(4)将()X s 展开为部分分式2210059010515125012501()(2)(1261)614121261s X s s s s s s s s s +==⋅-⋅+++++++ 22225151100625614122501(6)52501(6)5s s s s s +=⋅-⋅+⋅-⋅+++++ 则其z 变换为26622612261255100cos52sin 5()6114125012cos525012cos5z z z ze ze X z z z e z ze e z ze e --------=⋅-⋅+⋅-⋅---+-+8。

Altium第08章-模拟行为仿真实现

>Altium Designer,打开AD13.0软件。

2.在AD主界面主菜单下选择New->Project->PCB

Project,创建一个名字为PCB_Project1.PrjPCB的新工

程。 3.按照前面所介绍的添加原理图的方法,添加名字为 Sheet1.SchDoc的原理图文件。

模拟行为仿真实现

何宾 2013.11

学习内容与目标

模拟行为仿真概念

基于行为模型的增益控制实现

基于行为模型的调幅实现

基于行为模型的滤波器实现

基于行为模型的压控振荡器实现

Copyright © 2009 Altium Limited

2

学习内容与目标

通过学习这个部分内容,能够更好地理解基于系统模 拟行为模型所实现的“系统级”电子线路前端设计的 SPICE验证。 通过SPICE的模拟行为仿真,更好的从系统级的角度把 握设计的原理,而不是仅仅局限在某个具体的设计实 现细节问题上。

Copyright © 2009 Altium Limited

基于行为模型的增益控制实现

构建增益控制行为模型 1.从Miscellaneous Devices.IntLib库、Simulation Pspice Functions.IntLib库中找到下列元件。并将其按照下图所示的位 置进行放置。

按下面参数设置:

Copyright © 2009 Altium Limited

基于行为模型的增益控制实现

Copyright © 2009 Altium Limited

基于行为模型的增益控制实现

3.Transient Analysis按默认参数设置。

eda教学1

EDA设计导论- PLD设计方法

设计已经从传统的自下而上的方法, 转变成自上而下的设计方法。传统上的设 计方法是自下而上的设计方法,是以固定 功能元件为基础,基于电路板的设计方法。 这种设计方法有下面的缺点:

第一章

系统调试、测试与性能分析

完整系统构成

设计依赖于设计人员的经验。

设计依赖于现有的通用元器件。

EDA 原理及应用

何宾 2008.09

E - mail: hebin@

课程进度安排:

56学时(课堂教学40学时,上机实验16学时) 课堂教学内容: 第1章-EDA设计导论 第2章-可编程逻辑器件设计方法 第3章-VHDL语言基础 第4章-数字逻辑单元设计 第5章-VHDL高级设计技术 第6章-基于HDL和原理图的设计输入 第7章-设计综合和行为仿真 第8章-设计实现和时序仿真 第9章-设计下载和调试 第10章-设计示例(数字钟、UART、数字电压表)

子系统设计的下载工具及硬件验证工具;

EDA设计导论- EDA技术涵义

● 大规模可编程逻辑器件(PLD)

第一章

现在所说的PLD器件一般包含现场可编程门阵列(FPGA)和复 杂可编程逻辑器件(CPLD)。

由于PLD的集成规模非常大,因此可利用先进的EDA工具进 行电子系统设计和产品开发。由于开发工具的通用性、设计语言的 标准化以及设计过程几乎与所用器件的硬件结构无关,因而设计开 发成功的各类逻辑功能块软件有很好的兼容性和可移植性。

EDA设计导论- EDA技术涵义

● 硬件描述语言

第一章

(5)支持的EDA工具:支持VHDL和Verilog的EDA工具很多,但 支持ABEL的综合器仅仅Dataio一家。

(6)国际化程度:VHDL和Verilog已成为IEEE标准,而ABEL正朝 国际化标准努力。在新世纪中,VHDL与Verilog语言将承担几乎全 部的数字系统设计任务。

“EDA技术”精品课程教学日历

第6章EDA工具应用

LPM使用

3

复习例6-10 P200

第七周

8

实验2正弦波信号发生器

LPM模块的使用

3

第八周

9

第7章有限状态机

3

预习实验8-1

第九周

10

实验3序列检测器设计

实验8-1

3

第十周

11

第8章RTL级设计

8.1 HDL描述的层次与风格

8.2 RTL描述与设计(1)

8.2 RTL描述与设计(2)

3

预习实验9-1

第十一周

12

实验4乐曲硬件演奏电路设计

实验9-1

3

第十二周

13

第9章行为仿真

3

10-8

预习实验5பைடு நூலகம்3

第十三周

14

实验5VGA显示控制电路设计

实验5-3

3

第十四周

15

第10章系统设计优化

总复习

3

第十五周

16

实验6创新设计实验

综合应用创新设计

答疑

3

第十六周

序号

授 课 内 容

大纲

要求

学时

作 业

备 注

1

第1章绪论

1.1EDA技术的发展

1.2现代数字系统的设计

1.3ASIC与FPGA

3

第一周

2

第2章FPGA结构原理

CPLD、FPGA的可编程原理、编程方法、JTAG

3

第二周

3

第3章Verilog HDL基础

3.1数字电路的描述

3.2 电路的行为描述(1)

3.3 电路的行为描述(2)

3

第8章电子线路综合设计1

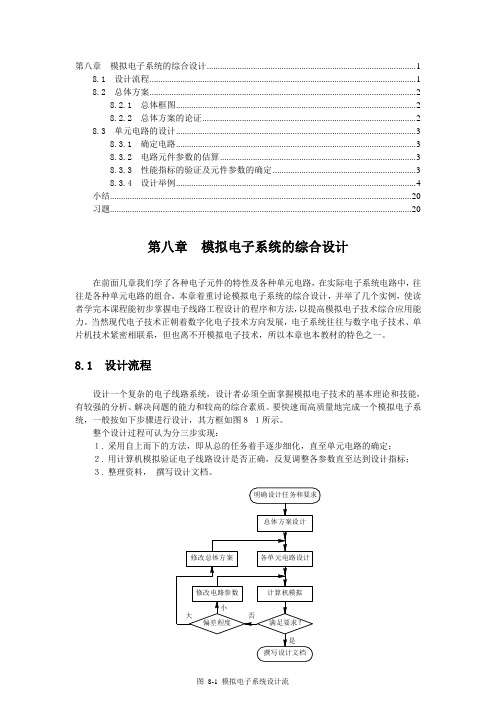

第八章 模拟电子系统的综合设计 (1)8.1 设计流程 .......................................................................................................... 1 8.2 总体方案 . (2)8.2.1 总体框图 ............................................................................................... 2 8.2.2 总体方案的论证 ..................................................................................... 2 8.3 单元电路的设计 .. (3)8.3.1 确定电路 (3)8.3.2 电路元件参数的估算 .............................................................................. 3 8.3.3 性能指标的验证及元件参数的确定 ......................................................... 3 8.3.4 设计举例 ............................................................................................... 4 小结........................................................................................................................ 20 习题 (20)第八章 模拟电子系统的综合设计在前面几章我们学了各种电子元件的特性及各种单元电路,在实际电子系统电路中,往往是各种单元电路的组合,本章着重讨论模拟电子系统的综合设计,并举了几个实例,使读者学完本课程能初步掌握电子线路工程设计的程序和方法,以提高模拟电子技术综合应用能力。

第8章 仿真模型的检验和验证

§8.3.1表面效度 仿真建模者的第一个目标是建立一个 使模型使用者和其他了解实际系统的人在 直观上认为合理的模型。 灵敏度分析也可以用来检查模型的表 面效度。 在进行灵敏度分析时,要注意选择最 关键的输入变量进行检验。

§8.3.2模型假设的验证 模型的假设一般分为两类:结构假设 和数据假设。 结构假设包括系统如何运行的问题, 通常涉及实际系统的简化和抽象。 数据假设应该以可靠数据的采集和对 数据正确的统计分析为基础。

§8.3.3输入—输出变换的验证 模型在验证阶段可视为一个输入—输 出变换。当输入数据和实际的输入数据一 致,并且模型中执行的策略也是系统中某 些点执行的策略时,模型的最终检验是模 型对实际系统未来行为特性的预测能力。

进行输入—输出变换验证的必要条 件是所研究系统的某种版本已经存在。 模型变化程度的影响从小到大为: ①单个数值参数的小变化。 ②统计分布形式的较小变化。 ③子系统逻辑结构的大变化。 ④新系统的不同设计方案的大变化。

⒋仿真结束后,运行模型是否打印了输 入参数,确信这些参数没有被修改过。 ⒌尽可能使运行模型成为一个独立文档。 ⒍如果运行模型包括动画,应该检验在 动画中观察到的是否能够模拟真实系统。 ⒎交互式运行控制器或试调器。 ⒏建议使用图形化界面。

能够快速显示出模型的合理性的两 组统计量是当前容量和总数。 对于特定的模型,不仅可以考虑特 定统计量是否合理,还可以计算某些长 时间运行系统的性能度量。 另一个对模型检验有帮助的重要方 法是文档说明。 更为复杂的有助于模型检验的方法 是跟踪。

Y 0 2.51 4.3 t0 5.34 S / n 0.82 / 6

对于双边检验:如果|t0|>tα/2,n-1,就拒 绝H0;否则接受H0。 查表得tα/2,n-1=2.571,因此拒绝H0。

计算机控制与仿真-第8章SIMULINK交互式仿真环境

封装是一种将子系统的内部实现细节隐藏起来,只暴露必要的接口和功能的技术。通过封装技术,用 户可以简化模型的复杂度,提高模型的可读性和可维护性。同时,封装还可以保护子系统的知识产权 ,防止未经授权的访问和修改。

03

连续系统建模与仿真方法

连续系统数学模型描述

微分方程

描述系统动态行为的数学形式,反映系统内部状态的 变化规律。

计算机控制与仿真第8章simulink交互

式仿真环境

目录

• Simulink交互式仿真环境概述 • Simulink模型构建基础 • 连续系统建模与仿真方法 • 离散系统建模与仿真方法

目录

• 混合系统建模与仿真方法 • 控制系统性能评估与优化 • 案例分析:倒立摆控制系统设计与仿真

01

Simulink交互式仿真环 境概述

传递函数

在频域中描述系统的输入与输出之间的关系,便于分 析系统的频率特性。

状态空间方程

以状态变量为核心描述系统动态行为,适用于多输入 多输出系统。

连续系统Simulink模型构建

模块库介绍

Simulink提供丰富的模块库,包括连续系统、 离散系统、数字信号处理等模块。

模型搭建步骤

创建模型窗口、选择所需模块、连接模块构建 系统模型。

基于Simulink的倒立摆控制系统设计

控制器设计

在Simulink中,可以使用各种控制算法来设计倒立摆控制器,如PID控制、 LQR控制、模糊控制等。设计过程中需要考虑控制器的稳定性、快速性和准确 性。

系统建模

根据倒立摆的数学模型,在Simulink中建立相应的系统模型。 该模型应包括倒立摆的物理参数、传感器和执行器等部分。

降低开发成本

Simulink的模块化设计和重用性 可以减少开发时间和成本,提高 开发效率。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计综合和行为仿真-综合选项的设置和综合

图8.1 综合属性设置窗口

设计综合和行为仿真-综合选项的设置和综合

准备对设计进行综合,然后生成网表(Netlist)文件, 下面给出综合的步骤; 1. 选择stopwatch.vhd 2. 在“Process”(处理)子窗口中,双击“Synthesis”, 开 始对设计进行综合。

图8.3 RTL原理图

设计综合和行为仿真-RTL符号查看

当完成综合后,在工程目录下,将存在一个NGC 文件。对于基于其它综合工具的综合实现可以参考 XST综合过程和相关综合工具的使用手册。

行为仿真的实现-生成测试向量

VHDL还可以描述变化的测试信号。描述测试信号的 变化和测试过程的模块叫做测试平台(Testbench),它可 以对任何一个Verilog/VHDL模块进行动态的全面测试。通 过对被测试模块的输出信号的测试,可以验证逻辑系统的 设计和结构,并对发现的问题及时修改。 测试平台是为逻辑设计仿真而编写的代码,它能直接 与逻辑设计接口。如图8.2所示,通过向逻辑设计施加激 励,检测被测模块的输出信号。

设计综合和行为仿真-XST综合工具概述

综合工具在对设计的综合过程中,主要执行以 下三个步骤: 1) 语法检查过程,检查设计文件语法是否有错误; 2) 编译过程,翻译和优化HDL代码,将其转换为综 合工具可以识别的元件序列; 3) 映射过程,将这些可识别的元件序列转换为可识 别的目标技术的基本元件;

设计综合和行为仿真

湖南大学电气与信息工程学院 叶佳卓

2014.4

设计综合和行为仿真-本章概要

本章详细介绍了设计综合和行为仿真的流程和方

法。 在设计综合部分,介绍了综合的概念、综合属性配置 方法和综合实现,以及RTL原理图查看。在行为仿真部 分,介绍了测试向量的生成、行为仿真工具、基于 Modelsim软件的行为仿真和基于ISE仿真器的行为仿真的 实现,同时还介绍了使用波形和VHDL语言建立测试向量 的方法。

查看综合报告(view Synthesis Report) 查看RTL原理图(View RTL schematic) 查看技术原理图(View Technology Schematic) 检查语法(Check Syntax) 产生综合后仿真模型(Generate Post-Synthesis Simulation Model)。

设计综合和行为真-XST综合工具概述

当所有的设计完成,并且进行完语法检查后,就可以 使用Xilinx的XST工具或Synplify工具进行综合了,综合工 具使用HDL代码,然后生成支持的网表格式EDIF或 NGC,然后Xilinx的实现工具将使用这些网表文件完成随 后的处理过程。 在ISE的主界面的处理子窗口的synthesis的工具可以完 成下面的任务:

设计综合和行为仿真-RTL符号查看

在综合完成后,XST将生成HDL代码所对应的原 理图描述(RTL Schematic)。可以通过RTL原理图查 看工具,看到综合后的逻辑连接关系。这里有两种原 理图描述: 1. RTL原理图(RTL Schmatic)是优化前的HDL代 码的逻辑; 2. 技术原理图(Technology Schematic)是HDL综 合完成后的设计和目标技术的映射。

设计综合和行为仿真-添加HDL测试平台

3. 点击“Open”按钮。 4. 检查该文件的“Association”属性选择为 “Simulation”。 5. 点击“OK”按钮。 ISE会自动识别顶层设计文件并将其与测试文件进行 关联。

设计综合和行为仿真 --基于Modelsim行为仿真实现

硬件描述语言如Verilog和VHDL等,都提供了两种基本 的建模方式:行为级和寄存器传输级。寄存器传输级是对 硬件逻辑进行可综合性的描述,使用的是VHDL语言中可 综合逻辑设计激励响应测试平台结果显示平台的描述部 分。 寄存器传输级代码可以由逻辑综合工具直接转换成门 级电路。 行为级描述是对硬件逻辑更为灵活和抽象的描述,描 述的重点在于硬件逻辑的功能,通常不考虑时序问题。行 为级代码通常不能被逻辑综合工具转换成门级电路。 测试平台以行为级描述为主,不使用寄存器传输级的 描述形式。

第8章 设计综合和行为仿真-行为仿真的实现 生成测试向量

建立测试平台时,首先应针对DUT的功能定义测试 向量;然后根据每一个测试向量的要求分别设计激励生成 和响应检测模块,要求激励生成模块能够能在DUT的接口 上产生该测试向量所需的信号激励,响应检测模块能够对 DUT在这种信号激励下的结果输出进行响应和检测;最后 将激励生成模块、DUT和响应检测模块相连,组成验证环 境,在仿真器上进行仿真,根据响应检测模块的检测报告 来判断测试向量是否通过测试。

设计综合和行为仿真-行为综合

行为级综合可以自动将系统直接从行为级描述综合为寄 存器传输级描述。 行为级综合的输入为系统的行为级描述,输出为寄存 器传输级描述的数据通路。 行为级综合工具可以让设计者从更加接近系统概念模 型的角度来设计系统。同时,行为级综合工具能让设计者 对于最终设计电路的面积、性能、功耗以及可测性进行很 方便地优化。 行为级综合所需要完成的任务从广义上来说可以分为分 配、调度以及绑定。

行为仿真的实现-生成测试向量

测试平台主要由两个组件构成:激励生成和响应检 测。它们同被测单元(DUT, Device Under Test)的关系如 图8.3所示。

激励生成 被测单元 图8.3 测试平台构成 响应检测

行为仿真的实现-生成测试向量

DUT是待测的逻辑电路。通常,DUT是使用硬件逻辑 描述语言HDL编写的寄存器传输级电路。 激励生成模块的主要功能是根据DUT输入接口的信号 时序,对DUT产生信号激励,将测试信号向量输入到DUT 中。响应检测模块根据DUT输入接口的信号时序,响应 DUT的输出请求,并检查输出结果的正确性。

设计综合和行为仿真-设置仿真工具

Xilinx的ISE工具提供了集成设计流程,该设计流程支 持基于Mentor Graphics公司Modelsim仿真工具和ISE仿真 工具,这两种仿真工具均可从工程向导中运行。 只有安装Modelsim软件才能使用Modelsim仿真工具, ModelSim PE和ModelSim SE是Mentor Graphics公司 ModelSim软件的完全版本。为配合ISE11库的仿真,需要 使用ModelSim6.0或更高版本。ModelSim XE是基于 ModelSim PE的ModelSim Xinlinx版本。 当安装ISE软件时,ISE仿真工具就自动安装完成,所 以不需要进行额外安装。

设计综合和行为仿真-行为综合

在集成电路设计领域,综合是指设计人员使用高级 设计语言对系统逻辑功能的描述,在一个包含众多结构、 功能、性能均已知的逻辑元件的逻辑单元库的支持下,将 其转换成使用这些基本的逻辑单元组成的逻辑网络结构实 现。这个过程一方面是在保证系统逻辑功能的情况下进行 高级设计语言到逻辑网表的转换,另一方面是根据约束条 件对逻辑网表进行时序和面积的优化。

设计综合和行为仿真-综合选项的设置和综合

综合选项能够使设计人员根据设计的要求进行设置 来影响综合行为。一种最常使用的综合选项是选择基 于面积或者速度,来实现综合优化目标。其它选项包 括控制触发器输出的最大扇出以及所希望的设计频率 等。

设计综合和行为仿真-综合选项的设置和综合

根据下面的步骤进入综合选项设置: 1. 在源文件(Source)视图中选择stopwatch.vhd文件 2. 在处理(Process)视图中,用鼠标右击“Synthesis” (综合)选项,在出现的菜单中选择“Properties”(属 性)。 3. 如图8.1所示,确保在属性设置窗口下的“Property display level”的选项设置为“Advanced”,这允许设计者 可 以看到所有可用的综合属性设置; 4. 在图8.1的界面左侧选择“Synthesis Option”标签选 项,将“Netlist Hierarchy”属性设置为“Rebuild”,点击

设计综合和行为仿真-RTL符号查看

通过下面的步骤,查看HDL设计的原理图描述: 1. 在处理子窗口,点击“+ Synthesize –XST”选 项,将其下面的功能分层展开; 2. 如果出现“Set RTL/Tech Viewer Startup Mode”(设置RTL/Tech 查看器启动模式)对话框,则选 择“Start with the Explored Wizard”。 3. 如图8.2的“Create RTL Schemaitc”(创建RTL符 号)开始界面,从“Available Element”列表中,选择 clk_divider和debounce元件,然后点击“Add”按钮将选 择的元件移动到“Selected Elements List”列表中。 4. 点击“Create Schematic”(创建原理图)按钮。

设计综合和行为仿真-RTL符号查看

图8.2 Create RTL Schemaitc开始界面

设计综合和行为仿真-RTL符号查看

RTL查看器允许设计者选择设计的一部分作为原理图 进行显示。如图8.3所示,当显示原理图时,双击符号, 进入到原理图和查看不同设计元件和连接性。鼠标右击 原理图来查看在原理图查看器中可以执行的各种操作。

设计综合和行为仿真-添加HDL测试平台

下面给出添加测试平台文件步骤和过程: 1. 如果建立一个新的测试平台文件,可选择 Project→New Source,选择文件类型为VHDL Test Bench 或Verilog Text Fixture,生成一个仿真文件,可以在这个 文件中定义所需要的测试平台及其测试向量。 2. 如果添加已经设计完成的测试平台文件,可选择 Project→Add Source,在该设计中选择测试平台文件 stopwatch_tb.vhd。

设计综合和行为仿真-行为综合

分配包括决定系统实现所需要的各个功能组件的个数 以及种类。这些组件以及资源来自采用寄存器传输级描述 的元件库,包括诸如运算逻辑单元、加法器、乘法器和多 路复用器等。分配同时也决定了系统中总线的数量、宽 度、以及类型。