10级DSP试卷A及答案

DSP试卷A答案

试卷A一、填空题1.1、指令周期1.2、程序读总线PRDB、程序地址总线PAB、数据读总线DRDB、数据写总线DWDB、数据读地址总线DRAB、数据写地址总线DWAB1.3、外部总线PBUS接口1.4、INTR、NMI、TRAP;片内外设信号;外部中断引脚上的信号1.5、程序存储器;数据存储器1.6、程序存储空间1.7、数据存储空间1.8、40 1.9、10 1.10、999(3E7h)二、简答题2.1、连续的自动排序模式:当触发信号触发SEQ1/SEQ2一组排序器对8个(可以小于8个)的任意通道按其预置好的排序进行转换。

每一轮转换结果被保存到8个结果寄存器,SEQ1的结果寄存器为RESULT0~RESULT7,SEQ2的结果寄存器为RESULT8~RESULT15。

当最后一个通道被转换结束后,即申请中断。

倘若这时CONTRUN位仍然为“1”,则SEQ1/SEQ2重新指向要转换的第一个通道。

重新开始新一轮的转换。

在启动/停止方式下可实现在时间上单个和多个启动信号触发源同步的功能,所不同的是,在排序器完成第一个转换序列之后,在中断服务程序中不需要被复位,也就是说:排序器初始指针不需要指到CONV00就可以被重新触发。

因此一个转换序列之后,排序器指针指到当前的通道。

在这种方式下,CONTRUN位必须被设置为“0”。

2.2、指令流水线由发生在指令执行期间内的一系列总线操作序列组成。

其特点是将指令的执行过程分为4个独立的阶段,即;(1)取指令阶段(Fetch);(2)指令译码阶段(Decode);(3)取操作数阶段(Operand);(4)指令执行阶段(Execute)。

由于上述4个阶段是相互独立的,所以这些操作同一时间段内可以并行进行。

因此,在任何给定的时钟周期内,可以同时有1~4条不同的指令被使能,而每条指令处于不同的执行阶段。

三、读程题3.1对下述指令进行注释,并填出指令执行后相关各寄存器和存储单元的内容: LDP #5 ;设置DP=5(指向0280h~02FFh 区)ADD 9h ,16 ;将数据存储单元0289h 的内容左移16位后加至;累加器。

DSP试卷10(答案)

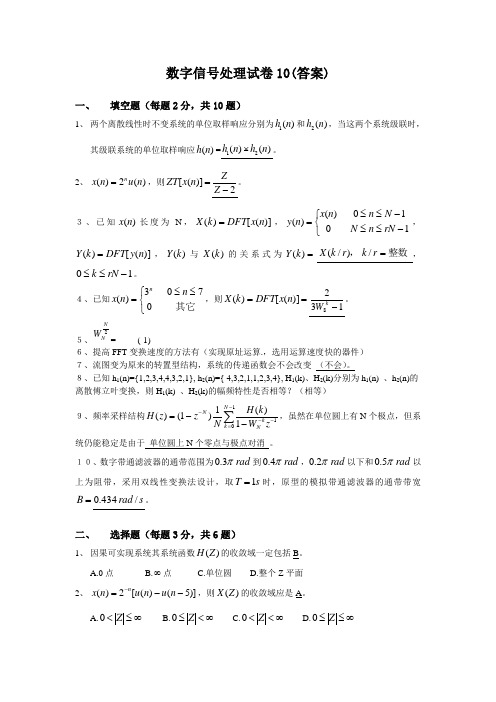

数字信号处理试卷10(答案)一、 填空题(每题2分,共10题)1、 两个离散线性时不变系统的单位取样响应分别为)(1n h 和)(2n h ,当这两个系统级联时,其级联系统的单位取样响应)(n h =)()(21n h n h ⨯。

2、 )(2)(n u n x n =,则=)]([n x ZT 2-Z Z。

3、已知)(n x 长度为N ,)]([)(n x DFT k X =,⎩⎨⎧-≤≤-≤≤=1100)()(rN n N N n n x n y ,)]([)(n y DFT k Y =,)(k Y 与)(k X 的关系式为=)(k Y 整数,=r k r k X /)/(,10-≤≤rN k 。

4、已知⎩⎨⎧≤≤=其它7003)(n n x n,则==)]([)(n x DFT k X 1328-k W 。

5、2N NW=_____(-1)6、提高FFT 变换速度的方法有(实现原址运算.,选用运算速度快的器件) 7、流图变为原来的转置型结构,系统的传递函数会不会改变 (不会)。

8、已知h 1(n)={1,2,3,4,4,3,2,1}, h 2(n)={ 4,3,2,1,1,2,3,4}, H 1(k)、H 2(k)分别为h 1(n) 、h 2(n)的离散傅立叶变换,则H 1(k) 、H 2(k)的幅频特性是否相等?(相等) 9、频率采样结构∑-=-----=1011)(1)1()(N k k N NzW k H N zz H ,虽然在单位圆上有N 个极点,但系统仍能稳定是由于 单位圆上N 个零点与极点对消 。

10、数字带通滤波器的通带范围为rad π3.0到rad π4.0,rad π2.0以下和rad π5.0以上为阻带,采用双线性变换法设计,取s T 1=时,原型的模拟带通滤波器的通带带宽=B s rad /434.0。

二、 选择题(每题3分,共6题)1、 因果可实现系统其系统函数)(Z H 的收敛域一定包括B 。

DSP原理与应用试题A答案及评分标准

2011—2012学年第1学期《DSP原理与应用》试题(A卷)答案及评分标准一、选择题(共5题,每题2分,共10分)1、C2、B3、D4、A5、D二、填空题(共10空,每空2分,共20分)1、数字信号处理器2、1、3、4 3、堆栈指针、页指针4、立即数寻址、堆栈寻址5、助记符、操作数三、指令解释(共4题,每题5分,共20分)1、将立即数60H装入AR3寄存器中2、无任何操作3、把数据从栈顶弹入到存储器映射寄存器4、(30H)=50H,(40H)=50H,AR3=60H,AR4=80H四、简答题(共3题,每题10分)1、答:目前,市场上主流的处理器有CPU、DSP、单片机、CPLD与FPGA等可编程逻辑器件,与DSP相比,它们的优缺点如下。

CPU优点是超过100MHz的工作频率;完善的开发手段;丰富的软件支持;支持各种扩展功能的整机、板卡;CPU的缺点是信号处理速度慢,不能满足实时要求;性价比、体积、功耗比DSP差。

单片机优点是中断多,适合做事务处理;控制接口多,适合以控制为主的模数混合设计;价格比DSP低得多;单片机缺点是没有硬件乘法器;输入/输出能力差,运算速度慢;存储器容量比DSP小;A/D精度比DSP低。

FPGA/CPLD优点是时序控制能力强(没有指令周期,速度快);控制能力较强(但比单片机差)。

FPGA/CPLD缺点是适合单一运算,混合功能实现差。

2、答:直接寻址是指在指令中包含有数据存储器地址的低7位,这7位作为偏移地址,与基地址一同构成16位的数据存储器地址。

数据页指针DP和堆栈指针SP都可以用来作为基地址,由寄存器ST1的CPL位决定采用何种指针,当CPL=0时,选用数据页指针DP的直接寻址方式。

选择DP中的9位数据作为高位,与指令中指定的数据存储器中的7位数据作为低位直接相连作为16位数据存储单元的地址,如下图示3、答:(1)中断请求某一外设发出中断请求时,将该外设的中断请求标志位(IFR)置1。

DSP测试题及答案-推荐下载

答:(1)TMS320VC5402 有 13 个可屏蔽中断。 (2)TMS320VC5402 有 的 13 个可屏蔽中断分别是:(课本 56 页最下面) (3)RS 和 NMI 属于外部硬件中断。

2、 TMS320VC5416-160 的指令周期是多少毫秒?它的运算速度是多少 MIPS? 答:TMS32S。

3、 TMS320C54x 芯片的流水线操作共有多少个操作阶段?每个阶段执行什么任务?完成 一条指令都需要哪些操作周期?

(2).bss x,4 .data table: .word 4,8,16,32 …… STM #x,AR1 RPT #2 MVPD table,*+AR2

答:数据表 table 中的常量 4 传送到以变量 x 的地址为地址的存储单元中;数据表 table 中 的常量 8 传送到以变量 x+1 的地址为地址的存储单元中;数据表 table 中的常量 16 传 送到以变量 x+2 的地址为地址的存储单元中。

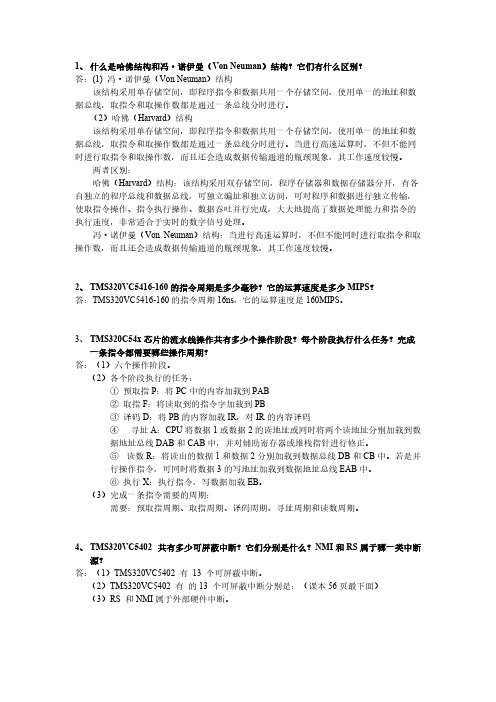

1、 什么是哈佛结构和冯·诺伊曼(Von Neuman)结构?它们有什么区别? 答:(1) 冯·诺伊曼(Von Neuman)结构

该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数 据总线,取指令和取操作数都是通过一条总线分时进行。

(2)哈佛(Harvard)结构 该结构采用单存储空间,即程序指令和数据共用一个存储空间,使用单一的地址和数 据总线,取指令和取操作数都是通过一条总线分时进行。当进行高速运算时,不但不能同 时进行取指令和取操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。 两者区别: 哈佛(Harvard)结构:该结构采用双存储空间,程序存储器和数据存储器分开,有各 自独立的程序总线和数据总线,可独立编址和独立访问,可对程序和数据进行独立传输, 使取指令操作、指令执行操作、数据吞吐并行完成,大大地提高了数据处理能力和指令的 执行速度,非常适合于实时的数字信号处理。 冯·诺伊曼(Von Neuman)结构:当进行高速运算时,不但不能同时进行取指令和取 操作数,而且还会造成数据传输通道的瓶颈现象,其工作速度较慢。

DSP原理及应用试卷_附答案卷A

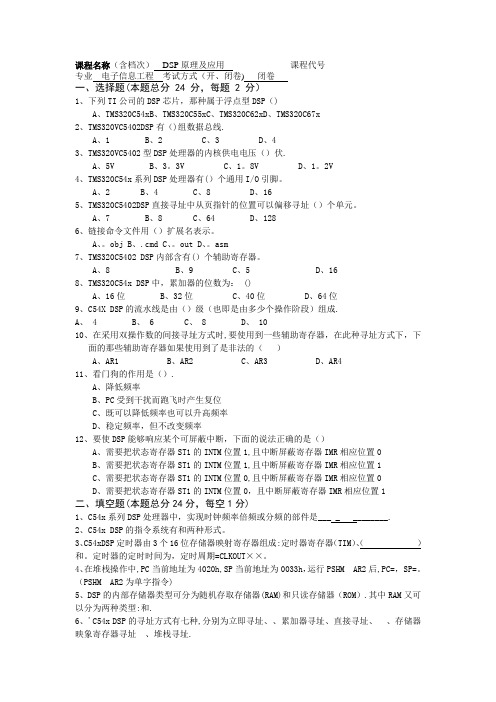

课程名称(含档次)DSP原理及应用课程代号专业电子信息工程考试方式(开、闭卷) 闭卷一、选择题(本题总分 24 分,每题 2 分)1、下列TI公司的DSP芯片,那种属于浮点型DSP()A、TMS320C54xB、TMS320C55xC、TMS320C62xD、TMS320C67x2、TMS320VC5402DSP有()组数据总线.A、1B、2C、3D、43、TMS320VC5402型DSP处理器的内核供电电压()伏.A、5VB、3。

3VC、1。

8VD、1。

2V4、TMS320C54x系列DSP处理器有()个通用I/O引脚。

A、2B、4C、8D、165、TMS320C5402DSP直接寻址中从页指针的位置可以偏移寻址()个单元。

A、7B、8C、64D、1286、链接命令文件用()扩展名表示。

A、。

objB、.cmdC、。

outD、。

asm7、TMS320C5402 DSP内部含有()个辅助寄存器。

A、8B、9C、5D、168、TMS320C54x DSP中,累加器的位数为: ()A、16位B、32位C、40位D、64位9、C54X DSP的流水线是由()级(也即是由多少个操作阶段)组成.A、 4B、 6C、 8D、 1010、在采用双操作数的间接寻址方式时,要使用到一些辅助寄存器,在此种寻址方式下,下面的那些辅助寄存器如果使用到了是非法的()A、AR1B、AR2C、AR3D、AR411、看门狗的作用是().A、降低频率B、PC受到干扰而跑飞时产生复位C、既可以降低频率也可以升高频率D、稳定频率,但不改变频率12、要使DSP能够响应某个可屏蔽中断,下面的说法正确的是()A、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置0B、需要把状态寄存器ST1的INTM位置1,且中断屏蔽寄存器IMR相应位置1C、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置0D、需要把状态寄存器ST1的INTM位置0,且中断屏蔽寄存器IMR相应位置1二、填空题(本题总分24分,每空1分)1、C54x系列DSP处理器中,实现时钟频率倍频或分频的部件是___ _ ________.2、C54x DSP的指令系统有和两种形式。

DSP原理及应用答案

(2) SP=0x3120;

三、应用题(10分)

得分

评卷人

设CLKOUT=8MHz,试阅读下列程序。试回答,引脚XF产生什么波形的信号?若要求方波周期改为16s,T0中断周期减小到原来一半,试说明程序的修改方法。

程序:

.title "time.asm"

.mmregs

rete修正指针marar30bar3ar0ar3并反向进位测试指令bitfx11x1条件转移bcl1ntctc位为零则转移到l1条件转移banzl2ar2ar2不为0则转移到l2条件转移xc1alt小于0跳过1条指令执行传送指令mvpdtablear1程序区到数据区的传送传送指令ltdar1数据t同时移位ar11ar1堆栈指令pshmpopmpshdpopd对mmr对数据区累加指令addar2a数据加上a存于a减法指令subar2a减去数据存于a条件减法subcdena用于除法运算乘法指令mpyanum数据与ah相乘存于b数据存于乘加指令macar2a数据与t相乘后加a的内容乘加指令macar2ar3a两个数据相乘后加a的内容位操作指令rsbxssbx重复指令rptzst1第14cpl直接寻址基址方式位st1第11intm可屏蔽中断总开关st1frct乘法小数方式控制位定时器参数内容描述定时周期clkouttddr1prd1pcr1512

.text

_c_int01:STM #x,AR1

RPT #15

MVPD table,* AR1+

CALL bitrev

end:B end

bitrev:STM #8,AR0

STM #x,AR3

STM #y,AR4

RPT #14

DSP试题及答案

1、常用的设备和CPU之间数据传送控制方式有4种,它们是程序直接控制方式、中断控制方式、DMA方式和通道方式。

2、DMA与普通中断方式的区别直接存储存取方式(DMA)是在存储器与输入输出设备间直接传送数据,是一种完全由硬件完成输入输出操作的方式。

普通中断方式是在数据缓冲寄存器满后,发中断请求,CPU进行中断处理DMA方式则是以数据块为单位传输的,在所要求传送的数据块全部传送结束时要求CPU进行中断处理,大大减少了CPU进行中断处理的次数总结:DMA方式不需CPU干预传送操作,仅仅是开始和结尾借用CPU一点时间,其余不占用CPU任何资源,中断方式是程序切换,每次操作需要保护和恢复现场1、简述DSP系统的构成和工作过程。

答:DSP系统的构成:一个典型的DSP系统应包括抗混叠滤波器、数据采集A/D转换器、数字信号处理器DSP、D/A转换器和低通滤波器等。

DSP系统的工作过程:①将输入信号x(t)经过抗混叠滤波,滤掉高于折叠频率的分量,以防止信号频谱的混叠。

②经过采样和A/D转换器,将滤波后的信号转换为数字信号x(n)。

③数字信号处理器对x(n)进行处理,得数字信号y(n)。

④经D/A转换器,将y(n)转换成模拟信号;⑤经低通滤波器,滤除高频分量,得到平滑的模拟信号y(t)。

2、简述DSP系统的设计步骤。

答:①明确设计任务,确定设计目标。

②算法模拟,确定性能指令。

③选择DSP芯片和外围芯片。

④设计实时的DSP芯片系统。

⑤硬件和软件调试。

⑥系统集成和测试。

3、DSP的引脚分为哪几类?答:F28x系列DSP的引脚分为如下5类:(1)XINTF(External Interface )信号(2)JTAG以及其他信号(3)模数转换输入信号(4)电源信号(5)GPIO信号4、F28x共有几种寻址方式?分别是哪几种?答:F28x共有四种寻址方式:(1) 直接寻址模式、(2) 堆栈寻址模式、(3)、间接寻址模式,(4) 寄存器寻址模式。

10级(A)卷参考答案及评分标准

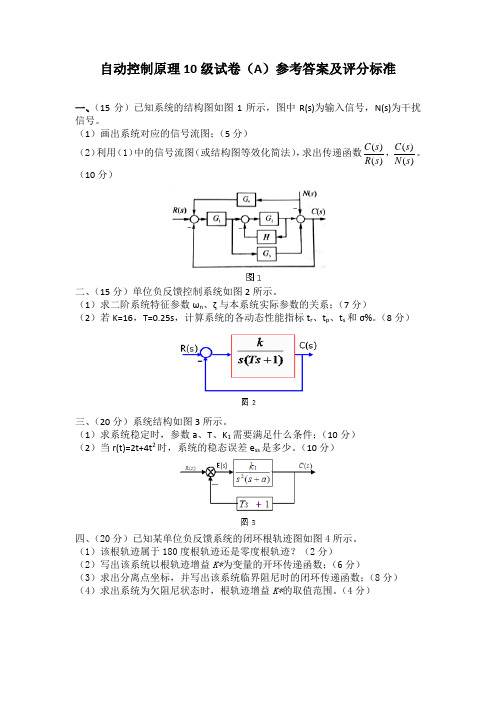

自动控制原理10级试卷(A )参考答案及评分标准一、(15分)已知系统的结构图如图1所示,图中R(s)为输入信号,N(s)为干扰信号。

(1)画出系统对应的信号流图;(5分)(2)利用(1)中的信号流图(或结构图等效化简法),求出传递函数)()(s R s C ,)()(s N s C 。

(10分)二、(15分)单位负反馈控制系统如图2所示。

(1)求二阶系统特征参数ωn 、ζ与本系统实际参数的关系;(7分)(2)若K=16,T=0.25s ,计算系统的各动态性能指标t r 、t p 、t s 和σ%。

(8分)三、(20分)系统结构如图3所示。

(1)求系统稳定时,参数a 、T 、K 1需要满足什么条件;(10分)(2)当r(t)=2t+4t 2时,系统的稳态误差e ss 是多少。

(10分)四、(20分)已知某单位负反馈系统的闭环根轨迹图如图4所示。

(1)该根轨迹属于180度根轨迹还是零度根轨迹?(2分)(2)写出该系统以根轨迹增益K*为变量的开环传递函数;(6分)(3)求出分离点坐标,并写出该系统临界阻尼时的闭环传递函数;(8分)(4)求出系统为欠阻尼状态时,根轨迹增益K*的取值范围。

(4分)五、(10分)某系统的开环传递函数为12)()(-=s s H s G 。

(1)试证明当ω由0→+∞变化时,系统的开环幅相曲线是一个半圆;(6分)(2)根据(1)中的证明结果,画出系统的开环幅相曲线,并利用奈氏判据判断闭环系统的稳定性。

(4分)六、(15分)已知某单位反馈的最小相位系统,有开环极点-40和-10,并且当开环增益K=25时,系统的开环幅相频率特性G (j ω)曲线如图所示。

(1)试写出开环传递函数G(s)的表达式;(5分)(2)作出其近似对数幅频特性曲线(要计算出各个转折频率处的幅值分贝数,并在曲线上标出);(6分)(3)求系统开环截止频率ωc 。

(4分)七、(10分)设离散控制系统结构如图所示。

DSP原理与应用-期末试卷A及答案资料

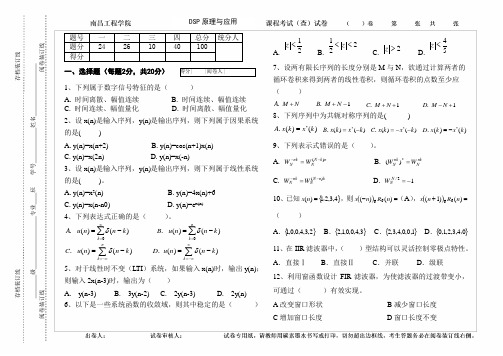

题号 题号一 二 三 四 总分 统分人题分 24 26 10 40 100 得分 一、选择题(每题2分,共20分) 得分| |阅卷人| 1、下列属于数字信号特征的是( ) A. 时间离散、幅值连续 B. 时间连续、幅值连续C. 时间连续、幅值量化D. 时间离散、幅值量化 2、设x(n)是输入序列,y(n)是输出序列,则下列属于因果系统 的是( ) A. y(n)=x(n+2) B. y(n)=cos(n+1)x(n) C. y(n)=x(2n) D. y(n)=x(-n)3、设x(n)是输入序列,y(n)是输出序列,则下列属于线性系统 的是( )。

A. y(n)=x 2(n) B. y(n)=4x(n)+6C. y(n)=x(n-n0)D. y(n)=e x(n) 4、下列表达式正确的是( )。

0. ()()k A u n n k δ∞==-∑ 0. ()()nk B u n n k δ==-∑ . ()()n k C u n n k δ=-∞=-∑ . ()()k D u n n k δ∞=-∞=-∑5、对于线性时不变(LTI )系统,如果输入x(n)时,输出y(n); 则输入2x(n-3)时,输出为( ) A. y(n-3) B. 3y(n-2) C. 2y(n-3) D. 2y(n)6、以下是一些系统函数的收敛域,则其中稳定的是( ) A. 12z < B. 122z << C. 2z > D. 45z <7、设两有限长序列的长度分别是M 与N ,欲通过计算两者的循环卷积来得到两者的线性卷积,则循环卷积的点数至少应( ). A M N + . 1B M N +- . 1C M N ++ . 1D M N -+ 8、下列序列中为共轭对称序列的是( ) . ()()A x k x k *= . ()()B x k x k *=- . ()()C x k x k *=-- . ()()D x k x k *=-9、下列表示式错误的是( )。

DSP处理器及应用试卷A标准答案

考试类别[学生填写](□正考 □补考 □重修 □补修 □缓考 □其它)一.DSP 芯片的主要结构特点什么?(10分)答:(1)哈佛结构(2)专用的硬件乘法器 (3)流水线操作 (4)特殊的DSP 指令 (5)快速的指令周期二.看门狗单元工作原理是什么?(10分)答:看门狗单元其本质是一个定时器电路;若使能看门狗单元,则在系统运行时,看门狗定时器自动计数;如果不能定时清除看门狗计数器(俗称“喂狗”,或“踢狗”Kick Dog ),那么看门狗定时器就会溢出从而引起看门狗中断,强行系统复位。

28XDSP 芯片有独立的看门狗模块,看门狗计数器WDCNTR 为8位,计数器达到最大值28-1=255 时,看门狗模块输出一个DSP 系统复位脉冲 。

喂狗操作:在看门狗计数器达到最大值之前向看门狗复位密钥寄存器WDKEY 先后写入0x55和0xAA ,则看门狗计数器清零,并自动开始下一轮的递增计数。

三.如图是外设时钟控制寄存器PCLKCR,若关断EVA 模块,使能ADC 模块,如何设置该寄存器?(10分)答:EV AENCLK=0, ADCENCLK=1.四.如果由片外30MHz 的有源晶振提供时基信号,需要如何设置使F2812的 CPU 系统时钟成为150MHz 频率?(10分)答:XF_XPLLDIS 设置成高电平,PLL 控制寄存器PLLCR 中0到3位(DIV)设置成1010,则CPU 系统时钟=30X=150MHz题号 一 二 三 四 五 六 七 八 九 十 总分 得分评阅人线订装郑州轻工业学院2017—2018学年 第1学期D S P 处理器及应用试卷A专业年级及班级 姓名 学号五、如图是通用定时器的连续增减计数模式,写出其工作原理。

(10分)答:GP定时器按照定标的输入时钟加计数,直到计数器的值和周期寄存器的值匹配,之后的下一个时钟的上升沿,GP减计数直到计数器为0,并开始以加计数的方式开始下一个计数周期,其间外设周期匹配、下溢、上溢等中断事件标志位产生,并产生可以启动ADC模块的事件。

dsp期末考试试题开卷

dsp期末考试试题开卷### DSP期末考试试题#### 一、选择题(每题2分,共20分)1. 在数字信号处理中,DFT(离散傅里叶变换)的主要作用是什么?A. 频域分析B. 信号滤波C. 信号放大D. 信号调制2. 下列哪个不是数字滤波器的设计方法?A. 脉冲响应不变法B. 双线性变换法C. 窗函数法D. 傅里叶变换法3. 以下哪个是线性时不变系统的属性?A. 时间可变B. 线性C. 非线性D. 时变4. 采样定理指出,如果信号的最高频率为f_max,那么采样频率至少应为:A. f_maxB. 2f_maxC. 3f_maxD. 4f_max5. FFT(快速傅里叶变换)的主要优点是什么?A. 计算精度高B. 计算速度快C. 易于实现D. 适用于所有信号...(此处省略其他选择题)#### 二、简答题(每题10分,共20分)1. 简述数字滤波器和模拟滤波器的区别,并举例说明数字滤波器的应用场景。

2. 解释什么是过采样和欠采样,并讨论它们在信号处理中的影响。

#### 三、计算题(每题15分,共30分)1. 给定一个离散时间信号 x[n] = {1, 2, 3, 4, 5},请计算其DFTX[k],并画出幅度谱和相位谱。

2. 假设有一个低通滤波器,其理想频率响应为H(ω) = 1 (0 ≤ ω≤ π/3),H(ω) = 0 (π/3 < ω ≤ π)。

请设计一个简单的数字低通滤波器,并给出其脉冲响应 h[n]。

#### 四、分析题(每题15分,共30分)1. 讨论在数字信号处理中,时域分析和频域分析各自的优势和局限性。

2. 描述一个实际的信号处理问题,说明如何使用数字滤波器来解决该问题,并解释所选滤波器类型的理由。

#### 五、综合应用题(共30分)1. 设计一个数字滤波器,用于去除音频信号中的噪声。

请说明所选滤波器的类型,设计过程,以及预期的滤波效果。

2. 给定一段音频信号,使用FFT分析其频谱特性,并讨论如何通过数字滤波器改善其音质。

DSP历年期末试卷及答案

膂试卷1腿一.填空题(本题总分12分,每空1分)1.TMS320VC5402型DSP 的内部采用条位的多总线结构。

芆2.TMS329VC5402型DSP 有个辅助工作寄存器。

袂3.在链接器命令文件中,.在链接器命令文件中,PAGE PAGE PAGE 1通常指1通常指1通常指________________________存储空间。

存储空间。

蚀4.TI 公司DSP 处理器的软件开发环境是处理器的软件开发环境是______________________________________________________。

羇5.直接寻址中从页指针的位置可以偏移寻址个单元。

莆6.TMS320C54x 系列DSP 处理器上电复位后,程序从指定存储地址程序从指定存储地址________________________单元开始工作。

单元开始工作。

芃7.MS320C54X DSP 主机接口HPI 是________________位并行口。

位并行口。

莂8.TMS320VC5402型DSP 处理器的内核供电电压处理器的内核供电电压________________________伏。

伏。

羀9. C54x 系列DSP 上电复位后的工作频率是由片外3个管脚;;来决定的。

蒆二.判断题(本题总分10分,每小题1分,正确打“√”,错误打“×”)蚄1.DSP DSP 处理器处理器TMS320VC5402的供电电压为5V 5V。

()袀2.TMS320VC5402型DSP 内部有8K 字的ROM ROM,,用于存放自举引导程序、用于存放自举引导程序、u u 律和A 律扩展表、sin 函数表以及中断向量表。

(?? ?? ))3.MEMORY 伪指令用来指定链接器将输入段组合成输出段方式,以及输出段在存储器中的位置。

(?? ?? ))4. DSP 的流水线冲突产生的原因是由于DSP 运行速度还不够快。

()蝿5.DSP 和MCU 属于软件可编程微处理器,用软件实现数据处理;而不带CPU 软核的FPGA 属于硬件可编程器件,用硬件实现数据处理。

DSP原理及应用答案(精)

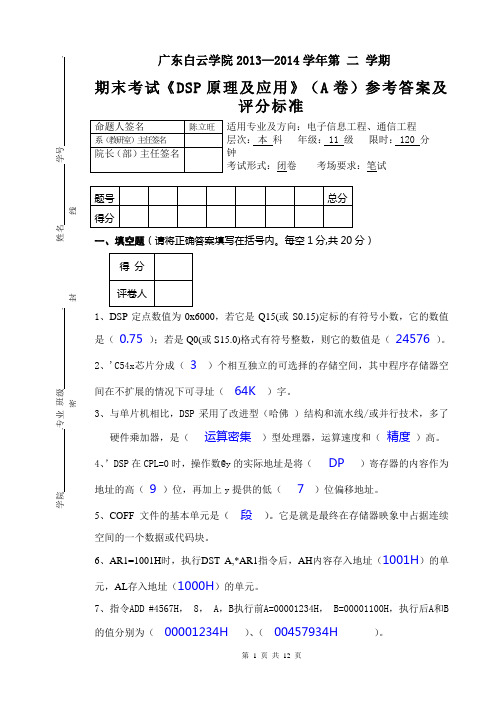

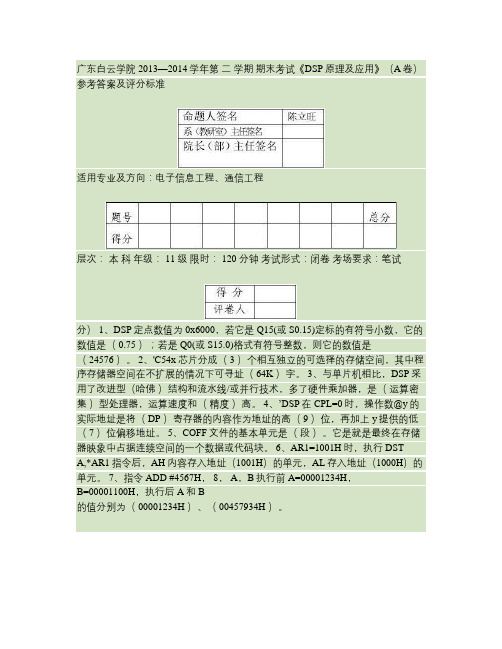

广东白云学院2013—2014学年第二学期期末考试《DSP原理及应用》(A卷)参考答案及评分标准适用专业及方向:电子信息工程、通信工程层次:本科年级: 11 级限时: 120 分钟考试形式:闭卷考场要求:笔试分) 1、DSP定点数值为0x6000,若它是Q15(或S0.15)定标的有符号小数,它的数值是( 0.75 );若是Q0(或S15.0)格式有符号整数,则它的数值是( 24576 )。

2、'C54x芯片分成( 3 )个相互独立的可选择的存储空间,其中程序存储器空间在不扩展的情况下可寻址( 64K )字。

3、与单片机相比,DSP采用了改进型(哈佛)结构和流水线/或并行技术,多了硬件乘加器,是(运算密集)型处理器,运算速度和(精度)高。

4、’DSP在CPL=0时,操作数@y的实际地址是将( DP )寄存器的内容作为地址的高( 9 )位,再加上y提供的低( 7 )位偏移地址。

5、COFF文件的基本单元是(段)。

它是就是最终在存储器映象中占据连续空间的一个数据或代码块。

6、AR1=1001H时,执行DST A,*AR1指令后,AH内容存入地址(1001H)的单元,AL存入地址(1000H)的单元。

7、指令ADD #4567H, 8, A,B执行前A=00001234H,B=00001100H,执行后A和B的值分别为( 00001234H )、( 00457934H )。

第 1 页共 12 页8、 'C54x芯片的中断系统可分为硬件中断和(软件中断),还可以分为可屏蔽中断和(非屏蔽中断)。

9、'C54x芯片的硬件复位地址为( FF80H ),INT0的中断序号为16,IPTR=1FFH时其中断向量地址为( FFC0H )。

10. 在’C54x DSP寻址和指令系统中,操作数Xmem和Ymem表示(数据存储器双寻址数据),Lmem表示(长字寻址的32位数据存储器数据)。

DSP final10-answer-推荐下载

B. 时域为离散周期序列,频域也为离散周期序列

C. 时域为离散无限长序列,频域为连续周期信号

D. 时域为离散有限长序列,频域也为离散有限长序列

C. 2πδ(ω) )

C. 3y(n)

5.若一模拟信号为带限,且对其抽样满足奈奎斯特条件,理想条件下将抽样信号通过 即可完全不失

真恢复原信号( )

A. 理想低通滤波器

4. 实序列 x(n)的 10 点 DFT[x(n)]=X(k)(0≤k≤9),已知 X(1)=1+j,则 X(9)=________。 5. 设 X (z) 是 x(n) 的 Z 变换,则 x* (n) 的 Z 变换为 ______ 。

三、判断题(每题 2 分,共 10 分)

1. FFT 是 DTFT 的快速算法。( ) 2. IIR 滤波器和 FIR 滤波器设计方法根据模拟滤波器来设计数字滤波器的。( ) 3. 输入信号不同,则对应的系统频率响应特性也不同。( )

4. 有限长序列 x(n) 的 N 点 DFT 可以看作是 x(n) 以 N 为周期延拓序列的 DFS 的主值区间。( )

5. 频率采样法是设计 FIR 滤波器的一种方法。( )

四、完成下列各题(每题 5 分,共 20 分)

1. 画出按时域抽取 N=4 点基 2FFT 的信号流图。 答:

2. 有一理想抽样系统,抽样频率为 s 6 ,抽样后经理想低通滤波器 Ha ( j) 还原,其中有两个输入 信号 xa1(t) cos 2 t , xa2 (t) cos 5 t ,问输出信号 ya1(t) , ya2 (t) 是否有失真?

2012-2013(二)通信、电子 10 级数字信号处理(A)参考答案及评分标准

一、选择题(四选一,每题 1 分,共 10 分)

DSP试题及答案集(附复习资料)解析

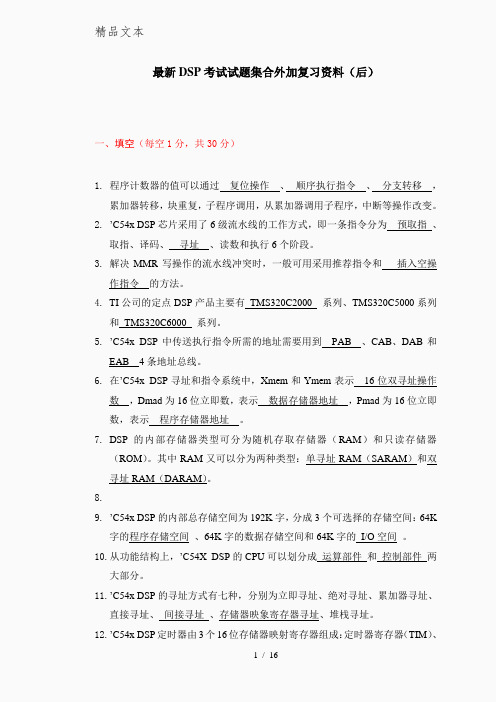

最新DSP考试试题集合外加复习资料(后)一、填空(每空1分,共30分)1.程序计数器的值可以通过复位操作、顺序执行指令、分支转移,累加器转移,块重复,子程序调用,从累加器调用子程序,中断等操作改变。

2.’C54x DSP芯片采用了6级流水线的工作方式,即一条指令分为预取指、取指、译码、寻址、读数和执行6个阶段。

3.解决MMR写操作的流水线冲突时,一般可用采用推荐指令和插入空操作指令的方法。

4.TI公司的定点DSP产品主要有TMS320C2000 系列、TMS320C5000系列和TMS320C6000 系列。

5.’C54x DSP中传送执行指令所需的地址需要用到PAB 、CAB、DAB和EAB 4条地址总线。

6.在’C54x DSP寻址和指令系统中,Xmem和Ymem表示16位双寻址操作数,Dmad为16位立即数,表示数据存储器地址,Pmad为16位立即数,表示程序存储器地址。

7.DSP的内部存储器类型可分为随机存取存储器(RAM)和只读存储器(ROM)。

其中RAM又可以分为两种类型:单寻址RAM(SARAM)和双寻址RAM(DARAM)。

8.9.’C54x DSP的内部总存储空间为192K字,分成3个可选择的存储空间:64K字的程序存储空间、64K字的数据存储空间和64K字的I/O空间。

10.从功能结构上,’C54X DSP的CPU可以划分成运算部件和控制部件两大部分。

11.’C54x DSP的寻址方式有七种,分别为立即寻址、绝对寻址、累加器寻址、直接寻址、间接寻址、存储器映象寄存器寻址、堆栈寻址。

12.’C54x DSP定时器由3个16位存储器映射寄存器组成:定时器寄存器(TIM)、定时器周期寄存器(PRD )和 定时器控制寄存器(TCR ) 。

13. 主机接口(HPI ,Host Port Interface ) 是TMS320C54x 系列定点芯片内部具有的一种接口部件,主要用于DSP 与其他总线或CPU 进行通信。

DSP历年期末试卷及答案

试卷1一.填空题(本题总分 分,每空 分).❆✞型 的内部采用 条 位的多总线结构。

.❆✞型 有 个辅助工作寄存器。

.在链接器命令文件中, ✌☝☜ 1通常指♉♉♉♉♉♉♉♉存储空间。

.❆✋公司 处理器的软件开发环境是♉♉♉♉♉♉♉♉♉♉♉♉♉♉♉♉♉♉。

.直接寻址中从页指针的位置可以偏移寻址 个单元。

.❆⌧系列 处理器上电复位后,程序从指定存储地址♉♉♉♉♉♉♉♉单元开始工作。

. ✠ 主机接口☟✋是♉♉♉♉♉♉♉♉位并行口。

❆✞型 处理器的内核供电电压♉♉♉♉♉♉♉♉伏。

⌧系列 上电复位后的工作频率是由片外 个管脚 ;; 来决定的。

二.判断题(本题总分 分,每小题 分,正确打“√”,错误打“×”) . 处理器❆ ✞ 的供电电压为 ✞。

( ) .❆✞型 内部有 字的 ,用于存放自举引导程序、◆律和✌律扩展表、♦♓⏹函数表以及中断向量表。

(∙∙ ). ☜✡伪指令用来指定链接器将输入段组合成输出段方式,以及输出段在存储器中的位置。

(∙∙ ) 的流水线冲突产生的原因是由于 运行速度还不够快。

( ). 和 ✞属于软件可编程微处理器,用软件实现数据处理;而不带 ✞软核的☞ ☝✌属于硬件可编程器件,用硬件实现数据处理。

∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙∙ ∙∙∙ (∙∙ ) ⌧系列 的 ✞寄存器及片内外设寄存器映射在数据存储空间的♒♒中。

( ) ❆✠ 系列 可以通过设置 ✞☹✡位实现数据存储空间和程序存储空间共享片内 。

(∙∙ ) ❆✞型 汇编指令 ☜✌✌的寻址范围为 字。

( ) 在❆✞型 所有中断向量中,只有硬件复位向量不能被重定位,即硬件复位向量总是指向程序空间的 ☞☞ ☟位置。

DSP原理与应用试卷A及答案

《DSP 原理与应用A 卷》试卷第1页(共2页)班级业余本/业余专/脱产本/脱产专专业姓名学号成绩密封线一、填空题(每空1分,总共20分)1、常用的设备和CPU 之间数据传送控制方式有4种,它们是,,,。

2、定时器主要由3个寄存器所组成,包括、、。

3、TI 公司DSP 处理器的软件开发环境是__________________。

4、在C54X 系列中,按流水线工作方式,分支转移指令的分为哪两种类型:_______、_______。

5、TMS320VC5402型DSP 的CPU 采用寄存器作为专用硬件实现移位功能。

6、汇编语句“STL A ,@y ”中“@y ”表示寻址方式。

7、DSP 片内寄存器在C 语言中一般采用方式来访问,常常采用的方法是将DSP 寄存器地址的列表定义在。

8、TMS320VC5402型DSP 处理器的内核供电电压_______伏。

9、DSP 技术是利用专用或通用数字信号处理芯片,通过__运算的方法对信号进行处理。

10、C54x 的程序中,“.text ”段是_________段,主要包含_______________。

11、TMS320C54X 具有两个通用I/O 口,________用于输入外设的状态;________用于输出外设的控制信号。

二、选择题(每题2分,总共20分)1、下面对一些常用的伪指令说法正确的是:()A、.def 所定义的符号,是在当前模块中使用,在别的模块中定义的符号;B、.ref 所定义的符号,是当前模块中定义,并可在别的模块中使用的符号;C、.sect 命令定义的段是未初始化的段;D、.usect 命令定义的段是未初始化的段。

2、要使DSP 能够响应某个可屏蔽中断,下面的说法正确的是()A、需要把状态寄存器ST1的INTM 位置1,且中断屏蔽寄存器IMR 相应位置0B、需要把状态寄存器ST1的INTM 位置1,且中断屏蔽寄存器IMR 相应位置1C、需要把状态寄存器ST1的INTM 位置0,且中断屏蔽寄存器IMR 相应位置0D、需要把状态寄存器ST1的INTM 位置0,且中断屏蔽寄存器IMR 相应位置13、对于TMS320C54x 系列DSP 芯片,下列说法正确的是()A、8位DSPB、32位DSPC、定点型DSPD、浮点型DSP 4、执行指令PSHM AR5之前SP=03FEH ,则指令执行后SP=()A 、03FDHB 、03FFHC 、03FCHD 、0400H 5、TMS320C54X DSP 中有()个辅助寄存器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

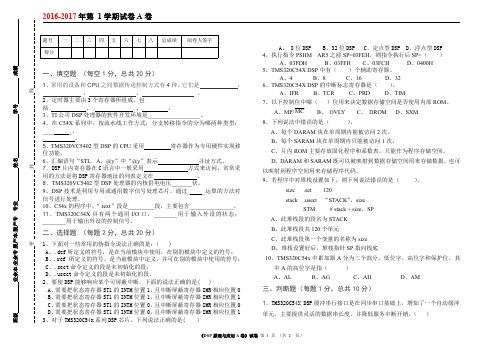

2012~2013一 DSP 技术及应用(A)信息科学技术学院 10级电子信息工程本科(答案写在答题纸上,写在试题纸上无效)一、单项选择题(每题2分,共20分)1.TMS320C54X DSP 的定时器可以实现_______、_______计数。

A 分频,加1B 分频,减1C 不分频,加1D 不分频,减1 2.TMS320C54X DSP HPI 口是_______位的_______口。

A 16,并行B 16,串行C 8,并行D 8,串行3.TMS320C54X DSP 具有_______位的并行乘法器,连接一个_______位的专用加法器。

A 17×17,40 B 17×17,32 C 16×16,40 D 16×16,32 4.TMS320C54X DSP 具有________个________位的累加器。

A 2,40 B 1,40 C 2,32 D 1,325.TMS320C54X DSP 的32个中断源分为14级,其中________级别最高。

A INTR B NMI C RS D INT0 6.当TMS320C54X DSP 复位时,中断向量为________。

A FF00HB FF80HC 0080HD 0000H7.外部存储器存取时间应小于_______的机器周期,否则需通过软件或硬件插入等待状态。

A 20% B 40% C 60% D 80% 8. TMS320C54X DSP 采用改进的哈佛结构,围绕______条_______位总线建立。

A 8,16 B 16,8 C 8,8 D 16,16 9.每个中断向量表文件中,都该包含________中断。

A 不可屏蔽B 复位C 定时器D 软件10.TMS320C54xDSP 多通道缓冲串口(MCBSP )发送和接收通道数最多可达________路。

A 128 B 64 C 32 D 16 二、填空题(每题2分,共20分)1.TMS320C54X 中定义可执行代码段的汇编指令为_______。

2. 根据如右图所示数据存储器和SP 的配置,执行相应程序段后,累加器A=________。

3.TMS320C54X 可编程定时器的定时周期 =(时 钟周期)*(定标器+1)*(________________ +1)。

4.累加器A=FF FFFF F001,对其进行规格化处理后, 累加器A 的数值为 ________5.TMS320C54X 为了能和慢速设备通信配备了一 个软件等待状态寄存器(SWWSR),用来设置等待状态,其最多可以插入_____个软件等待状态。

6. DSP 芯片采用流水线作业,使处理器的能力大大提高。

C54x 具有________级深度的指令流水线。

7. C54x 有多种数据寻址方式,指令LD *AR1+%, A 是________________寻址方式。

课程考试试题 学期 学年 拟题学院(系): 适 用 专 业:8. 存储器映像寄存器位于DSP的________存储空间。

9. 两个有符号小数相乘,乘积带有2个符号位。

可以通过设置状态位______,使结果左移1位,消除冗余符号位。

10. C54x通过外部总线接口来寻址片外存储器和I/O口。

其中_______信号用来控制数据传送的方向。

三、简答题(每题5分,共25分)1.简述冯•诺依曼结构、哈佛结构和改善型哈佛结构的特点?2.TMS320C54X DSP的串行接口有哪几种类型,它们之间有什么区别?3.简述TMS320C54X DSP中断的分类,并分别说明两种中断的范围。

4.请说明C54X DSP堆栈的使用方法,如何用汇编语言定义堆栈并加以简单说明?5.在软件开发过程中,将C语言源程序转换成可执行文件需要经过哪些主要步骤。

四、编程题(10分)按下述要求编写出TMS320C54X DSP汇编源程序。

计算z=x+y-w。

其中(x=10,y=24,w=31)要求:A源程序含必要的伪指令;B 加入适当的指令注释。

五、应用题(10分)对以下列表文件,假设链接时X重新定位在地址7100h,.text段重新定位到从地址7200h开始,那么Y的重定位值为7204h。

1、链接器利用两个重定位入口,如何对目标文件中的两次引用进行修正。

(5分)2、依次给出列表文件的各组成部分。

(5分)列表文件:1 0100 X .set 0100h ;给X赋值2 0000 .text3 0000 F073 B Y ;生成一个重定位入口0001 0004’4 0002 F020 LD #X,A ;生成一个重定位入口0003 0000!5 0004 F7E0 Y: RESET六、应用题(15分)用TMS320C5410 控制XF引脚以实现闪烁灯的实例如下,1、试分析该程序有哪几部分组成,各部分完成的主要功能?2、对标号○1-○5的指令段进行简要注释,3、编写该程序的链接命令文件。

;源程序清单.mmregs.def CodeStart.text CodeStart:SSBX XFCALL DelayRSBX XFCALL DelayB CodeStart Delay:STM #999,AR1 ;○1 LOOP1: STM #4999, AR2 ;○2 LOOP2: BANZ LOOP2,*AR2- ;○3 BANZ LOOP1,*AR1- ;○4RET ;○5.end2013 学年一学期DSP技术及应用(A))间干分)再(2(3(2目标模块组合成一个可执行的COFF文件。

(2分)四、编程题(10分)1、计算z=x+y-w。

其中(x=10,y=24,w=31)要求:A 源程序含必要的伪指令;B 加入适当的指令注释。

;程序清单:.title “1.asm”.mmregs.def CodeStart(2分).datax: .word 10 ;初始化变量y: .word 24w: .word 31z: .word 0(2分).textCodeStart:LD # x , DP ;装载数据指针DP (2分)SUM1:LD @x,A;将x地址的内容送AADD @y,A;将y地址的内容与A中x值相加SUB @w,A;将A中的内容与w 相减,得zSTL A,@z ;将A的的计算值存入z 地址中.end(4分)五、应用题(10分)对以下列表文件,假设链接时X重新定位在地址7100h,.text段重新定位到从地址7200h开始。

1、那么Y的重定位值为多少。

链接器利用两个重定位入口,如何对目标文件中的两次引用进行修正。

(5分)2、依次给出列表文件的各组成部分。

(5分)列表文件:1 0100 X .set 0100h ;给X赋值2 0000 .text3 0000 F073 B Y ;生成一个重定位入口0001 0004’4 0002 F020 LD #X,A ;生成一个重定位入口0003 0000!5 0004 F7E0 Y: RESET答:1、Y的重定位值为7204h。

(1分)F073 B Y变成F0730004’7204 (2分)F020 LD #X,A变成F0200000!7100 (2分)2、列表文件的组成部分依次为行号、段程序计数器、目标代码以及源程序。

(5分)六、应用题(15分)用TMS320C5410 控制XF引脚以实现闪烁灯的实例如下,1、试分析该程序有哪几部分组成,各部分完成的主要功能?2、对标号○1-○5的指令段进行简要注释,3、编写该程序的链接命令文件。

1.答:该程序由主程序、子程序两部分组成;(2分) 通过延时子程序控制XF的输出,以一定的时间间隔输出高或低电平。

(3分)2.程序段Delay:STM #999,AR1 ;○1循环次数1000LOOP1: STM #4999, AR2 ;○2循环次数5000LOOP2: BANZ LOOP2,*AR2- ;○3如果AR2不等于0,AR2减1,跳转到LOOP2;如果等于0,则循序执行下一条指令BANZ LOOP1,*AR1- ;○4如果AR1不等于0,AR1减1,跳转到LOOP1;如果等于0,则循序执行下一条指令RET ; ○5返回(5分).end3.链接配置文件/* TestXF.cmd */-e CodeStart /*程序入口,必须在程序中定义相应的标号*/ (1分)MEMORY{page 0:PRAM: org=0100h len=0F00h/*定义程序存贮区,起始0100H,长度0F00H*/}(2分) SECTIONS{.text:>PRAM page 0/*将.text段映射到page0的param区*/}(2分)。