利用Virtex-5器件实现QDR II SRAM接口

利用Virtex-5LXT应对串行背板接口设计挑战

利用Virtex-5LXT应对串行背板接口设计挑战采用串行技术进行高端系统设计已占很大比例。

在《EETimes》杂志最近开展的一次问卷调查中,有92%的受访者表示2006 年已开始设计串行I/O 系统,而在2005 年从事串行设计的仅占6?%。

串行技术在背板应用中的盛行,大大促进了这一比例的提高。

随着对系统吞吐量的要求日益提高,陈旧的并行背板技术已经被带宽更高、信号完整性更好、电磁辐射和功耗更低、PCB 设计更为简单的基于串行解串器(SerDes)技术的背板子系统所代替。

诸如XAUI 和千兆位以太网(GbE)等有助于简化设计、实现互操作性的标准串行协议的问世,进一步推动了串行技术的应用。

此外,PCI 工业计算机制造商协会(PICMG)制定的AdvancedTCA 和MicroTCA 等串行背板规格标准,也对串行技术的快速普及起到了重要作用。

串行背板技术具有极大的优越性,不但广泛用于通信系统、计算机系统、存储系统,还被应用到电视广播系统、医疗系统和工业/测试系统等。

设计“顽症”尽管串行技术的应用已日益普遍,但许多设计挑战依然横亘在设计人员面前。

背板子系统是整个系统的“心脏”,它必须能够在板卡间提供可靠的信号传输。

因此,在背板设计中,确保很高的信号完整性(SI)是首要任务。

另外,采用能够以极低误码率驱动背板的、基于SerDes 技术的适当芯片也至关重要。

在设计人员重复利用旧背板上的早期元件和设计规则的“早期系统升级”应用中,利用芯片元件来改善SI 尤为重要。

开发串行背板协议和交换接口(fabric interface)也是设计人员面临的一个挑战。

大多数背板设计都利用了采用专有协议的早期专用集成电路(ASIC),甚。

Virtex-5 FPGA教学实验系统手册

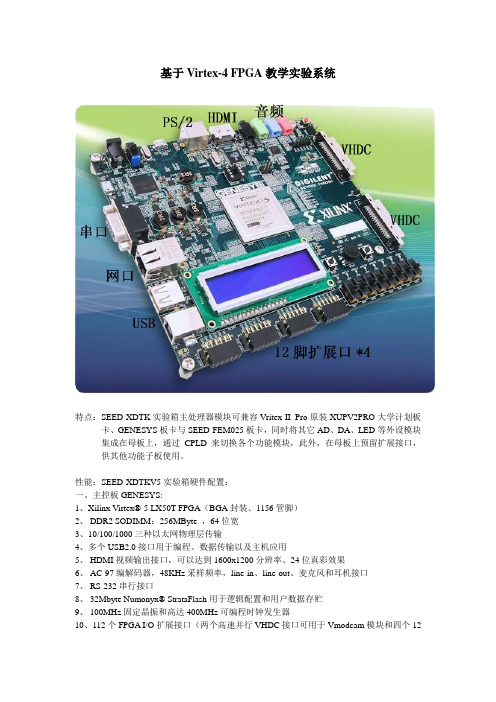

基于Virtex-4 FPGA教学实验系统特点:SEED-XDTK实验箱主处理器模块可兼容Vritex-II Pro原装XUPV2PRO大学计划板卡、GENESYS板卡与SEED-FEM025板卡,同时将其它AD、DA、LED等外设模块集成在母板上,通过CPLD来切换各个功能模块,此外,在母板上预留扩展接口,供其他功能子板使用。

性能:SEED-XDTKV5实验箱硬件配置:一、主控板GENESYS:1、Xilinx Virtex®-5 LX50T FPGA(BGA封装、1156管脚)2、DDR2 SODIMM:256MByte ,64位宽3、10/100/1000三种以太网物理层传输4、多个USB2.0接口用于编程、数据传输以及主机应用5、HDMI视频输出接口,可以达到1600x1200分辨率、24位真彩效果6、AC-97编解码器,48KHz采样频率,line-in、line-out、麦克风和耳机接口7、RS-232串行接口8、32Mbyte Numonyx® StrataFlash用于逻辑配置和用户数据存贮9、100MHz固定晶振和高达400MHz可编程时钟发生器10、112个FPGA I/O扩展接口(两个高速并行VHDC接口可用于Vmodcam模块和四个12管脚接头可用于扩展其他模块)11、GPIO包括8个LED指示灯、2个按键、两轴导航开关、8个滑动开关以及1个12、16x2字符LCD13、USB下载线、有机玻璃保护罩二、SEED-XDTK_Mboard母板:1、高速AD/ DA功能,串行AD/ DA功能2、LCD显示模块3、数码管显示模块4、点阵显示模块5、CAN总线模块6、USB模块7、RTC+EEPROM模块8、蜂鸣器9、键盘模块三、7寸液晶;四、标准CCD摄像头。

性能:SEED-XDKTV5实验箱可提供近30个教学实验:一、基础实验1. LED实验2. LED点阵实验3. 键盘实验4. 并行AD、DA实验5. 串行AD、DA实验6. LCD显示实验7. RTC读取实验8. USB传输实验9. 音频输入输出实验10. 以太网接口实验11. 视频采集输出实验二、FPGA实验(Xilinx XUP ISE课程)1. ISE8.2使用流程实验2. Architecture Wizard与PACE实验3. 全局时序约束实验4. 综合技术实验5. IP核生成工具使用实验6. ISE8.2 环境下Chipscope 使用实验三、SOPC基础实验(Xilinx XUP EDK课程)1. Basic Hardware 设计实验2. 添加IP核实验3. Custom IP Core设计实验4. 建立Basic Software 应用程序实验5. SDK使用实验6. HW/SW System调试实验四、SYSTEM GENERATOR(Xilinx XUP DSP课程)1. 使用System Generator创建12x8MAC2. 使用HDL Co-Simulation验证MAC FIR Filter3. 设计一个FIR Filter4. 深入了解量化和溢出参数5. 控制系统6. 设计一个MAC FIR应用领域:1、FPGA专业实验室建设2、SOPC教学研究3、利用FPGA实现图象、语音处理、网络传输4、计算机相关专业教学5、软件无线电专业。

业界最快QDR SRAM(静态随机存取

业界最快QDR SRAM(静态随机存取

包括赛普拉斯半导体公司和瑞萨电子公司在内的QDR联盟日前宣布推出业界最快的四倍数据率(QDR) SRAM(静态随机存取存储器)。

这些新型存储器将被命名为QDRII+ Xtreme并将以高达633兆赫兹(MHz)的时钟频率允许。

这些器件将与现有的QDR II+器件在管脚、尺寸和功能方面兼容,从而使网络交换机、路由器及聚合平台制造商不必修改电路板设计,只需提高系统内时钟速度即可大幅改善产品性能。

新型QDR II+ Xtreme SRAM将采用x18 o或x36字宽,4或2次突发访问。

4次突发器件的随机存取速率(RTR)可达每秒6.33亿次,工作时钟频

率为633MHz,这是QDR SRAM器件现有的最高速度。

2次突发器件以450MHz的频率工作,RTR可达每秒9亿次随机传输,这比以同样频率运行的上一代4次突发器件的RTR提高了一倍。

随机存取速率的定义是每秒进行的完全随机存取次数,是重要的存储器指标,用以衡量增加的线或交换速度。

赛普拉斯存储器事业部执行副总裁Dana Nazarian 说:QDR II+ Xtreme产品无需重新进行系统设计即可大幅提升性能,这对于期望赶上流量要求步伐的网络设备制造商非常有吸引力。

QDR联盟正积极制定一系列后续解决方案,以支持网络工业界对存储器不断提高的要求。

QDR II布线指南

在VTT与地间连接退耦电容。

在其他VTT引脚处使用0.1uF电容。

可以使用Altera电源分配网络设计工具(Altera Power Distribution Network(PDN)Design tool)验证容性退耦。

电源

地,1.5V/1.8V作为电源层。

存储器的VCCIO在单个分隔信号层中保持至少20mil(0.020英寸或0.508mm)间隔。

PCB布局指南

表格7-4概括了QDR II和QDR II SRAM常用走线布局指南。

以下布线指南包括若干+/-基于长度的规则。如果你不能模拟PCB实施的实际延时特性,这些基于长度的指南可以用来得到一阶时序的近似值(first order timing approximations),但不包括串扰幅度。

互补时钟在P和N信号之间应保持长度匹配,±2ps延时或近似±10mils(0.254mm)。

VTT独立走线或以250mil(6.35mm)线宽电源走线。

所有晶振和PLL电源独立走线或以100mil(2.54mm)线宽电源走线。

一般走线

所有具体延时匹配要求包括PCB走线延时、不同层之间的传输、速度差异以及串扰。为了减少PCB层传送差异,Altera推荐来自于同一网络的信号应在同一层走线;如果同一网络的信号必须在不同层走线,应保持相同的阻抗特性,而且必须模拟出PCB走线最坏状况容限,用以确定实际传输延时差别。典型的later to later走线延时差异是15ps/inch。

表7-4.QDR II和QDR II+SRAM布局指南(第2章第2部分)

参数

指南

时钟走线

时钟线在内层电路板上with outer-layer走线长度保持低于150ps延时(近似500mils,12.7mm)。

Virtex-5 系列概述

DS100 (v4.4) 2008 年 9 月 23 日

/cn

先期产品技术说明

1

Virtex-5 系列概述

R

表 1: Virtex-5 FPGA 系列器件

器件

可配置逻辑块 (CLB)

Block RAM 模块

DSP48E

阵列 (行 x 列)

Virtex-5 Slice(1)

2

/cn

DS100 (v4.4) 2008 年 9 月 23 日

先期产品技术说明

XC5VLX85

120 x 54 12,960 840

48 192 96 3,456 6 不适用

XC5VLX110 160 x 54 17,280 1,120

64 256 128 4,608 6 不适用

XC5VLX155 160 x 76 24,320 1,640 128 384 192 6,912 6 不适用

1

不适用

XC5VLX30T 80 x 30 4,800

320

32

72 36 1,296 2 不适用

XC5VLX50T 120 x 30 7,200

480

48 120 60 2,160 6 不适用

XC5VLX85T 120 x 54 12,960 840

48 216 108 3,888 6 不适用

XC5VLX110T 160 x 54 17,280 1,120

64 296 148 5,328 6 不适用

XC5VLX155T 160 x 76 24,320 1,640 128 424 212 7,632 6 不适用

XC5VLX220T 160 x 108 34,560 2,280 128 424 212 7,632 6 不适用

面对高速网络存储,在QDR SRAM和RLDRAM之间应谨慎选择

当今的高速网络应用需要高带宽和高密度存储器解决方案。

例如,标准的网络线路卡需要用于各种操作的存储器,包括信息包缓冲器、查找表和队列管理等诸多功能。

为了确保存储器带宽不会成为应用吞吐量的瓶颈,选择正确的存储器解决方案是至关重要的。

本文将介绍适合于网络应用的存储器。

具体来说,就是四倍数据速率静态RAM(QDR SRAM)和低延迟动态RAM(RLDARM),并就其最为适合的应用进行了比较。

网络SRAM的发展标准的同步SRAM(最早的主流同步SRAM)是高速缓冲存储器应用的理想选择。

然而,尽管其应用十分广泛,但对于规定了一个平衡读/写模式的网络应用而言,他们并不是合适之选。

因为写操作后紧跟着的读操作将导致在数据总线上出现争用状态。

为了解决总线争用问题,人们研发了“无总线延迟”(NoBL)、也称“零总线转向”(ZBT)型SRAM。

这些SRAM在外围电路中包含了数据寄存器,用于实现流水线型的读和写操作,由此消除“等待”周期并实现峰值总线利用率。

然而,随着线路速率达到每秒几十千兆位(Gbps),和速度、带宽和接口相关的各种瓶颈问题必须得到解决。

许多不但需要较高的工作速度、而且还需要对存储器进行同时读写操作的应用已涌现出来。

虽然最初很适合于网络架构,但是,NoBL SRAM却无法满足其性能需要的不断攀升。

因此,人们研发出了最新一代的网络存储器——QDR/DDR系列SRAM,旨在满足如今网络应用的速度、密度和带宽需要。

作为最新一代的同步SRAM,QDR和QDR-II SRAM是由QDR协会(赛普拉斯、瑞萨、IDT、NEC和三星)的成员公司研发的。

该网络SRAM系列和双倍数据速率(DDR)和DDR-II SRAM一起提供了面向任何网络系统的完整存储器解决方案。

QDR和QDR-II SRAM的速度高达300MHz以上,密度为9Mb至72Mb(今后有望扩展至高达288Mb以上)。

QDR和QDR-II SRAM具备用于读和写操作的单独端口,因而消除了总线争用。

Virtex-5 FPGA 系列简介

封面专题 2007年1月• 针对嵌入式处理和超高速串行 I/O 进行优化的 FXT 平台 相对于Virtex -4 系列,Virtex -5 系列中配置最高的型号的平均速度提高了30%,容量提高了65%,动态功耗降低了35%,芯片面积缩小了45%,结果实现了达到每项功能的最低成本。

高性能和高密度ExpressFabric ™技术实现了逻辑和局部互连布线。

它将查找表 (LUT)、六个独立的输入和一个新的对角互连结构结合在一起,如图1所示。

相对于 Virtex -4 架构而言,ExpressFabric 技术利用更少的 LUT 层次以及更少的串行连接(面向相邻构件)Virtex -5 系列结合了65纳米工艺技术的固有优势和创新设计,该创新设计立足于我们对产品应用的更深入的理解。

本文中,我将对Virtex -5器件进行概述,解释其基础技术,同时简短回顾世界领先的FPGA 架构设计背后的故事。

工艺技术和架构创新 Virtex -5 FPGA 基于65纳米的三栅极氧化层技术,使用先进的硅组合模块(ASMBL ™) 架构并且实现了更高级别的系统集成。

这个全新的产品系列提供了一个高级平台,可以满足用户对于建造具有更高性能、更高密度、更低功耗和更低成本的可编程系统日益增长的需求。

满足上述一个或者两个需求也许比较容易,但是挑战在于我们要同时满足所有这些需求。

我们通过将先进的IC 工艺、创新的架构以及电路设计相结合,成功地应对了这些挑战。

首先在 Virtex -4 系列中引入的成熟的 ASMBL 芯片版图架构,可以提供所要求器件资源(逻辑、存储器、算术、I/O和IP)的最优组合,从而为以下四个新平台创造了最佳条件:• 针对高性能逻辑进行优化的 LX 平台 • 针对具有低功耗串行 I/O 的高性能逻辑进行优化的 LXT 平台 • 针对具有低功耗串行 I/O 的高性能算术和存储密集型 DSP 进行优化的SXT 平台我们选择了一套客户设计方案,然后使用 ISE ™8.1i 软件实现该方案。

Virtex-5 FPGA 六输入 LUT 架构的优势

白皮书: Virtex-5 FPGAVirtex-5 FPGA 六输入 LUT 架构的优势作者: Andrew Percey新型 Virtex™-5 架构基于具有双 LUT 功能的真正六输入 LUT,与同类架构相比,在资源占用率方面具有显著优势。

本白皮书详述这些优势,重点在 Xilinx 的65nm 高端 FPGA 器件 (Virtex-5FPGA) 与 Altera(Stratix III FPGA) 之间进行比较。

© 2007 Xilinx, Inc. All rights reserved.XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.架构介绍图1 所示为 Xilinx Virtex-5 FPGA 的基本架构:具有相关逻辑的六输入 LUT。

图2 所示为 Altera Stratix III FPGA 的基本架构:自适应逻辑模块(即 ALM)。

图 1:Virtex-5 FPGA 六输入 LUT 架构图 2:Stratix III ALM 架构Xilinx 六输入 LUT 是共有 64位逻辑编程空间和六个独立输入的查找表,能够实现任意六输入功能和一两个较小功能的多种组合。

该六输入 LUT 还包括相关的进位逻辑、MUX 和触发器。

该六输入 LUT 的某些逻辑部分也可用作 64位 RAM 或 32位移位寄存器。

有关更多信息,请见 UG190:《Virtex-5 用户指南》。

Altera ALM 包括两个自适应 LUT (ALUT),共有 64位逻辑编程空间和八个共用输入,也能实现任意六输入功能和一两个较小功能的多种组合。

基于Virtex5的PCI-Express总线接口设计

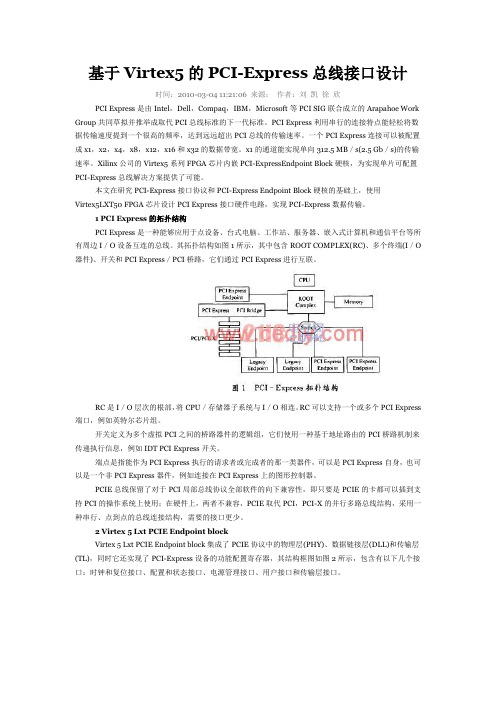

基于Virtex5的PCI-Express总线接口设计时间:2010-03-04 11:21:06 来源:作者:刘凯徐欣PCI Express是由Intel,Dell,Compaq,IBM,Microsoft等PCI SIG联合成立的Arapahoe Work Group共同草拟并推举成取代PCI总线标准的下一代标准。

PCI Express利用串行的连接特点能轻松将数据传输速度提到一个很高的频率,达到远远超出PCI总线的传输速率。

一个PCI Express连接可以被配置成x1,x2,x4,x8,x12,x16和x32的数据带宽。

x1的通道能实现单向312.5 MB/s(2.5 Gb/s)的传输速率。

Xilinx公司的Virtex5系列FPGA芯片内嵌PCI-ExpressEndpoint Block硬核,为实现单片可配置PCI-Express总线解决方案提供了可能。

本文在研究PCI-Express接口协议和PCI-Express Endpoint Block硬核的基础上,使用Virtex5LXT50 FPGA芯片设计PCI Express接口硬件电路,实现PCI-Express数据传输。

1 PCI Express的拓扑结构PCI Express是一种能够应用于点设备、台式电脑、工作站、服务器、嵌入式计算机和通信平台等所有周边I/O设备互连的总线。

其拓扑结构如图1所示,其中包含ROOT COMPLEX(RC)、多个终端(I/O 器件)、开关和PCI Express/PCI桥路,它们通过PCI Express进行互联。

RC是I/O层次的根部,将CPU/存储器子系统与I/O相连。

RC可以支持一个或多个PCI Express 端口,例如英特尔芯片组。

开关定义为多个虚拟PCI之间的桥路器件的逻辑组,它们使用一种基于地址路由的PCI桥路机制来传递执行信息,例如IDT PCI Express开关。

端点是指能作为PCI Express执行的请求者或完成者的那一类器件,可以是PCI Express自身,也可以是一个非PCI Express器件,例如连接在PCI Express上的图形控制器。

【配置知识】Virtex-5 FPGA 的配置

【配置知识】Virtex-5 FPGA的配置配置方案Xilinx 为终端用户提供了配置Virtex-5 FPGA 所需的灵活性。

Virtex-5 FPGA 支持以下方案:串行最简单的配置方案,串行吞吐量。

主串行Xilinx FPGA 驱动Xilinx PROM CLK,因为Xilinx PROM 为Xilinx FPGA 提供了串行(x1)配置数据。

从串行Xilinx PROM 的内部振荡器驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xilinx FPGA 提供了串行(x1)配置数据。

从串行外部时钟驱动Xilinx PROM CLK,Xilinx PROM 驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xil inx FPGA 提供了串行(x1)配置数据。

返回页首从串行外部时钟驱动Xilinx FPGA CLK 和Xilinx PROM CLK,因为Xilinx PROM 为Xilinx FPGA 提供了串行(x1)配置数据。

主SPIVirtex-5 FPGA 驱动SPI PROM 时钟,因为SPI PROM 为Virtex-5 FPGA 提供了串行(x1)配置数据。

并行并行配置,可以实现最快速的吞吐量主并(Master-SelectMap)Xilinx FPGA 驱动Xilinx PROM CLK,因为Xilinx PROM 为Xilinx FPGA 提供了字节宽的(x8)配置数据。

返回页首从并(slave-SelectMAP)Xilinx PROM 的内部振荡器驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xilinx FPGA 提供了字节宽的(x8)配置数据。

从并(slave-SelectMAP)外部时钟驱动Xilinx PROM CLK,Xilinx PROM 驱动Xilinx FPGA CCLK,因为Xilinx PROM 为Xil inx FPGA 提供了字节宽的(x8)配置数据。

XILINX_VIRTEX-5

© 2006–2007 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, the Brand Window, and other designated brands included herein are trademarks of Xilinx, Inc. All other trade-marks are the property of their respective owners. PowerPC is a trademark of IBM, Inc. All specifications are subject to change without notice.Virtex-5 Electrical CharacteristicsVirtex™-5 FPGAs are available in -3, -2, -1 speed grades, with -3 having the highest performance.Virtex-5 D C and AC characteristics are specified for both commercial and industrial grades. Except the operating temperature range or unless otherwise noted, all the D C and AC electrical parameters are the same for a particular speed grade (that is, the timing characteristics of a -1 speed grade industrial device are the same as for a -1 speed grade commercial device). However, only selected speed grades and/or devices might be available in the industrial range.All supply voltage and junction temperature specifications are representative of worst-case conditions. The parame-ters included are common to popular designs and typical applications.This Virtex-5 data sheet, part of an overall set of documen-tation on the Virtex-5 family of FPGAs, is available on the Xilinx website:•Virtex-5 Family Overview •Virtex-5 User Guide•Virtex-5 Configuration Guide•Virtex-5 XtremeDSP™ Design Considerations •Virtex-5 Packaging and Pinout Specification•Virtex-5 RocketIO™ GTP Transceiver User Guide •Virtex-5 Tri-mode Ethernet MAC User Guide•Virtex-5 Integrated Endpoint Block User Guide for PCI Express® Designs•Virtex-5 System Monitor User Guide •Virtex-5 PCB Designer’s GuideAll specifications are subject to change without notice.Virtex-5 DC CharacteristicsVirtex-5 Data Sheet:DC and Switching CharacteristicsDS202 (v3.6) November 5, 2007Advance Product SpecificationTable 1: Absolute Maximum RatingsSymbolDescriptionUnitsV CCINT Internal supply voltage relative to GND –0.5 to 1.1V V CCAUX Auxiliary supply voltage relative to GND –0.5 to 3.0V V CCO Output drivers supply voltage relative to GND –0.5 to 3.75V V BATT Key memory battery backup supply –0.5 to 4.05V V REF Input reference voltage–0.5 to 3.75V V IN (3)3.3V I/O input voltage relative to GND (4) (user and dedicated I/Os)–0.75 to4.05V 2.5V or below I/O input voltage relative to GND (user and dedicated I/Os)–0.75 to V CCO + 0.5V V TSVoltage applied to 3-state 3.3V output (4) (user and dedicated I/Os)–0.75 to 4.05V Voltage applied to 3-state 2.5V or below output (user and dedicated I/Os)–0.75 to V CCO + 0.5V T STG Storage temperature (ambient)–65 to 150°C T SOL Maximum soldering temperature (2)+220°C T JMaximum junction temperature (2)+125°CNotes:1.Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, andfunctional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.2.For soldering guidelines and thermal considerations, see UG195: Virtex-5 Packaging and Pinout Specification on the Xilinx website.3. 3.3V I/O absolute maximum limit applied to DC and AC signals.4.For 3.3V I/O operation, refer to UG190: Virtex-5 User Guide, Chapter 6, 3.3V I/O Design Guidelines .Table 2: Recommended Operating ConditionsSymbol Description Temperature Range Min Max UnitsV CCINT Internal supply voltage relative to GND, T J = 0°C to +85°C Commercial0.95 1.05V Internal supply voltage relative to GND, T J = –40°C to +100°C Industrial0.95 1.05VV CCAUX(1)Auxiliary supply voltage relative to GND, T J = 0°C to +85°C Commercial 2.375 2.625V Auxiliary supply voltage relative to GND, T J = –40°C to +100°C Industrial 2.375 2.625VV CCO(2,4,5)Supply voltage relative to GND, T J = 0°C to +85°C Commercial 1.14 3.45V Supply voltage relative to GND, T J = –40°C to +100°C Industrial 1.14 3.45VV IN 3.3V supply voltage relative to GND, T J = 0°C to +85°C Commercial GND – 0.20 3.45V 3.3V supply voltage relative to GND, T J = –40°C to +100°C Industrial GND – 0.20 3.45V 2.5V and below supply voltage relative to GND,T J = 0°C to +85°CCommercial GND – 0.20V CCO+ 0.2V2.5V and below supply voltage relative to GND,T J = –40°C to +100°CIndustrial GND – 0.20V CCO+ 0.2VI IN Maximum current through any pin in a powered or unpoweredbank when forward biasing the clamp diode.Commercial10mAIndustrial10mAV BA TT(3)Battery voltage relative to GND, T J = 0°C to +85°C Commercial 1.0 3.6V Battery voltage relative to GND, T J = –40°C to +100°C Industrial 1.0 3.6VNotes:1.Recommended maximum voltage drop for V CCAUX is 10 mV/ms.2.Configuration data is retained even if V CCO drops to 0V.3.V BATT is required only when using bitstream encryption. If battery is not used, connect V BATT to either ground or V CCAUX.4.Includes V CCO of 1.2V, 1.5V, 1.8V, 2.5V, and 3.3V.5.The configuration supply voltage V CC_CONFIG is also known as V CCO_0Table 3: DC Characteristics Over Recommended Operating ConditionsSymbol Description Data Rate Min Typ Max Units V DRINT Data retention V CCINT voltage (below which configuration data might be lost)0.75V V DRI Data retention V CCAUX voltage (below which configuration data might be lost) 2.0VI REF V REF leakage current per pin10µAI L Input or output leakage current per pin (sample-tested)10µAC IN Input capacitance (sample-tested)8pFI RPU(1)Pad pull-up (when selected) @ V IN = 0V, V CCO = 3.3V20150µAPad pull-up (when selected) @ V IN = 0V, V CCO = 2.5V1090µAPad pull-up (when selected) @ V IN = 0V, V CCO = 1.8V545µAPad pull-up (when selected) @ V IN = 0V, V CCO = 1.5V330µAPad pull-up (when selected) @ V IN = 0V, V CCO = 1.2V215µAI RPD(1)Pad pull-down (when selected) @ V IN = 2.5V 5110µA I BATT(2)Battery supply current150nAn Temperature diode ideality factor 1.0002n r Series resistance 5.0ΩNotes:1.Typical values are specified at nominal voltage, 25°C.2.Maximum value specified for worst case process at 25°C.Important NoteTypical values for queiscent supply current are now specified at nominal voltage, 85ºC junction temperatures (T j). Xilinx recommends analyzing static power consumption at T j = 85ºC because the majority of designs operate near the high end of the commercial temperature range. D ata sheets for older products (e.g., Virtex-4 devices) still specify typical quiescent supply current at T j = 25ºC. Queiscent supply current is specified by speed grade for Virtex-5 devices. Use the XPOWER™ Estimator (XPE) spreadsheet tool (download at /power) to calculate static power consumption for conditions other than those specified in Table 4.Table 4: Typical Quiescent Supply CurrentSymbol Description DeviceSpeed and Temperature Grade Units -3 (C)-2 (C & I)-1 (C & I)I CCINTQ Quiescent V CCINT supply current XC5VLX30480480300mAXC5VLX30T507507317mAXC5VLX50651651449mAXC5VLX50T689689475mAXC5VLX8510721072883mAXC5VLX85T11151115866mAXC5VLX110139113911109mAXC5VLX110T144814481154mAXC5VLX220N/A27832278mAXC5VLX220T N/A28442328mAXC5VLX330N/A41933432mAXC5VLX330T N/A42673492mAXC5VSX35T720720554mAXC5VSX50T10921092840mAXC5VSX95T N/A19241475mA I CCOQ Quiescent V CCO supply current XC5VLX30 1.5 1.5 1.5mAXC5VLX30T 1.5 1.5 1.5mAXC5VLX50222mAXC5VLX50T222mAXC5VLX85333mAXC5VLX85T333mAXC5VLX110444mAXC5VLX110T444mAXC5VLX220N/A88mAXC5VLX220T N/A88mAXC5VLX330N/A1212mAXC5VLX330T N/A1212mAXC5VSX35T 1.5 1.5 1.5mAXC5VSX50T222mAXC5VSX95T N/A44mAPower-On Power Supply RequirementsXilinx FPGAs require a certain amount of supply current during power-on to insure proper device initialization. The actual current consumed depends on the power-on ramp rate of the power supply.The power supplies can be can be turned on in any sequence, though the specifications shown in Table 5 are for the recommended power-on sequence of V CCINT , V CCAUX , and V CCO . Xilinx does not specify the current for other power-on sequences.Table 5 shows the minimum current required by Virtex-5devices for proper power-on and configuration.If the current minimums shown in Table 5 are met, the device powers on properly after all three supplies have passed through their power-on reset threshold voltages.The FPGA must be configured after V CCINT is applied.Once initialized and configured, use the XPOWER tools to estimate current drain on these supplies.I CCAUXQQuiescent V CCAUX supply currentXC5VLX30383838mA XC5VLX30T 434343mA XC5VLX50575757mA XC5VLX50T 626262mA XC5VLX85939393mA XC5VLX85T 989898mA XC5VLX110125125125mA XC5VLX110T 130130130mA XC5VLX220N/A 229229mA XC5VLX220T N/A 236236mA XC5VLX330N/A 345345mA XC5VLX330T N/A 353353mA XC5VSX35T 494949mA XC5VSX50T 747474mA XC5VSX95TN/A131131mANotes:1.Typical values are specified at nominal voltage, 85°C junction temperatures (T j ). Industrial(I) grade devices have the same typical values ascommercial (C) grade devices at 85°C, but higher values at 100°C. Use the XPE tool to calculate 100°C values.2.Typical values are for blank configured devices with no output current loads, no active input pull-up resistors, all I/O pins are 3-state and floating.3.If DCI or differential signaling is used, more accurate quiescent current estimates can be obtained by using the XPOWER Estimator (XPE) orXPOWER Analyzer (XPA) tools.Table 4: Typical Quiescent Supply Current (Continued)SymbolDescriptionDeviceSpeed and Temperature GradeUnits-3 (C)-2 (C & I)-1 (C & I)Table 5: Power-On Current for Virtex-5 DevicesDevice I CCINTMINI CCAUXMINI CCOMINUnits Typ (1)MaxTyp (1)MaxTyp (1)MaxXC5VLX302357650mA XC5VLX30T 2468650mA XC5VLX5032011450mA XC5VLX50T 33612450mA XC5VLX85492186100mA XC5VLX85T515196100mASelectIO™ DC Input and Output LevelsValues for V IL and V IH are recommended input voltages. Values for I OL and I OH are guaranteed over the recom-mended operating conditions at the V OL and V OH test points. Only selected standards are tested. These are cho-sen to ensure that all standards meet their specifications. The selected standards are tested at a minimum V CCO with the respective V OL and V OH voltage levels shown. Other standards are sample tested.XC5VLX110623250100mA XC5VLX110T 651260100mA XC5VLX2201023458150mA XC5VLX220T 1056472150mA XC5VLX3301470690150mA XC5VLX330T 1509706150mA XC5VSX35T 3079850mA XC5VSX50T 47214850mA XC5VSX95T804262100mANotes:1.Typical values are specified at nominal voltage, 25°C.Table 5: Power-On Current for Virtex-5 Devices (Continued)Device I CCINTMINI CCAUXMINI CCOMINUnits Typ (1)MaxTyp (1)MaxTyp (1)MaxTable 6: Power Supply Ramp TimeSymbol DescriptionRamp Time Units V CCINT Internal supply voltage relative to GND 0.20 to 50.0ms V CCO Output drivers supply voltage relative to GND 0.20 to 50.0ms V CCAUXAuxiliary supply voltage relative to GND0.20 to 50.0msTable 7: SelectIO DC Input and Output Levels I/O StandardV ILV IHV OLV OH I OL I OH V, MinV, MaxV, MinV, MaxV, MaxV, MinmAmALVTTL –0.30.8 2.0 3.450.4 2.4Note(3)Note(3)LVCMOS33, LVDCI33–0.30.8 2.0 3.450.4V CCO – 0.4Note(3)Note(3)LVCMOS25, LVDCI25–0.30.7 1.7V CCO + 0.30.4V CCO – 0.4Note(3)Note(3)LVCMOS18, LVDCI18–0.335% V CCO 65% V CCO V CCO + 0.30.45V CCO – 0.45Note(4)Note(4)LVCMOS15, LVDCI15–0.335% V CCO 65% V CCO V CCO + 0.325% V CCO 75% V CCO Note(4)Note(4)LVCMOS12–0.335% V CCO 65% V CCO V CCO + 0.325% V CCO 75% V CCO Note(6)Note(6)PCI33_3(5)–0.230% V CCO 50% V CCO V CCO 10% V CCO 90% V CCO Note(5)Note(5)PCI66_3(5)–0.230% V CCO 50% V CCO V CCO 10% V CCO 90% V CCO Note(5)Note(5)PCI-X (5)–0.235% V CCO50% V CCOV CCO10% V CCO90% V CCONote(5)Note(5)GTLP –0.3V REF – 0.1V REF + 0.1–0.6N/A 36N/A GTL –0.3V REF – 0.05V REF + 0.05–0.4N/A 32N/A HSTL I_12–0.3V REF – 0.1V REF + 0.1V CCO + 0.325% V CCO75% V CCO 6.3 6.3HSTL I (2)–0.3V REF – 0.1V REF + 0.1V CCO + 0.30.4V CCO – 0.48–8HSTL II (2)–0.3V REF – 0.1V REF + 0.1V CCO + 0.30.4V CCO – 0.416–16HSTL III (2)–0.3V REF – 0.1V REF + 0.1V CCO + 0.30.4V CCO – 0.424–8HSTL IV (2)–0.3V REF – 0.1V REF + 0.1V CCO + 0.30.4V CCO – 0.448–8DIFF HSTL I (2)–0.350% V CCO – 0.150% V CCO + 0.1V CCO + 0.3––––DIFF HSTL II (2)–0.350% V CCO – 0.150% V CCO + 0.1V CCO + 0.3––––SSTL2 I –0.3V REF – 0.15V REF + 0.15V CCO + 0.3V TT – 0.61V TT + 0.618.1–8.1SSTL2 II –0.3V REF – 0.15V REF + 0.15V CCO + 0.3V TT – 0.81V TT + 0.8116.2–16.2DIFF SSTL2 I –0.350% V CCO – 0.1550% V CCO + 0.15V CCO + 0.3––––DIFF SSTL2 II –0.350% V CCO – 0.1550% V CCO + 0.15V CCO + 0.3––––SSTL18 I –0.3V REF – 0.125V REF + 0.125V CCO + 0.3V TT – 0.47V TT + 0.47 6.7–6.7SSTL18 II –0.3V REF – 0.125V REF + 0.125V CCO + 0.3V TT – 0.60V TT + 0.6013.4–13.4DIFF SSTL18 I –0.350% V CCO – 0.12550% V CCO + 0.125V CCO + 0.3––––DIFF SSTL18 II–0.350% V CCO – 0.12550% V CCO + 0.125V CCO + 0.3––––Notes:1.Tested according to relevant specifications.2.Applies to both 1.5V and 1.8V HSTL.ing drive strengths of 2, 4, 6, 8, 12, 16, or 24 mA.ing drive strengths of 2, 4, 6, 8, 12, or 16 mA.5.For more information on PCI33_3, PCI66_3, and PCI-X, refer to refer to UG190: Virtex-5 User Guide, Chapter 6, 3.3V I/O Design Guidelines .6.Supported drive strengths of 2, 4, 6, or 8 mA.Table 7: SelectIO DC Input and Output Levels (Continued)I/O StandardV ILV IHV OLV OH I OL I OH V, MinV, MaxV, MinV, MaxV, MaxV, MinmAmAHT DC Specifications (HT_25)LVDS DC Specifications (LVDS_25)Extended LVDS DC Specifications (LVDSEXT_25)Table 8: HT DC Specifications Symbol DC ParameterConditionsMin Typ Max Units V CCO Supply Voltage2.38 2.5 2.63V V OD Differential Output Voltage R T = 100 Ω across Q and Q signals495600715mV Δ V OD Change in V OD Magnitude –1515mV V OCM Output Common Mode Voltage R T = 100 Ω across Q and Q signals 495600715mV Δ V OCM Change in V OCM Magnitude –1515mV V ID Input Differential Voltage 2006001000mV Δ V ID Change in V ID Magnitude –1515mV V ICM Input Common Mode Voltage 440600780mV Δ V ICMChange in V ICM Magnitude–1515mVTable 9: LVDS DC Specifications Symbol DC ParameterConditionsMin Typ Max Units V CCO Supply Voltage2.382.52.63V V OH Output High Voltage for Q and Q R T = 100 Ω across Q and Q signals 1.675V V OL Output Low Voltage for Q and QR T = 100 Ω across Q and Q signals0.825V V ODIFF Differential Output Voltage (Q – Q), Q = High (Q – Q), Q = High R T = 100 Ω across Q and Q signals 247350600mV V OCM Output Common-Mode Voltage R T = 100 Ω across Q and Q signals1.125 1.250 1.375V V IDIFF Differential Input Voltage (Q – Q), Q = High (Q – Q), Q = High 100350600mV V ICMInput Common-Mode Voltage0.31.22.2VTa ble 10: Extended LVDS DC Specifications Symbol DC ParameterConditionsMin Typ Max Units V CCO Supply Voltage2.382.5 2.63V V OH Output High Voltage for Q and Q R T = 100 Ω across Q and Q signals – 1.785V V OL Output Low Voltage for Q and QR T = 100 Ω across Q and Q signals0.715––V V ODIFF Differential Output Voltage (Q – Q), Q = High (Q – Q), Q = High R T = 100 Ω across Q and Q signals 350–820mV V OCM Output Common-Mode Voltage R T = 100 Ω across Q and Q signals 1.125 1.250 1.375V V IDIFF Differential Input Voltage (Q – Q), Q = High (Q – Q), Q = High Common-mode input voltage = 1.25V 100–1000mV V ICMInput Common-Mode VoltageDifferential input voltage = ±350 mV0.31.22.2VLVPECL DC Specifications (LVPECL_25)These values are valid when driving a 100Ω differential load only, i.e., a 100Ω resistor between the two receiver pins. The V OH levels are 200 mV below standard LVPECL levels and are compatible with devices tolerant of lower com-mon-mode ranges. Table 11 summarizes the D C output specifications of LVPECL. For more information on using LVPECL, see UG190: Virtex-5 User Guide, Cha pter 6, SelectIO Resources.Ta ble 11: LVPECL DC SpecificationsSymbol DC Parameter Min Typ Max Units V OH Output High Voltage V CC – 1.025 1.545V CC – 0.88V V OL Output Low Voltage V CC – 1.810.795V CC – 1.62V V ICM Input Common-Mode Voltage0.6 2.2V V IDIFF Differential Input Voltage(1,2)0.100 1.5V Notes:1.Recommended input maximum voltage not to exceed V CCAUX + 0.2V.2.Recommended input minimum voltage not to go below –0.5V.RocketIO GTP Transceiver SpecificationsRocketIO GTP Transceiver DC CharacteristicsTa ble 12: Absolute Maximum RatingsSymbol Description Units MGTAVCCPLL Analog supply voltage for the GTP_DUAL shared PLL relative to GND–0.5 to 1.32V MGTAVTTTX Analog supply voltage for the GTP_DUAL transmitters relative to GND–0.5 to 1.32V MGT AVTTRX Analog supply voltage for the GTP_DUAL receivers relative to GND–0.5 to 1.32V MGTAVCC Analog supply voltage for the GTP_DUAL common circuits relative to GND–0.5 to 1.32V–0.5 to 1.32V MGT AVTTRXC Analog supply voltage for the resistor calibration circuit of the GTP_DUALcolumnNotes:1.Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, andfunctional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability.Ta ble 13: Recommended Operating Conditions(1)(2)Symbol Description Min Max Units MGT AVCCPLL(1)Analog supply voltage for the GTP_DUAL shared PLL relative to GND 1.14 1.26V MGT AVTTTX(1)Analog supply voltage for the GTP_DUAL transmitters relative to GND 1.14 1.26V MGTAVTTRX(1)Analog supply voltage for the GTP_DUAL receivers relative to GND 1.14 1.26V MGT AVCC(1)Analog supply voltage for the GTP_DUAL common circuits relative to GND0.95 1.05V1.14 1.26V MGTAVTTRXC(1)Analog supply voltage for the resistor calibration circuit of the GTP_DUALcolumnNotes:1.Each voltage listed requires the filter circuit described in UG196: Virtex-5 RocketIO GTP T ransceiver User Guide.2.Voltages are specified for the temperature range of T J = –40°C to +100°C.Ta ble 14: DC Characteristics Over Recommended Operating Conditions(2)Symbol Description Min Typ Max UnitsI MGTAVTTTX GTP_DUAL tile transmitter termination supply current(3)7190mAI MGTAVCCPLL GTP_DUAL tile shared PLL supply current3660mAI MGTAVTTRXC GTP_DUAL tile resistor termination calibration supply current0.10.5mAI MGTAVTTRX GTP_DUAL tile receiver termination supply current(3)0.10.5mAI MGTAVCC GTP_DUAL tile internal analog supply current56110mAR REF Precision reference resistor for internal calibration termination49.55050.5ΩNotes:1.Typical values are specified at nominal voltage, 25°C, with a 3.2 Gb/s line rate.2.I CC numbers are given per GTP_DUAL tile with both GTP devices operating with default settings.3.AC coupled TX/RX link.Ta ble 15: Quiescent Supply CurrentSymbol Description Device Typ(1)Max UnitsI CCINTQ Quiescent internal supply current XC5VLX30T mAXC5VLX50T mAXC5VLX85T mAXC5VLX110T mAXC5VLX220T mAXC5VLX330T mAXC5VSX35T mAXC5VSX50T mAXC5VSX95T mAI VTTTXQ Quiescent transmitter supply current XC5VLX30T mAXC5VLX50T mAXC5VLX85T mAXC5VLX110T mAXC5VLX220T mAXC5VLX330T mAXC5VSX35T mAXC5VSX50T mAXC5VSX95T mA I AVCCPLLQ Quiescent GTP_DUAL PLL supply current XC5VLX30T mAXC5VLX50T mAXC5VLX85T mAXC5VLX110T mAXC5VLX220T mAXC5VLX330T mAXC5VSX35T mAXC5VSX50T mAXC5VSX95T mAI VTTRXCQ Quiescent receiver termination switching supply current XC5VLX30T mAXC5VLX50T mAXC5VLX85T mAXC5VLX110T mAXC5VLX220T mAXC5VLX330T mAXC5VSX35T mAXC5VSX50T mAXC5VSX95T mATa ble 15: Quiescent Supply Current (Continued)Symbol Description Device Typ(1)Max UnitsI TTRXQ Quiescent receiver termination supply current XC5VLX30T mAXC5VLX50T mAXC5VLX85T mAXC5VLX110T mAXC5VLX220T mAXC5VLX330T mAXC5VSX35T mAXC5VSX50T mAXC5VSX95T mAI VCCQ Quiescent internal analog supply current XC5VLX30T mAXC5VLX50T mAXC5VLX85T mAXC5VLX110T mAXC5VLX220T mAXC5VLX330T mAXC5VSX35T mAXC5VSX50T mAXC5VSX95T mA Notes:1.Typical values are specified at nominal voltage, 25°C.2.Given for entire die. Powered and unconfigured.3.Unconnected (if channel is driven to voltage).4.More accurate quiescent current estimates can be obtained by using the XPOWER Estimator (XPE) or XPOWER Analyzer (XPA) tools.RocketIO GTP Transceiver DC Input and Output LevelsTable 16 summarizes the D C output specifications of the Virtex-5 RocketIO GTP Transceivers. Figure 1 shows the single-ended output voltage swing. Figure 2 shows the peak-to-peak differential output voltage. Consult UG196: Virtex-5 RocketIO GTP T ransceiver User Guide for further details.Ta ble 16: GTP Transceiver DC SpecificationsSymbolDC ParameterConditionsMinTyp MaxUnitsDV PPIN Differential peak-to-peak inputvoltageExternal AC coupled ≤ 3.2 Gb/s 1502000mV External AC coupled > 3.2 Gb/s 1802000mV V IN Absolute input voltage DC coupledMGT AVTTRX = 1.2V –4001200mV V CMIN Common mode input voltage DC coupledMGT AVTTRX = 1.2V 800mV DV PPOUT Differential peak-to-peak output voltage (1)TXBUFDIFFCTRL = 000, TX_DIFF_BOOST = ON 1400mV V SEOUT Single-ended output voltage swing (1)TXBUFDIFFCTRL = 000, TX_DIFF_BOOST = ON700mV V CMOUT Common mode output voltage Equation basedMGT AVTTTX = 1.2V 1200 – Amplitude/2mVR IN Differential input resistance 90100120ΩR OUT Differential output resistance 90100120ΩT OSKEW T ransmitter output skew15ps C EXTRecommended external AC coupling capacitor (2)75100200nFNotes:1.The output swing and preemphasis levels are programmable using the attributes discussed in UG196:Virtex-5 RocketIO GTP Transceiver UserGuide and can result in values lower than reported in this table.2.Values outside of this range can be used as appropriate to conform to specific protocols and standards.Figure 1: Single-Ended Output Voltage SwingFigure 2: Peak-to-Peak Differential Output VoltageTable 17 summarizes the DC input specifications of the Virtex-5 RocketIO GTP Transceivers. Figure 3 shows the single-ended input voltage swing. Figure 4 shows thepeak-to-peak differential clock input voltage swing. Consult UG196: Virtex-5 RocketIO GTP Transceiver User Guide for further details.Ta ble 17: RocketIO GTP Clock DC Input Level Specification (1)SymbolDC ParameterConditions MinTypMaxUnitsDV PPIN Differential peak-to-peak input voltage2008002000mV V SEIN Single-ended input voltage 1004001000mVR IN Differential input resistance80105130ΩCEXTRequired external AC coupling capacitor75100200nFNotes:1.V MIN = 0V and V MAX = 1200mVFigure 3: Single-Ended Clock Input Voltage Swing Peak-to-PeakFigure 4: Differential Clock Input Voltage Swing Peak-to-PeakRocketIO GTP Switching CharacteristicsConsult UG196:Virtex-5 RocketIO GTP Transceiver User Guide for further information. Ta ble 18: GTP Transceiver PerformanceSymbol DescriptionSpeed GradeUnits -3-2-1F GTPMAX Maximum GTP transceiver data rate 3.75 3.75 3.2Gb/s F GPLLMAX Maximum PLL frequency 2.0 2.0 2.0GHz F GPLLMIN Minimum PLL frequency 1.0 1.0 1.0GHzTa ble 19: CRC Block Switching CharacteristicsSymbol DescriptionSpeed GradeUnits -3-2-1F CRC CRCCLK maximum frequency320320250MHzTa ble 20: GTP Transceiver Reference Clock Switching CharacteristicsAll Speed GradesUnits Symbol Description Conditions Min Typ MaxF GCLK Reference clock frequency range(1)CLK60350MHzT RCLK Reference clock rise time20% – 80%200400ps T FCLK Reference clock fall time80% – 20%200400ps T DCREF Reference clock duty cycle CLK455055% T GJTT Reference clock total jitter, peak-peak(2)CLK40ps T LOCK Clock recovery frequency acquisitiontimeInitial PLL lock1msT PHASE Clock recovery phase acquisition time Lock to data after PLL hasrelocked to the reference clock.Includes lock to reference time.200µsNotes:1.The clock from the GTP_DUAL differential clock pin pair can be used for all serial bit rates. GREFCLK can be used for serial bit rates up to 1 Gb/s.2.Measured at the package pin.Figure 5: Reference Clock Timing ParametersTa ble 21: GTP User Clock Switching Characteristics(1)Speed GradeUnits Symbol Description Conditions-3-2-1F TXOUT TXOUTCLK maximum frequency375375320MHz F RXREC RXRECCLK maximum frequency375375320MHzT RX RXUSRCLK maximum frequency375375320MHzT RX2RXUSRCLK2 maximum frequency RXDA TAWIDTH = 0350350320MHz RXDA TAWIDTH = 1187.5187.5160MHzT TX TXUSRCLK maximum frequency375375320MHzT TX2TXUSRCLK2 maximum frequency TXDA T AWIDTH = 0350350320MHz TXDA T AWIDTH = 1187.5187.5160MHzNotes:1.Clocking must be implemented as described in UG196: Virtex-5 RocketIO GTP T ransceiver User GuideTa ble 22: GTP Transmitter Switching CharacteristicsSymbol Description Min Typ Max UnitsF GTX Serial data rate range0.1F GTPMAX Gb/sT RTX TX Rise time140ps T FTX TX Fall time120ps T LLSKEW TX lane-to-lane skew(1) 2 + 500 ps UI V TXOOBVDPP Electrical idle amplitude20mV T TXOOBTRANS Electrical idle transition time40ns T J3.75T otal Jitter(2) 3.75 Gb/s0.35UID J3.75Deterministic Jitter(2)0.19UIT J3.2T otal Jitter(2) 3.20 Gb/s0.35UID J3.2Deterministic Jitter(2)0.19UIT J2.5T otal Jitter(2) 2.50 Gb/s0.30UID J2.5Deterministic Jitter(2)0.14UIT J2.0T otal Jitter(2) 2.00 Gb/s0.30UID J2.0Deterministic Jitter(2)0.14UIT J1.25T otal Jitter(2) 1.25 Gb/s0.20UID J1.25Deterministic Jitter(2)0.10UIT J1.00T otal Jitter(2) 1.00 Gb/s0.20UID J1.00Deterministic Jitter(2)0.10UIT J500T otal Jitter(2)500 Mb/s0.10UID J500Deterministic Jitter(2)0.04UIT J100T otal Jitter(2)100 Mb/s0.02UID J100Deterministic Jitter(2)0.01UI Notes:ing same REFCLK input with TXENPMAPHASEALIGN enabled for up to four consecutive GTP_DUAL sites.ing PLL_DIVSEL_FB = 2, INTDATAWIDTH = 1.3.All jitter values are based on a Bit-Error Ratio of 1e–12.Ethernet MAC Switching CharacteristicsConsult UG194:Virtex-5 T ri-mode Ethernet Media Access Controller User Guide for further information.Ta ble 23: GTP Receiver Switching CharacteristicsSymbolDescriptionMin Typ Max Units F GRX Serial data rate RX oversampler not enabled 0.5F GTPMAXGb/s RX oversampler enabled0.10.5Gb/s R XOOBVDPP OOB detect threshold peak-to-peakOOBDETECT_THRESHOLD = 10060105165mV R XSST Receiver spread-spectrum tracking (1)Modulated @ 33 KHz–50000ppm R XRL Run length (CID)Internal AC capacitor bypassed 150UI R XPPMTOLData/REFCLK PPM offset toleranceACDR 2nd -order loop enabled–10001000ppmSJ Jitter ToleranceJT_SJ 3.75Sinusoidal Jitter (2) 3.75 Gb/s 0.30UI JT_SJ 3.2Sinusoidal Jitter (2) 3.20 Gb/s 0.40UI JT_SJ 2.50Sinusoidal Jitter (2) 2.50 Gb/s 0.40UI JT_SJ 2.00Sinusoidal Jitter (2) 2.00 Gb/s 0.40UI JT_SJ 1.00Sinusoidal Jitter (2) 1.00 Gb/s 0.30UI JT_SJ 500Sinusoidal Jitter (2)500 Mb/s 0.30UI JT_SJ 500Sinusoidal Jitter (2)500 Mb/s OS 0.30UI JT_SJ 100Sinusoidal Jitter (2)100 Mb/s OS0.30UISJ Jitter Tolerance with Stressed EyeJT_TJSE 3.2T otal Jitter with Stressed Eye (3)3.20 Gb/s 0.87UI JT_SJSE 3.2Sinusoidal Jitter with Stressed Eye (3)3.20 Gb/s0.30UINotes:ing PLL_RX_DIVSEL_OUT = 1.ing 80 MHz sinusoidal jitter only in the absence of deterministic and random jitter.3.Stimulus signal includes 0.4UI of DJ and 0.17UI of RJ. RX equalizer is enabled.4.All jitter values are based on a Bit Error Ratio of 1e –12.Ta ble 24: Maximum Ethernet MAC PerformanceDescriptionSpeed GradeUnits-3-2-1Ethernet MAC Maximum Performance10/100/1000Mb/s。

Xilinx最新Virtex-5 FXT FPGA集成PowerPC 440处理器模块

Xilinx最新Virtex-5 FXT FPGA集成PowerPC 440处理器模块赛灵思公司(Xilinx)日前宣布推出Virtex-5 FXT器件。

这些FPGA器件在业界率先集成了嵌入式PowerPC 440处理器模块、高速RocketIO GTX收发器和专用XtremeDSP处理能力。

作为65nm Virtex-5系列的第四款平台,Virtex-5 FXT提供了极高的性能,还可帮助设计人员降低系统成本、缩小板尺寸并减少元件数量。

在赛灵思公司以及业界领导厂商提供的逻辑、嵌入式和DSP开发工具以及IP内核的支持下,Virtex-5 FXT FPGA为有线和无线通信、音频/视频广播设备、军事、航空航天、工业系统以及其它众多应用提供了一个终极系统集成平台。

“在单片器件上集成重要处理性能和SERDES元件,可为那些需要节约板级空间和成本、同时又需要满足高性能要求的设计人员提供巨大的价值。

”市场调查公司Forward Concepts的创始人、总裁兼分析师Will Strauss说,“例如,在无线应用中,Virtex-5 FXT平台技术可以支持的基站类型是受到高度关注的,特别是在支持4G通信系统的LTE(长期演化)基带的应用领域。

”这次发布,意味着组成赛灵思公司Virtex-5系列的四款领域优化的FPGA平台已经全部推出。

Virtex-5是第一个充分发挥了65nm工艺性能、密度和成本优势的FPGA系列产品,提供了无与伦比的性能和密度领先优势。

与前一代90nm FPGA相比,速度平均提高30%,逻辑容量增加65%。

在取得这一突破性性能提升的同时,赛灵思公司还成功地降低了动态功耗,与前一代器件相比降低了35%。

四个面向领域优化的平台LX、LXT、SXT和FXT,提供了范围广泛的多种器件选择,支持工程师以更高的成本效益实现电子系统设计,并根据自己的特定设计选择具有最佳资源组合的FPGA器件。

这四个平台分别针对逻辑密集、嵌入式处理、数字信号处理(DSP)以及串行连接应用提供了优化的逻辑、I/O以及硬IP模块资源组合。

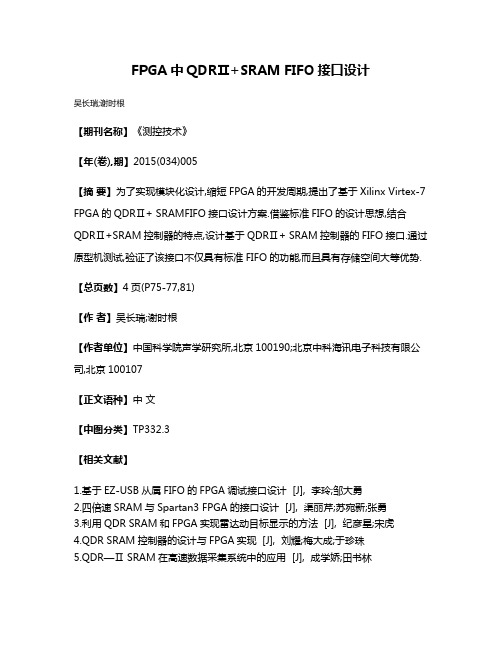

FPGA中QDRⅡ+SRAM FIFO接口设计

FPGA中QDRⅡ+SRAM FIFO接口设计

吴长瑞;谢时根

【期刊名称】《测控技术》

【年(卷),期】2015(034)005

【摘要】为了实现模块化设计,缩短FPGA的开发周期,提出了基于Xilinx Virtex-7 FPGA的QDRⅡ+ SRAMFIFO接口设计方案.借鉴标准FIFO的设计思想,结合QDRⅡ+SRAM控制器的特点,设计基于QDRⅡ+ SRAM控制器的FIFO接口.通过原型机测试,验证了该接口不仅具有标准FIFO的功能,而且具有存储空间大等优势.【总页数】4页(P75-77,81)

【作者】吴长瑞;谢时根

【作者单位】中国科学院声学研究所,北京100190;北京中科海讯电子科技有限公司,北京100107

【正文语种】中文

【中图分类】TP332.3

【相关文献】

1.基于EZ-USB从属FIFO的FPGA调试接口设计 [J], 李玲;邹大勇

2.四倍速SRAM与Spartan3 FPGA的接口设计 [J], 渠丽芹;苏宛新;张勇

3.利用QDR SRAM和FPGA实现雷达动目标显示的方法 [J], 纪彦星;宋虎

4.QDR SRAM控制器的设计与FPGA实现 [J], 刘耀;梅大成;于珍珠

5.QDR—Ⅱ SRAM在高速数据采集系统中的应用 [J], 成学娇;田书林

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

利用Virtex5器件实现QDR II SRAM接口提要本应用指南说明了利用 Virtex‐5 器件实现 4 字突发四倍数据速率 (Quad Data Rate QDR II)SRAM 接口及其时序的详细信息此可综合的参考设计利用 Virtex‐5 系列独有的 I/O 和时钟控制功能,实现了 300 MHz (600 Mb/s) 的性能水平,使每个 36 位存储器接口的总流量达到 43.2Gb/s此设计在最大限度降低资源使用量的同时还大幅简化了在 FPGA 内采集读数据的任务此方案提供了一个简单的用户接口,可通过利用一个或多个 QDR II 接口简便地集成到一个完整的FPGA 设计中简介QDR SRAM 器件为满足更高的带宽存储要求而开发,以网络和电信应用为目标基本 QDR 架构具有独立的读、写数据通路,便于同时操作每个时钟周期内,两个通路均使用双倍数据速率 (DDR) 传输发送两个字,一个在时钟上升沿发送,一个在时钟下降沿发送结果,在每个时钟周期内会传输四个总线宽度的数据(两个读和两个写),这就是四倍数据速率的由来QDR I 和 QDR II 的规范由 QDR 联盟(Cypress、IDT、NEC、Samsung 和 Renesas)共同定义和开发有关 QDR 规范、QDR 联盟和 QDR 存储器产品的其他信息,请参考第 16 页上的“参考”QDR 存储器器件以 2 字突发和 4 字突发架构提供针对每个读或写请求,2 字突发器件传输两个字DDR 地址总线用于在前半个时钟周期允许读请求,在后半个时钟周期允许写请求与之相反,4 字突发器件针对每个读或写请求传输四个字,这样便只需要一个单倍数据速率 (SDR)地址总线,就能最大程度地利用数据带宽读、写操作请求必须在交替的时钟周期(即不重叠的时钟周期)内进行,以分享地址总线本应用指南所讨论的参考设计针对的是 4 字突发 QDR II SRAM 器件QDR II 架构的独特性能之一是源同步回送时钟 (CQ) 输出,它与器件输入时钟 (K) 频率相同,与通过读通路输出 (Q) 传输的数据边沿对齐CQ 时钟输出使用 QDR II 存储器器件内的延迟锁定环 (DLL) 电路被重新安排,使其与 Q 数据输出对齐对于在远端器件上进行的读数据采集操作,此种时钟传输(亦称源同步)接口方法允许较大的时序余量第 2 页图1 的时序图表示 4 字突发 QDR II 存储器接口上的并发读/ 写操作QDR II 存储器的所有输入与输入时钟(K 和 K)同步,传输给存储器时,数据中心通常与输入时钟 K 及 K 边沿对齐注: 低有效的读控制 (R) 和写控制 (W) 引脚在时钟周期内交替出现,以实现单独 SDR 地址总线 (SA) 的共享写总线数据输入 (D) 值在 DDR 模式下被发送到存储器,开始于写控制引脚激活后的下一个K时钟上升沿读总线数据输出 (Q) 值在 DDR 模式下从存储器中发送,并与 CQ 和 CQ 源同步回送时钟输出边沿对齐在 CQ 时钟输出的上升沿(紧随 K 输入时钟的下一个上升沿之后),读总线中的第一个字开始发送在从数据输入 (D) 字中选择要写入存储器的特定字节时,QDR II 存储器还可使用低有效的字节写 (BW) 使能引脚为清晰起见,图1 中省略了这些信号图1 的时序图表示 2 字突发 QDR II 存储器接口上的并发读/ 写操作在时钟的前半个周期,DDR 地址总线允许读地址被传输给存储器;在时钟的后半个周期,DDR 地址总线允许写地址出现于其中因此,低有效的读控制 (/R) 和写控制 (/W) 引脚可在同一时钟周期内设定两个写总线数据输入 (D) 值在 DDR 模式下被发送到存储器,开始于写地址有效前的那个 K 时钟上升沿读总线数据输出 (Q) 值在 DDR 模式下从存储器中发送,并与 CQ 和/CQ 源同步回送时钟输出边沿对齐在 /CQ 时钟输出的上升沿(紧随 /K 输入时钟的下一个上升沿之后),读总线中的第一个字开始发送设计概述图2 为 Virtex‐5 QDR II 参考设计的高层次框图,表明了 QDR II 存储器器件的外部连接以及用于发送读/ 写命令的 FPGA 内部资源接口在图2 中,QDR II 器件的 C 和 C 引脚均被设定为 High如第 4 页图3 所示,Virtex‐5 QDR II 参考设计由以下四个主要部分组成:用户接口物理接口读/ 写状态机延迟校准状态机此用户接口使用完全基于 SDR 信号的简单协议创建读/ 写请求此模块主要由 FIFO16 基元构成,用于在读/ 写操作执行前后存储相应的地址和数据值有关用户接口时序协议的详情,请参阅第 5 页“用户接口”读/ 写状态机主要负责监控用户接口模块内 FIFO 的状态,调整用户接口和物理接口间的数据流,并向外部存储器器件发送实际读/ 写命令此状态机确保读/ 写操作按照 QDR II存储器规范的要求,以并发方式在最短延迟内完成物理接口负责生成正确的时序关系和 DDR 信号,以便以符合其命令协议和时序要求的方式与外部存储器器件通信延迟校准状态机是物理层中一个不可分割的组成部分,大大简化了在 FPGA 内采集读数据的任务,同时又可实现最佳性能Virtex‐5 器件的每个输入引脚都包含一个可动态调整的可编程延迟元件 (IDELAY),用于控制 5 ns 窗口中输入通路上的延迟时间延迟校准状态机利用此独特功能调整从存储器器件返回的读数据的时序,因此它无需任何复杂的数据采集技术即可直接与全局 FPGA 系统时钟 (USER_CLK0) 实现同步第 5 页表1 总结了 Virtex‐5 QDR II 参考设计的规范,包括性能目标和器件应用细节实现详情实现QDR II 参考设计的目的是利用 Virtex‐5 系列的独特功能I/O、时钟控制和存储元件技术方面的发展使此设计的高性能和全承包操作得以实现以下部分对此设计的实现给出进一步的详细说明用户接口用户接口模块利用六个 FIFO16 模块来存储读/ 写操作的地址和数据值三个 FIFO16模块用于写命令,一个用于存储写地址 (USER_AD_WR) 和字节写使能 (USER_BW_n) 信号,另外两个用于存储要写入存储器的 Low (USER_DWL) 和 High (USER_DWH) 36 位数据字读命令也使用三个 FIFO16 模块,一个用于存储读地址 (USER_AD_RD),另两个用于存储由于执行读而从存储器中返回的 Low (USER_QRL) 和 High (USER_QRH) 36 位数据字第 6 页图4 表示使用 4 字突发参考设计时,向用户接口发送读/ 写请求所需的时序协议如前所述,此接口使用了所有已与主 FPGA 设计系统时钟 (USER_CLK0) 同步的 SDR信号写请求在 USER_CLK0 上升沿期间通过低有效的 USER_W_n 信号创建此 18 位写地址(USER_AD_WR) 必须在此同一时钟边沿传输此时,要写入存储器的第一个和第二个 36 位数据字也会分别传输给 36 位 USER_DWL 和 USER_DWH 输入总线4 字突发的第三个字和第四个字会在下一个 USER_CLK0 上升沿分别传输给 USER_DWL 和 USER_DWH读请求在 USER_CLK0 上升沿期间通过低有效的 USER_R_n 信号创建此 18 位读地址(USER_AD_RD) 必须在此同一时钟边沿传输执行读命令后,4 字突发值存储于读数据 FIFO中在 USER_CLK0 上升沿,一个低有效的 USER_QEN_n 信号会检索这些值并将其传输至 36位 USER_QRL 和 USER_QRH 输出第一和第二个字在首个周期中传输,此时的USER_QEN_n 设置为 Low,紧接着是第三和第四个字在随后一个周期中传输,此时的USER_QEN_n 也设置为 Low与 QDR II 存储器本身不同,用户接口在同一时钟周期接受读、写请求(如图4 所示的第三个周期)读/ 写状态机管理向外部存储器器件所发送的读与写请求的交替,使用户接口免于承担这项职责用户接口还提供了一批用于指示读/ 写 FIFO 状态的信号,在图4 中未显示高有效的USER_WR_FULL 输出表明写 FIFO 已满此情况表明,写请求队列缩减之前将不再接受任何写请求USER_WR_FULL 为 High 时创建的任何写请求都将被直接忽略类似情况适用于读请求的 USER_RD_FULL 信号高有效的 USER_QR_EMPTY 输出表明不再有读数据值存储在读数据 FIFO 中在此情况下从USER_QRL 和 USER_QRH 总线读值的尝试将被忽略此情况会一直持续,直到执行其他读命令并且有相关数据值存入读数据 FIFO读/ 写状态机第 8 页图5 为 4 字突发读/ 写状态机的状态图此状态机负责调节用户接口和物理接口之间的数据流它根据保存在用户接口 FIFO 中的请求向外部存储器器件发送读/ 写命令USER_RESET 每次都会将状态机恢复到 INIT 状态,此时存储器暂停运行,直到延迟校准状态机完成所有 QDR_Q 输入的 IDELAY 模块上的延迟调整,使读通路数据与 FPGA 系统时钟(USER_CLK0) 中心对齐校准操作完成的信号是一个高有效的 DLY_CAL_DONE 输入,该输入将读/ 写状态机转换到空闲状态,以等候来自用户接口的读/ 写请求在空闲状态,写命令首先假设向存储器写数据必须始终发生在任何有效读数据出现之前当没有待处理的读或写请求时,此状态机将在空闲状态下循环运行用户接口 FIFO 中的待处理写请求会使状态机转入写状态,在此状态下,写命令通过内部的WR_INIT_n 选通脉冲发送此选通脉冲从 FIFO 中取出写地址和数据值,并使外部 QDR_W_n写控制选通脉冲进入存储器器件如果包含待处理读请求,此状态机会随之转入读状态,此时内部 RD_INIT_n 选通脉冲被激活RD_INIT_n 选通脉冲从 FIFO 中取出读地址,并向存储器器件发送一个外部 QDR_R_n 选通脉冲作为此处理过程的结果之一,对读数据 FIFO 中的返回值也将进行采集读/ 写状态机持续监控用户接口 FIFO 状态信号,以确定是否存在待处理读/ 写请求连续不断的并发读/ 写请求流将导致状态机只在读状态和写状态之间转换,以确保正确无误地将请求交替发送到外部存储器一串只写请求将导致空闲状态和写状态轮流出现,同样,一串读请求也会在空闲状态和读状态间转换物理接口Virtex‐5 QDR II 参考设计的物理接口为读/ 写命令与外部存储器器件之间的通信生成实际的I/O 信号和时序关系,包括 DDR 数据信号它提供必要的时序余量及为满足整体设计性能规范所需的 I/O 信号标准QDR II 设计的所有 I/O 信号都使用 HSTL‐I 发送此部分详细介绍物理接口的每个部件时钟控制机制此 QDR II 设计使用的是所有 Virtex‐5 I/O 模块中都有的输出 DDR (ODDR) 基元这些内置DDR 寄存器功能极大地简化了以下任务:生成准确的时钟、地址和数据,以及与 QDR II 存储器器件通信的控制信号IDDR 和 ODDR 基元都有多种运行模式,可分别确定采集或传输的DDR 数据以怎样的方式出现在 FPGA 内部资源和 I/O 引脚中QDR II 设计中的时钟控制机制(第 9 页图6)使用反沿 (opposite‐edge) 模式的 ODDR 寄存器来为存储器器件生成 QDR_K 和 QDR_K_n 时钟因为时钟信号的时序与 QDR II 地址、数据和控制信号几乎相同,此时钟传输机制会有效地从时序余量因素中删除 FPGA 的 clock‐to‐out参数因此,就 clock‐to‐out 参数而言,所有外部传输信号都得以“匹配”写通路QDR II 存储器的写通路包括执行写操作所必需的地址、数据和控制信号写地址(QDR_AD_WR)、控制选通脉冲 (QDR_W_n) 和字节写使能 (QDR_BW_n) 信号都使用 SDR 格式不过,写数据值 (QDR_D) 利用 DDR 信号在规定的时钟周期实现所需的 2 字或 4 字突发所有这些写通路信号在传输时都必须与 QDR_K 和 QDR_K_n 时钟边沿中心对齐因此,这些信号的输出寄存器与 USER_CLK270 时钟同步信号以同样的频率运行,但对于USER_CLK0则会出现 270°(时钟周期的 75%)的相差这能确保对输入 QDR_K 和QDR_K_n 时钟边沿而言,存储器器件有足够的建立与保持余量第 10 页图7 说明了如何使用 USER_CLK270 和 ODDR 寄存器为 QDR_D 写数据通路生成所需的 DDR 信号ODDR 寄存器配置为同沿 (same‐edge) 模式,允许在 USER_CLK270的同一上升沿从 FPGA 架构中同时采集两个 36 位数据字(FIFO_DWL 和 FIFO_DWH)FIFO_DWL 值在此上升沿后立即发送到 QDR_D 写数据总线,随后,FIFO_DWH 值在 USER_CLK270 的下一个下降沿从 ODDR 模块发送对此过程加以重复,以生成一个 4 字写数据突发使用 I/O 模块中的单个触发器以类似的方式生成读/ 写地址、字节写使能和读/ 写控制选通脉冲,以创建与 USER_CLK270 同步的 SDR 信号读数据通路基于 CQ 的数据采集机制可以实现以极高的时钟速率从存储器中采集读数据此数据采集机制使用在每个 I/O 中都提供的 ISERDES 功能输入时钟 (CQ) 和数据 (Q) 经延迟后与 ISERDES 模块中的系统时钟 (CLK0) 保持同步读数据通路包括两个阶段:读数据采集和读数据重新采集两个阶段均在各个 Virtex‐5I/O 的内置 ISERDES 中实现途经 BUFIO 的 CQ 信号将采集 ISERDES 模块内首组寄存器中的输入读数据 (Q)第二组寄存器用来将 CQ 域中的数据传输至系统时钟域ISERDES 具有三种时钟输入:CLK、OCLK 和 CLKDIV读数据 (Q) 在 CLK (CQ) 域经采集完成后,通过 OCLK 和 CLKDIV 传输至系统时钟(图8):CLK:布线通过 BUFIO 的读时钟 (CQ) 提供 CLK 时钟输入OCLK 和 CLKDIV:这些时钟负责对输入数据进行串并转换由于数据以与接口速度相同的频率进行传输,系统时钟 (CLK_0) 提供针对 OCLK 和 CLKDIV 的输入在ISERDES 中采集到的数据可以被写入 Virtex‐5 FPGA 中的内置 FIFO36 模块基于 CQ 的数据采集机制要求将读时钟(CQ 和 CQ)置于 clock‐capable I/O (CCIO) 中,时钟从这些位置可以访问各组 (bank) 内可用的 BUFIO对于 x36 宽的 QDR II SRAM 接口,CQ_P 和 CQ_N 均用来采集读数据(第 11 页图9)一个Virtex‐5 器件中的每个组都包含 40 个 I/O,因此一个 x36 接口的读数据需要置于两个组中CQ_P 用来采集一个组中的首组字节,而 CQ_N 用来采集相邻组中剩余的数据字节CQ_P 和CQ_N 均需置于相应组中 CCIO 的 P 侧延迟校准延迟校准逻辑负责提供读数据 (Q) 和时钟 (CQ) 所需要的延迟,以便将采集到的数据与 FPGA时钟中心对齐当来自 IDELAYCTRL 的 IDELAY_READY 信号设定为 High,且存储器初始化所需的时钟周期得到满足时,延迟校准状态机就会启动校准过程包含单次写,随后向同一位置连续进行读,直到找到 Q 和 CQ 信号正好需要的延迟值读校准开始后,校准状态机会执行以下步骤:1. 增加 CQ 和 Q 上的 tap 延迟值如果在某个 tap 值上初次获取了有效数据,则此tap 值标志着数据有效窗口的开端2. 继续增加 CQ 和 Q 的 tap 延迟值,直到达到有效窗口的终端3. 将 CQ 置于此有效窗口的中央降低 tap 值,直到 CQ 被固定于数据有效窗口的中央4. 对于 CQ 和 FPGA 时钟,数据总线 (Q) 将置于中央重新设置 Q 的 tap 值,即可针对 CQ和系统时钟 (CLK0) 得出 Q 的有效窗口对于 CQ 和 FPGA 时钟,数据信号 (Q)将置于中央当所有 Q 信号围绕 CQ 固定后,延迟校准过程就结束了,并继之以读使能校准读使能逻辑对向存储器发送的读命令进行校准,为已采集到并写入读数据 FIFO 的数据生成写使能校准逻辑使用 SRL16 构建而成,有助于确定读命令信号所需寄存器级数的数量,以生成正确的写使能信号板设计中的考虑因素尽管 Virtex‐5 系列产品提供了许多与 I/O 和时钟控制相关的高级功能,大大简化了存储器接口设计,但为了使接口可靠而高效,仍需注意基本的电路板设计标准需特别强调的是,读和写通路接口的源同步特性要求接口时钟、数据及控制信号具有相匹配的电路板布线长度例如,QDR II 器件输入信号(QDR_K、QDR_K_n、QDR_W_n、QDR_R_n、QDR_SA、QDR_BW_n 和 QDR_D)的布线长度必须完全匹配,以将控制、地址及数据线接至具备充足建立与保持余量的存储器器件物理接口的实现可确保这些信号在离开 FPGA 器件输出时与QDR_K和 QDR_K_n 时钟边沿中心对齐电路板布线必须确保这种关联状态能持续到存储器器件输入同样,QDR II 器件输出信号(QDR_Q、QDR_CQ)必须具备完全匹配的布线长度,以使这些信号在 Virtex‐5 器件的输入端实现边沿对齐要实现直接时钟控制读数据采集方法,这一点非常关键所有合适的板设计工具都可以在可接受的容错范围内轻松满足这些布线长度时序分析本 Virtex‐5 QDR II 参考设计利用该器件的独特 I/O 和时钟控制功能,可最大限度地提高性能与时序余量,同时大大降低对详细布局和管脚分配分析的需求本部分针对地址/ 控制通路、写数据通路及读(或采集)数据通路给出一个时序分析示例地址/ 控制通路先前已讨论过,读/ 写地址总线、字节写使能信号和读/ 写控制选通脉冲都与USER_CLK270时钟保持同步这可以确保,对于来自 USER_CLK0 的输入 QDR_K 和QDR_K_n 时钟边沿,这些 SDR 信号具备对存储器器件的有充足的建立与保持余量表2 根据用一个 Virtex‐5 器件实现的 300 MHz 4 字突发 QDR II 存储器器件接口,显示针对这些信号的一个时序分析示例写数据通路写数据 (QDR_D) 也与 USER_CLK270 保持同步不过,写数据字作为 DDR 进行发送,因此在QDR_K 和 QDR_K_n 上升沿均需具备充足的建立与保持余量相应地,表3 所示写通路的时序分析包括了存储器时钟的最大占空比失真,并基于 300 MHz 4 字突发 QDR II 存储器器件及速度级别为 ‐11 的 Virtex‐5 器件读数据通路(数据采集)读数据通路 (QDR_Q) 值直接被采集至 SERDES 内的 USER_CLK0 时钟域表4 显示读数据采集的时序分析结论本应用指南说明了利用 Virtex‐5 器件实现 4 字突发 QDR II SRAM 接口及其时序的详细信息数据采集机制的应用大大简化了在 FPGA 内采集读数据的任务,且为当前及下一代 QDR IISRAM 存储器器件提供了高效、强大、可扩展的存储器接口解决方案此 QDRII 参考设计可从 Xilinx 网站下载。