Scan Design and Secure Chip

人教版高中英语选择性必修第三册精品课件 Unit 2 分层跟踪检测(2)

cut out,be composed of,shave off,stick to,take up 4.Developers should have the courage of their convictions and

stick to what they do best. 5.It might be a good idea to shave off your beard before going to Beijing for the interview.

ⅠⅡⅢⅣⅤ

After three months’ training using the stimulators,Marc more or less stopped experiencing pace freezing.Marc says that passing through narrow paths or turning had previously caused pace freezing,which led to him falling five or six times a day.Marc has now been using the stimulator for two years and says he hardly falls any more,allowing him to walk several kilometres at a time.

解析 细节理解题。根据第二段中“However,many people don’t respond to these treatments,particularly if their condition is advanced,says Courtine.”可 知,Courtine 的团队设计这个装置是因为传统的治疗方法对许多人特别是 病情严重的人帮助不大。

modern system-on-chip design on arm 笔记

modern system-on-chip design on arm 笔记Modern system-on-chip (SoC) design on ARM involves the integration of multiple components onto a single chip, enabling high-performance computing in a compact and power-efficient package. In this note, we will explore some key aspects of SoC design on ARM.1. Architecture: ARM provides a range of processor architectures, such as ARM Cortex-A, Cortex-R, and Cortex-M, each catering to different application requirements. SoC designers need to select the appropriate architecture based on factors like performance, power consumption, and real-time processing capabilities.2. Integration of Components: SoC design involves integrating various components like the processor core, memory subsystem, peripherals, and interfaces onto a single chip. This integration enables efficient communication between different components, reducing latency and power consumption.3. Power Management: Power management is a critical aspect of SoC design, as modern devices demand high performance while maintaining long battery life. SoC designers use techniques like power gating, clock gating, and voltage-frequency scaling to optimize power consumption in different operating modes.4. Security: With the increasing connectivity of devices, SoC design needs to prioritize security. ARM provides TrustZone technology, enabling the isolation of secure and non-secure software and protecting sensitive data from unauthorized access. SoC designers need to incorporate security features and developrobust encryption and authentication mechanisms.5. Verification and Validation: SoC designers undertake rigorous verification and validation processes to ensure the correct functioning of the integrated components. This involves testing the system for diverse scenarios, corner cases, and performance benchmarks. Advanced verification techniques like simulation, formal verification, and emulation are utilized to detect and fix design flaws.6. Software Development: SoC designers work closely with software developers to optimize software architecture for the specific SoC design. This collaboration involves developing device drivers, firmware, and operating systems that leverage the hardware capabilities effectively.7. Packaging and Manufacturing: Once the SoC design is finalized, it needs to be packaged and manufactured. The packaging involves integrating the chip into a package with appropriate interconnects and thermal management. The manufacturing process includes wafer fabrication, die testing, and final assembly.In conclusion, modern SoC design on ARM involves selecting the right processor architecture, integrating components, optimizing power consumption, ensuring security, thorough verification and validation, software development, and packaging/manufacturing. All these aspects collectively contribute to the successful deployment of efficient and high-performance ARM-based SoCs.。

英语作文-集成电路设计行业的智能芯片与系统解决方案

英语作文-集成电路设计行业的智能芯片与系统解决方案The design and development of intelligent chips and system solutions in the integrated circuit design industry have revolutionized the way we interact with technology. These advancements have not only enhanced the performance and efficiency of electronic devices but have also opened up new possibilities for innovation in various fields.One of the key aspects of intelligent chip design is the integration of artificial intelligence (AI) algorithms. By incorporating AI into the chip architecture, designers are able to create systems that can learn and adapt to different situations, making them more efficient and versatile. This has led to the development of smart devices that can recognize speech, images, and patterns, enabling them to provide personalized experiences for users.Moreover, intelligent chips have also played a crucial role in the development of autonomous systems. By combining sensors, processors, and communication modules, designers have been able to create self-driving cars, drones, and robots that can navigate and interact with their environment without human intervention. These advancements have not only improved efficiency and safety but have also opened up new opportunities for automation in various industries.In addition to AI integration, intelligent chip design also focuses on energy efficiency and miniaturization. By optimizing the power consumption of chips and reducing their size, designers are able to create devices that are not only more environmentally friendly but also more portable and convenient for users. This has led to the development of wearable devices, smart home appliances, and IoT devices that can seamlessly integrate into our daily lives.Furthermore, intelligent chip design has also enabled the development of advanced security features. By incorporating encryption, authentication, and secure bootmechanisms into the chip architecture, designers are able to create systems that can protect sensitive data and prevent unauthorized access. This has become increasingly important in today's interconnected world, where cyber threats are becoming more sophisticated and prevalent.Overall, the integration of intelligent chips and system solutions in the integrated circuit design industry has transformed the way we interact with technology. From AI-powered devices to autonomous systems and energy-efficient gadgets, these advancements have not only improved the performance and efficiency of electronic devices but have also opened up new possibilities for innovation in various fields. As technology continues to evolve, intelligent chip design will play a crucial role in shaping the future of electronics and revolutionizing the way we live and work.。

华为突破技术封锁自主研发芯片英语作文

华为突破技术封锁自主研发芯片英语作文全文共3篇示例,供读者参考篇1Huawei Breaks Through Technological Blockade withSelf-developed ChipsIn recent years, the Chinese tech giant Huawei has been faced with a technological blockade from the United States, which has severely restricted its access to key components such as semiconductors. However, Huawei has not been deterred by these challenges. Instead, the company has focused on developing its own chips, in a bid to achieve self-reliance and break free from the shackles of technological dependence.The development of self-developed chips by Huawei has been a monumental task, requiring significant investment in research and development, as well as a high level of technical expertise. In order to achieve this goal, Huawei has recruited top talent from around the world, investing heavily in training and development programs to nurture a new generation of chip designers and engineers.One of the key milestones in Huawei's journey towardsself-reliance in chip manufacturing was the launch of its flagship Kirin chipset series. This series of chips has been widely acclaimed for its performance and efficiency, and has been used in some of Huawei's most popular smartphones and tablets. The Kirin chipset series has not only enhanced Huawei's competitiveness in the global market but has also served as a testament to the company's ability to innovate and adapt in the face of adversity.In addition to developing its own chips, Huawei has also invested in building a state-of-the-art semiconductor manufacturing facility in China. This facility is equipped with cutting-edge technology and has the capacity to produce a wide range of chips for Huawei's various products. By establishing this manufacturing facility, Huawei has taken a significant step towards achieving self-sufficiency in chip production, reducing its reliance on external suppliers and ensuring a stable supply chain for its products.The success of Huawei in breaking through the technological blockade and developing its own chips has not only bolstered the company's position in the global market but has also inspired a new wave of innovation in the semiconductor industry.Many other Chinese companies have followed in Huawei's footsteps, investing in research and development to develop their own chips and reduce their dependence on foreign suppliers.In conclusion, Huawei's efforts to develop self-developed chips have been a remarkable achievement, demonstrating the company's commitment to innovation and self-reliance in the face of adversity. By breaking through the technological blockade and achieving self-sufficiency in chip manufacturing, Huawei has not only secured its future competitiveness but has also paved the way for a new era of technological innovation in China and beyond.篇2Huawei has recently made a significant breakthrough in overcoming technological blockades through self-developed chips. As a global leader in telecommunications, Huawei has faced challenges due to the restrictions imposed on it by certain governments. However, the company has shown resilience and innovation by investing heavily in its own research and development capabilities to create cutting-edge chips for its devices.Huawei's success in developing its own chips is a result of years of dedication and investment in research and development. The company's chip division, HiSilicon, has been working tirelessly to create top-of-the-line chips that can match or even surpass those produced by Western companies. The recent unveiling of the Kirin 9000 chipset, the world's first 5nm 5G SoC, is a testament to Huawei's technological prowess and its ability to compete on a global scale.The development of the Kirin 9000 chipset represents a major milestone for Huawei as it showcases the company's ability to break through technological barriers and achieveself-sufficiency in chip production. With this new chipset, Huawei can now reduce its reliance on external suppliers and ensure the supply chain for its devices remains secure in the face of external pressures.In addition to the Kirin 9000 chipset, Huawei has also made significant strides in other areas of chip development. The company has invested heavily in artificial intelligence (AI) chips and is working on developing its own AI processing units (APUs) to power its future devices. These AI chips will enable Huawei to deliver cutting-edge features and capabilities in its devices,further solidifying its position as a technological innovator in the industry.Overall, Huawei's breakthrough in self-developed chips is a testament to the company's commitment to innovation and its ability to overcome challenges through technology. By investing in its research and development capabilities, Huawei has shown that it can compete at a global level and continue to push the boundaries of what is possible in the world of telecommunications. With its self-developed chips, Huawei is setting the stage for a new era of technological advancement and shaping the future of the industry.篇3In recent years, Huawei, a leading global provider of information and communications technology (ICT) infrastructure and smart devices, has faced significant challenges due to technological restrictions imposed by the United States government. In response to these challenges, Huawei has been focusing on developing its own semiconductor technology to reduce reliance on foreign suppliers and ensure the security and sustainability of its supply chain.The United States government has placed Huawei on a trade blacklist, citing national security concerns and alleging that the company's products pose a threat to U.S. interests. This move has severely restricted Huawei's access to vital technologies, including semiconductor chips developed and manufactured by American companies. As a result, Huawei has been forced to find alternative ways to source these critical components and maintain its competitive edge in the global market.To overcome these obstacles, Huawei has made significant investments in research and development to accelerate the development of its own semiconductor technology. The company has established a dedicated division, Huawei HiSilicon, which focuses on designing and manufacturing advanced chips for use in its smartphones, telecommunications equipment, and other devices. Huawei has also built partnerships with Chinese semiconductor companies and academic institutions to leverage their expertise and resources in developing cutting-edge semiconductor technology.One of the key achievements of Huawei in its efforts to break through technological constraints is the development of its Kirin series of processors. These chips are designed to deliver high performance, energy efficiency, and advanced features to meetthe demands of today's increasingly complex and data-intensive applications. The latest Kirin processors, such as the Kirin 990 and Kirin 980, incorporate advanced technologies such as artificial intelligence (AI) processing, 5G connectivity, and advanced image processing capabilities.In addition to developing its own semiconductor technology, Huawei has also been exploring alternative sources of chips and components to diversify its supply chain and reduce its dependence on U.S.-based suppliers. The company has partnered with companies in countries such as Taiwan, South Korea, and Japan to secure a stable and reliable supply of key components for its products. Huawei has also invested in building its own manufacturing facilities and production lines to increase its capacity for producing semiconductor chips and other components in-house.Despite the challenges and obstacles it has faced, Huawei's efforts to break through technological constraints and develop its own semiconductor technology have shown promising results. The company's Kirin processors have received positive reviews for their performance, efficiency, and innovation, and have enabled Huawei to maintain its position as a leading player in the global ICT market.Looking ahead, Huawei remains committed to investing in research and development, fostering innovation, and building partnerships with technology companies and academic institutions to drive further advancements in semiconductor technology. By continuing to strengthen its capabilities in chip design and manufacturing, Huawei aims to secure its position as a key player in the global semiconductor industry and ensure the long-term success and sustainability of its business.。

MCUXpresso 配置工具的快速入门指南(网络版)说明书

1简介MCUXpresso 配置工具属于 NXP Cortex-M 处理器工具。

为了展示部分功能,您可以在 上在线查看引脚和时钟简化版本。

•引脚工具可用于配置引脚路由和电气化属性。

•时钟工具可用于配置系统时钟。

这些工具可用于评估芯片特性和功能,也可用于生成初始化代码。

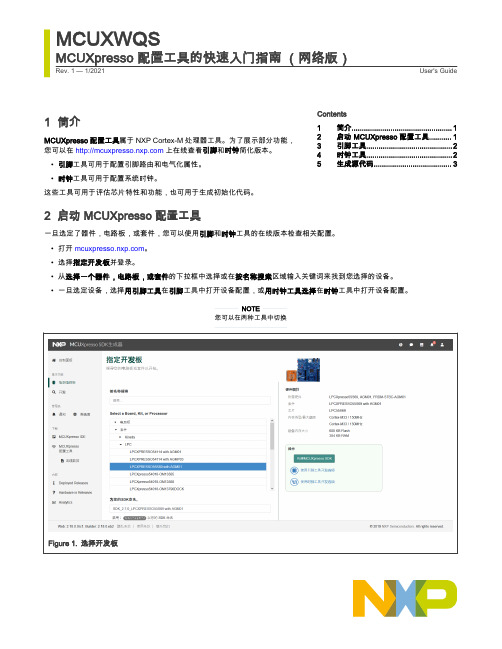

2启动 MCUXpresso 配置工具一旦选定了器件,电路板,或套件,您可以使用引脚和时钟工具的在线版本检查相关配置。

•打开 。

•选择指定开发板并登录。

•从选择一个器件,电路板,或套件的下拉框中选择或在按名称搜索区域输入关键词来找到您选择的设备。

•一旦选定设备,选择用引脚工具在引脚工具中打开设备配置,或用时钟工具选择在时钟工具中打开设备配置。

您可以在两种工具中切换Figure 1.选择开发板Contents 1简介.................................................12启动 MCUXpresso 配置工具...........13引脚工具..........................................24时钟工具..........................................25生成源代码.. (3)MCUXWQSMCUXpresso 配置工具的快速入门指南 (网络版)Rev. 1 — 1/2021User's Guide所有的工具设置会被保存于配置中。

3引脚工具引脚工具允许显示和配置处理器的引脚。

可在引脚、外设信号或封装视图中完成基本配置。

可在路由引脚视图中调整更高级的设置(引脚电气功能)。

Figure 2.引脚工具4时钟工具时钟工具允许在时钟表视图中显示和更改时钟源以及输出设置。

可通过时钟显示图和详情视图调整更高级的设置。

可在时钟表,时钟显示图,和详情视图中更改时钟环境全局设置,例如运行模式、MCG 模式和 SCG 模式。

Figure 3.时钟工具5生成源代码在主菜单中,选择视图 > 源代码来打开源代码界面以查看生成的源代码。

Datacard Secure ID Solutions产品介绍说明书

TRUST THE EXPERTSIN SECURE IDENTIFICATIONPROTECT THE PEOPLE AND PLACES THAT MATTER MOSTThink about all the people who interact with your organization every day.Employees, customers, students, visitors — all of them are vital to your success. Equally critical is a secure environment. One that protects your stakeholders, facilities and data from a wide range of threats.Secure ID solutions from Datacard Group can help you increase security in any organization around the world. No other manufacturer offers a wider range of fully integrated solutions.This flexibility is critical. Because for small businesses, a secure ID solution may involve name-and-photo IDs, while schools and universities may require magnetic stripes that integrate with access control. Corporations and government agencies often need highly secure IDs with holographic laminates, and retailers may want to add a photo or digital signature to gift and loyalty cards.Datacard Group offers secure ID solutions to meet your needs and fit your budget.FLEXIBLE CHOICES FOR IMPROVING SECURITYDatacard Group offers one of the broadest portfolios of secure ID solutions available today. Whether you are printing your first ID cards, creating IDs for new facilities or employees, or enhancing your current cards with the latest technologies, we can provide exactly what you need.The key is versatility. We design and test the components of our solutions to work together in many different combinations. That means you can mix-and-match software, capture systems, card printers and other elements in a unique configuration that aligns perfectly with your top priorities.FROM A WORLD LEADER IN SECURE ID SOLUTIONSUnlike other manufacturers, Datacard Group specializes in end-to-endsolutions for secure IDs. Customers around the world insist on the Datacard ®brand because our solutions incorporate advanced technology to solve critical issues in many markets. We also continuously develop innovative features that increase durability, speed and output quality. The end result is exceptional customer satisfaction.Here are the steps your organization can take to create the right secure IDs.Datacard Group sales channels offer all of the products described here — and much more.1. Power Up Your Identification Software Identification software is where it all begins. This application enables you to customize card designs, manage cardholder images and related data, and print custom reports.2. Capture Images and Biometrics Use a digital camera to photograph the cardholder. Capture the cardholder’s fingerprint image and/or other biometrics, and record a digital signature.3. Print CardsAfter data capture, a desktop card printer prints the card in a single color, full-color or rewritable pixels. It may also encode the magnetic stripe or smart card chip.4. Reload SuppliesHigh-quality color ribbons, topcoats and laminates help ensure exceptional image quality, consistency and security.Periodically, you will need to replace supplies as they are consumed.5. Receive Professional Service Whether you work with Datacard SM Global Services directly or with one of the skilled dealers or distributors in our extensive service network, you will gain access to a team with the expertise and experience required to optimize performance.CRITICAL ISSUES TO ADDRESS• Design:One- or two-sided? One-color or full-color? Photos and/or logos?• Functionality:Visual identification or machine-readable authentication?• Environment:Average ID life span, daily usage, physical threats?• Demand:Volume of IDs,centralized/distributed production, growth plans?• Security:Access control integration,biometrics, sophisticated laminates?• Information:Data types, centralized database, secure Web access?HOW TO BUILD A MORE S ECURE ENVIRONMENTCREATE THE RIGHT CARD SOLUTIONS FOR YOUR ENVIRONMENTSecure ID cards can be used in a diverse number of ways. That is why Datacard ®secure ID solutions aredesigned to accommodate a broad array of needs across multiple markets and applications. Regardless of your specific needs, you can expect seamless compatibility, outstanding reliability and superior value. Plus, theseproducts can be integrated with an even wider range of third-party offerings for highly specialized applications.1. VI S UAL IDENTIFICATION S OLUTION• Essential car d d esi g n software • Mi d - to hi g h-volume car d p rintin g IDEAL FOR :• Retail • Gift car d s • Loyalty car d s • S tore d value• Time-an d -atten d ance • C asinos2. TRAN S ACTIONAL S OLUTION• S ecure ima g e ca p ture • Biometric ca p ture• C ar d p rintin g an d security laminate a pp lication • S o p histicate d ID software IDEAL FOR :• Government• National ID p ro g rams • Driverís license p ro g rams • Hi g h-tech cor p orations • Universities4. ADVANCED S ECURITY S OLUTION• Professional ima g e ca p ture • Hi g h-quality car d p rintin g • A d vance d ID software IDEAL FOR :• C or p orations• Hos p itals/healthcare • Visitor mana g ement • Universities3. ACCE SS CONTROL S OLUTION• Basic ima g e ca p ture • Low-volume car d p rintin g • Entry-level ID software IDEAL FOR :• S taff IDs • E d ucation • Health clubs• Membershi p or g anizationsS ecure IDs for ACCE SS CONTROL, which allowem p loyees an d visitors to enter facilities or lo g in to networks, may inclu d e:• Proximity car d s that utilize an embe dd e d ra d io frequency i d entification (RFID) trans p on d er• Magnetic stri p e enco d in g that su pp orts car d -swi p e systemsFor ADVANCED S ECURITY a pp lications, secure IDs require the most so p histicate d features available:• Printe d finger p rint image for p erceive d security • S tore d fin g er p rint minutia or other im p ossible-to-re p licate b iometrics• Datacar d ® DuraGar d ® virtual e dg e-to-e dg e security laminates with holo g ra p hic ima g es, micro p rintin g , g uilloche p atterns an d other o p tical variable d evices (OVDs)• Ultraviolet fluorescent p rintin gFor basic VI S UAL IDENTIFICATION , you can use:• Brilliant color p hotos • Logos an d other gra p hics • C ar d hol d er signature• Tam p er-evi d ent ghost imagesS ecure car d s can store d ata to su pp ort e-p urse, time- an d -atten d ance an d other TRAN S ACTIONAL systems with:• S cannable b ar co d es • Enco d e d magnetic stri p es• C ontact or contactless smart car d s p ersonalize d with machine-rea d able d ataThese offerin g s make it sim p le to ca p ture car d hol d er ima g es an d biometrics with exce p tional efficiency.Datacar d ® Tru ™ Photo Intro solutionFor low-volume, manual ima g e ca p ture an d cro pp in g Datacar d ® Tru ™ Photo solution For automate d one-click ca p ture an d cro pp in g Datacar d ®Tru ™Photo Professional solution For automate d hi g h-quality ima g e ca p ture an d cro pp in gDatacar d ® Tru ™ S ignature solution C a p tures an d stores d i g ital si g natures Datacar d ® Tru ™ Finger p rint solutionC a p tures fin g er p rint ima g es an d /or minutiaEA S Y IMAGE AND BIOMETRIC CAPTUREOur versatile, easy-to-use software fits virtually any user environment.Datacar d ® ID Works ® i d entification software This flexi b le, p owerful p latform comes in four unique versions: • ID Works Intro for entry-level ID car d s• ID Works Basic for essential car d d esi g n an d p rintin g • ID Works S tan d ar d for a d vance d car d d esi g n an d d atabase mana g ement• ID Works Enter p rise for so p histicate d security, biometrics an d smart car d a pp licationsDatacar d ® ID Works ® Visitor Manager solutionS cans g overnment-a pp rove d cre d entials an d p rints secure IDs for fast visitor enrollmentU S ER-FRIENDLY IDENTIFICATION S OFTWAREDatacar d car d p rinters d eliver outstan d in g ima g e quality, reliabilityan d versatility.Datacar d ® S P 25 Plus car d p rinterAffor d able full-color or rewritable car d s for manual-fee d a pp lications Datacar d ® S P35 Plus car d p rinter Easy-to-use p rinter for one-si d e d color car d s Datacar d ®S P55 Plus car d p rinter Fast p rint s p ee d s for one- or two-si d e d color car d sDatacar d ® S P75 Plus car d p rinterPro d uces hi g hly secure IDs an d a pp lies virtual e dg e-to-e dg e laminates Datacar d ® RP90 Plus car d p rinterUses retransfer technolo g y to p rint on heavy-d uty com p osite car d sPOWERFUL, VER S ATILE CARD PRINTER SDatacar d ® Certifie d S u pp lies featurin g Intelli g ent S u pp lies Technolo g y ™hel p ensure su p erior ima g e quality, consistent car d p rintin g an d outstan d in g p erformance. They incor p orate p atente d RFID technolo g y, which allows Datacar d car d p rinters to reco g nize when the su pp lies are installe d , automatically a d just settin g s an d track consum p tion. Datacar d ® DuraGar d ® virtual e d ge-to-e d ge security laminates feature stan d ar d an d customize d o p tical variable d evices (OVDs), inclu d in g holo g ra p hic artwork, micro p rintin g , g uilloche p atterns, laser retrievable covert text an d color shift ink. These exclusive su pp ly items si g nificantly im p rove car d security an d d urability.Datacar d S M Glo b al S ervices an d our extensive network of service ex p erts s p ecialize in hel p in g or g anizations of all kin d s p lan an dim p lement successful secure ID p ro g rams. These d e d icate d ex p erts can work with you to accelerate d e p loyment, resolve common issues an d fine-tune p rocesses.HIGH-QUALITY S UPPLIE S AND DEDICATED S ERVICE STHE INDUSTRY’S BEST-SELLING SECURE ID SOLUTIONSDatacard secure ID solutions include everything you need to build a more secure environment for your organization. Because they are engineered to work together seamlessly, Datacard secure ID solutions provide outstanding uptime and proven long-term reliability. So you can protect your people and facilities — as well as your technology investment.CONVENIENT DESIGN, EXCELLENT EASE OF USEConvenient card printingThe SP35 Plus card printer is designed for easy operationand er-friendly features include:• A printer driver that provides message prompts,recovery instructions,color image previews and online user help• Driver support for Microsoft®Windows®2000,XP and Windows Vista®operating systems • Quick-change supplies• Operator-replaceable printheads • Front-facing input andoutput card hoppers• Small,efficient design• Continuous card cleaning The Datacard®SP35 Plus card printer delivers everything you need to print vivid, one-sided cards. With its productive print speed, superb image quality and easy operation, this convenient printer is ideal for issuing education, healthcare and staff IDs — and more.•Exceptional productivity.The SP35 Plus card printer personalizes up to 160 full-color cards or 750 one-color cards per hour. This printer is also extremely light and portable, weighing only nine pounds. Its sleek design and compact size make it a welcome addition to any desktop.• Superb edge-to-edge imaging. The SP35 Plus card printer leverages Advanced Imaging Technology™to produce vivid and vibrant full- or one-color photos, graphics and text across the entire card surface. This exclusive technology uses optimized print ribbons and user-adjustable controls to yield smooth, uniform and solid backgrounds, improved color matching with image capture devices, enhanced bar code printing and sharp reproduction of edges and fine text.• Multiple options and capabilities.In addition to standard bar code printing, the SP35 Plus card printer gives you the option to integrate magnetic stripe encoding and smart card personalization with a factory option or simple field upgrade. So, you can purchase these printers with confidence, knowing you can upgrade your card printing capabilities at any time.DATACARD®SP35 PLUS CARD PRINTER11111Bren Road WestMinnetonka, MN 55343-9015+1 952 Plus card printer offers an ideal mix of convenience and simplicity in an attractive,Datacard, Intelligent Supplies Technology and Advanced Imaging Technology are registered trademarks, trademarks and/or service marks of DataCard Corporation in the United States and/or other countries. Microsoft, Windows, and Windows Vista are registered trademarks of MicrosoftCorporation. Names and logos on sample cards are fictitious. Any similarity to actual names, trademarks or tradenames is coincidental.©2007-2008 DataCard Corporation. All rights reserved.Specifications subject to change without er-friendly operationAudible and visual message prompts Electrical requirements 100/120V,www.ID (800) 321-4405。

电子密码锁中英文对照外文翻译文献

电子密码锁中英文对照外文翻译文献This article discusses the design of a matrix keyboard and LCD display based on a microcontroller unit (MCU) for use in electronic password locks。

The keyboard and display are crucial components of the lock。

allowing users to input their password and receive feedback on the lock's status。

The design includes a 4x4 matrix keyboard and a 16x2 LCD display。

both of which are controlled by the MCU。

The article provides a detailed n of the design process。

including the hardware and are components。

and XXX.nXXX and electronic components to provide users with access control。

One key component of these locks is the keyboard and display。

which allow users to input their password and receive feedback on the lock's status。

In this article。

we will discuss the design of a matrix keyboard and LCD display based on an MCU for use in electronic password locks.DesignThe design of the matrix keyboard and LCD display is based on an MCU。

斯普锐SE3102N系列二维码识读引擎集成手册说明书

SE3102N Embedded 2D Barcode Scan Engine Intergration guideSE3102N 系列二维码识读引擎集成手册苏州斯普锐智能系统有限公司Email:*******************Tel: 400-850-8151目录目录Disclaimer免责声明 (3)Revision History版本记录 (4)Chapter 1 Introduction介绍 (5)1.1Product Overview 产品概述 (5)1.2Illumination 照明指示 (5)Chapter 2 Installation安装 (6)2.1General Requirements 一般要求 (6)2.1.1 ESD 静电保护 (6)2.1.2 Dust and Dirt 防尘防污 (6)2.1.3 Ambient Environment 环境 (6)2.1.4Thermal Considerations 散热考虑 (6)2.1.5 Installation Orientation安装朝向 (7)2.2Optics 光学相关 (7)2.2.1 Window Placement 窗口放置 (7)2.2.2Window Material and Color 窗口材质与颜色 (8)2.2.3Scratch Resistance and Coating 窗口防刮与涂层 (8)2.2.4Window Size窗口尺寸 (8)2.2.5Ambient Light 环境光 (10)2.2.6 Eye Safety 人眼安全 (10)2.2.7Mounting 装嵌 (10)Chapter 3 Electrical Specifications电气特性 (12)3.1Power Supply 电源要求 (12)3.2Ripple Noise纹波噪声 (12)3.3 DC Characteristics 直流特性 (12)3.3.1Operating Voltage 工作电压 (12)3.3.2Current 电流 (13)Chapter 4Interfaces接口 (14)4.1Host Interface Connector主机接口连接器 (15)4.2Flat Flexible Cable扁平柔性电缆 (15)4.3Communication Interfaces通讯接口 (16)4.4Control Interfaces 控制接口 (16)4.4.1 Trigger 触发 (16)4.4.2Beeper 蜂鸣器信号 (17)4.4.3 Decode LED 解码 LED信号 (18)4.4.4 SE3102N engine datasheet 引擎数据表 (19)Disclaimer免责声明2014 Suzhou SuperMax Smart System Co., Ltd. All rights reserved.苏州斯普锐智能系统有限公司对本声明拥有最终解释权。

10-tips-for-successful-scan-design-part-one

10 tips for successful scan design: part oneKen Jaramillo - February 17, 2000Although scan-design methodologies have existed for several years, many companies are just starting to explore the use of scan, particularly as these companies create more complex, system-o--chip (SOC) designs. With gate counts increasing at an enormous rate, producing high-fault-coverage production tests without using scan techniques becomes increasingly difficult. Scan is becoming a necessary design methodology to produce high-quality chips.If you're just starting out in scan design, this two-part series provides useful design tips to ensure successful adoption of scan-design methodologies within your company or design group. Part one reviews the scan methodology and techniques. Part two presents the tips. By adhering to these tips, you can produce chips that current automatic-test-pattern-generation (ATPG) tools can process to generate scan-based test vectors providing high fault coverage.Before starting your project, research scan-design methodologies and read as much as you can. In addition to this series, references 1 and 2 are great introductions to scan. (You can also download "Simple case study." ) Don't expect just the "scan expert" of the project to learn scan techniques. Get everyone involved. The more the designers know, the easier it is for them to produce scan-friendly designs. (See sidebar "Glossary" for a list of definitions and acronyms.)Also, don't underestimate the amount of time it takes to produce a scan design. If your company is just starting out, scan design will require a large amount of time. You may encounter many pitfalls and unexpected problems. Your managers may want to send the chip to the fab without allowing you much time to simulate the test patterns produced by the ATPG tools. But if you don't run back-annotated simulations of the test patterns, then don't expect the patterns to work. These simulations will alert you to timing problems, tool problems, and functional problems.Why is scan important?Designers create functional simulations to verify the proper operation of their designs. For example, a designer of a memory controller creates simulations to verify that the design operates correctly within the system. This approach is fine for the virtual world, in which the chip is only bits and pieces of HDL coding. However, you ultimately want to manufacturer a real chip and verify that it works properly. Production tests can verify that the manufacturer correctly implemented the design and that the design is free from flaws, such as power and ground shorts, open interconnections due to dust particles, and others. In short, production testing ensures that the customer receives high-quality parts with low failure rates.In the past, you could use functional simulations to generate test vectors, which you could then useto verify newly manufactured chips on a tester. But because of the high gate counts and extreme complexity of today's SOC designs, these production-test techniques are quickly running out of steam. You can still use functional simulations to verify the operation of a design, but producing enough simulations to provide high fault coverage is becoming more difficult. For example, consider a 500,000-gate design that contains an embedded ARM processor, an embedded DSP µP, a complex memory controller, and several high-gate-count peripherals. Although design teams can produce enough functional simulations to verify the chip, these functional simulations would probably provide only about 80% fault coverage if you used them to produce production-test vectors. The amount of effort necessary to create additional simulations that result in high fault coverage, 95% for example, would be difficult and time consuming.With the advent of scan-design techniques and ATPG tools, however, you can take this same design and quickly produce several thousand production-test vectors that provide high fault coverage. The use of scan-design techniques simplifies the problem of test-pattern generation by reducing the design, or sections of a design, into purely combinational logic. Then you can make use of fast and efficient algorithms in ATPG tools—algorithms that the tool designer developed for combinational logic—to generate high-fault-coverage vectors.What is scan?The goal of any production-testing scheme is to verify that the chip is manufactured correctly. Consider the simple circuit in Figure 1. If you want to verify that node A is not stuck at 0, due to a manufacturing flaw that shorts this node to ground, you can create the vector (A=1, B=0, C=0). Setting B and C low allows modifications of A to directly control the output at D. If A is stuck at 0, then D will be 0, no matter what value drives A. Similarly, you can create other vectors to verify that each node is not stuck high or low. You can manually create these simple test vectors with little effort. However, if the design is complicated and contains thousands of flip-flops and hundreds of thousands of combinational logic gates, manually creating these test vectors is laborious.The use of scan-design techniques allows you to use all of the flip-flops in a design as a big shift register during scan testing. Thus, you can shift patterns into the chip, for example to drive the inputs of Figure 1's circuit with A=1, B=0, and C=0. The flip-flops capture the functional data that results from the test pattern, for example to capture the value at D, which is 1, and you can shift out the results. This internal scan increases the controllability and observability of internal nodes by connecting storage cells into a long shift register, or scan chain, and by enhancing the logic of these cells to support a scan-shift mode that allows for serial loading and unloading of scan chain's contents.In normal operational mode, the scan chain does not affect system operation. When you select scan mode, however, the outputs of each storage cell in the scan design become primary inputs to the combinational logic, which increases controllability. The inputs of each scan storage cell allow registering of the outputs of the combinational logic, which increases observability. ATPG tools are proficient at generating test patterns to provide high fault coverage for combinational logic. Scan allows the tools to have easy access to all the combinational logic in the design.Figure 2a shows a simple circuit without any scan circuitry. The circuit contains three flip-flops and some combinational logic. This circuit could represent a simple state machine with a registered output. You add scan to this design to create the design in Figure 2b. You need to add only three additional pins, or pads, for scan testing: a scan-input pin for serial data input, a scan-output pin for serial data output, and a scan-enable pin for scan-mode control. This design shares the scan clock with the system clock. You can often use multiplexers to combine these pads with system-operation pads, which reduces the I/O overhead. This example forms a serial scan chain from the scan-inputpad, connecting each flip-flop into a scan register that is 3 bits long. The output of the final flip-flop connects to the scan-output pad. Each of the flip-flops in Figure 2b is now a flip-flop with a multiplexed input. The scan-enable signal selects between the normal functional-data input, which comes from the combinational-logic clouds, and the scan data, which comes from the scan input or the previous flip-flop. The scan-chain ordering is from flip-flop 1 to flip-flop 3.Figure 3 illustrates the timing for scan testing of Figure 2b's circuit. The timing sequence consists of three stages: first scan mode, then normal system mode, then scan mode again. Scan enable=1 selects the scan mode, during which data serially loads into the scan chain from the scan-input signal. When the scan chain is fully loaded, which requires one scan clock for each storage cell in the scan chain, scan enable=0 selects the normal system mode. In this mode, the system applies one system clock, applies data at the primary inputs of the chip, and observes data at the primary outputs of the chip. This procedure captures data from the combinational-logic elements of the design into the scan-storage cells. The system asserts and deasserts the scan-enable signal on the falling edge of the clock, which helps ease timing, especially the hold-time constraints. In the last and third part of the sequence, the system again selects scan mode with scan enable=1 and uses the scan clock to unload the scan chain through the scan output. The tester then checks this output data against expected values. While captured data shifts out of the scan chain, the system can load input data from the next scan-test pattern into the scan chain.Figure 4 shows a circuit with two clock domains and with the scan circuit in place. The upper portion of the figure shows clock domain 1 using clk1 and consists of two flip-flops and some combinational logic. The bottom portion of the figure shows clock domain 2 using clk2; it consists of three flip-flops and some combinational logic. You can think of the circuit as two state machines with a shared communication signal, A, that flip-flop 5 synchronizes to clk2. This example includes two scan chains, one for each clock domain. The first scan chain starts with scan input 1 going through flip-flops 1 and 2 to scan output 1. The second scan chain starts with scan input 2 going through flip-flops 3, 4, and 5 to scan output 2. The circuit has only one scan-enable signal, even though there are two scan chains. Because the two scan chains interact—via the functional path from flip-flop 1 toflip- flop 5—you have to be careful when you assert the clocks during the capture cycle, or you could end up with a hold-time violation at flip-flop 5.Figure 5 illustrates the timing for scan testing of this circuit. Similar to the timing diagram in Figure 3, this sequence has three stages. During scan mode, when scan enable=1, data loads serially into the scan chains from scan input 1 and scan input 2. Each of the two scan chains loads in parallel. The length of the longest scan chain determines the length of the scan-shift operation. Scan chain 2 is three flip-flops long. Therefore, the scan-shift operation takes three clocks. Scan chain 1 is only two flip-flops long. However, you can still shift three data values into this chain as long as the first value is a "don't care."As in Figure 3, when the scan chains are loaded, scan enable=0 selects normal mode: The system applies one clock, applies data at the primary inputs of the chip, and observes the data at the primary outputs of the chip. As before, this action captures data from the combination-logic elements of the design into the scan-storage cells. However, the capture cycle in Figure 5 differs from the cycle in Figure 3, which has only one clock domain. Because two clock domains exist and interact, the capture cycle must stagger the assertion of the clocks. Staggering the clocks prevents any timing problems with the data crossing the clock domains. The capture cycle first clocks data into scan chain 1, at the first clock after scan enable goes low, to capture data into the clk1-based flops. The capture cycle then clocks data into scan chain 2, at the second clock after scan enable goes low, to capture data into the clk2 based flops. After capture data latches into the flip-flops on scan chain 1, the functional input to flip-flop 5 of the second scan chain will change. Only sequential-based ATPG tools can handle this situation. Purely combinational-based ATPG tools cannot. If you're using a combinational ATPG tool, you should tell the tool to assert only one of the clocks during the capture cycle. The tool then asserts clk1 or clk2 only during the capture cycle, which results in a higher number of patterns for the same level of fault coverage.Finally, the cycle again selects scan mode, and the system uses the scan clocks to unload the scan chains through the scan-output pins. While capture data shifts out of the scan chains, input data from the next scan-test pattern can begin loading. Note that Figure 5 shows the first cycle of the shift.Scan techniques and elementsAll of the examples so far use flip-flops with multiplexed inputs for the scan-storage elements. These multiplexed flip-flops are only one type of scan-storage element. The other types of scan elements are clocked scan elements and level-sensitive-scan-design (LSSD) elements. Each type of scan element provides its own benefits. Multiplexed flip-flop and clocked-scan techniques are better suited for designs that contain edge-triggered flip-flops. LSSD techniques are better suited for latch-based designs. The type of scan element you decide to use depends on your design and your ASIC vendor. The examples in this article use the multiplexed flip-flop technique.A multiplexed flip-flop scan element contains a single D-type flip-flop with multiplexed inputs that allows selection of either normal functional data or scan- input data. Figure 6a shows a multiplexed flip-flop scan element. In normal mode (scan enable=0), the system data, or functional input, goes through to the flip-flop, which registers the data. In scan mode (scan enable=1), scan data goes through to the flip-flop so that the flip-flop registers the scan data.Clocked-scan elements are similar to multiplexed flip-flop elements but use a dedicated test clock to register scan data into the flip-flop (Figure 6b). During normal operation, the system clock registers the system data at the functional input into the flip-flop. During scan mode, the scan clock registers the scan data into the flip-flop.LSSD uses three independent clocks to capture data into the two latches within the scan cell (Figure 6c). During normal mode, the master latch uses the system clock to latch system data at the functional input and to output this data to the normal functional-data output path. During scan mode, the two scan clocks control the latching of data through the master and slave latches to generate the data at the scan output.Lockup latchesScan chains are vulnerable to clock-skew problems for two main reasons. The first reason has to do with layout and propagation delay. The same clock may drive hundreds or thousands of scan-storage cells with no circuitry between them. Logically adjacent storage cells in the scan chain may be physically separated in the layout. Clock skew between successive scan-storage cells must be less than the propagation delay between the scan output of the first storage cell and the scan input of the next storage cell. Otherwise, data slippage may occur. Thus, data that latches into the first scan cell also latches into the second scan cell. This situation results in an error because the second scan cell should latch the first scan cell's "old" data rather than its "new" data. Figure 7 demonstrates that the path delay for the data is less than that of the clock. Thus, the "new" data at Da passes all the way through to Dd in one clock period. The second flip-flop should have latched the "old" value at Dc (a logic high) rather than the "new" value.The second reason for clock skew is that clock domains separate the scan chains. For example, allthe flip-flops from the clk1 clock domain in Figure 4 are linked in the same scan chain. Likewise all the flip-flops from the clk2 clock domain form a second scan chain. If you want to link these two scan chains to form a single scan chain, timing problems could result. Two clock trees generate the two clocks, which introduces some amount of skew between the two clocks. You cannot link the two scan chains unless you handle this clock-skew problem. The timing for this scenario would be very much the same as that in Figure 7 except there would be two separate clocks rather than a single clock. Lockup latches are nothing more than transparent latches. You use them to connect two scan-storage elements in a scan chain in which excessive clock skew exists. Figure 8 illustrates the use of lockup latches. The circuit contains two flip-flops. Flip-flop 1 represents the end of the scan chain that contains only elements that are in the clk1 clock domain. Flip-flop 2 represents the beginning of the scan chain that contains only elements that are in the clk2 clock domain. Although the figure doesn't show it, these flip-flops have multiplexed inputs. The inputs of these flip-flops represent the scan inputs of the multiplexers. The latch has an active-high enable, which becomes transparent only when clk1 goes low and effectively adds a half clock of hold time to the output of flip-flop 1. In this figure, you assume that the system synchronously asserts clk1 and clk2, which would be the normal case during scan-mode operation. Although the clocks synchronously assert, some amount of clock skew between them still exists because they come from different clock trees.Figure 8 shows the use of lockup latches to connect scan chains from different clock domains. However, you can just as easily use these latches to connect scan chains from various blocks within a chip that, although on the same scan chain, are physically remote from each other on the die. You want to make the latch transparent during the inactive part of the clock. For example, both flip-flops in Figure 8 trigger on the rising edge of the clock. Therefore, you want to make the lockup latch transparent during the low period of the clock. If the flip-flops trigger on the falling edge of the clock, you want the latch to be transparent when the clock is high.Author infoKen Jaramillo is a principal engineer at Philips Semiconductors, where he has worked for four years. He has worked as designer and architect of ASICs, FPGAs, and boards for products including avionics, high-speed serial buses, high-performance gaming platforms, PCI-bus-related products, high-performance PC audio, and high-speed networking products. He has a BSEE from the University of Missouri (Kansas City) and a BSCE from the University of Missouri (Columbia).Subbu Meiyappan is a senior design engineer at VLSI Technology, a subsidiary of Philips Semiconductors. He has worked for the company for three years, designing, developing, synthesizing, simulating, and validating high-performance intellectual-property blocks for PCI, ARM-ASB-based devices, and high-performance ASICs. He has a BE from Annamalai University (Annamalai Nagar, India) and an MS from Tennessee Technological University (Cookeville, TN).REFERENCE1. Scan Synthesis User Guide, Synopsys, .2. ASIC/IC Design-for-Test Process Guide, Mentor Graphics, .。

芯片失效分析系统Avalon软件系统说明书

DATASHEET Overview Avalon software system is the next-generation CAD navigation standard for failure analysis, design debug and low-yield analysis. Avalon is a power packed product with tools, features, options and networking capability that provides a complete system for fast, efficient and accurate investigation of inspection, test and analysis jobs. Avalon optimizes the equipment and personnel resources of design and semiconductor failure analysis (FA) labs by providing an easy-to-use software interface and navigation capabilities for almost every type of test and analytical failure analysis equipment.Avalon enables closer collaboration of product and design groups with FA labs, dramatically improving time to yield and market. Avalon can import CAD design data from all key design tools and several user-proprietary formats while providing visual representations of circuits that can be annotated, exploded, searched and linked with ease.Benefits • Improves failure analysis productivity through a common software platform for various FA equipment • Significantly decreases time to market with reduced FA cycle time • Faster problem solving by cross-mapping between device nodes to view all three design domains (layout, netlist and schematic) simultaneously • Increases accuracy of FA root cause analysis using advanced debug tools • Single application that overlays images from various FA equipment on to design layout • Secure access to all FA information using KDB™ database • Design independent system that supports all major layout versus schematic (LVS)• Complete access to all debug tools critical to failure trace, circuit debug and killer defect source analysis • Simple deployment setup with support for Linux and Windows • Seamless integration with legacy Camelot™ and Merlin™ databases • Ease of conversion for layout, netlist and schematic data and establishes cross-mapping links between each data entityCAD Navigation andDebug Solutions forFailure AnalysisAvalonFigure 1: Avalon CAD-navigation system integrating layout, signal tracing and 3D viewSupporting all CAD Design DataSynopsys is committed to being the leading provider of software solutions that links all CAD design data. Avalon is a comprehensive package that reads all EDA tools and design data from verification systems and several user-proprietary formats. The KDB™database is designed to interface with all key design formats.Today, there are more EDA developers and more verification package choices; Synopsys is the only company thatsupports all of them.• LVS Conversions: Cadence (Assura, DIVA), Mentor Graphics (CheckMate, Calibre), Synopsys (Hercules, ICV)• Netlist Conversion: SPICE, EDIF, OpenAccess• Layout Conversion: GDSII, OASIS®The highest priorities for Avalon users are faster data accessibility, support diverse failure analysis equipment and availability of debug tools. Avalon provides the optimal solution for both small and continually-expanding FA labs and design debug teams. The Avalon database is design independent and offers a superior level of data consistency and security. The unique design of the internal database schema guarantees compatibility with decades-old databases. This is an indispensable feature for all failure analysis, QAand manufacturing organizations especially in the automotive industry.Figure 2: Avalon SchemView and NetView provide an easy way to navigate inside circuit schematicsProviding Critical Analysis FunctionsIn addition to its CAD navigation and database capabilities, Avalon’s analysis features have become indispensable to the FA lab. Different viewing options are critical in tracking potential failures and determining the source and origin of killer defects. Avalon includes special schematic capabilities and layout features that are invaluable to FA engineers as they debug chips manufactured using new processes.Avalon View Only Client consists of maskview, netview, schemview, i-schemview, K-EDIT, defect wafermap and 3D-SAA. The list below details some of the most commonly used applications.Defect Wafer Map integrates defect inspection data with the device CAD design using the defect coordinates to navigate an equipment stage and pinpoint the defect for closer inspection and characterization. Avalon sorts defects by size, location or class, as well as layout location and allows the user to define custom wafer maps. Additionally, users can classify defects, attach images and write updated information to the defect files.Figure 3: Defect Wafer Map pinpoints defects for closer inspectionSchemView provides tracking of potential failures through visualization of the chip logic. Cross-mapping of nets and instances to the device layout and netlist, SchemView helps determine the source and origin of chip failures. SchemView helps determine the source and origin of chip failures. The entire design is displayed in cell hierarchy format, allowing push-down to a transistor level.Figure 4: K-Edit allows collaboration between design, fab and labI-Schem (Interactive Schematic) creates a schematic from a netlist in a net-oriented format allowing forward and backward tracking to locate a fault. Features like Add Driver or Add Input Cone allow for quick analysis and verification of diagnostic resultsin scan chains.Figure 5: I-Schem creates a schematic from a netlistK-Bitmap allows equipment CAD navigation when analyzing memory chips by identifying the physical location of failingmemory cells. It eliminates tedious screen counting by converting the logical addresses, or row and column coordinates, to thephysical location.Figure 6: K-Bitmap identifies the physical location of bit addresses in memory devices3D Small-Area Analysis provides a three-dimensional cross- section capability to FA engineers, enabling faster localization of circuit failures to accelerate IC manufacturing yield improvement.Figure 7: 3D Small-Area Analysis enables faster localization of circuit failuresHot-Spot Analyzer allows user to draw regions on the layout that correspond to hot-spot regions (emission spots) to detect the crucial nets. It finds the nets in each hot-spot region and plots a pareto graph of nets crossing one or more hotspots which helps to easily locate the killer net.Figure 8: Hot-Spot Analyzer displays number of nets in a hot spotUser-Defined Online Search (UDOS) allows users to search a small area of a die for unique polygon features, repeated features or lack of features. Applications include, but are not limited to, FIB-able regions, repeaters, pattern fidelity and lithographic applications.Figure 9: User-Defined Online Search (UDOS) finds easy-to-access tracesPassive Voltage Contrast Checker (PVC) quickly and accurately validates the integrity of a circuit’s conductivity and provides detailed information for identifying suspect faults at via or metal tracesFigure 10: Passive Voltage Contrast (PVC) Checker identifies suspect vias or metal tracesElectronic Virtual Layer marks objects to represent net connectivity during a FIB deposit or cut using KEdit. The online trace will simulate the new connectivity to the virtual layer. PVC checker could be used on this virtual layer to simulate the crack or short.Check Adjacent Nets allows logical analysis of nets. This command line tool finds the adjacent nets which are within user-specified threshold distance to find shorts.Export Partial Layout enables the customer to share partial layout data with service labs without compromising the IP of the product.Image Mapper automates the image alignment process in Avalon Maskview and saves a lot of time and effort spent inmanual alignment.Advanced 3D Viewer displays real time 3D view of the selected layout area. It shows each process step in the 3D view for which it uses the process data along with design data. It zooms into smaller details and helps to minimize unintended consequences during FIB cuts due to underneath high density structure.Avalon SolutionAvalon brings all the advantages of enterprise-wide computing for FA of the chip. Avalon is an open architecture system that connects users over local and wide area networks for seamless integration and database sharing. Instrument integration throughout the fab and other locations throughout the enterprise enables viewing, modifying, characterizing and testing the same wafer location with different instruments, or the same location on wafers at different facilities using the same chip design.Figure 11: Avalon’s open architecture integrates with Synopsys’ Yield ExplorerIC DesignToolsFigure 12: Avalon server solutionComprehensive Library of FA Tool DriversAvalon provides navigation with almost every equipment used in the FA lab. With a continued commitment to support drivers for all types of test and analysis equipment, Synopsys will continue to develop driver interfaces for new tools as they are introduced to the market, as well as the next generation of existing tools.Equipment Supported by Avalon• Analytical Probe Stations• Atomic Force Microscopes• E-Beam Probers• IR Imaging• Mechanical Stage Controllers• Emission Microscopes• Microanalysis Systems• FIB Workstation• Laser Voltage Probe• LSM• EDA LVS• Microchemical Lasers• OBIC Instruments• Optical Review• SEM Tools• Photon Emission Microscopes• Laser Scan Microscopes©2018 Synopsys, Inc. All rights reserved. Synopsys is a trademark of Synopsys, Inc. in the United States and other countries. A list of Synopsys trademarks isavailable at /copyright.html . All other names mentioned herein are trademarks or registered trademarks of their respective owners.。

阿特美 AT97SC3204 信任平台模块数据手册摘要说明书

This is a summary document. The complete document is available under NDA. For more information, please contact your local Atmel sales office. Features●Fully compliant to the Trusted Computing Group (TCG) Trusted Platform Module(TPM) version 1.2 specification●Compliant with TCG PC client-specific TPM Interface Specification (TIS) version 1.2●Single-chip, turnkey solution●Hardware asymmetric crypto engine●Atmel® AVR® RISC microprocessor●Internal EEPROM storage for RSA keys●33MHz Low Pin Count (LPC) bus for easy PC interface●Secure hardware and firmware design and chip layout●Internal, high-quality Random Number Generator (RNG) – FIPS 140-2 compliant●NV storage space for 1756 bytes of user defined data● 3.3V supply voltage●28-lead thin TSSOP, 28-lead wide TSSOP, or 40-pad QFN packages●Offered in both commercial (0 to 70°C) and industrial (-40 to +85°C)temperature rangesDescriptionThe Atmel AT97SC3204 is a fully integrated security module designed to be integrated into personal computers and other embedded systems. It implements version 1.2 of the Trusted Computing Group (TCG) specification for Trusted Platform Modules (TPM).The TPM includes a cryptographic accelerator capable of computing a 2048-bit RSA signature in 200ms and a 1024-bit RSA signature in 40ms. Performance of the SHA-1 accelerator is 20μs per 64-byte block.The chip communicates with the PC through the LPC interface. The TPM supports SIRQ (for interrupts) and CLKRUN to permit clock stopping for power savings in mobile computers.Atmel AT97SC3204Trusted Platform Module LPC InterfaceSUMMARY DATASHEET1.Pin Configurations and PinoutsTable 1-1.Pin ConfigurationsTable 1-2.Pinouts2.Block DiagramThe TPM includes a hardware random number generator, including a FIPS-approved Pseudo Random NumberGenerator that is used for key generation and TCG protocol functions. The RNG is also available to the system togenerate random numbers that may be needed during normal operation.The chip uses a dynamic internal memory management scheme to store multiple RSA keys. Other than the standard TCG commands (TPM_FlushSpecific, TPM_Loadkey2), no system intervention is required to manage this internal key cache.The TPM is offered to OEM and ODM manufacturers as a turnkey solution, including the firmware integrated on the chip.In addition, Atmel provides the necessary device driver software for integration into certain operating systems, along with BIOS drivers. Atmel will also provide manufacturing support software for use by OEMs and ODMs during initialization and verification of the TPM during board assembly.Full documentation for TCG primitives can be found in the TCG TPM Main Specification, Parts 1 to 3, on the TCG Web site located at https://. TPM features specific to PC Client platforms are specified in the “TCG PC Client Specific TPM Interface Specification, Version 1.2”, also available on the TCG web site. Implementation guidance for 32-bit PC platforms is outlined in the “TCG PC Client Specific Implementation Specification for Conventional BIOS for TCG Version 1.2”, also available on the TCG website.3.Ordering InformationNote: 1.Please see the AT97SC3204 datasheet addendum for the complete catalog number ordering code.4.Package Drawings4.128X1 — 28-lead Thin TSSOP4.240ML1 — 40-pad VQFN5.Revision HistoryAtmel Corporation1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311F: (+1)(408) 436.4200| © 2013 Atmel Corporation. All rights reserved. / Rev.: Atmel-5295ES-TPM-AT97SC3204-LPC-Interface-Datasheet-Summary-032013Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, AVR®, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted。

半导体制造的常用名词

半导体制造的常用名词发表于: 2007-5-07 17:10 作者: luhaoxinglhx 来源: 半导体技术天地Ingot - A cylindrical solid made of polycrystalline or single crystal silicon from which wafers are cut.晶锭- 由多晶或单晶形成的圆柱体,晶圆片由此切割而成。

Laser Light-Scattering Event - A signal pulse that locates surface imperfections on a wafer.激光散射- 由晶圆片表面缺陷引起的脉冲信号。

Lay - The main direction of surface texture on a wafer.层- 晶圆片表面结构的主要方向。

Light Point Defect (LPD) (Not preferred; see localized light-scatterer)光点缺陷(LPD) (不推荐使用,参见“局部光散射”)Lithography - The process used to transfer patterns onto wafers.光刻- 从掩膜到圆片转移的过程。

Localized Light-Scatterer - One feature on the surface of a wafer, such as a pit or a scratch that scatters light. It is also called a light point defect.局部光散射- 晶圆片表面特征,例如小坑或擦伤导致光线散射,也称为光点缺陷。

Lot - Wafers of similar sizes and characteristics placed together in a shipment.批次- 具有相似尺寸和特性的晶圆片一并放置在一个载片器内。

封装测试

Ø Modeled fault testing

Ø Will detect 100% of detectable modeled faults Ø Requires only 47 vectors Ø Vectors can be generated and analyzed by ATPG tools Ø Note: some of the faults are not able to be detected by

Ø Stuck-short: a single transistor is permanently stuck in short state

Ø Detection of a stuck-open fault requires two vectors

Ø A collapsed fault set contains one fault from each equivalence subset

Ø The length of ATPG patterns is reduced significantly after considering the fault collapse

Microelectronics

上海交通大学微电子学院

Transistor (Switch)Faults

Ø MOS transistor is considered an ideal switch and two types of faults are modeled:

Ø Stuck-open: a single transistor is permanently stuck in open state

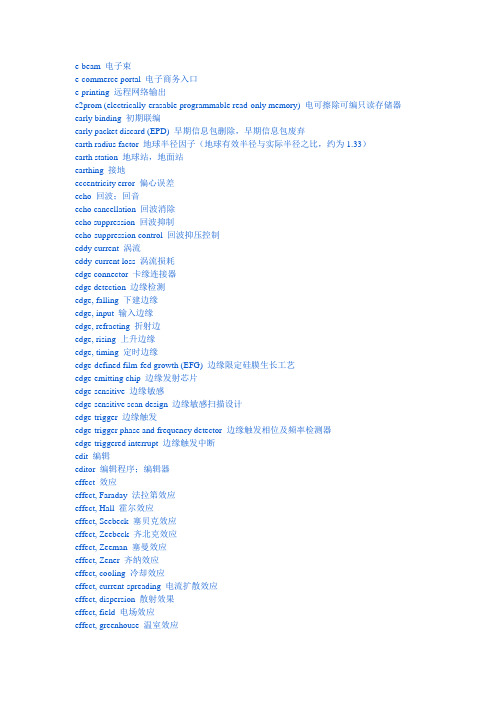

IT专业英语词典-E