2-4译码器设计

数字电路——2-4译码器设计

目录1 绪论 (1)1.1设计背景 (1)2 电路分析 (2)2.1 2-4功能分析 (2)2.2 2-4译码器逻辑图 (3)3 系统建模与仿真 (4)3.1 建模 (4)3.2 仿真波形 (5)4 仿真结果分析 (7)5 小结与体会 (8)参考文献 (9)1 绪论1.1设计背景在数字系统中,经常需要将一中代码转换为另一种代码,以满足特定的需求,完成这种功能的电路称为码转化电路。

译码器就属于其中一种。

而译码就是编码的逆过程,它的功能是将具有特定含义的二进制码转换成对应的有效输出信号,具有译码功能的的逻辑电路称为译码器。

而2-4译码器是唯一地址译码器,是将一系列的代码转换成与之一一对应有效的信号。

常用于计算机中对存储单元地址的译码,因此,设计2-4译码器具有很强的现实意义。

1.2 matlab简介MATLAB是由美国mathworks公司发布的主要面对科学计算、可视化以及交互式程序设计的高科技计算环境。

它将数值分析、矩阵计算、科学数据可视化以及非线性动态系统的建模和仿真等诸多强大功能集成在一个易于使用的视窗环境中,为科学研究、工程设计以及必须进行有效数值计算的众多科学领域提供了一种全面的解决方案,并在很大程度上摆脱了传统非交互式程序设计语言(如C、Fortran)的编辑模式,代表了当今国际科学计算软件的先进水平。

它主要由MATLAB和Simulink两大部分组成。

本设计主要采用simulink进行设计与仿真。

Simulink是MATLAB最重要的组件之一,它提供一个动态系统建模、仿真和综合分析的集成环境。

在该环境中,无需大量书写程序,而只需要通过简单直观的鼠标操作,就可构造出复杂的系统。

Simulink具有适应面广、结构和流程清晰及仿真精细、贴近实际、效率高、灵活等优点,并基于以上优点Simulink已被广泛应用于控制理论和数字信号处理的复杂仿真和设计。

同时有大量的第三方软件和硬件可应用于或被要求应用于Simulink。

数字电路——2-4译码器设计

-------------------------------------------------------------------------------目录1 绪论 (1)1.1设计背景 (1)2 电路分析 (2)2.1 2-4功能分析 (2)2.2 2-4译码器逻辑图 (3)3 系统建模与仿真 (4)3.1 建模 (4)3.2 仿真波形 (5)4 仿真结果分析 (8)5 小结与体会 (9)参考文献 (10)1 绪论1.1设计背景在数字系统中,经常需要将一中代码转换为另一种代码,以满足特定的需求,完成这种功能的电路称为码转化电路。

译码器就属于其中一种。

而译码就是编码的逆过程,它的功能是将具有特定含义的二进制码转换成对应的有效输出信号,具有译码功能的的逻辑电路称为译码器。

而2-4译码器是唯一地址译码器,是将一系列的代码转换成与之一一对应有效的信号。

常用于计算机中对存储单元地址的译码,因此,设计2-4译码器具有很强的现实意义。

1.2 matlab简介MATLAB是由美国mathworks公司发布的主要面对科学计算、可视化以及交互式程序设计的高科技计算环境。

它将数值分析、矩阵计算、科学数据可视化以及非线性动态系统的建模和仿真等诸多强大功能集成在一个易于使用的视窗环境中,为科学研究、工程设计以及必须进行有效数值计算的众多科学领域提供了一种全面的解决方案,并在很大程度上摆脱了传统非交互式程序设计语言(如C、Fortran)的编辑模式,代表了当今国际科学计算软件的先进水平。

它主要由MATLAB和Simulin k两大部分组成。

本设计主要采用simulink进行设计与仿真。

Simulink是MATLAB最重要的组件之一,它提供一个动态系统建模、仿真和综合分析的集成环境。

在该环境中,无需大量书写程序,而只需要通过简单直观的鼠标操作,就可构造出复杂的系统。

Simulink具有适应面广、结构和流程清晰及仿真精细、贴近实际、效率高、灵活等优点,并基于以上优点Simulink已被广泛应用于控制理论和数字信号处理的复杂仿真和设计。

山东交通学院译码器和数据选择器实验报告

实验十译码器和数据选择器一、实验目的1、熟悉集成译码器。

2、了解集成译码器应用。

二、实验原理译码器是将给定代码译成相应状态的电路。

双2-4线集成变量译码器74LS139如图10-1所示。

每个2-4线译码器有两个输入端(A、B)和四个输出端(Y0、Y1、Y2、Y3)。

两个输入端可以输入四种数码,即00、01、10、11,对应的四种输出状态是0111、1011、1101、1110。

G为使能端,当G=0时,译码器能正常工作,当G=1时,不能工作,输出端全部为高电平(即“1”)。

数据选择器有多个输入,一个输出。

其功能类似单刀多掷开关,故又称多路开关(MUX)。

在控制端的作用下可从多路并行数据中选择一路送输出端。

双4选1数据选择器74LS153如图10-2所示。

以其中的一个数据选择器为例,C0、C1、C2、C3为输入端,可同时输入四种不同的数据(信号),Y为被选中的数据的输出端,G为使能端(低电平时工作),A、B为选择控制端。

设四个输入端的输入信号分别为C0、C1、C2、C3则其功能如表10-1所示。

三、实验仪器及材料1、双踪示波器2、器件74LS139 双2—4线译码器 1片74LS153 双4选1数据器 1片74LS00 二输入端四与非门 1片四、实验预习要求1、复习有关译码器和数据选择器的原理。

2、根据实验任务,画出所需的实验线路及记录表格。

五、实验内容及步骤1、译码器功能测试将74LS139译码器按图10-1,接线,按表10-2输入电平分别置位,填写输出状态表图10-1 74LS139译码器表10-22、译码器转换将双2—4线译码器转换为3—8线译码器。

(1)画出转换电路图。

(2)在实验仪上接线并验证设计是否正确。

(3)设计并填写该3—8线译码器功能表,画出输入、输出波形。

3、数据选择器的测试及应用将双4选1数据选择器74LS153参照图10-2接线,测试其功能并填写功能表。

(1)将选择端1(G)、2(B)、14(A)脚接逻辑电平开关;(2)将实验仪脉冲信号源中固定连续脉冲4个不同频率的信号接到数据选择器4个输入端:3(250KHz)、4(100KHz)、5(10KHz)、6(1KHz);将选择端置位,使输出端7(1Y)接示波器,可分别观察到4种不同频率脉冲信号。

2-4译码器原理

2-4译码器原理摘要:I.2-4译码器概述A.定义和背景B.应用领域II.2-4译码器原理A.工作原理B.电路结构C.信号处理过程III.2-4译码器的实现A.常见实现方法B.实际应用案例C.性能评估IV.2-4译码器的优缺点A.优点B.缺点V.结论正文:I.2-4译码器概述2-4译码器,顾名思义,是一种将二进制信号转换为四位输出信号的电路。

在数字信号处理、通信和计算机科学等领域中,这种电路的应用非常广泛。

例如,在计算机中,2-4译码器可以将一个字节中的两个二进制位转换为四个输出信号,以便进行进一步的处理。

II.2-4译码器原理2-4译码器的工作原理非常简单。

它可以接收两个输入信号,根据输入信号的不同组合,产生四个输出信号。

电路结构主要包括输入端、逻辑门和输出端。

A.工作原理当输入信号发生变化时,2-4译码器会根据输入信号的不同组合产生对应的输出信号。

例如,当输入信号为00时,输出信号为0000;当输入信号为01时,输出信号为0001;以此类推。

B.电路结构2-4译码器的电路结构主要包括输入端、逻辑门和输出端。

输入端用于接收两个输入信号,逻辑门用于根据输入信号的组合产生输出信号,输出端用于将产生的输出信号传递给其他电路。

C.信号处理过程当输入信号发生变化时,逻辑门会根据输入信号的组合产生相应的输出信号。

例如,当输入信号为00时,与门输出为0,非门输出为1,或门输出为0,从而产生输出信号0000;当输入信号为01时,与门输出为0,非门输出为0,或门输出为1,从而产生输出信号0001。

III.2-4译码器的实现A.常见实现方法常见的2-4译码器实现方法包括使用逻辑门、触发器等电路元件。

例如,可以使用与门、非门和或门组成逻辑电路,实现2-4译码器功能。

B.实际应用案例2-4译码器在实际应用中得到广泛的应用。

例如,在计算机中,可以使用2-4译码器将一个字节中的两个二进制位转换为四个输出信号,以便进行进一步的处理。

2-4 译码器的设计

实验一

译码器的设计(2-4 译码器)姓名:

学号:

专业:自动化

年级:2008

译码器的设计(2-4 译码器)

一:实验目的

1:能了解组合逻辑中译码器电路的设计原理。

2:能利用CPLD数字发展实验系统设计一个二对四译码器。

3:能自行验证所设计电路的正确性。

二:实验内容及要求

设计一个2-4译码器,并下载到实验板进行验证。

三:实验器材

1.软件:Altera公司的Quartus || 软件。

2.芯片:Altera公司的EP2C8T144C8。

3.开发平台:台湾掌宇公司的CIC-31智能型可编程数字开发系统。

四:实验步骤

1.建立名为 decoder2-4的工程文件,并在 Quartus || 原理图编辑环境中绘制电路图,如下图所示。

2.保存文件,检查及编译。

3.建立波形文件,并进行功能仿真,仿真结果如下图所示。

输入输出

S1 (P132)

S0

(P129)

m3

(P100)

m2

(P101)

m1

(P112)

m0

(P113)

0 0 0 0 0 1

0 1 0 0 1 0

1 0 0 1 0 0 1 1 1 0 0 0。

数字电路——2-4译码器设计说明

目录1 绪论 (1)1.1设计背景 (1)2 电路分析 (2)2.1 2-4功能分析 (2)2.2 2-4译码器逻辑图 (3)3 系统建模与仿真 (4)3.1 建模 (4)3.2 仿真波形 (5)4 仿真结果分析 (8)5 小结与体会 (9)参考文献 (10)1 绪论1.1设计背景在数字系统中,经常需要将一中代码转换为另一种代码,以满足特定的需求,完成这种功能的电路称为码转化电路。

译码器就属于其中一种。

而译码就是编码的逆过程,它的功能是将具有特定含义的二进制码转换成对应的有效输出信号,具有译码功能的的逻辑电路称为译码器。

而2-4译码器是唯一地址译码器,是将一系列的代码转换成与之一一对应有效的信号。

常用于计算机中对存储单元地址的译码,因此,设计2-4译码器具有很强的现实意义。

1.2 matlab简介MATLAB是由美国mathworks公司发布的主要面对科学计算、可视化以及交互式程序设计的高科技计算环境。

它将数值分析、矩阵计算、科学数据可视化以及非线性动态系统的建模和仿真等诸多强大功能集成在一个易于使用的视窗环境中,为科学研究、工程设计以及必须进行有效数值计算的众多科学领域提供了一种全面的解决方案,并在很大程度上摆脱了传统非交互式程序设计语言(如C、Fortran)的编辑模式,代表了当今国际科学计算软件的先进水平。

它主要由MATLAB和Simulink两大部分组成。

本设计主要采用simulink进行设计与仿真。

Simulink是MATLAB最重要的组件之一,它提供一个动态系统建模、仿真和综合分析的集成环境。

在该环境中,无需大量书写程序,而只需要通过简单直观的鼠标操作,就可构造出复杂的系统。

Simulink具有适应面广、结构和流程清晰及仿真精细、贴近实际、效率高、灵活等优点,并基于以上优点Simulink已被广泛应用于控制理论和数字信号处理的复杂仿真和设计。

同时有大量的第三方软件和硬件可应用于或被要求应用于Simulink。

含两个2-4译码器的74HC139芯片版图

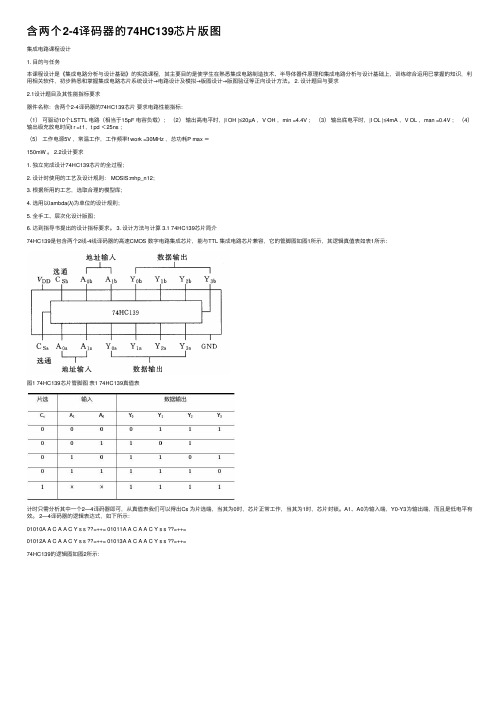

含两个2-4译码器的74HC139芯⽚版图集成电路课程设计1. ⽬的与任务本课程设计是《集成电路分析与设计基础》的实践课程,其主要⽬的是使学⽣在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运⽤已掌握的知识,利⽤相关软件,初步熟悉和掌握集成电路芯⽚系统设计→电路设计及模拟→版图设计→版图验证等正向设计⽅法。

2. 设计题⽬与要求2.1设计题⽬及其性能指标要求器件名称:含两个2-4译码器的74HC139芯⽚要求电路性能指标:(1)可驱动10个LSTTL 电路(相当于15pF 电容负载);(2)输出⾼电平时,|I OH |≤20µA ,V OH ,min =4.4V ;(3)输出底电平时,|I OL |≤4mA ,V OL ,man =0.4V ;(4)输出级充放电时间t r =t f ,t pd <25ns ;(5)⼯作电源5V ,常温⼯作,⼯作频率f work =30MHz ,总功耗P max =150mW 。

2.2设计要求1. 独⽴完成设计74HC139芯⽚的全过程;2. 设计时使⽤的⼯艺及设计规则: MOSIS:mhp_n12;3. 根据所⽤的⼯艺,选取合理的模型库;4. 选⽤以lambda(λ)为单位的设计规则;5. 全⼿⼯、层次化设计版图;6. 达到指导书提出的设计指标要求。

3. 设计⽅法与计算 3.1 74HC139芯⽚简介74HC139是包含两个2线-4线译码器的⾼速CMOS 数字电路集成芯⽚,能与TTL 集成电路芯⽚兼容,它的管脚图如图1所⽰,其逻辑真值表如表1所⽰:图1 74HC139芯⽚管脚图表1 74HC139真值表计时只需分析其中⼀个2—4译码器即可,从真值表我们可以得出Cs 为⽚选端,当其为0时,芯⽚正常⼯作,当其为1时,芯⽚封锁。

A1、A0为输⼊端,Y0-Y3为输出端,⽽且是低电平有效。

2—4译码器的逻辑表达式,如下所⽰:01010A A C A A C Y s s ??=++= 01011A A C A A C Y s s ??=++=01012A A C A A C Y s s ??=++= 01013A A C A A C Y s s ??=++=74HC139的逻辑图如图2所⽰:图2 74HC139逻辑图3.2 电路设计本次设计采⽤的是m12_20的模型库参数进⾏各级电路的尺⼨计算,其参数如下: NMOS: εox =3.9×8.85×10﹣12F/m µn =605.312×10﹣4㎡/Vst ox =395×10﹣10m V tn =0.81056V PMOS: εox =3.9×8.85×10﹣12F/m µp =219×10﹣4㎡/Vst ox =395×10﹣10m V tp =﹣0.971428V 3.2.1 输出级电路设计根据要求输出级电路等效电路图如图3所⽰,输⼊Vi 为前⼀级的输出,可认为是理想的输出,即V IL =Vss, V IH =V DD 。

CMOS2-4译码器设计与HSPICE仿真

《集成电路设计》课程设计报告基于HSPICE的晶体管级电路设计与仿真题目:CMOS2-4译码器设计与HSPICE仿真学院专业班级学生姓名指导教师提交日期目录一、设计目的 (1)二、设计要求和设计指标 (1)三、设计内容 (1)3.1 CMOS2-4译码器原理及电路设计 (1)3.1.1 门级设计 (1)3.1.2 门的CMOS实现 (2)3.2 仿真结果与分析 (5)四、总结 (7)五、主要参考文献 (10)一、设计目的熟悉《数字集成电路设计》课程,学习Hspice软件的使用,以及.sp文件的编写,进一步理解掌握CMOS设计组合逻辑电路与时序逻辑电路的基本知识,继而熟练地运用半导体集成电路知识。

二、设计要求和设计指标(1)了解C2MOS 主从正沿触发寄存器的电路结构、电路原理;(2)了解电路具体参数,包含的晶体管数目、晶体管尺寸、连线情况等;(3)利用HSPICE软件,编写.sp 文件;(4)仿真该sp 文件,得出描述电路性能的函数图线、波形等参数;(5)在具体的软硬件实验环境中,进行设计模拟、仿真和调试,解决设计调试中的具体问题;得出结论,并完成设计。

三、设计内容3.1 CMOS2-4译码器原理及电路设计3.1.1门级设计译码器是组合逻辑电路的一个重要器件,把代码状态的特定含义“翻译”出来的过程叫做译码,实现译码操作的电路称为译码器。

译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

而CMOS2-4译码,是将其输入的两位二进制代码“00”“01”“10”“11”进行翻译,从而控制电路的输出线路,实现四路译码的过程。

其真值表如图表1所示:A B Y0 Y1 Y2 Y30 0 0 1 1 10 1 1 0 1 11 0 1 1 0 11 1 1 1 1 0图表1由图表1可以得到CMOS2-4译码器的布尔表达式为:Y0=Y1=Y2=Y3=从而可以得到CMOS2-4译码器门级设计的电路图,如图表2:U3A123U1A 12U5A123U6A123U2A 12U4A123图表2这样,通过两个非门和四个与非门就可以实现如图表1中的真值表所示的逻辑功能。

(完整word版)2对4译码器VHDL实验报告.doc

通信与信息工程学院2012 /2013学年第二学期软件设计实验报告模块名称二对四译码器专业电子信息工程学生班级B100109学生学号学生姓名指导教师梅中辉、王奇、周晓燕、孔凡坤实验目的:本软件设计的目的和任务: 1.使学生全面了解如何应用该硬件描述语言进行高速集成电路设计; 2.通过软件使用、设计与仿真环节使学生熟悉 EDA-VHDL 开发环境; 3. 通过对基本题、综合题的设计实践,使学生掌握硬件系统设计方法(自底向上或自顶向下),熟悉 VHDL 语言三种设计风格,并且培养学生应用 VHDL 语言解决实际问题的能力。

实验设备: 1:微型计算机2:quartus II 开发软件实验课题: 2 对 4 译码器实验描述:设计一个 2 对 4 译码器(输入: A B 输出: Y3 Y2 Y1 Y0 ),真值表如图:A B Y3 Y2 Y1 Y00 0 1 1 1 00 1 1 1 0 11 0 1 0 1 11 1 0 1 1 1一:实验目的1:能了解组合逻辑中译码器电路的设计原理。

2:能利用 CPLD数字发展实验系统设计一个二对四译码器。

3:能自行验证所设计电路的正确性。

二:实验内容及要求设计一个 2-4 译码器,并验证输出数值的正确性。

三:实验器材1. 软件: Altera公司的Quartus ||软件。

2. 芯片: Altera公司的EP2C8T144C8。

1)、选择 Block Diagran/Schenatic File,单击 OK 按钮,打开图形2)、进入原理图编辑页面如下:导入逻辑门电路符号、输入/输出符号,用导线连接各逻辑单元如下:工程建立与编译建立工程:在 D 盘建立 test 文件夹,进入 quartusII7.2 主界面,新建编辑代码页面,选择 VHDL file ,点击 OK代码输完后存盘,文件名必需为 test8(文件名必须与实体名一致),目录为,按 project 菜单下 set as top-level entity 命令。

2-4译码器原理

2-4译码器原理摘要:1.2-4 译码器的概念2.2-4 译码器的工作原理a.二进制到四进制编码b.译码器的设计与实现c.2-4 译码器的应用场景3.2-4 译码器的优缺点分析4.2-4 译码器的发展趋势与展望正文:2-4 译码器是一种将二进制信号转换为四进制信号的设备,它在数字通信、计算机科学等领域具有广泛的应用。

本文将详细介绍2-4 译码器的原理、工作方式以及应用场景,并对其优缺点进行分析,展望未来的发展趋势。

首先,我们需要了解2-4 译码器的概念。

在数字通信中,信息的传输和处理通常采用二进制编码系统,但由于二进制系统只有两种状态,往往不能满足实际应用中的需求。

因此,研究人员提出了将二进制信号转换为四进制信号的方法,即2-4 译码器。

通过使用2-4 译码器,可以有效提高信息传输的效率和可靠性。

接下来,我们来探讨2-4 译码器的工作原理。

首先,二进制到四进制编码是译码器的核心功能。

在这个过程中,需要将二进制信号与特定的编码规则对应起来,从而实现二进制到四进制的转换。

其次,译码器的设计与实现是关键步骤。

为了完成高效的译码任务,需要设计合适的译码器结构,以满足不同应用场景的需求。

目前,已有多种类型的2-4 译码器实现方案,如基于查找表的译码器、基于阵列处理的译码器等。

在了解了2-4 译码器的工作原理之后,我们来探讨一下它的应用场景。

2-4 译码器广泛应用于数字通信、计算机科学等领域,其中最典型的应用是四电平脉冲幅度调制(PAM-4)系统。

在PAM-4 系统中,采用2-4 译码器将二进制信号转换为四进制信号,从而实现更高的传输速率和更长的传输距离。

此外,2-4 译码器还在其他领域发挥着重要作用,如数字信号处理、图像处理等。

当然,2-4 译码器也存在一些优缺点。

优点主要表现在它能提高信息传输的效率和可靠性,使得数字通信系统具有更好的性能。

而缺点则主要体现在设计和实现过程中可能遇到的挑战,如译码器结构的复杂性、译码误差的产生等。

2-4译码器电路仿真

实验七译码器和数据选择器一、实验目的1.熟悉集成译码器。

2.了解集成译码器应用。

二、实验原理1.74LS139 为两个2线-4 线译码器,共有54/74S139和54/74LS139 两种线路结构型式,当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。

若将选通端(G1)作为数据输入端时,139 还可作数据分配器。

图7-1 74LS139管脚图2.74LS153 双4选1数据选择器(有选通输入端)简要说明:153 为两组 4 选 1 数据选择器,数据选择端(AB)为两组共用,按二进制译码,以供两组从各自的4个数据(1C0――1C3,2C0――2C3)中分别选取 1 个所需的数据。

只有在两组各自的选通端(1G、2G)为低电平时才可选择数据。

管脚图如图7-2所示:图7-2 74LS153管脚图三、预习要求1、懂得译码器的工作原理。

2、了解如何利用译码器设计实际应用电路。

三、实验内容1.译码器功能测试将74LS139译码器按图7-3接线并截图,按表7-l输入电平分别置位、填输出状态表7-1。

表7-12.数据选择器的测试及应用(1)将双4选1数据选择器74LS153参照图7-4接线.测试其功能并填写功能表(2)利用函数发生器产生4个不同频率的信号接到数据选择器4个输入端,将选择端置位,用示波器同时观测4对各自对应的输入端与输出端波形,并截图。

图7-4表7-23.译码器转换将双2一4线译码器转换为3—8线译码器。

(1)请自行设计电路,画出转换电路图,并截图。

(2)引设计并填写该3一8线译码器功能表,用字发生器模拟8种状态的输入,并用逻辑分析仪同时读取输入与输出波形,并截图。

2-4转3-8译码器实验报告

2-4转3-8译码器实验报告

实验目的:

掌握2-4转3-8译码器的基本原理和应用,了解其译码功能和

逻辑电路设计。

实验器材:

2-4转3-8译码器芯片、数字逻辑实验箱、杜邦线等。

实验原理:

2-4转3-8译码器是一种常用的数字电路器件,用于将2位二

进制输入数据转换为8个输出信号。

其逻辑功能如下:

- 当输入为00时,输出Y0为1,其余输出为0;

- 当输入为01时,输出Y1为1,其余输出为0;

- 当输入为10时,输出Y2为1,其余输出为0;

- 当输入为11时,输出Y3为1,其余输出为0。

实验步骤:

1. 将2-4转3-8译码器芯片插入数字逻辑实验箱的芯片插座中。

2. 连接实验箱电源,并将电压调整到5V。

3. 将多根杜邦线依次连接译码器芯片和实验箱上的连接端,确保连接正确。

4. 将示波器的触发方式调整为外部触发,并将其中一根杜邦线接入示波器的外部触发输入端。

5. 设计四组输入数据,并分别将它们输入到译码器的AB端。

6. 观察示波器上的输出波形,检查译码器的输出是否满足预期。

实验结果:

根据设计输入数据和观察波形,可以确认2-4转3-8译码器的输出与理论相符,实现了正确的译码功能。

实验总结:

通过本次实验,我们成功地了解了2-4转3-8译码器的基本原理和应用,并实际操作了相应的电路搭建和数据传输。

这个实验对于我们进一步深入理解数字逻辑电路设计和应用有着重要的指导作用。

FPGA实验二2-4译码器设计实验报告原版

FPGA实验⼆2-4译码器设计实验报告原版得分:数字系统设计课程实验实验⼆2-4译码器设计1、⽤CSAE语句进⾏2-4译码器设计程序设计library ieee;use ieee.std_logic_1164.all;entity decoder24isport(a:in std_logic_vector(1downto0);--定义输⼊信号a(1..0) s:out std_logic_vector(3downto0));--定义输出信号s(3..0) end decoder24;architecture behave of decoder24isbeginprocess(a)begincase a iswhen"00"=>s<="1110";--当a=00时,s(0)=0 when"01"=>s<="1101";--当a=01时,s(1)=0 when"10"=>s<="1011";--当a=10时,s(2)=0 when"11"=>s<="0111";--当a=11时,s(3)=0when others=>null;end case;end process;end behave;仿真结果a s(填灯亮和灭)a(1)a(2)LED2LED3LED4LED5 00灭灭灭亮01灭灭亮灭10灭亮灭灭11亮灭灭灭下载后LED2,6,7亮按下up后LED4,6,7亮2、⽤IF语句进⾏2-4译码器设计程序设计library ieee;use ieee.std_logic_1164.all;entity d24isport(a:in std_logic_vector(1downto0);--定义输⼊信号a(1..0) s:out std_logic_vector(3downto0));--定义输出信号s(3..0) end d24;architecture behave of d24isbeginprocess(a)beginif a="00"then s<=(0=>'0',others=>'1');--当a=00时,s(0)=0 elsif a="01"then s<=(1=>'0',others=>'1');--当a=01时,s(1)=0 elsifa="10"then s<=(2=>'0',others=>'1');--当a=10时,s(2)=0 elsif a="11"then s<=(3=>'0',others=>'1');--当a=11时,s(3)=0 else s<= (others=>'0');end if;end process;end behave;仿真结果a s(填灯亮和灭)a(1)a(2)LED2LED3LED4(pin68)LED5 00灭灭灭亮01灭灭亮灭10灭亮灭灭11亮灭灭灭引脚配置如表:端⼝引脚实验板上名称端⼝引脚实验板上名称端⼝引脚实验板上名称a(1)132up s(3)64LED2s(1)68LED4 a(0)131left s(2)67LED3s(0)69LED5实验总结:由于有了之前实验的操作基础,所以在做这个实验时遇到的阻⼒不⼤,⽐较顺利的完成了。

集成电路课程设计--含2个 2-4线译码器的74HC139芯片

集成电路课程设计----含2个2-4线译码器的74HC139芯片一.目的与任务本课程设计是《集成电路分析与设计》的实践课程,其主要目的是为了在了解了集成电路的基本结构的基础上进一步的学习集成电路的设计,本次设计通过对TANNER TOOLS PRO工具的使用让我们能够从简单入手到能设计一个完整的芯片,。

并进行电路仿真对比。

二.课程设计题目、内容及要求2.1 设计题目1.器件名称:一个3-8译码器的74HC138芯片;2.要求的电路性能指标:(1)可驱动10个LSTTL电路(相当于15pF电容负载);(2)输出高电平时,︱IoH︱≤20uA,Voh,min=4.4V;(3)输出低电平时,︱IoL︱≤4mA,Vol,max=0.4V;(4)输出级充放电时间tr = tf,tpd<25ns;(5)工作电源5V,常温工作,工作频率fwork =30MHz,总功耗Pmax=150mW。

2.2 设计内容(1)功能分析及逻辑设计(2)电路设计(3)估算功耗与延时(4)电路模拟与仿真(5)版图设计(全手工、层次化设计)(6)版图检查:DRC与LVS(7)后仿真(选做)(8)版图数据提交2.3 设计要求(1)独立完成设计74HC138 芯片的全过程;(2)设计时使用的工艺及设计规则:MOSIS:mamin08;(3)根据所用的工艺,选取合理的模型库;(4)选用以lambda(λ)为单位的设计规则;(5)全手工、层次化设计版图;(6)达到指导书提出的设计指标要求。

三、74HC139电路简介3.1 通用74HC139芯片的引脚图74HC139芯片包含两个2-4译码器,它的通用引脚图入图1其中,(1A0、1A1)和(2A0、2A1)分别为两个译码器的地址输入端,而1E (以下取名为Csa )和2E (以下取名为Csb )分别为两个译码器的使能端(低电平有效),1Y0~1Y7和2Y0~2Y7为译码器的数据输出端。

3.2通用74HC139的真值表 通用74HC139的真值表如表一3.3通用74HC139的逻辑表达式根据表一,我们可以很容易得到一下的逻辑表达式 Y0=E+A1+A0=01A A E ∙∙ Y1=E+A1+0A =01A A E ∙∙ Y2=E+1A +A0=01A A E ∙∙ Y3=E+1A +0A =01A A E ∙∙3.4通用74HC139的逻辑图,如图2所示图二所示为通用74HC139芯片的其中一个译码器的逻辑图。

数字电路__2_4译码器的设计

目录1 绪论 (1)1.1设计背景 (1)2 电路分析 (2)2.1 2-4功能分析 (2)2.2 2-4译码器逻辑图 (3)3 系统建模与仿真 (4)3.1 建模 (4)3.2 仿真波形 (5)4 仿真结果分析 (7)5 小结与体会 (8)参考文献 (9)1 绪论1.1设计背景在数字系统中,经常需要将一中代码转换为另一种代码,以满足特定的需求,完成这种功能的电路称为码转化电路。

译码器就属于其中一种。

而译码就是编码的逆过程,它的功能是将具有特定含义的二进制码转换成对应的有效输出信号,具有译码功能的的逻辑电路称为译码器。

而2-4译码器是唯一地址译码器,是将一系列的代码转换成与之一一对应有效的信号。

常用于计算机中对存储单元地址的译码,因此,设计2-4译码器具有很强的现实意义。

1.2 matlab简介MATLAB是由美国mathworks公司发布的主要面对科学计算、可视化以及交互式程序设计的高科技计算环境。

它将数值分析、矩阵计算、科学数据可视化以及非线性动态系统的建模和仿真等诸多强大功能集成在一个易于使用的视窗环境中,为科学研究、工程设计以及必须进行有效数值计算的众多科学领域提供了一种全面的解决方案,并在很大程度上摆脱了传统非交互式程序设计语言(如C、Fortran)的编辑模式,代表了当今国际科学计算软件的先进水平。

它主要由MATLAB和Simulin k两大部分组成。

本设计主要采用simulink进行设计与仿真。

Simulink是MATLAB最重要的组件之一,它提供一个动态系统建模、仿真和综合分析的集成环境。

在该环境中,无需大量书写程序,而只需要通过简单直观的鼠标操作,就可构造出复杂的系统。

Simulink具有适应面广、结构和流程清晰及仿真精细、贴近实际、效率高、灵活等优点,并基于以上优点Simulink已被广泛应用于控制理论和数字信号处理的复杂仿真和设计。

同时有大量的第三方软件和硬件可应用于或被要求应用于Simulink。

2-4译码器设计

在Logisim中,设计一个高电平有效2线-4线译码器,使能Enable高电平有效。相关知识

译码器(Decoder)将二进制代码的特定含义翻译出来,是一类多输入多输出组合逻辑器件,其可以分为:变量译码和显示译码两类。变量译码器一般是一种较少输入变为较多输出的器件,常见的有n线-2^n线译码和BCD码译码两类;显示译码器用来将二进制数转换成对应的七段码,一般其可分为驱动LED和驱动LCD两类。

计算机中通常有地址译码器、指令译码器等。2-4译码器的电路原理图如下: