Altera Cyclone IV GX系列FPGA开发方案

Altera Cyclone IV GX系列的特性及FPGA开发套件的设计方案介绍

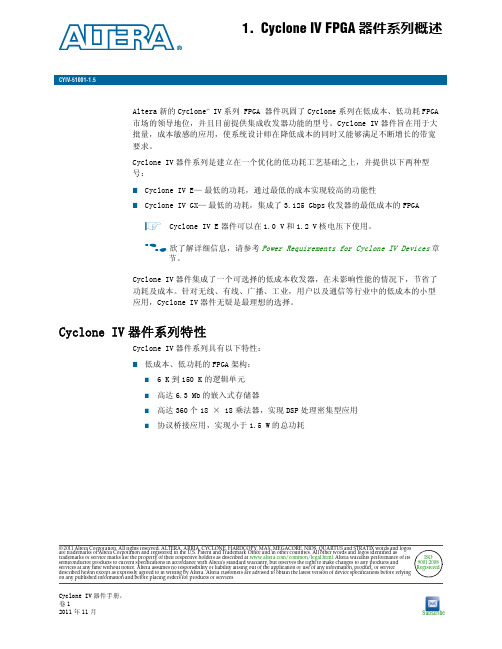

Altera Cyclone IV GX系列的特性及FPGA开发套件的设计方案介绍Altera 公司的Cyclone IV 系列FPGA包括两个系列:Cyclone IV E和Cyclone IV GX,具有低成本、低功耗的FPGA 架构,6 K 到150 K 的逻辑单元,高达6.3 Mb 的嵌入式存储器,小于1.5 W 的总功耗;Cyclone IV GX 器件提供高达八个3.125 Gbps高速收发器,用于大批量,成本敏感的应用如无线、有线、广播、工业,用户以及通信等行业。

本文介绍了Cyclone IV 器件系列主要特性,收发器通道框图以及Cyclone IV GX FPGA开发套件主要特性,框图,电路图和材料清单。

Altera 新的Cyclone®IV 系列FPGA 器件巩固了Cyclone 系列在低成本、低功耗FPGA 市场的领导地位,并且目前提供集成收发器功能的型号。

Cyclone IV 器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

Cyclone IV 器件系列是建立在一个优化的低功耗工艺基础之上,并提供以下两种型号:■Cyclone IV E- 最低的功耗,通过最低的成本实现较高的功能性■Cyclone IV GX- 最低的功耗,集成了3.125 Gbps 收发器的最低成本的FPGA Cyclone IV 器件集成了一个可选择的低成本收发器,在未影响性能的情况下,节省了功耗及成本。

针对无线、有线、广播、工业,用户以及通信等行业中的低成本的小型应用,Cyclone IV 器件无疑是最理想的选择。

Cyclone IV 器件系列主要特性:■低成本、低功耗的FPGA 架构:■6 K 到150 K 的逻辑单元■高达6.3 Mb 的嵌入式存储器■高达360 个18 ×18 乘法器,实现DSP 处理密集型应用■协议桥接应用,实现小于1.5 W 的总功耗■Cyclone IV GX 器件提供高达八个高速收发器以支持:■高达3.125 Gbps 的数据速率■8B/10B 编码器/ 解码器。

嵌入式开发笔记——MCU配置Altera-Cyclone系列FPGA

嵌入式开发笔记——MCU配置Altera-Cyclone系列FPGA作者:zzssdd2E-mail:*******************1、需求描述FPGA内部是SRAM储存结构,掉电后程序就会丢失,故需要将FPGA程序保存在掉电不丢失的储存介质中(比如FLASH、EMMC、SD卡等),在每次上电时读取程序进行配置。

2、功能分析项目中使用的FPGA型号是Altera公司(现属于Intel)的Cyclone系列。

在Altera的文档《Cyclone Device Handbook,Volume1》的第13章节讲述了该系列FPGA的几种配置方式。

FPGA'的三种配置模式模式描述AS(Active serial)模式FPGA主动配置。

该模式由FPGA主动从外部储存器读取配置数据PS(Passive serial)模式FPGA被动控制。

该模式由外部控制器对FPGA进行配置JTAG模式通过外部下载器下载到FPGA内部SRAM中FPGA选择配置模式通过MSEL0和MSEL1引脚不同的电平来选择配置方式(如果使用JTAG配置则可以忽略这些引脚配置)MSEL1 MSEL0 模式0 0 AS0 1 PSx x JTAG最终确定的方案是使用PS模式通过MCU来升级、配置FPGA。

下面主要讲使用MCU对FPGA进行PS模式下的配置过程。

PS模式配置引脚时序•发起配置请求o nCONFIG引脚拉低tCFG时间然后拉高,等待nSTATU拉低响应请求•进行配置o FPGA在DCLK引脚的上升沿采集DATA引脚Bit数据,LSB在前传输方式•配置完成o等待CONF_DONE引脚回应一个高电平表示配置完成PS配置模式时序参数3、功能实现配置FPGA用到的变量和标志static uint8_t fpga_cfg_buf[W25Q_SECTOR_SIZE]; //储存从FLASH读出数据static __IO uint8_t fpga_cfg_sta = 0x00; //记录配置状态//配置过程用到的标识enum{FPGA_CFG_ENABLE = 0x01,FPGA_CFG_START = 0x02,FPGA_CFG_DONE = 0x04,FPGA_CFG_OVER = 0x08,};MCU与FPGA连接引脚配置/**************************************************************** ******** 函数: fpga_config_init* 功能: 配置FPGA引脚* 输入: 无* 输出: 无*************************************************************** ********/void fpga_config_init(void){GPIO_InitTypeDef GPIO_InitStruct = {0};/* 引脚时钟使能 */FPGA_PIN_CLK_ENABLE();/* nCFG、DAT、CLK配置为输出 */GPIO_InitStruct.Pin = FPGA_nCFG_PIN;GPIO_InitStruct.Mode = GPIO_MODE_OUTPUT_PP;GPIO_InitStruct.Pull = GPIO_NOPULL;GPIO_InitStruct.Speed = GPIO_SPEED_FREQ_HIGH;HAL_GPIO_Init(FPGA_nCFG_PORT, &GPIO_InitStruct);GPIO_InitStruct.Pin = FPGA_DAT_PIN;HAL_GPIO_Init(FPGA_DAT_PORT, &GPIO_InitStruct);GPIO_InitStruct.Pin = FPGA_CLK_PIN;HAL_GPIO_Init(FPGA_CLK_PORT, &GPIO_InitStruct);/* nSTA、CFG_DONE配置为输入 */GPIO_InitStruct.Pin = FPGA_nSTA_PIN;GPIO_InitStruct.Mode = GPIO_MODE_INPUT;GPIO_InitStruct.Pull = GPIO_NOPULL;HAL_GPIO_Init(FPGA_nSTA_PORT, &GPIO_InitStruct);GPIO_InitStruct.Pin = FPGA_CFG_DONE_PIN;HAL_GPIO_Init(FPGA_CFG_DONE_PORT, &GPIO_InitStruct);/* 配置引脚默认状态 */HAL_GPIO_WritePin(FPGA_nCFG_PORT, FPGA_nCFG_PIN, GPIO_PIN_SET);HAL_GPIO_WritePin(FPGA_DAT_PORT, FPGA_DAT_PIN, GPIO_PIN_RESET);HAL_GPIO_WritePin(FPGA_CLK_PORT, FPGA_CLK_PIN, GPIO_PIN_RESET);}MCU对FPGA配置过程/**************************************************************** ******** 函数: fpga_config_process* 功能: FPGA程序配置* 输入: _uiDataSize:FPGA配置文件大小* _uiStartAddr:FLASH储存FPGA配置文件地址* 输出: 失败:< 0; 成功:0*************************************************************** ********/int fpga_config_process(uint32_t _uiDataSize, uint32_t _uiStartAddr){UINT interrupt_save;uint16_t i, j;uint32_t uiTout, uiRdAddr, uiCnt = 0;fpga_cfg_sta = 0;uiRdAddr = _uiStartAddr;/*############## 第一阶段:发起配置请求########################*/FPGA_PinWrite(FPGA_nCFG_PORT,FPGA_nCFG_PIN,GPIO_PI N_RESET);dwt_delay_us(100);FPGA_PinWrite(FPGA_nCFG_PORT,FPGA_nCFG_PIN,GPIO_PI N_SET);dwt_delay_us(40);/* 等待FPGA回应:100ms超时 */for (uiT out = 0; uiT out < 10000; uiTout++){if (GPIO_PIN_RESET == FPGA_PinRead(FPGA_nSTA_PORT,FPGA_nSTA_PIN)){SET_BIT(fpga_cfg_sta, FPGA_CFG_START);break;}dwt_delay_us(10);}/* 是否响应? */if (!READ_BIT(fpga_cfg_sta, FPGA_CFG_START)){return -1;}/*############## 第二阶段:进行配置########################*/do{W25Q_ReadBuffer(fpga_cfg_buf, uiRdAddr, W25Q_SECTOR_SIZE);uiRdAddr += W25Q_SECTOR_SIZE;for (i = 0; i < W25Q_SECTOR_SIZE; i++){/* 按bit写入,LSB在前 */DISABLE_IRQ();for (j = 0; j < 8; j++){if (fpga_cfg_buf[i] & 0x01){FPGA_PinWrite(FPGA_DAT_PORT,FPGA_DAT_PIN,GPIO_PIN_S ET);}else{FPGA_PinWrite(FPGA_DAT_PORT,FPGA_DAT_PIN,GPIO_PIN_ RESET);}FPGA_PinWrite(FPGA_CLK_PORT,FPGA_CLK_PIN,GPIO_PIN_R ESET); Delay(2);FPGA_PinWrite(FPGA_CLK_PORT,FPGA_CLK_PIN,GPIO_PIN_S ET); Delay(2);FPGA_PinWrite(FPGA_CLK_PORT,FPGA_CLK_PIN,GPIO_PIN_R ESET); Delay(2);fpga_cfg_buf[i] >>= 1;ENABLE_IRQ();/* 数据写入完毕退出 */if (++uiCnt >= _uiDataSize){SET_BIT(fpga_cfg_sta, FPGA_CFG_OVER);break;}}}while(RESET == READ_BIT(fpga_cfg_sta, FPGA_CFG_OVER));/*############## 第三阶段:等待配置完成回应########################*/for (i = 0, uiT out = 0; uiTout < 20000; uiTout++){dwt_delay_us(100);if (GPIO_PIN_SET == FPGA_PinRead(FPGA_CFG_DONE_PORT,FPGA_CFG_DONE_PIN)) {if (++i >= 10){SET_BIT(fpga_cfg_sta, FPGA_CFG_DONE);break;}}else{i = 0;}if (READ_BIT(fpga_cfg_sta, FPGA_CFG_DONE)) {return 0;}else{return -1;}}。

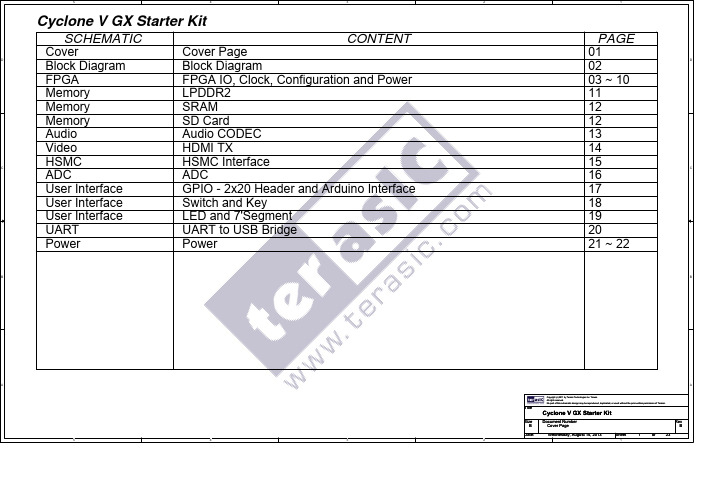

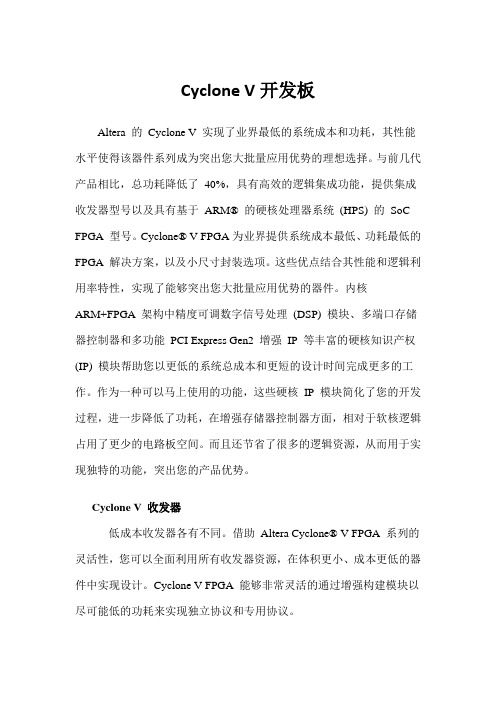

Cyclone V GX 开发板原理图 (5CGXFC5C6F27)

SRAMSD CardAudio CODECHDMI TXHSMC InterfaceADCGPIO - 2x20 Header and Arduino InterfaceSwitch and KeyLED and 7'SegmentUART to USB BridgePowerCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.All rights reserved.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.Title5432TitleSize Document Number Date:Copyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.Block DiagramCyclone V GX Starter KitB Friday, November 15, 2013SWITCH7-SEGMENTADC InterfaceDDR2LP_DQ7DDR2LP_DM0DDR2LP_DQ4DDR2LP_DQ5DDR2LP_DQ14DDR2LP_DQ15DDR2LP_CKE0DDR2LP_DM1DDR2LP_DQ12DDR2LP_DQ13DDR2LP_DQ11DDR2LP_CKE1DDR2LP_DQS_n1DDR2LP_DQS_p1DDR2LP_DQ8DDR2LP_DQ9GNDDDR2LP_DQ10DDR2LP_CA0DDR2LP_CA1SW[9..0]HEX0_D[6..0]HEX1_D[6..0]ADC_CONVST ADC_SCK ADC_SDO ADC_SDITitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.IO_4A/DIFFIO_RX_B30N/DQ4B/B_DQ_4Y13IO_4A/DIFFIO_RX_B30P/DQ4B/B_DQ_5W12IO_4A/DIFFIO_TX_B32N/DQ4B/B_DQ_7AF12IO_4A/DIFFIO_TX_B32P/DQ4B/B_DM_0AF11IO_4A/DIFFIO_TX_B33N/GND AC13IO_4A/DIFFIO_RX_B34N/DQ5B/B_DQ_8AC15IO_4A/DIFFIO_TX_B33P/DQ5B/B_DQ_10AC14IO_4A/DIFFIO_RX_B34P/DQ5B/B_DQ_9AB15IO_4A/DIFFIO_RX_B35N/DQSN5B/B_DQSN_1V14IO_4A/DIFFIO_TX_B36N/DQ5B/B_DQ_11AF13IO_4A/DIFFIO_RX_B35P/DQS5B/B_DQS_1U14IO_4A/DIFFIO_TX_B36P/B_CKE_1AE13IO_4A/DIFFIO_TX_B37N/DQ5B/B_CKE_0AF14IO_4A/DIFFIO_RX_B38N/DQ5B/B_DQ_12AB16IO_4A/DIFFIO_TX_B37P/DQ5B/B_DQ_14AE14IO_4A/DIFFIO_RX_B38P/DQ5B/B_DQ_13AA16IO_4A/DIFFIO_TX_B40N/DQ5B/B_DQ_15AF18IO_4A/DIFFIO_TX_B40P/DQ5B/B_DM_1AE18IO_4A/DIFFIO_RX_B46N/DQ6B/B_DQ_20IO_4A/DIFFIO_RX_B46P/DQ6B/B_DQ_21IO_4A/DIFFIO_TX_B48N/DQ6B/B_DQ_23IO_4A/DIFFIO_TX_B48P/DQ6B/B_DM_2IO_4A/DIFFIO_RX_B50N/DQ7B/B_DQ_24IO_4A/DIFFIO_TX_B49P/DQ7B/B_DQ_26IO_4A/DIFFIO_RX_B50P/DQ7B/B_DQ_25IO_4A/DIFFIO_RX_B51N/DQSN7B/B_DQSN_3IO_4A/DIFFIO_TX_B52N/DQ7B/B_DQ_27IO_4A/DIFFIO_RX_B51P/DQS7B/B_DQS_3IO_4A/DIFFIO_RX_B54N/DQ7B/B_DQ_28IO_4A/DIFFIO_TX_B53P/DQ7B/B_DQ_30IO_4A/DIFFIO_RX_B54P/DQ7B/B_DQ_29IO_4A/DIFFIO_TX_B56N/DQ7B/B_DQ_31IO_4A/DIFFIO_TX_B56P/DQ7B/B_DM_3IO_4A/DIFFIO_RX_B58N/DQ8B/B_DQ_32IO_4A/DIFFIO_TX_B57P/DQ8B/B_DQ_34IO_4A/DIFFIO_RX_B58P/DQ8B/B_DQ_33IO_4A/DIFFIO_RX_B59N/DQSN8B/B_DQSN_4IO_4A/DIFFIO_TX_B60N/DQ8B/B_DQ_35IO_4A/DIFFIO_RX_B59P/DQS8B/B_DQS_4IO_4A/DIFFIO_RX_B62N/DQ8B/B_DQ_36IO_4A/DIFFIO_TX_B61P/DQ8B/B_DQ_38IO_4A/DIFFIO_RX_B62P/DQ8B/B_DQ_37IO_4A/DIFFIO_TX_B64N/DQ8B/B_DQ_39IO_4A/DIFFIO_TX_B64P/DQ8B/B_DM_4IO_3B/DIFFIO_TX_B24N/DQ3B/B_CA_1AF6IO_3B/DIFFIO_TX_B24P/DQ3B/B_CA_0AE6SRAM_D0SRAM_D1SRAM_D2SRAM_D3SRAM_D4SRAM_D5SRAM_D6SRAM_D7SRAM_D8SRAM_D9SRAM_D10SRAM_D11SRAM_D12SRAM_D13SRAM_D14SRAM_D15HDMI_TX_VS HDMI_TX_HSHDMI_TX_D19HDMI_TX_D1HDMI_TX_D2HDMI_TX_D3HDMI_TX_D5HDMI_TX_D6HDMI_TX_D9HDMI_TX_D11HDMI_TX_D18HDMI_TX_D17HDMI_TX_D16HDMI_TX_D15HDMI_TX_D12HDMI_TX_D14TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NIO_6A/DIFFIO_TX_R34P/DQ5R E24IO_6A/DIFFIO_TX_R34N/DQ5R E25IO_6A/DIFFIO_RX_R35P/DQ5R K24IO_6A/DIFFIO_TX_R36P/DQ5R F24IO_6A/DIFFIO_RX_R35N/DQ5R K23IO_6A/DIFFIO_TX_R36N/DQ5R G24IO_6A/DIFFIO_RX_R37P/DQS5R L23IO_6A/DIFFIO_TX_R38PH23IO_6A/DIFFIO_RX_R37N/DQSN5R L24IO_6A/DIFFIO_TX_R38N/DQ5R H24IO_6A/DIFFIO_RX_R39P/DQ5R H22IO_6A/DIFFIO_TX_R40P/DQ5R F23IO_6A/DIFFIO_RX_R39N/DQ5R J23IO_6A/DIFFIO_TX_R40N G22IO_6A/DIFFIO_RX_R41P L22IO_6A/DIFFIO_RX_R41NK21IO_5B/DIFFIO_RX_R15P/DQ2R R24IO_5B/DIFFIO_TX_R16P/DQ2RU24IO_5B/DIFFIO_RX_R15N/DQ2R R25IO_5B/DIFFIO_TX_R16NV25IO_5B/DIFFIO_TX_R18P/DQ3R AB26IO_5B/DIFFIO_TX_R18N/DQ3R AA26IO_5B/DIFFIO_RX_R19P/DQ3R T26IO_5B/DIFFIO_RX_R19N/DQ3RR26IO_5B/DIFFIO_RX_R21P/DQS3R P21IO_5B/DIFFIO_TX_R22PW25IO_5B/DIFFIO_RX_R21N/DQSN3RP22IO_5B/DIFFIO_TX_R22N/DQ3R W26IO_5B/DIFFIO_RX_R23P/DQ3R N25IO_5B/DIFFIO_TX_R24P/DQ3RU25IO_5B/DIFFIO_RX_R23N/DQ3R P26IO_5B/DIFFIO_TX_R24NU26Audio CODECHSMC_D0HSMC_RX_n0HSMC_RX_p0HSMC_RX_n10HSMC_RX_p10HSMC_RX_p9HSMC_RX_n9HSMC_RX_p11HSMC_RX_n11HSMC_RX_n12HSMC_RX_p12HSMC_RX_p1HSMC_RX_n1HSMC_RX_n7HSMC_RX_p7HSMC_TX_n8HSMC_TX_p8HSMC_TX_p9HSMC_TX_n9HSMC_TX_p10HSMC_TX_n10HSMC_TX_p0HSMC_TX_n0HSMC_TX_p2HSMC_TX_n2HSMC_TX_n1HSMC_TX_p1HSMC_TX_n4HSMC_TX_p4HSMC_TX_n3HSMC_TX_p3HSMC_TX_n6HSMC_TX_p6AUD_XCK 13AUD_DACDAT 13AUD_ADCDAT 13AUD_DACLRCK 13AUD_ADCLRCK13AUD_BCLK 13TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NIO_7A/DIFFIO_TX_T6N/DQ1T/T_DQ_35IO_7A/DIFFIO_RX_T7P/DQ1T/T_DQ_33IO_7A/DIFFIO_TX_T8P/DQ1T/T_DQ_34IO_7A/DIFFIO_RX_T7N/DQ1T/T_DQ_32IO_7A/DIFFIO_TX_T10P/DQ2T/T_DM_3IO_7A/DIFFIO_TX_T10N/DQ2T/T_DQ_31IO_7A/DIFFIO_RX_T11P/DQ2T/T_DQ_29IO_7A/DIFFIO_TX_T12P/DQ2T/T_DQ_30IO_7A/DIFFIO_RX_T11N/DQ2T/T_DQ_28IO_7A/DIFFIO_RX_T13P/DQS2T/T_DQS_3IO_7A/DIFFIO_RX_T13N/DQSN2T/T_DQSN_3IO_7A/DIFFIO_TX_T14N/DQ2T/T_DQ_27IO_7A/DIFFIO_RX_T15P/DQ2T/T_DQ_25IO_7A/DIFFIO_TX_T16P/DQ2T/T_DQ_26IO_7A/DIFFIO_RX_T15N/DQ2T/T_DQ_24IO_7A/DIFFIO_TX_T22P/T_RESETN B15IO_7A/DIFFIO_TX_T22N/DQ3T/T_DQ_19C15IO_7A/DIFFIO_RX_T23P/DQ3T/T_DQ_17C14IO_7A/DIFFIO_TX_T24P/DQ3T/T_DQ_18A8IO_7A/DIFFIO_RX_T23N/DQ3T/T_DQ_16D15IO_7A/DIFFIO_TX_T24N/GNDA9IO_7A/DIFFIO_TX_T26P/DQ4T/T_DM_1C9IO_7A/DIFFIO_TX_T26N/DQ4T/T_DQ_15B9IO_7A/DIFFIO_RX_T27P/DQ4T/T_DQ_13E16IO_7A/DIFFIO_TX_T28P/DQ4T/T_DQ_14D10IO_7A/DIFFIO_RX_T27N/DQ4T/T_DQ_12D16IO_7A/DIFFIO_TX_T28N/DQ4T/T_CKE_0C10IO_7A/DIFFIO_RX_T29P/DQS4T/T_DQS_1N12IO_7A/DIFFIO_TX_T30P/T_CKE_1B10IO_7A/DIFFIO_RX_T29N/DQSN4T/T_DQSN_1M12IO_7A/DIFFIO_TX_T30N/DQ4T/T_DQ_11A11IO_7A/DIFFIO_RX_T31P/DQ4T/T_DQ_9F16IO_7A/DIFFIO_TX_T32P/DQ4T/T_DQ_10E10IO_7A/DIFFIO_RX_T31N/DQ4T/T_DQ_8E15IO_7A/DIFFIO_TX_T32N/GNDE11IO_7A/DIFFIO_TX_T34P/DQ5T/T_DM_0B12IO_7A/DIFFIO_TX_T34N/DQ5T/T_DQ_7A13IO_7A/DIFFIO_RX_T35P/DQ5T/T_DQ_5G12IO_7A/DIFFIO_TX_T36P/DQ5T/T_DQ_6A12IO_7A/DIFFIO_RX_T35N/DQ5T/T_DQ_4F12IO_7A/DIFFIO_TX_T36N/DQ5T/T_ODT_1B11IO_7A/DIFFIO_RX_T37P/DQS5T/T_DQS_0M11IO_7A/DIFFIO_TX_T38P/T_ODT_0C13IO_7A/DIFFIO_RX_T37N/DQSN5T/T_DQSN_0L11IO_7A/DIFFIO_TX_T38N/DQ5T/T_DQ_3C12IO_7A/DIFFIO_RX_T39P/DQ5T/T_DQ_1E13IO_7A/DIFFIO_TX_T40P/DQ5T/T_DQ_2D11IO_7A/DIFFIO_RX_T39N/DQ5T/T_DQ_0D13GXB L2 is C7 FPGA onlyHSMC_GXB_RX_p3HSMC_GXB_RX_n3HSMC_GXB_TX_p3HSMC_GXB_TX_n3SMA_GXB_TX_pSMA_GXB_RX_pREFCLK_p1REFCLK_n1SMA_GXB_RX_p SMA_GXB_RX_nSMA_GXB_TX_p SMA_GXB_TX_n TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.GXB_L1GXB_L25CGXFC5C6F27C7NREFCLK1LNP6REFCLK1LP N7GXB_TX_L5NK1GXB_TX_L5P K2GXB_RX_L5P,GXB_REFCLK_L5P M2GXB_RX_L5N,GXB_REFCLK_L5N M1GXB_TX_L4N P1GXB_TX_L4P P2GXB_RX_L4P,GXB_REFCLK_L4P T2GXB_RX_L4N,GXB_REFCLK_L4N T1GXB_TX_L3N W3GXB_TX_L3P W4GXB_RX_L3P,GXB_REFCLK_L3P V2GXB_RX_L3N,GXB_REFCLK_L3N V1RREF_TLB1GXB_RX_L8n,GXB_REFCLK_L8n D1GXB_RX_L8p,GXB_REFCLK_L8p D2GXB_RX_L7n,GXB_REFCLK_L7n F1GXB_RX_L7p,GXB_REFCLK_L7p F2GXB_RX_L6n,GXB_REFCLK_L6n H1GXB_RX_L6p,GXB_REFCLK_L6p H2GXB_TX_L6p G4GXB_TX_L6n G3GXB_TX_L7p E4GXB_TX_L7n E3GXB_TX_L8p C4GXB_TX_L8nC3REFCLK2Lp M6REFCLK2LnL5R1990R2042KJ12J7R1980C1360.01uVCCIO = 3.3VVCCIO = 3.3VVCCIO = 2.5VVCCIO = 2.5VHSMC_CLKIN_p1HSMC_CLKIN_n1CLOCK_50_B7A HSMC_CLKIN_n1HSMC_CLKIN_n2CLOCK_50_B5B CLOCK_50_B6A GPIO0GPIO2I2C_SDACLOCK_125_n GPIO8GPIO7GPIO6GPIO4CLOCK_50_B8A HSMC_CLKIN0HSMC_CLKIN_p2HSMC_CLKIN_n2VCC2P5VCC2P5VCC2P5VCC3P3VCC2P5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C2690.1u 10V C2680.1u 10VC1110.1u 10VR188100R197100R200100R11220KC2670.1u 10V Bank 5BBank 6ABank 7ABank 8A5CGXFC5C6F27C7NIO_5B/CLK7P,FPLL_BR_FBP/DIFFIO_RX_R9P T21IO_5B/CLK7N,FPLL_BR_FBN/DIFFIO_RX_R9NT22IO_5B/CLK6P/DIFFIO_RX_R17P R20IO_5B/CLK6N/DIFFIO_RX_R17NP20IO_5B/FPLL_BR_CLKOUT0,FPLL_BR_CLKOUTP,FPLL_BR_FB/DIFFIO_TX_R20P/DQ3RIO_5B/FPLL_BR_CLKOUT1,FPLL_BR_CLKOUTN/DIFFIO_TX_R20N/DQ3RIO_6A/CLK5P/DIFFIO_RX_R25P N20IO_6A/CLK5N/DIFFIO_RX_R25NM21IO_6A/FPLL_TR_CLKOUT0,FPLL_TR_CLKOUTP,FPLL_TR_FB/DIFFIO_TX_R28P/DQ4RIO_6A/FPLL_TR_CLKOUT1,FPLL_TR_CLKOUTN/DIFFIO_TX_R28N/DQ4RIO_6A/CLK4P,FPLL_TR_FBP/DIFFIO_RX_R33P K25IO_6A/CLK4N,FPLL_TR_FBN/DIFFIO_RX_R33NK26IO_7A/CLK11P/DIFFIO_RX_T25P G15IO_7A/CLK11N/DIFFIO_RX_T25NG14IO_7A/CLK10P/DIFFIO_RX_T33P H12IO_7A/CLK10N/DIFFIO_RX_T33N G11IO_8A/CLK9P/DIFFIO_RX_T41P N9IO_8A/CLK9N/DIFFIO_RX_T41NM10IO_8A/FPLL_TL_CLKOUT0,FPLL_TL_CLKOUTP,FPLL_TL_FB/DIFFIO_TX_T44P/DQ6T/T_CA_2IO_8A/FPLL_TL_CLKOUT1,FPLL_TL_CLKOUTN/DIFFIO_TX_T44N/DQ6T/T_CA_3IO_8A/CLK8P,FPLL_TL_FBP/DIFFIO_RX_T49P L8IO_8A/CLK8N,FPLL_TL_FBN/DIFFIO_RX_T49N K9U20MSEL Settings : MSEL[4:0] = 10010 Active serial (AS)(x1 and x4),no compression, no security, fast PORFPGAHSMCSD_DAT0SD_DAT1SD_DAT2SD_DAT3SD_CMD SD_CLK MSEL0MSEL1MSEL3MSEL2MSEL4BST_TDI BST_TDO JTAG_FPGA_TDI FPGA_CONF_DONE FPGA_nSTATUS FPGA_nCONFIGHSMC_JTAG_TDI HSMC_JTAG_TDO JTAG_FPGA_TDO FPGA_nCEGPIO34GPIO11GPIO23GPIO22GPIO21GPIO20GPIO19GPIO17GPIO15GPIO14GPIO13GPIO12GPIO31VCC3P3VCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R1730DNI R520R1770DNI RN2210K12345678Bank 9A5CGXFC5C6F27C7NIO_3A/DATA6/DIFFIO_RX_B1N/DQ1B T7IO_3A/DATA5/DIFFIO_TX_B2NU7IO_3A/DATA8/DIFFIO_RX_B1P/DQ1B T8IO_3A/DATA7/DIFFIO_TX_B2P/DQ1B V8IO_3A/DATA10/DIFFIO_RX_B3N/DQSN1B W8IO_3A/DATA9/DIFFIO_TX_B4N/DQ1BAB6IO_3A/DATA12/DIFFIO_RX_B3P/DQS1B Y9IO_3A/DATA11/DIFFIO_TX_B4PAA6IO_3A/DATA14/DIFFIO_RX_B5N/DQ1B R10IO_3A/DATA13/DIFFIO_TX_B6N/DQ1B AA7IO_3A/CLKUSR/DIFFIO_RX_B5P/DQ1B R9IO_3A/DATA15/DIFFIO_TX_B6P/DQ1B Y8IO_5A/PR_REQUEST/DIFFIO_TX_R1N/DQ1RAC23IO_5A/CVP_CONFDONE/DIFFIO_TX_R3N/DQ1RAA23IO_5A/nPERSTL1/DIFFIO_RX_R6N/DQSN1R U22MSEL0M7CONF_DONE A6MSEL1L6nSTATUS B5nCED5MSEL2A2MSEL3K5nCONFIG F5MSEL4J5IO_3A/PR_DONE/DIFFIO_RX_B7NR8IO_3A/PR_READY/DIFFIO_TX_B8N/DQ1BAD6IO_3A/PR_ERROR/DIFFIO_RX_B7P P8IO_3A/DIFFIO_TX_B8P/DQ1BAD7R530VCCAUX_VCCA_FPLLVCC2P5VCC3P3VREF_3P3_VCCIOTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NVCC VCC VCC VCC VCC VCCVCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCCPGM AA9VCCPGM W22VCCPGM F8VCCBATVCCPD5B R21VCCPD6A J22VCCPD6A L21VCCPD7A8AF19VCCPD7A8A F17VCCPD7A8A F13VCCPD7A8A F11VCCPD7A8A F9VCCA_FPLL W7VCCA_FPLL J6VCCA_FPLLY21VCCA_FPLL G21VCC_AUX G9VCC_AUX E14VCC_AUX G19VCC_AUXAB20VCC_AUX AB14VCC_AUX AA85CGXFC5C6F27C7NVCCIO4A U18VCCIO4A AE22VCCIO4A AA20VCCIO4A AD19VCCIO4A Y17VCCIO4A W14VCCIO4A AC16VCCIO4A AF15VCCIO4A AB13VCCIO4A AE12VCCIO5A V21VCCIO5A AB23VCCIO5B N26VCCIO5B T25VCCIO5B W24VCCIO5B R22VREFB4AN0AD15VREFB5AN0W23VREFB5BN0P25CYCLONE V GX XCVR PowerU14-122.5V2.5Vfor VCCIO_VCCPD 2.5Vfor VCCIO_VCCPD 3.3Vfor VCCIO 1.2VVCCH_GXBL VCCAUX_VCCA_FPLLVCC1P2VCC3P3VCC2P5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C2204.7n 50VC25522n 16VC1674.7u 6.3VC2510.01u 50VC1830.01u 50VC2320.47u 10VC1804.7n 50VC1782.2n 50VC1940.01u 50VC1701u 10VC1720.47u 10VC2504.7n 50VC1764.7u 6.3VC10510u 6.3VC2492.2n 50VC1910.01u 50VC1044.7u 6.3VC1820.1u 10VC2460.01u 50VC1900.1u 10VC25322n 16VC1851u 10VC2590.1u 10VC2130.01u 50VC25247n 25VNote:Place decoupling caps near LPDDR2 power pins place close to DDR2 chipDDR2LP_CKE0DDR2LP_CS_n0DDR2LP_DM0DDR2LP_DM1DDR2LP_DQ2DDR2LP_DQ3DDR2LP_DQ4DDR2LP_DQ5DDR2LP_DQ6DDR2LP_DQ7DDR2LP_DQ8DDR2LP_DQ9DDR2LP_DQ10DDR2LP_DQ11DDR2LP_DQ12DDR2LP_DQ13DDR2LP_DQ14DDR2LP_DQ15DDR2LP_DM3DDR2LP_DQ31DDR2LP_DQ24DDR2LP_DQ25DDR2LP_DQ26DDR2LP_DQ27DDR2LP_DQ28DDR2LP_DQ29DDR2LP_DQ30DDR2LP_DM2DDR2LP_DQ16DDR2LP_DQ17DDR2LP_DQ19DDR2LP_DQ18DDR2LP_DQ20DDR2LP_DQ22DDR2LP_DQ21DDR2LP_DQ23DDR2LP_ZQ0DDR2LP_ZQ1DDR2LP_CKE1DDR2LP_CS_n1DDR2LP_CK_nVCC1P2TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C1450.1u 10V240DNIC1580.1u 10VR169 4.7K R1684.7K DNIC15510u 10VDNU0A1DNU1A2NC0A3NC1A4NC2A5NC3A6NC4A7NC5A8NC6A9NC7A10DNU2A22DNU3A23DM2AB20DNU10AB22DNU8AB1DNU9AB2CS#0AB3CS#1AB4NC/ZQ AC11CKE0AC3CKE1AC4DNU4B1DNU5B2DM3B20DNU6B22DNU7B23NC8B4NC9B6NC10B7NC11B9NC12D1NC13D2NC14E1NC15E2NC16F1NC17G1NC18G2NC19H1NC20H2NC21J1NC22K1NC23K2NC24L1DM1L23DM0N23ZQ P1DQ30A13DQ29A14DQ26A16DQ25A17DQ16AB12DQ18AB14DQ20AB15DQ22AB17DQ17AC13DQ19AC14DQ21AC16DQ23AC17DQ31B12DQ28B14DQ27B15DQ24B17DQ15C22DQ14D23DQ12E22DQ13E23DQ11F22DQ10G23DQ8H22DQ9H23DQ6T22DQ7T23DQ5U22DQ4V23DQ2W22DQ3W23240C4010u 10VC14622n 16VMT42L128M32D1LF-25WTVSS A21VSS AA1VDD2AA2VDD2AB10VSS AB11VDD2AB21VSS AC21VSS AC5VSS/NC AC9VSS B10VDD2B21VSS/NC B5VSS/NC B8VSS C1VDD2C2VSS/NC F2VSS/NCJ2VDD2L22VSS M2VSS M23VSS R1VDD2R2VSSQ A12VSSQ A15VSSQ A18VDDQ AA22VDDQ AB13VDDQ AB16VDDQ AB19VSSCA AB7VSSQ AC12VSSQ AC15VSSQAC18VSSQ C23VDDQ D22VSSQ F23VDDQ G22VSSQ J23VDDQ K22VSSQ P23VDDQ R22VSSQ U23VSSCA V1VDDQ V22VSSQ Y23C1594.7u 6.3VC16222n 16VC1530.1u 10VSD_DAT1SD_DAT0SD_DAT3SD_DAT2SD_CMDSD_DAT2SD_DAT3SD_CMD SRAM_CE_n SRAM_OE_n SRAM_WE_n SRAM_LB_n SRAM_UB_nSRAM_D11SRAM_D12SRAM_D15SRAM_D13SRAM_D9SRAM_D10SRAM_D14SRAM_CE_nSRAM_A14SRAM_A16SRAM_A15SRAM_A17SRAM_A13VCC3P3_SDVCC3P3_SDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R185RN1010K 12345678L2130ohm, 3ASRAM 256Kx16nCE 6G N D 12nWE 17A1326A1427A1828D930D1031D1132G N D34D1235D1336D1437D1538nLB 39nUB40nOE 41A1542A1643A1744123J6c k e tDAT3CMD DAT2R11710KDefault :I2C Address 0x34/35AUD_XCKAUD_BCLKAUD_DACDAT AUD_DACLRCK AUD_ADCDATAUD_ADCLRCK I2C_SDA_3P3I2C_SCL_3P3AUD_MUTEAUD_CSBAUD_I2C_SDAT AUD_I2C_SCLK AGND AGNDVCC_AUDDVCC_AUDDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R18680R1502K DNIC22100u C13410u 6.3VU7SSM2603BCLK 7H P V D D 12XTO 2D C V D D 3MICBIAS21MICIN22RLINEIN 23LLINEIN24MUTE25CSB26SDIN27SCLK28ROUT 17A V D D18A G N D19VMID 20LOUT16P G N D 15RHPOUT 14LHPOUT13XTI/MCLK 1D G N D4RECLRC11RECDAT 10D B V D D5CLKOUT6PBDAT 8PBLRCK 9E P _G N D 29C1390.1u 10V DNIR2822R20330R3022R1512K DNIR174.7KC151u 10VDefault :I2C Address 0x72/0x73Pull-high to FPGA bank I/O powerNote:Place Capacitor near ADV7513 DVDD pinsHDMI_TX_CLK HDMI_TX_DE HDMI_TX_VS HDMI_TX_HS HDMI_HPD CEC_CLKHDMI_SPDIF HDMI_MCLK HDMI_I2S0HDMI_I2S1HDMI_I2S2HDMI_I2S3HDMI_SCLK HDMI_LRCLKHDMI_TX_D17HDMI_TX_D18HDMI_TX_D19HDMI_TX_D20HDMI_TX_D21HDMI_TX_D22HDMI_TX_D23CLK_12MHz VCC1P8VCC1P8_DVDDVCC1P8VCC1P8_AVDDVCC1P8_DVDDVCC1P8_PVDDVCC1P8_AVDDVCC3P3_DVDD VCC3P3_DVDDVCC1P8_AVDDVCC1P2VCC1P8_DVDDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C3510u 6.3VR15349.9DNI R12822DNIR1242K X312MHZDNIVCC 4OUT 3GND2EN1C1490.1u 10VL910uH74479887310AC1520.1u 10VC1380.1u 10VR129R1252K DNIC1290.1u 10VDNIC1300.1u 10VL410uHR80R138887ADV7513BSWZD1743D1842D1941D2040D2139D2238D2337CLK 53DE63HSYNC 64VSYNC 2R_EXT 14HPD 16SPDIF 3MCLK 4I2S05I2S16I2S27I2S38SCLK 9LRCLK 10PD22DVDD_3V 29DVDD11DVDD211DVDD331DVDD451PVDD 12BGVDD 13AVDD115AVDD219AVDD325EPAD_GND65R130R127TX_n TX_p RX_p RX_nDefaultJumper OpenHSMC_RX_p5HSMC_RX_n5HSMC_TX_p5HSMC_TX_n5HSMC_CLKIN_p1HSMC_CLKIN_n1NET_HSMC_GXB_TX_p0NET_HSMC_GXB_TX_n0HSMC_TX_n0HSMC_CLKOUT_n1HSMC_CLKOUT_p1HSMC_RX_p6HSMC_RX_n6HSMC_TX_n6HSMC_TX_p6HSMC_RX_n1HSMC_RX_p1HSMC_RX_p7HSMC_RX_n7HSMC_TX_p7HSMC_TX_n7HSMC_TX_p1HSMC_TX_n1HSMC_RX_p2HSMC_RX_n2HSMC_CLKOUT0HSMC_JTAG_TCKHSMC_CLKIN0HSMC_JTAG_TDI HSMC_JTAG_TMS HSMC_JTAG_TDO HSMC_D1HSMC_TX_p2HSMC_TX_n2HSMC_GXB_TX_p0HSMC_GXB_TX_n0HSMC_D2HSMC_RX_p3HSMC_RX_n3HSMC_RX_p0HSMC_GXB_RX_n0HSMC_GXB_RX_p0HSMC_RX_n0HSMC_TX_n3HSMC_TX_p3HSMC_D3HSMC_RX_n4HSMC_RX_p4HSMC_TX_p4HSMC_TX_n4HSMC_TX_p0HSMC_D0HSMC_SDAHSMC_SCLI2C_SDA I2C_SCLHSMC_SDA HSMC_SCLVCC12_HSMCVCC12_HSMCVCC3P3_HSMCVCC3P3_HSMCVCC12_HSMCVCC3P3VCC3P3_HSMCTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R460C12010u 35V C2650.1u 25VTP1Dummy PinC2660.1u 25V R18722R49JP13HEADER 212C11510u 6.3V C24822u 25V 116416816516616729293131333335353737393930303232343436363838404041414343454547474949515153535555575759596161636365656767696971717373757577777979818183838585878789899191939395959797999942424444464648485050525254545656585860606262646466666868707072727474767678788080828284848686888890909292949496969898100100161161162162163163164164R18622XJ1Jumper-2.54mmVREF ADC_IN1ADC_IN2ADC_IN3ADC_IN5ADC_IN6ADC_IN7ADC_IN0ADC_IN4ex_ADC_SDO ADC_VREFADC_REFCOMP ex_ADC_CONVST ex_ADC_SDIex_ADC_SCK TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C7810u 10V C800.1u 10VCH0CH1CH2CH3CH4CH5CH6CH7COMG N DG N D G N DG N DG N D G N DVREFREFCOMP SDISCKSDOCONVD V D DO V D DA V D D 1A V D D 1U17LTC2308CUF22232412345625910112018781516171412131921C1021n 50VC981n 50V C8210u 10VC991n 50V C1001n 50V TP13TP_YELLOWC790.1u 10VR8649.9C872.2u 10VC1011n 50V C840.1u 10VGPIO_D0GPIO_D2GPIO_D4GPIO_D6GPIO_D8GPIO_D1GPIO_D3GPIO_D5GPIO_D7GPIO_D9GPIO_D14GPIO_D12GPIO_D10GPIO_D18GPIO_D16GPIO_D22GPIO_D20GPIO_D24GPIO_D15GPIO_D13GPIO_D11GPIO_D19GPIO_D17GPIO_D23GPIO_D21GPIO_D25GPIO_D26GPIO_D28GPIO_D30GPIO_D32GPIO_D34GPIO_D33GPIO_D31GPIO_D29GPIO_D27GPIO_D35GPIO_D7GPIO_D11GPIO_D15GPIO_D19GPIO_D23GPIO_D27GPIO3GPIO20GPIO_D20Arduino_IO0CPU_RESET_n Arduino_Reset_nAnalog_In1Analog_In2Analog_In3Arduino_Reset_nAnalog_In0Arduino_AD4_IO14Arduino_AD5_IO15Analog_In6Analog_In7Arduino_IO11Arduino_IO12Arduino_IO13Arduino_Reset_nArduino_IO15Arduino_IO14GNDVCC5VCC12VCC3P3VCC3P3VCC5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.BAT54S D15BAT54S123JP14HEADER 2x3123456D38BAT54S123BAT54S D13BAT54S123R22222R2242.2K DNIRN418BAT54S BAT54S RN1118BAT54S D45BAT54S123BAT54S 3BAT54S R2252.2K DNID43BAT54S123JP9BOX Header 2X20M 12345678910111312141618202224262715171921232528293133353739303234363840Reserved 6x6mm tact switchSW1SW0SW2SW3BTN3BTN1BTN2BTN0VCC1P2VCC1P2TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.RN2318BUTTON1TACT SW DNI4321SW0SLIDE SW12345BUTTON3TACT SW DNI4321SW2SLIDE SW12345SW1SLIDE SW12345RN311RN2610K12345678BUTTON2TACT SW DNI4321RN2412012345678B2A2E1G0F0E0B1C1D1F1G1C0B0A0D0A1C2D2E2F2HEX0_D0HEX0_D1HEX0_D2HEX0_D3HEX0_D4HEX0_D5HEX0_D6HEX1_D0HEX1_D1HEX1_D3HEX1_D4HEX1_D2HEX1_D5HEX1_D6HEX2_D0HEX2_D1HEX2_D2HEX2_D3HEX2_D4HEX2_D5GPIO22GPIO23GPIO24GPIO25GPIO26GPIO27GPIO28GPIO30GPIO29HEX2_D0HEX3_D0HEX2_D1HEX3_D1HEX2_D2HEX2_D3HEX2_D4HEX2_D5HEX2_D6LEDR0LEDG1LEDG2LEDG3LEDG4LEDG5LEDG6LEDG7LEDR1LEDR2LEDR3LEDR4LEDR5LEDR6LEDR7VCC_HEX2VCC_HEXVCC_HEXVCC_HEX2VCC_HEXTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.e d dpc g b f a CA1CA2HEX07Segment Display12345610987ON1S2121615RN1868012345678e d c b f a CA1CA2HEX2124561098RN1668012345678RN1568012345678ON1S1SW DIP-812345678161514131211109RN1912345678e d dpc g b f a CA1CA2HEX17Segment Display12345610987R2010R20510kRN1768012345678Self Powered and Internal OSCUSB to UARTUART_CTSRX_LEDTX_LEDUART_RTSFT232_DP FT232_DM UART_RX UART_TX UART_RESET_nUART_RXLED UART_TXLED UART_CTS UART_RTSUART_CTSUART_RTSUART_PW_ENVCC5_UARTVCC3P3_UARTVCC5_UARTVCC5_USB_UARTVCCIO_UART VCC2P5VCC5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.DNITP_YELLOWU4FT232R VCC19VCCIO 1G N D 4RESET 183V3OUT16USBDP 14USBDM15TXD 30RXD 2CTS#8RTS#32DSR#6DTR#31DCD#7RI#3CBUS022NC15A G N D 24NC212NC313NC525NC629NC423OSCI 27OSCO 28G N D 17G N D 20TEST26CBUS121CBUS311CBUS210CBUS49E P _G N D33R71M R14310kC140.1u 25VTPD2E001DRLRU2VCC 1NC2IO13GND4IO25D9LEDR21R220DNIC314.7u 6.3VL24321R142 4.7K C60.1u 25VR23R15733C330.1u 25VC80.1u 25V DNITP_YELLOWD8LEDG21R15633C254.7u 6.3VC270.1u 25VL2230ohm, 3A10kC184.7u 6.3VRamp TimeTsoft-start = 0.99 msec3.3V / 5AVCC1P1_PGOOD VCC3P3_PGOOD VCC3P3_INTVCCVCC3P3_INTVCCVCC12VCC1P1_INTVCCVCC3P3_INTVCCTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.LTC3605EUF#PBFITH 6CLKIN24S G N D22P G N D 110E P _P G N D 225SW616FB4RT 1CLKOUT23R66316K R6910KC623.3n 50VR471050VU11PHMODE 2MODE 3TRACK/SS 5P V I N 117P V I N 218BOOST20PGOOD8SW111SW212SW313SW414SW515SW616RUN 7VON 9SVIN19I N T V C C21C4822u 25V C570.1u 25VD12CMDSH-3C17339p 50V 12.4K DNIC721n 50VR182100K+C656.3V330u 1239p 50V DNIR1940DNIPOWER SWC5022u 25VXJ3Jumper-2.54mmC58 2.2u 6.3VC7168p 50V2.5VTantalum330u 2L121uH 744311100R6715KR18411.5K DNIC510.1u 25VRamp Time = 1.2 msecVCC3P3VCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R109200KC561u 10VC532.2u 10VLT3080-1U10OUT11OUT22OUT33SET 4IN28IN17NC6V_CONTROL 5OUT49DNIC494.7n 50VC521u 10VR44180KC5422u 6.3VC1124.7n 50V6.3VXJ6Jumper-2.54mmGND13URXFOSC_24BST_TMS URD UTXE UWR URXFSI_WU UD7EEPDATA EEPCSEEPCLK USB_RESETnBST_TDI BST_TDO ISP_TCK ISP_TMS ISP_TDI ISP_TDOUSB_RESETn TRGNST TRGNCSO TRGASDO TRGDCLK TRGNCE TRGTDO TRGTMSTRGOE TRGOEFPGA_nCEUART_RESET_nPWRONPWRON BST_TCK VCC5_USBVCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.FT245BLLQFP-32TEST31RXF#12EEDATA 2XTIN 27XTOUT 28G N D17D718RD#16WR 15TXE#14A G N D 29EECS 32EESK 1RESET#4SI/WU 11PWREN#10USBDM 8G N D 9R14110KR2070DNIR13310KR1480DNIC14347p 50VBAT54SDW 123R13027EPM240M100C4N IO-B1-10G1IO-B1-11G2IO-B1-12F3IO-B1-13H1IO-B1-14H3IO-B1-15H2IO-B1-16L1IO-B1-17L2IO-B1-18K3IO-B1-19L3IO-B1-20K4IO-B1-21L4IO-B1-22K5IO-B1-23L5IO-B1-24L6IO-B1-25K6IO-B1-26J6IO-B1-27L7IO-B1-28K7IO-B1-29/DEV_OE L8IO-B1-30/DEV_CLRn K8IO-B1-31L9IO-B1-32K9IO-B1-33L10IO-B1-34K10IO-B1-35L11IO-B1-8/GCLK1E1IO-B1-9F1TCK K1TDI J2TDO K2TMS J1G N D I N TG 4G N D I N T E 8IO-B1-36J5IO-B1-37J7R14422。

基于Altera Cyclone系列FPGA器件实现开发板的方案设计

基于Altera Cyclone系列FPGA器件实现开发板的方案设计1 引言现场可编程门阵列(FPGA,Field Programmable Gate Array)的出现是超大规模集成电路(VISI)技术和计算机辅助设计(CAD)技术发展的结果。

FPGA器件集成度高、体积小,具有通过用户编程实现专门应用的的功能。

它允许电路设计者利用基于计算机的开发平台,经过设计输入、仿真、测试和校验,直到达到预期的效果。

利用FPGA可以大大缩短系统的研制周期,减少资金投入。

更吸引人的是采用FPGA器件可以将原来的电路板级产品集成为芯片级产品,从而降低了功耗,提高了可靠性,同时还可以很方便的对设计进行在线修改。

FPGA 器件成为研制开发的理想器件,特别适于产品的样机开发和小批量生产,因此人们也把FPGA称为可编程的ASIC。

可以断定FPGA在结构、密度、功能、速度和灵活性方面将得到进一步的发展。

随着工艺和结构的改进,FPGA的集成度将进一步提高,性能将进一步完善,成本将逐渐下降,在现代电子系统设计中将起到越来越重要的作用。

2 硬件电路设计及原理2.1 硬件电路整体结构本设计的开发板电路包括6个部分:下载电路、下载接口、FPGA、电源电路、和扩展接口。

其电路结构框图如下:2.1.1主芯片EPlC3T144C8Altera Cyclone系列FPGA是A1tera公司2003年9月份推出的,基于1.5v,O.13μm 工艺,Cyclone是一个性价比很高的FPGA系列。

其中EPlC3T144是Cyclone系列中的一员,共有2910逻辑单元,59904RAM bits,1个PLLs,最多有104个用户I/O,可以说这款FPGA的资源非常丰富,足够满足大型设计的需要。

本设计选用Altera公司的Cyclone系列芯片,芯片型号为EPlC3T144C8,因为该芯片是Altera公司推出的低价格、高容量的FPGA,其以较低的价格、优良的特性及丰富的片上资源在实际应用中被广泛的采用,这些都是其他同类产品无法相比的。

Altera新增五款基于Cyclone V FPGA的低成本开发套件,起价49美元

Altera新增五款基于Cyclone V FPGA的低成本开发套件,起价49美元在公共开发环境支持下,系列产品优化了功耗、成本和性能Altera公司今天宣布,新增五款基于其Cyclone V FPGA的低成本开发套件。

这些新开发套件入门价格只有49美元,方便了设计人员以高性价比方式开始FPGA开发。

Altera为业界提供了最全面的系列低成本解决方案,考虑客户独特的设计需求而优化了功耗和性能。

系列产品包括CPLD、FPGA和SoC,均由Quartus II开发环境提供支持。

Altera 系列产品的密度范围在业界最广,封装选择最多,适用于多种大批量应用和系统。

Altera产品市场资深总监Patrick Dorsey评论说:“Altera一直致力于为业界提供最优低成本系列解决方案。

其他供应商此时的重点已经不是低成本产品,迫使客户使用不同的设计环境,而Altera仍然关注交付多种系列产品,在公共设计环境支持下,优化工艺技术,帮助客户迅速提高产量。

”最全面的系列开发套件Altera及其合作伙伴提供30多种开发套件,主要面向Altera的系列低成本CPLD、FPGA和SoC。

套件为开发低成本和低功耗系统级设计,迅速得到结果提供了快速简单的方法。

五款Cyclone V FPGA 28 nm新开发套件最近加入到系列产品中,进一步方便了系统设计,支持设计人员以高性价比方式集成Cyclone V FPGA。

这些新开发套件包括:• 49美元的Arrow BeMicro CV开发套件,安装了Cyclone V E FPGA。

这一低成本开发套件支持开发人员迅速启动其Cyclone V FPGA工程。

• 179美元的TerASIC Cyclone V GX入门套件包括了高速中间连接器(HSMC)和Arduino连接器,支持客户迅速构建其低功耗视频系统,包括,汽车辅助驾驶和人机接口等。

• 349美元的Altima Cyclone V GX开发套件为开发低成本、低功耗、基于FPGA的系统级设计提供了快速简单的方法。

FPGA的数字脉冲延时发生器设计

敬请登录网站在线投稿(t o u g a o.m e s n e t.c o m.c n)2021年第2期79F PG A的数字脉冲延时发生器设计陈泽洋(天津大学理学院,天津300072)摘要:本文主要介绍了一种数字式脉冲延时发生器的设计方法,该方案是基于A l t e r a(被I n t e l收购)的C y c l o n e I V系列F P G A实现的,为了同时满足高延时分辨率与大的可调范围,采用了粗细结合的延时方法,粗延时通过计数器法实现,细延时通过A D9501专用延时芯片实现;为了让用户与系统进行通信,在F P G A内部构建了N i o s I I软核处理器,并且编写软件程序实现人机交互㊂对系统的关键模块进行了仿真,仿真结果显示模块设计符合需求,最终延时系统可以实现精度为16.5p s㊁可调范围约为1.1s的延时㊂关键词:F P G A;A D9501;延脉冲发生时器;N i o s I I中图分类号:T N7文献标识码:AD e s i g n o f D i g i t a l P u l s e D e l a y G e n e r a t o r B a s e d o n F P G AC h e n Z e y a n g(S c h o o l o f S c i e n c e,T i a n j i n U n i v e r s i t y,T i a n j i n300072,C h i n a)A b s t r a c t:I n t h e p a p e r,a d e s i g n m e t h o d o f d i g i t a l p u l s e d e l a y g e n e r a t o r i s d e s i g n e d,w h i c h i s b a s e d o n A l t e r a's c y c l o n e I V s e r i e s F P G A.I n o r d e r t o m e e t t h e r e q u i r e m e n t s o f h i g h d e l a y r e s o l u t i o n a n d l a r g e a d j u s t a b l e r a n g e,c o m b i n e t h e c o a r s e d e l a y a n d f i n e d e l a y,t h e c o a r s e d e-l a y i s r e a l i z e d b y c o u n t e r m e t h o d,a n d t h e f i n e d e l a y i s r e a l i z e d b y A D9501s p e c i a l d e l a y c h i p.I n o r d e r t o e n a b l e u s e r s t o c o mm u n i c a t e w i t h t h e s y s t e m,N i o s I I s o f t c o r e p r o c e s s o r i s b u i l t i n F P G A,a n d s o f t w a r e p r o g r a m i s w r i t t e n t o r e a l i z e h u m a n-c o m p u t e r i n t e r a c t i o n.T h e k e y m o d u l e s o f t h e s y s t e m a r e s i m u l a t e d,a n d t h e s i m u l a t i o n r e s u l t s s h o w t h a t t h e m o d u l e d e s i g n m e e t s t h e r e q u i r e m e n t s.T h e f i n a l d e l a y s y s t e m c a n a c h i e v e a d e l a y a c c u r a c y o f16.5p s a n d a d y n a m i c r a n g e o f1.1s.K e y w o r d s:F P G A;A D9501;p u l s e d e l a y g e n e r a t o r;N i o s I I0引言脉冲延时发生器作为一种时序同步装置在激光系统[1-2]㊁雷达系统[3]㊁飞行时间质谱仪[4-5]等领域应用广泛,它可以对触发信号进行延时后输出脉冲信号,用户可以设定延时的大小㊂延时的分辨率与延时的可调范围是衡量其性能的两个重要参数,可以实现脉冲延时的方法有计数器法㊁存储器法[6]㊁专用延时芯片[7]等方法㊂计数器法与存储器法可以实现可调范围比较大的延时,不过延时精度由于受到时钟频率的限制只能做到纳秒量级,专用延时芯片法的延时精度可以做到皮秒量级,不过可调范围在微秒量级㊂F P G A是一种可编程逻辑器件,用户可以通过V e r i l o g H D L等设计文件在F P G A内部设计所需要的逻辑电路,与A S I C相比具有设计周期短㊁设计灵活等优点㊂本文介绍的延时脉冲发生器以A l t e r a(被I n t e l收购)的C y c l o n e I V系列F P G A为核心,采用粗细结合的延时方案,并且利用N i o s I I软核处理器用于系统控制,实现了脉冲延时发生器的设计㊂1基于F P G A的脉冲延时发生器整体设计延时系统的工作模式分为内触发模式与外触发模式㊂系统的设计框图如图1所示㊂工作在内触发模式时,触发信号由系统内部产生,用户可以设定触发信号的频率大小㊂工作在外触发模式时,触发信号由外部提供㊂整个延时系统的延时由粗延时部分和细延时部分组成,粗延时利用计数器法实现㊂计数器法的延时分辨率由采样时钟决定,本系统的采样时钟通过将外部50MH z晶振倍频得到,最终倍频数由系统能运行的最大时钟频率决定㊂细延时是利用A D9501实现的,A D9501通过8位控制字对单位粗延时进一步细分,得到16.5p s延时分辨率㊂P C机通过C P2102串口桥接芯片将设定的延时信息发送给N i o s I I软核处理器,延时信息包含用户设定的粗延时以及细延时,N i o s I I将粗延时信息经由P I O I P核传递到粗延时模块,细延时信息被转换成8位控制字,输出80M i c r o c o n t r o l l e r s &E m b e d d e d S ys t e m s 2021年第2期w w w .m e s n e t .c o m .c n图1 脉冲延时发生器的整体设计框图到A D 9501对其细延时进行控制㊂触发信号依次经过粗延时模块与A D 9501模块最终实现脉冲延时㊂其中内触发源模块㊁粗延时模块㊁N i o s I I 模块是在一块F P G A 内部㊂2 内触发源模块设计内触发源模块的作用是在内触发模式下提供触发信号㊂该模块的时序图如图2所示㊂图2 内触发源模块时序图c l k 为输入模块的时钟信号,d i v 为用户设定的分频数,c o u n t e r 为对时钟信号进行计数的计数器,o u t p u t 为最终输出的触发信号㊂当时钟信号到来时,启动计数器对时钟信号进行计数㊂当计数器计数的值等于d i v 时,将输出信号取反,同时计数器置零;当计数器的值不等于分频数时,输出保持不变,计数器持续对时钟信号进行计数㊂用户通过设置d i v 的值改变计数器的计数值,进而控制输出信号的跳变,从而达到对时钟信号进行分频的目的㊂3 粗延时模块设计粗延时模块负责对外部触发信号进行粗略延时,然后将延时后的脉冲输出到A D 9501进行细延时㊂该模块由输入时钟信号c l k ㊁触发信号t r i ㊁两个计数器p u l s e 1和pu l s e 2㊁两个计数器c o u n t e r 1和c o u n t e r 2组成㊂A D 9501的内部有一个斜波发生器,每次触发信号到来之后斜波发生器电压从0开始上升,当斜波发生器电压值与D A C 设定值相等时,拉高延时输出引脚电平,该斜波电压的置零是通过复位引脚实现的,拉复位引脚时,斜波发生器进行复位,如果不对其进行复位,则当下一个脉冲到来时,斜波发生器的电压是大于D A C 电压的,延时输出一直处于高电平状态,所以不能输出延时脉冲㊂由此可知,粗延时模块应该输出两个脉冲给A D 9501,分别为pu l s e 1和p u l s e 2,一个用于触发细延时,另一个用于将A D 9501斜波发生器置零㊂通过设定p u l s e 1与p u l s e 2之间的时间间隔就可以控制延时脉冲的脉宽大小㊂c o u n t -e r 1和c o u n t e r 2分别是延时计数器和脉宽计数器,通过延时控制字d e l a y 和脉宽控制字w i d t h 控制计数器计数到多少时输出脉冲信号,该模块的时序如图3所示㊂经过实验得知粗延时模块能够运行的最大时钟为240MH z,则粗延时分辨率为1/240MH z =4.2n s ,c o u n t e r 的位数设为28位,则最大延时为4.2n s ˑ228ʈ1.1s㊂图3 粗延时模块时序图4 细延时模块设计细延时模块是以A D 9501为核心实现的,它是在粗延时的分辨率基础上进一步细分实现更高分辨率的延时,A D 9501通过8位控制字对4.2n s 进行细分,则细分后的延时分辨率为4.2n s /28-1=16.5n s ㊂A D 9501的最小延迟(t P D )是触发电路延迟㊁斜坡发生器延迟和比较器延迟的总和㊂触发电路延迟和比较器延迟是固定的,斜坡发生器延迟是受线性斜坡变化率和偏移电压值影响的㊂最大延迟是t P D 和满量程(t D F S )的总和㊂斜坡发生器延迟是斜坡从其重置电压转换到D A C 电压所需的时间,D A C 电压由用户通过数字输入进行编程㊂满量程延迟(t D F S )由电容C e x t 和电阻R s e t 决定,范围为2.5n s ~10μs ,它们的关系如下:t D F S =R s e t ˑ(C e x t +8.5p F )ˑ3.84当满量程延时小于等于326n s 时,接C e x t 的引脚应当悬空;当满量程延时超过326n s 时,C e x t 引脚与电源之间可以最大加500p F 的电容㊂R s e t 的取值范围为50Ω~10k Ω㊂本设计想要实现满量程4.2n s 的延时,R s e t 大小应设置为128Ω,接C e x t 的引脚悬空㊂5 N i o s I I 控制模块设计从经济与系统复杂程度方面考虑,选用N i o s I I 软核处理器来实现P C 机对于系统的控制㊂N i o s I I 需要实现的功能为从P C 接收用户设定的延时值,然后将延时值发送给延时模块㊂利用Q s ys 自带I P 核可以实现加速设计,敬请登录网站在线投稿(t o u ga o .m e s n e t .c o m.c n )2021年第2期81图4 控制模块程序流程图实现数据接收与传输所需添加的主要I P 核有U A R T 与P I O ㊂P C 通过C P 2102将数据发送到U A R T I P 核的读寄存器,U A R T I P 核的r x d a t a寄存器接收到数据,使能读取中断,并将读取的数据在中断服务子程序中赋值给P I O ,就实现了P C 对延时系统的控制,图4为控制模块的程序流程图㊂6 关键模块仿真结果本设计的两个关键模块为内触发源模块与粗延时模块,编写测试文件对两个模块分别进行仿真,内触发源模块的仿真结果如图5所示㊂图5中信号从上到下依次是时钟信号c l k㊁复位信号r s t ㊁分频数d i v ㊁计数器c o u n t e r ㊁输出信号o u t ㊂可以看出,当分频数依次为0㊁1㊁2㊁3时,输出信号o u t 分别经过1个时钟周期㊁2个时钟周期㊁3个时钟周期㊁4个时钟周期发生电平的跳变,因此仿真结果表明,可以通过分频控制字d i v 来控制输出信号的分频数㊂粗延时模块的仿真结果如图6所示㊂图中信号从上到下依次是时钟信号c l k ㊁复位信号r s t ㊁触发信号t r㊁延时计数器c o u n t ㊁脉宽计数器c o u n t 1㊁延时控制字d e l a y㊁脉宽控制字w i d t h ㊁延时脉冲信号p u l s e 1㊁脉宽控制信号pu l s e 2㊂从仿真结果可以看出,当延时控制字为13㊁脉宽控制字为4时,触发信号到来之后的13个时钟信号输出p u l s e 1,pu l s e 1之后4个时钟信号输出p u l s e 2,该模块的设计符合需求㊂图5内触发源模块仿真结果图6 粗延时模块仿真结果7 性能比较将计数器法㊁专用延时芯片法㊁本设计的方法从可调范围㊁延时分辨率㊁功能扩展三个方面进行比较,结果如表1所列㊂表1 三种延时方法比较延时方法可调范围延时分辨率功能扩展计数器法m s ,s 量级n s 量级无法功能扩展专用延时芯片μs 量级ps 量级无法功能扩展本设计s 量级ps 量级便于功能扩展由表1中可知,本设计方法在保持计数器法与专用延时芯片方法优点的同时弥补了两种方法各自的不足,并且基于F P G A 灵活的特点,可以通过设计逻辑电路与编写N i o s I I 软核模块程序进行再次开发,以满足其他系统集成或者功能升级的需求㊂8 结 语目前国内的商用脉冲延时发生器主要依赖国外进口,价格一般在几万元到十几万元不等,价格昂贵并且性价比不高,本设计的脉冲延时发生器在满足高精度与大的可调范围的同时,成本方面也有很大的优势,整个系统制作成本仅为400元左右㊂在当今环境下,自主设计的脉冲延时发生器在商业与科技领域均具有重要意义㊂参考文献[1]蒋军敏,刘进元,刘百玉,等.用于激光打靶装置中的85敬请登录网站在线投稿(t o u ga o .m e s n e t .c o m.c n )2021年第2期85节的非线性特性耗费时间,无论系统的非线性多严重,均能按特定的关系进行转换㊂经数值分析将优化后的数据代入式(1)及联立式(1)和式(7),线性补偿前后物体位移y 和像点位移x 的关系如图6所示㊂y =270192x14216.256-398.32x+e d(8)图6 线性补偿前后物体位移y 和像点位移x 的关系5 结 语本文从反射式激光三角法测量原理公式㊁测量范围㊁分辨率及结构参数优化出发,用工程软件MA T L A B 对系统的各个参数之间的约束关系进行了分析与优化,使得参数优化过程得以简化,同时在实际中可根据器件因素和测量范围的要求不同随时改变,提高了设计的灵活性,降低了设计初期的费用,最后通过数值分析了造成物体位移与像点位移呈非线性的原因,并用线性补偿的方法使物体位移与像点位移线性输出,从而提高了测距传感器线性度与精度,降低了系统误差,实现了高精度大位移的测量㊂参考文献[1]王晓嘉,高隽,王磊.激光三角法综述[J ].仪器仪表学报,2004(S 2):601604,608.[2]L a r s L i n d n e r ,O l e g S e r g i y e n k o ,J u l i o C R o d r ígu e z Q u i ño n e z ,e t a l .M o b i l e r o b o t v i s i o n s y s t e m u s i n g c o n t i n u o u s l a s e r s c a n n i n gf o r i n d u s t r i a l a p pl i c a t i o n [J ].T h e I n d u s t r i a l R o b o t ,2016,43(4):360369.[3]S u Z h i q i ,H e Q i n g,X i e Z h i .I n d i r e c t m e a s u r e m e n t o f m o l t e n s t e e l l e v e l i n t u n d i s h b a s e d o n l a s e r t r i a n g u l a t i o n [J ].T h e R e -v i e w o f s c i e n t i f i c i n s t r u m e n t s ,2016,87(3):035117.[4]宋腾,张凤生,任锦霞.直射式激光位移传感器光束入射角对测量精度的影响[J ].机械,2017,44(2):3741.[5]Z h u a n g B H.N o n c o n t a c t m e a s u r e m e n t o f s c r a t c h o n a i r c r a f t s k i n s [J ].A p p l i e d l a s e r ,1997(2):4936.[6]任伟明,孙培懋,王亚雷,等.一种标定三角测量法激光位移计的方法[J ].光学技术,1997(3):1113,16.[7]赵景海,孙飞显.基于残差补偿的激光位移传感器测距方法[J ].计算机工程,2018,44(10):298302.[8]曹红超,陈磊,王波,等.一种改进型高精度激光三角位移传感器的结构设计研究[J ].激光杂志,2007(6):1415.[9]X u e l i H a o ,A i m i n S h a ,Z h a o yu n S u n ,e t a l .L a s e r b a s e d m e a s u r i n g m e t h o d f o r m e a n j o i n t f a u l t i n g va l u e o f c o n c r e t e p a v e m e n t [J ].O p t i k I n t e r n a t i o n a l J o u r n a l f o r L i gh t a n d E -l e c t r o n O pt i c s ,2016,127(1):274278.[10]胡纪五,史雪飞.仪表线性化优化设计[J ].电测与仪表,2000(2):58.[11]卢治功,贺鹏,职连杰,等.基于最小二乘法多项式拟合三角测量模型研究[J ].应用光学,2019,40(5):853858.[12]姜庆胜,计时鸣,张利.基于计算机视觉的机械零件平面曲线检测和识别研究[J ].机电工程,2005(7):47.樊鹏辉(硕士研究生),主要研究方向为传感器技术;杨光永(副教授),主要研究方向为传感器技术㊁机器人技术;程满(硕士研究生),主要研究方向为A G V 路径规划;刘叶(硕士研究生),主要研究方向为电机控制;徐天奇(教授),主要研究方向为传感器技术㊁自动化㊂(责任编辑:薛士然 收稿日期:2020-09-11) 新型同步系统的研究[J ].光子学报,2002(3):381383.[2]D T i a n ,G Y a n g .D e s i g n a n d d e v e l o p m e n t o f a m i n i a t u r e d i gi t a l d e l a y g e n e r a t o r f o r l a s e r i n d u c e d b r e a k d o w n s p e c t r o s c o p y[J ].I n s t r u m e n t a t i o n s c i e n c e &t e c h n o l o g y,2015(43):115124.[3]S Z h a o l i n ,L N a n ,W Y i n a n .H i g h r e s o l u t i o n p r o gr a mm a b l e d i g i t a l d e l a y g e n e r a t o r d e s i gn a n d r e a l i z a t i o n [C ]//2010I n -t e r n a t i o n a l C o n f e r e n c e o n I n t e l l i g e n t S y s t e m D e s i gn a n d E n -g i n e e r i n g A p p l i c a t i o n I E E E C o m p u t e r S o c i e t y,2010.[4]C L F e n g ,L G a o ,J H L i u .L a s e r m a s s s p e c t r o m e t r yf o r o n -l i n e d i ag n o s i s o f r e a c t i v e p l a s m a s w i th m a n y s p e ci e s [J ].R e -v i e w o f S c i e n t i f i c I n s t r u m e n t s ,2011(6):261434.[5]S V K o v t o u n ,R D E n gl i s h ,R J C o t t e r .M a s s c o r r e l a t e d a c c e l -e r a t i o n i n a r e f l e c t r o n MA L D I T O F m a s s s pe c t r o m e t e r :A n a p p r o a c hf o r e n h a n c e d r e s o l u t i o n o v e r a b r o a d m a s s r a ng e [J ].J o u r n a l o f th e A m e ri c a n S o c i e t y f o r M a s s S p e c t r o m e t r y,2002(13):135143.[6]邱有刚,黄建国,李力.基于F P G A 数字延迟单元的实现和比较[J ].电子测量技术,2011,34(9):6568.[7]马艳喜.数字延时器A D 9501的性能及其应用[J ].电子元器件应用,2002,4(11):2728.陈泽洋,主要研究方向为快点子学与离子光学㊂(责任编辑:薛士然 收稿日期:2020-08-19)。

Cyclone IV FPGA 器件系列概述

30

高速收发器 ( 注释 6)

2

4

4

4

8

8

8

8

收发器最大数据速率 (Gbps)

2.5

2.5

2.5

3.125

3.125

3.125

3.125

3.125

PCIe(PIPE) 硬核 IP 模 块

1

1

1

1

1

1

1

1

用户 I/O 块

9

9

9

11

11

11

11

11

( 注释 7) ( 注释 7) ( 注释 7) ( 注释 8) ( 注释 8) ( 注释 8) ( 注释 8) ( 注释 8)

? 1?:Cyclone IV FPGA 器件系列概述

封装矩阵

Altera 公司 2011 年 11 月

封装矩阵

表 1-3 列出了 Cyclone IV E 器件封装产品。

表 1-3. Cyclone IV E 器件系列的封装产品 ( 注释 1)

封装

E144

M164

尺寸 ( 毫米 )

22 × 22

资源

逻辑单元 (LE)

6,272 10,320 15,408 22,320 28,848 39,600 55,856 75,408 114,480

嵌入式存储器 (Kbits)

270

414

504

594

594 1,134 2,340 2,745 3,888

嵌入式 18 × 18 乘法器 15

23

56

66

ISO 9001:2008 Registered

Cyclone IV 器件手册, 卷1 2011 年 11 月

简化Xilinx和AlteraFPGA调试过程

QuestaSim

Mentor Graphics公司的仿 真工具,支持多种硬件描述 语言和高级编程语言。

Байду номын сангаас REPORT

CATALOG

DATE

ANALYSIS

SUMMAR Y

04

实际应用案例分析

Xilinx FPGA调试案例

案例描述:某通信系统使用Xilinx FPGA进行信号处理,但在实际应用

Verilog)转换为FPGA配置文件 的工具。

通过使用HST,开发人员可以避 免手动编写低级代码,从而提高

开发效率。

HST还提供了丰富的调试功能, 如仿真、时序分析等,帮助开发

人员快速定位和解决问题。

嵌入式逻辑分析仪

嵌入式逻辑分析仪是一种集成在 FPGA板上的高性能逻辑分析工

具。

它能够捕获FPGA上的信号,并 将其转换为易于分析的格式,如

SUMMAR Y

05

结论与展望

当前研究的局限性和未来研究方向

当前研究主要集中在FPGA设计过程中的调试技术,但实际应用中可能还需要考虑其 他因素,如硬件加速、功耗优化等。

未来研究可以进一步探索如何将调试技术与硬件优化技术相结合,以提高FPGA设计 的效率和性能。

针对不同领域的应用需求,研究具有针对性的调试方法和技术,以满足特定领域的 性能和功能要求。

中遇到性能瓶颈。

调试过程

使用ChipScope Pro工具捕获FPGA 内部信号,分析数据传输瓶颈。

优化HDL代码,提高逻辑运算效率。

调整时钟网络,减少时钟偏斜。

结果:性能提升30%,满足了实时信 号处理需求。

Altera FPGA调试案例

cyclone4简介

Cyclone IV 器件手册, 卷1

Altera 公司 2011 年 11 月

第 1 章 :Cyclone IV FPGA 器件系列概述

1–3

器件资源

■ 高达 532 个用户 I/O ■ 高达 840 Mbps 发送器 (Tx), 875 Mbps Rx 的 LVDS 接口 ■ 支持高达 200 MHz 的 DDR2 SDRAM 接口 ■ 支持高达 167 MHz 的 QDRII SRAM 和 DDR SDRAM

? 1?:Cyclone IV FPGA 器件系列概述

封装矩阵

Altera 公司 2011 年 11 月

封装矩阵

表 1-3 列出了 Cyclone IV E 器件封装产品。

表 1-3. Cyclone IV E 器件系列的封装产品 ( 注释 1)

封装

E144

M164

尺寸 ( 毫米 )

22 × 22

最大用户 I/O ( 注释 9)

72

150

150

290

310

310

475

475

表 1-2 注释:

(1) 应用于 F169 和 F324 封装。

(2) 应用于 F484 封装。

(3) 仅有两个多用途 PLL 可应用于 F484 封装。 (4) 其中两个通用 PLL 可以支持收发器时钟。欲了解详细信息,请参阅 Clock Networks and PLLs in Cyclone IV Devices

ISO 9001:2008 Registered

Cyclone IV 器件手册, 卷1 2011 年 11 月

Subscribe

1–2

第 1 章 :Cyclone IV FPGA 器件系列概述

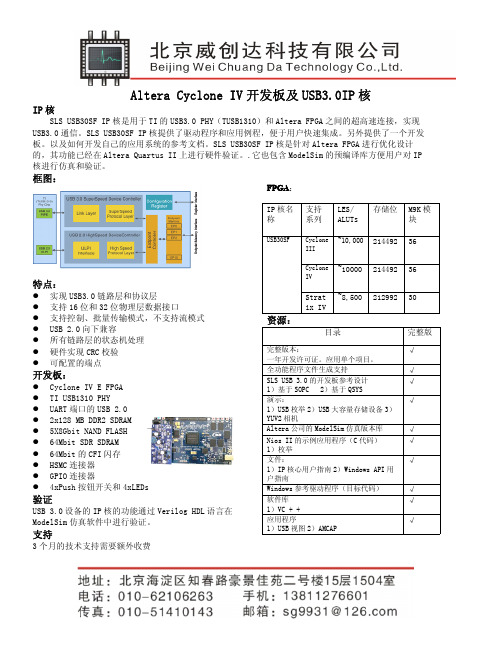

Altera Cyclone IV开发板及USB3.0IP核

完整版 √ √ √ √

开发板:

√ √ √

验证

USB 3.0 设备的 IP 核的功能通过 Verilog HDL 语言在 ModelSim 仿真软件中进行验证。

√ √ √

支持

3 个月的技术支持需要额外收费

Strat ix IV

资源:

目录

完整版本: 一年开发许可证。应用单个项目。 全功能程序文件生成支持 SLS USB 3.0 的开发板参考设计 1)基于 SOPC 2)基于 QSYS 演示: 1)USB 枚举 2)USB 大容量存储设备 3) YUV2 相机 Altera 公司的 ModelSim 仿真版本库 Nios II 的示例应用程序(C 代码) 1)枚举 文件: 1)IP 核心用户指南 2)Windows API 用 户指南 Windows 参考驱动程序(目标代码) 软件库 1)VC + + 应用程序 1)USB 视图 2)AMCAP

框图:

FPGA: IP 核名 称

USB30SF

支持 系列

Cyclone III Cyclone IV

LES/ ALUTs

~10,000

存储位

M9K 模 块 36 36 30

214492 214492 2:

� � � � � � � � � � � � � � � � � 实现 USB3.0 链路层和协议层 支持 16 位和 32 位物理层数据接口 支持控制、批量传输模式,不支持流模式 USB 2.0 向下兼容 所有链路层的状态机处理 硬件实现 CRC 校验 可配置的端点 Cyclone IV E FPGA TI USB1310 PHY UART 端口的 USB 2.0 2x128 MB DDR2 SDRAM 5X8Gbit NAND FLASH 64Mbit SDR SDRAM 64Mbit 的 CFI 闪存 HSMC 连接器 GPIO 连接器 4xPush 按钮开关和 4xLEDs

Cyclone IV系列FPGA的配置方式及其工程应用

( 1 . S c h o o l o f C o mp u t e r S c i e n c e, Xi a n Un i v e r s i t y o f P o s t s a n d T e l e c o mmu n i c a t i o n s , Xi a n 7 l O 0 6 1, C h i n a;

Ke y wor d s:F P GA;C y c l o n e I V;c o n i f g u r a t i o n s c h e me ;J T AG;a c t i v e s e i r a l ;a c t i v e p a r a l l e l ;p a s s i v e s e i r a l ;f a s t p a s s i v e p a r a l l e l

Har d wa r e Tec h n i q ue

C y c l o n e I V系列 F P G A 的配置方式及其 工程应 用

赵 勇 , 孟 李 林 , 李 小 龙 ( 1 . 西安 邮 电大 学 计 算 机 学 院 , 陕 西 西安 7 1 0 0 6 1 ; 2 . 西安 邮 电大 学 电子 工 程 学院 , 陕 西 西安 7 1 0 0 6 1 )

该 系列 F P G A 配置 方 式 的 灵 活 多样 性 。 关 键 词 :F P G A; C y c l o n e I V; 配置 方 式 ; J T AG; 主 动 串行 ; 主动 并 行 ; 被 动 串行 ; 快 速 被 动 并 行

中 图 分 类 号 :T P 3 6 8 文 献 标 识 码 :A 文 章 编 号 :1 6 7 4 — 7 7 2 0( 2 0 1 3) 1 9 — 0 0 2 5 — 0 4

Cyclone V开发板

Cyclone V开发板Altera 的Cyclone V 实现了业界最低的系统成本和功耗,其性能水平使得该器件系列成为突出您大批量应用优势的理想选择。

与前几代产品相比,总功耗降低了40%,具有高效的逻辑集成功能,提供集成收发器型号以及具有基于ARM® 的硬核处理器系统(HPS) 的SoC FPGA 型号。

Cyclone® V FPGA为业界提供系统成本最低、功耗最低的FPGA 解决方案,以及小尺寸封装选项。

这些优点结合其性能和逻辑利用率特性,实现了能够突出您大批量应用优势的器件。

内核ARM+FPGA 架构中精度可调数字信号处理(DSP) 模块、多端口存储器控制器和多功能PCI Express Gen2 增强IP 等丰富的硬核知识产权(IP) 模块帮助您以更低的系统总成本和更短的设计时间完成更多的工作。

作为一种可以马上使用的功能,这些硬核IP 模块简化了您的开发过程,进一步降低了功耗,在增强存储器控制器方面,相对于软核逻辑占用了更少的电路板空间。

而且还节省了很多的逻辑资源,从而用于实现独特的功能,突出您的产品优势。

Cyclone V 收发器低成本收发器各有不同。

借助Altera Cyclone® V FPGA 系列的灵活性,您可以全面利用所有收发器资源,在体积更小、成本更低的器件中实现设计。

Cyclone V FPGA 能够非常灵活的通过增强构建模块以尽可能低的功耗来实现独立协议和专用协议。

Cyclone V SoCFPGA使用宽带互联干线链接,Altera SoC 集成了基于ARM 的硬核处理器系统(HPS),包括处理器、外设和存储器接口。

Cyclone® V SoC 在一个基于ARM 的用户可定制芯片系统(SoC) 中集成了分立处理器、FPGA 和数字信号处理(DSP) 功能,帮助您降低了系统功耗、系统成本,减小了电路板面积,提高了系统性能。

Altera FPGA 同时实现了硬核知识产权(IP) 的性能和低功耗特性以及可编程逻辑的灵活性。

Altera新Cyclone IV

Altera 新Cyclone IV

Altera 新Cyclone IV FPGA 拓展了Cyclone FPGA 系列

Altera 拓展其成功的Cyclone FPGA 系列并延续其收发器技术领先优势,于今天发布Cyclone IV FPGA 新系列。

在移动视频、语音和数据访问以及高质量3D 图像对低成本带宽需求的推动下,Cyclone IV FPGA 系列增加了对主流串行协议的支持,不但实现了低成本和低功耗,而且还提供丰富的逻辑、存

储器和DSP 功能。

Cyclone IV FPGA 系列有两种型号。

Cyclone IV GX 器件具有150K 逻辑单元(LE)、6.5-Mbit RAM、360 个乘法器,以及8 个支持主流协议的集成3.125- Gbps 收发器,这些协议包括千兆以太网(GbE)、SDI、CPRI、V-by-One,Cyclone IV GX 还为PCI Express (PCIe)提供硬核IP。

这些低功耗器件封装大小只有11x11 mm,非常适合无线、固网、广播、工业和消费类等市场的低成本、小型封装应用。

Cyclone IV E 器件前所未有的同时实现了低成本、高性能和低功耗,在手持式软件无线电等低功耗应用中,其功耗比以前的Cyclone 产品低25%。

Altera 产品和企业市场副总裁Vince Hu 评论说:“Cyclone IV FPGA 将会进一步拓展FPGA 的应用领域。

Cyclone IV FPGA 成本足以和ASSP 相竞争,其灵活性是无与伦比的,很显然,它是下一代设计的最佳选择。

设计人员采

用Cyclone IV 系列的创新功能很容易支持多种协议,简化电路板设计,开发。

Altera量产发售低成本低功耗Cyclone IV FPGA

件 模 块 , 提 供 监 测 An ri 件 堆 栈 的重 要 洞 察 能 力 , 可 dod软 包 括 An r i 统 级 事 件 分 析器 。 d od系

A tr tai V F GA 通 过 l aSrt I P e x

A 8 8 , 款 全新 的监 控 器 为设 计 师 提供 了他 们 开发 完 整 D 2 0这 电池监 控 和 保 护 系 统 前 端 所 需 的 最 终 解 决 方 案 。 A 88 D 20

为 集 成式 解 决方 案 , 监控 6个 电 池 单元 的 电 压 和 2路 温 可 度 输 入 。该器 件 由电池 组 供 电 , 以针 对过 压 、 可 过温 或 欠 压 这 3种 状 况 中 的任 何一 种 , 供 共享 式 或单 独 式报 警 。 提

Al r 司 宣布 , t t F GA通 过 Itr k n联 盟 t a公 e Sr i I P a x V nel e a

用 的 硬件 加 速 器 、 立 的 计 算 单 元 以及 D 独 MA 存 储 映 射 ,

实 现 了后 台执 行 F T/ I I 信 号 处 理 工 作 的 能 力 , F F T/I R 可

ADI 出用 于能 源 、 业和 汽 车应 用 的 推 工 锂 电池 监 控 和 保 护 系统

An lgDeie ,Ic 最 新 推 出 的 锂 电 池 监 控 和 保 护 ao vc s n . 系统 , 成 了包 括 电压 和 电流 测 量 、 号 隔离 以 及 安 全 监 集 信

清影 片 的下 载 时 间 长 达 3个 小 时 , 同样 一部 标 清 影 片 的 而 下 载仅 需 要 3 O分 钟 。

altera fpga开发流程

altera fpga开发流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!1. 设计规划确定设计目标和功能需求。

选择合适的 Altera FPGA 器件。

Cyclone IV系列FPGA的配置方式及其工程应用

Cyclone IV系列FPGA的配置方式及其工程应用赵勇;孟李林;李小龙【期刊名称】《微型机与应用》【年(卷),期】2013(000)019【摘要】为了高效正确配置 Altera Cyclone IV 系列 FPGA ,详细研究了该系列FPGA 配置的引脚、方式、原理图、过程、时序和数据格式等,并比较了各配置方式。

同时,通过一个实际工程应用表明该系列 FPGA 配置方式的灵活多样性。

%In order to efficiently and correctly configure the FPGA chip of Altera Cyclone IV series, the FPGA configuration′s pins, scheme, schematic, process, timing, data format is studied in detail and compares the configuration scheme with each other. Meanwhile, the flexibility and diversity of this series FPGA configuration scheme is showed by an engineering application in practical.【总页数】4页(P25-28)【作者】赵勇;孟李林;李小龙【作者单位】西安邮电大学计算机学院,陕西西安 710061;西安邮电大学电子工程学院,陕西西安 710061;西安邮电大学计算机学院,陕西西安 710061【正文语种】中文【中图分类】TP368【相关文献】1.FPGA配置及Cyclone系列PS模式的工程应用 [J], 丛文;李新红2.基于Cyclone IV的单核FPGA远程更新系统设计 [J], 徐晓康; 邵俊波; 赵晓宇; 邱长青3.Altera量产发售低成本低功耗Cyclone IV FPGA [J],4.CycloneⅣ拓展Altera低成本Cyclone FPGA系列 [J], 梦雷5.低成本低功耗Cyclone IV FPGA [J],因版权原因,仅展示原文概要,查看原文内容请购买。

Altera低成本Cyclone Ⅳ FPGA满足高带宽应用需求

Altera低成本Cyclone Ⅳ FPGA满足高带宽应用需求陈楠

【期刊名称】《世界电子元器件》

【年(卷),期】2009(000)012

【摘要】@@ 日前,Altera发布新系列CycloneⅣ FPGA,延续其收发器技术的领先优势.当前移动视频、语音和数据访问以及高质量3D图像对低成本带宽需求与日俱增,与此同时,终端产品市场,如智能电话等领域竞争激烈,价格大幅下降,令成本问题变得愈加敏感.因此,市场需要能即时满足用户需求.并具有低成本高性能的灵活器件,正是看准这一市场趋势,Cydone Ⅳ FPGA应运而生.

【总页数】1页(P24)

【作者】陈楠

【作者单位】

【正文语种】中文

【相关文献】

1.CycloneⅡ FPGA满足低成本大批量应用需求 [J], 李

2.Cyclone Ⅱ FPGA满足低成本大批量应用需求 [J],

3.低成本FPGA应用潜力无限--Altera Cyclone Demo Day集锦 [J], 刘洪

4.Altera新Cyclone IV FPGA抢占ASSP市场满足了大批量、低成本串行协议解决方案需求 [J], 陈颖莹

5.CycloneⅣ拓展Altera低成本Cyclone FPGA系列 [J], 梦雷

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Altera Cyclone IV GX 系列FPGA 开发方案

Altera 公司的Cyclone IV 系列FPGA 包括两个系列:Cyclone IV E 和Cyclone IV GX,具有低成本、低功耗的FPGA 架构,6 K 到150 K 的逻辑单元, 高达6.3 Mb 的嵌入式存储器,小于1.5 W 的总功耗;Cyclone IV GX 器件提供高达八个3.125 Gbps 高速收发器,用于大批量,成本敏感的应用如无线、有线、广播、工业,用户以及通信等行业.本文介绍了Cyclone IV 器件系列主要特性,收发器通道框图以及Cyclone IV GX FPGA 开发套件主要特性,框图,电路图和材料清单.

Altera 新的Cyclone®IV 系列FPGA 器件巩固了Cyclone 系列在低成本、低功耗FPGA 市场的领导地位,并且目前提供集成收发器功能的

型号。

Cyclone IV 器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

Cyclone IV 器件系列是建立在一个优化的低功耗工艺基础之上,并提供以下两种型号:

■Cyclone IV E 最低的功耗,通过最低的成本实现较高的功能性。