Flexible DSP platform for various workload patterns

2、TMS320系列DSP的介绍

OMAP OMAP5910

TM

C5441 532 MIPS C5421 200 MIPS C5420 200 MIPS C5470

C54xTM+ARM7

C54xTM DSP

World’s Most Popular DSP Over 500 Million Shipped $5 Billion in Design-ins

C5407 120 MIPS

Feature Integration

TI所推进的开放式多媒体应用平台 所推进的开放式多媒体应用平台

Open Multimedia Application Platform 处理器

Applications Processor Integrated Baseband and Applications Processor

TV 因特网 浏览器 无线 AP

?

高集成度的OMAP5910提供单片系统功能 提供单片系统功能 高集成度的

OMAP5910 Core TMS320C55xTM DSP

DSP

32 16

3 Timers Watchdog Timer Interrupt Handler 2 McBSP 2MCSI 3 UART 18 GPIO 4 Mailboxes

TMS320C6000DSP的应用

同一应用的多通道复用

蜂窝基站 复用的调制解调器 中央办公交换机 多信道线路回声抵消 多信道话音编码器 Head end cable modem 中央办公XDSL

TMS320C6000DSP的应用(续)

视频图象的压缩、处理、传输

远程监控(PSTN/ISDN/ADSL) 网络视频终端 数码摄像机

Traffic Ctrl 75 MHz

Freescale 微控制器学习套件 (PBMCUSLK) 产品说明说明书

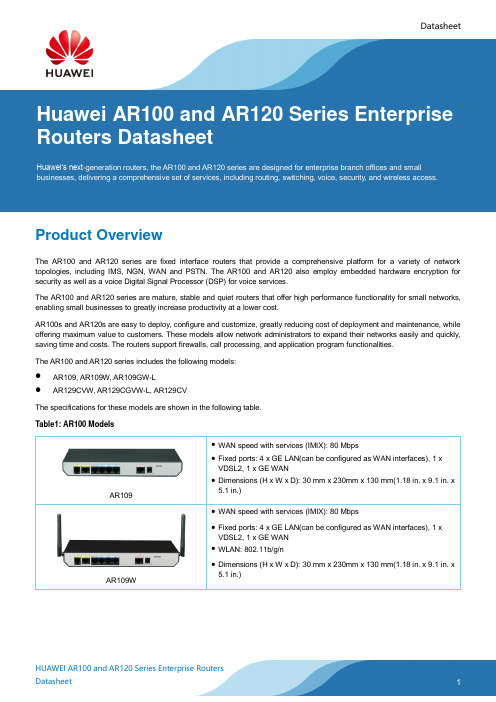

Application Module Student Learning Kit (AP5211SLK Shown)Freescale’s Microcontroller Student Learning Kits The PBMCUSLK can be used standalone for introductory circuit design orused in conjunction with the application modules. The PBMCUSLK allowsyou to easily migrate from one application module to another, providinggreat flexibility in using a range of 8-, 16- and 32-bit microcontrollers.Features:>Integrated HCS12/HCS12X/HCS08USB BDM pod>USB or wall transformer powered(+3.3, +5 or ±15V*)>Replaceable, solderless breadboard>Eight LED’s, push buttons,DIP switches>2-line, 8-character LCD display>Integrated buzzer and potentiometer>COM port (RS-232/MONO8 capable)>Configurable direct connect feature*15V not available when powered from USB BDM Project Board Student Learning Kit (PBMCUSLK)OverviewFreescale’s Microcontroller Student Learning Kits (MCUSLK) now give you the flexibility to choose!The MCUSLKs now come with a feature-rich project board and your choice of an Application Module Student Learning Kit (APSLK).Best of all, the application modules are specifically designed to plug directly into the project board to enrich development.The APSLK can be used standalone for small projects or plugged into the project board. The APSLK contains an application module (microcontroller board), CodeWarrior ®programming development tools, as well as documentation, power and communications cables to provide you with a comprehensive learning environment. Application Modules:>8-bit HCS08• APS08QG8SLK >16-bit HCS12/HCS12X/DSP • APS12DT256SLK • APS12C32SLK • APS12XDT512SLK • AP56F801SLK >32-bit ColdFire ® Processor • AP5211SLK • AP5223SLK (on-chip Ethernet)>RF transceiver**• AP13192USLK **Freescale’s newest SLK keeps you up to date with the latest innovations.Now, wireless development is simple by providing ZigBee™specification-ready RF transceivers, SMAC software andsupport documentation.CodeWarrior Development Studio is a powerful and user-friendly tool suite designed to increase your software development productivity.It shares a common interface across MCU families, making the environmenteasy to use. With unrivaled features such as the Processor Expert TM applicationdesign tool, a highly optimized compiler and the project manager with built-intemplates, the tool suite’s integrated development environment (IDE) allowsthe student to focus on the application software. The CodeWarrior environmentalso features an intuitive graphical source-level debugger with integratedprofiling capabilities, data visualization, instruction set simulation and much more.National Instrument’s Educational Laboratory VirtualInstrumentation Suite (NI ELVIS)is a LabVIEW-based, hands-ondesign and prototyping environment geared for university engineering andscience courses. NI ELVIS consists of LabVIEW virtual instruments, amultifunction data acquisition device and a custom-designed bench-topworkstation. The combination of NI ELVIS with the MCUSLK is ideal forconducting microcontroller instruction, as they provide a powerful developmentand debugging platform through the integrated instrument suite of NI ELVIS.The NI ELVIS integrated instrument suite provides essential functionalityfor teaching microcontrollers, including:> Manual and programmable power supply for poweringthe student project board > Manual and programmable signal generator and digital/analog outputs to provide stimulus to MCU input signals > Multiple instruments to acquire, visualize and analyze MCU output signals > LabVIEW integration to provide flexible design, analysis, testing and reporting Contacts for additional information:Andy Mastronardi Director, University Program Freescale Semiconductor, Inc.******************************John McLellan Applications Engineer Freescale Semiconductor, Inc.********************Ravi Marawar, Ph.D.Academic Program Manager National Instruments*******************A Prototyping Environment for EducationMicrocontroller Student Learning Kit PLUS CodeWarrior Development Tools and National Instruments’Educational Laboratory Virtual Instrumentation Suite (NI ELVIS)Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.© Freescale Semiconductor, Inc. 2006Document Number: STUDENTLEARNFSREV 1Learn More: For more information about other University Program product solutions from Freescale, please visit /universityprogram .The MCUSLKs are excellent teachingsolutions and can be used in a diversemix of coursework, such as:>Electronic Circuit Design I and II>Introduction to Microcontrollers>Microcontroller Interfacingand Applications>Mixed Signals and Circuits>Real-Time Digital Signal Processing>Real-Time Embedded Microcontrollers>Senior Project Design>MechatronicsYour students can also benefit from thereasonable price point and versatilityof MCUSLKs and are encouraged topurchase their own kit to use throughouttheir studies.。

IND560 weighing terminal和Fill-560应用软件商品说明书

2Industrial Weighing and MeasuringDairy & CheeseNewsIncrease productivitywith efficient filling processesThe new IND560 weighing terminal enables you to boost speed and precision during the filling process. Choose from a wide range of scales and weigh modules to connect to the terminal.The versatile IND560 excels in control-ling filling and dosing applications, delivering best-in-class performance for fast and precise results in manual, semi-automatic or fully automatic operations. For more advanced filling, the Fill-560 application software adds additional sequences and component inputs. Without complex and costly programming you can quickly con-figure standard filling sequences, or create custom filling and blending applications for up to four compo-nents, that prompt operators for action and reduce errors.Ergonomic design Reducing operator errors is achieved through the large graphic display which provides visual signals.SmartTrac ™, the METTLER TOLEDO graphical display mode for manual operations, which clearly indicate sta-tus of the current weight in relation to the target value, helps operators to reach the fill target faster and more accurately.Connectivity and reliabilityMultiple connectivity options are offered to integrate applications into your con-trol system, e.g. Allen-Bradley ® RIO, Profibus ®DP or DeviceNet ™. Even in difficult vibrating environments, the TraxDSP ™ filtering system ensures fast and precise weighing results. High reli-ability and increased uptime are met through predictive maintenance with TraxEMT ™ Embedded MaintenanceTechnician.METTLER TOLEDO Dairy & Cheese News 22Speed up manual operations with flexible checkweighingB e n c h & F l o o r S c a l e sHygienic design, fast display readouts and the cutting-edge color backlight of the new BBA4x9 check scales and IND4x9 terminals set the standard for more efficient manual weigh-ing processes.Flexibility through customizationFor optimal static checkweighing the software modules ‘check’ and‘check+’ are the right solutions. They allow customization of the BBA4x9 and the IND4x9 for individual activi-ties and needs, e.g. manual portion-ing or over/under control. Flexibility is increased with the optional battery which permits mobility. Hygienic design Easy-to-clean equipment is vital in food production environments. Both the BBA4x9 scale and the IND4x9 ter-minal are designed after the EHEDGand NSF guidelines for use in hygi-enically sensitive areas.Even the back side of the scale stand has a smooth and closed surfacewhich protects from dirt and allowstrouble-free cleaning.Fast and preciseThe colorWeight ® display with a colored backlight gives fast, clear indication when the weight is with-in, below or above the tolerance.The color of the backlight can be chosen (any mixture of red, greenand blue) as well as the condition itrefers to (e.g. below tolerance). The ergonomic design enables operators to work more efficiently due to less exhaustion.Short stability time, typically between 0.5s and 0.8s, ensures high through-put and increased productivity.PublisherMettler-Toledo GmbH IndustrialSonnenbergstrasse 72CH-8603 Schwerzenbach SwitzerlandProductionMarCom IndustrialCH-8603 Schwerzenbach Switzerland MTSI 44099754Subject to technical changes © 06/2006 Mettler-Toledo GmbH Printed in SwitzerlandYellow – weight above toleranceGreen – weight within toleranceRed – weight below toleranceYour benefits• Fast and precise results and operations • Higher profitability• Ergonomic design, simple to operate • Mobility up to 13h due to optional batteryFast facts BBA4x9 and IND4x9• 6kgx1g, 15kgx2g, 30kgx5g (2x3000d), for higher capacity scales: IND4x9 terminal • Weights and measures approved versions 2x3000e • Functions: simple weighing, static checkweighing, dispensing • Color backlight, bar graph • Tolerances in weight or %• 99 Memory locations • Optional WLAN, battery• Meets the IP69k protection standardsagainst high-pressure and steam cleaning • Complete stainless steel construction Immediate checkweighing resultswith color Weight®EHEDGThe colored backlight of the LC display provides easy-to- recognize indication whether the weight is within the tolerancelimits or not.WLANMETTLER TOLEDO Dairy & Cheese News 23HACCP programs, GMP (Good Manufacturing Practice), pathogen monitoring and good cleaning practices are essential for effective food safety plans. Our scales are constructed for compliance with the latest hygienic design guidelines.Hygienic design to improve food safetyMETTLER TOLEDO supports you in complying with the latest food safety standards like BRC, IFS or ISO 22000 by offering solutions which are:• Compliant with EHEDG (European Hygienic Engineering & Design Group) and NSF (National Sanitation Foundation) guidelines • Full V2A stainless steel construc-tions, optional V4A load plates • Smooth surface (ra < 0.8μm)• Easy-to-clean construction, no exposed holes • Radius of inside corners > 3mm• Ingress protection rating up to IP69k• Hermetically sealed loadcellsYour benefits• Reduce biological and chemical contamination risks • Fast and thorough cleaning procedures • Fulfillment of hygiene regulations • Long equipment life thanks to rugged designGuaranteed serviceKeep your business runningAvoid unnecessary downtime with our wide range of service packages.With a range of innovative service solutions offering regulatory compli-ance, equipment calibration, train-ing, routine service and breakdown assistance, you can profit from sus-tained uptime, together with ongoing performance verification and long life of equipment. There is a range of contract options designed to comple-ment your existing quality systems. Each one offers its own unique set of benefits depending on the equipment and its application.4/serviceFast facts PUA579 low profile scale • 300kgx0.05kg – 1500kgx0.2kg • Open design• Lifting device for easy cleaning • EHEDG conform(300 and 600kg models -CS/-FL)• Free size scale dimensions • Approach rampsExample:PUA579 first EHEDG conform floor scaleEHEDGW e i g h P r i c e L a b e l i n gChallenges faced in the packaging area are:• Responding quickly to retailer demands while improving margins • Improving pack presentation • Minimizing downtime and product giveawaysWith a complete offering of cutting-edge weighing technology, high-per-formance printing, and smart soft-ware solutions, we can help you tackle your labeling challenges whether they are very simple or highly demanding. Intuitive human-machine interfaceTouch-screen operator displays withgraphical icons guide the operator intuitively and reduce nearly every operation to just one or two key-strokes. This interface allows reduced operator training as well as increased operating efficiency.Advanced ergonomics and sani-tary designOur weigh-price labelers are made out of stainless steel for extensive pro-tection against food contamination. Careful attention to hygienic design requirements, with no dead spots and few horizontal parts, ensure that the labelers are easy to clean.Modular designOur product offering includes both manual and automatic weigh-price labelers constructed of flexible “build-ing blocks.” Different combinations and configurations can meet specific budget and operational requirements. METTLER TOLEDO will help you toselect the right:• Scale performance • Display technology • Memory capacity • IT connections • Degree of automation• Integration kitsA large range of options and peripher-als give flexibility for meeting unique requirements e.g. wireless network, hard disks, external keyboards, bar code scanners, RFID transponder, dynamic checkweighing, or metal detection.Weigh-price-labeling Ergonomic, modular, fastEtica 2300 standard manual labelerFor individual weight labeling of various products, high- speed weighing, smart printing and fast product changes are essential. METTLER TOLEDO offers static and automated solutions for both manual and high-speed prepack applica-tions. Choose from our Etica and PAS product range.METTLER TOLEDO Dairy & Cheese News 24Etica 2400i combination with automatic stretch wrappersEtica 2430G multi-conveyer weigh-price labeler rangeEfficient label applicatorsThe unique Etica label applicator (Etica G series) does not require an air compressor, allowing savings on initial equipment expense and ongo-ing maintenance costs. Labels are gently applied in any pre-memorized orientation.PAS systems provide motorized height adjustment and places the label in any corner of the package. Users will have a new degree of freedom in planning their case display layouts to maximize both product presentation and consumer impact.Smart label design tools Retailers want labels to carry clear, correct information, in accordance with their traceability and style requirements. Our solutions are equipped with labeldesign software tools which facili-tate the design of labels customizedfor retailers demands. A touch-screenallows the user to create specific labels– even with scanned elements such aslogos and graphics, pre-programmedlabel templates, or RFID.Versatile integration capabilitiesThe engineers at METTLER TOLEDOworked closely with Europe’s leadingautomatic stretch wrapper suppliersto design performance-enhancingand cost-effective weigh-wrap-labelsystem solutions. Achieving a smallsystem footprint means the systemsrequire only slightly more floor spacethan the wrapper alone.The PAS and Etica weigh-price label-ers can be integrated via TCP/IP ina METTLER TOLEDO scale network,in host computer systems and goodsmanagement systems.Etica weigh-price-labeling systems• Static and automatic weigh-price-labeling up to 55 pieces/min.• Operator displays:– 5.7” color back-lighted LCD (Etica 2300 series)– 10.4” high resolution touch screen (Etica 4400 series)• 3 inch graphic thermal printer (125 to 250mm/sec) withfully programmable label format (max. size 80x200mm)• Data memory:– 64 to 256 Mb RAM– 128 Mb to 10 Gb mass storage– Unlimited number of logo graphics and label descriptions• Interfaces:– 1 serial RS232 interface– Optional second RS232 + RS485 + Centronics port– Ethernet network communication interface(10baseT), TCP/IP, 2 USB ports (1)– Optional: hand-held bar code scanner for automatictraceability data processingGarvens PAS 3008/3012 price labelersEtica 4400METTLER TOLEDO Dairy & Cheese News 2FlexMount ® weigh moduleFast, reproducible and reliable batch-ing and filling are key success factors for your production process. Various factors can affect precision: foam can compromise optical/radar sensors, and solids do not distribute evenly in a tank or silo. Our weighing techno-logy is not affected by these condi-tions and provides direct, accurate and repeatable measurement of mass without media contact. In addition our range of terminals and transmit-ters/sensors enable easy connectivity to your control systems.Key customer benefits• Increased precision and consistencyof your material transfer processes• Faster batching process throughsupreme TraxDSP ™ noise and vibration filtering • Minimal maintenance cost Fast facts terminals/transmitters: PTPN and IND130• Exclusive TraxDSP ™ vibration rejection and superior noise filter-ing system • Easy data integration through a variety of interfaces, including Serial, Allen-Bradley ® RIO, Modbus Plus ®, Profibus ® and DeviceNET • IP65 stainless harsh versionsProcess terminal PTPN• Local display for weight indication and calibration checks • Panel-mount or stainless steel desk enclosureIND130 smart weight transmitter• Direct connectivity where no local display is required • Quick setup and run via PC tool • CalFREE ™ offers fast and easy cali-bration without test weights • DIN rail mounting versionPLCIND1306Tank and silo weighing solutions master your batching processesT a n k & S i l o W e i g h i n g S o l u t i o n sBoost your productivity and process uptime with reliable weighing equipment – improved batching speed and precision, maximum uptime at low maintenance cost.TraxDSP ™ ensures accurate results evenin difficult environments with vibrationPTPN process terminalMETTLER TOLEDO Dairy & Cheese News 27Quality data under control?We have the right solutionConsistently improving the quality of your products requires the ability of efficiently controlling product and package quality parameters in a fast-changing and highly competi-tive environment.Competition in the food industry –with high volumes but tight margins – causes demands for efficient quality assurance systems. Statistical Quality Control (SQC) systems for permanent online information and documenta-tion about your key quality para-meters convert into real cost savings.Our solutions for Statistical Quality Control (SQC) combine ease of opera-tion, quality data management and analysis functionality.• We offer mobile compact solutions with embedded SQC intelligence up to networked systems with an SQL database.• The systems are upgradeable and can be expanded and adapted to meet changing customer needs.• Simple and intuitive prompts guide the user through the sample proc-ess, reducing training costs as well as sampling errors.• Realtime analysis and alarms help to take immediate corrective measures and to save money by reducing overfilling.Throughout the manufacturing pro-cess, METTLER TOLEDO SQC solu-tions analyze your important product and package quality parameters andpresent them the way you want, help-ing to comply to legislation, to control and document your product qualityand your profitability.Metal detectionCheckweigher Sample check ® onlinequality data analysis/dairy-cheeseFor more informationMettler-Toledo GmbH CH-8606 Greifensee SwitzerlandTel. +41 44 944 22 11Fax +41 44 944 30 60Your METTLER TOLEDO contact:1. SevenGo ™ portable pH-meter2. In-line turbidity, pH and conductivity sensors3. DL22 Food and beverage analyzer4. Halogen moisture analyzersA wide range of solutions to improve processes1. Statistical Quality Control/Statistical Process Control2. Process weighing3. Predictive maintenance4. Methods of moisture content determinationShare our knowledgeLearn from our specialists – our knowledge and experience are at your disposal in print or online.Learn more about all of our solutions for the dairy and cheese industry at our website. You can find information on a wide range of topics to improve your processes, including case studies,application stories, return-on invest-ment calculators, plus all the product information you need to make aninformed decision.1 2 341423。

电气自动化专业英语词汇

电气自动化专业英语比较常见的有关词,cylinder 汽缸stopper 死档forklift 叉车chain链条flowchart 流程图pulse frequency modulation control PFMpulse width modulation control P WMtime blet同步带spare parts,buffer备件pneumatic气动electomechanical机电的solenoid 线圈motor 电机valve 阀DD motor 直驱电机(圆盘电机)LIM linear induction motor直线电机SM(servo motor)伺服电机conveyor 传送带inverter 变频器RFID(radio frequency identification)射频识别系统sensor 传感器photoelectric sensor 光电开关light curtain光幕proximity sensor接近开关barcode 条形码barcode reader条码识别器anti-vibration抗震anti-static 抗静电cable tires ,nylon strip(尼龙扎带)电缆扎带wiring duct,wire trough线槽cableveyor电缆拖链optical fiber sensor 光纤传感器optical fiber amp光纤放大器cable marker电缆线号OOBA 开箱检查PLC MAIN BASE plc主基板solt 插槽backboard bus 背板总线POWER SUPPLY MODULE电源模块battary 电池motion module位置模块DC INPUT MODULE DC输入模块DC OUTPUT MODULE DC输出模块anolog output module模拟量输出模块anolog input module模拟量输入模块ETHERNET MODULE以太模块CONNECTOR 连接器terminal resistance终端电阻remote i/o 远程i/ofiber cable 光缆touch panel触摸屏adapater适配器servo amplifer伺服放大器encoder cable编码器电缆rotating transformer旋转变压器motor power plug电机电源插头barker plug制动器插头speed contorler速度控制器breaker,no-fuse breaker,断路器magnatic contactor接触器overload relay 热继led indicator light led指示灯emergency button急停按钮selector switch 选择开关realy继电器timer定时器counter计数器filter滤波器ball screw滚柱丝杠terminal block接线端子排terminal piece终端片symbol bar标志条multilayer sound and light signal lamp多层式声光信号灯buzzer 报警器wire beezer 线鼻子heat shrinkoing tubing热缩管nylon flexible conduit,polyamide tubing波纹管flecible cable曲挠电缆electronic ballast电子镇流器sheathed control cable屏蔽控制电缆horsepower 马力slip转差率SSR(Solid State Relay)固态继电器gain增益power frequency工频harmonic谐波air knife风刀anodizing阳极化DI Water去离子水BJ(bubble jet)二流体exhaust 排气drain排水humidity湿度RH 相对湿度perssure压力temperature 温度negatibe pole负极positive pole正极common 公共端source 原极sink 漏极FFU(fan filter unit)风扇过滤单元intensity,绝缘体conductor导体tact time节拍life time寿命NG(no good)不良品OKREWORK再生laminator,coat,贴膜vaccum真空absolute encoder绝对值编码器ABS absolute position绝对位置INC increase pisition 增量位置velocity速度accelerated time加速时间decelare timeanalog to digital convertet A/Dantenna 天线acceleration加速度stroke 行程bolt螺栓bolt holebypass 旁路interpolation插补100baseT 双绞线电缆相连速率100mbpsthreshole灰度值tolerance容忍度TBD 待决定capacitor电容有功active powerreactive power 无功lower limit 上限upper limit 下限CIM computer integration manufacturing电脑整合制造FA factory automation工厂自动化DIW DE-Ionized Water去离子水UPW Ultra-pure Water超纯水clean room洁净室HEPA high efficient particulate air filter高效粒子空气过滤MGV manual guided vehicle 人力搬运车AGV automatic guided vehicle 自动搬运车IR infra-red 红外线recipe配方maintenance维护exposure 曝光cleaner清洗机etcher蚀刻机plasma等离子vent 破真空CDA compressed dry air压缩干燥空气scribe切割break 掰断grind研磨aligment对位,定位line reactor 进线电抗器tap分接头power factor功率因数no-load空载full load满载lighting光源lens镜头caramer摄像机frame grabber影像采集卡AOI automatic optical inspection自动光学检验line-scan线性扫描,线阵area-scan面阵WD 工作距离Back light 逆光、背光自动聚焦Depth of field 景深pass:指的是用“视觉系统”对被测体进行检测之后的结果为正确。

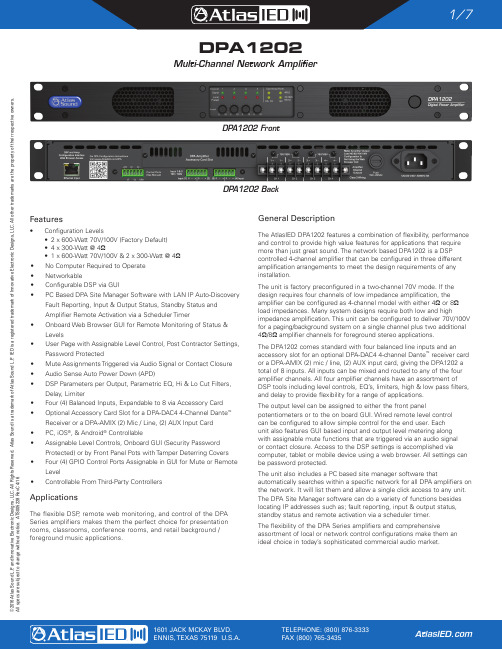

至拉斯声音DPA1202多通道网络音频放大器说明书

o u n d L .P . a n d I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l R i g h t s R e s e r v e d . A t l a s S o u n d i s a t r a d e m a r k o f A t l a s S o u n d L .P . I E D i s a r e g i s t e r e d t r a d e m a r k o f I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l o t h e r t r a d e m a r k s a r e t h e p r o p e r t y o f t h e i r r e s p e c t i v e o w n e r s . s u b j e c t t o c h a n g e w i t h o u t n o t i c e . A T S 005228 R e v C 4/16DPA1202Multi-Channel Network AmplifierFeatures• C onfiguration Levels • 2 x 600-Watt 70V/100V (Factory Default) • 4 x 300-Watt @ 4Ω • 1 x 600-Watt 70V/100V & 2 x 300-Watt @ 4Ω• No Computer Required to Operate • Networkable• Configurable DSP via GUI•PC Based DPA Site Manager Software with LAN IP Auto-Discovery Fault Reporting, Input & Output Status, Standby Status and Amplifier Remote Activation via a Scheduler Timer• Onboard Web Browser GUI for Remote Monitoring of Status & Levels• User Page with Assignable Level Control, Post Contractor Settings, Password Protected• Mute Assignments Triggered via Audio Signal or Contact Closure • Audio Sense Auto Power Down (APD)• DSP Parameters per Output, Parametric EQ, Hi & Lo Cut Filters, Delay, Limiter• Four (4) Balanced Inputs, Expandable to 8 via Accessory Card • Optional Accessory Card Slot for a DPA-DAC4 4-Channel Dante ™ Receiver or a DPA-AMIX (2) Mic / Line, (2) AUX Input Card • PC, iOS ®, & Android ® Controllable• Assignable Level Controls, Onboard GUI (Security Password Protected) or by Front Panel Pots with Tamper Deterring Covers • Four (4) GPIO Control Ports Assignable in GUI for Mute or Remote Level•Controllable From Third-Party ControllersApplicationsThe flexible DSP , remote web monitoring, and control of the DPA Series amplifiers makes them the perfect choice for presentation rooms, classrooms, conference rooms, and retail background / foreground music applications.General DescriptionThe AtlasIED DPA1202 features a combination of flexibility, performance and control to provide high value features for applications that require more than just great sound. The network based DPA1202 is a DSP controlled 4-channel amplifier that can be configured in three different amplification arrangements to meet the design requirements of any installation.The unit is factory preconfigured in a two-channel 70V mode. If the design requires four channels of low impedance amplification, the amplifier can be configured as 4-channel model with either 4Ω or 8Ω load impedances. Many system designs require both low and highimpedance amplification. This unit can be configured to deliver 70V/100V for a paging/background system on a single channel plus two additional 4Ω/8Ω amplifier channels for foreground stereo applications.The DPA1202 comes standard with four balanced line inputs and an accessory slot for an optional DPA-DAC4 4-channel Dante ™ receiver card or a DPA-AMIX (2) mic / line, (2) AUX input card, giving the DPA1202 a total of 8 inputs. All inputs can be mixed and routed to any of the four amplifier channels. All four amplifier channels have an assortment of DSP tools including level controls, EQ’s, limiters, high & low pass filters, and delay to provide flexibility for a range of applications.The output level can be assigned to either the front panelpotentiometers or to the on board GUI. Wired remote level controlcan be configured to allow simple control for the end user. Eachunit also features GUI based input and output level metering along with assignable mute functions that are triggered via an audio signal or contact closure. Access to the DSP settings is accomplished viacomputer, tablet or mobile device using a web browser. All settings can be password protected.The unit also includes a PC based site manager software thatautomatically searches within a specific network for all DPA amplifiers on the network. It will list them and allow a single click access to any unit. The DPA Site Manager software can do a variety of functions besides locating IP addresses such as; fault reporting, input & output status, standby status and remote activation via a scheduler timer.The flexibility of the DPA Series amplifiers and comprehensiveassortment of local or network control configurations make them an ideal choice in today’s sophisticated commercial audio market.DPA1202 FrontDPA1202 Backo u n d L .P . a n d I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l R i g h t s R e s e r v e d . A t l a s S o u n d i s a t r a d e m a r k o f A t l a s S o u n d L .P . I E D i s a r e g i s t e r e d t r a d e m a r k o f I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l o t h e r t r a d e m a r k s a r e t h e p r o p e r t y o f t h e i r r e s p e c t i v e o w n e r s . s u b j e c t t o c h a n g e w i t h o u t n o t i c e . A T S 005228 R e v C 4/16o u n d L .P . a n d I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l R i g h t s R e s e r v e d . A t l a s S o u n d i s a t r a d e m a r k o f A t l a s S o u n d L .P . I E D i s a r e g i s t e r e d t r a d e m a r k o f I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l o t h e r t r a d e m a r k s a r e t h e p r o p e r t y o f t h e i r r e s p e c t i v e o w n e r s . s u b j e c t t o c h a n g e w i t h o u t n o t i c e . A T S 005228 R e v C 4/16o u n d L .P . a n d I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l R i g h t s R e s e r v e d . A t l a s S o u n d i s a t r a d e m a r k o f A t l a s S o u n d L .P . I E D i s a r e g i s t e r e d t r a d e m a r k o f I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l o t h e r t r a d e m a r k s a r e t h e p r o p e r t y o f t h e i r r e s p e c t i v e o w n e r s . s u b j e c t t o c h a n g e w i t h o u t n o t i c e . A T S 005228 R e v C 4/16NOTES:1. P ower level measurment is define as follows: 1Hz Sine wave signal burst of 20 cycles (20mS) at 1% THD+N, followed by 480 cycles of a 1kHz sine wave at 10% of the max power. Other power measurements are available upon requests.2. Power measurement with Ethernet connected. Without Ethernet connected deduct .2W.3. Average Power is defined as Pink Noise input signal applied to achieve 1/4 of the 4 Ohm or 70.7V power rating.4. Max Power is defined as 1 KHz input signal applied to achieve the maxium power output before clipping into a 4 Ohm or 70.7V load.o u n d. I E D i s a r e g i s t e r e d t r a d e m a r k o f I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l o t h e r t r a d e m a r k s a r e t h e p r o p e r t y o f t h e i r r e s p e c t i v e o w n e r s . s u b j e Dimensional Drawings13.70 14.36 14.49Optional AccessoriesDPA-DAC4 - Dante™ 4-Channel Receiver CardDPA-AMIX - 4-Channel Mic / Line AUX Mixer Amp Cardo u n d L .P . a n d I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l R i g h t s R e s e r v e d . A t l a s S o u n d i s a t r a d e m a r k o f A t l a s S o u n d L .P . I E D i s a r e g i s t e r e d t r a d e m a r k o f I n n o v a t i v e E l e c t r o n i c D e s i g n s , L L C . A l l o t h e r t r a d e m a r k s a r e t h e p r o p e r t y o f t h e i r r e s p e c t i v e o w n e r s . s u b j e c t t o c h a n g e w i t h o u t n o t i c e . A T S 005228 R e v C 4/16Architect and Engineer SpecificationsThe power amplifier shall be a 4-channel switch mode power amplifier with efficient BASH Hybrid topology output circuitry with a Global Switch Mode PFC power supply. The amplifier shall be configurable as 4-channel low impedance 4Ω or 8Ω mode, 2-channel high impedance 70V/100V mode, or low impedance 2-channel 4Ω or 8Ω and 1-channel high impedance 70V/100V mode. The amplifier shall be factory shipped pre-configured in a two-channel 70V/100V mode. The I/O Router shall be configured as follows: Input 1 routed to Outputs 1 and 2 and Input 3 routed to Outputs 3 and 4 and will not require a computer or network to use in default mode.The performance specifications shall match or exceed the following:70V/100V x 2CH = 600W; 4Ω x 4CH = 300W; 8Ω x 4CH = 150W, (reference specification Notes 1-4 above); Input Sensitivity 750mV Balanced, 0dBU; Input Impedance Balanced 40k Ω; Max Input Level channels 1-4, +14dBU, 7dBU inputs 5-8 with Dante ™; THD 1% at rated output, .2% T ypical;Frequency Response -3dB 20Hz – 20kHz (DSP set to flat); Signal to Noise Ratio -100dB Below Rated Output – A Weighted; Crosstalk >70dB @1kHz; Protection circuits =Thermal, Short, Signal Limiter; Sleep Mode (Ethernet Active) 3.5W, 12BTU; Standby/ADP mode 14W. 48BTU; Max Power All CH driven 70.7V/100V (default mode) = 1511W, 2450BTU. Dimensions: 1 x RU, 19" W x 1.75" H x 14.5" D. Weight 13.1 lbs.The power amplifier shall have a front panel power switch and three states of idle power, Idle Active Mode, Sleep Mode, and Standby Auto Power Down (APD) Mode. Each mode shall have an LED indicator on the front panel indicating the power status. When in Sleep Mode, the Ethernet shall remain active for access to the amplifiers on board GUI.The amplifier shall include convection cooling with dynamic fan assist for extreme conditions. If the unit is not being used or in Standby mode, the fan shall not be needed for cooling and shall remain Off until the unit is in heavy use. As heat is generated in the amplifier during use, the fan shall activate at a low speed and increase as needed to keep the amplifier at safe operating temperature. The amplifier’s air flow shall be from rear to front. The front panel controls shall consist of four volume controls that can be removed and replaced with included security covers. Above each volume control, LED indicators for Signal and Limit/Protect/Mute shall provide the amplifier output operating condition. The 4-channel output operating mode shall be displayed to the right of the output indicators using multicolorLEDs. These indicators illustrate if Channels 1/2 and 3/4 are low impedance 4Ω or 8Ω individually configured or combined making a 70V / 100V output. Amplifier operation mode settings shall be completed using the internal DSP GUI.On the rear panel, the amplifier shall have an IEC AC receptacle thatoperates from 110V - 120V & 220V - 240V and shall automatically sense the AC Mains voltage and change voltage settings. A removable AC Mains fuse shall be provided for protection.The rear-mounted Input connectors for inputs 1 - 4 shall be individuallyremovable 3-way 3.5mm Phoenix type connectors that accept balanced line input signals (+) (–) and (GND) pins and will support unbalanced signals by connecting the (–) and (GND) pins together. The amplifier configuration and I/O Routing shall be done in the GUI. Any Input shall be capable of being routed to any Output.The rear-mounted Output connector shall be a screw terminal block type for connecting speakers to the amplifier. The recommended wire to use shall be Class 3 rated,14-gauge wire or lower for speaker wiring. Amplifier output channel configurations shall be done in the amplifier GUI. The amplifier shall be shipped with two speaker output terminal covers for safety. Included in the carton with the amplifier shall be eight (8) spade crimp terminals that accept 12-gauge wire and four (4) security cover screws (M3 x 8mm). T erminal block screws shall be M4. The amplifier shall be pre-configured at the factory for two-channel 70V/100V mode.The amplifier shall have one (1) rear mounted Accessory Card Slot to add accessory modules. Accessory modules shall make available 4 additional inputs (for a total of 8) that can be routed to any of the four output channels. Optional accessory cards shall be a Four-Channel Dante ™ Digital Audio Input Card and a Four-Channel Analog Mic / Line, Auxiliary Input Card.The amplifier shall have a rear-mounted Ethernet Connector to connect to a Local Area Network (LAN), computer, or router/switch using a standard RJ45 cable to access the amplifier’s DSP and control settings.When network enabled, the amplifier shall have a GUI Home page with Input and Output active meters, Output Configuration indicators, with Tab selections to navigate to User PC Control page, Amplifier Setup page, Mobil Control page, IP Configuration page where you can label I/O, Update page for Firmware upload, and About page. All four amplifier channels shall have an assortment of DSP tools with navigation icons to the following individual GUI pages: Amplifier Configuration, Mute, Link & Ports Assign, I/O Router Assign, Hi & Lo Pass Filters, 5-Band Parametric EQ, Output Level, Delay, and Limiter.The amplifier shall have four (4) rear-mounted Control Ports to allow assigned/configured Remote Level or Mute functions to be activated by external contact closure relay or controlled by voltage. Each Control Port pin shall be assigned to one function such as Mute or Level, but not both. Control Port assignment shall be done in the GUI “Mute, Link, Port Assignment Page”. The factory default assignments for the Amplifier Control Ports shall be as follows: C1 Controls CH 1/2 70V / 100V Output Remote Level, C2 Not Assigned, C3 Controls CH 3/ 4 70V / 100V Output Remote Level, C4 Not Assigned. The Control Ports shall provide +10V and GND connections for Remote Level controls using 10k Ω Linear Taper pots. The amplifier shall have Site Manager software to do a variety of functions including locating DPA amplifiers' IP addresses; fault reporting, input & output status, standby status and remote activation via a scheduler timer. The amplifier shall be an AtlasIED DAP1202.。

英语教研活动议课稿(3篇)

第1篇Introduction:Ladies and gentlemen, esteemed colleagues, and fellow educators, it is my great pleasure to present our English research and teaching activity, focusing on the discussion of lesson planning. Today, we gather here to share our insights, experiences, and innovative ideas that can enhance our teaching practices and contribute to the overall development of our students. Let us delve into the intricacies of lesson planning and explore ways to make our English classes more engaging and effective.I. Introduction to Lesson PlanningA. Definition and Importance of Lesson PlanningB. The Role of Lesson Planning in Student LearningC. The Challenges and Benefits of Effective Lesson PlanningII. Theoretical FrameworkA. Principles of Lesson Planning1. Objectives and Goals2. Content and Materials3. Instructional Strategies4. Assessment and EvaluationB. Theoretical Models of Lesson Planning1. Madeline Hunter’s Model2. Wiliam and Thompson’s Lesson Study3. Van Merrienboer’s 4C ModelIII. Lesson Planning ProcessA. Identifying Objectives and Goals1. Alignment with Curriculum Standards2. Student Learning Outcomes3. Assessment MethodsB. Selecting Content and Materials1. Textbooks and Resources2. Authentic Materials3. Technology IntegrationC. Designing Instructional Strategies1. Direct Instruction2. Inquiry-Based Learning3. Collaborative LearningD. Assessing and Evaluating Learning1. Formative and Summative Assessment2. Student Feedback and Self-Assessment3. Adjusting Instruction Based on Assessment ResultsIV. Case Study: Lesson Planning for a High School English ClassA. Introduction to the Lesson1. Topic: Shakespearean Sonnets2. Grade Level: 11th Grade3. Duration: 45 minutesB. Objectives and Goals1. To analyze the structure and themes of Shakespearean sonnets.2. To improve students' critical thinking and analytical skills.3. To enhance students' appreciation for Shakespearean literature.C. Content and Materials1. Textbook: “Shakespeare: The Complete Sonnets”2. Authentic mater ials: Sonnets from Shakespeare’s works3. Technology: PowerPoint presentation, online resourcesD. Instructional Strategies1. Introduction to the lesson: Teacher presents a brief overview of Shakespearean sonnets and their significance.2. Direct instruction: Teacher explains the structure and themes of Shakespearean sonnets.3. Inquiry-based learning: Students work in groups to analyze and discuss selected sonnets.4. Collaborative learning: Groups present their findings to the class, and the teacher facilitates a discussion.5. Summarizing and closing: Teacher summarizes the key points and highlights the importance of understanding Shakespearean sonnets.E. Assessment and Evaluation1. Formative assessment: Teacher observes students’ participation and engagement during group discussions.2. Summative assessment: Students complete a written assignment, analyzing a selected sonnet and discussing its structure and themes.3. Student feedback and self-assessment: Students reflect on their learning and provide feedback on the lesson.V. Group Discussion and ReflectionA. Sharing Experiences and Challenges1. What are the common challenges faced while planning English lessons?2. How do we overcome these challenges?B. Innovative Ideas and Best Practices1. How can we incorporate technology into our lesson planning?2. What are some effective strategies for engaging students in English classes?3. How can we ensure that our lessons are culturally relevant and inclusive?VI. ConclusionLadies and gentlemen, today’s discussion has provided us with valuable insights and innovative ideas for lesson planning in English classes. By following the principles of effective lesson planning and adapting our strategies to meet the needs of our students, we can create engaging and impactful learning experiences. Let us continue to collaborate, share our experiences, and grow as educators in our quest to enhance the learning and development of our students.Thank you for your participation and contributions to this English research and teaching activity. We look forward to applying these ideas in our classrooms and witnessing the positive impact on our students’ learning journey.[End of the议课稿]第2篇Introduction:Ladies and gentlemen, esteemed colleagues, and guests, welcome to our English teaching and research activity. Today, we are gathered here to engage in a collaborative lesson planning session. This session aims to enhance our teaching skills, share innovative ideas, and foster a conducive learning environment for our students. Let us begin with a brief introduction to the topic and the objectives of this session.I. Introduction to the TopicThe topic of our lesson planning session is "Enhancing Student Engagement in English Language Learning through Interactive Activities." With the increasing importance of English as a global language, it is crucial for us to find effective ways to engage our students in the learning process. Interactive activities not only make the learning experience more enjoyable but also facilitate better understanding and retention of the language.II. Objectives of the Session1. To identify effective interactive activities that can be incorporated into English language lessons.2. To discuss and analyze the impact of these activities on student engagement and learning outcomes.3. To share practical tips and strategies for implementing these activities in our classrooms.4. To encourage collaboration and professional development among English teachers.III. Presentation of Lesson PlansA. Lesson Plan 1: "Role-Playing Scenarios"Objective: To improve students' speaking and listening skills while fostering cultural awareness.Materials:1. A list of common scenarios (e.g., shopping, traveling, dining out)2. Props and costumes (optional)Procedure:1. Divide the class into small groups.2. Assign each group a scenario to act out.3. Provide a few minutes for the groups to prepare their roles and dialogues.4. Conduct the role-playing activity in the classroom.5. Encourage students to observe and participate actively.6. After the activity, hold a class discussion to reflect on the scenarios and cultural aspects.B. Lesson Plan 2: "English Corner"Objective: To provide a platform for students to practice speaking English in a relaxed and informal setting.Materials:1. A designated area in the classroom or school2. A schedule for the English Corner sessionsProcedure:1. Designate a specific time and place for the English Corner sessions.2. Encourage students to bring a topic of their choice for discussion.3. Assign a facilitator to lead the discussions and ensure that everyone gets a chance to speak.4. Provide guidelines on proper grammar and pronunciation.5. Rotate the facilitator role among students to ensure equal participation.C. Lesson Plan 3: "Group Projects"Objective: To enhance students' collaborative skills and critical thinking abilities.Materials:1. Project topics (e.g., research on famous English-speaking countries, creating a short English film)2. Resources for research and productionProcedure:1. Assign groups based on students' interests and abilities.2. Provide guidelines on the project's scope and expectations.3. Hold regular group meetings to monitor progress and offer assistance.4. Encourage students to share their findings and experiences with the class.5. Evaluate the projects based on criteria such as creativity, teamwork, and language proficiency.IV. Discussion and AnalysisNow that we have presented our lesson plans, let us engage in a discussion and analysis of their potential impact on student engagement and learning outcomes.1. What are the strengths and weaknesses of each lesson plan?2. How can we adapt these activities to cater to diverse learning styles and abilities?3. What are some challenges we might face while implementing these activities, and how can we overcome them?4. How can we assess the effectiveness of these activities in improving student engagement and learning outcomes?V. Practical Tips and StrategiesBased on the discussion, let us now share some practical tips and strategies for implementing these interactive activities in our classrooms.1. Be flexible and adapt the activities to suit your students' needs.2. Provide clear instructions and guidelines to ensure a smooth flow of the activity.3. Encourage active participation and create a supportive learning environment.4. Use technology and multimedia resources to enhance the learning experience.5. Regularly assess and reflect on the effectiveness of the activities to make improvements.VI. ConclusionIn conclusion, today's English teaching and research activity has provided us with valuable insights into enhancing student engagement in English language learning through interactive activities. By implementing these activities in our classrooms, we can create a more dynamic and engaging learning environment that fosters better understanding and retention of the language. Let us continue to collaborate, share our experiences, and strive for excellence in our teaching practices.Thank you for your participation and contributions to this session. We look forward to witnessing the positive impact of these interactive activities on our students' language skills and overall learning experience.第3篇Introduction:Ladies and gentlemen, esteemed colleagues, and esteemed guests, welcome to today's English teaching and research activity. The purpose of this session is to engage in a reflective lesson planning process, where we can share our insights, experiences, and best practices in English language teaching. We will discuss various aspects of lesson planning, including curriculum design, teaching strategies, assessment methods, and student engagement. Let's dive into the heart of our discussion and explore the intricacies of effective lesson planning.I. Introduction to the TopicA. Importance of Lesson PlanningLesson planning is a crucial component of effective teaching. It provides a structured framework for teachers to organize their lessons, ensure a logical progression of content, and cater to the diverse needs of students. A well-planned lesson enhances student engagement, promotes critical thinking, and fosters a positive learning environment.B. Objectives of the SessionThe objectives of this session are to:1. Share insights and experiences in lesson planning.2. Discuss different aspects of lesson planning, such as curriculum design, teaching strategies, and assessment methods.3. Identify best practices for engaging students in English language learning.4. Collaboratively develop a comprehensive lesson plan for a selected topic.II. Curriculum Design and Content SelectionA. Understanding the CurriculumThe first step in lesson planning is to have a clear understanding of the curriculum. We should be familiar with the learning objectives, assessment criteria, and the content that needs to be covered.B. Content SelectionSelecting appropriate content is essential for creating engaging and relevant lessons. We should consider the following factors:1. Student interest and prior knowledge.2. Age and proficiency level of the students.3. Integration of cross-curricular themes.4. Alignment with the curriculum objectives.III. Teaching Strategies and MethodsA. Introduction to Different Teaching StrategiesTeaching strategies are the methods used by teachers to facilitate learning. We will explore various strategies such as direct instruction, inquiry-based learning, collaborative learning, and project-based learning.B. Selecting the Right StrategyThe choice of teaching strategy depends on the learning objectives, student needs, and the content being taught. We should consider the following factors:1. Student engagement and motivation.2. Learning outcomes and assessment methods.3. Time and resources available.4. Teacher expertise and comfort level.IV. Student Engagement and MotivationA. Importance of Student EngagementStudent engagement is vital for effective learning. Engaged students are more likely to participate actively, think critically, and retain information.B. Techniques for Student EngagementWe will discuss various techniques for engaging students, such as:1. Interactive activities and games.2. Technology integration.3. Group work and collaborative learning.4. Real-world connections and authentic resources.V. Assessment Methods and EvaluationA. Purpose of AssessmentAssessment is a critical component of lesson planning. It helps us monitor student progress, identify areas of strength and weakness, and make informed decisions about teaching and learning.B. Different Assessment MethodsWe will explore various assessment methods, such as:1. Formative and summative assessments.2. Oral and written assessments.3. Self-assessment and peer-assessment.4. Portfolio assessment and project-based assessment.VI. Collaborative Lesson PlanningA. Sharing Ideas and ResourcesCollaborative lesson planning allows us to leverage the collective expertise and experiences of our colleagues. We will share our ideas, resources, and best practices.B. Developing a Comprehensive Lesson PlanBased on the discussions and insights gained throughout the session, we will collaboratively develop a comprehensive lesson plan for a selected topic. This plan will include the following elements:1. Lesson objectives and learning outcomes.2. Introduction and engagement activities.3. Main content delivery and teaching strategies.4. Student engagement and assessment activities.5. Conclusion and reflection.Conclusion:In conclusion, effective lesson planning is a vital skill for English language teachers. By understanding the curriculum, selecting appropriate content, utilizing various teaching strategies, and incorporating engaging activities, we can create dynamic and effective lessons that cater to the diverse needs of our students. Today's session has provided us with a platform to share our insights, experiences, and best practices in lesson planning. Let us continue to work together, support each other, and strive for excellence in our teaching endeavors.Thank you for your participation and contributions to this enriching session. May our collective efforts contribute to the continuous improvement of English language teaching and student learning outcomes.。

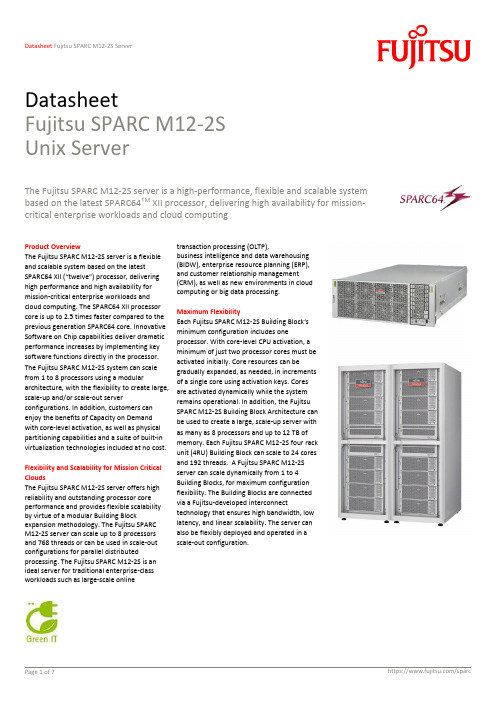

富士通SPARC M12-2S服务器说明书

DatasheetFujitsu SPARC M12-2S Unix ServerThe Fujitsu SPARC M12-2S server is a high-performance, flexible and scalable system based on the latest SPARC64TM XII processor, delivering high availability for mission-critical enterprise workloads and cloud computingProduct OverviewThe Fujitsu SPARC M12-2S server is a flexible and scalable system based on the latest SPARC64 XII (“twelve ”) processor, delivering high performance and high availability for mission-critical enterprise workloads and cloud computing. The SPARC64 XII processor core is up to 2.5 times faster compared to the previous generation SPARC64 core. Innovative Software on Chip capabilities deliver dramatic performance increases by implementing key software functions directly in the processor. The Fujitsu SPARC M12-2S system can scale from 1 to 8 processors using a modulararchitecture, with the flexibility to create large, scale-up and/or scale-out serverconfigurations. In addition, customers can enjoy the benefits of Capacity on Demand with core-level activation, as well as physical partitioning capabilities and a suite of built-in virtualization technologies included at no cost.Flexibility and Scalability for Mission Critical CloudsThe Fujitsu SPARC M12-2S server offers high reliability and outstanding processor core performance and provides flexible scalability by virtue of a modular Building Blockexpansion methodology. The Fujitsu SPARC M12-2S server can scale up to 8 processors and 768 threads or can be used in scale-out configurations for parallel distributedprocessing. The Fujitsu SPARC M12-2S is an ideal server for traditional enterprise-classworkloads such as large-scale onlinetransaction processing (OLTP),business intelligence and data warehousing (BIDW), enterprise resource planning (ERP), and customer relationship management (CRM), as well as new environments in cloud computing or big data processing.Maximum FlexibilityEach Fujitsu SPARC M12-2S Building Block‘s minimum configuration includes oneprocessor. With core-level CPU activation, a minimum of just two processor cores must be activated initially. Core resources can begradually expanded, as needed, in increments of a single core using activation keys. Cores are activated dynamically while the system remains operational. In addition, the Fujitsu SPARC M12-2S Building Block Architecture can be used to create a large, scale-up server with as many as 8 processors and up to 12 TB of memory. Each Fujitsu SPARC M12-2S four rack unit (4RU) Building Block can scale to 24 cores and 192 threads. A Fujitsu SPARC M12-2S server can scale dynamically from 1 to 4 Building Blocks, for maximum configuration flexibility. The Building Blocks are connected via a Fujitsu-developed interconnecttechnology that ensures high bandwidth, low latency, and linear scalability. The server can also be flexibly deployed and operated in a scale-out configuration.■Up to eight 12-core, 4.25 GHz SPARC64 XII processors for a total of 96 cores and 768 powerful threads ■Superior enterprise application performance for small to large ERP, BIDW, SCM, CRM, Big Data, and Analytics workloads■Maximum cost savings with efficient consolidation of a large number of applications with diverse requirements on a single server■Flexible main memory configurations: from 64 GB to 12 TB, and supporting mixed DIMM capacities ■Radically improved response times and throughput performance by running entire databases in memory, eliminating costly disk accesses■Mainframe-class reliability, availability, and serviceability (RAS) capabilities ■Robust RAS features availability to support the most demanding 24/7 mission-critical applications■Modular Building Block Architecture■Dynamically expand resources easily and economicallyfrom 1 to 8 processor sockets■High-speed interconnect technology■Linear scaling from 1 Building Block to 4 Building Blocks tohandle planned and unplanned workload growth■Core-based CPU Activation■Ability to pay for only the resources that are needed,minimizing initial investment and avoiding expensiveupgrades■Fast and economical system capacity growth in incrementsas small as a single processor core with no downtime■Software-on-Chip instructions implementing key software functions directly in SPARC64 XII processors ■Drastic performance gains for a wide range of applications such as encryption, decimal arithmetic operations, anddatabase accelerators built into each CPU core■ 1.5 times higher memory access performance by adopting DDR4 memory directly attached to each processoraccelerates Oracle Database in-memory dramatically■New Vapor and Liquid Loop Cooling (VLLC) technology for innovative and compact system design ■Twice the cooling performance of Liquid Looping Cooling (LLC) technology used in Fujitsu M10 servers■Dramatic reduction in space and completely self-contained, requiring no maintenance■Layered virtualization including Oracle VM Server for SPARC and Oracle Solaris Zones technologies ■Higher levels of system utilization and cost reduction with flexible resource configurations■Massive server consolidation without the need to acquire additional software■Supports Oracle Solaris 11 and Oracle Solaris 10, also Solaris 9 and 8 with Oracle Solaris Legacy Container ■Investment protection for application software as well as system management and administration expertise,avoiding costly and complex migrations■Oracle Solaris Binary Application Guarantee■Preservation of software investments with guaranteedcompatibility, allowing existing SPARC Solaris applicationsto run unmodifiedFeatures and benefitsWorld-Class Enterprise Performance with Extreme Core Technology Fujitsu SPARC M12 servers featuring the 12-core SPARC64 XII processor provide superior performance for mission-critical enterprise workloads and cloud computing. Employing proven Fujitsu supercomputer technology for highly parallel computing and an innovative cooling technology to achieve low latency access time between memory and CPU, the Fujitsu SPARC M12 servers can process large amounts of data in a short period of time. These technologies provide superior performance for enterprise workloads such as online transaction processing (OLTP), enterprise resource planning (ERP), business intelligence and data warehousing (BIDW), supply chain management (SCM), and customer relationship management (CRM), as well as new environments in cloud computing or data processing.Pay as You Grow Dynamic ScalabilityThe modern enterprise needs a flexible platform that provides superior performance and availability for current application environments as well as the ability to scale for future growth and technological needs. The Fujitsu SPARC M12-2S server features unique dynamic scaling to grow as the business grows. With CPU Activation, customers can activate CPU resources on a CPU core basis and expand from a single CPU socket and two cores, while paying for only the processor cores that are needed. In addition, Fujitsu SPARC M12-2S allows for the gradual addition of resources such as CPU, memory, and PCIe slots through the dynamic addition of Building Blocks connected via the high-speed interconnect. Together, CPU Activation and Building Block Architecture enable rapid, granular and cost-effective growth from a very small configuration up to as many as 8 CPU sockets and 96 processor cores.High Availability for Mission-Critical ApplicationsThe Fujitsu SPARC M12-2S server delivers high availability to support demanding mission-critical applications. It comes with mainframe-class reliability, availability, and serviceability (RAS) features including automatic recovery with instruction retry, extended error-correcting code (ECC) protection, guaranteed data path integrity, configurable memory mirroring, and many more RAS capabilities. Furthermore, major system components are redundant and hot-swappable for increased availability and serviceability. Innovative Software on Chip TechnologyFujitsu SPARC M12-2S servers feature Software on Chip (SWoC) technology, which implements common software code sequences directly in the processor hardware, offering significant enhancements for key database functions. Two Software on Chip technologies, SIMD (Single Instruction Multiple Data) and decimal floating point ALUs (Arithmetic Logical Units), directly accelerate Oracle Database in-memory processing with specific hardware instructions. SWoC encryption acceleration is also implemented, providing high-speed encryption processing (encryption/decryption) using the Oracle Solaris encryption library. Also, the load placed on the CPU when the database is encrypted is reduced and a secure work environment can be configured.New High-Efficiency Cooling TechnologyThe new Fujitsu hybrid cooling technology, Vapor and Liquid Loop Cooling (VLLC), in Fujitsu SPARC M12-2S servers is an innovative high-efficiency vapor and liquid cooling technology that maximizes performance, minimizes space, and reduces noise. VLLC achieves twice the cooling performance of Liquid Loop Cooling (LLC) used in FujitsuM10 servers. VLLC also dramatically improves the internal layout of the server, allowing CPUs and memory to be packed closer together; reducing memory latency. VLLC is completely self-contained and requires no maintenance. This efficient cooling system can lead to significant cost savings for businesses.Advanced Virtualization and ConsolidationSPARC processor-based servers are among the world’s best consolidation and virtualization platforms. The Fujitsu SPARC M12-2S server supports up to 4 physical partitions, and as many as 256 Oracle VM Server for SPARC domains per physical partition, enabling massive server consolidation and cost savings.Oracle Solaris: The World’s Most Advanced Enterprise Operating SystemThe Fujitsu SPARC M12-2S server supports Oracle Solaris 11 and Oracle Solaris 10. In addition, all Fujitsu SPARC M12 servers benefit from the Oracle Solaris Binary Application Guarantee, with guaranteed binary and source-code compatibility for legacy applications. Oracle Solaris offers the powerful Solaris ZFS file systems and unmatched capabilities such as dynamic tracing (DTrace), cryptographic infrastructure, user and process rights management, and the Oracle Solaris IP Filter. In addition, Oracle Solaris 9 and 8 are supported using Oracle Solaris Legacy Containers.TopicsSpecificationsProcessorCPU SPARC64 XII: 12-core processor, 8 Simultaneous Multithreading threads per core,Two instruction pipelines per core, SPARC V9 architecture, Error Checking andCorrection (ECC) protectionLevel 1 cache per core64 K data cache and 64 K instruction cacheLevel 2 cache per core512 KBLevel 3 cache per CPU socket32 MBClock speed 4.25 GHzSoftware on Chip features•SIMD Single Instruction Multiple Data Vector Processing•Extended Floating-Point Registers•Decimal Floating-Point Processing. IEEE 754 standard and Oracle Number•Cryptographic Processing. Supported encryption modes are AES, DES, 3DES,DH, DSA, ECC, RSA and SHASystemCPU•Up to 2 CPUs: 1 Building Block configuration•Up to 8 CPUs: 4 Building Block configurationMain memory•Up to 3 TB per unit, with 64 GB DIMMs: 1 Building Block configuration•Up to 12 TB per unit, with 64 GB DIMMs: 4 Building Block configurationI/O•8 PCI Express 3.0 short, low-profile slots (eight lanes):1 Building Block configuration•32 PCI Express 3.0 short, low-profile slots (eight lanes):4 Building Block configuration•Up to 352 PCI Express slots with optional PCI Expansion Units•4-port 10GbE, 1 SAS-2 port, 2-port USB per Building BlockMemory bandwidth (per chip)153 GB/secService processor One per Building BlockStorageLocal storage Up to eight 600 GB or 1.2 TB internal 2.5-in. SAS HDDs or 400 GB or 800GB eMLCSAS SSDs (can be mixed)SoftwareOperating system Control Domain:•Oracle Solaris 11.4 + SRU 11.4.48.126.1 or later*Guest Domains:•Oracle Solaris 11.4 or later•Oracle Solaris 11.3 or later•Oracle Solaris 11.2 or later•Oracle Solaris 11.1 or later•Oracle Solaris 10 1/13**•Oracle Solaris 10 8/11**•Oracle Solaris 10 9/10*** The following operating systems are supported on the condition that theoptional LAN card is mounted, because they cannot use the onboard LAN:Oracle Solaris 11.3 SRU 11.3.17.5.0 or laterOracle Solaris 11.2 SRU 11.2.15.5.1Oracle Solaris 11.1 SRU 11.1.21.4.1Oracle Solaris 10 1/13 150310-03 or laterSoftware** Plus required patchesOracle Solaris 9 or 8 branded zones run within an Oracle Solaris 10 domain.Please see the Fujitsu SPARC M12 Systems Product Notes manual for SRU/patchrequirements.Software included•Oracle Solaris 11.4 or later, which includes Oracle VM Server for SPARC•Oracle Solaris ZFS (default file system)Management software •XSCF monitoring/control facility•XSCF software, which manages hardware configuration and health, domainconfiguration and status, error monitoring, and notifications.System monitoring Oracle Enterprise Manager Ops Center 12c Release 3 Update 2 or laterOracle Enterprise Manager Cloud Control 13c Release 1 or laterVirtualization Built-in, no-cost Oracle VM Server for SPARC provides the flexibility and power ofrunning multiple logical domains in a single server. Multiple Oracle Solaris Zonesmay be run within a single Oracle VM Server for SPARC logical domain.Reliability, Availability, and ServiceabilityKey features •End-to-end ECC protection•Guaranteed data path integrity•Automatic recovery with instruction retry•Dynamic L1, L2 and L3 cache way degradation•ECC and Extended ECC protection for memory, memory mirroring, periodicmemory patrol, and predictive self-healing•Hardware redundancy in memory (when mirroring), HDD, SSD(SoftwareRAID), PCI cards (Multipath configuration), power system, PSU, fan, vaporand liquid cooling pumps, and XSCF (on configuraions with two or moreBuilding Blocks)•Hot-pluggable HDD/SSD, PSU, PCIe cards, fans, and XSCF (on configuraionswith two or more Building Blocks)•Live operating system upgrades•Firmware updates during system operationEnvironmentAC power 200 V to 240 V ±10% (50/60 Hz)Power consumption Single Building Block maximum 3,292 W4 Building Blocks maximum 13,168 WOperating temperature •5° to 35° C (41° to 95° F) at an altitude of 0 m to 500 m•5° to 33° C (41° to 91° F) at an altitude of 501 m to 1,000m•5° to 31° C (41° to 88° F) at an altitude of 1,001 m to 1,500 m•5° to 29° C (41° to 84° F) at an altitude of 1,501 m to 3,000 mNon-operating temperature-25° C to 60° C (-13° F to 140° F) (packed)0 to 50° C (32° F to 122° F) (non-packed)Altitude Up to 3,000 m (9,843 ft.)Acoustic Noise•8.2 B (1 CPU) / 8.5 B (2 CPUs)•64 dB (1 CPU) / 68 dB (2 CPUs)Cooling 11,850 kJ/h per Building BlockDimensions and Weight per Building BlockHeight17.5 cm (6.9 in.)Width44.0 cm (17.3 in.)Depth80.0 cm (31.5 in.)Weight60 kg (132.3 lb.)RegulationsSafety•UL/CSA 60950-1, UL/CSA 62368-1, EN 62368-1, IEC 60950-1, and IECRegulations62368-1 CB Scheme with all country differences EMC•Emissions: FCC 47 CFR 15, ICES-003, EN 55032, KN32, EN 61000-3-2, EN61000-3-3, JIS C 61000-3-2•Immunity: EN 55035, KN35Productshttps:///global/products/ In addition to the Fujitsu SPARC M12 Server, Fujitsu offers a full portfolio of other computing products.Computing products■ S torage systems: ETERNUS■ S erver: PRIMERGY , PRIMEQUEST, Fujitsu SPARC M12, BS2000/OSD Mainframe ■ C lient Computing Devices: LIFEBOOK, STYLISTIC, ESPRIMO, FUTRO, CELSIUS ■ P eripherals: Fujitsu Displays, Accessories ■ S oftware ■ N etworkProduct Support Services with differentservice levels agreements are recommended to safeguard each product and ensure smooth IT operation.Solutionshttps:///global/solutions The Fujitsu solutions combine reliable Fujitsu products with the best in services, know-how and worldwide partnerships.Fujitsu's Solutions include parts of one or more activity groups (e.g., planning,implementation, support, management, and training services) and are designed to solve a specific business need.Infrastructure Solutions are customerofferings created by bringing Fujitsu’s best products, services and technologies together with those from partners to deliver benefit to our customers’ businesses .Industry Solutions are tailored to meet the needs of specific verticals.Business and Technology Solutions provide a variety of technologies developed to tackle specific business issues such as security and sustainability, across many verticals.Serviceshttps:///global/services/ Several customizable Fujitsu Service offerings ensure that IT makes a realdifference and delivers true business value. We do this by leveraging our extensive experience in managing large, complex, transformational IT programs to help clients in planning, delivering and operating IT services in a challenging and changing business environment.Application Services support the development, integration, testing,deployment and on-going management of both custom developed and packagedapplications. The services focus on delivering business and productivity improvements for organizations.Business Services respond to the challenge of planning, delivering and operating IT in a complex and changing IT environment. Managed Infrastructure Services enable customers to deliver the optimal ITenvironment to meet their needs – achieving high levels of IT service quality andperformance for data center and end user environments.Environment - Fujitsu GlobalFujitsu Green Policy Innovation is ourworldwide project for reducing burdens on the environment. Using our global know-how, we aim to resolve issues of environmental energy efficiency through IT. Please find further information at:Learn more about Fujitsu, please contact your Fujitsu sales representative, Fujitsu business partner,or visit our website.https:///sparc© Copyright 2023 Fujitsu limitedFujitsu, the Fujitsu logo, [other Fujitsu trademarks /registered trademarks] are trademarks or registered trademarks ofFujitsu Limited in Japan and other countries.Technical data subject to modification and delivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded. Designations may be trademarks and/or copyrights of the respective manufacturer, the use of which by third parties for their own purposes may infringe the rights of such owner.More informationContact FUJITSUFujitsu SPARC M12 Server https:///sparc 2023-07-11 WW -EN。

SL Loudspeaker 52 A W 产品说明说明书

FEATURESActive loudspeaker with inbuilt power supplyOptimized for speech intelligibilityIntegrated DSP with frequency adjust-ments and high pass filterAuto sleep modeFlexible wallmount included in deliveryARCHITECT’S SPECIFICATIONSSL Loudspeaker 52 A WThe loudspeaker shall be optimized for speech intelligibility and shall be suitable for meeting rooms with up to 16 partici-pants on site.The loudspeaker shall feature two input sockets for connecting audio signals: one balanced input terminal (e.g. Phoenix Con-tact MC 1.5/3-ST-3.5 or similar) and one unbalanced RCA input.The loudspeaker shall feature three 3-posi-tion adjustment switches for adjusting its high, medium and low frequency levels for optimum sound quality depending on the mounting position and the room charac-teristics. The loudspeaker‘s high pass filter shall be adjustable to 50 Hz, 70 Hz or 100 Hz. The input sensitivity shall be selectable between −6 dBu, 0 dBu or +10 dBu. Input impedance (balanced and unbalanced) shall be > 10 k O.TECHNICAL DATAACOuSTICSFrequency response ± 3 dB .................................53 − 30,000 Hz Max. SPL at 1 m (150 − 5,000 Hz) .....................97 dB SPLTHD at 90 dB SPL at 1 m > 200 Hz ....................< 1 % ELECTROnICSnominal output power woofer ............................40 WRMS at 1 % THD(with deactivated limiter)nominal output power tweeter ...........................40 WRMS at 1 % THD(with deactivated limiter)THD + n vs. frequency at 1 W output ................0.16 %SnR at 1 kHz ............................................................95 dBCMRR ..........................................................................71 dBCrossover frequency ...............................................4.5 kHzSlope low pass woofer ...........................................12 dB/oct. (2nd order) Slope high pass tweeter ........................................24 dB/oct. (4th order) Resonance frequency high pass woofer ............55 Hz; 75 Hz; 100 Hz Slope high pass woofer ........................................24 dB/oct. (4th order)SL Loudspeaker 52 A W2Bass reflex portContinued on page 2 Continued on page 2The loudspeaker shall have a frequency response (+-3 dB) of 53 – 30,000 Hz. Ma-ximum sound pressure level at 1 m (150 to 5,000 Hz) shall be 97 dB SPL. THD at 90 dB SPL at 1 m > 200 Hz shall be < 1 %. nominal output power of the woofer and the tweeter (RMS at 1% THD and with deactivated limiter) shall be 40 W, respec-tively. THD plus noise vs. frequency at 1 W output power shall be 0.16 %. Signal-to-noise ratio at 1 kHz shall be 95 dB. Com-mon mode rejection ratio shall be 71 dB. The loudspeaker shall operate on 100−240 V AC, 50 – 60 Hz. The loudspeaker shall have an On/OFF power switch and shall feature a second switch for activating/ deactivating the auto standby mode.If enabled, the auto standby mode shall become active after 20 minutes without audio signal.The loudspeaker shall have a housing with pre-drilled mounting points and shall be supplied complete with a wall mounting kit (consisting of a wall bracket, a loudspeaker bracket, 2 spacers, a safety wire, screws and anchors).The loudspeaker’s dimensions shall be approximately 240mm x 140mm x 161mm (9.45" x 5.51" x 6,34"); its weight shall be approximately 3.1kgThe loudspeaker shall be the Sennheiser SL Loudspeaker 52 A W.TECHNICAL DATAPOSITIOn ADJuSTMEnTSHF ................................................................................ f = 2800 Hz, Gain +1.4dBflatf = 2800 Hz, Gain −1.5dBMF ............................................................................... fl atf = 100 Hz, Gain −2.7dBf = 230 Hz, Gain −3.7dBLF ................................................................................ fl atf = 800 Hz, Gain −2.0dB, 6dB Lowshelff = 800 Hz, Gain −4.0dB, 6dB Lowshelf Input sensitivity at 97 dB SPL .............................. S witch positions−6 dBu0 dBu10 dBuSwitch−on level switch–on automatics .............1.4 mVRMSAuto standby ...........................................................20 minInput impedance: .................................................... b alanced > 10 k Ounbalanced > 10 k OPRODuCT PROPERTIESPower consumption (standby) ............................ 230 V AC; 0.47 W /110 V AC; 0.34 WPower consumption (idle) .................................... 230 V AC; 4.75 W /110 V AC; 4.53 WPower consumption (max) ................................... 230 V AC; 95 W /110 V AC; 91 WDimensions (H x W x D) .........................................240mm x 140mm x 161mm Weight .......................................................................3.1 kgMounting points ...................................................... 2 x M6 on rear panel with depth10mmDELIVERY INCLUDES1 SL Loudspeaker 52 A W1 SpeakerMount 1001 wall bracket1 loudspeaker bracket2 spacers1 set of safety wire, screws and anchors1 quick guide1 safety guideThe mains cable is not included in the delivery.Mains cables with different lengths and for different countries are available as an accessory.Sennheiser electronic GmbH & Co. KG Am Labor 1, 30900 Wedemark, Germany 0 1 / 1 4 S e n n h e i s e r i s a r e g i s t e r e d t r a d e m a r k o f S e n n h e i s e r e l e c t r o n i c G m b H & C o . K G . w w w . s e n n h e i s e r . c o m . C o p y r i g h t ©0 5 / 2 0 1 3 . A l l r i g h t s r e s e r v e d . E r r o r s a n d o m i s s i o n s e x c e p t e d .。

Digital Signal Processing

Digital Signal Processing Digital Signal Processing (DSP) is a vital field that has revolutionized various aspects of our lives. From audio and video processing to telecommunications and medical imaging, DSP plays a crucial role in enhancing the quality of signals and extracting useful information from them. In this response, I will discuss the significance of DSP from multiple perspectives, highlightingits impact on different industries and the emotional elements associated with its advancements. From a technological perspective, DSP has opened up a world of possibilities. With the advent of high-speed processors and advanced algorithms, DSP techniques have become more powerful and versatile. This has enabled the development of sophisticated audio and video processing systems that can remove noise, enhance clarity, and even manipulate signals to create special effects. For example, in the entertainment industry, DSP is used to improve the audio quality of music recordings, making them more enjoyable for listeners. It also plays a crucial role in video editing, allowing professionals to enhance visual effects and create stunning visuals. In the field of telecommunications, DSP has revolutionized the way we communicate. From mobile phones to satellite communication systems, DSP algorithms are used to encode, transmit, and decode signals, ensuring reliable and high-quality communication. This has led to improved voice and video call quality, faster data transfer rates, and increased capacity in wireless networks. The emotional impact of these advancements is evident in our daily lives. We can now connect with our loved ones, no matter where they are in the world, with crystal-clear audio and video, bridging the distance and bringing us closer together. Another area where DSP has made significant contributions is medical imaging. Techniques like computed tomography (CT), magnetic resonance imaging (MRI), and ultrasound heavily rely on DSP algorithms to process and reconstruct images from raw data. This hasrevolutionized the diagnosis and treatment of various medical conditions, enabling doctors to visualize internal structures with unprecedented detail. The emotional impact of this cannot be overstated. DSP has saved countless lives by enabling early detection of diseases, guiding surgical procedures, and monitoring treatment progress. In addition to these industries, DSP has also found applications infields like radar and sonar systems, seismology, speech recognition, and even financial analysis. In radar and sonar systems, DSP algorithms are used to process the received signals and extract useful information about the surrounding environment. In seismology, DSP helps in detecting and analyzing earthquakes, providing valuable insights into the Earth's structure and predicting potential hazards. Speech recognition systems, like those used in virtual assistants, rely on DSP techniques to accurately interpret and respond to human speech. Infinancial analysis, DSP algorithms are used to analyze market data and make predictions, aiding in decision-making and risk management. The advancements in DSP have undoubtedly improved our lives in numerous ways, but it is essential to consider the ethical implications as well. With the increasing use of DSP in surveillance systems, privacy concerns have become more prominent. The ability to process and analyze vast amounts of audio and video data raises questions about the balance between security and individual privacy. It is crucial to develop regulations and guidelines to ensure that DSP technologies are used responsibly and ethically. In conclusion, Digital Signal Processing has had a profound impact on various industries, enhancing the quality of signals and extracting valuable information. From technological advancements to emotional impacts, DSP has revolutionized fields like entertainment, telecommunications, medical imaging, and more. However, it is important to consider the ethical implications and ensurethat DSP technologies are used responsibly. As we continue to push the boundaries of DSP, we must strive to strike a balance between technological advancements and the well-being of individuals and society as a whole.。

Digital Signal Processing in Audio