跨导运算放大器及其Spice电路模型的构建

具有恒定跨导的RAIL-TO-RAILCMOS运算放大器设计指导

具有恒定跨导的Rail-to-Rail CMOS运算放大器设计指导陈斯(徐州师范大学物理系电子科学教研室)注:文章中有很多关于MOS方面的基础知识,可能对于你们来说比较陌生,可以去找一些关于这方面的书籍看看。

下学期我会给你们做专门的讲解的。

你们先作个大概的了解,并确定具体的方向。

1引言近年来,随着集成电路工艺尺寸的不断减小,低电压的发展趋势越来越快。

下图为半导体工艺与电源电压的关系。

从图中可以看出,电压随着工艺最小尺寸的减小而不断降低。

电压减小的原因是因为尺寸的减小导致了器件的击穿电压的减小。

此外数字电路的功耗正比于电源电压的平方,因此,为了减小功耗必须降低电源的电压。

但是从模拟电路设计者来看,电源电压的减小会导致模拟信号动态范围的减小。

如果MOS管的域值电压随着电源的降低而等比减小的话,动态范围就不会受到严重的影响。

但由于数字逻辑的原因,域值电压不能大幅地减小,所以低电压会对电路的设计带来一定的影响。

2 一般原理在模拟电路和数模混合电路中,对于低电压的追求逐渐成为集成电路的一种时尚。

然而低电压导致了运算放大器输入共模范围的降低,传统的PMOS或NMOS差分对输入已不能满足大的输入共模范围的要求。

为解决这一瓶颈,rail-to-rail运算放大器随之而产生。

通常的Rail-to-Rail运放采用两级结构,运放的输出级可以采用简单的class-A或class-AB来实现,难点在于输入级的设计。

输入级一般采用PMOS和NMOS并联的互补差分结构,但其跨导在整个共模输入范围内变化两倍。

这种跨导的变化不仅影响环路的增益, 也会影响运放的频率补偿。

同时,由于输入信号是rail-to-rail ,具有很高的信噪比,因此要求整个rail-to-rail 运放的输入级保持恒定的跨导(g m )。

一般来说,运算放大器的输入级都采用差分放大器的输入模式。

在CMOS 工艺中,差分放大器可以通过PMOS 或NMOS 的差分对来实现。

spice和spectre软件使用和运放的仿真方法

斜坡上升 阶跃信号

激励

3.脉冲信号源 V1 N1 N2 PULSE(v1 v2 td tr tf pw per)

V1 N1 N2 PULSE(0 5 1p 1p 1p 5u 10u) 注:v1:值1

v2:值2 td:延迟时间 tr:上升时间 tf:下降时间 pw:脉冲宽度 per:周期

方波

激励

4.正弦信号源 V1 N1 N2 SIN(v0 va freq td θ Φ) V1 N1 N2 SIN(0 1 1) 注:v0:偏置值

基本语法

1. 不区分大小写(case insensitive) 2. 注释:* or $ 3. 数量级表示符号:

T

E12

G

E9

MEG

E6

K

E3

M

E-3

U

E-6

N

E-9

p

E-12

F

E-15

(关键不要搞错M和MEG) 4.赋值单位可以省略

仿真网表的五个主要组成部分

1.电路网表 2.激励 3.仿真分析语句 4.输出命令 5.模型库文件

添加模型时,添加此库文件,section选项只填上tt就可以了!

Hspice模型文件的结构(.lib)

**说明** .lib tt ……参数 .lib “路径/模型名.lib” mos .lib “路径/模型名.lib” bjt .lib “路径/模型名.lib” diode .endl tt ……(包括.lib ss,.lib sf,.lib fs,.lib ff等)

电路网表

包含的内容有器件连接关系、模型名、参 数值、(赋值)、并联个数、(初始值) 例: R1 N1 N2 R W=10u L=1u R2 N1 N2 10K C1 N1 N2 C W=10u L=1u C2 N1 N2 10p C3 N1 N2 10p IC=1

跨导运算放大器设计实例

李福乐 lifule@

1

Specifications

• CSMC 0.6um DPDM CMOS Process • GBW > 100MHz, PM > 60 when CL=2pF • DC Gain > 80dB • Output swing > 4V (differential) • Full differential architecture • Low Power (Large FOM)

所设计的OTA要应用于课程设计10bit cyclic ADC中。 在开关电容ADC中,ADC的速度取决于级电路的建立速度,而级电路的建立过程 可视为由大信号压摆区和小信号线性建立区构成,其中,小信号建立区的时间通 常要占到总建立时间的80%~90%,因此,OTA的大信号压摆率对ADC的速度影响 较小; 从另一个方面来说,压摆率只取决于偏置电Байду номын сангаас,当偏置电流和电容确定后,无论 输入管的VGS-VT是大是小,压摆率都不变。对于连续信号处理电路,我们希望 OTA在整个设计带宽内工作时,输出信号不会因为摆率跟不上而幅度受限,这个 时候需要SR/GBW大一些,即输入管的VGS-VT大一些;但是,对于采样信号处理 电路,比如我们所要设计的ADC,当我们确定好偏置电流,然后降低输入管的 VGS-VT,这个时候,SR不变,GBW变大,即SR/GBW变小了,而最终的建立时 间反而缩小了,ADC的速度加快了。 因此,SPEC中没有提出对SR的具体要求。 注意:不同应用对SR/GBW的不同要求!

3

MOST parameters

• u? Cox?

– Find out un, up, toxn and toxp from model library

(完整word版)跨导运算放大器的设计

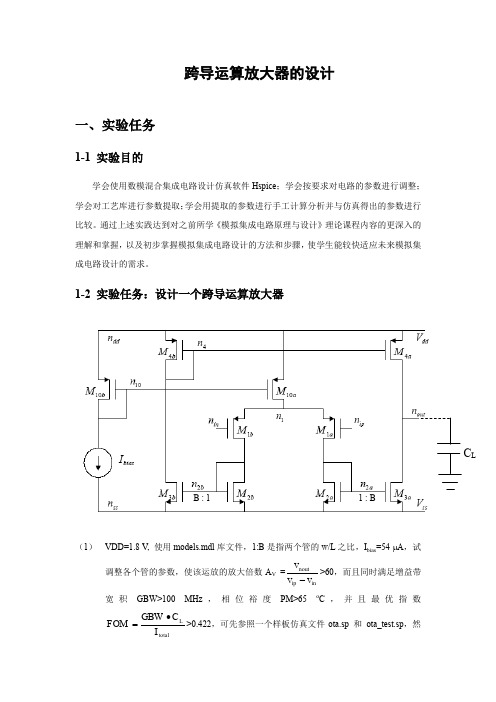

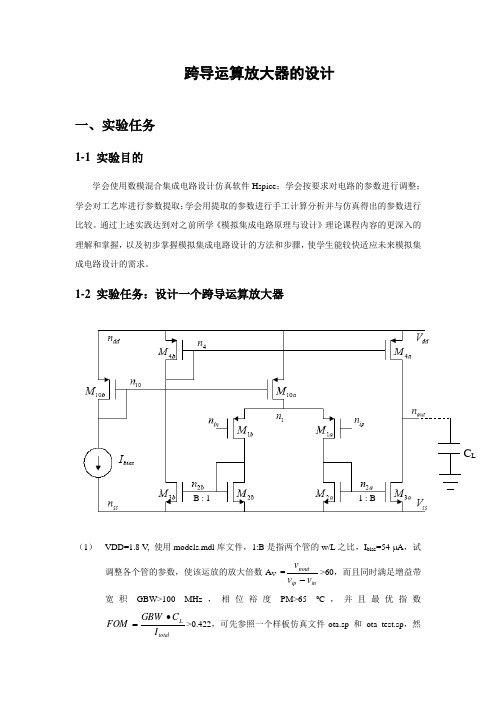

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

(完整word版)跨导运算放大器的设计

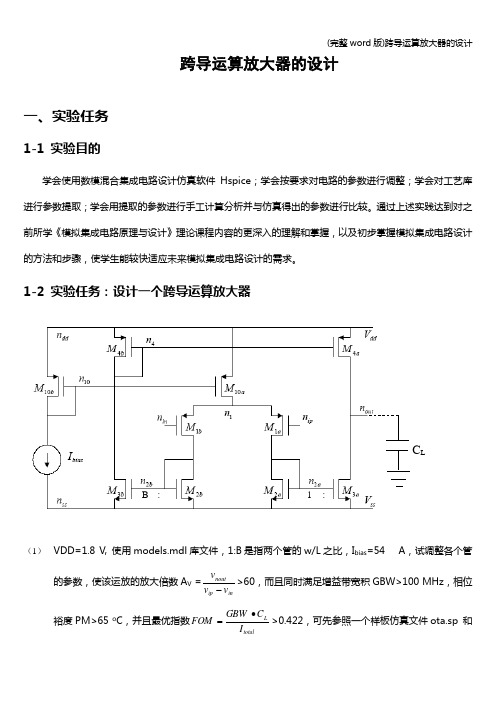

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V, 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54A ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C ,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和C LB : 1 1 : Bota_test.sp ,然后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较;(3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少?最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

运算放大器构成的18种功能电路(带multisim仿真)

(1)反相比例放大器:将输入加至反相端,同时将正相端子接地,由运放的虚短和虚断V U U 0==+-,又有102R U U R U U i -=---,得输出为:i U R RU 210-= 仿真电路为:取:Ω==k R R 2221,tV U sin 21=,得到输出结果为:tV U sin 40-=输出波形为:(2)电压跟随器:当同相比例放大器的增益为1时,可得到电压跟随器,其在两个电路的级联中具有隔离缓冲作用。

可消除两级电路间的相互影响。

其仿真波形为:取输入为4V,频率为1kHz的方波,得到输出结果为:(3)同相比例放大器:将INA133的2,5和1,3端子分别并联,以此运放作为基本放大器,反馈网络串联在输入回路中,且反馈电压正比于输入电压,引入串联电压负反馈。

反馈电压1211U R R R U f +=由运放的虚短和虚断,有输出电压为:1120)1(U R R U += 其仿真电路为:取tV U sin 21=,Ω==k R R 2212,得到结果为:tV U sin 60= 其输出波形为:(4)反相器:当方向比例放大器增益为1时可得到反相器电路,其仿真电路为:取:tV U sin 21=,输出结果为:tV U U sin 210-=-=仿真输出波形为:(5)同相相加器;将输入信号引至同相端,得到同相相加器由INA133内置电阻设计如下电路,得到输出结果为:210U U U += 仿真电路为:取tV U sin 21=,tV U sin 32=,由公式得到结果为:tV U sin 50= 仿真输出波形为:(6)相减器:将输入信号分别加在INA133的正相和反相输入端,可得到相减电路,其仿真电路如下: 其输出结果为:210U U U -=取tV U sin 51=,tV U sin 22=,计算输出结果为:tV U sin 30=其仿真输出波形为:(7)积分器:利用INA133及电容可构成反相积分器,仿真电路如下图,电阻2R 与运放构成积分器,电阻1R 可起到保护作用,防止低频信号增益过大。

第八讲 跨导运放的分析与设计讲解

由于零点的作用,相位裕度 从60多度减小至39度!

交流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

分析miller补偿效应

.probe ac v(vo1) v(vo) vp(vo)

.op

*.dc v_vdc 2.48 2.495 0.0001

失调分析

在MOS晶体管的参数中考虑失配 例:原有的 W=12u, M=2 修改为 W=‘12u+12u*0.04u*alfa/sqrt(2*12um*5um)’ M=2 delvto=‘12.5n*alfa/sqrt(2*12um*5um)’ 这里alfa为(0,1)高斯分布变量 依次将网表的内容按照上面的方法修改

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

.probe dc v(vo1) v(vo)

.op .dc v_vdc 2.48 2.495 0.0001

精扫

*.trans 10ns 200ns 20ns 0.1ns

*.ac dec 10 1k 100meg $sweep rzv 0 2k 0.2k

耗,因此可查得电路功耗为2.47mW • 对于MOS管,注意各参量的含义:region、id、vgs、

vds、vth、vdsat、gm、gmb、gds……可查得流过 M_U3的偏置电流为149.8uA,并注意到M_M3的 region为Linear

直流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt

一种恒跨导输入级轨到轨运算放大器的设计

• 189•基于CSMC 0.5um工艺设计了一种输入级恒跨导、高增益轨到轨运算放大器,输入级采用尾电流补偿结构实现了运放在全电压输入范围内输入级的恒跨导,输出级采用MOS管耦合AB类输出级实现全摆幅输出。

利用Pspice对该运算放大器仿真得到开环增益116dB,相位裕度45.6°,单位增益带宽约6.1MHZ,全电压输入范围内输入级跨导变化约为1.2%,实现了输入级跨导在全电压输入范围内的恒定。

传统的轨到轨运算放大器由于输入级跨导变化较大的原因很难进行合理的频率补偿,从而给电路的稳定性带来了很大的不确定性。

为了确保输入级跨导的恒定,以往常采用电流镜技术、电流平方根法、冗余差分对法等。

本文在详细研究了1:3电流镜电路的基础上采用了一种输入级尾电流补偿的方法设计了一款输入级恒跨导运算放大器,该运算放大器在全电压输入范围内实现了输入级跨导的基本恒定。

1 传统轨到轨运放输入级设计传统的轨到轨运放常采用互补差分对管作为运放的输入级,如图1所示。

图1 传统轨到轨运放输入级三极管的跨导:其中q为电子的电量,k为玻尔兹曼常数,T为热力学温度,所以对于任意的NPN或PNP管其跨导都与集电极偏置电流IC成线性关系。

当输入共模电压V in 在(V I1为电流源I1上的压降,V BE1,2为Q1、Q2管发射结导通压降)时PNP对管导通,NPN对管截止,此时输入级的跨导为PNP 对管的跨导:。

同理,当输入电压时NPN对管导通,PNP对管截止,此时输入级的跨导NPN 对管的跨导:。

当输入电压为时,此时输入对管全部导通,输入级跨导为两对对管单独工作时跨导之和。

综上,传统输入级的跨导在全电压输入范围内变化值接近2倍。

无法实现输入级的跨导在整个电压输入范围内保持恒定。

2 恒跨导轨到轨输入级设计通过对经典轨到轨运算放大器输入级的分析,三极管作为输入管时,其跨导与导通管的集电极电流成线性关系。

通过控制输入管导通时集电极电流的大小就可以改变输入级的跨导。

集成电路_Spice,Spectre仿真总结

集成电路_Spice,Spectre仿真总结集成电路_Spice,Spectre仿真总结Designers-Guide to Spice and Spectre 1995 USA Designers-Guide to Spice a nd Spectre — Ken Kundert 11.1 绪论 1. 为什么要读这本书①该书是介于算法和教你如何操作软件之间的一本书可以帮助你更好的使用Simulator的设置。

② Simulator仿出的结果可靠不精确不是否收敛应该如何处理如何设置③读完这本书你应该会 1 Simulator如何计算结果 2 Simulator 会产生何种错误如何识别 3 如何提高仿真精度 4 如何克服不收敛的情况 5 对于一些特殊电路会产生什么错误如何识别 6 明白仿真器里设置convergenceerror control的一些重要参数 7 能知道仿真器的错误信息出在什么地方如何解决2. 电路仿真软件的发展历史①直接方法求出电路的微分方程组用数值积分方法差分化然后用牛顿迭代法求解非线性代数方程组。

?是最准确可靠最通用的方法② Explicit integration methods ?方法问题很多③ relaxiton methods ?方法问题很多 3. Spice Options ① Global Options: Abstol控制电流默认为1pA Vntol控制电压默认为1uV Reltol相对误差对于牛顿收敛准则和截断误差准则同时起作用默认10-3对于重要电路这个应该设置小一些比如说10-5或者10-6Gmin防止非线性器件关断后的浮空节点默认为10-12 Ω-1LimptsPivrelPivtol无用处② DC Analysis Options: ltl1DC工作点最大牛顿迭代次数默认100 ltl2DC Sweep最大牛顿迭代次数默认50 ltl6Source Stepping的最大步长数增加以上3个值可以增加DC牛顿迭代收敛但是会降低速度。

第七章 集成电路器件及SPICE模型

MOS结构电容

a a + + + + + + + + + 1.0 Co 沟道 Cdep 沟道 耗尽层 p型衬底 Vss Vss (a) (b) Vgs d tox Cgb Co 0.2 积累区 耗尽区 反型区

MOS电容 (a)物理结构 (b)电容与Vgs的函数关系

MOS结构电容

Cox Cox Í µ µ Æ

l ' / 4

集总元件

由于尺寸的小型化,几乎所有集成电路的有 源元件都可认为是集总元件。前面讨论的无 源元件也可作为集总元件来处理; 随着工作频率的增加,使得一些诸如互连线 的IC元件的尺寸可以与传输信号的波长相比; 这时,集总元件模型就不能有效地描述那些 大尺寸元件的性能,应该定义为分布元件。

2

MIM电容

电容模型等效电路:

固有的自频率:

f0

1 2 LC

金属叉指结构电容

MOS结构电容

平板电容和PN结电容都不相同,MOS核心部分,即 金属-氧化物-半导体层结构的电容具有独特的性质。

它的电容-电压特性取决于半导体表面的状态。

随着栅极电压的变化,表面可处于: 积累区 耗尽区 反型区

有源电阻

I D + V S I IDS I O G S + V D (b) VGS V VTP

G

O

I IDS

VTN V (a)

VGS

MOS有源电阻及其I-V曲线

2t ox L V V 直流电阻: Ron︱VGS=V = I n ox W (V VTN ) 2

交流电阻:

跨导运算放大器的设计

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp ,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

模拟集成电路设计(跨导运算放大器)【范本模板】

模拟集成电路课程设计跨导放大器学院:电信学院班级:微电子92组长:曾云霖(09053057)组员:黄雄(09053042)蒋仪(09053043)跨导放大器设计设计题目:基于所给的CMOS工艺设计一款跨导放大器.跨导放大器的特点是具有非常大的输出阻抗,将输入电压转换成电流输出,相当于压控电流源。

该电路的设计同样需要包括偏置电压电流产生电路。

设计指标:设计指标:(供参考)性能参数测试条件参数指标负载电容30pF电源电压范围 2.5~5.5V静态电流VDD=3。

6V,Temp=27℃〈250μA输出摆幅输入共模电压VDD =3。

6V,Temp=27℃VDD =3。

6V,Temp=27℃0.6~1。

2V0。

1~1V开环增益(低频)VDD =3。

6V,Temp=27℃1800~2200单位增益带宽VDD =3。

6V,Temp=27℃>3MHz相位裕度VDD =3。

6V,Temp=27℃〉60°PSRR(低频)VDD =3。

6V,Temp=27℃>65dB跨导(低频)VDD =3.6V,Temp=27℃(900~1100)μA /V 转换速率VDD =3。

6V,Temp=27℃>3V/μs设计要求:1.确定设计指标(以上指标供参考,可以进行适当修改,但需说明原因); 2.根据设计指标,可以在参考电路结构基础上确定参数和改进设计,也可以查找文献采用其它结构的电路或创造新的电路结构进行设计;3.阅读模型文件,了解可以选用的器件类型与尺寸范围;4.手工设计:根据拟定的设计指标,初步确定满足指标的各元件的模型与参数:MOS:沟道长度与宽度,并联个数;电阻:宽度、长度、串并联个数;电容:宽度、长度、并联个数;三极管:并联个数.5.采用全典型模型,27℃,验证电路是否满足设计指标;6.设计偏置电路:a)选定电路结构;b) 手工设计:确定各元件的模型与尺寸;c)采用全典型模型,仿真验证偏置电流源的性能;7.将偏置电路和主体电路合在一起仿真,采用全典型模型,27℃,VDD=3.6V,要求电路达到“设计指标"要求,否则应对电路结构和参数进行修改与优化,直至满足要求(可能需要多次调整),并应包括以下内容:a)一输入端固定为0。

跨导运算放大器及其Spice电路模型的构建

2.1 CMOS模拟集成电路基本单元2.1.1 MOS场效应管的基本结构绝缘栅场效应管又叫作MOS场效应管,意为金属-氧化物-半导体场效应管。

图2.1为MOS场效应管的结构和电路符号。

图中的N型硅衬底是杂质浓度低的N型硅薄片。

在它上面再制作两个相距很近的P区,分别引为漏极和源极,而由金属铝构成的栅极则是通过二氧化硅绝缘层与N型衬底及P型区隔离。

这也是绝缘栅MOS场效应管名称的由来。

因为栅极与其它电极隔离,所以栅极是利用感应电荷的多少来改变导电沟道去控制漏源电流的。

MOS场效应管的导电沟道由半导体表面场效应形成。

栅极加有负电压,而N型衬底加有正电压。

由于铝栅极和N型衬底间电场的作用,使绝缘层下面的N型衬底表面的电子被排斥,而带正电的空穴被吸引到表面上来。

于是在N型衬底的表面薄层形成空穴型号的P型层,称为反型层,它把漏源两极的P区连接起来,构成漏源间的导电沟道。

沟道的宽窄由电场强弱控制。

MOS场效应管的栅极与源极绝缘,基本不存在栅极电流,输入电阻非常高。

[20,21]图2.1MOS场效应管的结构和电路符号Fig.2.1 Structure and circuit symbol that MOS Field-Effect Transistor 场效应管有P型和N型之分。

这里的P型或N型,指的是导电沟道是P型还是N 型,即导电沟道中是空穴导电还是电子导电。

因为场效应管中只有一种载流子参加导电,所以又常称为“单极型晶体管”。

P型沟道和N型沟道的MOS场效应管又各分为“耗尽型”和“增强型”两种。

耗尽型指栅极电压为零时,就存在导电沟道,漏源中间有一定电流。

增强型MOS场效应管,则只有在栅极电压大于零的情况下,才存在导电沟道。

2.1.2 MOS场效应管的模型化2.1.2.1MOS场效应管的大信号模型MOS管的大信号(直流)特性可以用它的电流方程来描述。

以N沟道增强型MOS管为例,特性曲线和电流方程如图2.2所示。

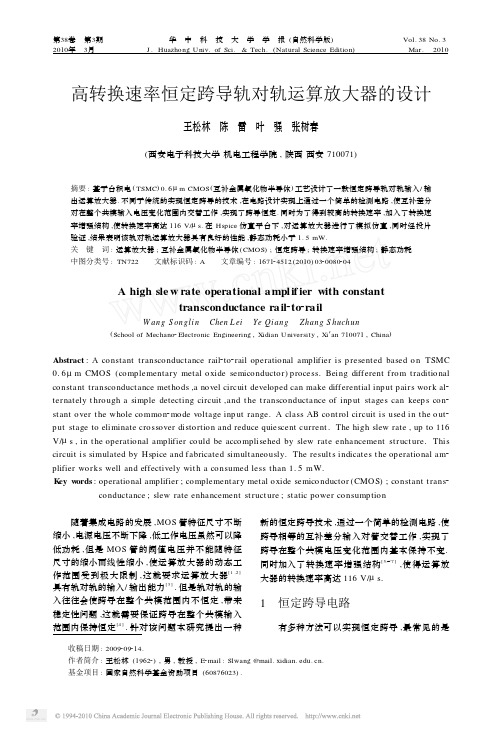

高转换速率恒定跨导轨对轨运算放大器的设计

第38卷 第3期2010年 3月 华 中 科 技 大 学 学 报(自然科学版)J.Huazhong Univ.of Sci.&Tech.(Natural Science Edition )Vol.38No.3 Mar. 2010收稿日期:2009209214.作者简介:王松林(19622),男,教授,E 2mail :Slwang @.基金项目:国家自然科学基金资助项目(60876023).高转换速率恒定跨导轨对轨运算放大器的设计王松林 陈 雷 叶 强 张树春(西安电子科技大学机电工程学院,陕西西安710071)摘要:基于台积电(TSMC )0.6μm CMOS (互补金属氧化物半导体)工艺设计了一款恒定跨导轨对轨输入/输出运算放大器.不同于传统的实现恒定跨导的技术,在电路设计实现上通过一个简单的检测电路,使互补差分对在整个共模输入电压变化范围内交替工作,实现了跨导恒定.同时为了得到较高的转换速率,加入了转换速率增强结构,使转换速率高达116V/μs.在Hspice 仿真平台下,对运算放大器进行了模拟仿真,同时经投片验证,结果表明该轨对轨运算放大器具有良好的性能,静态功耗小于1.5mW.关 键 词:运算放大器;互补金属氧化物半导体(CMOS );恒定跨导;转换速率增强结构;静态功耗中图分类号:TN722 文献标识码:A 文章编号:167124512(2010)0320080204A high sle w rate operational amplif ier with constanttransconductance rail 2to 2railW ang S ongli n Chen L ei Ye Qi ang Zhang S huchun(School of Mechano 2Electronic Engineering ,Xidian University ,Xi ′an 710071,China )Abstract :A constant t ransconductance rail 2to 2rail operational amplifier is presented based o n TSMC0.6μm CMOS (complementary metal oxide semiconductor )process.Being different from traditional constant t ransconductance met hods ,a novel circuit developed can make differential inp ut pairs work al 2ternately t hrough a simple detecting circuit ,and t he t ransconductance of inp ut stages can keep s con 2stant over t he whole common 2mode voltage inp ut range.A class AB cont rol circuit is used in t he out 2p ut stage to eliminate crossover distortion and reduce quiescent current.The high slew rate ,up to 116V/μs ,in t he operational amplifier could be accomplisehed by slew rate enhancement st ruct ure.This circuit is simulated by Hspice and fabricated simultaneously.The result s indicates t he operational am 2plifier works well and effectively wit h a consumed less t han 1.5mW.K ey w ords :operational amplifier ;complementary metal oxide semiconductor (CMOS );constant t rans 2conductance ;slew rate enhancement st ruct ure ;static power consumption 随着集成电路的发展,MOS 管特征尺寸不断缩小,电源电压不断下降,低工作电压虽然可以降低功耗,但是MOS 管的阈值电压并不能随特征尺寸的缩小而线性缩小,使运算放大器的动态工作范围受到极大限制,这就要求运算放大器[1,2]具有轨对轨的输入/输出能力[3].但是轨对轨的输入往往会使跨导在整个共模范围内不恒定,带来稳定性问题,这就需要保证跨导在整个共模输入范围内保持恒定[4].针对该问题本研究提出一种新的恒定跨导技术,通过一个简单的检测电路,使跨导相等的互补差分输入对管交替工作,实现了跨导在整个共模电压变化范围内基本保持不变.同时加入了转换速率增强结构[5~7],使得运算放大器的转换速率高达116V/μs.1 恒定跨导电路有多种方法可以实现恒定跨导,最常见的是利用电流补偿实现跨导恒定[8],这种方法的缺点是过分依赖于理想的平方律模型,当MOS 管工作在强反型层和弱反型层时不能通用.另一方法是最大/最小电流选择法[9],这种方法是在输入共模电压范围内只取跨导最大的差分对,其缺点是电路设计相对复杂,并且电路工作时跨导较小的差分对也在工作,只是没有将其变化的信号电流输出去,因此浪费了一部分能量.图1为本文设计的恒定跨导电路.输入互补差分对由MN 1和MN 2,M P 1和M P 2组成.MN 4和M P 4、基准电流源I ref 、电阻R N 1,R N 2和R P 1-R P 2以及门电路开关SW 1和SW 2共同组成恒定跨导电路的检测电路.电路工作原理为:当输入共模电压比较低时,只有PMOS 差分对工作,则输入级总跨导G m.tot =G mp (差分对跨导).随着输入共模电平V CM 的上升,MP 3的源漏电压V SDMP 3减小,一旦V CM ≥V ref 2时,MP 4导通,M P 4的漏端输出高电平使开关SW 2闭合,NMOS 差分对开始工作,此时由于共模电压比较高,V CM >V ref 1,MN 4截止,MN 4的漏图1 恒定跨导输入级电路结构端输出高电平使开关SW 1断开,PMOS 差分对停止工作,则G m.tot =G mn (NMOS 差分对跨导).随着V CM 的下降,V DSMN 3减小,一旦V CM ≤V ref 1时,MN 4导通,MN 4的漏端输出低电平使开关SW 1闭合,PMOS 差分对开始工作,此时由于共模电压比较低,V CM <V ref 2,M P 4截止,M P 4的漏端输出低电平使开关SW 2断开,NMOS 差分对停止工作,则G m.tot =G mp .由此可知NMOS 管工作的共模输入电压的范围为V ref 1≤V CM ≤V DD ,PMOS 管工作的共模输入电压的范围为V GND ≤V CM ≤V ref 2,选择合理的参数,使G mn =G mp ,就可保证输入级总跨导在整个共模输入电平变化范围之内保持恒定.V ref 1和V ref 2的设定如下:因为V GSN 1,2≈V GSMN 4,V SGP 1,2≈V SGMP 4,近似认为V ref 1≈I ref R N 2,V ref 2≈V DD -I ref R P 2,并且V ref 1≤V ref 2,此外V ref 1-V GSN 1,2≥V OD.MN 3,V ref 2-V SGN 1,2≥V OD.MP 3,这是为了避免MN 3和M P 3工作在非线性区,保证整个共模范围内跨导恒定,其中,V OD 为过驱动电压.由于差分对交替工作时,检测电路会使即将工作的差分对先工作,之后再关断另一对差分对,这种时序控制方式保证输入级电路时刻都有跨导(即始终有增益),有效地避免在切换过程中出现信号的不连续现象.2 转换速率增强结构由于该运算放大器主要用于TF T 2L CD 源极驱动,对运算放大器的转换速率要求较高,因此在电路设计时加入了转换速率增强结构,此结构主要作用是当运算放大器经历大信号转换时加快输出信号的翻转,而当小信号放大时不影响运算放大器的其他性能.转换速率增强结构电路如图2所示,PMOS 差分对工作时的转换速率增强结构与NMOS 差图2 转换速率增强结构电路分对工作时的结构类似,图2只给出NMOS 差分对工作时电路.其中:M 1~M 6和M 10~M 11分别组成运算放大器的第一级(低压Cascode 结构)和第二级(推挽输出结构);M 7,M 8,M 9和M 12则组成了转换速率增强结构电路.电路具体工作原理为:正常情况下,I M 7>I 4,I 5>I M 8,此时A 点电压为高电平,B 点电压为低电平,开关管M 9和M 12不导通.当在正向端POS 加一个正阶跃信号时,M 2截止,尾电流I 1全部流入M 1,使M 5的电流瞬间变小,相应地镜像管M 7和M 8上的电流也变得很小,使I 4>I M 7,I 5>I M 8,A 点电压由高变低,B 点始终保持为低电平,使M 9导通,电流源I 6给运算放大器输出端V OU T・18・第3期 王松林等:高转换速率恒定跨导轨对轨运算放大器的设计 提供电流,加速了正向转换速率.同样,当在负向端N EG 加一个正阶跃信号时,M 1截止,尾电流I 1全部流入M 2,使M 5的电流瞬间变得很大,相应地镜像管M 7和M 8上的电流也变得很大,使I M 7>I 4,I M 8>I 5,B 点电压由低变高,A 点始终保持为高电平,使M 12导通,电流源I 3加快运算放大器输出端V OU T 的放电,加速了负向转换速率.同样的原理应用在PMOS 差分对工作时的转换速率增强结构电路上.3 仿真及测试结果基于台积电(TSMC )0.6μm CMOS 工艺模型,电源电压V DD 为12V ,在Hspice 仿真平台下对所设计的电路进行模拟仿真,图3给出了运算图3 在不同温度下跨导随共模电压变化的仿真曲线1—-40℃;2—25℃;3—85℃;4—125℃放大器在不同温度(-40℃,25℃,85℃,125℃)下跨导随共模电压变化的仿真曲线图,表明跨导在整个共模变化范围内变化仅为0.5%,基本保持恒定,且在整个曲线中没有出现尖锐的不连续现象,符合设计要求.此外,该轨对轨运算放大器已在该工艺线上投片,对芯片进行实测验证.图4为运算放大器轨对轨特性实测波形,其中:CH 2为输出波形;C H 4为输入波形.测试条件:电源电压V DD =12V ,运算放大器接成单位增益缓冲级结构,输入端加一个0~12V 的满摆幅信号,结果表明运算放大器具有良好的轨对轨特性.图4 运算放大器轨对轨特性实测波形图5是运算放大器转换速率特性实测波形,图5 运算放大器转换速率实测波测试条件为:电源电压V DD =12V ,运算放大器接成单位增益缓冲级结构,在运算放大器的输入端加一个在1~9V 之间跳变的正负阶跃信号,如CH 4波形所示,观察输出波形C H 2,结果显示:正向转换速率(SR +)约为118V/μs ,负向转换速率(SR -)约为-114V/μs ,运算放大器具有较高的转换速率,满足设计要求.在后端版图设计过程中,通过合理的布局、布线,减少运算放大器的失调.含有恒定跨导轨对轨运算放大器的芯片中运算放大器的面积仅为400μm ×275μm.表1还给出了运算放大器其他性能指标及与文献中指标的对比.表1 运算放大器的性能指标及与文献中指标的对比参数本文文献[10]文献[11]电源电压/V 3~1233输入级跨导变化率/%≤0.52.9-低频增益/dB 110.063.680.0单位增益带宽/M Hz 18.20 3.554.30共模抑制比/dB 120.787.6-转换速率/(V ・μs -1)118/-1148.5/-8.235/-35电源抑制比/dB112.0068.73-静态功耗/mW<1.501.63 注:“/”前为SR +的;“/”后为SR -的为使轨对轨运算放大器在整个共模电压变化范围内都能稳定,需要保证运算放大器的输入级跨导不随共模电压的变化而变化,相比传统的轨对轨运算放大器,本文提出了一种结构简单、具有高转换速率的恒定跨导轨对轨运算放大器.通过一个简单的检测电路,使两个跨导相等的互补输入差分对交替工作,保证输入级跨导在整个共模电压变化范围内保持恒定.在电路中加入转换速率增强结构后,显著提高了运算放大器的转换速率.仿真及实测结果显示该运算放大器具有良好的性能,跨导在整个共模电压变化范围内变化小于0.5%,保证了运算放大器的稳定性,并且静态・28・ 华 中 科 技 大 学 学 报(自然科学版) 第38卷电流很低,可应用于各种低压高速信号处理场合.参考文献[1]邹雪城,鲁 力,张程龙,等.采用负电阻技术的增益恒定放大器[J].华中科技大学学报:自然科学版, 2008,36(6):54256.[2]陈晓飞,刘三清,张诗娟,等.一种新颖的全差分CM O S运算放大器的设计[J].华中科技大学学报:自然科学版,2004,32(12):21223.[3]Baez2Villegas D,Silva2Martinez J.Quasi rail2to2railvery low2voltage OP2AMP with a single PMOS input differential pair[J].IEEE Trans on Circuit and Sys2 tem2II,2006,53(11):117521179.[4]Yan Shouli,Hu Jingyu,Song Tongyu,et al.A con2stant2gm rail2to2rail op amp input stage using dynamic current scaling technique[C]∥IEEE International Symposium on Circuits and System.K obe:IEEE, 2005:256722570.[5]Yavari M,Maghari N,Shoaei O.An accurate analy2sis of slew rate for two2stage CMOS op amps[J].IEEE Trans on Circuit and System2II,2005,52(3):1642167.[6]Chiu J ui2Te.Rail2to2rail operational amplifier with anenhanced slew rate:United States Patent,7339430 [P].2006207226.[7]Rezaei M,Zhian2Tabasy E,Ashtiani S J.Slew rateenhancement method for folded2cascode amplifiers [J].Electronics Letters,2008,44(21):12262 1228.[8]艾 伦.CMOS模拟集成电路设计[M].2版.冯 军,李智群,译.北京:电子工业出版社,2005. [9]朱 莹,李 丽.一种高共模抑制比恒定跨导运算放大器[J].微电子学,2007,37(1):2422245.[10]Ramirez2Angulo J,Lopez2Martin A J,Carvajal RG,et al.Class2AB f ully differential voltage follow2 ers[J].IEEE Trans on Circuit and System2II,2008,55(2):1312135.[11]Di2Cataldo G,Grasso A D,Pennisi S.Two CMOScurrent feedback operational amplifiers[J].IEEETrans on Circuits and System2II,2007,54(11):9442948.(上接第71页)[2]Shin D J,Sung W J,K im I K.Simple SNR estima2tion methods for QPSK modulated short bursts[C]∥Proceeding of G lobal Telecommunications Confer2 ence.New Y ork:IEEE,2001:364423647.[3]Athanasios D,Kalivas G.SNR estimation for low bitrate OFDM systems in AW GN channel[C]∥Proceed2 ing of International Conference on Networking,Inter2 national Conference on Systems and International Conference on Mobile Communications and Learning Technologies.Mauritius:IEEE,2006:1982203. [4]Wiesel A,G oldberg J,Messer2Yaron H.SNR esti2mation in time2varying fading channels[J].IEEE Transactions on Communications,2006,54(5):8412 848.[5]Morelli M,Moretti M,Imbarlina G,et al.Low com2plexity SNR estimation for transmissions over time2 varying flat2fading channels[C]∥Proceeding of IEEE Wireless Communications and Networking Confer2 ence.Budapest:IEEE,2009:124.[6]Boumard S.Novel noise variance and SNR estimationalgorithm for wireless MIMO OFDM systems[C]∥Proceeding of IEEE G lobal Telecommunications Con2 ference.San Francisco:IEEE,2003:133021334. [7]Ren G,Chang Y,Zhang H.SNR estimation algo2rithm based on the preamble for wireless OFDM sys2 tems[J].Science in China Series F:Information Sci2 ences,2008,51(7):9652974.[8]Ren G,Chang Y,Zhang H.A new SNR’s estimatorfor Q PSK modulations in an AW GN channel[J].IEEE Transactions on Circuits and Systems2II: Express Brieves,2005,52(6):3362338.[9]林宏志,朱光喜,王德胜,等.正交频分复用系统中脉冲成型信道估计算法[J].华中科技大学学报:自然科学版,2009,37(2):124.[10]Gappmair W.Cramer2Rao lower bound for non2data2aided SNR estimation of linear modulation schemes [J].IEEE Transactions on Communications,2008, 56(5):6892693.[11]Jeruchim M C,Balaban P,Shanmugan K S.Simula2tion of communication systems:modeling,method2 ology,and techniques[M].2nd Edition.NewY ork:Kluwer Acdemic Publishers,2000.・38・第3期 王松林等:高转换速率恒定跨导轨对轨运算放大器的设计 。

集成电路器件及SPICE模型通用课件

场效应管的SPICE模型

场效应管SPICE模型是模拟场效应管特性的数学模型。

场效应管SPICE模型包括沟道电流、阈值电压等参数,用于模拟场效应管在电路 中的行为。

集成电路器件SPICE模型的参数提取与优化

异构集成与三维集成中的SPICE模型挑战

随着集成电路技术的发展,异构集成和三维集成已经成为趋势。在异构集成和三维集成中, 不同材料和器件之间的相互作用和耦合效应更加复杂,因此需要更加精细的SPICE模型来模 拟。

现有的SPICE模型主要是针对单一器件或单一材料的仿真而设计的,因此在异构集成和三维 集成中需要进行改进和扩展。这需要研究新的建模方法和参数提取技术,以适应不同材料和 器件之间的耦合效应。

电阻器

电阻器是限流元件,用于调节 电路中的电流和电压,分为线 绕、薄膜和厚膜电阻器等类型。

电容器

电容器是储能元件,用于隔直、 滤波和旁路等作用,分为陶瓷、

薄膜和电解电容器等类型。

集成电路器件的工作原理

双极型晶体管工作原理

双极型晶体管利用载流子的扩散与漂移运动 控制电流,具有电流放大作用。

二极管工作原理

优化设计

基于SPICE模型的仿真结果,可以对 电路设计进行优化,改进电路的性能 指标,降低功耗和提高稳定性。

元件匹配与版图布局

元件匹配

SPICE模型可以模拟元件之间的匹配 情况,帮助设计者找到元件的最佳配 置,以确保电路性能的稳定。

版图布局

利用SPICE模型进行版图布局的模拟, 可以预测元件之间的耦合效应和信号 干扰,从而优化版图设计。

VS

效率

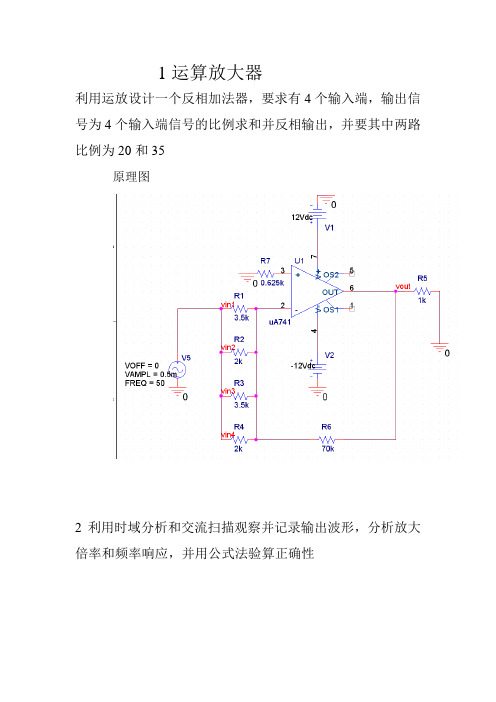

pspice运算放大器 反馈放大 串联稳压电路.

1运算放大器利用运放设计一个反相加法器,要求有4个输入端,输出信号为4个输入端信号的比例求和并反相输出,并要其中两路比例为20和35原理图2利用时域分析和交流扫描观察并记录输出波形,分析放大倍率和频率响应,并用公式法验算正确性2.1静态工作点及公式法公式法2.2时域分析60mV40mV20mV-0mV-20mV-40mV-60mV0s10ms20ms30ms40ms50ms60ms70ms80ms90ms100ms V(vin2)V(vout)V(vin2)V(vin3)V(vin4)Time2.3交流扫描1201008060402010mHz100mHz 1.0Hz10Hz100Hz 1.0KHz10KHz100KHz 1.0MHz10MHz100MHz 1.0GHz V(vout) / V(vin1)Frequency3测试不同负载时的输出波形3.1当R=1时原理图波形图50mV0V-50mV0s10ms20ms30ms40ms50ms60ms70ms80ms90ms100ms V(vin1)V(vout)Time3.2当R=1000k原理图波形图60mV40mV20mV-0mV-20mV-40mV-60mV0s10ms20ms30ms40ms50ms60ms70ms80ms90ms100ms V(vin1)V(vout)Time4测试上下限截止频率4.1原理图波形图由图,此电路是一个低通滤波器,没有下限截止频率,可以由输出下降到原来的0.7倍读出上限截止频率fH=9k2反馈放大电路1利用三极管实现电压并联负反馈电路,要求使用3个三极管级联并联放大电路原理图2.1时域分析2.2交流扫描2.3公式法以及静态工作点3测试不同负载时的输出波形3.1当R=1时原理图波形图3.2当R=1M时原理图波形图3测试上下限截止频率原理图波形图由图,此电路是一个低通滤波器,没有下限截止频率,可以由输出下降到原来的0.7倍读出上限截止频率fH=124k串联稳压电路设计并实现串联稳压电路1原理图2.1时域分析2.2交流扫描由图,此电路是一个低通滤波器2.3测试上限截止频率其上限截止频率fH=190k2.4静态工作点以及公式法3利用直流扫描分析稳压过程原理图波形图如图当Vin<14V时,Vout随Vin线性增加,这是因为稳压管未到稳压值,其电压也是随输入增加而增加。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2.1 CMOS模拟集成电路基本单元2.1.1 MOS场效应管的基本结构绝缘栅场效应管又叫作MOS场效应管,意为金属-氧化物-半导体场效应管。

图2.1为MOS场效应管的结构和电路符号。

图中的N型硅衬底是杂质浓度低的N型硅薄片。

在它上面再制作两个相距很近的P区,分别引为漏极和源极,而由金属铝构成的栅极则是通过二氧化硅绝缘层与N型衬底及P型区隔离。

这也是绝缘栅MOS场效应管名称的由来。

因为栅极与其它电极隔离,所以栅极是利用感应电荷的多少来改变导电沟道去控制漏源电流的。

MOS场效应管的导电沟道由半导体表面场效应形成。

栅极加有负电压,而N型衬底加有正电压。

由于铝栅极和N型衬底间电场的作用,使绝缘层下面的N型衬底表面的电子被排斥,而带正电的空穴被吸引到表面上来。

于是在N型衬底的表面薄层形成空穴型号的P型层,称为反型层,它把漏源两极的P区连接起来,构成漏源间的导电沟道。

沟道的宽窄由电场强弱控制。

MOS场效应管的栅极与源极绝缘,基本不存在栅极电流,输入电阻非常高。

[20,21]图2.1MOS场效应管的结构和电路符号Fig.2.1 Structure and circuit symbol that MOS Field-Effect Transistor 场效应管有P型和N型之分。

这里的P型或N型,指的是导电沟道是P型还是N 型,即导电沟道中是空穴导电还是电子导电。

因为场效应管中只有一种载流子参加导电,所以又常称为“单极型晶体管”。

P型沟道和N型沟道的MOS场效应管又各分为“耗尽型”和“增强型”两种。

耗尽型指栅极电压为零时,就存在导电沟道,漏源中间有一定电流。

增强型MOS场效应管,则只有在栅极电压大于零的情况下,才存在导电沟道。

2.1.2 MOS场效应管的模型化2.1.2.1MOS场效应管的大信号模型MOS管的大信号(直流)特性可以用它的电流方程来描述。

以N沟道增强型MOS管为例,特性曲线和电流方程如图2.2所示。

图2.2 特性曲线和电流方程Fig.2.2 Characteristic property curve and electric current equation如果栅源偏置电压GS V 大于MOS 管的阈值电压T V ,则在P 型衬底的表面由于静电感应会产生大量的电子,形成导电沟道。

当漏区相对于源区加一正电压DS V 时,在器件内部的沟道中就会产生电流D I 。

MOS 管的工作状态可分为三个区,即电阻区(线性区)、饱和区和截止区。

(1)截止区: V GS <V T 。

此时不能产生导电沟道,漏极电流I D =0。

(2)电阻区:V GS >V T 且V DS <V GS -V T 。

])(2[2'2DS DS T GS D V V V V LW K I --= (2.1) 其中,W 是沟道宽度,L 是沟道长度,V T 阈值电压,0'C K μ=称为跨导参数,μ是载流子的沟道迁移率,0C 是单位电容的栅电容。

(3)饱和区:V GS >V T 且V DS >V GS -V T 。

临界饱和条件为V DS =V GS -V T ,临界饱和时的漏极电流为:2'()2D GS T K W I V V L=- (2.2) 在饱和区,V DS 增大时,I D 几乎不变,所以上式也是饱和区的漏极电流一般公式。

当考虑到沟道长度调变效应之后,饱和区的MOS 管漏极电流为:2'()(1)2D GS T DS K W I V V V Lλ=-+ (2.3) 其中,λ为沟道长度调制系数,对于长度为L 的MOS 管,其大信号特性可近似认为λ是常数,并只取决于生产工艺,而与D I 无关。

[22,23]2.1.2.2 MOS 场效应管的小信号模型输入信号的幅度与电源电压相比较一般很小,它在直流偏置工作点附近变化时,可以近似认为器件工作在线性区间。

大信号特性可以确定器件的直流工作点,小信号特性可以用来设计器件和电路的性能。

MOS 管的小信号模型可以直接由直流模型得出。

在大多数应用中,MOS 管被偏置在饱和区工作,考虑到栅源、栅漏及漏源之间的寄生电容,MOS 管的饱和区小信号模型如图2.3所示。

GSD m V I g ∂∂= (2.4) 式中, m g 为跨导,表征输入电压对输出电流的控制能力。

对于在饱和区工作的模型参数,应用式2.2和2.4得:D m I LW K g '2= (2.5) 其中,D I 是漏极的直流电流。

G图2.3 小信号模型Fig.2.3 S mall signal model当电路在低频工作时可以不考虑这些寄生电容的影响,此时的小信号等效电路如图2.4所示。

图2.4不考虑电容影响的小信号等效电路Fig.2.4 Small signal equivalent circuit that do’t consider capacitance affects2.1.3 CMOS 电流镜电流镜是模拟集成电路中普遍存在的一种标准部件,在传统的电压模式运算放大器设计中,电流镜用来产生偏置电流和作为有源负载。

2.1.3.1 基本CMOS 电流镜IR VSSIO IR(a)基本NMOS 电流镜 (b )基本PMOS 电流镜图2.5 基本CMOS 电流镜Fig.2.5 Fundamental CMOS electric current mirror基本CMOS 电流镜如图2.5所示,其中图(a)为NMOS 电流镜,图(b)为PMOS 电流镜。

在图(a)中,M 1的栅源短接,V DSI >V GS - V TI ,所以M l 总工作于饱和区。

只要V DS2>V DS1-V T2,M 2也工作于饱和区,漏极的交流输出电阻很高,这是图(a)作为电流镜的必要条件。

在这个条件下,由式2.3,有:)1()(2'22222222DS T GS O V V V L W K I λ+-= (2.6) )1()(2'11211111DS T GS R V V V L W K I λ+-= (2.7) 如果Ml 与M2完全匹配,有''21'K K =,V T1=V T2,,λ1=λ2 =λ,则:212121(1)(1)O DS R DS I W L V I W L V λλ+=+ (2.8) 对于基本CMOS 电流镜,由于沟道长度调制效应的影响,当MOS 管的漏源电压不等时,会引起电流镜电流跟随误差。

但由于λ很小,所以误差也很小。

2.1.3.2 CMOS 级联电流镜VSSIO IR(a)NMOS 级联电流镜 (b)PMOS 级联电流镜图2.6 CMOS 级联电流镜 Fig.2.6 CMOS level unites the voltaic mirror图2.6为级联电流镜电路图。

图中M 1与M 3级联,M 2与M 4级联。

图2.6(a)为NMOS 级联电流镜,图2.6(b)为PMOS 级联电流镜。

在图2.6中,有I O =I D2,I R =I D1 ,V GS1=V GS2,由式2.3得:)1(')1('1121122122DS DS R O V L W K V L W K I I λλ++= (2.9) 因为M 1与M 3级联,I D1=I D3,又V DS1=V GS1,V DS3=V GS3,那么当M1与M3的工艺参数相同时,由饱和区漏极电流表达式可知:V GS1=V GS3 。

M2与M4级联,有I D2=I D4,由饱和区漏极电流表达式可知:V GS2=V GS4。

对于V DS1、V DS2,有V DS1=V GS1,V DS2=V GS3-V GS4+V GS1 ,又V GS1=V GS2,可得:V DS1=V DS2 。

如果M 1、M 2的工艺参数相等,那么可得:2112O R I W L I W L = (2.10)当1122L W L W =时,有: R O I I = (2.11)由于级联电流镜的漏源电压基本相等,其电流跟随特性较好,跟随精度较高。

2.1.4 基本源耦差分对电路的跨导分析源耦合差分放大器在模拟集成电路中有着广泛的应用,如集成运放的输入级均采用差分放大器的电路结构[24]。

这是因为差分放大器只对差分信号进行放大,而对共模信号可进行抑制,有很强的抗干扰能力,并具有漂移小、级与级间很容易直接耦合等优点。

如图2.7所示为一个基本的MOS 源耦合差分对管电路。

图中的M1、M2是完全对称的,其工作电流(IDI 、ID2)由电流源Iss 提供。

输出电流ID1、ID2的大小依赖于输入电压的差值(Vi1-Vi2),但ID1和ID2之和恒等于电流源Iss ,在M1和M2的漏极分别接上电阻负载或MOS 管有源负载,即构成差分放大器,由电流输出转换成电压输出,实现电压放大。

Vi1Vi2V-图2.7 基本源耦合差分放大器电路Fig.2.7 Fundamental source coupling differences amplifiers circuitMOS 管M1和M2满足理想对称条件,其体效应和沟道长度调制效应均可忽略,并且始终工作在饱和区,则根据MOS 管在饱和区的电流方程式有:211)(T G S D V V K I -⋅= (2.12)222)(T G S D V V K I -⋅= (2.13)式中,LW K K 2'=差模输入电压为:KI K I V V V D D GS GS id 2121+=-= (2.14) 又:SS D D I I I =+21 (2.15) 则联立可得:21212221id SS SS idSS D V I K KI V I I -+= (2.16) 22212221id SS SS idSS D V I K KI V I I --= (2.17) 从而得到源耦合差分对的输出电流为:221212id SS id SS D D O V I K V I K I I I -⋅⋅⋅=-= (2.18) 跨导: SS idSSid SS id O m I V K I V K I K V I g 21)1(222⋅-⋅-⋅=∂∂= (2.19)上式表明,CMOS 源耦差分放大器的跨导与Iss 的平方根成正比,同时也与K 的平方根成正比,可通过调节偏置电流或差分对管沟道宽长比W/L 来调节跨导的数值。

2.2 MOS-OTA 基本电路模型及工作原理跨导运算放大器,简称OTA (Operational Transconductance Amplifier ),是一种电压输入、电流输出的电子放大器,可分为双极型和MOS 型两种,它们的功能在本质上是相同的,都是线性电压控制电流源。