compiler-03_practic

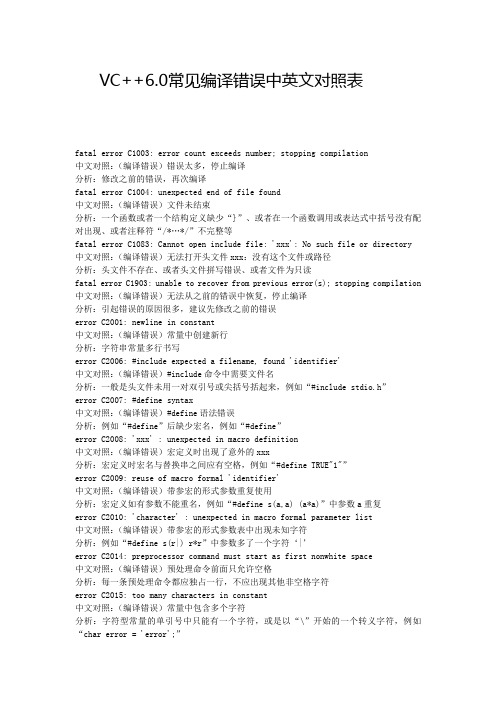

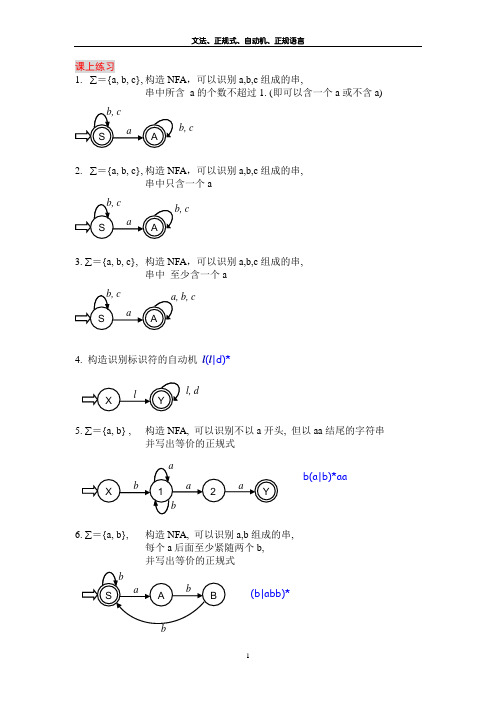

VC++6.0常见编译错误中英文对照表

VC++6.0常见编译错误中英文对照表fatal error C1003: error count exceeds number; stopping compilation中文对照:(编译错误)错误太多,停止编译分析:修改之前的错误,再次编译fatal error C1004: unexpected end of file found中文对照:(编译错误)文件未结束分析:一个函数或者一个结构定义缺少“}”、或者在一个函数调用或表达式中括号没有配对出现、或者注释符“/*…*/”不完整等fatal error C1083: Cannot open include file: 'xxx': No such file or directory 中文对照:(编译错误)无法打开头文件xxx:没有这个文件或路径分析:头文件不存在、或者头文件拼写错误、或者文件为只读fatal error C1903: unable to recover from previous error(s); stopping compilation 中文对照:(编译错误)无法从之前的错误中恢复,停止编译分析:引起错误的原因很多,建议先修改之前的错误error C2001: newline in constant中文对照:(编译错误)常量中创建新行分析:字符串常量多行书写error C2006: #include expected a filename, found 'identifier'中文对照:(编译错误)#include命令中需要文件名分析:一般是头文件未用一对双引号或尖括号括起来,例如“#include stdio.h”error C2007: #define syntax中文对照:(编译错误)#define语法错误分析:例如“#define”后缺少宏名,例如“#define”error C2008: 'xxx' : unexpected in macro definition中文对照:(编译错误)宏定义时出现了意外的xxx分析:宏定义时宏名与替换串之间应有空格,例如“#define TRUE"1"”error C2009: reuse of macro formal 'identifier'中文对照:(编译错误)带参宏的形式参数重复使用分析:宏定义如有参数不能重名,例如“#define s(a,a) (a*a)”中参数a重复error C2010: 'character' : unexpected in macro formal parameter list中文对照:(编译错误)带参宏的形式参数表中出现未知字符分析:例如“#define s(r|) r*r”中参数多了一个字符‘|’error C2014: preprocessor command must start as first nonwhite space中文对照:(编译错误)预处理命令前面只允许空格分析:每一条预处理命令都应独占一行,不应出现其他非空格字符error C2015: too many characters in constant中文对照:(编译错误)常量中包含多个字符分析:字符型常量的单引号中只能有一个字符,或是以“\”开始的一个转义字符,例如“char error = 'error';”error C2017: illegal escape sequence中文对照:(编译错误)转义字符非法分析:一般是转义字符位于 ' ' 或 " " 之外,例如“char error = ' '\n;”error C2018: unknown character '0xhh'中文对照:(编译错误)未知的字符0xhh分析:一般是输入了中文标点符号,例如“char error = 'E';”中“;”为中文标点符号error C2019: expected preprocessor directive, found 'character'中文对照:(编译错误)期待预处理命令,但有无效字符分析:一般是预处理命令的#号后误输入其他无效字符,例如“#!define TRUE 1”error C2021: expected exponent value, not 'character'中文对照:(编译错误)期待指数值,不能是字符分析:一般是浮点数的指数表示形式有误,例如123.456Eerror C2039: 'identifier1' : is not a member of 'identifier2'中文对照:(编译错误)标识符1不是标识符2的成员分析:程序错误地调用或引用结构体、共用体、类的成员error C2041: illegal digit 'x' for base 'n'中文对照:(编译错误)对于n进制来说数字x非法分析:一般是八进制或十六进制数表示错误,例如“int i = 081;”语句中数字‘8’不是八进制的基数error C2048: more than one default中文对照:(编译错误)default语句多于一个分析:switch语句中只能有一个default,删去多余的defaulterror C2050: switch expression not integral中文对照:(编译错误)switch表达式不是整型的分析:switch表达式必须是整型(或字符型),例如“switch ("a")”中表达式为字符串,这是非法的error C2051: case expression not constant中文对照:(编译错误)case表达式不是常量分析:case表达式应为常量表达式,例如“case "a"”中“"a"”为字符串,这是非法的error C2052: 'type' : illegal type for case expression中文对照:(编译错误)case表达式类型非法分析:case表达式必须是一个整型常量(包括字符型)error C2057: expected constant expression中文对照:(编译错误)期待常量表达式分析:一般是定义数组时数组长度为变量,例如“int n=10; int a[n];”中n为变量,这是非法的error C2058: constant expression is not integral中文对照:(编译错误)常量表达式不是整数分析:一般是定义数组时数组长度不是整型常量error C2059: syntax error : 'xxx'中文对照:(编译错误)‘xxx’语法错误分析:引起错误的原因很多,可能多加或少加了符号xxxerror C2064: term does not evaluate to a function中文对照:(编译错误)无法识别函数语言分析:1、函数参数有误,表达式可能不正确,例如“sqrt(s(s-a)(s-b)(s-c));”中表达式不正确2、变量与函数重名或该标识符不是函数,例如“int i,j; j=i();”中i不是函数error C2065: 'xxx' : undeclared identifier中文对照:(编译错误)未定义的标识符xxx分析:1、如果xxx为cout、cin、scanf、printf、sqrt等,则程序中包含头文件有误2、未定义变量、数组、函数原型等,注意拼写错误或区分大小写。

Encounter RTL Compiler命令参考手册(中文版)说明书

July 20092003-2009 Cadence Design Systems, Inc. All rights reserved.Portions © Concept Engineering GmbH. Used by permission.Printed in the United States of America.Cadence Design Systems, Inc. (Cadence), 2655 Seely Ave., San Jose, CA 95134, USA.Product Encounter™ RTL Compiler contains technology licensed from, and copyrighted by: Concept Engineering GmbH, and is 1998-2006, Concept Engineering GmbH. All rights reserved.Open SystemC,Open SystemC Initiative,OSCI,SystemC,and SystemC Initiative are trademarks or registered trademarks of Open SystemC Initiative, Inc. in the United States and other countries and are used with permission.Trademarks:Trademarks and service marks of Cadence Design Systems,Inc.contained in this document are attributed to Cadence with the appropriate symbol. For queries regarding Cadence’s trademarks, contact the corporate legal department at the address shown above or call 800.862.4522. All other trademarks are the property of their respective holders.Restricted Permission:This publication is protected by copyright law and international treaties and contains trade secrets and proprietary information owned by Cadence.Unauthorized reproduction or distribution of this publication,or any portion of it,may result in civil and criminal penalties.Except as specified in this permission statement,this publication may not be copied,reproduced,modified,published,uploaded,posted,transmitted, or distributed in any way, without prior written permission from Cadence. Unless otherwise agreed to by Cadence in writing, this statement grants Cadence customers permission to print one (1) hard copy of this publication subject to the following conditions:1.The publication may be used only in accordance with a written agreement between Cadence and itscustomer.2.The publication may not be modified in any way.3.Any authorized copy of the publication or portion thereof must include all original copyright, trademark,and other proprietary notices and this permission statement.4.The information contained in this document cannot be used in the development of like products orsoftware, whether for internal or external use, and shall not be used for the benefit of any other party, whether or not for consideration.Patents:Cadence Product Encounter™RTL Compiler described in this document,is protected by U.S.Patents [5,892,687]; [6,470,486]; 6,772,398]; [6,772,399]; [6,807,651]; [6,832,357]; and [7,007,247]Disclaimer:Information in this publication is subject to change without notice and does not represent a commitment on the part of Cadence. Except as may be explicitly set forth in such agreement, Cadence does not make, and expressly disclaims, any representations or warranties as to the completeness, accuracy or usefulness of the information contained in this document. Cadence does not warrant that use of such information will not infringe any third party rights,nor does Cadence assume any liability for damages or costs of any kind that may result from use of such information.Restricted Rights:Use,duplication,or disclosure by the Government is subject to restrictions as set forth in FAR52.227-14 and DFAR252.227-7013 et seq. or its successorContentsAlphabetical List of Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17Preface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23 About This Manual. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24 Additional References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .24 How to Use the Documentation Set. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25 Reporting Problems or Errors in Manuals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26 Customer Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26 Cadence Online Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26 Other Support Offerings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26 Messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 Man Pages. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27 Command-Line Help . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Getting the Syntax for a Command . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Getting the Syntax for an Attribute. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .28 Searching for Attributes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29 Searching For Commands When Y ou Are Unsure of the Name . . . . . . . . . . . . . . . .29 Documentation Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30 T ext Command Syntax. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .301Navigation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .31 basename. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32 cd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33 dirname . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35 dirs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .36filter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..37find . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39 inout_mate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44 ll . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45ls. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46 popd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50 pushd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51 pwd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .52 vdir_lsearch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53 what_is. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .542General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .57 alias . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..58 all_inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59 all_outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60 apropos . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .61 clear . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..62 date . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63 enable_transparent_latches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64 exec_embedded_script . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .65 exit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..67 get_attribute. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68 get_liberty_attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .71 get_read_files. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .72 help. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ..73 include . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .74 lcd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .75 license . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .76 license checkin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .77 license checkout. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .78 license list. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .79 lls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .80 lpopd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .81 lpushd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82 lpwd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83 man . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .84 more. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85quit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .87 rc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88 redirect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .92 reset_attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .94 resume. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .96 sdc_shell . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .97 set_attribute . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .98 shell . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .101 suppress_messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .102 suspend . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .103 unsuppress_messages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1043GUI Text. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .105 General GUI T ext Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .106 gui_hide . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107 gui_info. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107 gui_raise. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107 gui_reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .107 .gui_selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108 gui_show . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108 gui_status. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108 gui_update . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .108 HDL Viewer GUI Text Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .109 gui_hv_clear. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110 gui_hv_get_file. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110 gui_hv_load_file. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .110 gui_hv_set_indicators. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .111 Schematic Viewer GUI T ext Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .112 gui_sv_clear. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113 gui_sv_get_instance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113 gui_sv_grey . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .113 gui_sv_highlight . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .114 gui_sv_load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .115 Physical Viewer GUI T ext Commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .116gui_pv_airline_add. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .117 gui_pv_airline_delete. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118 gui_pv_airline_display . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .118 gui_pv_airline_raw_add. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119 gui_pv_clear. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .119 gui_pv_highlight. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .120 gui_pv_highlight_update . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122 gui_pv_label. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .122 gui_pv_redraw . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123 gui_pv_selection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123 gui_pv_snapshot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123 gui_pv_zoom_fit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125 gui_pv_zoom_in. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125 gui_pv_zoom_out. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .125 gui_pv_zoom_to. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1254Chipware Developer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .127 cwd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .128 cwd check. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .129 cwd create_check. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .133 cwd report_check. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .135 hdl_create. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137 hdl_create binding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .138 hdl_create component . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .140 hdl_create implementation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .142 hdl_create library . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .144 hdl_create operator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145 hdl_create package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146 hdl_create parameter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .148 hdl_create pin. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1505Input and Output. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153 decrypt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .155encrypt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .156 export_critical_endpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .159 read_config_file . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161 read_cpf. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162 read_def. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .163 read_dfm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .164 read_dft_abstract_model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .166 read_encounter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .167 read_hdl. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .168 read_io_speclist. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172 read_netlist. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .173 read_saif. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .175 read_sdc. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .176 read_spef. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .178 read_tcf . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .179 read_vcd. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .180 restore_design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .181 write_atpg. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .183 write_bsdl. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .184 write_compression_macro. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .185 write_config_template . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .186 write_def. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187 write_design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .188 write_dft_abstract_model. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .189 write_do_ccd . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .190 write_do_ccd compare_sdc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .191 write_do_ccd generate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .192 write_do_ccd propagate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .193 write_do_ccd validate. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .195 write_do_clp. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .196 write_do_lec. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .198 write_do_verify cdc. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .200 write_encounter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .202 write_et_atpg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .205 write_et_bsv. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .206 write_et_mbist . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .207write_et_rrfa. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .208 write_ets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .209 write_ett . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .210 write_forward_saif . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .211 write_hdl. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .212 write_io_speclist. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .215 write_saif . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .216 write_scandef. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .217 write_script. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .218 write_sdc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .221 write_sdf. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .224 write_set_load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .227 write_spef. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .228 write_tcf . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .229 write_template . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2306Constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .233 clock_uncertainty . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .234 create_mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .237 define_clock. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .240 define_cost_group . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .245 derive_environment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .246 external_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .248 generate_constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .252 multi_cycle . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .254 path_adjust. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .259 path_delay . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .263 path_disable. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .266 path_group. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .269 propagate_constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .272 specify_paths. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .274 validate_constraints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2807Elaboration and Synthesis. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .283 elaborate . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .284 remove_assigns_without_optimization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .286 remove_inserted_sync_enable_logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .288 retime. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .289 set_remove_assign_options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .291 synthesize . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2948Analysis and Report. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .301 all_connected. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .304 all des. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .305 all des inps. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .306 all des insts. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .307 all des outs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .308 all des seqs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .309 all lib. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .311 all lib bufs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .312 all lib ties. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .313 analyze_library_corners. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .314 check_design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .316 clock_ports. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .321 compare_sdc . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .322 fanin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .323 fanout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .326 report . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .328 report area . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332 report boundary_opto. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .334 report buskeepers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .335 report cdn_loop_breaker . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .336 report cell_delay_calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .338 report checks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .339 report clock_gating. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .342。

Memory Compiler使用介绍

Memory Compiler使用介绍在使用Memory Compiler时,请务必确保你的RAM从头到位的规格与设定都相同,否则会造成一些不可避免的错误。

首先在RTL代码阶段,要用到RAM就要用Artisan公司提供的Memory Compile产生的verilog代码,此时不需要着急产生其他后阶段的必要数据,因为RTL代码阶段只需要行为级模型即可。

当进入门级代码后,RAM compiler就要产生其他的相关数据了,同时要考虑RAM版图的位置与方向。

由于一个大的设计不会设计一次就会完成,所以有两个重点,第一个是每次使用RAM compiler时都一定要让它产生特性设置文档,避免忘记自己做过的设定。

第二件事是对应的文件名要定义好,否则RAM的方向不同但是又用到了相同的文件名,就会把原始数据覆盖掉。

下图为SRAM在流程中需要产生的文档RTL阶段在RTL阶段主要只是产生verilog行为级和设置文件。

因为在RTL阶段不需要考虑RAM的位置信息。

Memory Compiler提供4种选择,分别为ra1sh,ra2sh,rf1sh,rf2sh。

前面的ra与rf分别指的是SRAM与registerfile,其中rf在同样的情况下比ra占的面积小,但是rf的大小有限制,其限制大小位4096bits。

而后面1sh与2sh表示位单端口还是双端口,如果SRAM的容量比较大的话,相同设置下,1sh比2sh面积要小,速度也要快,功耗要低。

Memory Compiler运行界面如下图所示instance name:该设置是对RAM的命名,由于ram的特性有地址和位数,所以在命名的时候尽量包含这些信息。

number of words:该设置用来确定RAM的深度,即寻址空间大小。

number of bits:该设置用来确定RAM的宽度。

frequency:该设置用来确定RAM的工作频率,该设置确定后就可以基本确定RAM的功耗,估计的结果位平均电流,通过该数据来设定电源环的宽度。

chap1-3-compiler-example

编译器实现

任务:编译程序1+2+3到栈式计算机 阶段三:代码生成

小结

编译器构造和具体的编译器目标相关, 目前的结构:

思考题

任务:编译程序1+2+3到栈式计算机 阶段四:代码优化(常量折叠优化)

例如:1+2 ==> 3

编译器例子

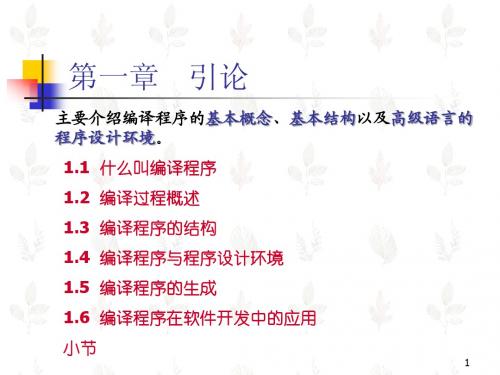

编译原理

华保健

bjhua@

简单的编译器实例

源语言:加法表 达式语tack

两种语法形式:

整型数字:n 加法 :e1+e2

一个操作数栈 两条指令:

压栈指令:push n 加法 指令:add

源语言Sum

两种语法形式:

整型数字:n 加法 :e1+e2

例子:

栈式计算机Stack

一个操作数栈 两条指令:

压栈指令:push n 加法指令:add

例子:

编译器的阶段

任务:编译程序1+2+3到栈式计算机 阶段一:词法语法分析

编译器实现

任务:编译程序1+2+3到栈式计算机 阶段二:语法树构建

算法导论第三版第二章第一节习题答案

算法导论第三版第⼆章第⼀节习题答案2.1-1:以图2-2为模型,说明INSERTION-SORT在数组A=<31,41,59,26,41,58>上的执⾏过程。

NewImage2.1-2:重写过程INSERTION-SORT,使之按⾮升序(⽽不是按⾮降序)排序。

注意,跟之前升序的写法只有⼀个地⽅不⼀样:NewImage2.1-3:考虑下⾯的查找问题:输⼊:⼀列数A=<a1,a2,…,an >和⼀个值v输出:下标i,使得v=A[i],或者当v不在A中出现时为NIL。

写出针对这个问题的现⾏查找的伪代码,它顺序地扫描整个序列以查找v。

利⽤循环不变式证明算法的正确性。

确保所给出的循环不变式满⾜三个必要的性质。

(2.1-3 Consider the searching problem:Input: A sequence of n numbers A D ha1; a2; : : : ;ani and a value _.Output: An index i such that _ D AOEi_ or the special value NIL if _ does not appear in A.Write pseudocode for linear search, which scans through the sequence, looking for _. Using a loop invariant, prove that your algorithm is correct. Make sure that your loop invariant fulfills the three necessary properties.)LINEAR-SEARCH(A,v)1 for i=1 to A.length2 if v = A[i]3 return i4 return NIL现⾏查找算法正确性的证明。

精品课件-C程序设计(第三版)(荣政)-第8章

第八章 指针

指针类型是对所有类型的指针的总称,指针的类型是指 针所指对象的数据类型。例如,pc是指向字符变量的指针, 简称字符指针。字符指针是基本类型的指针之一,除各种基 本类型之外,允许说明指向数组的指针、指向函数的指针、 指向结构体和共用体的指针以及指向各类指针的指针。在C 语言中只有指针被允许用来存放地址的值,其它类型的变量 只能存放该类型的数据。(很多书中用指针一词来指地址值, 或用指针变量来代表指针,阅读中应注意其具体含义。)

例8.2中指向整型的指针point在定义之后直接使用了,这 两条语句在编译时不会出现语法错误,但在使用时却几乎肯定 会出问题。表面上看,scanf()函数的参数要求给出的是地址, 而point的值就代表的是地址,但是point的值究竟是多少,也 就是说point究竟指向哪里,我们无法得知,在这种情况下就 对point指向的单元进行输入操作,将冲掉point指向的单元的 原有内容,假如这个单元是操作系统的所在处,就破坏了操作 系统,显然是一件危险的事。

为了理解指针的概念,程序员要有关于计算机如何在存储 器中存储信息的基本知识。以下简单地介绍个人计算机中存储 器存储的情况。

第八章 指针

个人计算机中CPU可以直接访问的,用来存储程序和数据 的记忆部件称为内存储器,内存储器由成千上万个顺序存储单 元组成,每个单元由一个惟一的地址标识。给定计算机的存储 器地址范围为从0到所安装的存储器数量的最大值。在计算机 上运行的每一个程序都要使用存储器。例如,操作系统要占用 一些计算机存储空间,每个应用程序也要占用计算机存储空间。 按照面向过程的结构化程序设计方法,程序代码和程序要处理 的数据是分开存储的,所以,一个程序在内存中要占两部分空 间:数据部分和指令代码部分。

第八章 指针

3.5节 语法分析的自动生成-编译原理及实践教程(第3版)-黄贤英-清华大学出版社

%%

• 第二节是文法记号的声明,一般以%start S 的形式说明文法的开始符号,用%token

辅助过程

IF、DO、…、ID、… 的形式说明记号。记 号被YACC赋予了不会与任何字符值冲突的

数字值

• 数据类型、全局变量

等遵循C语言的定义, %{

可包含预处理语句等, 需要用%{和%}括起来

#include<stdio.h> %}

的最受欢迎的语法分析生成器

• Jflex——是一个Java的词法/语法分析生成器

• Jison ——JavaScript解析器。Jison 将一个上下文无关语

法作为输入,输出对应的JavaScript代码,类似Yacc

• Grammatica——C#和Java的语法剖析器生成器。相对于

其它一些类似的工具如yacc和ANTLR有了更好的改进:创 建了更好的注释和易读的源代码/拥有错误自动恢复并能 够详述错误信息/支持语法、词法测试与调试.

– YACC在对源文件进行编译时,将对所有的单词和非终 结符进行编码,并用该编码建立分析表和语法分析器 。单词的编码原则是:字符单词使用其对应的ASCII码 ,有名单词则由分析器进行编码。用户在对有名单词 进行命名时,一定要注意不要和使用该单词名的C源程 序中已有的宏名相同,否则在编译该C模块时是会产生 宏定义冲突的。

由Johnson等人在美国Bell实验室研制开发

• yacc生成的编译器主要是用C语言写成的语法解析

器(Parser),需要与词法分析器Lex一起使用, 再把两部份产生出来的C程序一并编译。

• yacc本来只在Unix系统上才有,GNU 版叫做 Bison。

现在已普遍移植到Windows及其他平台。

精典材料Patran的PCL用户手册V20

MSC.Patran PCL HandbookIn a Nutshell (7)What is PCL? (7)What can PCL be used for? (8)How does PCL work? (9)All you really need to know is on this page! (10)Documentation (10)PCL for Everyone (11)Entering Equations (11)Entering Data (12)Session Files (13)Rebuilding Models (14)PCL for the More Adventurous (17)Parametric Modeling (17)Adding a Graphical User Interface, GUI (21)Exercise 1: Session Files (22)PCL Programming Basics (24)Overview (24)PCL Expressions (26)Expressions, Comments, Syntax Tips (26)Identifiers (28)Naming Conventions (28)Variable / Function Scope (29)Structure of a PCL Function (30)Function Basics (30)Simple PCL function Example (31)Exercise 2: Hello World! (33)Exercise 3: Effective PCL (34)PCL Operators (35)String comparisons (35)PCL Variables and Constants (36)Datatypes (36)Variable Scope (37)Directly Allocated Arrays (38)Virtual arrays (39)Virtual strings (41)Loop Control Statements (42)For Loop (42)While Loop (42)Repeat Loop (43)BREAK (44)CONTINUE (45)Exercise 4: Writing Files (46)Exercise 5: Reading Files (48)Conditional Control Statements (49)IF Statement (49)SWITCH Statement (50)Structure of a PCL Function (51)Compiling and Linking PCL Functions (54)Primary PCL Directives (55)Compiling PCL outside of MSC.Patran (59)Linking Compiled Libraries (60)Other PCL Directives (61)Start Up Files (62)Exercise 6: p3epilog.pcl (63)Debugging (64)Debugging Compile Errors (64)Debugging Runtime Errors (65)Accessing PCL Functions (67)From The Command Line (67)From Any MSC.Patran Form (68)PCL Functions with Field Variables (69)MSC.Patran Built-In Functions (70)Naming Conventions for Applications (71)Naming Conventions for Other Operations (72)Exercise 7: Group Elements By Shape (74)Graphical User Interface (75)The PCL Class Statement (76)PCL Widgets (77)Required Functions for Building/Displaying a Form (78)The init() Function (78)The display() Function (79)Widget Callbacks (82)What Are They? (82)What Are They Used For? (83)Callback Arguments (Widget Function Data) (83)Widget Placement (85)Widget Variables (87)Modifying Widgets (88)Getting Data from Widgets (89)Putting it all Together (Example) (90)Exercise 8: Simple Form (92)The C-Preprocessor and Include Files (93)Make Files (94)Exercise 9: Callbacks (96)Handling Errors and Messaging (98)Errors from Built-In Functions (98)Custom Error Messages (99)Using User Messages Database (99)Without a Messages Database (100)Taking Advantage of the UNDO Feature (102)Select Mechanism (103)Select Mechanism GUI Mechanics (103)Select Databoxes, Select Frames, and Select Menus (103)GUI PCL Example (105)List Processor (106)List Processor Mechanics (106)All You Really Need to Know (107)Exercise 10: Form to Group Elms By Shape (110)Executing Programs Outside of MSC.Patran (112)Spawning Remote Processes (112)Locking a database (114)Using C and Fortran executables to access a MSC.Patran database directly. (115)External Access of an MSC.Patran Database (116)Special Widgets (118)File Widget (118)Spreadsheet Widget (121)Exercise 11: File Widget (122)Adding Help/Description to your PCL (123)Percent Complete (124)Functions (124)Example (124)Event Manager (125)General (125)Functions (126)Example (126)Primitive Graphics (127)Graphic Objects (127)Graphic Segments (128)Example (129)Another Example (130)Exercise 12: Primitive Graphics (131)MSC.Patran Customization (132)Adding Utility Programs to the Main Menu (132)Example (133)Example: p3_user_menu.my_menu.def (134)Customizing the MSC.Patran Toolbar (135)Exercise 13: Pulldown Menu (138)Exercise 14: Toolbar (139)Some Final Thoughts (141)Appendix A (144)Built-in Function Examples (144)Documentation for a typical MSC.Patran built-in function. (145)To get all the nodes and their global coordinates (146)To get the topology of every element (147)To get the shape of every element (148)To get all the element connectivity for all elements (149)To get the elements associated to a particular element property set (150)To get an element property value (shell thickness) for a specific element (151)To get a material property value (153)To get a list of all groups (154)To get the nodes and elements associated to the current group (154)To get result values for specified elements (155)Appendix B (164)Strings & String Functions (164)Declaration (165)Initialization (165)String Comparisons (165)Functions (166)Appendix C (174)Noteworthy Functions (174)sys_mov e_raw(...) (175)mth_array_search(...). (176)mth_sort(...) . (177)mth_sort_row(...).. (178)mth_sort_column(...) . (178)fem_geom_edge_length(...) .. (179)fem_geom_face_area(...). (179)fem_geom_elem_volume(...). (179)fem_geom_elem_location(...) .. (180)Appendix D (181)Form Spacing Parameters (appforms.p) (181)* SPACING (182)Appendix E (205)MSC.Patran Architecture (205)Appendix F (207)Shareware Compiling Functions (207)Appendix G (210)Parametric Patran (210)Appendix H (216)Additional List Processor Notes (216)List Processor Mechanics (217)List Processor Functions (217)List Processor Sublist Functions (219)List Processor Attribute Functions (220)Miscellaneous List Processor Functions (220)List Processor Examples (222)Easy to Use List Processor Functions (226)Appendix I (227)Key Mapping (227)Appendix J (230)Widget Classification (230)Appendix K (233)User Defined AOM (233)In a NutshellWhat is PCL?❑PCL stands for Patran Command Language❑Comprehensive, fully functional computer programming language❑Specifically and uniquely suited for MCAE applications ❑Delivered as a part of MSC.Patran❑Versatile and easy to useWhat can PCL be used for?❑Integrate application or site-specific programs with the MSC.Patran user interface and database❑Generate parametric/variational models for design/optimization ❑Integrate commercial and/or in-house analysis codes with MSC.Patran❑Display custom graphics❑Access the MSC.Patran database❑Create new and/or enhanced MSC.Patran functionality❑Database management for analysis files❑Eliminate tedious, repetitive proceduresHow does PCL work?❑All MSC.Patran commands are first interpreted by the PCL command interpreter❑PCL expressions are interpreted by a C program❑PCL functions can be compiled into libraries (more efficient binary representation) and “linked” with a MSC.Patran session❑“Built-in” PCL functions are written in C or FORTRAN❑MSC.Patran forms and menus can be created via PCL calls to Xlib, the X-window function library❑FORTRAN and C functions can be “linked” with MSC.Patran through PCLAll you really need to know is on this page! Documentation❑PCL and Customization - General programming guide for PCL.How to build forms, compile, manage libraries, access thedatabase, read/write files, etc.❑PCL Reference – Description of functions written to the session file.❑Develop: The MSC.Patran Toolkit – Documentation of additional functions for database access, etc.PCL for Everyone Entering EquationsUse of PCL when creating spatial fields:‘X + ‘X**2 –sinr(‘X)The PCL interpreter interprets anythingimmediately following a ‘ symbo l as afield variable as opposed to a PCLfunction, such as, sinr().Entering DataUse of PCL when entering geometric coordinates: [ `5./16.` 0 0 ]The PCL interpreter “evaluates” expressions enclosed in back tics, “`”.Other examples:[ `radius/length` 0 0 ]< `cosr(theta)` 1 1 >[ `MyFunction(radius)` 0 1 ]Session FilesSession and journal files are comprised entirely of PCL commands. Model changes (dimensions, mesh density, etc.) can be made quickly by editing and then replaying the session or journal files.$# Session file patran.ses.01 started recording at 16-Aug-01 14:33:54$# Recorded by: MSC.Patran 2001STRING asm_create_patch_xy_created_ids[VIRTUAL]asm_const_patch_xyz( "1", "<10 10 0>", "[0 0 0]", "Coord 0", @asm_create_patch_xy_created_ids )$# 1 Patch created: Patch 1STRING sgm_edit_surface_add_h_edit_ids[VIRTUAL]sgm_edit_surface_add_hole( 1, 1., TRUE, "", "[5 5 0]", "", "Surface 1", @sgm_edit_surface_add_h_edit_ids )$# 1 Surface Edited: Surface 1$# Session file patran.ses.01 stopped recording at 16-Aug-01 14:34:52Rebuilding ModelsThe following session file creates a trimmed surface, 10” x10”with a 1” diameter hole at the center. Note that the parameter that controls the diameter of the hole is indicated below.$# Session file patran.ses.01 started recording at 16-Aug-01 14:33:54$# Recorded by: MSC.Patran 2001STRING asm_create_patch_xy_created_ids[VIRTUAL]asm_const_patch_xyz( "1", "<10 10 0>", "[0 0 0]", "Coord 0", @asm_create_patch_xy_created_ids )$# 1 Patch created: Patch 1STRING sgm_edit_surface_add_h_edit_ids[VIRTUAL]sgm_edit_surface_add_hole( 1, 1., TRUE, "", "[5 5 0]", "", "Surface 1", @ sgm_edit_surface_add_h_edit_ids )$# 1 Surface Edited: Surface 1$# Session file patran.ses.01 stopped recording at 16-Aug-01 14:34:52In the session file below, the previous session file is edited to change the hole diameter from 1” to 4”$# Session file patran.ses.01 started recording at 16-Aug-01 14:33:54$# Recorded by: MSC.Patran 2001STRING asm_create_patch_xy_created_ids[VIRTUAL]asm_const_patch_xyz( "1", "<10 10 0>", "[0 0 0]", "Coord 0", @asm_create_patch_xy_created_ids )$# 1 Patch created: Patch 1STRING sgm_edit_surface_add_h_edit_ids[VIRTUAL]sgm_edit_surface_add_hole( 1, 4., TRUE, "", "[5 5 0]", "", "Surface 1", @ sgm_edit_surface_add_h_edit_ids )$# 1 Surface Edited: Surface 1$# Session file patran.ses.01 stopped recording at 16-Aug-01 14:34:52Session files can be executed or “played” by selecting File/Session/Play … from the top menu.PCL for the More Adventurous Parametric Modeling❑Session files can be parameterized by defining and using variables during the MSC.Patran session❑First, variables are declared and initialized via the MSC.Patran command lineSecond, the variables are used as input into the appropriate MSC.Patran forms (note the use of ` `, back tics)Upon application, the PCL interpreter evaluates `radius` (i.e., sets it equal to 1.0 in this example) and creates the curve. Note that the variable is passed to the session file in its unevaluatedBy using variables as parameters during MSC.Patran input, it is very easy to edit and change dimensions, mesh parameters, etc. in the session file.PCL for the more Adventurous Adding a Graphical User Interface, GUIThe next step might be to create a user interface to run the plate session file!Exercise 1: Session FilesUse MSC.Patran to create a parameterized session file that createsa rectangular surface with an arbitrarily located hole.1) Create variables for the dimensions shown below.2) Steps:a) Create variables using MSC.Patran’s command lineb) Create/Surface/XYZ (use variables length and width)c) Edit/Surface/Add Hole (use x_center, y_center, and diameter) Extra credit: Include error checking, i.e., it doesn’t make sensefor the hole to be outside the surface boundary.IF (x_center + diameter/2.0 > length) THEN RETURNExtra credit: Include meshing, boundary conditions, elementproperties, etc.Extra credit: Use ui_read_real(prompt) to enter the variablevalues interactivelyExtra credit: Turn your session file into a PCL FUNCTION.Exercise 1 Below is an image showing an MSC.Patran form allowing the interactive creation of the model for this exercise.NB – See Appendix G for notes about Parametric Patran.1) Variables and macros are defined interactively via a GUI2) Variables and macros are persistent3) Plus, more. See Appendix G for the detailsPCL Programming Basics Overview❑PCL is a full-featured programming language.❑Operators for arithmetic, relational, and string expressions.Examples include:❑Variables with type, scope, and dimension attributes INTEGER i, j, status, NodeIds(1000)LOGICAL flagREAL xyz(1000, 3), pressure(100), timeGLOBAL STRING my_group[32], all_groups[32](100)❑Dynamically allocated virtual strings and arraysINTEGER node_ids(VIRTUAL)STRING groups[32](VIRTUAL), MyString[VIRTUAL]❑Intrinsic functions for math, string manipulation, etc.sinr(angle)cosd(angle)mth_abs(MyVal)mth_sort(MyArray, CompactDuplicates, NumLeft)mth_array_search(MyArray, Look4, Sorted)str_length(MyString)str_substr(MyString, Position, SubStringLength)str_index(StringToSearchIn, StringToSearchFor)str_token(MyString, Delimiter, TokenNumber, [Compress])PCL Programming Basics ❑Loop control features, such as, WHILE, FOR, REPEAT, and LIST❑Conditional control structure, such as, IF-THEN-ELSE and SWITCH-CASE❑Subroutine (procedure) and function (command) calls❑Class grouping of related functions❑Read/write access to external ASCII and/or binary filestext_open(FileName, Options, 0, 0, FileId)text_read_string(FileId, InString, InStringLength)text_write_string(FileId, OutString)text_read(FileId, Format, MyIntegers, MyReals, MyChar)text_write(FileId, Format, MyIntegers, MyReals, MyChar)text_close(FileId, Options)file_exists(FileSpec, Options)file_delete(FileSpec)❑Access to MSC.Patran “built-in” functions that allow for direct access to the MSC.Patran database, geometry creation,drawing graphic primitives,db_count_nodes(NumNodes)db_get_node_ids(NumNodes, NodeIds)asm_const_grid_xyz(output_ids, coordinates_list, coord_frame, @created_ids)PCL Expressions Expressions, Comments, Syntax Tips❑Sample PCL expressions include:theta = 360.0 – MTH_ASIND(MyAngle)IF (radius >= 20.0) THEN radius = 20.0length = str_length(MyString)build_gear_geometry(30., 56., 3)❑PCL comments begin with a “/*” and end with a “*/”/*This is a comment.Look Ma, I’m making comments in PCL!Has anyone seen or heard from Elvis lately?*/a = 2 /* set mysterious factor equal to 2 */❑Alternatively, single line comments may begin with “$”$ Don’t you just hate to comment your programs?❑More than one PCL expression can co-exist on a line using a semi-colon, “;”alpha = 30.0; beta = 120.0❑PCL expressions can be continued on subsequent lines by using the “@” symbolui_wid_set(main_form, @“HEIGHT”, @NewHeight)ui_wid_set( /* widget_id */ main_form, @/* parameter */ “HEIGHT”, @/* value */ NewHeight)PCL Expressions ❑Don’t break expressions in the middle of a keyword, constant, or identifier❑Multiple blanks are the same as a single blank space❑Lines beginning with “!” (bang operator) are echoed to the xterm (UNIX) or command window (NT), but are not executedIn MSC.Patran type: !`i` nodes createdIn the xterm you see: %27 nodes created❑PCL expressions beginning with “>” are echoed to the session file❑PCL expressions can be typed directly into MSC.Patran at the command line❑PCL expressions may also be created with an editor in a text file and directed into MSC.Patran as a session file or by using the PCL directive !!INPUTIdentifiersNaming Conventions❑Function names and/or variable names are called identifiers ❑Can be up to 32 characters long❑Must begin with a non-digit❑Case insensitive (as is all of PCL)❑Cannot be a reserved keyword, i.e., FOR, IF, etc.❑Valid identifierscurrent_groupCurrentGroupMyString❑Invalid identifiersa_very_very_very_very_very_very_very_very_long_name 95abclistIdentifiers Variable / Function Scope❑Global variable names and functions share the same name space❑When two function names or two variable names conflict, the most recent addition supercedes the previous❑When function names and variable names conflict, the variable name takes precedence❑When compiling functions, PCL will indicate if a function name is superceded by writing “Cleared memory function” to thehistory window❑Hint: Use a unique prefix to keep function definitions separate,i.e au_do_this_and_that.pclStructure of a PCL Function Function Basics❑PCL functions begin with a FUNCTION statement and end with an END FUNCTION statement.❑The FUNCTION statement may contain an argument list to be passed in or out of the function.❑An optional RETURN statement can be used to return a calculated value from the function to the calling statement.❑Processing of the function terminates at either the END FUNCTION statement or a RETURN statement.❑There may be multiple RETURN statements within a single function.Simple PCL function Exampleanother_simple_function(29)$#My favorite number is 29$#My least favorite number is 13Sample output. The ui_write functions writetext to the history window, the session file(patran.ses.##), and the journal file(model.db.jou)Exercise 2: Hello World!Write and execute a PCL function that accepts a single real number argument and echoesHello World, my favorite number is ….to the MSC.Patran session file and history window.Your function will use either the ui_write(…),ui_writef(…), or ui_writec(…) functions.If you use the ui_writef(…) and ui_writec(…) functions, refer to the documentation for the correct format specifiers.Extra credit: How would this function change if you wanted to echo your favorite 10 numbers to the session file? Extra credit: How would this function change if you wanted to echo your favorite color to the session file?Exercise 3: Effective PCLWrite an essay on how the effective use of PCL could:a) Help create a lasting world peaceb) Eliminate world hungerc) Conquer the common coldd) Stop global warmingExtra credit: How could PCL be used to find Elvis?PCL OperatorsExamplesDist = mth_sqrt((x2-x1)**2 + (y2-y1)**2 + (z2-z1)**2) MyString3 = MyString2//”hijk”IF (a == b) THEN c = dIF (a == b && a == c) THEN ui_write(“Equilibrium”)x += 1 (this is equivalent to x = x +1)String comparisons❑The string comparison operators are special in that they ignore trailing blanks and uppercase and lowercase. Therefore, all of the following expressions are TRUE“ABC” == “ABC ““ABC” == “abc”❑Leading blanks are compared, i.e., “TEST” != “ TEST”❑To perform case sensitive comparisons use the str_equal() function, i.e.,IF (str_equal(GroupName1, GroupName2)) THEN RETURN 0PCL Variables and Constants Datatypes❑LOGICAL Boolean value: TRUE or FALSELOGICAL done, created31-1)❑INTEGER Value between +/- (2INTEGER i, num_nodes, node_id❑REAL Single precision floating value between 1.0E-30 and1.0E+30 (positive or negative)REAL x, y, z, force, pressure❑STRING Character string surrounded by double quotes, “Have you seen Elvis?”. Size or string length is defined with brackets, [ ]STRING FileName[80], GroupName[32]❑WIDGET Value is assigned by calls toUI_WIDGET_NAME_CREATE(…), used to create andmanipulate forms, etc.WIDGET main_form, MyButton, group_lboxVariable Scope❑GLOBAL Available to all functions during the MSC.Patransession❑LOCAL Default, only visible within the defining function ❑STATIC Same as LOCAL, but retains its value betweencalls❑CLASSWIDE Available to all functions in the CLASS andretains its value during the MSC.Patran sessionDirectly Allocated Arrays❑Directly allocated arrays can have any number of subscripts (dimensions), defined within parentheses ()❑Assigned upper and lower bounds, ArrayName(Lower:Upper)INTEGER MyArray(2:10)❑ Default lower bound is 1 (not 0) ❑ Available for all datatypes❑Row major (unlike Fortran which is column major)INTEGER MyArray(2, 3) = 1, 2, 3, 4, 5, 6❑Array dimensions are inherited from the argument list, i.e., PCL passes by reference❑Declaration ExamplesREAL displacements(6, 200) STRING group_names[32](20) INTEGER ids(0:2, 0:4, 0:10) LOGICAL exists(12)Virtual arrays❑Any variable can be defined as a VIRTUAL array instead of a directly allocated array. Virtual arrays do not have storagelocations assigned to them at program initialization. The size and amount of storage is allocated as requested and can bereused for other virtual arrays.❑To declare a virtual array, use the keyword VIRTUAL in place of the subscripts for the declaration, i.e.,REAL MyVals(VIRTUAL)INTEGER NodeIds(VIRTUAL)❑Storage is allocated using the function, sys_allocate_array(), or sys_allocate_array(MyVals, 1, 300)sys_allocate_array(MyVals, 1, 300, 1, 3)sys_allocate_array(MyVals, 1, 300, 1, 3, 0, 5)etc.❑Storage may be reallocated using the function,sys_reallocate_array(),sys_reallocate_array(MyVals, 1, 300, 1, 3)❑Storage may be freed using the function, sys_free_array(), sys_free_array(MyVals)Virtual array examplePCL Variables and Constants Virtual strings❑Any string variable can be defined as a VIRTUAL length string instead of a fixed length string. Virtual length strings do nothave storage locations assigned to them at programinitialization. The string length is allocated as requested and can be reused.❑To declare a virtual length string, use the keyword in place of the subscripts for the declaration, i.e.,STRING picklist[VIRTUAL]❑The string length is allocated using the sys_allocate_string() functionsys_allocate_string(picklist, 1000)❑The string length may be modified using thesys_reallocate_string() functionsys_reallocate_string(picklist, 2000)❑The string storage may be freed using the sys_free_string() functionsys_free_string(picklist)❑ A virtual length string can also be a virtual array, i.e., STRING picklists[VIRTUAL](VIRTUAL)Loop Control StatementsFor Loop❑SyntaxFOR (var=numeric_expr TO numeric_exprnumeric_expr label statements … END FOR❑ExampleAvgTemp = 0.0FOR (i = 1 TO NumNodes) AvgTemp += NodalTemp(i) END FORAvgTemp = AvgTemp/NumNodesWhile Loop❑SyntaxWHILE (logical_expression ) [label ] statements … END WHILE❑ExampleAvgTemp = 0.0 i = 1WHILE (i <= NumNodes)AvgTemp += NodalTemp(i) i += 1 END WHILEAvgTemp = AvgTemp/NumNodesRepeat LoopThis is similar to a WHILE Loop except that it will always be executed at least once. Only use REPEAT loops if you want to ALWAYS execute the loop at least once, otherwise us a WHILE loop.❑SyntaxREPEAT [label]statements …UNTIL (logical_expression)❑ExampleAvgTemp = 0.0i = 1REPEATAvgTemp += NodalTemp(i)i += 1UNTIL (i > NumNodes)AvgTemp = AvgTemp/NumNodesBREAKThe BREAK statement is used to exit a loop prior to its normal termination. It can be used in any of the loop statements.BREAK [❑END WHILE…❑Example 2 (nested loops, using labels)WHILE (i <= NumNodes) MainLoopWHILE (j <= 100) AnotherLoopWHILE (k <= 200) InnerLoopIF (status != 0) THEN BREAK MainLoopIF (status != 0) THEN BREAK AnotherLoopIF (status != 0) THEN BREAKIF (status != 0) THEN BREAK InnerLoopEND WHILEEND WHILEEND WHILECONTINUEThe CONTINUE statement is used to skip to the end of the loop ❑SyntaxCONTINUE [label]❑Example 1 (reading a text file)INTEGER file_id, lengthSTRING read_str[80]/* read grid information */WHILE (text_read_string(file_id, read_str, length) == 0)END WHILE❑Example 2 (nested loop, using labels)WHILE (i <= NumNodes) MainLoopREPEAT InnerLoopCONTINUE MainLoopBREAK InnerLoopCONTINUECONTINUE InnerLoopUNTIL (j > 1000)END WHILEstatements …Exercise 4: Writing FilesCreate a PCL function to write nodal data to a user-defined file. 1) The function should have a single argument, the filename to becreated, i.e., FUNCTION write_nodes_to_file(FileName)2) The data should be written to the file as a table, i.e.,Node Id x-coordinate y-coordinate z-coordinate3) Use virtual arrays4) Use the following built-in functions:db_count_nodes(NumNodes)db_get_node_ids(NumNodes, NodeIds)db_get_nodes(NumNodes, NodeIds, rcids, acids, NodeXYZ)text_open(FileName, Options, idum, idum, FileId)text_close(FileId, Options)text_write(FileId, Format, Ints, Reals, Chars)text_write_string(FileId, OutString)5) Use the documentation if you have questions about thearguments to the built-in functions.6) Think about your choice for the format argument in thetext_write(…) function. Will your file be comma or spacedelimited? Will it be fixed or free format?7) Sample code outline:a) Declare variablesb) Count nodes in the databasec) Allocate arraysd) Get node Idse) Get node coordinatesf) Open fileg) Write data to the file with a looph) Close filei) Be sure to include a message that the file output is completeWriting Files Extra credit: Include a header line at the top of the file thatincludes the filename and the total number of nodeswritten to the file.Exercise 5: Reading FilesWrite a function to read the file created in Exercise 4.1) The function should accept a single argument, i.e., the filenameto be read.FUNCTION ReadFile(FileName)2) Use the data in the file to create nodes with the following built-in function from the PCL Reference Manual:fem_create_nodes_1(RefCIDList, AnalysisCIDList, GeomFlag, @NodeIDList, XYZList, NodesCreatedList)3) Use the following built-in functions:text_open(FileName, Options, idum, idum, FileId)text_close(FileId, Options)text_read(FileId, Format, Ints, Reals, Chars)4) Sample code outline:a) Declare variablesb) Open the filec) Read the file within a loopd) Create new nodes as the file is read within the loope) Close the fileExtra credit: What if a node ID to be created already exists in the database?Extra credit: What if the file to be read doesn’t exist? Whatfunction can be used to determine if a file exists? Extra credit: Searching the documentation reveals anotherfunction that can be used to create nodes, i.e.,db_create_nodes(num_nodes, rcids, acids, xyz, group_id,node_ids, node_exists). Why might you use thisfunction versus fem_create_nodes_1(…)?Conditional Control Statements IF Statement❑SyntaxIF (logical_expression) THENstatements …ELSE IF (logical_expression) THENstatements …ELSEstatements …END IF❑ExampleIF (MyKeyWord == “CBAR” || MyKeyWord == “CBEAM”) THEN statements …ELSE IF (MyKeyWord == “CTRIA” || MyKeyWord == “CQUAD”) THEN statements …ELSE IF (MyKeyWord == “GRID”) THENstatements …ELSEstatements …END IF。

Lauterbach黑芯调试器TRACE32在线帮助说明书