CRC8_verilog

CRC编码译码Verilog实现程序代码

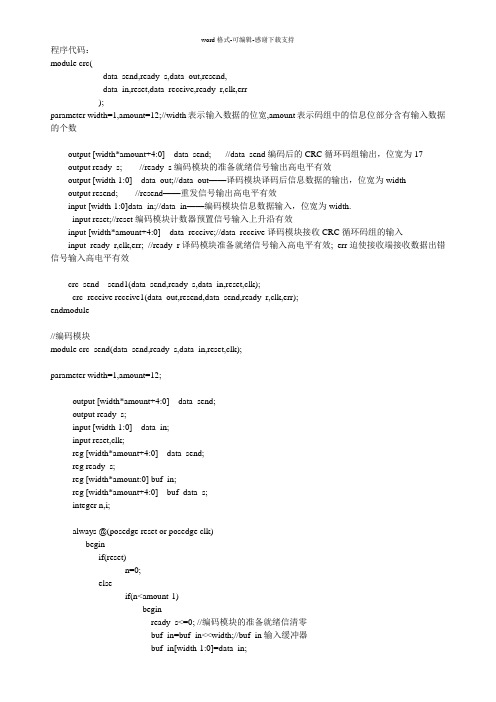

程序代码:module crc(data_send,ready_s,data_out,resend,data_in,reset,data_receive,ready_r,clk,err);parameter width=1,amount=12;//width表示输入数据的位宽,amount表示码组中的信息位部分含有输入数据的个数output [width*amount+4:0] data_send; //data_send编码后的CRC循环码组输出,位宽为17 output ready_s; //ready_s编码模块的准备就绪信号输出高电平有效output [width-1:0] data_out;//data_out——译码模块译码后信息数据的输出,位宽为widthoutput resend; //resend——重发信号输出高电平有效input [width-1:0]data_in;//data_in——编码模块信息数据输入,位宽为width.input reset;//reset编码模块计数器预置信号输入上升沿有效input [width*amount+4:0] data_receive;//data_receive译码模块接收CRC循环码组的输入input ready_r,clk,err; //ready_r译码模块准备就绪信号输入高电平有效; err迫使接收端接收数据出错信号输入高电平有效crc_send send1(data_send,ready_s,data_in,reset,clk);crc_receive receive1(data_out,resend,data_send,ready_r,clk,err);endmodule//编码模块module crc_send(data_send,ready_s,data_in,reset,clk);parameter width=1,amount=12;output [width*amount+4:0] data_send;output ready_s;input [width-1:0] data_in;input reset,clk;reg [width*amount+4:0] data_send;reg ready_s;reg [width*amount:0] buf_in;reg [width*amount+4:0] buf_data_s;integer n,i;always @(posedge reset or posedge clk)beginif(reset)n=0;elseif(n<amount-1)beginready_s<=0; //编码模块的准备就绪信清零buf_in=buf_in<<width;//buf_in输入缓冲器buf_in[width-1:0]=data_in;n=n+1;endelsebeginbuf_in=buf_in<<width;buf_in[width-1:0]=data_in;buf_data_s[width*amount+4:5]=buf_in;if(buf_in[11])buf_in[11:6]=buf_in[11:6]^6'b110101;if(buf_in[10])buf_in[10:5]=buf_in[10:5]^6'b110101;if(buf_in[9])buf_in[9:4]=buf_in[9:4]^6'b110101;if(buf_in[8])buf_in[8:3]=buf_in[8:3]^6'b110101;if(buf_in[7])buf_in[7:2]=buf_in[7:2]^6'b110101;if(buf_in[6])buf_in[6:1]=buf_in[6:1]^6'b110101;if(buf_in[5])buf_in[5:0]=buf_in[5:0]^6'b110101;buf_data_s[4:0]=buf_in[4:0];data_send[width*amount+4:0]=buf_data_s[width*amount+4:0];n=0;ready_s<=1;endendendmodule//解码模块module crc_receive(data_out,resend,data_receive,ready_r,clk,err);parameter width=1,amount=12;output [width-1:0] data_out;output resend;input [width*amount+4:0] data_receive;input ready_r,clk,err;reg [width-1:0] data_out;reg resend;reg [width*amount+4:0] buf_receive;reg [width*amount:0] buf_data_r;reg right;integer m;always @(posedge clk)beginif(ready_r)beginbuf_receive=data_receive;if(err)buf_receive[16]=~buf_receive[16];buf_data_r[width*amount:0]=buf_receive[width*amount+4:5];if(buf_data_r[11])buf_data_r[11:6]=buf_data_r[11:6]^6'b110101;if(buf_data_r[10])buf_data_r[10:5]=buf_data_r[10:5]^6'b110101;if(buf_data_r[9])buf_data_r[9:4]=buf_data_r[9:4]^6'b110101;if(buf_data_r[8])buf_data_r[8:3]=buf_data_r[8:3]^6'b110101;if(buf_data_r[7])buf_data_r[7:2]=buf_data_r[7:2]^6'b110101;if(buf_data_r[6])buf_data_r[6:1]=buf_data_r[6:1]^6'b110101;if(buf_data_r[5])buf_data_r[5:0]=buf_data_r[5:0]^6'b110101;if(!(buf_data_r[4:0]^buf_receive[4:0]))beginright=1;resend=0;data_out=buf_receive[16];buf_receive=buf_receive<<width;m=1;endelsebeginright=0;resend=1;data_out='bz;endendelse if(right)beginif(m<amount)begindata_out=buf_receive[width*amount+4:width*amount+5-width];buf_receive=buf_receive<<width;m=m+1;endendendEndmodule测试代码:module crc_test;reg data_in,reset,clk,err;reg [15:0] shift;wire [16:0] data_send;wire ready;always #50 clk=~clk;initialbeginclk=0;err=0;shift=16'h8000;reset=0;#10 reset=1;#20 reset=0;#9600 err=1;#100 err=0;#500000 $finish;endalways @(posedge clk)begindata_in=shift[0];shift=shift>>1;shift[15]=shift[14]^shift[11];if(!shift[15:12]) shift[15:12]=4'b1000;endcrc_send send(data_send,ready,data_in,reset,clk);crc_receive receive(data_out,resend,data_send,ready,clk,err); endmodule。

介绍两个CRC源码生成工具,可生成Verilog和VHDL

32

lfsr_q <= {5{1'b1}};

33

end

ቤተ መጻሕፍቲ ባይዱ

34

else begin

35

lfsr_q <= crc_en ? lfsr_c : lfsr_q;

36

end

37

end // always

38 endmodule // crc

39

10

input

clk);

11

12

reg [4:0] lfsr_q,

13

lfsr_c;

14

assign crc_out = lfsr_q;

15

always @(*) begin

16

lfsr_c[0] = lfsr_q[0] ^ lfsr_q[2] ^ lfsr_q[3] ^ data_in[0] ^ dat

三、代码分析比较

1、 网 页 在 线 生 成 代 码

1 module CRC5_D8; 2 3 // polynomial: (0 2 5) 4 // data width: 8 5 // convention: the first serial bit is D[7] 6 function [4:0] nextCRC5_D8; 7 8 input [7:0] Data; 9 input [4:0] crc; 10 reg [7:0] d; 11 reg [4:0] c; 12 reg [4:0] newcrc; 13 begin 14 d = Data; 15 c = crc; 16 17 newcrc[0] = d[6] ^ d[5] ^ d[3] ^ d[0] ^ c[0] ^ c[2] ^ c[3]; 18 newcrc[1] = d[7] ^ d[6] ^ d[4] ^ d[1] ^ c[1] ^ c[3] ^ c[4]; 19 newcrc[2] = d[7] ^ d[6] ^ d[3] ^ d[2] ^ d[0] ^ c[0] ^ c[3] ^ c[4]; 20 newcrc[3] = d[7] ^ d[4] ^ d[3] ^ d[1] ^ c[0] ^ c[1] ^ c[4]; 21 newcrc[4] = d[5] ^ d[4] ^ d[2] ^ c[1] ^ c[2]; 22 nextCRC5_D8 = newcrc; 23 end 24 endfunction 25 endmodule 26

crc8 python 代码

crc8 python 代码CRC8是一种常用的循环冗余校验算法,用于检测数据传输中的错误。

在本文中,我们将介绍如何使用Python编写CRC8算法的代码。

CRC(Cyclic Redundancy Check)是一种通过对数据进行多项式除法运算来生成校验码的方法。

CRC8是其中一种常用的校验码,它采用8位二进制数表示校验结果。

CRC8算法通过对输入数据进行位运算和异或操作,生成一个8位的校验码。

我们需要定义一个CRC8多项式,它是一个8位二进制数,用于进行校验码的生成和校验。

常用的CRC8多项式有很多种,例如0x07、0x9B等。

在本文中,我们以0x07作为示例。

接下来,我们可以编写Python代码来实现CRC8算法。

我们首先定义一个crc8函数,该函数接受一个字节数组作为输入,返回一个8位的校验码。

```pythondef crc8(data):crc = 0poly = 0x07for byte in data:crc ^= bytefor _ in range(8):if crc & 0x80:crc = (crc << 1) ^ polyelse:crc <<= 1return crc & 0xFF```在上述代码中,我们首先初始化crc和poly变量,分别表示校验码和CRC8多项式。

然后,我们通过对输入数据进行位运算和异或操作来生成校验码。

最后,我们返回校验码的低8位。

现在,我们可以使用这个crc8函数来计算校验码。

我们可以定义一个字节数组作为输入,并调用crc8函数计算校验码。

```pythondata = [0x01, 0x02, 0x03, 0x04]checksum = crc8(data)print(f"CRC8校验码为:{checksum}")```在上述代码中,我们定义了一个包含四个字节的数据,并将其传递给crc8函数来计算校验码。

八位移位寄存器verilog代码

一、引言在数字电路设计中,移位寄存器是十分常见的电路元件。

它能够对输入的数据按照特定的规则进行位移操作,常见的有左移、右移、循环移位等。

在Verilog语言中,我们可以通过编写代码来实现八位移位寄存器。

本文将从深度和广度方面展开对八位移位寄存器的Verilog代码进行全面评估,并撰写有价值的文章。

二、基本概念在开始编写八位移位寄存器的Verilog代码之前,我们首先要明确其基本概念。

移位寄存器是一种能够在时钟信号的控制下,对输入数据进行位移操作的寄存器。

而八位移位寄存器则是指这个寄存器能够对八位二进制数据进行位移。

这意味着在Verilog代码中,我们需要定义一个八位的寄存器,并编写移位操作的逻辑。

我们还需要考虑如何控制时钟信号和输入数据,以使得移位操作能够按照我们的期望进行。

三、Verilog代码实现```verilogmodule shift_register(input wire clk, // 时钟信号input wire rst, // 复位信号input wire [7:0] data_in, // 输入数据output reg [7:0] data_out // 输出数据);// 初始化寄存器always @(posedge clk or posedge rst)beginif (rst)data_out <= 8'b00000000; // 复位时,将寄存器清零elsedata_out <= data_in; // 否则将输入数据写入寄存器end// 左移操作always @(*)begindata_out = {data_out[6:0], 1'b0}; // 将寄存器中的数据向左移动一位end// 右移操作always @(*)begindata_out = {1'b0, data_out[7:1]}; // 将寄存器中的数据向右移动一位endendmodule```以上是一个简单的八位移位寄存器的Verilog代码实现。

循环冗余校验(CRC)之verilog实现

循环冗余校验(CRC)之verilog实现本来是不想写的,是因为⾃⼰还没有彻底搞懂唯⼀的⼀个环节:软件实现和理论怎么对应。

对于我这种⿊⽩是⾮必须分明的⼈⽽⾔,这是⼀种折磨。

⽽这周类似的,悬⽽未决的事情远不⽌这⼀件。

这些导致这周过得很不爽快,但是我很清楚的明⽩我必须去⾯对,去接受,去改变,就像昨晚的欧冠,这么虐⼼的过程,说不定在最后迎来意想不到的⼤胜利。

循环校验,也称为CRC检验,这是⼀个很常见的,很成熟的。

该算法的理解很简单,随便⽤百度百科⼀搜,然后花半个⼩时估计就能完全理解了。

这篇博⽂描述:怎么实现硬件并⾏的CRC计算。

主要的参数为:1.⽣成多项式,在不同的协议中有不同的⽣成多项式,⼀般这些多项式都是确定的。

2.模2除法如果已经了解CRC算法,就明⽩它的原理就是将数据和多项式进⾏模2除,最后得到的余数就是最后的CRC。

这⾥需要记住的就是:模2除就是进⾏异或。

但是,如果上⾯的你都了解后,你会发现这些对于解决CRC算法完全没有作⽤,这就是坑爹的百科。

⽹络上⼤部分的CRC都是软件实现,其实在解压软件中就有CRC,但是此时⼜会出现⼀个问题,你会发现下载的软件对于同⼀个字符串,CRC算出来的结果会不同。

这⾥给⼀个表⽰正确的CRC计算软件:/softview/SoftView_100981.html软件界⾯:软件说明 :(作为⼀个搞硬件的,理解这些软件参数的确不是⼀个容易的活,搜了很多资料)width : 表⽰最后CRC的bit的位数Poly : 表⽰多项式对应的⼆进制数,这⾥没有进⾏颠倒,x4+x+1=10011,最⾼位省略,对应的就是0x03,如果颠倒就是0x1100。

init :表⽰软件寄存器初值,上图为0x00.refin : 如果此值为true,表⽰输⼊的数据需要进⾏⽐特翻转,也就是Bit7要变成最低位, Bit0要变成最⾼位,这⾥是每个字节⽽⾔,每个字节之间的关系不需要进⾏颠倒。

如果此值为false,表明不需要进⾏字节的⽐特翻转refout:如果此值为true,这表⽰进⾏异或后算出来的CRC需要进⾏整个⽐特翻转,然后存⼊,例如:123456789 (实际中只能为0,1,为了⽅便解释这⾥的翻转和refin的区别,此处6,7,8,9等都是⼀位),转换后就是:987654321.如果此值为false,例如:123456789,则该⼀步后的输出为123456789XorOut:最个是将异或后的数据,在refout后的得到的数据与该值进⾏异或后,最终结果才是软件计算的CRC。

Verilog语言实现并行(循环冗余码)CRC校验

Verilog语⾔实现并⾏(循环冗余码)CRC校验1 前⾔(1)什么是CRC校验?CRC即循环冗余校验码:是数据通信领域中最常⽤的⼀种查错校验码,其特征是信息字段和校验字段的长度可以任意选定。

循环冗余检查(CRC)是⼀种数据传输检错功能,对数据进⾏多项式计算,并将得到的结果附在帧的后⾯,接收设备也执⾏类似的算法,以保证数据传输的正确性和完整性。

LFSR计算CRC,可以⽤多项式G(x)表⽰,G(x) = X16+X12+X5+1模型可如下图所⽰。

(2)校验原理其根本思想就是先在要发送的帧后⾯附加⼀个数(这个就是⽤来校验的校验码,但要注意,这⾥的数也是⼆进制序列的,下同),⽣成⼀个新帧发送给接收端。

当然,这个附加的数不是随意的,它要使所⽣成的新帧能与发送端和接收端共同选定的某个特定数整除(注意,这⾥不是直接采⽤⼆进制除法,⽽是采⽤⼀种称之为“模2除法”)。

到达接收端后,再把接收到的新帧除以(同样采⽤“模2除法”)这个选定的除数。

因为在发送端发送数据帧之前就已通过附加⼀个数,做了“去余”处理(也就已经能整除了),所以结果应该是没有余数。

如果有余数,则表明该帧在传输过程中出现了差错。

要校验的数据加上此数据计算出来的crc组成新的数据帧,如下图所⽰。

模2除法:模2除法与算术除法类似,但每⼀位除的结果不影响其它位,即不向上⼀位借位,所以实际上就是异或。

在循环冗余校验码(CRC)的计算中有应⽤到模2除法。

(3)步骤CRC校验中有两个关键点,⼀是预先确定⼀个发送送端和接收端都⽤来作为除数的⼆进制⽐特串(或多项式),可以随机选择,也可以使⽤国际标准,但是最⾼位和最低位必须为1;⼆是把原始帧与上⾯计算出的除数进⾏模2除法运算,计算出CRC码。

1. 选择合适的除数2. 看选定除数的⼆进制位数,然后再要发送的数据帧上⾯加上这个位数-1位的0,然后⽤新⽣成的帧以模2除法的⽅式除上⾯的除数,得到的余数就是该帧的CRC校验码。

CRC编码译码Verilog实现程序代码

程序代码:module crc(data_send,ready_s,data_out,resend,data_in,reset,data_receive,ready_r,clk,err);parameter width=1,amount=12;//width表示输入数据的位宽,amount表示码组中的信息位部分含有输入数据的个数output [width*amount+4:0] data_send; //data_send编码后的CRC循环码组输出,位宽为17output ready_s; //ready_s编码模块的准备就绪信号输出高电平有效output [width-1:0] data_out;//data_out——译码模块译码后信息数据的输出,位宽为widthoutput resend; //resend——重发信号输出高电平有效input [width-1:0]data_in;//data_in——编码模块信息数据输入,位宽为width.input reset;//reset编码模块计数器预置信号输入上升沿有效input [width*amount+4:0] data_receive;//data_receive译码模块接收CRC循环码组的输入input ready_r,clk,err; //ready_r译码模块准备就绪信号输入高电平有效; err迫使接收端接收数据出错信号输入高电平有效crc_send send1(data_send,ready_s,data_in,reset,clk);crc_receive receive1(data_out,resend,data_send,ready_r,clk,err);endmodule//编码模块module crc_send(data_send,ready_s,data_in,reset,clk);parameter width=1,amount=12;output [width*amount+4:0] data_send;output ready_s;input [width-1:0] data_in;input reset,clk;reg [width*amount+4:0] data_send;reg ready_s;reg [width*amount:0] buf_in;reg [width*amount+4:0] buf_data_s;integer n,i;always @(posedge reset or posedge clk)beginif(reset)n=0;elseif(n<amount-1)beginready_s<=0; //编码模块的准备就绪信清零buf_in=buf_in<<width;//buf_in输入缓冲器buf_in[width-1:0]=data_in;n=n+1;endelsebeginbuf_in=buf_in<<width;buf_in[width-1:0]=data_in;buf_data_s[width*amount+4:5]=buf_in;if(buf_in[11])buf_in[11:6]=buf_in[11:6]^6'b110101;if(buf_in[10])buf_in[10:5]=buf_in[10:5]^6'b110101;if(buf_in[9])buf_in[9:4]=buf_in[9:4]^6'b110101;if(buf_in[8])buf_in[8:3]=buf_in[8:3]^6'b110101;if(buf_in[7])buf_in[7:2]=buf_in[7:2]^6'b110101;if(buf_in[6])buf_in[6:1]=buf_in[6:1]^6'b110101;if(buf_in[5])buf_in[5:0]=buf_in[5:0]^6'b110101;buf_data_s[4:0]=buf_in[4:0];data_send[width*amount+4:0]=buf_data_s[width*amount+4:0];n=0;ready_s<=1;endendendmodule//解码模块module crc_receive(data_out,resend,data_receive,ready_r,clk,err);parameter width=1,amount=12;output [width-1:0] data_out;output resend;input [width*amount+4:0] data_receive;input ready_r,clk,err;reg [width-1:0] data_out;reg resend;reg [width*amount+4:0] buf_receive;reg [width*amount:0] buf_data_r;reg right;integer m;always @(posedge clk)beginif(ready_r)beginbuf_receive=data_receive;if(err)buf_receive[16]=~buf_receive[16];buf_data_r[width*amount:0]=buf_receive[width*amount+4:5];if(buf_data_r[11])buf_data_r[11:6]=buf_data_r[11:6]^6'b110101;if(buf_data_r[10])buf_data_r[10:5]=buf_data_r[10:5]^6'b110101;if(buf_data_r[9])buf_data_r[9:4]=buf_data_r[9:4]^6'b110101;if(buf_data_r[8])buf_data_r[8:3]=buf_data_r[8:3]^6'b110101;if(buf_data_r[7])buf_data_r[7:2]=buf_data_r[7:2]^6'b110101;if(buf_data_r[6])buf_data_r[6:1]=buf_data_r[6:1]^6'b110101;if(buf_data_r[5])buf_data_r[5:0]=buf_data_r[5:0]^6'b110101;if(!(buf_data_r[4:0]^buf_receive[4:0]))beginright=1;resend=0;data_out=buf_receive[16];buf_receive=buf_receive<<width;m=1;endelsebeginright=0;resend=1;data_out='bz;endendelse if(right)beginif(m<amount)begindata_out=buf_receive[width*amount+4:width*amount+5-width];buf_receive=buf_receive<<width;m=m+1;endendendEndmodule测试代码:module crc_test;reg data_in,reset,clk,err;reg [15:0] shift;wire [16:0] data_send;wire ready;always #50 clk=~clk;initialbeginclk=0;err=0;shift=16'h8000;reset=0;#10 reset=1;#20 reset=0;#9600 err=1;#100 err=0;#500000 $finish;endalways @(posedge clk)begindata_in=shift[0];shift=shift>>1;shift[15]=shift[14]^shift[11];if(!shift[15:12]) shift[15:12]=4'b1000;endcrc_send send(data_send,ready,data_in,reset,clk);crc_receive receive(data_out,resend,data_send,ready,clk,err); endmodule。

verilog实现crc校验原理

verilog实现crc校验原理CRC(循环冗余校验)是一种常用的数据校验方法,用于检测数据传输过程中是否出现错误。

在Verilog中,我们可以实现CRC校验原理,以确保数据的完整性。

首先,我们需要了解CRC校验的基本原理。

CRC是通过生成多项式进行计算的。

在Verilog中,我们可以使用移位寄存器和异或逻辑门来实现CRC校验。

以下是一个用Verilog实现CRC校验原理的示例代码:```verilogmodule crc_check (input wire [7:0] data_in, // 输入数据input wire [7:0] crc_in, // 输入CRC校验码output wire crc_valid // CRC校验结果有效位);reg [7:0] crc_reg; // CRC校验寄存器reg [7:0] crc_poly; // CRC多项式initial begincrc_reg = crc_in; // 初始化CRC校验寄存器crc_poly = 8'b10001110; // 初始化CRC多项式(这里以8位CRC为例)endalways @(posedge clk or posedge rst) beginif (rst) begincrc_reg <= crc_in; // 复位CRC校验寄存器end else begincrc_reg <= {crc_reg[6:0], crc_reg[7]} ^ (data_in & crc_poly); // 移位寄存器并进行异或计算endendassign crc_valid = (crc_reg == 8'b00000000); // 当CRC校验寄存器的值为0时,表示数据无错误endmodule```在以上示例代码中,我们创建了一个名为`crc_check`的模块,该模块接收输入数据和CRC校验码,并输出CRC校验结果的有效位。

CRC8_verilog

CRC8_verilog`timescale 1ns / 1ps/////////////////////////////////////////////////////////////////// ///////////// // Company:// Engineer://// Create Date: 15:40:57 09/17/09// Design Name:// Module Name: crc8// Project Name:// Target Device:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments:///////////////////////////////////////////////////////////////////// /////////////module crc8(reset,clk,start,data_in,out_rs,crc_code);parameter width=32; //信息位宽input reset;input clk;input [width-1:0] data_in;input start;output [7:0] out_rs;output [width+7:0] crc_code;reg [5:0] cnt;reg [width+7:0] dat_reg;wire [width+7:0] crc_enc;wire [width+7:0] reg_tem;reg crc_16bit_end;reg [width+7:0] tmp;reg [width-1:0] cd;always @(posedge clk or negedge reset) beginif(!reset) begincnt <= 0;endelse if(start) begincnt <= 0;endelse if(cnt==34) begincnt <= 34;endelse begincnt <= cnt + 1'b1;endendalways @(posedge clk or negedge reset) begin if(!reset) begindat_reg <= 0;endelse if(start) begindat_reg <= {data_in,8'h00};endelse if(cnt>0 && cnt <33) begindat_reg <= crc_enc;endendalways @(posedge clk or negedge reset) beginif(!reset) begincrc_16bit_end <= 0;endelse if(cnt == 33) begincrc_16bit_end <= 0;endelse begincrc_16bit_end <= 1;endendalways @(posedge clk or negedge reset) begin if(!reset) begintmp <= 0;endelse if(cnt==32) begintmp <= reg_tem;endendalways @(posedge clk or negedge reset) beginif(!reset) begincd <= 0;endelse if(start) begincd <= data_in;endendassign reg_tem = (cnt>0) ? {dat_reg[width+6:0],1'b0} : dat_reg;assign crc_enc[width+7] = (reg_tem[width+7]==1) ? ~reg_tem[width+7] : reg_tem[width+7]; assign crc_enc[width+7-1:width] = reg_tem[width+7-1:width];assign crc_enc[width-1] = (reg_tem[width+7]==1) ? ~reg_tem[width-1] : reg_tem[width-1];assign crc_enc[width-2:0] = reg_tem[width-2:0];//always @(posedge clk or negedge reset) begin// if(!reset) begin// out_rs <= 0;// end// else if(!crc_16bit_end) begin// out_rs <= crc_reg;// end//endassign out_rs = (~crc_16bit_end) ? tmp[width+7:32] : 0;assign crc_code = (~crc_16bit_end) ? {cd,tmp[width+7:32]} : 0;endmodule。

8路抢答器verilog语言程序

8路抢答器v e r i l o g语言程序-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN/****************************************************************************** **Copyright(c) , All right reservedProject name : 八路抢答器File name :Author : THE CEmail============================================================================= Description : 八路抢答器Called by :File tree :============================================================================= Revision History:Date By Ver. Change Description------------------------------------------------------------------------------2012-12-26 THE C 首次归档******************************************************************************* */`timescale 1ns/100psmodule choose8_1(input clk,input rst,input [7:0] keyin,output reg [2:0] sel,output reg [7:0] display);reg [9:0] count;reg clk_1hz,flag;reg [4:0] t;reg [3:0] disp;reg [3:0] data;always @ (negedge clk)if (count<999)count=count+1;elsebegincount=0;clk_1hz=~clk_1hz;endalways @ (posedge clk or negedge rst)beginif (!rst)begindata <= 4'b1010;flag <= 1'b0;endelseif (!flag && t)case (keyin [7:0])8'b00000001 : begin data<=4'b0001; flag<=1; end 8'b00000010 : begin data<=4'b0010; flag<=1; end 8'b00000100 : begin data<=4'b0011; flag<=1; end 8'b00001000 : begin data<=4'b0100; flag<=1; end 8'b00010000 : begin data<=4'b0101; flag<=1; end 8'b00100000 : begin data<=4'b0110; flag<=1; end 8'b01000000 : begin data<=4'b0111; flag<=1; end 8'b : begin data<=4'b1000; flag<=1; enddefault : begin data<=data; flag<=flag; endendcaseelse;endalways @ (posedge clk_1hz or negedge rst)beginif (!rst)t<=30;elseif (t>0 && !flag)t<=t-1;elset<=t;endalways @ (posedge clk or negedge rst)beginif (!rst)sel [2:0] <= 3'b000;elsebeginsel [2:0] <= sel[2:0]+3'b001;endendalways @ (*)begincase( sel[2:0] )3'b000: disp [3:0] = t/10;3'b001: disp [3:0] = t%10;3'b010: disp [3:0] = 4'b1111;3'b011: disp [3:0] = 4'b1010+clk_1hz;3'b100: disp [3:0] = 4'b1010+clk_1hz;3'b101: disp [3:0] = 4'b1010+clk_1hz;3'b110: disp [3:0] = 4'b1111;3'b111: disp [3:0] = data;endcaseendalways @ (*)begincase( disp )4'b0000: display [7:0]=8'b01111110; //04'b0001: display [7:0]=8'b00110000; //14'b0010: display [7:0]=8'b01101101; //24'b0011: display [7:0]=8'b01111001; //34'b0100: display [7:0]=8'b00110011; //44'b0101: display [7:0]=8'b01011011; //54'b0110: display [7:0]=8'b01011111; //64'b0111: display [7:0]=8'b01110000; //74'b1000: display [7:0]=8'b01111111; //84'b1001: display [7:0]=8'b01111011; //94'b1010: display [7:0]=8'b00000001; //-default: display [7:0]=8'b00000000; //全灭 endcaseendendmodule。

CRC算法及Verilog实现知识分享

C R C算法及V e r i l o g实现CRC算法原理及其Verilog实现1CRC简介CRC校验是一种在数据通信系统和其它串行传输系统中广泛使用的错误检测手段。

通用的CRC标准有CRC-8、CRC-16、CRC-32、CRC-CCIT,其中在网络通信系统中应用最广泛的是CRC-32标准。

本文将以CRC-32为例,说明CRC编码的实现方式以及如何用verilog语言对CRC编码进行描述。

2二.模2运算在说明CRC编码方式之前,首先介绍一下模2运算法则,在CRC运算过程中会使用到模2除法运算。

模2运算是一种二进制运算法则,与四则运算相同,模2运算也包括模2加、模2减、模2乘、模2除四种运算。

模2运算用“+”表示加法运算,用“-”、“×”或“.”、“/”分别表示减法、乘法和除法运算。

与普通四则运算法则不同的是,模2加法是不带进位的二进制加法运算,模2减法是不带借位的二进制减法运算。

同时,模2乘法在累加中间结果时采用的是模2加法运算;模2除法求商过程中余数减除数采用的是模2减法运算。

因此,两个二进制数进行模2加减法运算时,相当于两个二进制数进行按位异或运算,每一位的结果只与两个数的当前位有关。

模2除法在确定商时,与普通二进制除法也略有区别。

普通二进制除法中,当余数小于除数时,当前位的商为0,当余数大于等于除数时,当前位的商为1。

模2除法在确定当前位的商时,只关心余数的首位,首位为1则商为1,首位为0则商为0。

1.模2加法的定义:0+0=0,0+1=1,1+0=1,1+1=0。

举例如下:1010+0110=1100。

2.模2减法的定义:0-0=0,0-1=1,1-0=1,1-1=0。

举例如下:1010-0110=1100。

3.模2乘法的定义:0×0=0,0×1=0,1×0=0,1×1=1。

举例如下:1011×101=100111列竖式计算:1011× 101——————101100001011——————100111其中横线之间的累加过程,采用的是2进制加法,不进位。

一个简单的8位处理器完整设计过程及verilog代码

一个简单的8位处理器完整设计过程及verilog代码来源: EETOP BBS 作者:weiboshe一个简单的8位处理器完整设计过程及verilog代码,适合入门学习参考,并含有作者个人写的指令执行过程(点击下方阅读原文到论坛可下载源码)1. CPU定义我们按照应用的需求来定义计算机,本文介绍一个非常简单的CPU的设计,它仅仅用来教学使用的。

我们规定它可以存取的存储器为64byte,其中1byte=8bits。

所以这个CPU就有6位的地址线A[5:0],和8位的数据线D[7:0]。

我们仅定义一个通用寄存器AC(8bits寄存器),它仅仅执行4条指令如下:Instruction Instruction Code OperationADD00AAAAAA AC<—AC+M[AAAAAA]AND01AAAAAA AC<—AC^M[AAAAAA]JMP10AAAAAA GOTO AAAAAAINC11XXXXXX AC<—AC+1除了寄存器AC外,我们还需要以下几个寄存器:地址寄存器 A[5:0],保存6位地址。

程序计数器 PC[5:0],保存下一条指令的地址。

数据寄存器 D[7:0],接受指令和存储器来的数据。

指令寄存器 IR[1:0],存储指令操作码。

2. 取指设计在处理器执行指令之前,必须从存储器取出指令。

其中取指执行以下操作:1〉通过地址端口A[5:0]从地址到存储器2〉等待存储器准备好数据后,读入数据。

由于地址端口数据A[5:0]是从地址寄存器中读出的,所以取指第一个执行的状态是Fetch1: AR<—PC接下来cpu发出read信号,并把数据从存储器M中读入数据寄存器DR中。

同时pc加一。

Fetch2: DR<—M,PC<—PC+1接下来把DR[7:6]送IR,把DR[5:0]送ARFetch3: IR<—DR[7:6],AR<—DR[5:0]3. 指令译码Cpu在取指后进行译码一边知道执行什么指令,对于本文中的CPU来说只有4条指令也就是只有4个执行例程,状态图如下:4. 指令执行对译码中调用的4个例程我们分别讨论:4.1 ADD指令ADD指令需要CPU做以下两件事情:1〉从存储器取一个操作数2〉把这个操作数加到AC上,并把结果存到AC所以需要以下操作:ADD1: DR<—MADD2: AC<—AC+DR4.2 AND指令AND指令执行过程和ADD相似,需要以下操作:AND1: DR<—MAND2: AC<—AC^DR4.3 JMP指令JMP指令把CPU要跳转的指令地址送PC,执行以下操作JMP1: PC<—DR[5:0]4.4INC指令INC指令执行AC+1操作INC1: AC<—AC+1总的状态图如下:5 建立数据路径这一步我们来实现状态图和相应的寄存器传输。

CRC校验课程设计verilog

CRC校验课程设计verilog一、教学目标本课程的目标是让学生掌握CRC校验的基本原理,并能够使用Verilog进行CRC校验器的设计和仿真。

通过本课程的学习,学生应能够:1.描述CRC校验的基本原理和流程。

2.理解CRC校验码的生成方法和步骤。

3.使用Verilog编写CRC校验器的模块代码。

4.进行CRC校验器的仿真测试,验证其正确性。

二、教学内容本课程的教学内容主要包括以下几个部分:1.CRC校验的基本原理:介绍CRC校验的定义、原理和流程,以及CRC校验码的生成方法和步骤。

2.Verilog的基本语法:回顾Verilog的基本语法和编程技巧,为后续的CRC校验器设计打下基础。

3.CRC校验器的设计:讲解如何使用Verilog编写CRC校验器的模块代码,包括CRC校验码的生成和检查。

4.CRC校验器的仿真:介绍如何使用仿真工具进行CRC校验器的仿真测试,验证其正确性。

三、教学方法为了激发学生的学习兴趣和主动性,本课程将采用多种教学方法相结合的方式进行教学。

包括:1.讲授法:讲解CRC校验的基本原理和Verilog的基本语法。

2.案例分析法:通过分析实际案例,让学生理解CRC校验器的设计方法和步骤。

3.实验法:让学生动手编写Verilog代码,进行CRC校验器的仿真测试。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将准备以下教学资源:1.教材:选用《数字逻辑与计算机设计》作为主要教材,介绍CRC校验的基本原理和Verilog的语法。

2.参考书:提供《Verilog HDL权威指南》等参考书籍,供学生深入学习Verilog编程。

3.多媒体资料:制作PPT课件,生动展示CRC校验的基本原理和设计方法。

4.实验设备:提供计算机和仿真工具,让学生进行CRC校验器的仿真测试。

五、教学评估本课程的教学评估将采用多元化的评估方式,以全面、客观、公正地评价学生的学习成果。

评估方式包括:1.平时表现:通过课堂参与、提问、讨论等方式评估学生的学习态度和积极性。

CRC-8校验方法

CRC-8校验方法CRC即循环冗余校验码(Cyclic Redundancy Check):是数据通信领域中最常用的一种差错校验码,其特征是信息字段和校验字段的长度可以任意选定。

CRC校验可以简单地描述为:例如我们要发送一些数据(信息字段),为了避免一些干扰以及在接收端的对读取的数据进行判断是否接受的是真实的数据,这时我们就要加上校验数据(即CRC 校验码),来判断接收的数据是否正确。

在发送端,根据要传送的k位二进制码序列,以一定的规则(CRC校验有不同的规则。

这个规则,在差错控制理论中称为“生成多项式”。

)产生一个校验用的r 位校验码(CRC 码),附在原始信息后边,构成一个新的二进制码序列数共k+r位,然后发送出去。

在接收端,根据信息码和CRC码之间所遵循的规则(即与发送时生成CRC校验码相同的规则)进行检验,校验采用计算机的模二除法,即除数和被除数(即生成多项式)做异或运算,进行异或运算时除数和被除数最高位对齐,进行按位异或运算,若最终的数据能被除尽,则传输正确;否则,传输错误。

CRC8即最终生成的CRC校验码为1字节,其生成多项式,生成多项式为g(x)=x8+x5+x4+1,相当于g(x)=1·x8+0·x7+0·x6+1·x5+1·x4+0·x3+0·x2+0·x1+1·x0,即对应的二进制数为100110001。

CRC8校验算法:1.CRC8校验的一般性算法:例如:信息字段代码为: 00000001 00000010 ————对应m(x)=x8+x生成多项式为:g(x)=x8+x5+x4+1 ————对应g(x)的二进制代码为:100110001现在我们将要对2字节数据0x0102生成CRC8校验码,并最终将生成的1字节CRC校验码跟在0x0102的后面,即0x01 02 ##,(##即8为CRC码),最终生成的3字节数据就是经CRC8校验生成的数据。

crc多项式的verilog实现

crc多项式的verilog实现以下是一个CRC多项式的Verilog实现的示例:```verilogmodule crc (input wire clk,input wire reset,input wire [7:0] data_in,input wire enable,output wire [7:0] crc_out);reg [7:0] crc_reg;always @(posedge clk or posedge reset) beginif (reset) begincrc_reg <= 8'b00000000;end else beginif (enable) begincrc_reg <= crc_reg ^ data_in;for (i = 0; i < 8; i = i + 1) beginif (crc_reg[7]) begincrc_reg <= crc_reg << 1 ^ 8'b10011001;end else begincrc_reg <= crc_reg << 1;endendendendendassign crc_out = crc_reg;endmodule```在这个示例中,`crc`模块定义了一个8位的CRC寄存器`crc_reg`,它通过异或运算 `^` 和移位运算 `<<` 实现CRC计算。

在时钟上升沿或复位信号 `reset` 上升沿触发的时候,如果复位信号 `reset` 为1,则将CRC寄存器重置为0;否则,如果使能信号 `enable` 为1,则计算CRC值。

计算CRC值的核心部分是循环 `for` 循环。

在每次循环中,如果CRC寄存器的最高位为1,则与CRC多项式 `8'b10011001` 异或;否则,只进行左移操作。

最后,通过 `assign` 语句,将计算出的CRC值赋给输出端口`crc_out`。

聊一聊CRC算法的硬件电路实现:串行电路和并行电路

聊一聊CRC算法的硬件电路实现:串行电路和并行电路

这一篇文章聊一聊CRC算法的硬件电路实现:串行电路和并行电路。

下面的内容还是IC君的朋友文武写的,IC君稍微做了优化排版和少量的编辑工作提升大家的阅读体验。

1

CRC硬件电路的实现很简单,下图给出教科书上任意生成多项式G(X)=gnXn+gn-1Xn-1+···+g1X+g0的电路结构:

为什么从右边输入data?

因为CRC是除余数,所以从右边输入数据,相当于把信息位data先左移位。

以简单的CRC8举例,多项式G(x)=X8 +X7 +X6 +X4 +X2 +1 的电路示意图如下:

对应的Verilog code代码如下:

上面的Verilog code上用了LFSR这种变量声明,有没有感到奇怪?

LFSR(线性移位寄存器)和CRC的算法很像的,有兴趣的可去看看LFSR的相关知识。

一位串行输入的CRC电路实现方法很简单,每周期的组合逻辑链路简单延时短。

它的缺点是输入位宽只有一位,所以一个clock周期只能算一位,如果是64bit的信息位就要64个clock周期。

如果需要传输的位数比较多,会对系统的性能产生比较大的影响。

假设要把输入位宽变成8位(byte)输入,电路将是什么样的呢?并行的CRC其实也简单,可以用提前抽取的概念来实现。

用下图来解释一下,CRCM有M个校验位就是有M个寄存器,现在把输入变成N位。

提前抽取就是通过关系函数得到下一个clock寄存器的输入nxt_crc[M-1:0]:

关系函数CN如下:

nxt_crc=CN(crc_out,data),。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////// // Company:

// Engineer:

//

// Create Date: 15:40:57 09/17/09

// Design Name:

// Module Name: crc8

// Project Name:

// Target Device:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

////////////////////////////////////////////////////////////////////////////////

module crc8(reset,clk,start,data_in,out_rs,crc_code);

parameter width=32; //信息位宽

input reset;

input clk;

input [width-1:0] data_in;

input start;

output [7:0] out_rs;

output [width+7:0] crc_code;

reg [5:0] cnt;

reg [width+7:0] dat_reg;

wire [width+7:0] crc_enc;

wire [width+7:0] reg_tem;

reg crc_16bit_end;

reg [width+7:0] tmp;

reg [width-1:0] cd;

always @(posedge clk or negedge reset) begin

if(!reset) begin

cnt <= 0;

end

else if(start) begin

cnt <= 0;

end

else if(cnt==34) begin

cnt <= 34;

end

else begin

cnt <= cnt + 1'b1;

end

end

always @(posedge clk or negedge reset) begin if(!reset) begin

dat_reg <= 0;

end

else if(start) begin

dat_reg <= {data_in,8'h00};

end

else if(cnt>0 && cnt <33) begin

dat_reg <= crc_enc;

end

end

always @(posedge clk or negedge reset) begin

if(!reset) begin

crc_16bit_end <= 0;

end

else if(cnt == 33) begin

crc_16bit_end <= 0;

end

else begin

crc_16bit_end <= 1;

end

end

always @(posedge clk or negedge reset) begin if(!reset) begin

tmp <= 0;

end

else if(cnt==32) begin

tmp <= reg_tem;

end

end

always @(posedge clk or negedge reset) begin

if(!reset) begin

cd <= 0;

end

else if(start) begin

cd <= data_in;

end

end

assign reg_tem = (cnt>0) ? {dat_reg[width+6:0],1'b0} : dat_reg;

assign crc_enc[width+7] = (reg_tem[width+7]==1) ? ~reg_tem[width+7] : reg_tem[width+7]; assign crc_enc[width+7-1:width] = reg_tem[width+7-1:width];

assign crc_enc[width-1] = (reg_tem[width+7]==1) ? ~reg_tem[width-1] : reg_tem[width-1];

assign crc_enc[width-2:0] = reg_tem[width-2:0];

//always @(posedge clk or negedge reset) begin

// if(!reset) begin

// out_rs <= 0;

// end

// else if(!crc_16bit_end) begin

// out_rs <= crc_reg;

// end

//end

assign out_rs = (~crc_16bit_end) ? tmp[width+7:32] : 0;

assign crc_code = (~crc_16bit_end) ? {cd,tmp[width+7:32]} : 0;

endmodule。