数字电路的基础知识教程第2章.

(数字电子技术基础)第2章. 门电路

• 小规模集成电路(SSI-Small Scale 小规模集成电路(SSI(SSI Integration), 每片组件内包含10~100 10~100个元件 Integration), 每片组件内包含10~100个元件 10~20个等效门 个等效门) (或10~20个等效门)。 • 中规模集成电路(MSI-Medium Scale 中规模集成电路(MSI (MSIIntegration),每片组件内含100~1000 100~1000个元件 Integration),每片组件内含100~1000个元件 20~100个等效门 个等效门) (或20~100个等效门)。 • 大规模集成电路(LSI-Large Scale 大规模集成电路(LSI (LSIIntegration), 每片组件内含1000~100 000个 Integration), 每片组件内含1000~100 000个 元件( 100~1000个等效门 个等效门) 元件(或100~1000个等效门)。 • 超大规模集成电路(VLSI-Very Large Scale 超大规模集成电路(VLSI (VLSIIntegration), 每片组件内含100 000个元件 Integration), 每片组件内含100 000个元件 1000个以上等效门 个以上等效门) (或1000个以上等效门)。

•

+5V

R1

T1

T5 R3

•

(2-30)

前级

后级

灌电流的计算

饱和

I OL

5 − T5压降 − T1的be结压降 = R1

5 − 0.3 − 0.7 ≈ 1.4mA = 3

(2-31)

关于电流的技术参数

名称及符号 输入低电平电流 IiL 输入高电平电流 IiH IOL 及其极限 IOL(max) IOH 及其极限 IOH (max) 含义 输入为低电平时流入输 入端的电流-1 入端的电流 .4mA。 。 输入为高电平时流入输 入端的电流几十 几十μ 。 入端的电流几十μA。 当 IOL> IOL(max)时,输出 不再是低电平。 不再是低电平。 当 IOH >IOH(max)时, 输出 不再是高电平。 不再是高电平。

数字电路基础知识部分(第二章)

练习一、一、填空题1、 模拟信号是在时间上和数值上都是 变化 的信号。

2、 脉冲信号则是指极短时间内的 电信号。

3、 广义地凡是 规律变化的,带有突变特点的电信号均称脉冲。

4、 数字信号是指在时间和数值上都是 的信号,是脉冲信号的一种。

5、 常见的脉冲波形有,矩形波、 、三角波、 、阶梯波。

6、 一个脉冲的参数主要有 、tr 、 、T P 、T 等。

7、 数字电路研究的对象是电路的 之间的逻辑关系。

8、 电容器两端的电压不能突变,即外加电压突变瞬间,电容器相当于 。

9、 电容充放电结束时,流过电容的电流为0,电容相当于 。

10、 通常规定,RC 充放电,当t = 时,即认为充放电过程结束。

11、 RC 充放电过程的快慢取决于电路本身的 ,与其它因素无关。

12、 RC 充放电过程中,电压,电流均按 规律变化。

13、 理想二极管正向导通时,其端电压为0,相当于开关的 。

14、 在脉冲与数字电路中,三极管主要工作在 和 。

15、 三极管输出响应输入的变化需要一定的时间,时间越短,开关特性 。

16、 选择题1 若逻辑表达式F A B =+,则下列表达式中与F 相同的是( ) A 、F A B = B 、F AB = C 、F A B =+2 若一个逻辑函数由三个变量组成,则最小项共有( )个。

A 、3 B 、4 C 、83 图9-1所示是三个变量的卡诺图,则最简的“与或式”表达式为( ) A 、A B A C B C ++B 、A B BC AC ++ C 、AB BC AC ++4 下列各式中哪个是三变量A 、B 、C 的最小项( ) A 、A B C ++ B 、A B C + C 、ABC 5、模拟电路与脉冲电路的不同在于( )。

A 、模拟电路的晶体管多工作在开关状态,脉冲电路的晶体管多工作在放大状态。

B 、模拟电路的晶体管多工作在放大状态,脉冲电路的晶体管多工作在开关状态。

C 、模拟电路的晶体管多工作在截止状态,脉冲电路的晶体管多工作在饱和状态。

数字电子技术第2章

① 线与逻辑图

演 示 文 稿 Presentation

A B

&

L1 L=L1 L2

C D

&

L2

线与逻辑图 EXIT EXIT

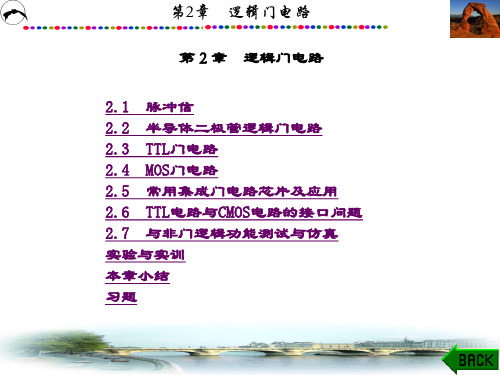

第2章 逻辑门电路

②

UCC

母线传输

(BUS)

B1

× ×

演 示 文 稿 Presentation

RC

B1

& 1

& 2 E2 B1

& n En B2

选 通 信 号 E1 数字信号1

(5) UOH (min) :输出高电平的下限值,2.4 V。 输出高电平的下限值, 。 (6) UOL (max) :输出低电平的上限值,0.4 V。 输出低电平的上限值, 。 (7) IOH (max) :高电平输出电流(拉电流)的上限值,0.4 mA。 高电平输出电流(拉电流)的上限值, 。 (8) IOL (max) :低电平输出电流(灌电流)的上限值,-16 mA。 低电平输出电流(灌电流)的上限值, 。 (9) VCC :电源电压,( ±5%)V。 电源电压,( ,(5± ) 。 EXIT EXIT

× × √

VD3 Z VT5

0

EXIT EXIT

第2章 逻辑门电路

A

演 示 文 稿 Presentation

B 0 1 0 1

Z 1 1 1 0

0 0 1 1

Z = AB

EXIT EXIT

第2章 逻辑门电路

2.TTL与非门的电压传输特性 . 与非门的电压传输特性

TTL与非门的电压传输特性是指其输出电压 O 与非门的电压传输特性是指其输出电压u 与非门的电压传输特性是指其输出电压 与输入电压u 的关系特性。 与输入电压 I的关系特性。

数字电子技术基础第三版第二章答案

第二章逻辑门电路第一节重点与难点一、重点:1.TTL与非门外特性(1)电压传输特性及输入噪声容限:由电压传输特性曲线可以得出与非门的输出信号随输入信号的变化情况,同时还可以得出反映与非门抗干扰能力的参数U on、U off、U NH和U NL。

开门电平U ON是保证输出电平为最高低电平时输入高电平的最小值。

关门电平U OFF 是保证输出电平为最小高电平时,所允许的输入低电平的最大值。

(2)输入特性:描述与非门对信号源的负载效应。

根据输入端电平的高低,与非门呈现出不同的负载效应,当输入端为低电平U IL时,与非门对信号源是灌电流负载,输入低电平电流I IL通常为1~1.4mA。

当输入端为高电平U IH时,与非门对信号源呈现拉电流负载,输入高电平电流I IH通常小于50μA。

(3)输入负载特性:实际应用中,往往遇到在与非门输入端与地或信号源之间接入电阻的情况,电阻的取值不同,将影响相应输入端的电平取值。

当R≤关门电阻R OFF时,相应的输入端相当于输入低电平;当R≥ 开门电阻R ON时,相应的输入端相当于输入高电平。

2.其它类型的TTL门电路(1)集电极开路与非门(OC门)多个TTL与非门输出端不能直接并联使用,实现线与功能。

而集电极开路与非门(OC 门)输出端可以直接相连,实现线与的功能,它与普通的TTL与非门的差别在于用外接电阻代替复合管。

(2)三态门TSL三态门即保持推拉式输出级的优点,又能实现线与功能。

它的输出除了具有一般与非门的两种状态外,还具有高输出阻抗的第三个状态,称为高阻态,又称禁止态。

处于何种状态由使能端控制。

3.CMOS逻辑门电路CMOS反相器和CMOS传输门是CMOS逻辑门电路的最基本单元电路,由此可以构成各种CMOS逻辑电路。

当CMOS反相器处于稳态时,无论输出高电平还是低电平,两管中总有一管导通,一管截止,电源仅向反相器提供nA级电流,功耗非常小。

CMOS器件门限电平U TH近似等于1/2U DD,可获得最大限度的输入端噪声容限U NH和U NL=1/2U DD。

数字电路第2章逻辑代数基础及基本逻辑门电路

(5)AB+A B = A (6)(A+B)(A+B )=A 证明: (A+B)(A+B )=A+A B+AB+0 A( +B+B) = 1 JHR A =

二、本章教学大纲基本要求 熟练掌握: 1.逻辑函数的基本定律和定理; 门、 2.“与”逻辑及“与”门、“或”逻辑及“或”

“非”逻辑及“非”门和“与”、“或”、“非” 的基本运算。 理解:逻辑、逻辑状态等基本概念。 三、重点与难点 重点:逻辑代数中的基本公式、常用公式、 基本定理和基本定律。

JHR

难点:

JHR

1.具有逻辑“与”关系的电路图

2.与逻辑状态表和真值表

JHR

我们作如下定义: 灯“亮”为逻辑“1”,灯“灭”为逻辑“0” 开关“通”为逻辑“1”,开关“断”为逻辑 “0” 则可得与逻辑的真值表。 JHR

3.与运算的函数表达式 L=A·B 多变量时 或 读作 或 L=AB L=A·B·C·D… L=ABCD… 1.逻辑表达式 2.逻辑符号

与非逻辑真值表

Z = A• B

3.逻辑真值表

逻辑规律:有0出1 全1 出0

JHR

A 0 0 1 1

B 0 1 0 1

Z 1 1 1 0

二、或非逻辑 1.逻辑表达式 2.逻辑符号

Z = A+ B

先或后非

3.逻辑真值表

JHR

三、与或非逻辑 1.逻辑表达式 2.逻辑符号

1.代入规则 在任一逻辑等式中,若将等式两边出现的同 一变量同时用另一函数式取代,则等式仍然成立。

JHR

代入规则扩大了逻辑代数公式的应用范围。例如摩 根定理 A+B = A ⋅ B 若将此等式两边的B用B+C 取代,则有

精品课件-数字电子技术-第2章

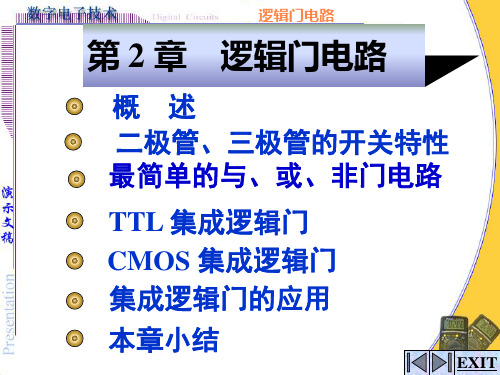

第2章 集成逻辑门电路

图2-7 双极型三极管输入特性曲线

第2章 集成逻辑门电路

图2-8 双极型三极管输出特性曲线

第2章 集成逻辑门电路

3. 双极型晶体管的静态特性 在数字逻辑电路中,三极管作为开关元件,工作于饱和区 和截止区。图2-9是一个由双极性晶体管构成的典型的单管共 射放大电路,三极管V的门限电压为Uon,当输入电压ui小于门 限电压Uon时,发射结处于反向偏置,三极管工作于截止状态, iB≈0,iC≈0, uo=UCC。当输入电压ui大于某一数值时,发射 结和集电结均达到正向偏置,三极管工作于饱和状态,饱和导 通的条件为

第2章 集成逻辑门电路

图2-4 (a) 或门电路;(b) 逻辑符号

第2章 集成逻辑门电路

表2-2(a) 二极管或门电平

第2章 集成逻辑门电路

表2-2(b) 二极管或门真值表

第2章 集成逻辑门电路

从真值表分析可知:只要A、B当中有一个是高电平,Y即

为高电平,只有A、B同时为低电平,Y才为低电平, “或”

第2章 集成逻辑门电路

第2章 集成逻辑门电路

2.1 概述 2.2 分立元件逻辑门电路 2.3 TTL集成逻辑门 2.4 CMOS集成逻辑门

第2章 集成逻辑门电路

2.1 概 述

门电路(gate circuit)是构成数字电路的基本单元。所 谓“门”就是一种条件开关,在一定的条件下,它允许信号通 过,条件不满足时,信号无法通过,从而形成高电平和低电平 两种状态。在二值逻辑中,逻辑变量的取值不是1就是0,在 电子电路中用高、低电平分别表示1 和 0

图2-2 二极管伏安特性的近似方法与等效电路

第2章 集成逻辑门电路

2. 实现与逻辑关系的电路称为与门。最简单的与门可以由二 极管和电阻组成。图2-3(a)所示是有两个输入端的与门电路, 图2-3(b)所示为它的逻辑符号。图中A、B为两个信号输入端, Y为输出端。设UCC=5 V,A、B输入端的高低电平分别为UIH=3 V 和UIL=0 V,二极管VD1、VD2的正向导通压降为UD=0.7 V。输入 端A、B

数字电子技术基础第2章

AB

1 1 1 0

A B

1 1 1 0

A B

1 0 0 0

AB

1 0 0 0

第2章 逻辑代数基础

2.2.2 三个重要规则

1. 代入规则

任何一个逻辑等式,如果将等式两边所出现的某一变量都

代之以同一逻辑函数,则等式仍然成立,这个规则称为代入 规则。 由于逻辑函数与逻辑变量一样,只有0、1两种取值, 所以代入规则的正确性不难理解。运用代入规则可以扩大基 本定律的运用范围。

第2章 逻辑代数基础

3

异或和同或运算的常用公式如表2.3.3所示。表中的公

式可以利用真值表或前面的公式证明。 表2.3.3 异或、同或运算的常用公式

名称 变量与 常量的 关系 交换律 结合律 分配律 反演律 调换律 奇偶律 异或公式 A 0=A A 1= A A A =1 A B=B A A B C=A (B C) A(B C)=AB AC 同或公式 A A A A A 1=A 0= A A =0 B=B A (B C)=(A C)=(A+B) B) C (A+C)

公式 1 A+1=1 A+0=A A+A=A A+ A =1 A+B=B+A (A+B)+C=A+(B+C) A+BC=(A+B)(B+C)

公式 2 A 0=0 A 1= A A A=A A A =0 A B=B A (A B) C=A (B C) A (B+C)=AB+AC

B A B L

特点:任1 则1, 全0则0

或逻辑表达式: L = A +B

数字电子技术基础课后习题答案第2章习题答案

思考题:题2.1.1 答:肖特基二极管(SBD)、分流。

题2.1.2 答:基区、滞后。

题2.1.3 答:(A)、(B) 。

题2.1.4 答:对。

题2.2.1 答:A、B。

题2.2.2 答:C、D。

题2.2.3 答:4ns。

题2.2.4 答:(A)、(C)、。

题2.2.5 答:降低、降低。

题2.2.6 答:0、1和三态题2.2.7 答:若一个输出高电平,另一个输出低电平时,会在T4和T5间产生一个大电流,烧毁管子。

OC门“线与”在输出接一电阻和一5-30V电源电压。

题2.2.8 答:能、分时。

题2.2.9 答:1. 为了缩短传输延迟时间,电路中使用肖特基管和有源泄放电路,另外,还将输入级的多发射极管改用SBD代替,由于SBD没有电荷存储效应,因此有利于提高电路的工作速度。

电路中还接入了D3和D4两个SBD,当电路的输出端由高电平变为低电平时,D4经T2的集电极和T5的基极提供了一条通路,一是为了加快负载电容的放电速度,二是为了加速T5的导通过程。

另外,D3经T2的集电极为T4的基极提供了一条放电通路,加快了T4的截止过程。

2. 为降低功耗,提高了电路中各电阻的阻值,将电阻R5原来接地的一端改接到输出端,以减小T3导通时电阻R5上的功耗。

题2.3.1 答:A。

题2.3.2 答:A。

题2.3.3 答:A。

题2.3.4 答:导通。

题2.3.5 答:B、C。

思考题:题2.4.1 答:(A)分流。

题2.4.2 答:(B) 内部电阻和容性负载。

题2.4.3 答:(B) 3.3V;(C)5V;(D) 30V。

题2.4.4 答:CMOS反相器和CMOS传输门。

题2.4.5 答:加入缓冲器保证输出电压不抬高或者降低,正逻辑变负逻辑或者相反,与非变成或非,或者或非变为与非。

题2.4.6 答:(C)低、高。

题2.4.7答:(A) OD门;(B) OC门;(C)三态门。

16题2.4.8 答:(A)驱动大负载;(B)电平移位。

数字电子技术基础第二章门电路PPT课件

或门

实现逻辑或运算,当至少 一个输入为高电平时,输 出为高电平;否则输出为 低电平。

非门

实现逻辑非运算,当输入 为高电平时,输出为低电 平;当输入为低电平时, 输出为高电平。

门电路的分类

按功能分类

可分为与门、或门、非门、 与非门、或非门等。

按结构分类

可分为晶体管-晶体管逻辑 门(TTL)、金属氧化物 半导体逻辑门(MOS)等。

实践能力。

02 门电路的基本概念

逻辑门电路

逻辑门电路是数字电路的基本 单元,用于实现逻辑运算。

常见的逻辑门电路有与门、或 门、非门、与非门、或非门等。

逻辑门电路通常由晶体管、电 阻、电容等元件组成,具有高 电平、低电平和高阻态三种输 出状态。

常用逻辑门电路

01

02

03

与门

实现逻辑与运算,当所有 输入都为高电平时,输出 为高电平;否则输出为低 电平。

门电路在其他领域的应用

自动化控制

门电路可以用于实现自动化控制中的逻辑控制、 顺序控制等功能。

电子游戏

门电路可以用于实现电子游戏中的逻辑运算、状 态检测等功能。

智能家居

门电路可以用于实现智能家居中的控制逻辑、传 感器检测等功能。

05 门电路的实例分析

实例一:基本逻辑门电路的应用

基本逻辑门电路

包括与门、或门、非门等,是数字电路中最基本的逻辑单 元。

06 总结与展望

门电路的重要性和作用

门电路是数字电子技术的核心组件,它在数字电路中起到逻辑运算和信号控制的作 用。

门电路能够实现逻辑函数的运算,从而实现各种复杂的逻辑功能,是构成各种数字 系统和电子设备的基础。

门电路在计算机、通信、自动化等领域中有着广泛的应用,对现代科技的发展起着 至关重要的作用。

数字电子技术基础-第二章--逻辑门电路基础

A

≥1

B

L=A+B

负逻辑体制呢?

三、非门电路

第三节 TTL逻辑门电路

一、标准生产工艺的TTL非门的工作原理

TTL的含义:Transistor Transistor

(一)输入VI为高电平3.6V时

(二)输入VI为低电平0.3V 时

二、标准生产工艺的TTL非门的电 路结构特点

1、输入级采用三极管以提高工作速度。

➢ (2)把三极管放入电路中,电路的拓扑结构回到从前。假设 三极管处于临界饱和状态(三极管既可以认为是处于饱和状态 也可以认为是处于放大状态,在放大区和饱和区的交界区域, 此时时的三特极征管IC=既ßI有B)饱,和求状此态时时三的极特管征的VC集ES电=极0.临3V界,饱又和有电放流大I状CS 态, 进极而管求的出集基 电极极临可界能饱流和过电的流最大IBS电。流集。电极临界饱和电流ICS是三

5 60 10

0.0083(mA)

因为iB>IBS 所以三极管处于饱和状态,如图2-15中的 E点所示。

(2)vi=-2V

(二)双极型三极管的动态开关特性

(1)延迟时间td—— 从输入信号vi正跳变的 瞬 间开始,到集电极电流iC上升到0.1ICS所需的 时间

(2)上升时间tr——集电极电流从0.1ICS上升到 0.9ICS所需的时间。

5V 0V

5V 5V

输出 VL 0V 0V 0V 5V

A

&

L=A·B

B

负逻辑体制

A

≥1

B

L=A+B

输入

VA

VB

0V 0V

0V 5V

5V 0V

5V 5V

输出 VL 0V 0V 0V 5V

【精品PPT】数字电子技术基础全套课件-2(2024版)

如果以逻辑变量作为输入,以运算结果作为 输出,当输入变量的取值确定之后,输出的取值 便随之而定。输出与输入之间的函数关系称为逻 辑函数。Y=F(A,B,C,…)

二、逻辑函数表示方法 常用逻辑函数的表示方法有:逻辑真值表(真

值表)、逻辑函数式(逻辑式或函数式)、逻辑 图、波形图、卡诺图及硬件描述语言。它们之间 可以相互转换。

( A B)

B A

( A B)

Y (( A B) ( A B)) ( A B)( A B) AB AB

5、波形图→真值表

A

1111

0000

B

11

11

00

00

C 1111

00

Y 11

00 11

0

00 0

ABC Y 00 0 0 t 00 1 1 01 0 1 t 01 1 0 10 0 0 t 10 1 1 11 0 0 t 11 1 1

A断开、B接通,灯不亮。

将开关接通记作1,断开记作0;灯亮记作1,灯 灭记作0。可以作出如下表格来描述与逻辑关系:

功能表

开关 A 开关 B 灯 Y

A

断开 断开

灭

0

断开 闭合

灭

0

1

闭合 断开

灭

1

闭合 闭合 亮

BY

00 真 10 值

00 表

11

两个开关均接通时,灯才会 Y=A•B

亮。逻辑表达式为:

实现与逻辑的电路称为与门。

与门的逻辑符号:

A

&

Y Y=A•B

B

二、或逻辑(或运算)

或逻辑:当决定事件(Y)发生的各种条件A,B,

C,…)中,只要有一个或多个条件具备,事件(Y)

精品课件-数字电子技术-第2章

第2章 逻辑门电路

图2.2.1 (a) 电路图; (b) 伏安特性曲线

第2章 逻辑门电路

二极管导通时的电阻叫正向电阻, 其值很小, 一般在几 欧至几百欧之间。 因此, 二极管导通时,如同一个具有0.7 V压降而电阻很小的闭合开关, 如图2.2.2为二极管正向导通 时的等效电路。 在数字电路分析中经常采用简化分析的方法, 往往忽略0.7 V压降和正向电阻。

第2章 逻辑门电路

模拟信号一般通过PCM(Pulse Code Modulation)脉码调 制方法量化为数字信号, 即让模拟信号的不同幅度分别对应 不同的二进制值, 例如采用8位编码可将模拟信号量化为 28=256个量级, 实用中常采取24位或30位编码。 数字信号一 般通过对载波进行移相(Phase Shift)的方法转换为模拟信号。 计算机、 计算机局域网与城域网中均使用二进制数字信号, 目前在计算机广域网中实际传送的则既有二进制数字信号,也 有由数字信号转换而得的模拟信号。

脉冲宽度tw占整个周期T的百分数,

第2章 逻辑门电路 图2.1.2 实际的矩形脉冲

第2章 逻辑门电路

一、 1. 什么是数字信号? 什么是模拟信号? 在我们所学 过的各种信号中哪些是数字信号, 2. 脉冲信号除了有矩形脉冲和尖脉冲外, 还有哪些

3. 脉冲信号的占空比是否都是1∶2的, 有没有其他比 例的脉冲信号?

第2章 逻辑门电路 图2.2.3 二极管截止时的等效电路

第2章 逻辑门电路

2. 工作在开关状态的二极管除了有导通和截止两种稳定状态 外, 还要在导通和截止之间转换, 这个转换的过程称为二极 管动态过程(或过渡过程)。 当输入电压波形如图2.2.4(a) 时, 理想开关的输出电流波形如图2.2.4(b)所示, 实际 的输出波形如图2.2.4(c)所示。

数字电子技术基础第二章重点(最新版)

逻辑门电路

2.2 半导体二极管和三极管的开关特性

2.2.1 二极管开关特性

Vcc

利用二极管的单向导电

性,此电路相当于一个受外

R

加电压极性控制的开关。

D

uI

uo

二极管开关电路

假定:UIH=VCC ,UIL=0 当uI=UIH时,D截止,uo=VCC=UOH 当uI=UIL时,D导通,uO=0.7=UOL

在数字系统的逻辑设计中,若采用NPN晶体管 和NMOS管,电源电压是正值,一般采用正逻辑。 若采用的是PNP管和PMOS管,电源电压为负值, 则采用负逻辑比较方便。 今后除非特别说明,一律采用正逻辑。

EXIT

逻辑门电路

2.1 概述

二、获得高低电平的方法及高电平和低电平的含义

获得高、低电平的基本原理

--- 开关断开 --- 开关闭合

EXIT

逻辑门电路

2.2.2半导体三极管的开关特性 一、三极管的开关作用及其条件

iC 临界饱和线 放大区

uI=UIL

+ uBE

三怎极样管控为制什它么饱和I的能C(sMa开用t) T和作关开S ?关?Q

-

区

O UCE(sat)

三极管关断的条件和等效电路

当输入 uI 为低电平,使 uBE < Uth时,三极管截止。

一、电路结构

输入级主要由三极管 T1 、基极电

阻 R1 和钳位二极管D1组成。

D1 为输入钳位二极管输,出用级以抑制

V1

V输入扰导这2 入时电通不端,压,但出大输抑D1现于入制不V的二端了3工中负极负输作间极管电入V,5级性导压端当由R其V式起干通被的45输和中输构T倒扰电钳负入3V出成、V相。压在极5的3结组推D放,正时性-负2构成0拉、大与常,干.极7,。作信二扰V性上号极,干,输管对

数字电路 完整课件讲解

2.1.4 MOS 管的开关特性

• 在数字集成电路中,一般都 在输入端加上保护电路。如图 在GS间加保护二极管DZ,当静 电压超过一定限度后,二极管 击穿导通,使静电荷泄放保护 氧化层不被击穿。

二、 CMOS 与非门、或非门、与门和或门

2、CMOS门电路的构图原则

①工作管(NMOS)与负载管(PMOS)要成对出现。 同一对NMOS、PMOS管栅极接在一起作为输入端; NMOS管的B极均接地,PMOS管的B极均接电源 ②工作管相串,相应的负载管应相并;工作管相并 相应的负载管相串。 ③工作管先串后并,则负载管应先并后串,工作管 先并后串,则负载管先串后并。 ④工作管相串为“与”,相并为“或”,由工作 管组 与负载管组联接点引出则倒相。

二个概念:

(1)输出高电平电流IOH

• 输出uo为高电平时,CMOS反相 器中,PMOS管T2导通,NMOS管T1 截止。Io从VDD经TP流出,供给负 载 RL 。 • 这时负载RL是向反相器索取电流,所以常常形 象地称之为拉电流负载,并把反相器能够输出的 最大电流IOH,叫带拉电流负载的能力。

(二)CMOS反相器的静态特性 2、输出特性: uo f (i0 )

(二)CMOS反相器的静态特性 1、输入特性: i I f (u I )

• 正常工作电压情况下,由于MOS 管输入电阻很高,iI≈0;

• 当uI>VDD+uDF时,保护二极管

D3导通,电流急剧增加; 当uI< - uDF时,D1导通,i1经D1、

RS流出,见P96图2.3.3(c)

(二)CMOS反相器的静态特性 2、输出特性: uo f (i0 )

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

T 2

D2 D 3

R1 4.7kΩ

+VCC ( + 5V ) Rb1

+VCC ( +5V) R b1

A B C

N N N

P P P

P

N

1

3

A B C

T1

TTL与非门的基本结构

+V CC ( +5V ) Rc 2 R b1 4kΩ

1

1.6kΩ Vc 2

1

Rc 4 130Ω

3

T 24

D

3 3 1

A B C

Vi

& G2

Vo

G1

Vi

“1”

2.4V

高电平电压 的范围

3.6V

3.6V

输出“1”

2.4V

VOH(min) V NH VON VOFF

输入“1”

2V

0.4V 0V

“0”

低电平电压 的范围

0.4V 0V

V OL(max)VNL 输出“0”

0.8V

输入“0”

0V

低电平噪声容限 高电平噪声容限

VNL=VOFF-VOL(max)=0.8V-0.4V=0.4V VNH=VOH(min)-VON=2.4V-2.0V=0.4V

L A B C

Rc 1kΩ

+VCC( + 5V) R 3kΩ

D

A B C

1

P

D

4

D5

3 1

L

T 2

D2 D 3

R1 4.7kΩ

2.2

TTL逻辑门电路

+VCC( +5V ) 1kΩ

3 1

一、TTL与非门的基本结构及工作原理 Rc R

3kΩ 1.TTL与非门的基本结构

D

A B C

1

P

D

4

D5

L

Rc 4 T4

1 3 2 3 3

当负载门的个数增

T3脱离饱和,输出低电

平升高。因此,把允许 灌入输出端的电流定义 为输出低电平电流IOL, 产品规定IOL=16mA。由 此可得出:

+VCC R b1 4K

1 1

+VCC R b1 4K

截止

D

截止 T3

1

输出低电平

3 2

I IL

I IL

I OL = I C3

+V 在工程实践中,有时需要将几个门的输出端并联使用,以实现与 CC ( + 5V ) 逻辑,称为 线与 。普通的TTL门电路不能进行线与。 T4 3

2 为此,专门生产了一种可以进行线与的门电路 ——集电极开路门。 D

产品规定IIL<1.6mA。

(2)输入高电平电流IIH——是指当门电路的输入端接高电

平时,流入输入端的电流。

有两种情况:

①寄生三极管效应:

+VCC +VCC

i B1i B1 R b1R b1 4K 4K 1V 2.1V

1

IIH=βPIB1, βP为寄生三极管的电流放大系数。

②倒置的放大状态: IIH=βiIB1,

N OL

I OL I IL

饱和

NOL称为输出低电平时的扇出系数。

(2)拉电流负载——当驱动门输 出高电平时,电流从驱动门拉出, 流至负载门的输入端。

Rc 4 T4

1 3 2 3 3

拉电流增大时, RC4 上的压降增大,会使输 出高电平降低。因此, 把允许拉出输出端的电 流定义为输出高电平电 流IOH。 产品规定:IOH=0.4mA。 由此可得出:

二、TTL与非门的开关速度

1.TTL与非门提高工作速度的原理

(1)采用多发射极三极管加快了存储电荷的消散过程。

+VCC Rc 2 i B1 1V R b1 4kΩ

1

1.6kΩ

3.6V A B C 0.3V

3

1.4V

1

3

T1 β iB1 0.7V

T2 2

3 1

Vo T3 2

Re 2 1kΩ

( 2 )采用了推拉式输出级,输出阻抗比较小,可迅速

+VCC Rc 2 R b1 4kΩ 3.6V 1.6kΩ Rc 4 130Ω

3 1

5V

3

综合上述两种情况, 该电路满足与非的 逻辑功能,即:

导通 T 24

1V

4.3V

D 3 1

1

导通 Vo

L A B C

A B C 0.3V

T1 饱和

T2 2

截止

3 1

3.6V

T3 2 截止

Re 2 1kΩ

E(3.6V,0.3V)

0.4V

D VOFF VON

E Vi (V)

0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0

3.抗干扰能力

TTL门电路的输出高低电平不是一个值,而是一个范围。 同样,它的输入高低电平也有一个范围,即它的输入信号允许一定 的容差,称为噪声容限。

& Vo

Vo

3.6V

3 1 3

A B C V i

T1

T2 2

1

V o (V)

R e2 1K

T3 2

A B C

2.4V

VO H ( m i n ) 2.5

2.0 1.5 1.0

V O L ( m a x0.5 )

0.4V

D

1.0

E

4.0

0.5

V OFF VON

1.5 2.0 2.5 3.0 3.5

V (V) i

2.几个重要参数

3

3 3 1

3 1 3

1

T 24 D

A

T1A

T T2A 2 22B

T1B

B

1

L

3 2T 3

R3

A B

≥1

L=A+B

3.与或非门

+V CC R1A

1

R2

R1B

1

R4

3

3

3 1 3

1

T 24

D

A1 A2

3 1

T1A

T T2A 2B 2 2

T1B

B1 B2

1

L

3 2 T3

R3

4.集电极开路门( OC门)

IIH I IH A 3.6V 3.6V

1

3

T1 T1 C

1.4V 3

βi为倒置放大的电流放大系数。

AB

0.3V

由于βp和βi的值都远小于1, 所以IIH的数值比较小,产品规定:IIH<40uA。

2.带负载能力

(1)灌电流负载——当驱动门输出低 加,灌电流增大,会使 电平时,电流从负载门灌入驱动门。

或逻辑真值表 输 入 B 0 1 0 1 输出 L 0 1 1 1

A B

≥1 L=A+B

A 0 0 1 1

二、三极管非门电路

+V

CC ( +5V)

RC Rb

3 1 T 2

L

A

1

L=A

A

1

L=A

A

非逻辑真值表 输 0V 5V 入 输 出 输 A 0 1 入 输 出 L 1 0

VA(V)

VL(V)

5V 0V

应的输入电压。即输入低电压的最大值。在产品手册中常

称为输入低电平电压,用VIL(max)表示。产品规定VIL(max) =0.8V。

Vo (V)

4.0 ( 4 ) 开门电平电压 VON—— 是指输出电压下降到 VOL A B ( max ) 时对 A(0V,3.6V) 3.5 B(0.6V,3.6V) 应的输入电压。即输入高电压的最小值。在产品手册中常 3.0 C(1.3V,2.48V) 称为输入高电平电压,用VIH 表示。产品规定 VIH(min) 2.4V C ( min ) V 2.5 OH( min) D(1.4V,0.3V) =2V。 2.0 1.5 1.0 0.5 0.4V V OL( max) D E (5)阈值电压Vth——电压传输特性的过渡区所对应的输入电压, Vo (V) Vi (V) 1.0 0.5 1.5 2.0 2.5 3.0 即决定电路截止和导通的分界线,也是决定输出高、低电 3.5 4.0 VOFF VON 4.0 压的分界线。 A B A(0V,3.6V) 3.5 B(0.6V,3.6V) 近似地:Vth≈VOFF ≈VON 3.0 C(1.3V,2.48V) 2.4V C VOH( min) 2.5 即Vi<Vth,与非门关门,输出高电平; D(1.4V,0.3V) 2.0 Vi>Vth,与非门开门,输出低电平。 E(3.6V,0.3V) 1.5 Vth又常被形象化地称为门槛电压 1.0 。 Vth的值为 1.3V~ 1. 4 V。 0.5 V OL( max)

+VCC R b1 4K

1 1

+VCC R b1 4K

导通

D

导通 T3

1

I OH = I E4

3输出高电平 2

I IH

I IH

截止

N OH

I OH I IH

NOH称为输出高电平时的扇出系数。

一般 NOL≠NOH ,常取两者中的较小值作为门电路的 扇出系数,用NO表示。

五、TTL与非门举例——7400

二极管与门和或门电路的缺点:

(1)在多个门串接使用时,会出现低电平偏离标准数值

的情况。

(2)负载能力差。

+VCC ( + 5V ) R 3kΩ

D 1 D

+VCC ( + 5V ) R 3kΩ

0V 5V

D2

p 5V

1