晶体时钟振荡器的选择

有关晶振的知识详解

晶振的工作原理是什么? [标签:电子资料]石英晶体若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应,晶振就是根据压电效应研制而成。

如果在晶片的两极上加交变电压,晶片就会产生机械振动,同时晶片的机械振动又会产生交变电场。

在一般情况下,晶片机械振动的振幅和交变电场的振幅非常微小,但当外加交变电压的频率为某一特定值时,振幅明显加大,比其他频率下的振幅大得多,这种现象称为压电谐振,它与LC回路的谐振现象十分相似。

它的谐振频率与晶片的切割方式、几何形状、尺寸等有关。

提问者:bangbanghoutai浏览次数:1539 提问时间:2007-12-08 15:55姓名:帮帮笔名:bangbanghoutai等级:副连长 (三级)回答数: 6395 次通过率: 43.47%主营行业:精细化学品公司:擅长领域:阿里旺旺雅虎实战案例答案收藏答案收藏答案分享给好友最新回答者:woyige等级:列兵 (一级)回答的其他贡献者:woyige>>目录∙1、石英晶体振荡器的结构∙2、压电效应∙3、符号和等效电路∙4、谐振频率∙5、石英晶体振荡器类型特点∙6、石英晶体振荡器的主要参数∙7、石英晶体振荡器的发展趋势∙8、石英晶体振荡器的应用1、石英晶体振荡器的结构编辑本段石英晶体振荡器是利用石英晶体(二氧化硅的结晶体)的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片(简称为晶片,它可以是正方形、矩形或圆形等),在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了石英晶体谐振器,简称为石英晶体或晶体、晶振。

其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。

下图是一种金属外壳封装的石英晶体结构示意图。

2、压电效应编辑本段若在石英晶体的两个电极上加一电场,晶片就会产生机械变形。

反之,若在晶片的两侧施加机械压力,则在晶片相应的方向上将产生电场,这种物理现象称为压电效应。

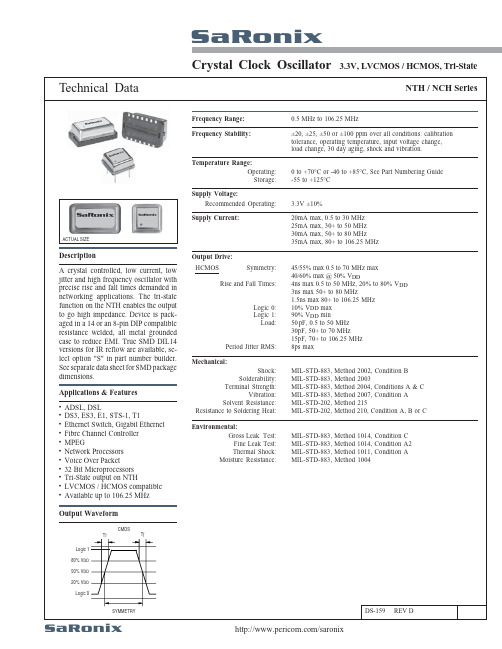

SaRonix NTH NCH Series 晶体时钟振荡器规格书说明书

NTH / NCH SeriesSaRonixCrystal Clock OscillatorTechnical Data3.3V, LVCMOS / HCMOS, Tri-State/saronixDS-159 REV DSymmetry:Rise and Fall Times:Logic 0:Logic 1:Load:Period Jitter RMS:0.5 MHz to 106.25 MHzFrequency Stability:Frequency Range:±20, ±25, ±50 or ±100 ppm over all conditions: calibrationtolerance, operating temperature, input voltage change,load change, 30 day aging, shock and vibration.Temperature Range:Operating:Storage:0 to +70°C or -40 to +85°C, See Part Numbering Guide-55 to +125°CSupply Voltage:Recommended Operating: 3.3V ±10%Supply Current:20mA max, 0.5 to 30 MHz25mA max, 30+ to 50 MHz30mA max, 50+ to 80 MHz35mA max, 80+ to 106.25 MHzACTUAL SIZEDescriptionA crystal controlled, low current, lowjitter and high frequency oscillator withprecise rise and fall times demanded innetworking applications. The tri-statefunction on the NTH enables the outputto go high impedance. Device is pack-aged in a 14 or an 8-pin DIP compatibleresistance welded, all metal groundedcase to reduce EMI. True SMD DIL14versions for IR reflow are available, se-lect option "S" in part number builder.See separate data sheet for SMD packagedimensions.Output Drive:45/55% max 0.5 to 70 MHz max40/60% max @ 50% V DD4ns max 0.5 to 50 MHz, 20% to 80% V DD3ns max 50+ to 80 MHz1.5ns max 80+ to 106.25 MHz10% V DD max90% V DD min50 pF, 0.5 to 50 MHz30pF, 50+ to 70 MHz15pF, 70+ to 106.25 MHz8ps maxHCMOSMechanical:Shock:Solderability:Terminal Strength:Vibration:Solvent Resistance:Resistance to Soldering Heat:MIL-STD-883, Method 2002, Condition BMIL-STD-883, Method 2003MIL-STD-883, Method 2004, Conditions A & CMIL-STD-883, Method 2007, Condition AMIL-STD-202, Method 215MIL-STD-202, Method 210, Condition A, B or CEnvironmental:Gross Leak Test:Fine Leak Test:Thermal Shock:Moisture Resistance:MIL-STD-883, Method 1014, Condition CMIL-STD-883, Method 1014, Condition A2MIL-STD-883, Method 1011, Condition AMIL-STD-883, Method 1004Applications & FeaturesADSL, DSLDS3, ES3, E1, STS-1, T1Ethernet Switch, Gigabit EthernetFibre Channel ControllerMPEGNetwork ProcessorsVoice Over Packet32 Bit MicroprocessorsTri-State output on NTHLVCMOS / HCMOS compatibleAvailable up to 106.25 MHz•••••••••••Output WaveformT r T fCMOSLogic 180% V DD50% V DD20% V DDLogic 0SYMMETRYSaRonixSaRonixSaRonixCrystal Clock Oscillator3.3V, LVCMOS / HCMOS,/saronixSaRonixTrue SMD Adaptor - 7.57mm HighSaRonix /saronix。

晶体Crystal振荡电路原理、分类及设计

晶体Crystal振荡电路原理、分类及设计目录1.文档简介 (3)2.晶体振荡电路的工作原理 (3)2.1石英晶体特性 (3)2.2并联型晶体振荡电路 (4)2.3串联型晶体振荡电路 (6)3.时钟的重要参数 (6)4.晶体振荡器种类 (11)4.1普通晶体振荡器 (11)4.2温度补偿晶体振荡器 (12)4.3恒温晶体振荡器 (14)5.CRYSTAL(晶体)电路设计 (14)5.1晶体电路设计器件说明及选择 (15)5.2PCB布局设计 (16)6.晶体常见问题举例 (16)6.1不起振问题分析与解决 (16)6.2频偏过大 (17)7.总结 (17)附录一相关公式推导一 (18)附录二相关公式推导二 (20)1.文档简介本文主要介绍了晶体振荡电路的工作原理,时钟的重要参数,晶体振荡器的种类,晶体电路设计及晶体常见问题的举例。

2.晶体振荡电路的工作原理晶体(石英晶体)振荡电路主要由主振电路和石英谐振器组成,主振电路将直流能量转换成交流能量,振荡器频率主要取决于石英晶体谐振器。

振荡电路一般采用反馈型电路,按晶体在振荡电路中的作用,又可以分为串联型晶体振荡电路和并联型晶体振荡电路。

本章首先介绍石英晶体的特性,然后分别介绍并联型晶体振荡电路和串联型晶体振荡电路的结构及工作原理。

2.1石英晶体特性晶体(石英晶体)之所以能作为振荡器产生时钟,是基于它的压电效应:所谓的压电效应是指电和力的相互转化,即,如果在晶体的两端施加压缩或拉伸的力,晶体的两端会产生电压信号;同样的,在晶体的两端施加电压信号,晶体会产生形变。

而且这种转化在某特定的频率上效率最高,此频率(由晶片的尺寸和形状决定)即为晶体的谐振频率。

实际应用的晶片是由石英晶体按一定的方向切割而成的,晶片的形状可以各种各样,如方形、矩形或圆形等。

由于晶体的物理性质存在各向差异性,相同的晶体按不同晶格方向切下的晶片,会产生不同的物理特性。

因此,晶体的切割方法是非常重要的,对石英晶体来说,有AT/BT/DT/GT/IT/RT/FC/SC等不同的切法,要根据具体的需求选择相应的切法切割晶片,其中最常用的有AT切和SC切。

晶体振荡原理

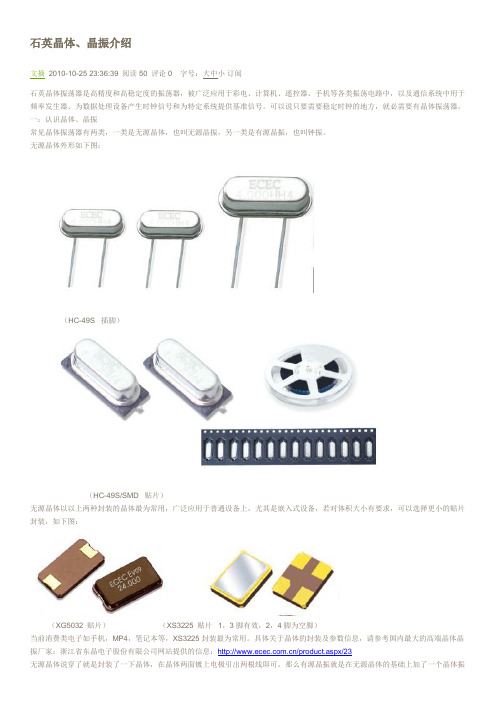

石英晶体、晶振介绍文摘2010-10-25 23:36:39 阅读50 评论0 字号:大中小订阅石英晶体振荡器是高精度和高稳定度的振荡器,被广泛应用于彩电、计算机、遥控器、手机等各类振荡电路中,以及通信系统中用于频率发生器、为数据处理设备产生时钟信号和为特定系统提供基准信号。

可以说只要需要稳定时钟的地方,就必需要有晶体振荡器。

一:认识晶体、晶振常见晶体振荡器有两类,一类是无源晶体,也叫无源晶振,另一类是有源晶振,也叫钟振。

无源晶体外形如下图:(HC-49S 插脚)(HC-49S/SMD 贴片)无源晶体以以上两种封装的晶体最为常用,广泛应用于普通设备上,尤其是嵌入式设备,若对体积大小有要求,可以选择更小的贴片封装,如下图:(XG5032 贴片)(XS3225 贴片1,3脚有效,2,4脚为空脚)当前消费类电子如手机,MP4,笔记本等,XS3225封装最为常用。

具体关于晶体的封装及参数信息,请参考国内最大的高端晶体晶振厂家:浙江省东晶电子股份有限公司网站提供的信息:/product.aspx/23无源晶体说穿了就是封装了一下晶体,在晶体两面镀上电极引出两根线即可,那么有源晶振就是在无源晶体的基础上加了一个晶体振荡电路,,比如采用一个74HC04或者54HC04之类的非门与晶体勾通三点式电容振荡电路,所以它具有电源,地,时钟输出三个脚,有些还会增加一个脚,就是晶振工作控制脚,当不需要工作的时候,可以关掉晶振降低功耗。

如下图:(OS3225 与XS3225外形一样,只是脚位定义不同1:EN控制脚,2:GND地,3:OUT信号输出,4:VCC电源,一般为3.3V 或者5V)。

晶振内部振荡电路等效图如下:非门5404的输出脚2就是信号输出脚。

二:晶体振荡电路原理分析(本篇由东晶电子网上独家代理创易电子提供技术文档)我们以最常见得MCU振荡电路为例,参考电路如下:很多人做MCU51单片机得时候,不明白晶体两边为什么要加两个电容,大小一般在15pF~33pF之间,有些特殊的,还需要在晶体上并联一个大电阻,一般老师的解释是提高晶体振荡电路的稳定性,有助于起振,而对于其根本原理没有解释。

单片机晶振频率

单片机晶振频率一、晶振频率的概念及作用晶振频率是指晶体振荡器的震荡频率,也就是单片机内部时钟的频率。

在单片机中,晶振频率起到了非常重要的作用。

它决定了单片机内部时钟的频率,从而影响了单片机的运行速度和精度。

因此,选择合适的晶振频率非常重要。

二、常见的晶振频率目前,市面上常见的晶振频率有4MHz、8MHz、16MHz等。

其中,4MHz和8MHz适用于一些低功耗应用场合,而16MHz则适用于一些高速运算场合。

当然,在一些特殊场合下也会使用其他频率的晶振。

三、如何选择合适的晶振频率1. 根据单片机型号选择不同型号的单片机支持不同范围内的晶振频率。

因此,在选择晶振时需要根据具体型号来确定可选范围。

2. 根据应用场景选择在实际应用中,需要根据具体应用场景来选择合适的晶振频率。

如果需要实现高速计算或者数据传输等操作,则需要使用较高频率的晶振;而如果需要实现低功耗应用,则可以选择较低频率的晶振。

3. 考虑外设设备在一些需要与外设设备进行通信的应用中,需要根据外设设备的要求来选择晶振频率。

例如,如果外设设备要求使用特定的时钟频率进行通信,则需要选择与之匹配的晶振频率。

四、晶振频率与系统时钟频率在单片机中,晶振频率和系统时钟频率是两个不同的概念。

晶振频率是指晶体振荡器震荡的频率,而系统时钟频率则是由单片机内部时钟分频器控制的。

因此,在选择晶振时需要考虑到系统时钟分频系数等因素。

五、常见问题及解决方法1. 晶振不工作可能原因:电路连接不良、晶体损坏、电源电压不稳定等。

解决方法:检查电路连接是否正确、更换新的晶体、检查电源是否稳定等。

2. 晶振工作不稳定可能原因:温度变化、电源波动等。

解决方法:加装温度补偿电路或者使用温度补偿型晶体;使用稳定可靠的电源等。

3. 晶振频率偏差过大可能原因:晶体参数不匹配、电容不匹配等。

解决方法:更换频率相近的晶体、更换合适的电容等。

六、总结在单片机应用中,选择合适的晶振频率非常重要。

需要根据单片机型号、应用场景、外设设备要求等因素来选择合适的晶振频率。

石英晶体振荡器原理

石英晶体振荡器原理石英晶体振荡器是利用石英晶体(二氧化硅的结晶体)的压电效应制成的一种谐振器件,它的基本构成大致是:从一块石英晶体上按一定方位角切下薄片(简称为晶片,它可以是正方形、矩形或圆形等),在它的两个对应面上涂敷银层作为电极,在每个电极上各焊一根引线接到管脚上,再加上封装外壳就构成了石英晶体谐振器,简称为石英晶体或晶体、晶振。

其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。

1.晶振概述晶振一般指晶体振荡器。

晶体振荡器BAV99-7是指从一块石英晶体上按一定方位角切下薄片(简称为晶片),石英晶体谐振器,简称为石英晶体或晶体、晶振;并添加到包装内部IC形成振荡电路的晶体元件称为晶体振荡器。

其产品一般用金属壳包装,也用玻璃壳包装.陶瓷或塑料包装。

2.晶振的工作原理石英晶体振荡器是一种由石英晶体压电效应制成的谐振器件。

其基本组成大致如下:从石英晶体上按一定方向角切下薄片,在两个对应面涂上银层作为电极,在每个电极上焊接一根导线,连接到管脚上。

此外,封装外壳构成石英晶体谐振器,简称石英晶体或晶体.晶体振动。

其产品一般用金属外壳包装,也有玻璃外壳.陶瓷或塑料包装。

如果在石英晶体的两个电极上增加一个电场,晶片就会发生机械变形。

相反,如果在晶片两侧施加机械压力,就会在晶片的相应方向产生电场,这种物理现象称为压电效应。

如果在晶片的两极上增加交变电压,晶片会产生机械振动,晶片的机械振动会产生交变电场。

一般来说,晶片机械振动的振幅和交变电场的振幅非常小,但当外部交变电压的频率为特定值时,振幅明显增远大于其他频率,称为压电谐振,与1C电路的谐振现象非常相似。

其谐振频率与晶片切割方法相似。

.几何形状.尺寸等相关。

晶体不振动时,可视为平板电容器,称为静电电容器C,晶片的大小和几何尺寸.与电极面积有关,一般几种皮法到几十种皮法。

当晶体振荡时,机械振动的惯性可以与电感1相等。

一般1值为几十豪亨到几百豪亨。

电容C可以等效晶片的弹性,C值很小,一般只有O.0002~0.1皮法。

石英晶体器件选用指南

石英晶体器件选用指南厦华电子研发中心 薛 元为了进一步降低开发成本、促进设计标准化以及便于公司物料管理,特编写此指南,以便各位设计师在后续的新品开发中选择适合产品的石英晶体器件。

1概述石英晶体器件是现代电子元器件领域应用最广泛的基础元件之一,可广泛用于各种电子技术应用方面。

它是用压电单晶石英(即水晶)制成的压电器件,不仅具有高度稳定的物理化学性能,而且弹性振动损耗极小。

与其它电子器件相比,压电石英晶体还有着很高的频率稳定度和高Q值(高达数百万),其主要原材料人造石英水晶的价格又较低,这些十分突出的优点,使其成为稳定频率和选择频率的重要器件。

我司目前主要使用的石英晶体器件主要包括了石英晶体谐振器(Quartz Crystal Resonator)和石英晶体振荡器(Quartz Crystal Oscillator)。

2工作原理2.1压电效应若在石英晶片上施加机械压力,则在晶片相应的方向上会产生一定的电场,这种物理现象称为压电效应。

反之,若在石英晶片两极加一电场,晶片会产生机械变形,继而产生频率振荡,这就是逆压电效应。

晶振和钟振就是采用其逆压电效应制成的。

一般情况下,无论是机械振动的振幅,还是交变电场的振幅都非常小。

但是,当交变电场的频率为某一特定值时,振幅骤然增大,产生共振,称之为压电振荡。

这一特定频率就是石英晶体的固有频率,也称谐振频率。

因石英晶片在石英材料中的方位不同,电场设置不同,会产生不同的振动模式,有长度伸缩振动,弯曲振动,面切变振动和厚度切变振动。

在实际使用过程中,从适用频率范围、压电活力、频率温度特性以及加工难易程度等方面综合考虑,一般采用AT切型的厚度振动模式,BT切型厚度振动模式以及DT切型面切变振动模式,X+5°切型长度伸缩振动模式。

2.2等效电路作为一个电气元件,晶体是由一选定的晶片,连同在石英上形成电场能够导电的电极及防护壳罩和内部支架装置所组成,其等效电路如图1所示。

晶体振荡器 MEMS振荡器

晶振的缺点

受石英晶体自身的特性限制,比较脆弱,抗 震性能差; 由于切割尺寸难以继续缩小,频率难以继续 提高; 受封装限制,体积、价格难以继续降低。

石英晶体振荡器市场规模TAM

据统计报道,目前全球石英晶体振荡器市场年 规模约为30亿美元,每年生产90亿颗石英晶体 振荡器,应用涉及汽车、电视、摄像机、个人 电脑、便携式设备等等几乎一切电子设备。

石英晶体的等效电路

影响振荡器工作的环境因素

影响振荡器工作的环境因素有:电磁干扰 (EMI)、机械震动与冲击、温度和湿度。这些 因素会增大输出频率的变化,增加不稳定性, 并且在有些情况下,还会造成振荡器停振。 所以,晶振的封装很讲究,金属、陶瓷外壳 起屏蔽和机械稳定作用。

无源晶振和有源晶振

市场上晶体振荡器分为无源有源晶振两种类型。无源晶 振与有源晶振(谐振)的英文名称不同,无源晶振为 crystal(晶体),而有源晶振则叫做oscillator(振荡 器)。无源晶振实际上是一颗石英晶体,需要借助于时 钟电路才能产生振荡信号,自身无法振荡起来,所以 “无源晶振”这个说法并不准确;有源晶振--振荡器模 块,才是一个完整的振荡器。 振荡器的性能受环境条件和电路元件选择的影响较大。 需认真对待振荡器电路的元件选择和线路板布局。相比 之下,有源晶振(钟振)更加稳定,工程应用更加方便。

MEMS 振荡器结构原理

MEMS谐振器是采用深度离子蚀刻技术在晶圆 上生成极细小且坚硬的机械结构,从而制成 谐振器。 MEMS 振荡器由下面部分组成

雕刻在硅片上面的谐振腔体 真空密封Cap 振荡器、PLL ASIC电路 封装

Build a MEMS Oscillator

1) Resonator

2) Packaged Resonator

晶振知识大普及

晶振术语解释1、晶振:即所谓石英晶体谐振器和石英晶体时钟振荡器的统称。

不过由于在消费类电子产品中,谐振器用的更多,所以一般的概念中把晶振就等同于谐振器理解了。

后者就是通常所指钟振。

2、分类。

首先说一下谐振器。

谐振器一般分为插件(Dip)和贴片(SMD)。

插件中又分为HC-49U、HC-49U/S、音叉型(圆柱)。

HC-49U一般称49U,有些采购俗称“高型”,而HC-49U/S一般称49S,俗称“矮型”。

音叉型按照体积分可分为3*8,2*6,1*5,1*4等等。

贴片型是按大小和脚位来分类。

例如7*5(0705)、6*3.5(0603),5*3.2(5032)等等。

脚位有4pin和2pin之分。

而振荡器也是可以分为插件和贴片。

插件的可以按大小和脚位来分。

例如所谓全尺寸的,又称长方形或者14pin,半尺寸的又称为正方形或者8pin。

不过要注意的是,这里的14pin和8pin都是指振荡器内部核心IC的脚位数,振荡器本身是4pin。

而从不同的应用层面来分,又可分为OSC(普通钟振),TCXO(温度补偿),VCXO(压控),OCXO(恒温)等等。

3、基本术语。

我想这也是很多采购同学比较模糊的地方。

这里我选了一些常用的谐振器术语拿来做一下解释。

Frequency Tolerance(调整频差):在规定条件下,在基准温度(25±2℃)与标称频率允许的偏差。

一般用PPm(百万分之)表示。

Frequency Stability(温度频差):指在规定的工作温度范围内,与标称频率允许的偏差。

用PPm 表示。

Aging(年老化率):在规定条件下,晶体工作频率随时间而允许的相对变化。

以年为时间单位衡量时称为年老化率。

Shunt Capacitance(静电容):等效电路中与串联臂并接的电容,也叫并电容,通常用C0表示。

Load Capacitance(负载电容):与晶体一起决定负载谐振频率fL的有效外界电容,通常用CL表示。

ds1302中文资料

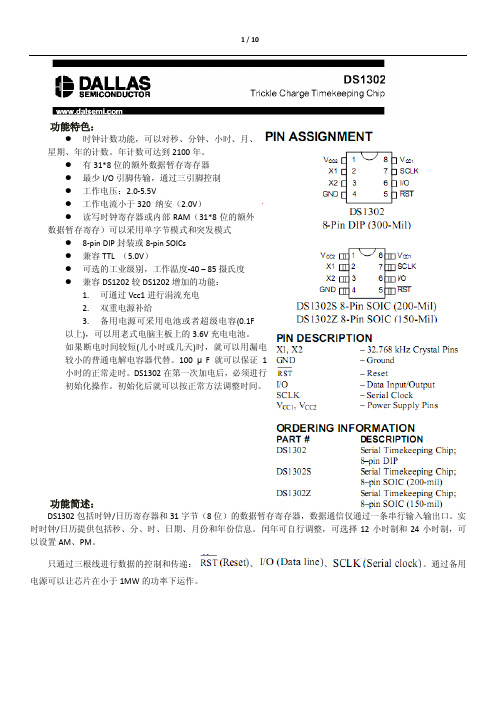

功能特色:●时钟计数功能,可以对秒、分钟、小时、月、星期、年的计数。

年计数可达到2100年。

●有31*8位的额外数据暂存寄存器●最少I/O引脚传输,通过三引脚控制●工作电压:2.0-5.5V●工作电流小于320 纳安(2.0V)●读写时钟寄存器或内部RAM(31*8位的额外数据暂存寄存)可以采用单字节模式和突发模式●8-pin DIP封装或8-pin SOICs●兼容TTL (5.0V)●可选的工业级别,工作温度-40 – 85摄氏度●兼容DS1202较DS1202增加的功能:1.可通过Vcc1进行涓流充电2.双重电源补给3.备用电源可采用电池或者超级电容(0.1F以上),可以用老式电脑主板上的3.6V充电电池。

如果断电时间较短(几小时或几天)时,就可以用漏电较小的普通电解电容器代替。

100 μF就可以保证1小时的正常走时。

DS1302在第一次加电后,必须进行初始化操作。

初始化后就可以按正常方法调整时间。

功能简述:DS1302包括时钟/日历寄存器和31字节(8位)的数据暂存寄存器,数据通信仅通过一条串行输入输出口。

实时时钟/日历提供包括秒、分、时、日期、月份和年份信息。

闰年可自行调整,可选择12小时制和24小时制,可以设置AM、PM。

只通过三根线进行数据的控制和传递:、、。

通过备用电源可以让芯片在小于1MW的功率下运作。

工作过程:主要工作原理图如Figure 1 所示:移位寄存器,控制逻辑,晶振,时钟和RAM 。

在进行任何数据传输时,必须被制高电平(注意虽然将它置为高电平,内部时钟还是在晶振作用下走时的,此时,允许外部读写数据),在每个SCLK 上升沿时数据被输入,下降沿时数据被输出,一次只能读写一位,适度还是写需要通过串行输入控制指令来实现(也是一个字节),通过8个脉冲便可读取一个字节从而实现串行输入与输出。

最初通过8个时钟周期载入控制字节到移位寄存器。

如果控制指令选择的是单字节模式,连续的8个时钟脉冲可以进行8位数据的写和8位数据的读操作,SCLK 时钟的上升沿时,数据被写入DS1302,SCLK 脉冲的下降沿读出DS1302的数据。

石英晶体多谐振荡器的振荡频率

石英晶体多谐振荡器的振荡频率1. 引言石英晶体多谐振荡器是一种常见的电子元器件,广泛应用于通信、计算机、电子设备等领域。

其主要功能是产生稳定的振荡信号,用于时钟同步、频率调节等应用。

本文将介绍石英晶体多谐振荡器的原理、结构和振荡频率的相关知识。

2. 石英晶体多谐振荡器的原理石英晶体多谐振荡器的工作原理基于石英晶体的压电效应。

石英晶体是一种具有压电性质的晶体材料,当施加外力或电场时,会产生电荷分布的变化,从而产生电势差。

利用这种压电效应,可以将石英晶体作为振荡器的振荡元件。

石英晶体多谐振荡器通常由石英晶体片、电容和电感组成。

石英晶体片被切割成特定的尺寸和方向,使其在特定频率下具有谐振特性。

电容和电感用于调节振荡电路的频率和稳定性。

3. 石英晶体多谐振荡器的结构石英晶体多谐振荡器的结构相对简单,主要包括石英晶体片、电容和电感等元件。

3.1 石英晶体片石英晶体片是石英晶体多谐振荡器的核心部件。

它通常采用石英晶体材料,通过特殊的切割和加工工艺制成。

石英晶体片的尺寸和方向决定了振荡器的谐振频率,因此选择合适的石英晶体片非常重要。

3.2 电容和电感电容和电感用于调节石英晶体多谐振荡器的频率和稳定性。

电容可通过改变电容值来调节振荡器的频率,而电感则可以提高振荡器的稳定性。

4. 石英晶体多谐振荡器的振荡频率计算石英晶体多谐振荡器的振荡频率可以通过以下公式计算:频率= 1 / (2 * π * √(L * C))其中,L为电感的值,C为电容的值。

这个公式表明,振荡频率与电感和电容的乘积成反比,因此可以通过调节电感和电容的值来改变振荡频率。

5. 石英晶体多谐振荡器的应用石英晶体多谐振荡器具有稳定、精准的特点,因此在许多领域都有广泛的应用。

5.1 时钟同步石英晶体多谐振荡器被广泛应用于电子设备中的时钟电路,用于提供稳定的时钟信号。

时钟同步对于电子设备的正常运行非常重要,石英晶体多谐振荡器的高稳定性和精准性确保了时钟信号的准确性。

晶振频率 石英钟

晶振频率石英钟石英钟是一种常见的时钟装置,它的核心部件是晶体振荡器,也就是我们常说的晶振。

晶振频率是指晶振每秒钟振动的次数,单位为赫兹(Hz)。

石英钟中使用的晶振频率通常为32.768kHz。

石英钟的出现可以追溯到20世纪30年代,当时人们对于时钟的精确度要求越来越高。

而传统的机械时钟虽然能够满足日常使用的需求,但是它们的精确度受到机械结构的限制,无法达到更高的精确度要求。

因此,科学家们开始寻找一种更加精确可靠的时钟装置。

晶振作为一种新型的时钟装置应运而生。

它利用了石英晶体的特殊物理性质,将电能转换为机械振动,从而产生稳定的频率信号。

石英晶体是一种具有高度结晶的石英矿石,它能够在电场的作用下产生压电效应,即在外力作用下会产生电荷分离。

利用这种特性,晶振可以在外界施加电场的作用下,产生稳定的振荡频率。

石英晶体的晶格结构决定了晶振的频率。

晶体振荡器通常由一个石英晶体片和两个电极组成。

当施加电压时,石英晶体会产生机械振动,振动的频率取决于晶体的物理尺寸和晶格结构。

通过精确地控制晶体片的尺寸和形状,以及晶格结构的优化设计,可以得到稳定的振荡频率。

石英钟中使用的晶振频率为32.768kHz,这是经过精密调校和优化设计的结果。

这个频率之所以被选择,是因为它具有以下几个优点。

首先,32.768kHz是石英晶体的自然振荡频率,因此可以实现最高的振荡效率。

其次,32.768kHz的整数倍频可以方便地与其他电子元件进行配合,实现时钟信号的分频和倍频。

最后,32.768kHz的频率相对较低,能够降低功耗并延长电池寿命。

石英钟中的晶振频率对于时钟的精确度起着关键作用。

晶振的频率越稳定,时钟的精确度越高。

因此,在制造石英钟时,需要对晶振的频率进行精确的控制和校准。

一般来说,制造商会使用专门的测试仪器对晶振频率进行测量,并根据测量结果进行频率校准。

同时,为了进一步提高时钟的精确度,还可以采用温度补偿技术,使得晶振频率在不同温度下保持稳定。

二颗 高精确度、低功耗、小体积32.768Khz 温补晶体振荡器TCXO

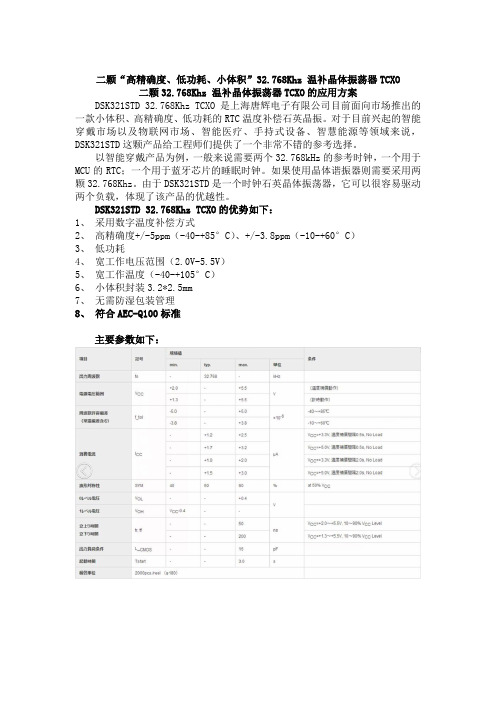

二颗“高精确度、低功耗、小体积”32.768Khz 温补晶体振荡器TCXO 二颗32.768Khz 温补晶体振荡器TCXO的应用方案 DSK321STD 32.768Khz TCXO是上海唐辉电子有限公司目前面向市场推出的一款小体积、高精确度、低功耗的RTC温度补偿石英晶振。

对于目前兴起的智能穿戴市场以及物联网市场、智能医疗、手持式设备、智慧能源等领域来说,DSK321STD这颗产品给工程师们提供了一个非常不错的参考选择。

以智能穿戴产品为例,一般来说需要两个32.768kHz的参考时钟,一个用于MCU的RTC;一个用于蓝牙芯片的睡眠时钟。

如果使用晶体谐振器则需要采用两颗32.768Khz。

由于DSK321STD是一个时钟石英晶体振荡器,它可以很容易驱动两个负载,体现了该产品的优越性。

DSK321STD 32.768Khz TCXO的优势如下:1、采用数字温度补偿方式2、高精确度+/-5ppm(-40-+85°C)、+/-3.8ppm(-10-+60°C)3、低功耗4、宽工作电压范围(2.0V-5.5V)5、宽工作温度(-40-+105°C)6、小体积封装3.2*2.5mm7、无需防湿包装管理8、符合AEC-Q100标准主要参数如下:DSK321STD 32.768Khz实物图:DSK321STD 32.768Khz温度曲线图:DSK321STD 32.768Khz TCXO从2013年底问世以来,在唐辉电子的大力推广之下,目前已经有诸多典型的应用案例,与一些知名品牌的MCU匹配使用:1、德州仪器TI的 MSP430系列2、意法STmicro的STM32系列3、日本瑞萨Renesas的RL78系列4、 Microchip额PIC18/MCP794xx系列5、 Energy Micro的EFG32系列6、 Fujitsu的MB89xx/MB951xx系列7、 NXPDE LPC11xx系列8、 Freescale的L4x/L5x系列第二颗32.768Khz简介如下。

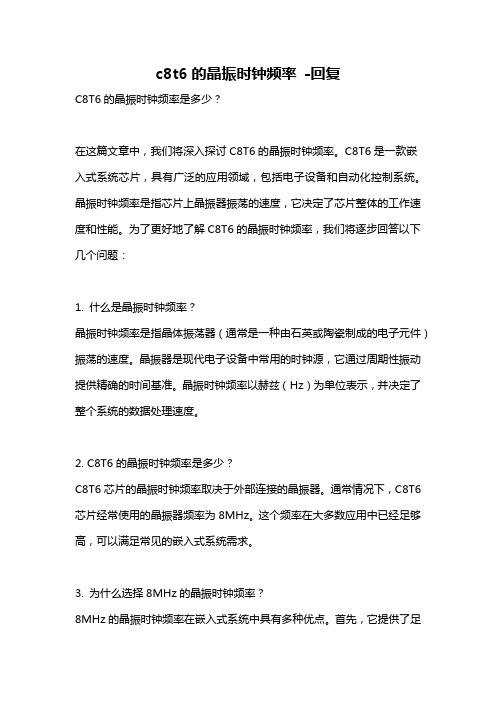

c8t6的晶振时钟频率 -回复

c8t6的晶振时钟频率-回复C8T6的晶振时钟频率是多少?在这篇文章中,我们将深入探讨C8T6的晶振时钟频率。

C8T6是一款嵌入式系统芯片,具有广泛的应用领域,包括电子设备和自动化控制系统。

晶振时钟频率是指芯片上晶振器振荡的速度,它决定了芯片整体的工作速度和性能。

为了更好地了解C8T6的晶振时钟频率,我们将逐步回答以下几个问题:1. 什么是晶振时钟频率?晶振时钟频率是指晶体振荡器(通常是一种由石英或陶瓷制成的电子元件)振荡的速度。

晶振器是现代电子设备中常用的时钟源,它通过周期性振动提供精确的时间基准。

晶振时钟频率以赫兹(Hz)为单位表示,并决定了整个系统的数据处理速度。

2. C8T6的晶振时钟频率是多少?C8T6芯片的晶振时钟频率取决于外部连接的晶振器。

通常情况下,C8T6芯片经常使用的晶振器频率为8MHz。

这个频率在大多数应用中已经足够高,可以满足常见的嵌入式系统需求。

3. 为什么选择8MHz的晶振时钟频率?8MHz的晶振时钟频率在嵌入式系统中具有多种优点。

首先,它提供了足够高的速度,可以满足大多数常见应用的需求。

其次,8MHz是一个相对常见的频率,易于获取和使用。

此外,8MHz的频率在功耗和成本方面也表现出良好的平衡。

因此,8MHz的晶振时钟频率成为了C8T6芯片的主要选择。

4. 是否可以使用其他频率的晶振器?是的,在某些特定的应用中,也可以选择其他频率的晶振器。

根据具体需求,C8T6芯片支持各种不同的晶振时钟频率。

通过更换晶振器,可以实现不同的速度和性能要求。

然而,需要注意的是,在更换晶振器时,可能需要调整其他相关电路,以确保系统的稳定性和兼容性。

5. 如何确认C8T6芯片的晶振时钟频率?要确认C8T6芯片的晶振时钟频率,可以通过以下几种方法之一进行验证。

首先,可以查看C8T6的数据手册或技术规格书,其中通常会明确列出晶振器的推荐频率。

其次,可以查看C8T6开发板或原始设计文档中是否提供了相关信息。

单片机内部时钟受温度影响规律

单片机内部时钟受温度影响规律

单片机内部时钟受温度影响是一个非常重要的问题,因为温度

变化会对时钟频率产生影响,进而影响整个系统的稳定性和性能。

单片机内部时钟通常由晶体振荡器或者RC振荡器提供,这些振荡器

的频率都会随着温度的变化而发生变化。

首先,晶体振荡器的频率会随着温度的变化而发生变化。

晶体

的振荡频率与温度密切相关,一般来说,温度升高会导致晶体的振

荡频率增加,温度降低会导致振荡频率减小。

这是由于晶体的物理

特性在不同温度下会发生变化,从而影响振荡频率。

其次,RC振荡器的频率也会受到温度的影响。

在RC振荡器中,电阻和电容的数值都会随着温度的变化而发生变化,进而影响振荡

器的频率稳定性。

另外,温度变化还会影响单片机内部其他元件的性能,比如晶

体管、电容器等,这些元件的性能变化也会对时钟频率产生影响。

为了解决单片机内部时钟受温度影响的问题,通常可以采取以

下措施,首先,选择温度稳定性好的晶体振荡器和元件,以减小温

度变化对时钟频率的影响;其次,可以在系统中加入温度补偿电路,通过监测温度变化来实时调整时钟频率,以保持系统的稳定性;另外,合理的PCB布局和散热设计也可以减小温度变化对单片机时钟

的影响。

总的来说,单片机内部时钟受温度影响是一个复杂的问题,需

要综合考虑振荡器、元件和系统设计等多个因素,才能有效地解决。

希望以上回答能够对你有所帮助。

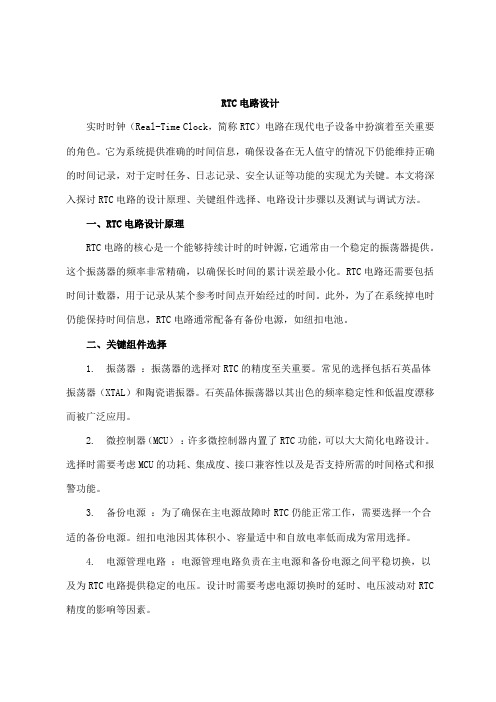

rtc电路设计

RTC电路设计实时时钟(Real-Time Clock,简称RTC)电路在现代电子设备中扮演着至关重要的角色。

它为系统提供准确的时间信息,确保设备在无人值守的情况下仍能维持正确的时间记录,对于定时任务、日志记录、安全认证等功能的实现尤为关键。

本文将深入探讨RTC电路的设计原理、关键组件选择、电路设计步骤以及测试与调试方法。

一、RTC电路设计原理RTC电路的核心是一个能够持续计时的时钟源,它通常由一个稳定的振荡器提供。

这个振荡器的频率非常精确,以确保长时间的累计误差最小化。

RTC电路还需要包括时间计数器,用于记录从某个参考时间点开始经过的时间。

此外,为了在系统掉电时仍能保持时间信息,RTC电路通常配备有备份电源,如纽扣电池。

二、关键组件选择1. 振荡器:振荡器的选择对RTC的精度至关重要。

常见的选择包括石英晶体振荡器(XTAL)和陶瓷谐振器。

石英晶体振荡器以其出色的频率稳定性和低温度漂移而被广泛应用。

2. 微控制器(MCU):许多微控制器内置了RTC功能,可以大大简化电路设计。

选择时需要考虑MCU的功耗、集成度、接口兼容性以及是否支持所需的时间格式和报警功能。

3. 备份电源:为了确保在主电源故障时RTC仍能正常工作,需要选择一个合适的备份电源。

纽扣电池因其体积小、容量适中和自放电率低而成为常用选择。

4. 电源管理电路:电源管理电路负责在主电源和备份电源之间平稳切换,以及为RTC电路提供稳定的电压。

设计时需要考虑电源切换时的延时、电压波动对RTC 精度的影响等因素。

三、电路设计步骤1. 确定需求:明确RTC电路需要满足的精度、功耗、接口等要求。

2. 选择振荡器:根据精度要求和成本考虑选择合适的振荡器类型。

3. 选择MCU :选择一个内置RTC功能且满足其他系统需求的MCU。

4. 设计电源管理电路:确保在主电源故障时能迅速切换到备份电源,并在主电源恢复时平稳切换回主电源供电。

5. 布局与布线:在PCB布局时,要注意将振荡器放置在靠近MCU的位置,以减小信号传输延迟和噪声干扰。

时钟和定时芯片降低抖动提高精度

时钟和定时芯片降低抖动提高精度时钟和定时芯片降低抖动提高精度时钟和定时芯片是现代电子产品中不可或缺的组成部分。

它们在各种应用中都具有重要的作用,如通信设备、计算机、汽车电子以及工业自动化等领域。

然而,由于各种因素的干扰,时钟和定时芯片在实际应用中可能会出现抖动问题,从而降低了精度。

本文将讨论抖动的原因以及如何通过各种方法来降低抖动,以提高时钟和定时芯片的精度。

一、抖动的原因抖动是指时钟或定时芯片在其理想频率周围产生的随机时间偏差。

其主要原因包括以下几个方面:1. 外部干扰:时钟和定时芯片可能会受到来自电源波动、信号干扰、温度变化等外部因素的干扰,从而导致抖动。

2. 设计缺陷:在时钟和定时芯片的设计中,可能存在电路设计不合理、布局问题或者材料质量等方面的缺陷,这些都可能对抖动产生影响。

3. 阻尼问题:时钟和定时芯片内部的振荡器可能存在阻尼不足的问题,从而导致抖动的产生。

4. 时钟信号传输问题:当时钟信号被传输到其他电路或系统时,可能会受到传输线路质量、噪声等因素的影响,从而引起抖动。

二、降低抖动的方法为了提高时钟和定时芯片的精度,需要采取相应的措施来降低抖动。

以下是几种常见的方法:1. 选择合适的振荡器:振荡器是时钟和定时芯片的关键组件,选择合适的振荡器对降低抖动至关重要。

一般而言,TCXO(温度补偿型晶体振荡器)和OCXO(精确温度补偿型晶体振荡器)具有较高的精度和稳定性,可用于要求较高精度的领域。

2. 优化电路设计:在时钟和定时芯片的设计过程中,需要注意电路的布局、功耗管理以及环境干扰等因素,优化电路设计可以有效减少抖动问题的发生。

3. 降低干扰影响:通过合理的防护措施,例如添加滤波电容、隔离干扰源等,可以有效降低外部干扰对时钟和定时芯片的抖动影响。

4. 传输线路优化:对于需要传输时钟信号的场景,应注意优化传输线路的设计,减少噪声干扰和信号失真,从而避免抖动问题的产生。

5. 使用校准技术:校准技术可以通过对时钟和定时芯片的输出进行实时校准,从而提高其精度和稳定性。

cpu时钟晶振工作原理

cpu时钟晶振工作原理

CPU时钟晶振是用于提供CPU工作时的基准时钟信号的电子

元件。

其工作原理如下:

1. 晶体振荡器:CPU时钟晶振通常采用石英晶体振荡器,其

中石英晶体作为振荡器的关键部件。

石英晶体具有压电效应,即在外加交变电场的作用下会产生机械振动。

由于晶体的振动频率非常稳定,因此石英晶体广泛应用于时钟电子设备中。

2. 反馈电路:晶振产生的振荡信号经过放大器和反馈电路处理后再次输入到晶振中。

反馈电路会生成一个相位和振幅适合晶振要求的反馈信号,使得晶振能够始终保持稳定的振荡。

3. 振荡频率控制:晶振的振荡频率取决于晶体的物理特性和其周围的电路元件。

为了控制晶振的振荡频率,可以通过调节晶振周围的电容、电感等元件的参数,或者通过改变反馈电路中的元件值。

4. 输出时钟信号:晶振的振荡信号经过整形电路进行处理,使其变成方波信号,同时根据需要可以进行频率分频操作。

最后,处理后的时钟信号送往CPU和其他芯片,作为基准时钟信号

驱动CPU和其他芯片的工作。

总结起来,CPU时钟晶振通过利用石英晶体的振荡特性和反

馈电路的控制,产生稳定的振荡信号,再经过整形和分频处理后,输出为方波时钟信号,为CPU和其他芯片提供工作时的

基准时钟。

时钟振荡器的性能及优缺点

时钟振荡器的性能及优缺点时钟振荡器是利用了晶体的压电效应制造的,当在晶片的两面上加交变电压时,晶片会反复的机械变形而产生振动,而这种机械振动又会反过来产生交变电压。

振荡器就是可以产生一定频率的交变电流信号的电路。

是一种能量转换装置——将直流电能转换为具有一定频率的交流电能。

其构成的电路叫振荡电路。

简单地说就是一个频率源,一般用在锁相环中。

详细说就是一个不需要外信号激励、自身就可以将直流电能转化为交流电能的装置。

一般分为正反馈和负阻型两种。

所谓“振荡”,其涵义就暗指交流,振荡器包含了一个从不振荡到振荡的过程和功能。

能够完成从直流电能到交流电能的转化,这样的装置就可以称为“振荡器”。

原理也很简单,它主要有由电容器和电感器组成的LC回路,通过电场能和磁场能的相互转换产程自由振荡。

要维持振荡还要有具有正反馈的放大电路,LC振荡器又分为变压器耦合式和三点式振荡器,很多应用石英晶体的石英晶体振荡器,还有用集成运放组成的LC振荡器。

由于器件不可能参数完全一致,因此在上电的瞬间两个三极管的状态就发生了变化,这个变化由于正反馈的作用越来越强烈,导致到达一个暂稳态。

暂稳态期间另一个三极管经电容逐步充电后导通或者截止,状态发生翻转,到达另一个暂稳态。

这样周而复始形成振荡。

那么,它和晶体振荡器有什么区别呢?晶体振荡器是指从一块石英晶体上按一定方位角切下薄片(简称为晶片),石英晶体谐振器,简称为石英晶体或晶体、晶振;而在封装内部添加IC组成振荡电路的晶体元件称为晶体振荡器。

其产品一般用金属外壳封装,也有用玻璃壳、陶瓷或塑料封装的。

当外加交变电压的频率为某一特定值时,振幅明显加大,比其它频率下的振幅大得多,产生共振,这种现象称为压电谐振。

晶振产生振荡必须附加外部时钟电路,一般是一个放大反馈电路,只有一片晶振是不能实现震荡的。

于是就有了时钟振荡器,将外部时钟电路跟晶振放在同一个封装里面,一般都有4个引脚了,两条电源线为里面的时钟电路提供电源,又叫做有源晶振,时钟振荡器,或简称钟振。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

晶振的选择

注意某些参数,设计工程师即可选择到适合应用的振荡器

M-tron Industries 公司Bill Jennewein 著

---- 今天无数电子线路和应用需要精确定时或时钟基准信号。

晶体时钟振荡器极为适

合这方面的许多应用。

---- 时钟振荡器有多种封装,它的特点是电气性能规范多种多样。

它有好几种不同的类

型:电压控制晶体振荡器(VCXO)

、恒温箱晶体振荡器

、温度补偿晶体振荡器(TCXO)

(OCXO),以及数字补偿晶体振荡器(DCXO)。

每种类型都有自己的独特性能。

---- 频率稳定性的考虑

---- 晶体振荡器的主要特性之一是工作温度内的稳定性,它是决定振荡器价格的重要因

素。

稳定性愈高或温度范围愈宽,器件的价格亦愈高。

---- 设计工程师要慎密决定对特定应用的实际需要,然后规定振荡器的稳定度。

指标过

高意味着花钱愈多。

---- 对于频率稳定度要求±20ppm 或以上的应用,可使用普通无补偿的晶体振荡器。

对于

成于±1 至±20ppm 的稳定度,应该考虑TCXO。

对于低于±1ppm 的稳定度,应该考虑OC

XO 或DCXO。

---- 输出

---- 必需考虑的其它参数是输出类型、相位噪声、抖动、电压稳定度、负载稳定性、功耗、封。

晶振器可HCMOS/TTL 兼容、ACMOS 兼容、装形式、冲击和振动、以及电磁干扰(EMI)

ECL 和正弦波输出。

每种输出类型都有它的独特波形特性和用途。

应该关注三态或互补输出的

要求。

对称性、上升和下降时间以及逻辑电平对某些应用来说也要作出规定。

许多DSP 和通信芯片组往往需要严格的对称性(45%至55%)和快速的上升和下降时间(小

于5ns)。

---- 相位噪声和抖动

---- 在频域测量获得的相位噪声是短期稳定度的真实量度。

它可测量到中央频率的1Hz

之内和通常测量到1MHz。

---- 振荡器的相位噪声在远离中心频率的频率下有所改善。

TCXO 和OCXO 振荡器以及其

它利用基波或谐波方式的晶体振荡器具有最好的相位噪声性能。

采用锁相环合成器产生输

出频率的振荡器比采用非锁相环技术的振荡器一般呈现较差的相位噪声性能。

---- 抖动与相位噪声相关,但是它在时域下测量。

以微微秒表示的抖动可用有效值或峰

—峰值测出。

许多应用,例如通信网络、无线数据传输、A TM 和SONET 要求必需满足严格

的拌动指标。

需要密切注意在这些系统中应用的振荡器的抖动和相位噪声特性。

---- 电源和负载的影响

---- 振荡器的频率稳定性亦受到振荡器电源电压变动以及振荡器负载变动的影响。

正确选

择振荡器可将这些影响减到最少。

设计者应在建议的电源电压容差和负载下检验振荡器的

性能。

不能期望只能额定驱动15pF 的振荡器在驱动50pF 时会有好的表现。

在超过建议

的电源电压下工作的振荡器亦会呈现坏的波形和稳定性。

---- 对于需要电池供电的器件,一定要考虑功耗。

引入3.3V 的产品必然要开发在3.3V 下

工作的振荡器。

---- 较低的电压允许产品在低功率下运行。

现今大部分市售的表面贴装振荡器在3.3V 下

工作。

许多采用传统5V 器件的穿孔式振荡器正在重新设计,以便在3.3V 下工作。

---- 封装

---- 与其它电子元件相似,时钟振荡器亦采用愈来愈小型的封装。

例如,M-tron 公司的

PDF created with pdfFactory trial version

M3L/M5L 系列表面贴装振荡器现在采用3.2×5.0×1.0mm 的封装。

通常,较小型的器件比

较大型的表面贴装或穿孔封装器件更昂贵。

小型封装往往要在性能、输出选择和频率选

择之间作出折衷。

---- 工作环境

---- 振荡器实际应用的环境需要慎重考虑。

例如,高的振动或冲击水平会给振荡器带来

问题。

---- 除了可能产生物理损坏,振动或冲击可在某些频率下引起错误的动作。

这些外部感

应的扰动会产生频率跳动、增加噪声份量以及间歇性振荡器失效。

---- 对于要求特殊EMI 兼容的应用,EMI 是另一个要优先考虑的问题。

除了采用合适的

P C 母板布局技术,重要的是选择可提供辐射量最小的时钟振荡器。

一般来说,具有较慢上

升/下降时间的振荡器呈现较好的EMI 特性。

---- 对于70MHz 以下的频率,建议使用HCMOS 型的振荡器。

对于更高的频率,可采用ECL

型的振荡器。

ECL 型振荡器通常具有最好的总噪声抑制,甚至在10 至100MHz 的较低频率下

,ECL 型也比其它型的振荡器略胜一筹。

PDF created with pdfFactory trial version 。