AD7705调试注意事项

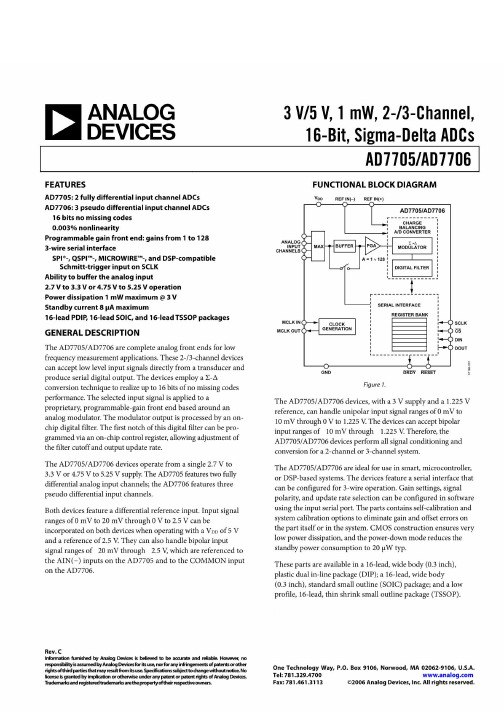

AD7705 及其应用

为此, 我们选用 AD7705 作为模数转换器。AD7705

1 闸位荷重仪的基本原理

在 闸 位 荷 重 仪 中 ,最 基 本 的 测 量 参 数 包 括 开 度 和荷重。闸位编码传感器与闸门启闭机主轴相连, 把闸门的提升高度转换为数字编码后可直接送入微 处 理 器;而 测 量 荷 重 我 们 采 用 压 力 传 感 器 。起 吊 闸 门时,传感器受力,输出电压信号。此信号经 A/D 转换后,由微处理器读入、处理并显示输出,进行 报警控制。图 1所示为闸位荷重仪的原理框图。

在我们的系统中,由于89C51的串行口用于扩展 RS-485 接口。因此,采用另一种方法,即用 89C51的 并行口模拟串行口的时序,完成对 AD7705的操作, 详细的连接方法如图 1 所示。把 89C51 的 P1.7、P1.6、

P1.5、P1.4 分别与 AD7705 的 DIN、SCLK、DOUT、CS

程增益 (具有 1、 2、 4、 8、 16、 32、 64、 128 八种

的 24 位并行输入口完全可以满足不同位数的编码

放 大 倍 数 )、可 编 程 输 出 数 据 更 新 率 及 自 校 准 和 系

器需要 ; 另一片 8255 用作键盘显示接口。

统 校 准 功 能;同 时 具 有 三 线 串 行 接 口 ,与 微 处 理 器

AD7705 是 AD 公司新推出的 16 位 Σ - Δ A/D 转换器。器件包括由缓冲器

图1 闸位荷重仪的原理框图

和 增 益 可 编 程 放 大 器( PGA )组 成 的 前 端来自拟调节电路、Σ - Δ调制器、可编

综 合 考 虑 仪 器 的 功 能 、运 行 环 境 及 经 济 效 益 等

程数字滤波器等部件。能直接将传感器测量到的 2

AD7705输出数据一直是0xffff的问题的解决过程

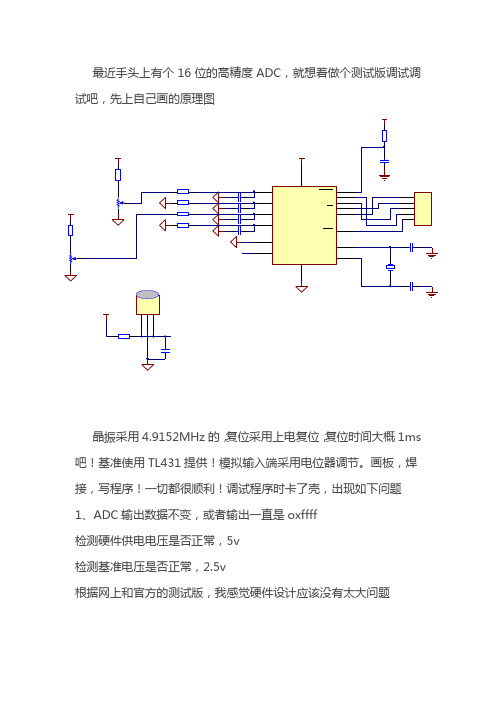

最近手头上有个16位的高精度ADC,就想着做个测试版调试调试吧,先上自己画的原理图晶振采用4.9152MHz的,复位采用上电复位,复位时间大概1ms 吧!基准使用TL431提供!模拟输入端采用电位器调节。

画板,焊接,写程序!一切都很顺利!调试程序时卡了壳,出现如下问题1、ADC输出数据不变,或者输出一直是oxffff检测硬件供电电压是否正常,5v检测基准电压是否正常,2.5v根据网上和官方的测试版,我感觉硬件设计应该没有太大问题那么目标锁定在软件上,首先怀疑的是时序,芯片上有个引脚DRDY,这个引脚变低时有数据输出,我用逻辑分析仪分析自己模拟SPI的时序,发现时序跟手册上的一样,而且DRDY也会置高和变低!根据这个分析这应该不是自己SPI时序的问题了!经过一早上的看手册,查资料,还是没有头绪,不知道哪来的一个念头,是不是芯片复位没有复位好呢?因为我采用的是上电复位,所以我觉得应该观察上电后输出的第一个数据是否正常,别愣着啦,赶紧测试!哇塞。

数据正确!调整电压,第一次上电后数据依然正确,按下单片机复位键,前几次正确,后面又变为0xffff了。

问题找到啦,芯片复位有问题!我改成单片机控制复位,把ADC的复位引脚接到单片机一个引脚上,通过引脚控制ADC复位,复位时间为10ms。

下载程序,上电测试,发现预期连续采集一百个数据,只输出了四五个!复位重来,效果一样,有时候只输出一个数据,庆幸的是数据都正确啦!这个时候没辙啦。

给adi亚太客服打电话。

至今没给回复。

nngt我还是靠自己吧!上网搜索,终于在一篇帖子中见到可能这么一句话“可能每次读AD7705的数据时都要把clock register,setup register 重新设置一遍,复位重来一遍”不管正确与否,试试再说!改程序,下载,看现象,哇塞!一次性输出100个数据,数据正常!可能大家跟我一样吧,怎么会这个样子呢。

我也很郁闷,手册上找不到连续读数据的时序,手册上看不到为什么这么做就数据正确啦!期待ADI工程师给我回复吧!!!不过总算是可以正常运行啦!谢天谢地你好啦!!!欢迎大家进我的空间,有问题可以在我的空间名字上找到我的联系方式/zhangkai0215/item/0c94e099cae3b83d336eeb0d主函数/*********************************************************Auther :zhang kaiDate :April 3, 2013File :main.cHardware :STC89C52Description :AD7705 driver use STC89C52 as MCU*********************************************************/#include <AT89X51.H>#include "AD7705_IO.h"#include "putchar.h"#include "intrins.h"unsigned char buf[4] = {0,0,0,0};void main(void){unsigned char i;InitUart();for(i=0;i<100;i++){CLR_RST();_nop_();SET_RST();CLR_CS();buf[0] = 0x21;WriteToAD7705(1,buf); //write communication register 0x20 to control the progress to write clock registerbuf[0] = 0x0c;WriteToAD7705(1,buf); //write clock register,50Hz update ratebuf[0] = 0x11;WriteToAD7705(1,buf); //write communication register 0x10 to control the progress to write setup registerbuf[0] = 0x44;WriteToAD7705(1,buf); //write setup register,Self-CalibrationAD7705WaitBusy (); //判忙TR1=1;buf[0] = 0x38;WriteToAD7705(1,buf); //write communication register 0x38 to control the progress to read data registerAD7705WaitBusy ();ReadFromAD7705(2,buf); //read data registeputchar(buf[1]);putchar(buf[0]);}SET_CS();while(1);}。

16位_模数转换器AD7705及其校准

16位 模数转换器AD7705及其校准陈勇钢,吴伯农(北方工业大学机电工程学院 北京 100041)摘 要:A D7705是A D 公司推出的16位高性能、低功耗 A /D 转换器,具有增益可编程放大器,可通过编程直接测量传感器输出的微弱信号。

介绍了A D7705的基本特点、结构以及常用片上寄存器的格式与编程注意事项。

自校准和系统校准可消除偏置和增益误差,由于现场条件变化不定,还详细介绍了适用于特定条件的现场校准与手动校准,最后给出了数据手册中没有的手动校准实例。

关键词:A D7705;模/数转换;校准;现场校准;手动校准中图分类号:T P352 文献标识码:B 文章编号:1004373X(2006)0412403Introduction and Calibration of the 16b Sigma Delta A/D Converter AD7705CH EN Y ong gang,WU Bonong(Co llege o f Electrom echanical Eng i neeri ng,No rt h China Universi t y o f T echnolog y,Beij ing,100041,China)Abstract :A D7705is a high per for mance and low pow er 16b Sig ma Delta A /D convert er which is intr oduced by the A D Company.It employ s a P rog rammable Ga in A mplif ier (PG A )and accepts low lev el signals directly fr om a t ransducer.T his paper int roduces its feat ur es and structur e.T he bit desig nations o f the co mmon on chip r egister s ar e outlined as well as the co nsiderations in pr og ramming.Self calibration and sy st em calibr ation on the AD7705remov es offset and g ains er ro rs fr om the dev ice.F iled calibration and manual ca-l ibr atio n ar e discussed ex haustively to deal w ith the uncert ain conditio ns,and an ex ample which can t be found in t he datasheet is presen -ted.Keywords :A D7705;A /D co nv ersion;calibration;field calibration;manua l calibr atio n收稿日期:200509161 AD7705简介AD7705是A D 公司推出的16位 (电荷平衡式)A/D 转换器。

AD7705中文资料_数据手册_参数

关于AD7705的技术文档

关于AD7705模块的技术文档一、模块描述1、简介:D7705/7706 是应用于低频测量的2/3 通道的模拟前端。

该器件可以接受直接来自传感器的低电平的输入信号,然后产生串行的数字输出。

利用Σ-∆转换技术实现了16 位无丢失代码性能。

选定的输入信号被送到一个基于模拟调制器的增益可编程专用前端。

片内数字滤波器处理调制器的输出信号。

通过片内控制寄存器可调节滤波器的截止点和输出更新速率,从而对数字滤波器的第一个陷波进行编程。

2、产品性能参数及特点:�AD7705:2 个全差分输入通道的ADC�AD7706:3 个伪差分输入通道的ADC16位无丢失代码0.003%非线性�可编程增益前端增益:1~128�三线串行接口SPITM、QSPITM、MICROWIRETM和DSP 兼容�有对模拟输入缓冲的能力�2.7~3.3V或4.75~5.25V工作电压� 3V电压时,最大功耗为1mW�等待电流的最大值为8μA�16脚DIP、SOIC和TSSOP封3、产品应用场合:AD7705/7706 是用于智能系统、微控制器系统和基于DSP 系统的理想产品。

其串行接口可配置为三线接口。

增益值、信号极性以及更新速率的选择可用串行输入口由软件来配置。

该器件还包括自校准和系统校准选项,以消除器件本身或系统的增益和偏移误差。

二、模块原理图三、引脚功能四、校准1、自校准过向设置寄存器的MD1和MD0写入相应值(0,1),器件开始自校准。

在单极性输入信号范围内,用来确定校准系数的零标度点是用差分输入对的输入端在器件内部短路(即,对于AD7705,AIN(+)=AIN(-)=内部偏置电压;对于AD7706,AIN=COMMON=内部偏置电压)。

增益可编程放大器(PGA)设置为用于零标度校准转换时选定的增益(由通信寄存器内的G1和G0位设置)。

满标度标准转换是在一个内部产生的VREF电压和选定增益的条件下完成的。

校准持续时间是6×1/输出速率。

AD7705的操作

AD7705的操作我现在使用外部TL431(2.5V基准电压),电源电压为5V,外接晶体振荡器2.4576MHz,电路如下:程序如下:--------------------------AD7705.H -----------------------------------#ifndef _AD7705_H_#define _AD7705_H_// 引脚定义sbit AD7705_SCLK = P2^4;sbit AD7705_DRDY = P2^5;sbit AD7705_DOUT = P2^6;sbit AD7705_DIN = P2^7;// 通讯寄存器地址定义#define WR_SETUP_REG 0x10 //选中设置寄存器,写#define RD_SETUP_REG 0x18 //选中设置寄存器,读#define WR_CLOCK_REG 0x20 //选中时钟寄存器,写#define RD_DATA_REG 0x38 //选中数据寄存器,读#define WR_OFFSET_REG 0x60 //选中offset寄存器,写#define RD_OFFSET_REG 0x68 //选中offset寄存器,读#define WR_FULL_REG 0x70 //选中full scale寄存器,写#define RD_FULL_REG 0x78 //选中full scale寄存器,读#define SYS_ZERO_CALI 0x80 //系统零校准模式#define SYS_FULL_CALI 0xC0 //系统满量程校准模式#define ZERO_CALIBRA TION 0x00 //系统零校准#define FULL_CALIBRA TION 0x01 //系统满量程校准#define CLOCK_REG_SET 0x04 //CLOCK寄存器设置,无分频,50HZ 输出更新速率#define DELAY() {_nop_();_nop_();_nop_();}// 函数声明void AD7705_Init(void);void AD7705_Reset(void);void AD7705_Start(void);uchar AD7705_ReadByte(void);void AD7705_WritByte(uchar d);float AD7705_ReadV ol(void);#endif--------------------------AD7705.C -----------------------------------//**************************************************************************** //功能:AD7705串行接口失步后将其复位。

半导体传感器AD7705BRUZ中文规格书

AD7705/AD7706Rev. C | Page 28 of 44THEORY OF OPERATIONCLOCKING AND OSCILLATOR CIRCUITThe AD7705/AD7706 each require a master clock input, which can be an external CMOS-compatible clock signal applied to the MCLK IN pin with the MCLK OUT pin left unconnected. Alternatively, a crystal or ceramic resonator of the correct frequency can be connected between MCLK IN and MCLK OUT, as shown in Figure 17. In this case, the clock circuit functions as an oscillator, providing the clock source for the part. The input sampling frequency, modulator sampling frequency, –3 dB frequency, output update rate, and calibration time are directly related to the master clock frequency, f CLKIN . Reducing the master clock frequency by a factor of two halves the above frequencies and update rate and doubles the calibration time. The current drawn from the V DD power supply is also related to f CLKIN . Reducing f CLKIN by a factor of two halves the digital part of the total V DD current, but does not affect the current drawn by the analog circuitry.Figure 17. Crystal/Resonator Connection for the AD7705/AD7706 Using the part with a crystal or ceramic resonator between the MCLK IN pin and MCLK OUT pin generally causes more current to be drawn from V DD than does clocking the part from a driven clock signal at the MCLK IN pin. This is because the on-chip oscillator circuit is active in the case of the crystal or ceramic resonator. Therefore, the lowest possible current on the AD7705/AD7706 is achieved with an externally applied clock at the MCLK IN pin with MCLK OUT unconnected, unloaded, and disabled.The amount of additional current taken by the oscillator depends on a number of factors. For example, the larger the value of the capacitor (C1 and C2) placed on the MCLK IN and MCLK OUT pins, the larger the current consumption on the AD7705/AD7706. To avoid unnecessarily consuming current, care should be taken not to exceed the capacitor values recommended by the crystal and ceramic resonator manufac-turers. Typical values for C1 and C2 are recommended by crystal or ceramic resonator manufacturers, usually in the range of 30 pF to 50 pF. If the capacitor values on MCLK IN and MCLK OUT are kept in this range, they do not result in any excessive current. Another factor that influences the current is the effective series resistance (ESR) of the crystal that appears between the MCLK IN and MCLK OUT pins of the AD7705/ AD7706. As a general rule, the lower the ESR value, the lower the current taken by the oscillator circuit. When operating with a clock frequency of 2.4576 MHz, there is a 50 μA difference in the current between an externally applied clock and a crystal resonator operated with a V DD of 3 V . With V DD = 5 V and f CLKIN = 2.4576 MHz, the typical current increases by 250 μA for a crystal- or resonator-supplied clock vs. an externally applied clock. The ESR values for crystals and resonators at this frequency tend to be low, and, as a result, there tends to be little difference between different crystal and resonator types. When operating with a clock frequency of 1 MHz, the ESR value for different crystal types varies significantly. As a result, the current drain varies across crystal types. When using a crystal with an ESR of 700 Ω, or when using a ceramic resonator, the increase in the typical current over an externally applied clock is 20 μA with V DD = 3 V , and 200 μA with V DD = 5 V . When using a crystal with an ESR of 3 kΩ, the increase in the typical current over an externally applied clock is 100 μA with V DD = 3 V , but 400 μA with V DD = 5 V . There is a start-up time before the on-chip oscillator circuit oscillates at its correct frequency and voltage levels. Typical start-up times with V DD = 5 V are 6 ms using a 4.9512 MHz crystal, 16 ms with a 2.4576 MHz crystal, and 20 ms with a 1 MHz crystal oscillator. Start-up times are typically 20% slower when a 3 V power supply is used. With 3 V supplies, depending on the loading capacitances on the MCLK pins, a 1 MΩ feedback resistor might be required across the crystal or resonator to keep the start-up times around 20 ms.The AD7705/AD7706 master clock appears on the MCLK OUT pin of the device. The maximum recommended load on this pin is 1 CMOS load. When using a crystal or ceramic resonator to generate the AD7705/AD7706 clock, it might be desirable to use this clock as the clock source for the system. In this case, it is recommended that the MCLK OUT signal be buffered with a CMOS buffer before being applied to the rest of the circuit. SYSTEM SYNCHRONIZATION The FSYNC bit of the setup register allows the user to reset the modulator and digital filter without affecting the setup conditions on the part. This allows the user to start gathering samples of the analog input at a known point in time, that is, when the FSYNC changes from 1 to 0. With a 1 in the FSYNC bit of the setup register, the digital filter and analog modulator are held in a known reset state, and the part does not process input samples. When a 0 is written to the FSYNC bit, the modulator and filter are taken out of this reset state, and the part resumes gathering samples on the next master clock edge.AD7705/AD7706Rev. C | Page 29 of 44The FSYNC input can also be used as a software start convert command, allowing the AD7705/AD7706 to be operated in a conventional converter fashion. In this mode, writing to the FSYNC bit starts conversion, and the falling edge of DRDY indicates when conversion is complete. The disadvantage of this scheme is that the settling time of the filter must be taken into account for every data register update; therefore, the rate at which the data register is updated is three times slower in this mode. Because the FSYNC bit resets the digital filter, the full settling time of 3 × 1/output rate must elapse before a new word is loaded to the output register. If the DRDY signal is low when FSYNC goes to 0, the DRDY signal is not reset to high by the FSYNC command, because the AD7705/AD7706 recognize that there is a word in the data register that has not been read. The DRDY line stays low until an update of the data register takes place, at which time it goes high for 500 × t CLKIN before returning low again. A read from the data register resets the DRDY signal high, and it does not return low until the settling time of the filter has elapsed and there is a valid new word in the data register. If the DRDY line is high when the FSYNC command is issued, the DRDY line does not return low until the settling time of the filter has elapsed. RESET INPUTThe RESET input on the AD7705/AD7706 resets the logic, digital filter, analog modulator, and on-chip registers to their default states. DRDY is driven high, and the AD7705/AD7706 ignore all communication to their registers while the RESET input is low. When the RESET input returns high, the AD7705/AD7706 start to process data, and DRDY returns low in 3 × 1/output rate, indicating a valid new word in the data register. However, the AD7705/AD7706 operate with their default setup conditions after a reset, and it is generally necessary to set up all registers and perform a calibration after a RESET command.The AD7705/AD7706 on-chip oscillator circuit continues to function even when the RESET input is low, and the master clock signal continues to be available on the MCLK OUT pin. Therefore, in applications where the system clock is provided by the AD7705/AD7706 clock, the AD7705/AD7706 produce an uninterrupted master clock during a RESET command. STANDBY MODE The STBY bit in the communication register of the AD7705/ AD7706 allows the user to place the part in a power-down mode when it is not required to provide conversion results. The AD7705/AD7706 retain the contents of their on-chip registers, including the data register, while in standby mode. When released from standby mode, the parts start to process data, and a newword is available in the data register in 3 × 1/output rate from when a 0 is written to the STBY bit.The STBY bit does not affect the digital interface, nor does it affect the status of the DRDY line. If DRDY is high when the STBY bit is brought low, it remains high until there is a valid new word in the data register. If DRDY is low when the STBY bit is brought low, it remains low until the data register is updated, at which time the DRDY line returns high for 500 × t CLKIN before returning low again. If DRDY is low when the part enters standby mode, indicating a valid unread word in the data register, the data register can be read while the part is in standby. At the end of this read operation, DRDY is reset to high. Placing the part in standby mode reduces the total current to 9 μA typical with V DD = 5 V , and 4 μA with V DD = 3 V when the part is operated from an external master clock, provided that this master clock has stopped. If the external clock continues to run in standby mode, the standby current increases to 150 μA typical with 5 V supplies, and 75 μA typical with 3.3 V supplies. If a crystal or ceramic resonator is used as the clock source, the total current in standby mode is 400 μA typical with 5 V supplies, and 90 μA with 3.3 V supplies. This is because the on-chip oscillator circuit continues to run when the part is in standby mode. This is important in applications where the system clock is provided by the AD7705/AD7706 clock so that the AD7705/AD7706produce an uninterrupted master clock in standby mode. ACCURACY Σ-Δ ADCs, like VFCs and other integrating ADCs, do not contain a source of nonmonotonicity and inherently offer no missing codes performance. The AD7705/AD7706 achieve excellent linearity by using high quality, on-chip capacitors that have a very low capacitance/voltage coefficient. The devices also achieve low input drift by using chopper-stabilization techniques in their input stage. To ensure excellent performance over time and temperature, the AD7705/AD7706 use digital calibration techniques that minimize offset and gain error. DRIFT CONSIDERATIONS The AD7705/AD7706 use chopper-stabilization techniques to minimize input offset drift. Charge injection in the analog switches and dc-leakage currents at the sampling node are the primary sources of offset voltage drift in the converter. The dc input leakage current is essentially independent of the selectedgain. Gain drift within the converter primarily depends on the temperature tracking of the internal capacitors. It is not affected by leakage currents.Measurement errors due to offset drift or gain drift can beeliminated at any time by recalibrating the converter. Using the system calibration mode also minimizes offset and gain errors in the signal conditioning circuitry. Integral and differential linearity errors are not significantly affected by temperature changes.。

AD7705调试注意事项

AD7705应用总结:最近用到了AD7705,先将AD7705的应用经验以及注意要点总结如下,这些经验同样适用于AD7799、AD7706等AD公司的拥有校准功能的AD芯片。

1.时序注意要点:数字接口迷失的时候可以通过ADIN输入持续32个脉冲周期(DCLK)以上的高电平将复位AD7705的数字接口,复位之后要等待500us 以上才能访问AD7705芯片,这种复位方式不会影响AD7705内部的任何寄存器,所有的寄存器将保持复位之前的内容,但所有的寄存器在数字接口迷失的状态下内容是不确定的,因此强烈建议在复位之后重新设置AD7705内部所有的寄存器,防止错误。

而芯片管脚RESET的复位将使片内所有的寄存器恢复到上电的默认值。

时钟输入信号DCLK是一种施密特出发信号,能够适应光耦合器的慢速边沿,其他数字输入信号的上升和下降时间不应超过1us。

2.AD7705时钟大于2M时,时钟设置寄存器的CLK位应置1,小于2M时应置0。

DCLK的脉冲宽度要满足最小的脉宽要求。

在时钟DCLK下降之后的低电平期间读取数据ADOUT。

在时钟DCLK的低电平期间设置要写入数据ADIN,然后在DCLK的上升沿写入到7705。

写入数据以及读取数据的时钟DCLK的数目要与(被写入或被读取的寄存器)的位数长度一致,多于或少于(寄存器位长度)的时钟DCLK数目都将导致操作错误。

在两次写操作之间,ADIN应最好保持在高电平:因为任何(读或写)操作都必须从写通信寄存器开始,而且写入通信寄存器的8个位中的第1位必须为0,后续的位才能被写入到通信寄存器。

所以当ADIN为0的时候,万一时钟DCLK受到干扰导致0写入通信寄存器,AD7705会误认为是写通信寄存器的操作开始而等待后续的7位位串,发生这种干扰之后会导致AD7705的数字接口迷失,从而导致内部寄存器的内容也许会变得未知状态。

此外,时钟信号DCLK在两次操作AD7705之间要保持高电平。

AD7705_最好的中文资料

CS

择,或在与 AD7705/7706 通信时,CS可用作帧同步信号 复位输入。低电平有效的输入,将器件的控制逻辑、接口逻辑、校准系 5 RESET 数、数字滤波器和模拟调制器复位至上电状态 对于 AD7705,差分模拟输入通道 2 的正输入端。对于 AD7706,模拟输入 6 AIN2(+)[AIN1] 通道 1 的输入端 对于 AD7705,差分模拟输入通道 1 的正输入端;对于 AD7706,模拟输入 7 AIN1(+)[AIN2] 通道 2 的输入端 对于 AD7705,差分模拟输入通道 1 的负输入端;对于 AD7706,COMMON 输 8 AIN1(-)[COMMON] 入端,模拟通道 1、2、3 的输入以此输入端为基准 基准输入端。AD7705/7706 差分基准输入的正输入端。基准输入是差分 9 REFIN(+) 的,并规定 REFIN(+)必须大于 REFIN(-)。REFIN(+)可以取 VDD 和 GND 之 间的任何值 基准输入端。AD7705/7706 差分基准输入的负输入端。REFIN(-)可以取 10 REFIN(-) VDD 和 GND 之间的任何值,且满足 REFIN(+)大于 REFIN(-) 对于 AD7705,差分模拟输入通道 2 的负输入端。对于 AD7706,模拟输入 11 AIN2(-)[AIN3] 通道 3 输入端 逻辑输出。这个输出端上的逻辑低电平表示可从 AD7705/7706 的数据寄存 器获取新的输出字。完成对一个完全的输出字的读操作后, DRDY引脚立即 回到高电平。如果在两次输出更新之间,不发生数据读出, DRDY将在下一 12

———— ————

————

13

DOUT

14 15 16

AD7705输出数据一直是0xffff的问题的解决过程

最近手头上有个16位的高精度ADC,就想着做个测试版调试调试吧,先上自己画的原理图晶振采用4.9152MHz的,复位采用上电复位,复位时间大概1ms 吧!基准使用TL431提供!模拟输入端采用电位器调节。

画板,焊接,写程序!一切都很顺利!调试程序时卡了壳,出现如下问题1、ADC输出数据不变,或者输出一直是oxffff检测硬件供电电压是否正常,5v检测基准电压是否正常,2.5v根据网上和官方的测试版,我感觉硬件设计应该没有太大问题那么目标锁定在软件上,首先怀疑的是时序,芯片上有个引脚DRDY,这个引脚变低时有数据输出,我用逻辑分析仪分析自己模拟SPI的时序,发现时序跟手册上的一样,而且DRDY也会置高和变低!根据这个分析这应该不是自己SPI时序的问题了!经过一早上的看手册,查资料,还是没有头绪,不知道哪来的一个念头,是不是芯片复位没有复位好呢?因为我采用的是上电复位,所以我觉得应该观察上电后输出的第一个数据是否正常,别愣着啦,赶紧测试!哇塞。

数据正确!调整电压,第一次上电后数据依然正确,按下单片机复位键,前几次正确,后面又变为0xffff了。

问题找到啦,芯片复位有问题!我改成单片机控制复位,把ADC的复位引脚接到单片机一个引脚上,通过引脚控制ADC复位,复位时间为10ms。

下载程序,上电测试,发现预期连续采集一百个数据,只输出了四五个!复位重来,效果一样,有时候只输出一个数据,庆幸的是数据都正确啦!这个时候没辙啦。

给adi亚太客服打电话。

至今没给回复。

nngt我还是靠自己吧!上网搜索,终于在一篇帖子中见到可能这么一句话“可能每次读AD7705的数据时都要把clock register,setup register重新设置一遍,复位重来一遍”不管正确与否,试试再说!改程序,下载,看现象,哇塞!一次性输出100个数据,数据正常!可能大家跟我一样吧,怎么会这个样子呢。

我也很郁闷,手册上找不到连续读数据的时序,手册上看不到为什么这么做就数据正确啦!期待ADI工程师给我回复吧!!!不过总算是可以正常运行啦!谢天谢地你好啦!!!欢迎大家进我的空间,有问题可以在我的空间名字上找到我的联系方式/zhangkai0215/item/0c94e099cae3b83d336eeb0d主函数/*********************************************************Auther :zhang kaiDate :April 3, 2013File :main.cHardware :STC89C52Description :AD7705 driver use STC89C52 as MCU*********************************************************/#include <AT89X51.H>#include "AD7705_IO.h"#include "putchar.h"#include "intrins.h"unsigned char buf[4] = {0,0,0,0};void main(void){unsigned char i;InitUart();for(i=0;i<100;i++){CLR_RST();_nop_();SET_RST();CLR_CS();buf[0] = 0x21;WriteToAD7705(1,buf); //write communication register 0x20 to control the progress to write clock registerbuf[0] = 0x0c;WriteToAD7705(1,buf); //write clock register,50Hz update ratebuf[0] = 0x11;WriteToAD7705(1,buf); //write communication register 0x10 to control the progress to write setup registerbuf[0] = 0x44;WriteToAD7705(1,buf); //write setup register,Self-CalibrationAD7705WaitBusy (); //判忙TR1=1;buf[0] = 0x38;WriteToAD7705(1,buf); //write communication register 0x38 to control the progress to read data registerAD7705WaitBusy ();ReadFromAD7705(2,buf); //read data registeputchar(buf[1]);putchar(buf[0]);}SET_CS();while(1);}。

AD7705的操作

AD7705的操作

AD7705是由Analog Devices公司推出的一款基于模拟/数字混合技

术的通用称重接口单元,其将模拟信号转换成数字信号,便于数字系统进

行处理,可以将传感器集成到数字系统中,实现多功能的称重系统。

AD7705有两种型号:AD7705-1和AD7705-2,其中,AD7705-1具有单

路输入,4种模拟量输入类型(电阻、电容、电压、电流),可定义的模

式和参考电压,2倍长量程和可编程滤波器,而AD7705-2则具有双路输入,其他参数相同。

采用的控制和数据通信接口包括UART,SPI,I2C和PWM/INTEGER。

一、精度高:以电流输入(TARA补偿)为例,其满量程误差最小可

达0.08%(最大满量程100克),实测偏差不大于0.2%,所以可以用于

仪表和计量定量计量应用。

二、模式多样性:AD7705可定制4种模式,分别是SCALE,

SCALE&HOLD,CONTINUOUS,CONTINUOUS&HOLD,可根据仪器的不同应用来

设置合适的模式,以提高AD7705的灵活性。

三、可编程参数:AD7705可编程参数,包括量程、模式,参考电压,滤波器等参数,可以根据实际应用需要,编程满足应用需求。

四、安全功能:AD7705具有3种安全功能,可以有效保护被测设备

的安全,它们分别是超载保护,超电压保护和超电容保护。

16位Σ-Δ模数转换器AD7705及其校准

16位Σ-Δ模数转换器AD7705及其校准

陈勇钢;吴伯农

【期刊名称】《现代电子技术》

【年(卷),期】2006(29)4

【摘要】AD7705是AD公司推出的16位高性能、低功耗Σ-Δ A/D转换器,具有增益可编程放大器,可通过编程直接测量传感器输出的微弱信号.介绍了AD7705的基本特点、结构以及常用片上寄存器的格式与编程注意事项.自校准和系统校准可消除偏置和增益误差,由于现场条件变化不定,还详细介绍了适用于特定条件的现场校准与手动校准,最后给出了数据手册中没有的手动校准实例.

【总页数】4页(P124-126,129)

【作者】陈勇钢;吴伯农

【作者单位】北方工业大学,机电工程学院,北京,100041;北方工业大学,机电工程学院,北京,100041

【正文语种】中文

【中图分类】TP352

【相关文献】

1.十六位模数转换器AD7705及其应用 [J], 敖振浪;李源鸿;谭鉴荣

2.16位模数转换器AD7705在安全帽质量检测中的应用 [J], 安然然;佟宁;乔晶

3.模数转换器AD7705在蓄电池质量检测中的应用 [J], 王勇军;韩宏阁

4.基于16位SAR模数转换器的误差校准方法 [J], 乔高帅;戴庆元;孙磊;谢芳

5.模数转换器AD7705及其接口电路 [J], 彭珊

因版权原因,仅展示原文概要,查看原文内容请购买。

十六位模数转换器AD7705及其应用

图3

气象探测仪电路图

2. 3

软件设计 使用 AD7705 之前, 首先要对所有寄存器进行设置 , 才能保证器件正常工作。在实际使用中, 首先选择模拟

输入模式 ( 单极性还是双极性 ) 、 是否需要缓冲、 时钟分频和输出更新速率 ; 根据外部输入信号的幅度来决定设置 器件的增益值, 本实例里通道 1 和通道 2 输入信号都是单极性, 但幅度不同, 所以循环选择通道 , 选择相应参数, 应用中选择输入通道单极性、 初始增益等于 8、 数据更新速率为 250Hz。根据实际确定所有参数以后, 对 AD7705 芯片进行设置, 参数设置方法比较独特 , 在设置参数之前, 首先对通信寄存器进行一次写操作 , 来决定下一个是什 么样的寄存器和什么样的操作内容 , 再进行下一步的参数写入, 读者可参考下面的 AD7705 初始化程序 InitADC( )。 模拟输入电路前端加入了一个简单的 R、 C 滤波器 , 会在输入电压中引起增益误差, 必须对器件进行校准 , 因 为每次系统校准可以对系统的增益、 偏移误差、 以及器件本身的内部误差进行补偿, 所以参数设置完毕以后, 应该 对器件进行一次系统校准 , 写入设置寄存器位 MD1 和 MD0 分别为 0 和 1 完成系统自校准 , 自校准后自动返回正 常模数转换工作模式。实际中各路输入信号幅度往往不完全相同 , 因此每转换一路就需要一次参数设置和系统 校准。还需注意的是 , 在非缓冲模式下使用时 , 系统校准还可以消除模拟输入端由电源阻抗引起的任何误差。 下面是用 C51 语言编写的初始化程序:

数据寄存器 : 这是一个十六位只读寄存器 , 它包含了最新的转换结果。 测试寄存器 : 用于测试期间器件, 用户一般不用。 零标度校准寄存器和满标度校准寄存器 : 都是 24 位, 用户一般不用。

AD7705 DRDY线不能变低解决方法

3:保证足够的延时 校准和数据AD转换都需要时间.要注意自己程序中是如何等待的这个时间的.读取DRDY可以直接读取AD7705第12脚的电平, 也可以在寄存器中读取.两者并无差别,逻辑电平上是一致的. 顺便举个等待的例子.

AD_CS_0;

//自校准配置完毕( while(GPIO_ReadInputDataBit(GPIOA,AD_DRDY)) //while(AD_DRDY) {

AD7705 DRDY

DRDY不能变低可能有以下几个情况: 1:保证通迅(SPI)畅通

2:保证配置正确 (1)不管是校准还是数据AD转换,数字滤波器同步位FSYNC都要置为0,这样AD7705的校准或者数据AD转换工作才能进行, 否则校准和AD转换不会进行,DRDY信号也不会变低。 (2)AD7705时钟大于2M时,时钟设置寄存器的CLK位应置1,小于2M时应置0。 (3)通道读取要正确.配置的通道1,不能去读通道2.

Cnt++; if(Cnt>50000) {

break; } } AD_CS_1;

//STM32F //C51

以上例子是自校准配置完后等待其完成.如果MCU执行速度很快.Cnt计数(延时)不够的话.很容易就出现DRDY一直 为高,无法正常工作的情况

解决方法就是加大Cnt. 或者最笨的方法,直接加几十个mS的延时,DelayMS(20); 再读取DRDY信号 或者一直等 while(AD_DRDY); 此法有产生死循环的可能.

总之,校准之后一定要足够的延时.

另外.在通道切换时,一定要做校准操作,至于是用哪个校准,看自己的应用.

第1页

AD7705输出数据一直是0xffff的问题的解决过程

最近手头上有个16位的高精度ADC,就想着做个测试版调试调试吧,先上自己画的原理图晶振采用4.9152MHz的,复位采用上电复位,复位时间大概1ms 吧!基准使用TL431提供!模拟输入端采用电位器调节。

画板,焊接,写程序!一切都很顺利!调试程序时卡了壳,出现如下问题1、ADC输出数据不变,或者输出一直是oxffff检测硬件供电电压是否正常,5v检测基准电压是否正常,2.5v根据网上和官方的测试版,我感觉硬件设计应该没有太大问题那么目标锁定在软件上,首先怀疑的是时序,芯片上有个引脚DRDY,这个引脚变低时有数据输出,我用逻辑分析仪分析自己模拟SPI的时序,发现时序跟手册上的一样,而且DRDY也会置高和变低!根据这个分析这应该不是自己SPI时序的问题了!经过一早上的看手册,查资料,还是没有头绪,不知道哪来的一个念头,是不是芯片复位没有复位好呢?因为我采用的是上电复位,所以我觉得应该观察上电后输出的第一个数据是否正常,别愣着啦,赶紧测试!哇塞。

数据正确!调整电压,第一次上电后数据依然正确,按下单片机复位键,前几次正确,后面又变为0xffff了。

问题找到啦,芯片复位有问题!我改成单片机控制复位,把ADC的复位引脚接到单片机一个引脚上,通过引脚控制ADC复位,复位时间为10ms。

下载程序,上电测试,发现预期连续采集一百个数据,只输出了四五个!复位重来,效果一样,有时候只输出一个数据,庆幸的是数据都正确啦!这个时候没辙啦。

给adi亚太客服打电话。

至今没给回复。

nngt我还是靠自己吧!上网搜索,终于在一篇帖子中见到可能这么一句话“可能每次读AD7705的数据时都要把clock register,setup register 重新设置一遍,复位重来一遍”不管正确与否,试试再说!改程序,下载,看现象,哇塞!一次性输出100个数据,数据正常!可能大家跟我一样吧,怎么会这个样子呢。

我也很郁闷,手册上找不到连续读数据的时序,手册上看不到为什么这么做就数据正确啦!期待ADI工程师给我回复吧!!!不过总算是可以正常运行啦!谢天谢地你好啦!!!欢迎大家进我的空间,有问题可以在我的空间名字上找到我的联系方式/zhangkai0215/item/0c94e099cae3b83d336eeb0d主函数/*********************************************************Auther :zhang kaiDate :April 3, 2013File :main.cHardware :STC89C52Description :AD7705 driver use STC89C52 as MCU*********************************************************/#include <AT89X51.H>#include "AD7705_IO.h"#include "putchar.h"#include "intrins.h"unsigned char buf[4] = {0,0,0,0};void main(void){unsigned char i;InitUart();for(i=0;i<100;i++){CLR_RST();_nop_();SET_RST();CLR_CS();buf[0] = 0x21;WriteToAD7705(1,buf); //write communication register 0x20 to control the progress to write clock registerbuf[0] = 0x0c;WriteToAD7705(1,buf); //write clock register,50Hz update ratebuf[0] = 0x11;WriteToAD7705(1,buf); //write communication register 0x10 to control the progress to write setup registerbuf[0] = 0x44;WriteToAD7705(1,buf); //write setup register,Self-CalibrationAD7705WaitBusy (); //判忙TR1=1;buf[0] = 0x38;WriteToAD7705(1,buf); //write communication register 0x38 to control the progress to read data registerAD7705WaitBusy ();ReadFromAD7705(2,buf); //read data registeputchar(buf[1]);putchar(buf[0]);}SET_CS();while(1);}。

AD7705的操作

AD7705的操作我现在使用外部TL431(2.5V基准电压),电源电压为5V,外接晶体振荡器2.4576MHz,电路如下:程序如下:--------------------------AD7705.H -----------------------------------#ifndef _AD7705_H_#define _AD7705_H_// 引脚定义sbit AD7705_SCLK = P2^4;sbit AD7705_DRDY = P2^5;sbit AD7705_DOUT = P2^6;sbit AD7705_DIN = P2^7;// 通讯寄存器地址定义#define WR_SETUP_REG 0x10 //选中设置寄存器,写#define RD_SETUP_REG 0x18 //选中设置寄存器,读#define WR_CLOCK_REG 0x20 //选中时钟寄存器,写#define RD_DATA_REG 0x38 //选中数据寄存器,读#define WR_OFFSET_REG 0x60 //选中offset寄存器,写#define RD_OFFSET_REG 0x68 //选中offset寄存器,读#define WR_FULL_REG 0x70 //选中full scale寄存器,写#define RD_FULL_REG 0x78 //选中full scale寄存器,读#define SYS_ZERO_CALI 0x80 //系统零校准模式#define SYS_FULL_CALI 0xC0 //系统满量程校准模式#define ZERO_CALIBRA TION 0x00 //系统零校准#define FULL_CALIBRA TION 0x01 //系统满量程校准#define CLOCK_REG_SET 0x04 //CLOCK寄存器设置,无分频,50HZ 输出更新速率#define DELAY() {_nop_();_nop_();_nop_();}// 函数声明void AD7705_Init(void);void AD7705_Reset(void);void AD7705_Start(void);uchar AD7705_ReadByte(void);void AD7705_WritByte(uchar d);float AD7705_ReadV ol(void);#endif--------------------------AD7705.C -----------------------------------//**************************************************************************** //功能:AD7705串行接口失步后将其复位。

AD7705/7706在仪器仪表中的应用 工业控制 解决方案

由于模拟输入和基准输入是差分的,模拟调制器的大部分电压都是共模电压,AD770 5/7706 的良好的共模抑制性能能消除这些共模输入信号里的共模噪声,数字滤波器能抑 制供电电源产生的除了调制器采样频率整数倍的频率以外的宽带噪声。此外 ,数字滤波器 还能消除模拟和基准输入信号里的噪声不使模拟调制器饱和。但是,由于它的分辨率太高, 而要求的噪声电平太小,所以,必须注意接地和电路布线。

(1) 低价格、高性能 (2) 集成化的数字滤波 (3) 与 DSP 技术的兼容性便于实现系统集成

AD7705/7706 是利用 Σ-△转换技术实现了 16 位无丢失代码性能。该器件可以接受 直接来自传感器的低电平的输入信号,然后产生串行的数字输出。

AD7705/7706 只需 2.7~3.3V 或 4.75~5.25V 单电源。AD7705 是双通道全 差分模拟输入,而 AD7706 是 3 通道伪差分模拟输入,二者都有一个差分基准输入。当电 源电压为 5V、基准电压为 2.5V 时,这二种器件都可将输入信号范围从 0~20mA 到 0~ 2.5V 的信号进行处理。还可以处理±20mV~±2.5V 的双极性输入信号。当电源电压为 3 V、基准电压为 1.225V 时,可处理 0~10mV 到 0~1.225V 的单极性输入信号,它的 双极性输入信号范围是±10mV 到±1.225V 对于 AD7705 是以 AIN(-)输入端为参考点,而 AD7706 是 COMMON 输入端。AD7705/7706 是用于智能系统、微控制器系统和基于 D SP 系统的理想产品。其串行接口可配置为三线接口。增益值、信号极性以及更新速率的 选择可用串行输入口由软件来配置。该器件还包括自校准和系统校准选项,以消除器件本 身或系统的增益和偏移误差。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AD7705应用总结:

最近用到了AD7705,先将AD7705的应用经验以及注意要点总结如下,这些经验同样适用于AD7799、AD7706等AD公司的拥有校准功能的AD芯片。

1.时序注意要点:数字接口迷失的时候可以通过ADIN输入持续32个脉冲周期(DCLK)以上的高电平将复位AD7705的数字接口,复位之后要等待500us 以上才能访问AD7705芯片,这种复位方式不会影响AD7705内部的任何寄存器,所有的寄存器将保持复位之前的内容,但所有的寄存器在数字接口迷失的状态下内容是不确定的,因此强烈建议在复位之后重新设置AD7705内部所有的寄存器,防止错误。

而芯片管脚RESET的复位将使片内所有的寄存器恢复到上电的默认值。

时钟输入信号DCLK是一种施密特出发信号,能够适应光耦合器的慢速边沿,其他数字输入信号的上升和下降时间不应超过1us。

2.AD7705时钟大于2M时,时钟设置寄存器的CLK位应置1,小于2M时应置0。

DCLK的脉冲宽度要满足最小的脉宽要求。

在时钟DCLK下降之后的低电平期间读取数据ADOUT。

在时钟DCLK的低电平期间设置要写入数据ADIN,然后在DCLK的上升沿写入到7705。

写入数据以及读取数据的时钟DCLK的数目要与(被写入或被读取的寄存器)的位数长度一致,多于或少于(寄存器位长度)的时钟DCLK数目都将导致操作错误。

在两次写操作之间,ADIN应最好保持在高电平:因为任何(读或写)操作都必须从写通信寄存器开始,而且写入通信寄存器的8个位中的第1位必须为0,后续的位才能被写入到通信寄存器。

所以当ADIN为0的时候,万一时钟DCLK受到干扰导致0写入通信寄存器,AD7705会误认为是写通信寄存器的操作开始而等待后续的7位位串,发生这种干扰之后会导致AD7705的数字接口迷失,从而导致内部寄存器的内容也许会变得未知状态。

此外,时钟信号DCLK在两次操作AD7705之间要保持高电平。

即:在不访问AD7705的空闲时刻,或者两次操作之间的空闲时刻,ADIN、DCLK都最好保持高电平为最可靠。

3.DRDY信号为数据AD转换完成的指示信号,低电平期间表示AD转换完成,可以读取数据寄存器的内容,高电平期间表示AD转换正在进行,这时不能访问数据寄存器。

对于系统校准和内部校准也一样,低电平期间表示校准完成,可以读取校准寄存器的内容,高电平期间表示校准正在进行,这时不能访问校准寄存器。

违反这些规定的操作,结果时未知的。

此外程序中千万不能把DRDY的逻辑搞反,否则结果不可预料。

4.不管是校准还是数据AD转换,数字滤波器同步位FSYNC都要置为0,这样AD7705的校准或者数据AD转换工作才能进行,否则校准和AD转换不会进行,DRDY信号也不会变低。

当FSYNC=0时,在校准或AD转换结束后DRDY 信号将变低,此时可以读取校准系数或者数据寄存器。

5..采用非缓冲模式时,AD7705模拟输入前端的电阻电容的变化对AD转换精度影响很大。

若系统工作时的信号源、温度环境、器件参数变化很大,导致AD7705模拟输入前端电路的参数跟系统校准时的参数不一致,误差会非常大。

缓冲模式能解决这种问题,当使能缓冲模式时,AD7705会在模拟输入端和AD转换器之间接入一个缓冲器Buffer,这样AD7705就能适应模拟输入前端信号源的大阻抗、器件参数(电阻电容)的变化、温度环境的变化等各种与系统校准时的不一致情况(即器件工作条件的变化)。

所以,AD7705的校准和正常工作最好都要在缓冲模式下进行。

6..电压输入范围:对于非缓冲模式,模拟输入信号范围是【GND-30mV】至【VDD+30mV】之间。

对于缓冲模式,模拟输入信号范围是【GND+50mV】至【VDD-1.5V】之间。

7.非缓冲模式、单极性、增益为GAIN:此时AD7705的反相输入端VIN -的范围是【GND-30mV】至【VDD+30mV-VREF/GAIN】之间,其中VREF 为AD7705的参考电压。

正相输入端VIN+的范围是【V-】至【V-+VREF/GAIN】。

如右图,即V+和V-都必须大于GND小于VDD,同时还要考虑单极性的输入范围,即V-还必须小于VDD+30mV-VREF/GAIN,才不至于模拟输入为V+max=【V-+VREF/GAIN】时大于VDD+30mV。

8.8.非缓冲、双极性、增益为GAIN:此时V+和V-都必须大于GAN小于VDD,V-还必须小于VDD+30mV-VREF/GAIN,这样输入V+max=【V -+VREF/GAIN】不至于大于VDD+30mV。

V-还必须大于GND-30mV +VREF/GAIN,才不至于输入V+min=【V――VREF/GAIN】时小于GND-30mV。

正相输入端VIN+的正信号输入范围是【V-】至【V-+VREF/GAIN】,正相输入端VIN+的负信号输入范围是【V-】至【V--REF/GAIN】。

如右图:其

中V+max为正的最大输入,V+min为负的最大输入。

9.缓冲模式、单极性、增益为GAIN:此时AD7705的反相输入端VIN-的范围是【GND+50mV】至【VDD-1.5V-VREF/GAIN】之间,其中VREF为AD7705的参考电压。

正相输入端VIN+的范围是【V-】至【V-+VREF/GAIN】。

如右图,即V+和V-都必须大于GND+50mV小于VDD-1.5V,同时还要考虑单极性的输入范围,即V-还必须小于VDD-1.5V-VREF/GAIN,才不至于输入V+max=【V-+VREF/GAIN】时大于VDD-1.5V。

10.缓冲模式、双极性、增益为GAIN:此时AD7705的反相输入端VIN -的范围是【GND+50mV+VREF/GAIN】至【VDD-1.5V-VREF/GAIN】之间,这样才不至于输入VIN+max=【V-+VREF/GAIN】时导致VIN+大于VDD-1.5V、输入VIN+min=【V――VREF/GAIN】时导致VIN+小于GND +50mV。

其中VREF为AD7705的参考电压。

正相输入端VIN+的正信号输入范围是【V-】至【V-+VREF/GAIN】,正相输入端VIN+的负信号输入范围是【V-】至【V--REF/GAIN】。

如右图:其中V+max为正的最大输入,V+min 为负的最大输入。

11.初使化时要选择校准方式:有自校准,和系统校准两种。

一般选自校准,这样不容易错。

注:有关缓冲模式,双极性,增益,零校准,满校准等状态,请查看AD7705说明文档。