SCHEMATIC1 _ PAGE1

OrCADCaptureCIS(Cadence原理图绘制)

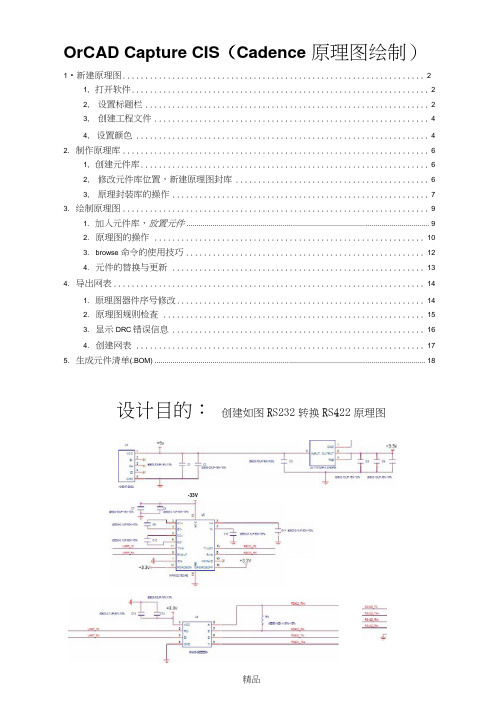

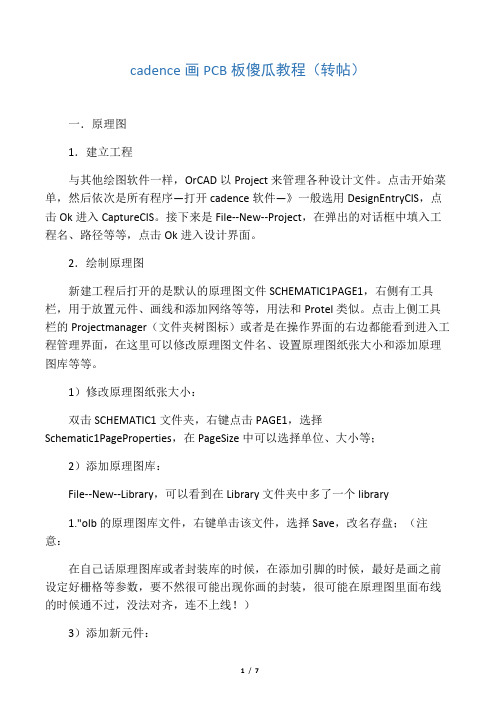

OrCAD Capture CIS(Cadence 原理图绘制)1•新建原理图 (2)1, 打开软件 (2)2, 设置标题栏 (2)3, 创建工程文件 (4)4, 设置颜色 (4)2. 制作原理库 (6)1, 创建元件库 (6)2, 修改元件库位置,新建原理图封库 (6)3, 原理封装库的操作 (7)3. 绘制原理图 (9)1. 加入元件库,放置元件 (9)2. 原理图的操作 (10)3. browse 命令的使用技巧 (12)4. 元件的替换与更新 (13)4. 导出网表 (14)1. 原理图器件序号修改 (14)2. 原理图规则检査 (15)3. 显示DRC错误信息 (16)4. 创建网表 (17)5. 生成元件淸单(.BOM) (18)设计目的:创建如图RS232转换RS422原理图-33V1.新建原理图1, 打开软件圈 Design Entry CISS Design Entry HDL Rules Checl U? Design Entry HDLPlease select the suite from which to check out the OrC^D Capture feature:0Capture_CIS_option with DCAD Unison EE 0(CAD_Cdptut_OS_option with OrCAD Unison Ultra 0rC^D^Capture^CIS^option with£rC^D EEDesigner Plus optiqs withWCAD PCB Designer BasicsUse as default2, 设置标题栏Options ------- DesignTempla teFPGA System Planner 级 Library Explorer 餾 License Client Configuration I毬 OrCAD PCB Editor jgOrCAD PCB Router 習 OrCAD SigXplorer S3 Package Designer 毬 PCB EditorCadence Product Choices 360$全中Altera 12.1 Build 177 Altium【CAD Capture CIS Allegro PCB Design CIS L Allegro PCB Librarian XL Allegro PCB Design CIS XL illpnrr. PPR 「IG创建完原理图工程后,也可以修改标题栏Options Schematic Page Properties3,创建工程文件File New ------ Projet4,设置颜色Options -------- Preferences2. 制作原理库1,创建元件库File ------- New ---- L ibrary2,修改元件库位置,新建原理图封库Save As另存为。

第二章Cadence的原理图设计要点

第二章 Cadence的原理图设计2.1Design Entry CIS软件概述Cadence软件系统有两套电路原理图的设计工具,一套是Design Entry HDL,另一套就是我们马上要开始学习的Design Entry CIS。

其中Design Entry HDL 是Cadence公司原本的原理图设计软件,可以用于芯片电路和板级电路的设计,其长处在于可以把芯片的电路原理图和板级电路原理图结合在一起,进行综合设计;而Design Entry CIS主要用于常规的板级电路设计,Design Entry CIS原本是OrCAD公司的产品,OrCAD公司后来被Cadence公司收购,于是Design Entry CIS也就成了Cadence公司的另一套电路原理图设计软件。

Design Entry CIS原理图设计软件的特点是直观、易学、易用,在业界有很高的知名度,利用Design Entry CIS原理图设计软件可以进行简单的(只有单张图纸构成的)电路原理图设计,也可以进行(由多张图纸拼接而成的)平坦式电路原理图设计,还可以进行(多张图纸按一定层次关系构成的)层次式电路原理图设计。

在本章中,我们首先学习简单的电路原理图设计,然后再学习较为复杂的平坦式和层次式电路原理图设计。

我们将围绕一块非常简单的STC系列单片机下载电路板,学习简单电路原理图的设计,同时在此过程中,还将学习到USB转UART串行口、STC系列单片机下载电路等方面的知识。

接着,我们将围绕一块ARM-7核心实验板,进行平坦式和层次式电路原理图的设计,而该核心板是配套于ARM-7实验箱。

在此过程中我们还将学习到嵌入式技术等方面的知识。

2.2初识Design Entry CIS一.启动Design Entry CIS我们在电脑上点击“开始→所有程序→Cadence SPB 16.2→Design Entry CIS”,如下图所示:这时将弹出如下对话框:图2-2 选择工作内容在这里我们选择“OrCAD Capture CIS”一项,点击“OK”按钮后,就实际启动了Design Entry CIS,出现如下界面:图2-3 OrCAD Capture CIS软件界面与大多数软件一样,OrCAD Capture CIS软件也是以项目方式管理我们的设计文件的。

OrCAD-PSPice-Allegro学习笔记(1121)

OrCAD--Pspice--Cadence 软件组成及功能Pspice原来不是OrCAD公司的产品,后来被OrCAD公司收购,并且集成OrCAD软件中,现在的OrCAD版本全部包含完整的Pspice。

Cadence是全球著名EDA软件公司,在OrCAD公司收购Pspice之后,将OrCAD公司收购,所以现在的OrCAD软件(包含Pspice)应该属于Cadence公司的产品。

Cadence公司针对PCB方面的EDA产品大概可以分为高端和低端,高端的是Cadence SPB,低端的是OrCAD。

不管高端低端,原理图设计主要用OrCAD 中的原理图软件---Capture CIS。

PCB绘图方面,高端Cadence SPB的叫Allegro,低端OrCAD的现在主要用Allegro的简化版,OrCAD都会包含完整的Pspice。

设计低端电路板一般用法:使用OrCAD(包括Pspice)来设计原理图部分,使用PADS设计PCB部分(高端的用Allegro)。

1、Orcad:Capture:电路原理图设计软件,可生成模拟电路、数字电路和模/数混合电路。

Pspice:电路仿真软件,可对Capture生成的原理图进行仿真分析,并对其进行优化。

Layout:印刷电路板图设计软件,可将Capture生成的原理图,转为印刷电路板图(PCB)-----不好用,一般选用PADS或Allegro进行Layout。

Express:逻辑仿真软件,可对Capture生成的数字电路模拟仿真,用于可编程逻辑器件设计。

2、Pspice:在电路系统仿真方面,独具特色,其他软件无法比拟,适合系统及电路级仿真,被公认为是通用电路模拟程序中最优秀的软件。

Cadence把Pspice AD和Pspice AA整合成一个产品包,并改名为AMS simulator。

----庞大的上万种元器件库,并可生成新元器件----高精度元器件模型、仿真精度高PSpice的四个主要/基本电路分析:----直流分析DC Sweep----交流分析AC Sweep----瞬态分析Time Domain(时域扫描)----直流工作点分析Bias Point(偏置点分析)3、Cadence Allegro:Allegro是Cadence推出的先进PCB设计布线工具。

1_schematic

Cadence IC设计实验中国科技大学电子科学与技术系IC教研组黄鲁胡新伟白雪飞2005年10月(实验例题由Cadence 公司提供)致谢!电子科学技术系刘烃海、矫逸书、祝超、梅汪生等同学帮助编写了部分实验章节;信息实验中心屈玉贵主任和方毅、周远远、刘贵英等老师不仅为实验提供了技术支持,准备好EDA软件licence、配置了计算机和软件运行环境,而且热情参与了本实验教学。

对于上述老师和同学们的辛勤工作和所做出的贡献,在此一并表示衷心地感谢!预备知识:UNIX你掌握UNIX操作系统的基本命令吗?下面几条常用命令可能会对你有用处。

提醒一下,UNIX命令是区分大小写的。

查文件:ls (不显示隐含文件)、la (或ls –a,显示所有文件)、ls |mpre(帧显)、la |more删文件:rm 文件名建新目录:mkdir 目录名删目录:\rm –r目录名( 慎用!!!)拷贝:cp 源文件名(含路径)目标文件名(含路径),例将isc用户的abc.suf 文件拷贝到自己的当前目录下:cp ~isc/abc.suf .解.tar打包文件:tar vxf 打包文件名解.tar.Z压缩文件:tar vxfZ 压缩文件名文件改名: mv 原文件名新文件名查命令与参数功能:man 命令***************************************************************************规定:本实验教材中红色为键入命令或字符,兰色为菜单项,紫色为功能键;“单击”指鼠标左键按下一次。

****************************************************************************实验一、Virtuoso Schematic Editor实验目的:掌握电原理图(schematic)设计输入方法。

边学边做[1]启动IC Design 软件:开机后按lab_readme.txt的说明用你的用户名和密码登录至服务器cp /eva01/cdsmgr/ ICDATA/SchemEd.tar . (提醒:最后是个小点,稍等)tar vxf SchemEd.tarcd adelabic5icfb若出现“What’s New”窗口,关掉它。

ORCAD原理图的绘制技巧

系统控制菜单 菜单栏

标题栏

工具栏

记录窗口 状态栏

工作区

第一步:新建Project(create a design project)

在菜单栏中选择>Project:

Analog or Mixed-signal Circuit 本项目以后将进行数/模混合仿真

PC Board Wizard 本项目以后将用来进行印刷版图设计

使用empty.opj模板 使用空白模板

• 一般来说,要选中第一项Create Based upon an existing project,在其下拉选框中,选择 Empty.opj。

• 单击OK, 就会出现项目管理窗口。在File标签中, 有Design Resources(设计资源)项目名.dsn SCHEMATIC1PAGE1,双击PAGE1,电路图 绘制窗口就出现了。

• Synchrosize up/down/cross是关于 管脚放置方向的

Place 主命令菜单

• Database part 调用internet上数据库 的元器件

• Off-page connector 端口连接符 • Hierarchical block 子电路框图 • Hierarchical port 层次电路框图中的

按钮调出下面的器件搜索对话框endmode结束模式mirrorhorizontally水平镜像mirrorvertically垂直镜像rotate旋转editproperties编辑属性placedatabasepart放置数据库元件ascendhierarchy上升层次zoomout放大缩小goto跳到指定位置字母代号元器件类别字母代号元器件类别gaas场效应晶体管独立电流源ustim数字电路激励信号源在显示的元件值上单击鼠标左键出现displayproperties对话框只需修改value栏内的值即可也可双击元件出现一个propertieseditor对话框在partreference栏内输入元件序号在value栏内修改元件值另外在将元件放置到绘图页之前按下鼠标右键打开快捷功能菜单选择editpartproperties就可打开editpart对话框选定元件后单击鼠标右键在弹出的快捷栏editproperties命令即可打开元器件属性编辑对话框在元件没有放置到电路图上之前点击鼠标右键从弹出的快捷方式中选择editproperties子命令切换到项目管理窗口选择整个设计绘图页文件夹或单一绘图页然后点击按钮或者选择菜单上toolsannotate功能这时调出annotate对话框电路中电学上相连的连线总线元器件引出端等构成一个网络net也叫节点

集成电路课程设计(CMOS二输入与门).

课程设计任务书学生姓名:王伟专业班级:电子1001班指导教师:刘金根工作单位:信息工程学院题目: 基于CMOS的二输入与门电路初始条件:计算机、Cadence软件、L-Edit软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:2周2、技术要求:(1)学习Cadence IC软件和L-Edit软件。

(2)设计一个基于CMOS的二输入的与门电路。

(3)利用Cadence和L-Edit软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2013.11.25-11.27学习Cadence IC和L-Edit软件,查阅相关资料,复习所设计内容的基本理论知识。

2013.11.28-12.5对二输入与门电路进行设计仿真工作,完成课设报告的撰写。

2013.12.6 提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (2)绪论 (3)一、设计要求 (4)二、设计原理 (4)三、设计思路 (4)3.1、非门电路 (4)3.2、二输入与非门电路 (6)3.3、二输入与门电路 (8)四、二输入与门电路设计 (9)4.1、原理图设计 (9)4.2、仿真分析 (10)4.3、生成网络表 (13)五、版图设计................................................... (20)5.1、PMOS管版图设计 (20)5.2、NMOS管版图设计 (22)5.3、与门版图设计 (23)5.4、总版图DRC检查及SPC文件的生成 (25)六、心得体会 (28)七、参考文献 (29)八、附录 (30)摘要本文从设计到仿真以及后面的版图制作等主要用到了Cadence IC软件和L-Edit软件等。

cadence使用方法

cadence使用方法一焊盘制作1. smt焊盘1)所有程序→cadence SPB15.7→PCB edit utilities→Pad designer;2) parameter选项中: type选single ,internal layer 选option,Unit 选毫米或mi l;3)layer 选项中设置焊盘:选Begin layer→regular pad 设置焊盘形状和大小;thermal relief 和anti pad 选NULL;4)取名SAVE as存盘。

2.通孔焊盘1)所有程序→cadence SPB15.7→PCB edit utilities→Pad designer;2) parameter选项中: type选through,internal layer 选option,Unit 选毫米或mi l;设置焊盘钻孔大小,焊盘字符(可不设);3)layer 选项中设置焊盘:选Begin layer→regular pad 设置焊盘形状和大小;thermal relief 和anti pad 比焊盘大0.8或1mm,同样设置end layer(底层),soldermask_top、soldermask_bottom设置比焊盘大0.15mm,paste_top、paste_bottom设置成与焊盘一样大。

4)取名save as存盘。

二封装制作1.所有程序→cadence SPB15.7→pcb editor→Allegro PCB designe XL;2.File→new,弹出New Drawing对话框,输入文件名,在Drawing type中选Package symbol→OK;3.设置绘画尺寸:Setup→drawing size ,分别设置类型、单位、左下角座标、绘图区宽、高→OK;4. 设置栅格:setup grid,将所有层栅格设为0.0254或1mil→OK;5. Layout→pins ,Options中选connect,选定焊盘、设置重复放置形式;6. 重复放置所有焊盘;7.放置元件边界区,用于DRC检查(通常与元器件一样大,与其外形丝印一样大):Add→Rectange,右边Option中选Package geometry和place bound_top,绘制边界(此项可以不做);8.添加零件外框(集成电路再增加1脚标识):Add→line ,选package geometry和silkscreen_top选项,在line width文本框中输入线的粗度;同样方法在Assembly_top 层添加同样图形(可不用);9.增加Ref Des层零件标号:Layout→Labels→Refdes,打开Option选项,选择Silkscreen_Top,单击1脚附近,输入标号如U*,D*,R*之类,同样方法在Assembly_top层添加同样图形;10.取名save as存盘。

caputer生成网表报错原因解析#(精选.)

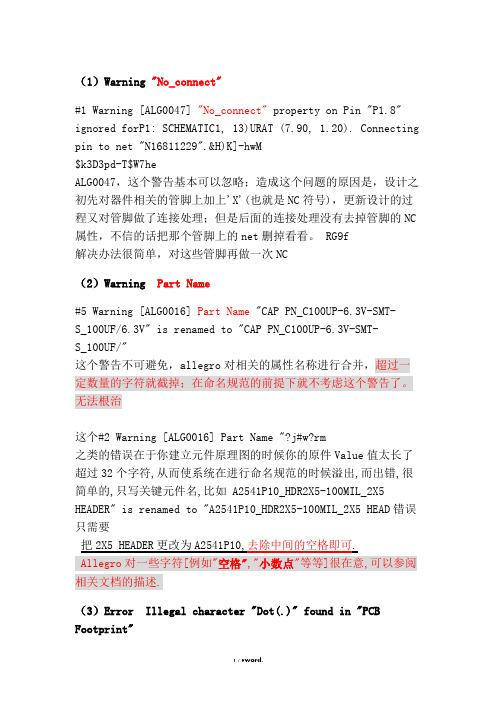

(1)Warning "No_connect"#1 Warning [ALG0047] "No_connect" property on Pin "P1.8" ignored forP1: SCHEMATIC1, 13)URAT (7.90, 1.20). Connecting pin to net "N16811229".&H)K]-hwM$k3D3pd-T$W7heALG0047,这个警告基本可以忽略;造成这个问题的原因是,设计之初先对器件相关的管脚上加上'X'(也就是NC符号),更新设计的过程又对管脚做了连接处理;但是后面的连接处理没有去掉管脚的NC 属性,不信的话把那个管脚上的net删掉看看。

RG9f解决办法很简单,对这些管脚再做一次NC(2)Warning Part Name#5 Warning [ALG0016] Part Name "CAP PN_C100UP-6.3V-SMT-S_100UF/6.3V" is renamed to "CAP PN_C100UP-6.3V-SMT-S_100UF/"这个警告不可避免,allegro对相关的属性名称进行合并,超过一定数量的字符就截掉;在命名规范的前提下就不考虑这个警告了。

无法根治这个#2 Warning [ALG0016] Part Name "?j#w?rm之类的错误在于你建立元件原理图的时候你的原件Value值太长了超过32个字符,从而使系统在进行命名规范的时候溢出,而出错,很简单的,只写关键元件名,比如 A2541P10_HDR2X5-100MIL_2X5 HEADER" is renamed to "A2541P10_HDR2X5-100MIL_2X5 HEAD错误只需要把2X5 HEADER更改为A2541P10,去除中间的空格即可.Allegro对一些字符[例如"空格","小数点"等等]很在意,可以参阅相关文档的描述.(3)Error Illegal character "Dot(.)" found in "PCB Footprint"#1 Error [ALG0081] Illegal character "Dot(.)" found in "PCB Footprint" property for component instance C255:PG16_AC97, PG16_AC97 (226.06, 132.08) .封装命名不能包含“.”(4)Error Illegal character "Forward Slash(/)" found in "PCB Footprint" property#1 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instanceC255: PG16_AC97, PG16_AC97 (226.06, 132.08) .#2 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instance D3: PG01_LED&Switch&7-Segment Disp, PG01_LED&Switch&7-Segment Disp (93.98, 33.02) .#3 Error [ALG0081] Illegal character "Forward Slash(/)" found in "PCB Footprint" property for component instanceC245: PG16_AC97, PG16_AC97 (205.74, 35.56) .封装命名不能包含“/”(5)比较隐藏的排除法Loading... E:\FPGA\SCH\allegro/pstchip.dat#34 WARNING(SPCODD-34): Expected ';' character on line 5308. Check the name and value syntax for invalid characters in theprimitive definition before the line number.ERROR(SPCODD-47): File ./allegro/pstchip.dat could not be loaded, and the packaging operation did not complete. Check the pxl.log file for the errors causingthis situation and package the design again.#53 ERROR(SPCODD-53): Packaging cannot be completed because packaging has encountered a null object ID. The design may not have been saved correctly. Save the schematic and rerun packaging.#187 Error [ALG0036] Unable to read logical netlist data.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\motherboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done*******掌握排错方法,查找文件pstchip.dat,第on line 5308 看看错误,便可以解决(6)封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决*********************************************************** *********************** Netlisting the design*********************************************************** **********************Design Name:E:\FPGA\SCH\basicboard.dsnNetlist Directory:E:\FPGA\SCH\allegroConfiguration File:D:\Cadence\SPB_16.2\tools\capture\allegro.cfgSpawning... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"#1 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property for component instance MG2: Basic, PG06_Stepmotor (180.34, 83.82) .#2 Error [ALG0081] Illegal character "White space" found in "PCB Footprint" property for component instance ISO1: Basic, PG05_DC Motor (134.62, 40.64) .#3 Info: PCB Editor does not support Dots(.), Forward Slash(/) and White space in footprint names. The supported characters include Alphabets, Numerics, Underscore(_) and Hyphen(-).#4 Aborting Netlisting... Please correct the above errors and retry.Exiting... "D:\Cadence\SPB_16.2\tools\capture\pstswp.exe" -pst -d "E:\FPGA\SCH\basicboard.dsn" -n"E:\FPGA\SCH\allegro" -c"D:\Cadence\SPB_16.2\tools\capture\allegro.cfg" -v 3 -j "PCB Footprint"*** Done ***封装命名中不能包含“小数点”、“/”、“空格”,把空格换成下划线或删除,可以解决(7)Warning#11 Warning [ALG0051] Pin "GND" is renamed to "GND#A6" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#12 Warning [ALG0051] Pin "GND" is renamed to "GND#A11" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#13 Warning [ALG0051] Pin "GND" is renamed to "GND#A1" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).#14 Warning [ALG0051] Pin "GND" is renamed to "GND#W8" after substituting illegal characters in Package XC3S1400A-4FG676-C_0FF , U1A: SCHEMATIC1, PG01_FPGACONFIG (2.40,3.10).这条警告信息,在命名规范的前提下就不考虑这个警告了。

CADENCE从原理图到PCB步骤(精)

CADENCE从原理图到PCB步骤一.原理图1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第一项OrCAD_Capture_CIS_option with capture,点击Ok进入Capture CIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Project manager(文件夹树图标)进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size 中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

4)生成网络表(Net List):在画板的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。

lec01OrCAD Capture简介

Ground

连接线路

当我们选择并放置好元件后,就可以进行连线 了。 Place Wire,或者单击右侧绘图工具栏第三 个图标,或者利用快捷键W或Shift+W。 注意:当我们的一部分元件的一端口排列在同 一条线上时,我们可以从第一个节点直接画到 最后一个节点,不用一个一个地点。

放置节点

Place Junction,或者单击右侧绘图工 具栏第六个图标,或者利用快捷键J或 Shift+J。

放置总线及总线引入线

Place Bus,或者单击右侧绘图工具栏 第五个图标,或者利用快捷键B或 Shift+B。 Place Bus Entry,或者单击右侧绘图工 具栏第七个图标,或者利用快捷键E或 Shift+E。

绘制电路原理图

加载元器件库 Place Part,或者单击右侧绘图工具栏 第二个图标,或者利用快捷键P或Shift+P

搜索 Place Part窗口中,点击Part Search按钮

Part

一些元件库的说明

ANALOG:模拟电子电路元件,如R, C, L BIPOLAR:三极管 DIODE:二极管 SOURCE:电源,如直流电压源、电流源, 交流电压源、电流源 SPECIAL:一些特殊元件:如电压表、电 流表

OrCAD Capture

OrCAD Capture简介

OrCAD/Capture CIS是一款功能强大的电 路图设计软件 设计方式

单页图纸绘制 拼接电路图设计(Flat designs) 分层电路图设计(Hierarchical designs)

Capture CIS软件的构成

cadence PCB 画图(傻瓜教程快速入门)

cadence画PCB板傻瓜教程(转帖)一.原理图1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用DesignEntryCIS,点击Ok进入CaptureCIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Projectmanager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1PageProperties,在PageSize中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1."olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!)3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选NewPart,或是NewPartFromSpreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

Cadence学习笔记1__原理图

新建元件时选择Heterogeneous,A部分和上面的一样画法,但是按键盘上的ctrl+N切换到B部分时,B部分是空白的,需要再画一次。

不管是Homogeneous还是Heterogeneous,点击工具栏ViewPakage,可以将A和B同时显示出来,如下图:

保存后,一个元件就画好了,画原理图时直接调用即可。

如果是由两部分组成的分裂元件,要在新建元件时在Parts per Pkg写2,这里分为Homogeneous和Heterogeneous两种。Homogeneous是只要画出A部分,B部分会默认的和A部分完全一样,Heterogeneous是画好A部分后,B部分仍然是空白的,需要再画。如果一个芯片包含了2个功能完全相同的部分,像下图中NE5532中的两个运放,就需要用到Homogeneous了,这里先选Homogeneous,点击ok。

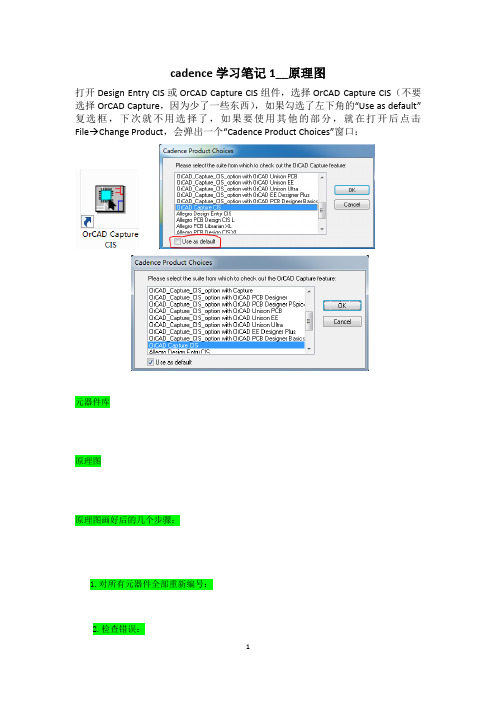

元器件

FileNewLibrary新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是NewPart From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCBFootprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

点击左侧工具栏make图标 ,所有的横线和竖线都变成粉红色的,这就生成了一个表格,鼠标右击选择Tag Pin Name,在引脚名这一列点一下,会在这一列最上面出现“Name”,同样的,右击选择TagPin Number,在引脚编号这一列点一下,会在这一列最上面出现“Num”,如果放错了,比如说该放Name的地方放成了Num,可以在放Num之后再点一次,Num就消失了,产生的结果如上图右。

Cadence 16.5 Design Entry CIS层次化电路设计详解

1 orca 也会独2 (的对名复量式模块当前概述Allegro D orcad Captur 也会简化绘图Design E 独立的工程本文假定子电路设a )建立b )将默(见图1)的对象,不改c )d ) 对子○1在对话框名复位为待定点“确定○2 再次在对话框量式自动编号切换至对模块;(对当前图纸中无Cadenc (Cadeegro Design En apture 工具进化绘图工作sign Entry CIS 工程opj 文件和文假定大家对电路设计建立子电路工将默认的SCH ;Cadence 不改倒也无碍在PAGE1图纸对子电路进执行Tools->An 对话框的Pack 为待定;确定”执行标再次执行Too 对话框的Pack 动编号;换至对话框的对Renumber纸中无复用模块adence 16.5 D Cadence 软件gn Entry CIS 工具进行了多方;y CIS 的层次化文件和设计大家对Cadence 设计步骤电路工程、子电SCHEMATIC1ence 是用图纸倒也无碍,但图纸上设计子电路进行元件序>Annotate Packaging 设置执行标注任务Tools->Anno Packaging 设置话框的PCB Edito mber Design 复用模块,则不16.5 Design 软件子电路CIS 工具是Cad 了多方面演进层次化电路设计设计dsn dence 基子电路MATIC1夹来代将来出现 图设计子电路,元件序号标注ate (小细节置页下注任务,元Annotate (见图置页下B Editor Reuse ign ……项可酌选该项esign Entry C 电路复用实战笔Cadence SPB 演进;合理应路设计总体上分文件存在。

本的的平坦式图dsn 文件;图纸夹改名为电名来代表一份图会出现很1 子电路工程,外引接口标注(这步很关细节,需选到页面下选中Res 所有元件名即变见图2页面下选中Incr euse 页面,项可酌情考虑该项); ntry CIS 层次实战笔记之原ce SPB 16.5最新理的应验层次体上分为子电路坦式图纸设计;采用平坦式名为电路名(一份图纸的,多SCHEMAITC 路工程结构及接口点添加端步很关键)点选到要标注Reset part re 名即变成附有)Incremental ,选中Gener 考虑,该项对当层次化电路之原理最新推出的验层次化电路设子电路设计和纸设计已经掌握式设计的(如Blk_Tra ,这里MAITC1结构及端口添加端口名,要标注的图纸夹art referances 成附有”?”的待ental reference Generate Reus 项对当前图纸电路设计图篇 by 李雪推出的电路图设电路设计会图设计和主电路设经掌握,计的基开始k_Transceiver 改名主为貌似不是很爽口标注,定义好各元图纸夹或工程ances to “的待定rence update Reuse Module前图纸中的复用设计详解李雪雷)路图设计工具会让图纸条理电路设计两步若不懂可先初步本开始步骤;eiver ),PAGE1要是为了引用时很爽;好各元件封装工程,菜单才被?”选项,定状态;date ,设为对元odule ,允许生的复用模块重新工具,它纸条理更加清晰,子电路名不用时区(见图才被激活,设为将元件为对元件进行成可块编号,基于原加清晰,电路以学习; 不用管分引用1); 激活); 将元件进行增可复用,若F o l l o w M e !3 点“确定e )主电路设a )建立b )执行系统Refenen Implame ImplamePath and 确定”执行标最后,电路设计建立主电路工执行菜单Pla 会弹出fenence :输入plamenation Ty plamentation Nth and Filenem 执行标注任务存盘,关闭子电设计步骤 电路工程、主电Place->Hiera 模块设置对话输入模块在主ion Type :选择tion Name :eneme :输入子图注任务,元子电路工程主电路的Hierarchical B 对话框,各参块在主电路中的子电路输入子电路子电路在2 子电路元件所有元件名自路工程;路的dsn 文件cal Block 工各参数置如路中的元件名电路的方子电路中复用模所在的图3 子路元件标注对名即自动编号文件,正常绘制或工具栏设置如下:元件名,如”实现方式,选复用模块名,dsn 文件路径插入子电路示标注对话框动编号,成主电路 B?”;Schematic ,输入路名(注意浏电路示意图并生成该图纸的电路; 的图标子 matic View 图纸夹注意浏览时调图纸的复用模块插入子电路模块 名称(如Blk_Tra 览时调整文件类复用模块;路模块(见图lk_Transceiver 类型为见图3); eiver ); .dsn );F o l l o w M e !边界作多处名复refe Renu 图纸并选路块当前号动打电路3 3.1 件重对话框中框;画完结束;c )调整d )子引用(e )对主○1在对话框名复位为待定点“确定○2再次执在对话框reference upd 切换至对Renumber De 图纸中的复用中Selec 路块名(对已经是主点“确定号,且(开子电电路元件逻辑生成主电路生复、缺失话框中画完后系统调整边界把子电路(如图4对主电路进行执行Tools->An 对话框的Pack 为待定; 确定”执行标再次执行Tools 对话框的Pack update ,设为换至对话框的ber Design for U 的复用模块Select Module 对于Genera 经是主电路确定”执行对各个此时,在其子电路件有不的编号辑生电路生成成时无需缺失等错误完成设置后,系统即自动在界框形状及框中路符像元件一样);路进行元件序号>Annotate Packaging 设置执行标注任务Tools->Annota Packaging 设置设为对元件话框的PCB Ed n for Using Reu 模块重新编号odule to Mark enerate Reuse 电路啦,呵呵执行标注任务复用模块重新编如果在主电路中路查看,就会发同的编号) 成及调用 网络表特殊操作,等错误;系统边添及各的在主电图4 层次化件序号标注ate (需中置页下注任务,元nnotate (见图置页对元件进行量CB Editor Reu g Reused modu 编号,Action Mark for 中Reuse Module ); 注任务,元编号;电路中双击子电现,不 ,由于的鼠标光标框上添加子电路端口的位布在主电路中用层次化设计主标注(这步很关先选中图纸页面下选中Res 所有元件名即变见图5)面下选中Incre 行增量式自动编r Reuse 面 module ,on 选为Uncon 窗中自动dule 项可所有元件名 击子电路块不同 在标注时确变为虚十字状子电路的外引位置布局,使其中使用,参与主计主电路原理步很关键) 纸夹) Reset part re 名即变成附有 Incremental 自动编号;页面,选中请求对当前Unconditional 动出现的子电可不选,因为件名即自动编路块,系统自的引用处的子 已经确定了层次十字状态,需要外引端口及更主电路的绘路图art referances 成附有”?”的待ental ; 当前onal ,子电动编统 了层次需要接及显示美观;的绘制示例 ances to “的待定 图5 主电关系,所网接着在主电路中要素(见图,而且可拷贝?”选项,定状态; 主电路标注以在网络表中不电路中画出见图3);插入、,设为将元件标注中不会模块插入操粘贴,将元件出现元F o l l o w M e !执行Tools->Create Netlist…,系统即生成网表;应注意的是此前对子电路中元件封装属性等描述将被主电路引用时继承;3.2 网表调用在PCB Editor中执行import logic即可导入逻辑网表及元件封装(基本的PCB设置及生成操作此处不表),跟平坦时设计时相同;--------------------------------------------- The End,敬请关注PCB篇-----------------------------------!eMwolloF。

Cadence中Capture向Allegro中导入网表时的常见错误

一、Capture生成netlist的时候报错:1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed错误解释:allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不一样,allegro.cfg 文件找不到是理所当然的。

处理办法:点生成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j"CC2430_DEMO"#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).#17 Aborting Netlisting... Please correct the above errors and retry.错误解释:Error [ALG0012] Property "PCB Footprint" missing from part <Part Reference>: <Schematic> , <Page> (<LocationX> , <LocationY)>A PCB Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.在Allegro中,每个器件都需要一个PCB封装。

跟我一步一步学习OrCAD-Capture-CIS(doc83页)

跟我一步一步学习OrCAD Capture CIS跟我一步一步学习 (1)OrCAD Capture CIS (1)第0章序言 (1)0.1 几款主流pcb软件比较 (1)0.2 Capture CIS中两个重要概念 (2)0.3 OrCAD Capture CIS 快捷键 (3)第1章 Capture 概述 (5)1.1 Capture 常用文档类型 (5)1.2 Capture软件包含的库 (5)1.3 Capture 设计流程: (6)1.4 原理图编辑窗口* (6)1.4.1 主命令菜单 (6)1.4.3 工具栏 (14)第2章 Capture工程管理 (15)2.1Capture 有三个主要工作窗口: (15)2.3建立工程及设置 (17)2.4 工程管理器 (20)2.5 原理图页相关操作 (21)第3章创建元器件及元器件库 (24)3.1 创建单个元件 (24)3.2 如何创建不规则图形元件 (29)3.3 创建复合封装元件 (33)3.3.1 Homogeneous类型元件画法 (34)3.3.2 Heterogeneous类型元件画法 (35)3.3.3 符合封装(分裂)元件的使用方法 (36)3.4 使用电子数据表创建和分割元件 (39)3.4.1 使用电子数据表创建元件 (39)3.4.2 使用电子数据表分割大元件 (40)3.5 CIS网上数据库直接抓取 (40)3.6 修改元器件 (43)第4章原理图的绘制 (45)4.1 添加元器件库及放置元件 (45)4.1.1 添加元件库 (45)4.1.2 放置普通元器件 (48)4.1.3 元器件的查找 (48)4.1.4 放置电源和地 (49)4.1.5 放置文本 (49)4.1.6 放置图形 (50)4.1.7 元件的基本操作 (50)4.2 创建电气连接 (51)4.2.1 在同一个页面创建电气互联 (51)4.2.2 在不同页面之间创建电气互联 (53)4.3 使用总线创建连接 (55)第5章层次电路设计 * (57)5.1 拼接式电路 (58)5.2 分层式电路结构 * (58)5.3 简单分层式电路图的绘制 * (59)5.4 复合分层式电路图的绘制 * (64)第6章 PCB高速布线预处理* (65)6.1 Capture到Allegro PCB Editor的信号属性分配 * (65)6.2 建立差分对 * (68)6.2.1 为两个Flat网络建立差分对(手动建立差分对)* (69)6.2.2 为多个at网络同时建立差分对(自动建立差分对)* (69)第7章原理图的后处理 (70)7.1 原理图检查 (70)7.1.1 原理图初步检查 (71)7.1.2 设计规则检查 (73)7.2 在原理图中搜索 (75)7.3 元件的添加与修改 (76)7.3.1 批量替换 replace cache (77)7.3.2 批量更新 update cache (78)7.3.3元器件编号 (78)7.4编辑元件的属性 (82)7.4.1 编辑元件属性的方法 (82)7.4.2 添加footprint属性 (84)7.4.3 定义元件分类属性 * (87)7.4.2 定义ROOM属性 * (89)7.4.2 定义按页摆放属性 * (89)7.5 生成网表与元件清单 (89)7.5.1 生成网表 (89)7.5.2 生成元件清单 (92)7.6 打印原理图 (94)第0章序言0.1几款主流PCB软件比较原理图设计软件:会ORCAD就可以了,支持的Netlist超多,基本是业界标准。

【Allegro档案】CADENCE从原理图到PCB

【Allegro档案】CADENCE从原理图到PCBCADENCE从原理图到PCB步骤⼀.原理图1.建⽴⼯程与其他绘图软件⼀样,OrCAD以Project来管理各种设计⽂件。

点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第⼀项OrCAD_Capture_CIS_option with capture,点击Ok 进⼊Capture CIS。

接下来是File--New--Project,在弹出的对话框中填⼊⼯程名、路径等等,点击Ok进⼊设计界⾯。

2.绘制原理图新建⼯程后打开的是默认的原理图⽂件SCHEMATIC1 PAGE1,右侧有⼯具栏,⽤于放置元件、画线和添加⽹络等等,⽤法和Protel类似。

点击上侧⼯具栏的Project manager(⽂件夹树图标)进⼊⼯程管理界⾯,在这⾥可以修改原理图⽂件名、设置原理图纸张⼤⼩和添加原理图库等等。

1)修改原理图纸张⼤⼩:双击SCHEMATIC1⽂件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size 中可以选择单位、⼤⼩等;2)添加原理图库:File--New--Library,可以看到在Library⽂件夹中多了⼀个library1.olb的原理图库⽂件,右键单击该⽂件,选择Save,改名存盘;3)添加新元件:常⽤的元件⽤⾃带的(⽐如说电阻、电容的),很多时候都要⾃⼰做元件,或者⽤别⼈做好的元件。

右键单击刚才新建的olb 库⽂件,选New Part,或是New Part From Spreadsheet,后者以表格的⽅式建⽴新元件,对于画管脚特多的芯⽚元件⾮常合适,可以直接从芯⽚Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,⽅便快捷。

Cadence中Capture向Allegro中导入网表时的常见错误

一、Capture生成netlist的时候报错:1.Unable to open c:\Cadence\PSD_14.2\tools\capture\allegro.cfg for reading. Please correct the above error(s) to proceed错误解释:allegro.cfg文件找不到或allegro.cfg文件不能打开,这个问题的根源是,有可能每台电脑上安装Allegro的的位置不一样,allegro.cfg 文件找不到是理所当然的。

处理办法:点生成netlist,点setup,修改路径为capture\allegro.cfg所在路径,把allegro.cfg文件的位置选择你现在安装目录的文件位置。

2. Spawning... "C:\Cadence\PSD_15.1\tools\capture\pstswp.exe" -pst -d "F:\gcht\CC2430\Projects\mysch.dsn" -n"C:\CADENCE\PSD_15.1\TOOLS\PROJECTS" -c"C:\Cadence\PSD_15.1\tools\capture\allegro.cfg" -v 3 -j"CC2430_DEMO"#1 Error [ALG0012] Property "PCB Footprint" missing from instance U3: SCHEMATIC1, PAGE1 (2.00, 2.10).#2 Error [ALG0012] Property "PCB Footprint" missing from instance C2: SCHEMATIC1, PAGE1 (2.30, 0.30).#17 Aborting Netlisting... Please correct the above errors and retry.错误解释:Error [ALG0012] Property "PCB Footprint" missing from part <Part Reference>: <Schematic> , <Page> (<LocationX> , <LocationY)>A PCB Footprint (JEDEC_TYPE in Allegro) is required for all parts in Allegro. Therefore all parts without this property are listed before aborting the netlisting. You can add the PCB Footprint property by selecting the part listed, then choosing Edit Properties from the pop-up menu and placing a value, such as dip14_3, on the part.在Allegro中,每个器件都需要一个PCB封装。

OrCAD_Capture_CIS软件基本操作

OrCAD Capture CIS 软件基本操作编写:樊伟敏Orcad Capture CIS 应用程序的操作方法与Window 窗口应用程序的操作方法类似。

本章在介绍Orcad Capture CIS 使用方法时,对窗口程序的概念不再做详细说明。

一、Capture CIS 的启动 1.Orcad 安装成功后,就可以启动和使用Capture 程序。

启动方法如下:1点击“开始”按钮,打开“开始”菜单;2将鼠标上移到“程序”命令,打开“程序”菜单;3将鼠标右移到“Orcad 10.5”命令,打开Orcad 菜单;4将鼠标再右移到“Capture CIS”菜单并单击,出现如图 1 所示的Orcad Capture 基本操作界面,同时打开的还有Session Log 窗口。

Session Log 窗口用于记录OrCAD/Captore CIS软件在运行过程中的多种信息。

图 1 Orcad Capture 的基本操作界面2.Capture CIS 的退出1从系统控制菜单关闭点击界面左上角Capture CIS 文字左侧的“系统控制菜单”图标,再点击其中的“关闭”命令,关闭程序。

2从文件菜单退出点击“File”下拉菜单,再点击“Exit”,执行退出命令,程序退出。

3使用关闭按钮单击Orcad Capture 程序窗口右上角的“关闭按钮”,关闭程序。

二、新建设计项目(Project)Capture 的Project 用于管理相关文件及属性。

新建Project 的同时,Capture 会自动创建相关的文件,如DSN、OPJ 文件等,根据创建的Project 类型的不同,生成的文件也不尽相同。

新建设计项目有 2 种方式:屏幕上弹出如图 2 所示New Project 对话框。

1使用下拉菜单:选择执行File/New/project 菜单子命令;2使用快捷键按钮:点击工具栏中的新建按钮。

图 2 New Project 对话框根据不同后续处理的要求,新建Project 时必须选择相应的类型。