AT91SAM7A2_0407中文资料

AT91SAM7 - CAN

SYNC_SEG: synchronize the different nodes PROP_SEG: compensate for signal delays across the network PHASE_SEG1 & 2: compensate for edge phase errors

1 Bit Time

10/11/2010

12

Protocol - CAN

CAN Bus Synchronization

Hard synchronization at Start Of Frame bit

Re-Synchronization on each Recessive to Dominant bit

10/11/2010

Protocol - CAN

Typical CAN Node

µController

CAN Controller RXD

CAN Transceiver CAN_L

CAN Bus is a simple 2-wire differential serial bus CAN Bus is terminated on each side by a 120 Ohm resistor

Frame Formats (3)

Four different frame formats: Data Frame : RTR Dominant ‘0’

Remote Frame : RTR Recessive ‘1’ and No Data Field

Data Frame has priority on Remote Frame

10/11/2010

7

Protocol - CAN

AT91SAM7S64学习资料

ARM入门笔记(1)前言如果您是一个单片机爱好者,当见到一款功能强大、性价比高的处理器时,一定会有一股很想掌握它、运用它的冲动,起码我是这样。

5年前第一次接触单片机(标准的51系列),就被它强大的功能所吸引,而痴迷于它,一直到今天。

在这期间的不同时期,各种增强型51,PIC、AVR,DSP和ARM等不同程度的吸引和诱惑着我。

有的已经玩过了,有的则没有,但很想玩的这股冲动一直存在心里,特别是对ARM。

记得2002年我就知道了ARM这个东东,眼睁睁地看着它一天天的火热,但由于对其开发工具及开发过程的不了解等原因一直只处于认识的阶段,尽管也曾玩过ZLG的2104开发板!可能是ZLG团队做的太出色的原因吧(详细的教材与源码,还有非常方便的工程模板),没过多久、没费多少劲就把里面的实验做完了,然后由于自已性格上的缺陷把它给扔在了一边,导致不到一个月就把大部分的东东还给了周老师。

直到前段时间,让我有机会真真正正的玩起了ARM!像最初玩8051那样的尽兴(出现问题时,吃不下饭、睡不着觉的那种痛苦和解决问题后的那种畅快)。

这篇文档就是记录了我在前段时间学习、调试目前最低价的ARM核处理器——AT91SAM7Sxx 时出现的问题与解决方法。

它尽量完整地记录了我从开始不懂ARM,到最终完成AT91SAM7S64各种外围实验的各个环节及整个过程,包括我在开始一个实验前的一些想法,实验目的,以及各个实验中,我以单片机的思维去思考时遇到的各种问题,和这些问题的解决方法。

现将自己的一点经验以及体会拿出来与大家共同分享,一来是希望能够为那些在ARM门口徘徊迷茫的人提供一些借鉴,使他们顺利越过这道门槛;二来是希望能够抛砖引玉,以结识更多有共同爱好的朋友。

由于我也是新手上路,文章中难免疏漏与错误,希望大家不吝指正,如果在调试AT91SAM7Sxx时有什么问题,欢迎大家共同讨论。

第一章开发工具与调试环境一.目标板所用实验板是参考ATMEL公司官方网站上发布的《AT91SAM7S-EK Evaluation Board User Guide》设计的,相当于AT91SAM7Sxx评估测试板,主要用于各种外围实验,结构框图如图1-1所示。

2010%E2%80%94%E2%80%942011%E5%AD%A6%E5%B9%B4%E5%88%9D%E4%B8%80%E7%AC%AC%E4%B8%80%E5%AD%A6%E6%9C%9F%E

2010——2011学年第一学期期中试卷初一英语注意事项:答案写在答题卷上。

本试卷满分100分,考试时间为90分钟。

第一部分听力(20分)一、找出你所听到的选项吗?试试看,你一定行的!(5分)()1. A. U B. Q C. W()2. A. SZX B. FIX C. NIF()3. A. floor B. fly C. flower()4. A. 587659 B. 589659 C. 586759()5.A. they B. there C. them二.情景反映,根据所听到的句子选择正确答语补全对话。

(5分)()6. A. Good morning, Ben B. Good afternoon, AliceC. Good evening, Dale()7. A. No, I’m not. B. No, I can’t. C. No, I don’t.()8. A. I am James B. That’s a ball C. It’s an egg.()9. A. It’s my father B. It’s a bike C. It’s John.()10. A. It’s black B. It’s a black C. They are black三.你先来听听他们在谈些什么,然后再来回答我的问题!(5分)听对话,回答11——12小题( )11. Where is the sign?A. In front of the house.B. In the middle of the park.C. On the right of the tree.( )12. What’s on the sign?A. Don’t feed the birds.B. Don’t feed the animals.C. Don’t feed her sister. 听对话,回答13——15小题( )13. What’s on the desk?A. A school bag.B. A radio.C. A camera.( )14. Whose camera is it?A. Peter’s.B. Jill’s.C. Mike’s.( )15. Is he a driver?A. He’s a worker.B. No, he isn’t.C. Yes, he is.四.听短文,填入所缺单词。

AT91SAM7S32参数芯片解密

AT91SAM7S32/64芯片解密AT91SAM7S32/64是接脚少的智能型ARM7(Smart ARM7)微控制器系列(SAM7S 系列)的首批产品,其闪存密度分别为32KB和64KB。

该系列还提供128KB及256KB 版本,型号为AT91SAM7S128/256。

这些产品整合了全套安全运行功能,其安全运行功能包括由片上(on-chip)RC振荡器计时的监视器、电源监控器以及闪存的硬件保护。

由于 AT91SAM7微控制器提供低成本的开发工具,因此能为因成本问题一直只能提供8位性能的众多应用带来32位的实时处理能力。

AT91SAM7S系列是专为把8位驱动器升级到32位而设的,特别是提升实时应用的固定性能。

该产品可通过嵌入式闪存(这是实现固定性能的先决条件)以27 MIPS的速度实现单周期指令存取。

其高级中断控制器可加强ARM7处理器的基本中断功能,以便在最少的指令周期内提供向量式优先中断。

此外,它的硬件位设置和重设注册可实现单周期位操作,从而无需屏蔽“读/改/写”序列。

原有代码的移植和鉴定对于需要升级至32位MCU的8位微控制器用户而言是一项重大任务。

为了便于应用开发,AT91SAM7S产品内置了强大的除错功能,其核心为JTAG 在线仿真接口,并在除错过程中辅以错位地址检测和监视器停用等片上硬件。

另外,Atmel还提供了一套工具包,包括评估板、JTAG-ICE 接口、工程实例以及与8位微控制器相同的开发工具,从而让用户加快学习速度。

AT91SAM7S微控制器集成了的功能还包括针对PC机连通性的USB 2.0全速设备端口,以及各种通信与控制接口如 8信道10位模数转换器。

外围数据控制器提供直接内存存取功能,可减小数据在外部I/O 信道和内存之间传输时的处理器运件时间。

其并行I/O控制器以一套32条可编程通用I/O线路来实现外围I/O的多任务操作。

另外,片上电压调节器可以实现3.3伏电压下的单电源工作。

AT91SAM7_DataSheet

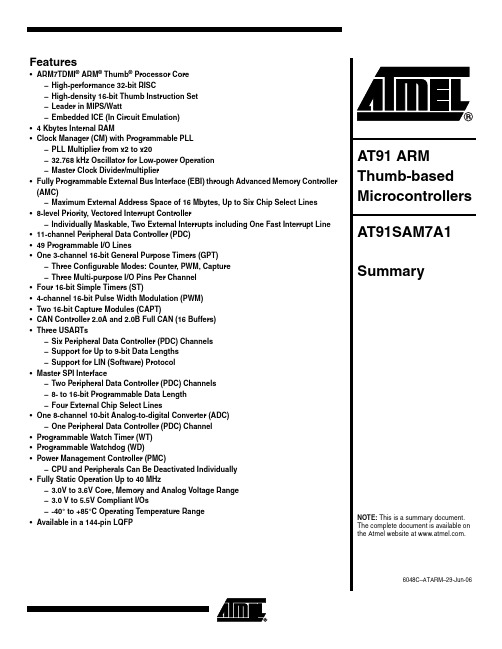

6117AS–ATARM–20-Oct-04Features•Incorporates the ARM7TDMI ® ARM ® Thumb ® Processor–High-performance 32-bit RISC Architecture –High-density 16-bit Instruction Set –Leader in MIPS/Watt–Embedded ICE In-circuit Emulation, Debug Communication Channel Support •256 Kbytes of Internal High-speed Flash, Organized in 1024 Pages of 256 Bytes –Single Cycle Access at Up to 30 MHz in Worst Case Conditions–Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed–Page Programming Time: 4 ms, Including Page Auto-erase, Full Erase Time: 10 ms –10,000 Write Cycles, 10-year Data Retention Capability, Sector Lock Capabilities, Flash Security Bit–Fast Flash Programming Interface for High Volume Production•64 Kbytes of Internal High-speed SRAM, Single-cycle Access at Maximum Speed •Memory Controller (MC)–Embedded Flash Controller, Abort Status and Misalignment Detection •Reset Controller (RSTC)–Based on Power-on Reset and Low-power Factory-calibrated Brownout Detector –Provides External Reset Signal Shaping and Reset Source Status •Clock Generator (CKGR)–Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and one PLL •Power Management Controller (PMC)–Software Power Optimization Capabilities, Including Slow Clock Mode (Down to 500 Hz) and Idle Mode–Three Programmable External Clock Signals •Advanced Interrupt Controller (AIC)–Individually Maskable, Eight-level Priority, Vectored Interrupt Sources–Two External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt Protected•Debug Unit (DBGU)–2-wire UART and Support for Debug Communication Channel interrupt, Programmable ICE Access Prevention •Periodic Interval Timer (PIT)–20-bit Programmable Counter plus 12-bit Interval Counter •Windowed Watchdog (WDT)–12-bit key-protected Programmable Counter–Provides Reset or Interrupt Signals to the System–Counter May Be Stopped While the Processor is in Debug State or in Idle Mode •Real-time Timer (RTT)–32-bit Free-running Counter with Alarm –Runs Off the Internal RC Oscillator•One Parallel Input/Output Controller (PIOA)–Thirty-two Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os –Input Change Interrupt Capability on Each I/O Line–Individually Programmable Open-drain, Pull-up Resistor and Synchronous Output •Eleven Peripheral Data Controller (PDC) Channels•One USB 2.0 Full Speed (12 Mbits per second) Device Port–On-chip Transceiver, 328-byte Configurable Integrated FIFOs •One Synchronous Serial Controller (SSC)–Independent Clock and Frame Sync Signals for Each Receiver and Transmitter –I²S Analog Interface Support, Time Division Multiplex Support–High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer •Two Universal Synchronous/Asynchronous Receiver Transmitters (USART)–Individual Baud Rate Generator, IrDA Infrared Modulation/Demodulation–Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support –Full Modem Line Support on USART1•One Master/Slave Serial Peripheral Interface (SPI)–8- to 16-bit Programmable Data Length, Four External Peripheral Chip SelectsAT91 ARM ® Thumb ®-based Microcontrollers AT91SAM7S256Summary PreliminaryNote: This is a summary document. A complete document is not available at this time. For more information, please contact your local Atmel sales office.2AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04•One Three-channel 16-bit Timer/Counter (TC)–Three External Clock Inputs, Two Multi-purpose I/O Pins per Channel –Double PWM Generation, Capture/Waveform Mode, Up/Down Capability •One Four-channel 16-bit PWM Controller (PWMC)•One Two-wire Interface (TWI)–Master Mode Support Only, All Two-wire Atmel EEPROMs Supported•One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os •IEEE 1149.1 JTAG Boundary Scan on All Digital Pins•5V-tolerant I/Os, including Four High-current Drive I/O lines, Up to 16 mA Each •Power Supplies–Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components –3.3V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply –1.8V VDDCORE Core Power Supply with Brownout Detector•Fully Static Operation: Up to 55 MHz at 1.65V and 85°C Worst Case Conditions •Available in a 64-lead LQFP PackageDescriptionAtmel’s AT91SAM7S256 is a member of a series of low pincount Flash microcontrollers based on the 32-bit ARM RISC processor. It features a 256 Kbyte high-speed Flash and a 64 Kbyte SRAM, a large set of peripherals, including a USB 2.0 device, and a com-plete set of system functions minimizing the number of external components. The device is an ideal migration path for 8-bit microcontroller users looking for additional per-formance and extended memory.The embedded Flash memory can be programmed in-system via the JTAG-ICE inter-face or via a parallel interface on a production programmer prior to mounting. Built-in lock bits and a security bit protect the firmware from accidental overwrite and preserves its confidentiality.The AT91SAM7S256 system controller includes a reset controller capable of managing the power-on sequence of the microcontroller and the complete system. Correct device operation can be monitored by a built-in brownout detector and a watchdog running off an integrated RC oscillator.The AT91SAM7S256 is a general-purpose microcontroller. Its integrated USB Device port makes it an ideal device for peripheral applications requiring connectivity to a PC or cellular phone. Its aggressive price point and high level of integration pushes its scope of use far into the cost-sensitive, high-volume consumer market.3AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Block DiagramFigure 1. AT91SAM7S256 Block DiagramTDI TDO TMS TCK NRSTFIQIRQ0-IRQ1PCK0-PCK2PMCPeripheral BridgePeripheral Data ControllerAICPLL RCOSCSRAM64 KbytesARM7TDMI ProcessorICEJT AG SCANJTAGSELPIOAUSART0SSCTimer CounterRXD0TXD0SCK0RTS0CTS0NPCS0NPCS1NPCS2NPCS3MISO MOSI SPCK Flash256 KbytesReset ControllerDRXD DTXDTF TK TD RD RK RF TCLK0TCLK1TCLK2TIOA0TIOB0TIOA1TIOB1TIOA2TIOB2Memory Controller Abort StatusAddress Decoder Misalignment DetectionP I OP I OAPBPOREmbedded Flash ControllerAD0AD1AD2AD3ADTRGPLLRC 11 ChannelsPDCPDC USART1RXD1TXD1SCK1RTS1CTS1DCD1DSR1DTR1RI1PDCPDC PDCPDC SPIPDCADCADVREFPDCPDCTC0TC1TC2TWD TWCKTWIOSC XIN XOUTVDDIN PWMCPWM0PWM1PWM2PWM31.8 V Voltage RegulatorUSB DeviceFIFODDM DDPT r a n s c e i v e rGNDVDDOUT BOD VDDCOREVDDCOREAD4AD5AD6AD7VDDFLASHFast Flash Programming InterfaceERASEP I OPGMD0-PGMD15PGMNCMDPGMEN0-PGMEN1PGMRDY PGMNVALID PGMNOE PGMCKPGMM0-PGMM3VDDIOTST DBGUPDCPDCP I OPIT WDT RTTSystem ControllerVDDCORE4AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Signal DescriptionTable 1. Signal Description ListSignal NameFunctionTypeActive LevelCommentsPowerVDDIN Voltage Regulator Power Supply Input Power 3.0V to 3.6V VDDOUT Voltage Regulator Output Power 1.85V nominal VDDFLASH Flash Power Supply Power 3.0V to 3.6V VDDIO I/O Lines Power Supply Power 3.0V to 3.6V VDDCORE Core Power Supply Power 1.65V to 1.95V VDDPLL PLL Power 1.65V to 1.95VGNDGroundGroundClocks, Oscillators and PLLsXIN Main Oscillator Input Input XOUT Main Oscillator Output Output PLLRC PLL FilterInput PCK0 - PCK2Programmable Clock OutputOutputICE and JTAGTCK Test Clock Input No pull-up resistor TDI Test Data In Input No pull-up resistor TDO Test Data Out Output TMS Test Mode Select Input No pull-up resistor JT AGSELJTAG SelectionInputPull-down resistor Flash MemoryERASEFlash and NVM Configuration Bits Erase CommandInputHighPull-down resistorReset/TestNRST Microcontroller Reset I/O LowPull-Up resistor TSTTest Mode SelectInputPull-down resistorDebug UnitDRXD Debug Receive Data Input DTXDDebug Transmit DataOutput AICIRQ0 - IRQ1External Interrupt Inputs Input FIQFast Interrupt InputInput5AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04PIOP A0 - P A31Parallel IO Controller AI/OPulled-up input at resetUSB Device PortDDM USB Device Port Data - Analog DDPUSB Device Port Data +Analog USARTSCK0 - SCK1Serial Clock I/O TXD0 - TXD1Transmit Data I/O RXD0 - RXD1 Receive Data Input RTS0 - RTS1Request To Send Output CTS0 - CTS1Clear To Send Input DCD1Data Carrier Detect Input DTR1Data Terminal Ready Output DSR1Data Set Ready Input RI1Ring IndicatorInputSynchronous Serial ControllerTD Transmit Data Output RD Receive Data Input TK Transmit Clock I/O RK Receive Clock I/O TF Transmit Frame Sync I/O RFReceive Frame SyncI/O Timer/CounterTCLK0 - TCLK2External Clock Inputs Input TIOA0 - TIOA2I/O Line A I/O TIOB0 - TIOB2I/O Line BI/O PWM ControllerPWM0 - PWM3PWM ChannelsOutput SPIMISO Master In Slave Out I/O MOSI Master Out Slave In I/O SPCK SPI Serial ClockI/O NPCS0SPI Peripheral Chip Select 0I/O Low NPCS1-NPCS3SPI Peripheral Chip Select 1 to 3OutputLowTable 1. Signal Description List (Continued)Signal NameFunctionTypeActive LevelComments6AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Two-Wire InterfaceTWD Two-wire Serial Data I/O TWCKTwo-wire Serial ClockI/OAnalog-to-Digital ConverterAD0-AD3Analog Inputs Analog Digital pulled-up inputs at reset AD4-AD7Analog Inputs Analog Analog InputsADTRG ADC Trigger Input ADVREFADC ReferenceAnalogFast Flash Programming InterfacePGMEN0-PGMEN1Programming Enabling Input PGMM0-PGMM3Programming Mode Input PGMD0-PGMD15Programming Data I/O PGMRDY Programming Ready Output High PGMNVALID Data Direction Output Low PGMNOE Programming Read Input LowPGMCK Programming Clock Input PGMNCMDProgramming CommandInputLow Table 1. Signal Description List (Continued)Signal NameFunctionTypeActive LevelComments7AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Package and PinoutThe AT91SAM7S256 is available in a 64-lead LQFP package.64-lead LQFP Mechanical OverviewFigure 2 shows the orientation of the 64-lead LQFP package. A detailed mechanicaldescription is given in the section Mechanical Characteristics of the full datasheet.Figure 2. 64-lead LQFP Package Pinout (Top View)Pinout334948321716164Table 2. AT91SAM7S256 Pinout in 64-lead LQFP Package1ADVREF 17GND 33TDI 49TDO 2GND 18VDDIO 34P A6/PGMNOE 50JTAGSEL 3AD419P A16/PGMD435P A5/PGMRDY 51TMS 4AD520P A15/PGMD336P A4/PGMNCMD 52P A315AD621P A14/PGMD237P A27/PGMD1553TCK 6AD722P A13/PGMD138P A2854VDDCORE 7VDDIN 23P A24/PGMD1239NRST 55ERASE 8VDDOUT 24VDDCORE 40TST 56DDM 9P A17/PGMD5/AD025P A25/PGMD1341P A2957DDP 10P A18/PGMD6/AD126P A26/PGMD1442P A3058VDDIO 11P A21/PGMD927P A12/PGMD043P A359VDDFLASH12VDDCORE 28P A11/PGMM344P A260GND 13P A19/PGMD7/AD229P A10/PGMM245VDDIO 61XOUT 14P A22/PGMD1030P A9/PGMM146GND 62XIN/PGMCK 15P A23/PGMD1131P A8/PGMM047P A1/PGMEN163PLLRC 16P A20/PGMD8/AD332P A7/PGMNVALID48P A0/PGMEN064VDDPLL8AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Power ConsiderationsPower SuppliesThe AT91SAM7S256 has six types of power supply pins and integrates a voltage regu-lator, allowing the device to be supplied with only one voltage. The six power supply pin types are:•VDDIN pin. It powers the voltage regulator; voltage ranges from 3.0V to 3.6V , 3.3V nominal. If the voltage regulator is not used, VDDIN should be connected to GND.•VDDOUT pin. It is the output of the 1.8V voltage regulator.•VDDIO pin. It powers the I/O lines and the USB transceivers; dual voltage range is supported. Ranges from 3.0V to 3.6V , 3.3V nominal.•VDDFLASH pin. It powers a part of the Flash and is required for the Flash to operate correctly; voltage ranges from 3.0V to 3.6V, 3.3V nominal.•VDDCORE pins. They power the logic of the device; voltage ranges from 1.65V to 1.95V , 1.8V typical. It can be connected to the VDDOUT pin with decouplingcapacitor. VDDCORE is required for the device, including its embedded Flash, to operate correctly.•VDDPLL pin. It powers the oscillator and the PLL. It can be connected directly to the VDDOUT pin.No separate ground pins are provided for the different power supplies. Only GND pins are provided and should be connected as shortly as possible to the system ground plane.Power ConsumptionThe AT91SAM7S256 has a static current of less than 60 µA on VDDCORE at 25°C,including the RC oscillator, the voltage regulator and the power-on reset when the brownout detector is deactivated. Activating the brownout detector adds 20 µA static current.The dynamic power consumption on VDDCORE is less than 50 mA at full speed when running out of the Flash. Under the same conditions, the power consumption on VDDFLASH does not exceed 10 mA.Voltage RegulatorThe AT91SAM7S256 embeds a voltage regulator that is managed by the System Controller.In Normal Mode, the voltage regulator consumes less than 100 µA static current and draws 100 mA of output current.The voltage regulator also has a Low-power Mode. In this mode, it consumes less than 20 µA static current and draws 1 mA of output current.Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscillations. The best way to achieve this is to use two capacitors in parallel: one external 470 pF (or 1 nF) NPO capacitor must be connected between VDDOUT and GND as close to the chip as possible. One external 2.2 µF (or 3.3 µF) X7R capacitor must be connected between VDDOUT and GND.Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. The input decoupling capacitor should be placed close to the chip. For example, two capacitors can be used in parallel: 100 nF NPO and 4.7 µF X7R.9AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Typical Powering SchematicsThe AT91SAM7S256 supports a 3.3V single supply mode. The internal regulator input connected to the 3.3V source and its output feeds VDDCORE and the VDDPLL. Figure 3 shows the power schematics to be used for USB bus-powered systems.Figure 3. 3.3V System Single Power Supply SchematicPower Source ranges from 4.5V (USB)to 18V3.3VVDDINVoltage RegulatorVDDOUTVDDIODC/DC ConverterVDDCOREVDDFLASHVDDPLL10AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04I/O Lines ConsiderationsJTAG Port PinsTMS, TDI and TCK are schmitt trigger inputs. TMS and TCK are 5-V tolerant, TDI is not.TMS, TDI and TCK do not integrate a pull-up resistor.TDO is an output, driven at up to VDDIO, and has no pull-up resistor.The pin JTAGSEL is used to select the JTAG boundary scan when asserted at a high level. The pin JTAGSEL integrates a permanent pull-down resistor of about 15 k Ω to GND, so that it can be left unconnected for normal operations.Test PinThe pin TST is used for manufacturing test or fast programming mode of the AT91SAM7S256 when asserted high. The pin TST integrates a permanent pull-down resistor of about 15 k Ω to GND, so that it can be left unconnected for normal operations. To enter fast programming mode, the pin TST and the pins PA0 and PA1 should be tied high.Driving the pin TST at a high level while PA0 or PA1 is driven at 0 leads to unpredictable results.Reset PinThe pin NRST is bidirectional. It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components or asserted low exter-nally to reset the microcontroller. There is no constraint on the length of the reset pulse,and the reset controller can guarantee a minimum pulse length. This allows connection of a simple push-button on the pin NRST as system user reset, and the use of the signal NRST to reset all the components of the system.The pin NRST integrates a permanent pull-up resistor to VDDIO .ERASE PinThe pin ERASE is used to re-initialize the Flash content and some of its NVM bits. It integrates a permanent pull-down resistor of about 15 k Ω to GND, so that it can be left unconnected for normal operations.PIO Controller A LinesAll the I/O lines PA0 to PA31 are 5V-tolerant and all integrate a programmable pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the PIO controllers.5V-tolerant means that the I/O lines can drive voltage level according to VDDIO, but can be driven with a voltage of up to 5.5V. However, driving an I/O line with a voltage over VDDIO while the programmable pull-up resistor is enabled can lead to unpredictable results. Care should be taken, in particular at reset, as all the I/O lines default to input with pull-up resistor enabled at reset.I/O Line Drive LevelsThe PIO lines PA0 to PA3 are high-drive current capable. Each of these I/O lines can drive up to 16 mA permanently.The remaining I/O lines (PA4 to PA31) can draw only 8 mA.However, the total current drawn by all the I/O lines cannot exceed 150 mA.11AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Processor and ArchitectureARM7TDMI Processor•RISC processor based on ARMv4T Von Neumann architecture –Runs at up to 55 MHz, providing 0.9 MIPS/MHz •Two instruction sets–ARM ® high-performance 32-bit instruction set –Thumb ® high code density 16-bit instruction set •Three-stage pipeline architecture–Instruction Fetch (F)–Instruction Decode (D)–Execute (E)Debug and Test Features •Integrated embedded in-circuit emulator –Two watchpoint units–Test access port accessible through a JTAG protocol –Debug communication channel•Debug Unit –Two-pinUART –Debug communication channel interrupt handling –Chip ID Register•IEEE1149.1 JTAG Boundary-scan on all digital pinsMemory Controller•Bus Arbiter –Handles requests from the ARM7TDMI and the Peripheral Data Controller •Address decoder provides selection signals for –Three internal 1 Mbyte memory areas –One 256 Mbyte embedded peripheral area•Abort Status Registers –Source, Type and all parameters of the access leading to an abort are saved –Facilitates debug by detection of bad pointers •Misalignment Detector –Alignment checking of all data accesses –Abort generation in case of misalignment•Remap Command –Remaps the SRAM in place of the embedded non-volatile memory –Allows handling of dynamic exception vectors•Embedded Flash Controller –Embedded Flash interface, up to three programmable wait states–Prefetch buffer, bufferizing and anticipating the 16-bit requests, reducing the required wait states–Key-protected program, erase and lock/unlock sequencer –Single command for erasing, programming and locking operations –Interrupt generation in case of forbidden operation12AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Peripheral Data Controller•Handles data transfer between peripherals and memories •Eleven channels –Two for each USART –Two for the Debug Unit–Two for the Serial Synchronous Controller –Two for the Serial Peripheral Interface –One for the Analog-to-digital Converter•Low bus arbitration overhead –One Master Clock cycle needed for a transfer from memory to peripheral –Two Master Clock cycles needed for a transfer from peripheral to memory•Next Pointer management for reducing interrupt latency requirements13AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Memory•256 Kbytes of Flash Memory –1024 pages of 256 bytes–Fast access time, 30 MHz single-cycle access in Worst Case conditions –Page programming time: 4 ms, including page auto-erase –Page programming without auto-erase: 2 ms –Full chip erase time: 10 ms–10,000 write cycles, 10-year data retention capability –16 lock bits, each protecting 16 sectors of 64 pages –Protection Mode to secure contents of the Flash •64 Kbytes of Fast SRAM–Single-cycle access at full speedMemory MappingInternal SRAMThe AT91SAM7S256 embeds a high-speed 64-Kbyte SRAM bank. After reset and until the Remap Command is performed, the SRAM is only accessible at address 0x00200000. After Remap, the SRAM also becomes available at address 0x0.Internal FlashThe AT91SAM7S256 features one bank of 256 Kbytes of Flash. At any time, the Flash is mapped to address 0x0010 0000. It is also accessible at address 0x0 after the reset and before the Remap Command.Figure 4. Internal Memory Mapping256M BytesFlash Before Remap SRAM After Remap Undefined Areas(Abort)0x000F FFFF0x001F FFFF0x002F FFFF 0x0FFF FFFF1 M Bytes1 M Bytes1 M Bytes253 M BytesInternal FlashInternal SRAM0x0000 00000x0010 00000x0020 00000x0030 000014AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Embedded FlashFlash OverviewThe Flash of the AT91SAM7S256 is organized in 1024 pages of 256 bytes. The 262,144bytes are organized in 32-bit words.The Flash contains a 256-byte write buffer, accessible through a 32-bit interface.The Flash benefits from the integration of a power reset cell and from the brownout detector. This prevents code corruption during power supply changes, even in the worst conditions.Embedded Flash ControllerThe Embedded Flash Controller (EFC) manages accesses performed by the masters of the system. It enables reading the Flash and writing the write buffer. It also contains a User Interface, mapped within the Memory Controller on the APB. The User Interface allows:•programming of the access parameters of the Flash (number of wait states, timings, etc.)•starting commands such as full erase, page erase, page program, NVM bit set, NVM bit clear, etc.•getting the end status of the last command •getting error status•programming interrupts on the end of the last commands or on errorsThe Embedded Flash Controller also provides a dual 32-bit Prefetch Buffer that opti-mizes 16-bit access to the Flash. This is particularly efficient when the processor is running in Thumb mode.Lock RegionsThe Embedded Flash Controller manages 16 lock bits to protect 16 regions of the flash against inadvertent flash erasing or programming commands. The AT91SAM7S256contains 16 lock regions and each lock region contains 64 pages of 256 bytes. Each lock region has a size of 16 Kbytes.If a locked-regions erase or program command occurs, the command is aborted and the EFC trigs an interrupt.The 16 NVM bits are software programmable through the EFC User Interface. The com-mand "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.Security Bit FeatureThe AT91SAM7S256 features a security bit, based on a specific NVM-Bit. When the security is enabled, any access to the Flash, either through the ICE interface or through the Fast Flash Programming Interface, is forbidden. This ensures the confidentiality of the code programmed in the Flash.This security bit can only be enabled, through the Command "Set Security Bit" of the EFC User Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1, and after a full flash erase is performed. When the security bit is deac-tivated, all accesses to the flash are permitted.It is important to note that the assertion of the ERASE pin should always be longer than 50 ms.As the ERASE pin integrates a permanent pull-down, it can be left unconnected during normal operation. However, it is safer to connect it directly to GND for the final application.15AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04Non-volatile Brownout Detector ControlTwo general purpose NVM (GPNVM) bits are used for controlling the brownout detector (BOD), so that even after a power loss, the brownout detector operations remain in their state.These two GPNVM bits can be cleared or set respectively through the commands "Clear General-purpose NVM Bit" and "Set General-purpose NVM Bit" of the EFC User Interface.•GPNVM Bit 0 is used as a brownout detector enable bit. Setting the GPNVM Bit 0 enables the BOD, clearing it disables the BOD. Asserting ERASE clears the GPNVM Bit 0 and thus disables the brownout detector by default.•The GPNVM Bit 1 is used as a brownout reset enable signal for the reset controller. Setting the GPNVM Bit 1 enables the brownout reset when a brownout is detected, Clearing the GPNVM Bit 1 disables the brownout reset. Asserting ERASE disables the brownout reset by default.Calibration BitsEight NVM bits are used to calibrate the brownout detector and the voltage regulator.These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.Fast Flash Programming InterfaceThe Fast Flash Programming Interface allows programming the device through either aserial JTAG interface or through a multiplexed fully-handshaked parallel port. It allows gang-programming with market-standard industrial programmers.The FFPI supports read, page program, page erase, full erase, lock, unlock and protect commands.The Fast Flash Programming Interface is enabled and the Fast Programming Mode is entered when the TST pin and the PA0 and PA1 pins are all tied high.The Flash of the AT91SAM7S256 is organized in 1024 pages of 256 bytes. It reads as 65,536 32-bit words.The Flash contains a 256-byte write buffer, accessible through a 32-bit interface.16AT91SAM7S256 Summary Preliminary6117AS–ATARM–20-Oct-04System ControllerThe System Controller manages all vital blocks of the microcontroller: interrupts, clocks,power, time, debug and reset.Figure 5. System Controller Block DiagramNRSTSLCKAdvanced Interrupt ControllerReal-Time Timer Periodic Interval Timer Reset ControllerP A0-P A31periph_nreset System ControllerWatchdog Timerwdt_fault WDRPROCPIO ControllerPORBODRCOSCgpnvm[0]calenPower Management ControllerOSCPLLXIN XOUTPLLRC MAINCKPLLCKpit_irqMCK proc_nresetwdt_irq periph_irq{2]periph_nreset periph_clk[2..14]PCK MCKpmc_irqUDPCK nirqnfiq rtt_irqEmbedded Peripheralsperiph_clk[2]pck[0-2]in out enableARM7TDMISLCKSLCK irq0-irq1fiq irq0-irq1fiqperiph_irq[4..14]periph_irq[2..14]intintperiph_nresetperiph_clk[4..14]Embedded Flashflash_poejtag_nresetflash_poe gpnvm[0..1]flash_wrdis flash_wrdis proc_nresetperiph_nreset dbgu_txddbgu_rxdpit_irq rtt_irq dbgu_irq pmc_irq rstc_irqwdt_irq rstc_irqSLCKgpnvm[1]Boundary Scan TAP Controllerjtag_nresetice_nreset debugPCK debug idledebugMemory ControllerMCK proc_nresetbod_rst_enproc_nreset periph_nreset periph_nresetidleDebug Unitdbgu_irq MCKdbgu_rxd periph_nresetforce_ntrst dbgu_txdUSB DevicePortUDPCK periph_nreset periph_clk[11]periph_irq[11]usb_suspendusb_suspendVoltage RegulatorstandbyVoltage Regulator Mode Controllersecurity_bitcalice_nreset force_ntrstcal。

AT91SAM7X256中文版

– 64K 字节 (AT91SAM7X256) – 32K 字节 (AT91SAM7X128)

• 内存控制器 (MC)

– 嵌入式 Flash 控制器, 中止状态和未对齐检测

• 复位控制器 (RSTC)

– 基于上电复位单元和经过工厂标定的低功耗掉电检测 – 提供外部信号整形和复位源状态

2. AT91SAM7X256 和 AT91SAM7X128 的配置比较

AT91SAM7X256 和 AT91SAM7X128 仅在存储器大小上有所差别。Table 2-1 是这两个设备的主 要配置差别。

Table 2-1. 配置差别

设备 AT91SAM7X256 AT91SAM7X128

Flash 256K 字节 128K 字节

欢迎访问本公司网站 /

免责声明

本资料英文版本来源于互联网,将其译成中文版本以便于中国广大ARM爱好者交 流、学习,请勿用于任何商业目的。

本文件为英文原本之非正式翻译,不保证翻译的真实性和准确性,同时声明文件以英 文版本为准。

由于嵌入式领域我国并无统一名称规范,大部分术语均直译,另有部分术语参考了 ATMEL 公司的 AT91SAM7S64 中文资料,由于译者对嵌入式领域理解的深度有限,难 免有疏漏和错误之处,也希望大家指出。

– 8 个完全可编程消息对象邮箱, 16 位时间标志计数器

• 一个同步串行控制器 (SSC)

– 每个接受器和发送器都有独立的时钟和帧同步信号 – 支持I²S 模拟接口, 支持分时复用 – 支持 32 位数据传输的高速连续数据流功能

• 两个通用同步/异步收发器 (USART)

– 独立的波特率发生器, 可以 IrDA 红外调制/解调 – 支持 ISO7816 T0/T1 智能卡, 硬件握手信号以及 RS485 – USART1 口支持全 Modem 线

UART接口说明

|AT91C_US_NBSTOP_1_BIT |AT91C_US_PAR_NONE

TxD0 3232 AT91SAM RxD0 电平转换

7X256

TxD0

RxD0

其它 通信设备

Hale Waihona Puke TxD0RxD0 PC机串口

USART框图

硬件握手通信通过RTS 与CTS 引脚自动管理溢出控制。 USART支持与使能由发送器到接收器的数据传输的外设数据控制器的连接。

PDC提供没有处理器干扰的链缓冲管理。

支持RS485 ❖ USART1 支持全功能的调制解调器信号

USART

USART 可管理多类型串行同步或异步通信 它支持下列通信模式:

▪ 5 到 9 位全双工异步串行通信: ▪– 高位或低位在先 ▪– 1、 1.5 或 2 位停止位 ▪– 奇检验、偶检验、标志、间隔或无 ▪– 接收器频率 8 或 16 倍重采样 ▪– 可选硬件握手 ▪– 可选调试解调器信号管理 ▪– 可选间断管理 ▪– 可选多点串行通信

RX232TXD RX232RXD

MAX232

C1+

VDD

C1-

V+

C2+

V-

C2TIOUT RIIN

GND T1IN RIOUT

3.3V

C3 104

C4 104 信号地 TXD RXD

RS-232C接口信号

UART串行数据格式

❖ 8位字长

8-bit Data

frame

Start D 0

D1

D2

–NACK 处理,有复制与反复限制的错误计数器 红外 IrDA调制解调

❖ 测试模式

远程回环、本地回环、自动回应

I2C目接说明

寄存器描述

TWI接口

TWI接口包含个寄存器(I2C接口包含7个寄存器)。

寄存器描述——TWI控制寄存器

TWI_CR寄存器:

寄存器描述——TWI主机模式寄存器

寄存器描述——TWI内部地址寄存器

寄存器描述——TWI时钟波形发生器寄存器

寄存器描述——TWI状态寄存器

寄存器描述——TWI中断使能寄存器

结束位,用于指 示传输的结束。

——主机发送 TWI应用示例

主模式数据发送的时序格式

S (1) 从器件地址 W (2) A 数据 (3) A 数据… (3) A/A P (4)

(1) 通过软件置位STA进入TWI主发送模式,TWI逻辑在总线空闲后 立即发送一个起始信号; (2) 在起始信号发送结束后,SI置位。将从机地址和写操作位装入 I2DAT,然后清零SI,将第一字节数据发出; (3) 当从机地址和W位发送结束并收到应答位(A)后,SI位再次置位。 此时将要发送的数据装入I2DAT,开始发送数据; (4) 在数据正确发送后,SI置位。此时如果要结束本次操作,那么置 位STO位,发送结束信号。

I2C简介——电气连接

I2C接口

I2C总线接口均为开漏或开集电极输出,因此需要 为总线增加上拉电阻Rp。

总线速率越高,总线上拉电阻就越小, 100Kbit/s总线速率,通常使用5.1K欧姆 的上拉电阻

TWD线上数据必须为8位。数据传输是高位在先;每字节后必须 有应答信号。每次传输的字节数目没有限制。每次传输以START 状态开始,以STOP状态停止。

TWI接口

TWI应用示例

AT91SAM7XXX对于TWI通信的处理是基于状态 标志进行的,不同的模式之间具有相通的分析方法, 这里仅介绍常用的主发送和主接收模式。

AT91SAM7S 系列 ARM 微控制器 快速入门

ATARM快速入门-基于AT91SAM7S系列ARM微控制器作者:Team Mcuzone网址:版本:Rev1.0a日期:2006-11版本信息:Rev1.0a: 2006-11成稿,原始版本版权信息:本资料部分资料取材于网络,若侵犯到某些个人或者公司的版权或其他利益,请主动和我们联系,我们将注明、更改、删除相关内容。

联系方法:QQ:8204136手机:139********MSN:hdapple_2000@目录介绍篇:1,ARM简介;2,AT91简介;3,ARM开发环境KEIL,IAR,ADS,RV,WINARM简介;4,ARM开发工具WIGGLER,MULTI-ICE,XLINK,ULINK简介;5,SAM7S32学习板介绍;6,LED范例演示;7,ARM/Thumb汇编指令集;硬件篇:1,AT91SAM7S供电(系统电源,1.8V,PLL);2,时钟设置,PLL设置,32K时钟;3,RESET电路(RESET电路);4,DBGU/ISP/BOOT;5,JTAG电路;6,ADC电路;7,IIC/TWI;8,SPI;9,USART10,PWM11,AIC;12,PMC;13,RTT;14,USB UART15,原理图介绍,分析,JTAG调试,DBGU下载演示软件篇:00,汇编指令分析;01,启动代码分析,头文件分析;1,GPIO(LED/KEY);2,UART;3,IIC/TWI(24C02);4,ADC(温度,光照度);5,Timer;6,RTT;7,PWM(LED);8,Uc/OS II;进阶篇:1,7S64的USB应用(S64-DEK);2,7X256的USB应用(7X256 LITE/EK);3,7X256的CAN应用(7X256 EK);4,7X256的NET应用(7X256 LITE/EK);附录:1,IAR下wiggler,MULTI-ICE的使用;2,SAM-BA中文用户手册;3,MULTI-ICE用户手册;4,XLINK用户手册;在开始阅读本书前,建议浏览一下ARM公司推荐的关于ARM的中文出版物,然后找几本比较适合自己的入门书籍来做一下预习工作,当然,也可以将本站整理的资料做为您的ARM入门必读书籍。

AT91SAM7SE512-AU中文资料

Features Array•Incorporates the ARM7TDMI® ARM® Thumb® Processor–High-performance 32-bit RISC Architecture–High-density 16-bit Instruction Set–Leader in MIPS/Watt–EmbeddedICE™ In-circuit Emulation, Debug Communication Channel Support •Internal High-speed Flash–512 Kbytes, Organized in Two Contiguous Banks of 1024 Pages of 256 Bytes Dual Plane (AT91SAM7SE512)–256 Kbytes (AT91SAM7SE256) Organized in One Bank of 1024 Pages of 256 Bytes Single Plane (AT91SAM7SE256)–32 Kbytes (AT91SAM7SE32) Organized in One Bank of 256 Pages of 128 BytesSingle Plane (AT91SAM7SE32)–Single Cycle Access at Up to 30 MHz in Worst Case Conditions–Prefetch Buffer Optimizing Thumb Instruction Execution at Maximum Speed–Page Programming Time: 6 ms, Including Page Auto-erase, Full Erase Time: 15 ms –10,000 Erase Cycles, 10-year Data Retention Capability, Sector Lock Capabilities, Flash Security Bit–Fast Flash Programming Interface for High Volume Production•32 Kbytes (AT91SAM7SE512/256) or 8 Kbytes (AT91SAM7SE32) of InternalHigh-speed SRAM, Single-cycle Access at Maximum Speed•One External Bus Interface (EBI)–Supports SDRAM, Static Memory, Glueless Connection to CompactFlash® andECC-enabled NAND Flash•Memory Controller (MC)–Embedded Flash Controller–Memory Protection Unit–Abort Status and Misalignment Detection•Reset Controller (RSTC)–Based on Power-on Reset Cells and Low-power Factory-calibrated BrownoutDetector–Provides External Reset Signal Shaping and Reset Source Status•Clock Generator (CKGR)–Low-power RC Oscillator, 3 to 20 MHz On-chip Oscillator and One PLL•Power Management Controller (PMC)–Power Optimization Capabilities, Including Slow Clock Mode (Down to 500 Hz) and Idle Mode–Three Programmable External Clock Signals•Advanced Interrupt Controller (AIC)–Individually Maskable, Eight-level Priority, Vectored Interrupt Sources–Two External Interrupt Sources and One Fast Interrupt Source, Spurious Interrupt Protected•Debug Unit (DBGU)–Two-wire UART and Support for Debug Communication Channel interrupt,Programmable ICE Access Prevention•Periodic Interval Timer (PIT)–20-bit Programmable Counter plus 12-bit Interval Counter•Windowed Watchdog (WDT)–12-bit key-protected Programmable Counter–Provides Reset or Interrupt Signals to the System–Counter May Be Stopped While the Processor is in Debug State or in Idle Mode26222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]•Real-time Timer (RTT)–32-bit Free-running Counter with Alarm –Runs Off the Internal RC Oscillator•Three Parallel Input/Output Controllers (PIO)–Eighty-eight Programmable I/O Lines Multiplexed with up to Two Peripheral I/Os –Input Change Interrupt Capability on Each I/O Line–Individually Programmable Open-drain, Pull-up Resistor and Synchronous Output –Schmitt Trigger on All inputs•Eleven Peripheral DMA Controller (PDC) Channels•One USB 2.0 Full Speed (12 Mbits per second) Device Port–On-chip Transceiver, Eight Endpoints, 2688-byte Configurable Integrated FIFOs •One Synchronous Serial Controller (SSC)–Independent Clock and Frame Sync Signals for Each Receiver and Transmitter –I²S Analog Interface Support, Time Division Multiplex Support–High-speed Continuous Data Stream Capabilities with 32-bit Data Transfer •Two Universal Synchronous/Asynchronous Receiver Transmitters (USART)–Individual Baud Rate Generator, IrDA ® Infrared Modulation/Demodulation–Support for ISO7816 T0/T1 Smart Card, Hardware Handshaking, RS485 Support –Full Modem Line Support on USART1•One Master/Slave Serial Peripheral Interfaces (SPI)–8- to 16-bit Programmable Data Length, Four External Peripheral Chip Selects •One Three-channel 16-bit Timer/Counter (TC)–Three External Clock Inputs, Two Multi-purpose I/O Pins per Channel –Double PWM Generation, Capture/Waveform Mode, Up/Down Capability •One Four-channel 16-bit PWM Controller (PWMC)•One Two-wire Interface (TWI)–Master, Multi-Master and Slave Mode Support, All Two-wire Atmel EEPROMs Supported –General Call Supported in Slave Mode•One 8-channel 10-bit Analog-to-Digital Converter, Four Channels Multiplexed with Digital I/Os •SAM-BA ™–Default Boot program–Interface with SAM-BA Graphic User Interface •IEEE ® 1149.1 JTAG Boundary Scan on All Digital Pins •Four High-current Drive I/O lines, Up to 16 mA Each •Power Supplies–Embedded 1.8V Regulator, Drawing up to 100 mA for the Core and External Components–1.8V or 3,3V VDDIO I/O Lines Power Supply, Independent 3.3V VDDFLASH Flash Power Supply –1.8V VDDCORE Core Power Supply with Brownout Detector•Fully Static Operation: Up to 48 MHz at 1.65V and 85°C Worst Case Conditions•Available in a 128-lead LQFP Green Package, or a 144-ball LFBGA RoHS-compliant Package36222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]1.DescriptionAtmel's AT91SAM7SE Series is a member of its Smart ARM Microcontroller family based on the 32-bit ARM7™ RISC processor and high-speed Flash memory.•AT91SAM7SE512 features a 512 Kbyte high-speed Flash and a 32 Kbyte SRAM.•AT91SAM7SE256 features a 256 Kbyte high-speed Flash and a 32 Kbyte SRAM.•AT91SAM7SE32 features a 32 Kbyte high-speed Flash and an 8 Kbyte SRAM.It also embeds a large set of peripherals, including a USB 2.0 device, an External Bus Interface (EBI), and a complete set of system functions minimizing the number of external components. The EBI incorporates controllers for synchronous DRAM (SDRAM) and Static memories and features specific circuitry facilitating the interface for NAND Flash, SmartMedia and CompactFlash.The device is an ideal migration path for 8/16-bit microcontroller users looking for additional per-formance, extended memory and higher levels of system integration.The embedded Flash memory can be programmed in-system via the JTAG-ICE interface or via a parallel interface on a production programmer prior to mounting. Built-in lock bits and a secu-rity bit protect the firmware from accidental overwrite and preserve its confidentiality.The AT91SAM7SE Series system controller includes a reset controller capable of managing the power-on sequence of the microcontroller and the complete system. Correct device operation can be monitored by a built-in brownout detector and a watchdog running off an integrated RC oscillator.By combining the ARM7TDMI processor with on-chip Flash and SRAM, and a wide range of peripheral functions, including USART, SPI, External Bus Interface, Timer Counter, RTT and Analog-to-Digital Converters on a monolithic chip, the AT91SAM7SE512/256/32 is a powerful device that provides a flexible, cost-effective solution to many embedded control applications.1.1Configuration Summary of the AT91SAM7SE512, AT91SAM7SE256 and AT91SAM7SE32The AT91SAM7SE512, AT91SAM7SE256 and AT91SAM7SE32 differ in memory sizes and organization. Table 1-1 below summarizes the configurations for the three devices.Table 1-1.Configuration SummaryDeviceFlash Size Flash Organization RAM Size AT91SAM7SE512512K bytes dual plane 32K bytes AT91SAM7SE256256K bytes single plane 32K bytes AT91SAM7SE3232K bytessingle plane8K bytes46222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]2.Block DiagramFigure 2-1.AT91SAM7SE512/256/32 Block Diagram Signal Description56222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]3.Signal DescriptionTable 3-1.Signal Description ListSignal NameFunctionTypeActive LevelCommentsPowerVDDIN Voltage Regulator and ADC Power Supply InputPower 3V to 3.6V VDDOUT Voltage Regulator Output Power 1.85V VDDFLASH Flash and USB Power Supply Power 3V to 3.6VVDDIO I/O Lines Power Supply Power 3V to 3.6V or 1.65V to 1.95V VDDCORE Core Power Supply Power 1.65V to 1.95V VDDPLL PLL Power 1.65V to 1.95VGNDGroundGroundClocks, Oscillators and PLLsXIN Main Oscillator Input Input XOUT Main Oscillator Output Output PLLRC PLL FilterInput PCK0 - PCK2Programmable Clock OutputOutputICE and JTAGTCK T est Clock Input No pull-up resistor TDI T est Data In Input No pull-up resistor.TDO T est Data Out Output TMS T est Mode Select Input No pull-up resistor.JT AGSELJT AG SelectionInputPull-down resistor.Flash MemoryERASEFlash and NVM Configuration Bits Erase CommandInputHighPull-down resistor Reset/TestNRST Microcontroller Reset I/O Low Pull-Up resistor TSTT est Mode SelectInputHighPull-down resistorDebug UnitDRXD Debug Receive Data Input DTXDDebug T ransmit DataOutput AICIRQ0 - IRQ1External Interrupt Inputs Input FIQFast Interrupt InputInput66222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]PIOP A0 - P A31Parallel IO Controller A I/O Pulled-up input at reset PB0 - PB31Parallel IO Controller B I/O Pulled-up input at reset PC0 - PC23Parallel IO Controller CI/OPulled-up input at resetUSB Device PortDDM USB Device Port Data - Analog DDPUSB Device Port Data +AnalogUSARTSCK0 - SCK1Serial Clock I/O TXD0 - TXD1T ransmit Data I/O RXD0 - RXD1 Receive Data Input RTS0 - RTS1Request To Send Output CTS0 - CTS1Clear To Send Input DCD1Data Carrier Detect Input DTR1Data T erminal Ready Output DSR1Data Set Ready Input RI1Ring IndicatorInputSynchronous Serial ControllerTD T ransmit Data Output RD Receive Data Input TK T ransmit Clock I/O RK Receive Clock I/O TF T ransmit Frame Sync I/O RFReceive Frame SyncI/OTimer/CounterTCLK0 - TCLK2External Clock Inputs Input TIOA0 - TIOA2Timer Counter I/O Line A I/O TIOB0 - TIOB2Timer Counter I/O Line BI/OPWM ControllerPWM0 - PWM3PWM Channels OutputSerial Peripheral InterfaceMISO Master In Slave Out I/O MOSI Master Out Slave In I/O SPCK SPI Serial ClockI/O NPCS0SPI Peripheral Chip Select 0I/O Low NPCS1-NPCS3SPI Peripheral Chip Select 1 to 3OutputLowTable 3-1.Signal Description List (Continued)Signal NameFunctionTypeActive LevelComments76222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]Two-Wire InterfaceTWD T wo-wire Serial Data I/O TWCKT wo-wire Serial ClockI/OAnalog-to-Digital ConverterAD0-AD3Analog Inputs Analog Analog InputsAD4-AD7Analog Inputs Analog Digital pulled-up inputs at resetADTRG ADC T rigger Input ADVREFADC ReferenceAnalogFast Flash Programming InterfacePGMEN0-PGMEN2Programming Enabling Input PGMM0-PGMM3Programming Mode Input PGMD0-PGMD15Programming Data I/O PGMRDY Programming Ready Output High PGMNVALID Data Direction Output Low PGMNOE Programming Read Input LowPGMCK Programming Clock Input PGMNCMDProgramming CommandInputLow External Bus InterfaceD[31:0]Data Bus I/O A[22:0]Address Bus Output NWAITExternal Wait SignalInputLowStatic Memory ControllerNCS[7:0]Chip Select Lines Output Low NWR[1:0]Write Signals Output Low NRD Read Signal Output Low NWE Write EnableOutput Low NUB NUB: Upper Byte Select Output Low NLBNLB: Lower Byte SelectOutputLowEBI for CompactFlash SupportCFCE[2:1]CompactFlash Chip Enable Output Low CFOE CompactFlash Output Enable Output Low CFWE CompactFlash Write Enable Output Low CFIOR CompactFlash I/O Read Signal Output Low CFIOW CompactFlash I/O Write Signal Output LowCFRNW CompactFlash Read Not Write Signal Output CFCS[1:0]CompactFlash Chip Select LinesOutputLowTable 3-1.Signal Description List (Continued)Signal NameFunctionTypeActive LevelComments86222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]EBI for NAND Flash SupportNANDCS NAND Flash Chip Select Line Output Low NANDOE NAND Flash Output Enable Output Low NANDWE NAND Flash Write EnableOutput Low NANDCLE NAND Flash Command Line Enable Output Low NANDALENAND Flash Address Line EnableOutputLowSDRAM ControllerSDCK SDRAM Clock Output Tied low after resetSDCKE SDRAM Clock EnableOutput High SDCS SDRAM Controller Chip Select Line Output LowBA[1:0]Bank SelectOutput SDWE SDRAM Write Enable Output Low RAS - CAS Row and Column Signal Output Low NBS[3:0]Byte Mask Signals Output Low SDA10SDRAM Address 10 LineOutputTable 3-1.Signal Description List (Continued)Signal NameFunctionTypeActive LevelComments96222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]4.PackageThe AT91SAM7SE512/256/32 is available in:•20 x 14 mm 128-lead LQFP package with a 0.5 mm lead pitch.•10x 10 x 1.4 mm 144-ball LFBGA package with a 0.8 mm lead pitch4.1128-lead LQFP Package OutlineFigure 4-1 shows the orientation of the 128-lead LQFP package and a detailed mechanical description is given in the Mechanical Characteristics section of the full datasheet.Figure 4-1.128-lead LQFP Package Outline (Top View)106222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]4.2128-lead LQFP PinoutTable 4-1.Pinout in 128-lead LQFP Package1ADVREF 33PB3165TDI 97SDCK 2GND 34PB3066TDO 98PC83AD735PB2967PB299PC74AD636PB2868PB1100PC65AD537PB2769PB0101PC56AD438PB2670GND 102PC47VDDOUT 39PB2571VDDIO 103PC38VDDIN 40PB2472VDDCORE 104PC29P A20/PGMD8/AD341PB2373NRST 105PC110P A19/PGMD7/AD242PB2274TST 106PC011P A18/PGMD6/AD143PB2175ERASE 107P A3112P A17/PGMD5/AD044PB2076TCK 108P A3013P A16/PGMD445GND 77TMS 109P A2914P A15/PGMD346VDDIO 78JTAGSEL 110P A2815P A14/PGMD247VDDCORE 79PC23111P A27/PGMD1516P A13/PGMD148PB1980PC22112P A26/PGMD1417P A12/PGMD049PB1881PC21113P A25/PGMD1318P A11/PGMM350PB1782PC20114P A24/PGMD1219P A10/PGMM251PB1683PC19115P A23/PGMD1120P A9/PGMM152PB1584PC18116P A22/PGMD1021VDDIO 53PB1485PC17117P A21/PGMD922GND 54PB1386PC16118VDDCORE 23VDDCORE 55PB1287PC15119GND 24P A8/PGMM056PB1188PC14120VDDIO 25P A7/PGMNVALID 57PB1089PC13121DM 26P A6/PGMNOE 58PB990PC12122DP 27P A5/PGMRDY 59PB891PC11123VDDFLASH28P A4/PGMNCMD60PB792PC10124GND 29P A361PB693PC9125XIN/PGMCK 30P A2/PGMEN262PB594GND 126XOUT 31P A1/PGMEN163PB495VDDIO 127PLLRC 32P A0/PGMEN064PB396VDDCORE128VDDPLL116222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]4.3144-ball LFBGA Package OutlineFigure 4-2 shows the orientation of the 144-ball LFBGA package and a detailed mechanical description is given in the Mechanical Characteristics section. Figure 4-2.144-ball LFBGA Package Outline (Top View)126222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]4.4144-ball LFBGA PinoutTable 4-2.SAM7SE512/256/32 Pinout for 144-ball LFBGA PackagePin Signal NamePin Signal Name Pin Signal Name Pin Signal Name A1PB7D1VDDCORE G1PC18K1PC11A2PB8D2VDDCORE G2PC16K2PC6A3PB9D3PB2G3PC17K3PC2A4PB12D4TDO G4PC9K4PC0A5PB13D5TDI G5VDDIO K5PA27/PGMD15A6PB16D6PB17G6GND K6PA26/PGMD14A7PB22D7PB26G7GND K7GND A8PB23D8PA14/PGMD2G8GND K8VDDCORE A9PB25D9PA12/PGMD0G9GND K9VDDFLASH A10PB29D10PA11/PGMM3G10AD4K10VDDIO A11PB30D11PA8/PGMM0G11VDDIN K11VDDIOA12PB31D12PA7/PGMNVALID G12VDDOUT K12PA18/PGMD6/AD1B1PB6E1PC22H1PC15L1SDCK B2PB3E2PC23H2PC14L2PC7B3PB4E3NRST H3PC13L3PC4B4PB10E4TCK H4VDDCORE L4PC1B5PB14E5ERASE H5VDDCORE L5PA29B6PB18E6TEST H6GND L6PA24/PGMD12B7PB20E7VDDCORE H7GND L7PA21/PGMD9B8PB24E8VDDCORE H8GND L8ADVREF B9PB28E9GND H9GNDL9VDDFLASH B10PA4/PGMNCMD E10PA9/PGMM1H10PA19/PGMD7/AD2L10VDDFLASH B11PA0/PGMEN0E11PA10/PGMM2H11PA20/PGMD8/AD3L11PA17/PGMD5/AD0B12PA1/PGMEN1E12PA13/PGMD1H12VDDIO L12GND C1PB0F1PC21J1PC12M1PC8C2PB1F2PC20J2PC10M2PC5C3PB5F3PC19J3PA30M3PC3C4PB11F4JT AGSEL J4PA28M4PA31C5PB15F5TMS J5PA23/PGMD11M5PA25/PGMD13C6PB19F6VDDIO J6PA22/PGMD10M6DM C7PB21F7GND J7AD6M7DP C8PB27F8GND J8AD7M8GND C9PA6/PGMNOE F9GND J9VDDCORE M9XIN/PGMCK C10PA5/PGMRDY F10AD5J10VDDCORE M10XOUT C11PA2/PGMEN2F11PA15/PGMD3J11VDDCORE M11PLLRC C12PA3F12PA16/PGMD4J12VDDIOM12VDDPLL136222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]5.Power Considerations5.1Power SuppliesThe AT91SAM7SE512/256/32 has six types of power supply pins and integrates a voltage regu-lator, allowing the device to be supplied with only one voltage. The six power supply pin types are:•VDDIN pin. It powers the voltage regulator and the ADC; voltage ranges from 3.0V to 3.6V , 3.3V nominal.•VDDOUT pin. It is the output of the 1.8V voltage regulator.•VDDIO pin. It powers the I/O lines; two voltage ranges are supported:–from 3.0V to 3.6V, 3.3V nominal –or from 1.65V to 1.95V , 1.8V nominal.•VDDFLASH pin. It powers the USB transceivers and a part of the Flash. It is required for the Flash to operate correctly; voltage ranges from 3.0V to 3.6V , 3.3V nominal.•VDDCORE pins. They power the logic of the device; voltage ranges from 1.65V to 1.95V, 1.8V typical. It can be connected to the VDDOUT pin with decoupling capacitor. VDDCORE is required for the device, including its embedded Flash, to operate correctly.•VDDPLL pin. It powers the oscillator and the PLL. It can be connected directly to the VDDOUT pin.In order to decrease current consumption, if the voltage regulator and the ADC are not used, VDDIN, ADVREF, AD4, AD5, AD6 and AD7 should be connected to GND. In this case VDDOUT should be left unconnected.No separate ground pins are provided for the different power supplies. Only GND pins are pro-vided and should be connected as shortly as possible to the system ground plane.5.2Power ConsumptionThe AT91SAM7SE512/256/32 has a static current of less than 60 µA on VDDCORE at 25°C, including the RC oscillator, the voltage regulator and the power-on reset when the brownout detector is deactivated. Activating the brownout detector adds 20 µA static current.The dynamic power consumption on VDDCORE is less than 80 mA at full speed when running out of the Flash. Under the same conditions, the power consumption on VDDFLASH does not exceed 10 mA.5.3Voltage RegulatorThe AT91SAM7SE512/256/32 embeds a voltage regulator that is managed by the System Controller.In Normal Mode, the voltage regulator consumes less than 100 µA static current and draws 100 mA of output current.The voltage regulator also has a Low-power Mode. In this mode, it consumes less than 20 µA static current and draws 1 mA of output current.Adequate output supply decoupling is mandatory for VDDOUT to reduce ripple and avoid oscil-lations. The best way to achieve this is to use two capacitors in parallel:146222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]•One external 470 pF (or 1 nF) NPO capacitor should be connected between VDDOUT and GND as close to the chip as possible.•One external 2.2 µF (or 3.3 µF) X7R capacitor should be connected between VDDOUT and GND.Adequate input supply decoupling is mandatory for VDDIN in order to improve startup stability and reduce source voltage drop. The input decoupling capacitor should be placed close to the chip. For example, two capacitors can be used in parallel: 100 nF NPO and 4.7 µF X7R.5.4Typical Powering SchematicsThe AT91SAM7SE512/256/32 supports a 3.3V single supply mode. The internal regulator input connected to the 3.3V source and its output feeds VDDCORE and the VDDPLL. Figure 5-1shows the power schematics to be used for USB bus-powered systems.Figure 5-1.3.3V System Single Power Supply Schematic156222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]6.I/O Lines Considerations6.1JTAG Port PinsTMS, TDI and TCK are schmitt trigger inputs and are not 5V-tolerant. TMS, TDI and TCK do not integrate a pull-up resistor.TDO is an output, driven at up to VDDIO, and has no pull-up resistor.The pin JTAGSEL is used to select the JTAG boundary scan when asserted at a high level. The pin JTAGSEL integrates a permanent pull-down resistor of about 15 k Ω to GND, so that it can be left unconnected for normal operations.6.2Test PinThe TST pin is used for manufacturing test or fast programming mode of the AT91SAM7SE512/256/32 when asserted high. The TST pin integrates a permanent pull-down resistor of about 15 k Ω to GND, so that it can be left unconnected for normal operations. To enter fast programming mode, the TST pin and the PA0 and PA1 pins should be tied high and PA2 tied low.Driving the TST pin at a high level while PA0 or PA1 is driven at 0 leads to unpredictable results.6.3Reset PinThe NRST pin is bidirectional. It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components or asserted low externally to reset the microcontroller. There is no constraint on the length of the reset pulse, and the reset controller can guarantee a minimum pulse length. This allows connection of a simple push-button on the NRST pin as system user reset, and the use of the NRST signal to reset all the components of the system.An external power-on reset can drive this pin during the start-up instead of using the internal power-on reset circuit.The NRST pin integrates a permanent pull-up of about 100 k Ω resistor to VDDIO .This pin is not 5V-tolerant and has schmitt trigger input.6.4ERASE PinThe ERASE pin is used to re-initialize the Flash content and some of its NVM bits. It integrates a permanent pull-down resistor of about 15 k Ω to GND, so that it can be left unconnected for nor-mal operations.This pin is debounced by the RC oscillator to improve the glitch tolerance. When the pin is tied to high during less than 100 ms, ERASE pin is not taken into account. The pin must be tied high during more than 220 ms to perform the re-initialization of the Flash.6.5SDCK PinThe SDCK pin is dedicated to the SDRAM Clock and is an output-only without pull-up and is not 5V-tolerant. Maximum Output Frequency of this pad is 48 MHz at 3.0V and 25 MHz at 1.65V with a maximum load of 30 pF.166222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]6.6PIO Controller linesAll the I/O lines PA0 to PA31, PB0 to PB31, PC0 to PC23 integrate a programmable pull-up resistor. Programming of this pull-up resistor is performed independently for each I/O line through the PIO controllers. Typical pull-up value is 100 k Ω.All the I/O lines have schmitt trigger inputs.6.7I/O Lines Current DrawingThe PIO lines PA0 to PA3 are high-drive current capable. Each of these I/O lines can drive up to 16 mA permanently.The remaining I/O lines can draw only 8 mA.However, the total current drawn by all the I/O lines cannot exceed 300 mA.176222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]7.Processor and Architecture7.1ARM7TDMI Processor•RISC processor based on ARMv4T Von Neumann architecture–Runs at up to 48 MHz, providing 0.9 MIPS/MHz •Two instruction sets–ARM ® high-performance 32-bit instruction set –Thumb ® high code density 16-bit instruction set •Three-stage pipeline architecture–Instruction Fetch (F)–Instruction Decode (D)–Execute (E)7.2Debug and Test Features•EmbeddedICE ™ (Integrated embedded in-circuit emulator)–Two watchpoint units–Test access port accessible through a JTAG protocol –Debug communication channel •Debug Unit–Two-pinUART–Debug communication channel interrupt handling –Chip ID Register•IEEE1149.1 JT AG Boundary-scan on all digital pins7.3Memory Controller•Programmable Bus Arbiter–Handles requests from the ARM7TDMI and the Peripheral DMA Controller •Address decoder provides selection signals for–Four internal 1 Mbyte memory areas –One 256-Mbyte embedded peripheral area –Eight external 256-Mbyte memory areas •Abort Status Registers–Source, Type and all parameters of the access leading to an abort are saved –Facilitates debug by detection of bad pointers •Misalignment Detector–Alignment checking of all data accesses –Abort generation in case of misalignment •Remap Command–Remaps the SRAM in place of the embedded non-volatile memory –Allows handling of dynamic exception vectors•16-area Memory Protection Unit (Internal Memory and peripheral protection only)186222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]–Individually programmable size between 1K Byte and 1M Byte –Individually programmable protection against write and/or user access –Peripheral protection against write and/or user access •Embedded Flash Controller–Embedded Flash interface, up to three programmable wait states–Prefetch buffer, buffering and anticipating the 16-bit requests, reducing the required wait states–Key-protected program, erase and lock/unlock sequencer –Single command for erasing, programming and locking operations –Interrupt generation in case of forbidden operation7.4External Bus Interface•Integrates Three External Memory Controllers:–Static Memory Controller –SDRAM Controller –ECC Controller•Additional Logic for NAND Flash and CompactFlash ® Support–NAND Flash support: 8-bit as well as 16-bit devices are supported–CompactFlash support: all modes (Attribute Memory, Common Memory, I/O, True IDE) are supported but the signals _IOIS16 (I/O and True IDE modes) and -ATA SEL (True IDE mode) are not handled.•Optimized External Bus:–16- or 32-bit Data Bus (32-bit Data Bus for SDRAM only)–Up to 23-bit Address Bus, Up to 8-Mbytes Addressable–Up to 8 Chip Selects, each reserved to one of the eight Memory Areas –Optimized pin multiplexing to reduce latencies on External Memories •Configurable Chip Select Assignment:–Static Memory Controller on NCS0–SDRAM Controller or Static Memory Controller on NCS1–Static Memory Controller on NCS2, Optional CompactFlash Support–Static Memory Controller on NCS3, NCS5 - NCS6, Optional NAND Flash Support –Static Memory Controller on NCS4, Optional CompactFlash Support –Static Memory Controller on NCS77.5Static Memory Controller•External memory mapping, 512-Mbyte address space •8-, or 16-bit Data Bus •Up to 8 Chip Select Lines •Multiple Access Modes supported–Byte Write or Byte Select Lines–Two different Read Protocols for each Memory Bank196222AS–ATARM–21-Aug-06AT91SAM7SE512/256/32 [Advance Information Summary]•Multiple device adaptability–Compliant with LCD Module–Programmable Setup Time Read/Write –Programmable Hold Time Read/Write •Multiple Wait State Management–Programmable Wait State Generation –External Wait Request –Programmable Data Float Time7.6SDRAM Controller•Numerous configurations supported–2K, 4K, 8K Row Address Memory Parts –SDRAM with two or four Internal Banks –SDRAM with 16- or 32-bit Data Path •Programming facilities–Word, half-word, byte access–Automatic page break when Memory Boundary has been reached –Multibank Ping-pong Access–Timing parameters specified by software–Automatic refresh operation, refresh rate is programmable •Energy-saving capabilities–Self-refresh, and Low-power Modes supported •Error detection–Refresh Error Interrupt•SDRAM Power-up Initialization by software•Latency is set to two clocks (CAS Latency of 1, 3 Not Supported)•Auto Precharge Command not used7.7Error Corrected Code Controller•Tracking the accesses to a NAND Flash device by triggering on the corresponding chip select •Single bit error correction and 2-bit Random detection.•Automatic Hamming Code Calculation while writing–ECC value available in a register•Automatic Hamming Code Calculation while reading–Error Report, including error flag, correctable error flag and word address being detected erroneous–Supports 8- or 16-bit NAND Flash devices with 512-, 1024-, 2048- or 4096-byte pages7.8Peripheral DMA Controller•Handles data transfer between peripherals and memories •Eleven channels。

启动代码的说明

2:快速强制

• 高级中断控制器提供的快速强制提供了任意普通中 断源在快速中断控制器改向特性。通(AIC_FFER) 禁用寄存器(AIC_FFDR)的写入来实现。对这些寄存 器写操作将更新控制每个内部或外部中断源特性的 快速强制状态寄存器(AIC_FFSR)。当快速强制使能, 可以检测边沿,但源无法触发一个普通中断且不能 被优先级处理程序处理。 • 保留给快速中断的源0 维持正常操作,成为一个快 速中断源。 • 不管是否快速中断源,快速中断向量寄存器中断源 应通过写中断清除命令寄存器(AIC_ICCR) 来清除。

一:AT91 ARM 概述

使用户在高性能和高代码密度之间进行平衡。 ARM7TDMI处理器为冯-诺依曼结构,具有三级 流水线,即指令获取、解码和执行三个阶段。 ARM7TDMI处理器的主要特点是: • ARM7TDMI基于ARMv4T结构 • 两个指令集 – ARM® 高性能32 位指令集 – Thumb® 高代码密度16位指令集 • 三级流水线结构

启动代码的说明

1.什么是启动代码

启动代码是芯片复位进入C语言的main()函 数前执行的一段初始化程序,主要是为芯 片运行提供基本的运行环境,如初始化存 储系统、寄存器、PLL(锁相环)和内存 重映射,处理异常等。

ARM公司只设计芯片核心,不直接生产芯 片。不同的公司生产的芯片有各自不同的 特色,使得每一种芯片的启动代码差别很 大,不易编写出统一的启动代码。 相应芯片的启动代码需要按照数据手册 上的寄存器和工作模式来写 。 下面以AT91SAM7为列,说明如何按照 收据手册编写启动代码 。

• 4. 先前的步骤已使跳转到相应的中断服务程序。 若不需要嵌套快速中断,则不用保存链接寄存器 (R14_fiq) 及SPSR_fiq。 • 5. 中断处理程序按要求执行。由于FIQ自身有专 用寄存器且用户R8 到R13为组,因此不需要保存 寄存器R8 到R13。其它寄存器, R0 到R7,使用 前必须保存并在结束后恢复(在下一步前)。注意, 若快速中断编程为电平敏感,此时必须清除中断 源以便释放中断源0。 • 6. 最后,链接寄存器R14_fiq在减4后恢复到PC中 (例如,使用指令SUB PC, LR, #4 )。这样将返回 中断执行前的状态,将SPSR 中值载入CPSR 中, 是否屏蔽快速中断由存于SPSR 中的状态决定。

AT91SAM7S64分析

芯片基本功能模块分析• 集成了ARM7TDMI® ARM® Thumb® 处理器–高性能的32 位RISC架构–高密度的16 位指令集–性能/功耗(MIPS/Watt) 的领先者–嵌入式ICE电路仿真,支持调试通讯分析:可以由FOUNDRY厂家license ARM7来解决,属于普通的ARM7内核• 64K 字节的片内高速Flash存储器,共512 页,每页128 字节–在最坏的条件下可以30 MHz 的速度进行单时钟周期访问,预取(Prefetch) 缓冲器可以实现Thumb指令的优化,使处理器以最快的速度执行指令–页编程时间为4 ms,包括页自动擦除,全片擦除时间为10 ms– 10,000 次的写寿命,10 年数据保持能力,扇区锁定功能,Flash 安全锁定位–适合量产的快速Flash编程接口分析:高速Flash也是由工艺厂家提供解决,但要分析性能与参数是否满足要求非易失性掉电检测控制掉电检测(BOD) 由两个通用的NVM (GPNVM)位控制。

因此即使没有了电源,掉电检测仍然可以保持用户的定义。

两个GPNVM 位的清除和设置分别通过EFC 用户接口的“清除通用NVM 位”命令和“设置通用NVM 位”命令来实现。

GPNVM 位0用于控制掉电检测的使能。

设置GPNVM0 将使能BOD,清除它即禁止BOD。

拉高ERASE 将清除GPNVM0,从而禁止BOD。

GPNVM 位1控制掉电检测信号是否可以用于系统复位。

置位GPNVM1使能这个功能,清零GPNVM1 则禁止掉电检测信号复位整个芯片。

拉高ERASE 将禁止掉电检测复位。

8个NVM位用于标定掉电检测器及电压调节器。

• 16K 字节的片内高速SRAM,可以在最高时钟速度下进行单时钟周期访问操作分析:由厂家提供解决,但控制器需要前端设计解决• 存储器控制器(MC)–嵌入式Flash控制器,异常中断(Abort)状态及未对齐(Misalignment) 检测分析:还需要分析这个MC详细的功能包括哪些?• 复位控制器(RSTC)–上电复位和经过工厂标定的掉电检测–提供复位源信息以及给外部电路使用的复位信号分析:需要详细分析功能,尤其掉电检测机制• 时钟发生器(CKGR)–低供耗RC 振荡器,3 到20MHz 的片上振荡器和一个PLL分析:RC振荡器应该由厂家解决,PLL应该可以免费得到• 电源管理控制器(PMC)–可以通过软件进行电源优化,包括慢速时钟模式( 低至500 Hz)和空闲(Idle)模式–三个可编程的外部时钟信号分析:类似SOC时钟模块,提供一些可编程控制,时钟切换,需要前端设计实现• 先进的中断控制器(AIC)–可以单独屏蔽的、具有8 个优先级的向量式中断源–两个外部中断源和一个快速中断源,可以防止虚假(spurious)中断分析:需要分析功能,要看看网上是否由可用的免费模块• 调试单元(DBGU)– 2线UART,支持调试通讯通道中断;可通过程序来禁止通过ICE进行访问分析:仅仅是uart?• 周期性间隔定时器(PIT)– 20位可编程的计数器,加上12 位的间隔计数器分析:类似timer,但12bit的间隔计数器要分析• 11 个外设数据控制器(PDC) 通道外设数据控制器(PDC) 在诸如UART、USART、SSC、SPI、MCI 等片上外设与片内或片外存储器间传输数据。

AT91SAM7X256中文版

ADTRG AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7

ADVREF

JTAG

DDM DDP

PWM0 PWM1 PWM2 PWM3 TF TK TD RD RK RF TCLK0 TCLK1 TCLK2 TIOA0 TIOB0 TIOA1 TIOB1 TIOA2 TIOB2 TWD TWCK CANRX CANTX

4

欢迎访问本公司网站 /

– 支持嵌入式 ICE 内电路仿真以及调试通讯接口 • 片内高速 Flash

– 256K 字节 (AT91SAM7X256) ,共 1024 页,每页 256 字节 – 128K 字节 (AT91SAM7X128) ,共 512 页,每页 256 字节

– 最差情况下仍保持 30 MHz 的单时钟周期存取速度 – 预读取缓冲器使 Thumb 指令最优化运行以达到最高速度 – 每页编程时间为 6 ms,包括页自动擦除, 全片擦除时间为 15 ms – 10,000 次擦写次数, 10 年数据保存能力, 扇区锁定能力,设置 Flash 安全位 – 对量大的数据内容提供快速 Flash 编程接口

– 只支持主模式,支持所有的两线 Atmel EEPROM

• 一个 8 通道 10 位模数转化器,其中四个通道与数字 I/O 接口复用 • SAM-BA™ Boot 助手

– 默认 Boot 编程方式 – 与 SAM-BA 图形用户界面的接口

• IEEE 1149.1 JTAG 边界扫描支持所有数字引脚 • 容许 5V 输入/输出,包括四个高电流驱动 I/O 线,每个高达 16 mA • 电源提供

AT91SAM7Sxx系列MCU Boot-Loader的设计

AT91SAM7Sxx系列MCU Boot-Loader的设计AT91SAM7xx 系列是Atmel 公司推出的基于ARM7内核的32位MCU。

用户代码编译在Thumb 模式下可获得16位指令宽度,从而节约内部程序空间。

目前这个系列芯片的内部Flash 空间范围从32KB到256KB, RAM空间范围是8KB 到 6?KB。

除了SAM7S32外,这个系列的芯片都内嵌有USB2.0全速通讯模块。

本文介绍的就是基于USB接口的用户程序升级工具。

我们知道 Atmel 公司为这个系列芯片提供了 SAM-BA 下载工具。

这个工具在产品阶段的应用有一定的局限,就是为了启动芯片内部的 SAM-BA 程序,用户需要短接芯片的TST引脚到电源端,然后上电10秒钟,再重新上电.本文介绍的Boot-loader 程序常驻在芯片内部Flash 空间,启动方法是用户按住产品的一个特定的按键然后上电。

这样大大简化了产品固件的升级过程。

1 Boot-loader 在Flash中的位置为了在整个SAM7Sxx系列中通用同一个Boot-Loader程序,我们把它定位在Flash的低端位置偏移量为0x800至0x15ff位置,共占用3584个字节空间。

相应的用户程序在链接时要避开使用这段地址。

笔者采用的是IAR编译环境,需要修改链接目标定位控制文件达到定位目标文件的目的。

以S256为例,需要修改at91SAM7S256_NoRemap.xcl 文件Boot-loader 的链接控制文件中需要修改的项目有:-DROMSTART1=00 中断向量表起始位置-DROMEND1=3F 中断向量表结束位置-DROMSTART2=800 目标程序起始位置-DROMEND2=15FF 目标程序结束位置CODE, ICODE CONST 的定位同样需要相应的修改。

Boot-loader 启动文件为Atmel提供(Cstartup.s79),但需要作一定修改:RSEG ICODE:CODE:ROOT(2) 改为RSEG INTVEC:CODE:ROOT(2) 把异常向量表定位在0x00至0x3f.异常向量表的末端添加语句RSEG ICODE:CODE:ROOT(2) 把启动代码定位在CODE段.用户应用项目需要修改at91SAM7S256_NoRemap.xcl文件中-DROMSTART1=00 中断向量表及启动代码起始位置-DROMEND1=7FF 中断向量表及启动代码结束位置-DROMSTART2=1600 目标程序起始位置-DROMEND2=3FFFF 目标程序结束位置CODE, ICODE CONST 的定位同样需要相应的修改。

Almel AT91SAM7S64 AT91 ARM Thumb 微处理器 说明书

特点Array•集成了ARM7TDMI® ARM® Thumb®处理器–高性能的32位RISC架构–高密度的16位指令集–性能/功耗(MIPS/Watt)的领先者–嵌入式ICE电路仿真,支持调试通讯•64K字节的片内高速Flash存储器,共512页,每页128字节–在最坏的条件下可以30 MHz的速度进行单时钟周期访问,预取(Prefetch)缓冲器可以实现Thumb指令的优化,使处理器以最快的速度执行指令–页编程时间为4 ms,包括页自动擦除,全片擦除时间为10 ms–10,000次的写寿命,10年数据保持能力,扇区锁定功能,Flash安全锁定位–适合量产的快速Flash编程接口•16K字节的片内高速SRAM,可以在最高时钟速度下进行单时钟周期访问操作•存储器控制器(MC)–嵌入式Flash控制器,异常中断(Abort)状态及未对齐(Misalignment)检测•复位控制器 (RSTC)–上电复位和经过工厂标定的掉电检测–提供复位源信息以及给外部电路使用的复位信号•时钟发生器(CKGR)– 低耗RC 振荡器,3 到20MHz 的片上振荡器和一个PLL•电源管理控制器(PMC)–可以通过软件进行电源优化,包括慢速时钟模式(低至500 Hz)和空闲(Idle)模式–三个可编程的外部时钟信号•先进的中断控制器(AIC)–可以单独屏蔽的、具有8个优先级的向量式中断源–两个外部中断源和一个快速中断源,可以防止虚假(spurious)中断•调试单元(DBGU)–2线UART,支持调试通讯通道中断;可通过程序来禁止通过ICE进行访问•周期性间隔定时器(PIT)–20位可编程的计数器,加上12位的间隔计数器•时间窗看门狗(WDT)–12位受预设值(key)保护的可编程计数器–为系统提供复位或中断信号–当处理器处于调试状态或空闲模式时可以停止计数器•实时定时器(RTT)–32位自由运行的具有报警功能的计数器–时钟来源于片内RC振荡器•一个并行输入/输出控制器(PIOA)–32个可编程的复用I/O,每个I/O最多可以支持两个外设功能–输入电平改变时,每个I/O都可以产生中断–可以独立编程为开漏输出、使能上拉电阻以及同步输出•11个外设数据控制器(PDC)通道•一个USB 2.0全速(12 Mbps)设备端口–片上收发器,328字节可编程的FIFO•一个同步串行控制器(SSC)–每个接收器和发送器都具有独立的时钟和帧同步信号–支持I²S,支持时分多址–支持32位数据传输的高速连续数据流功能•两个通用的同步/异步收发器(USART)–独立的波特率发生器,IrDA红外调制/解调–支持ISO7816 T0/T1智能卡,硬件握手信号,支持RS485–USART1支持全功能的调制解调器信号•主/从串行外设接口(SPI)–8到16位可编程的数据长度,4个片选线•一个3通道的16位定时器/计数器(TC)–3个外部时钟输入端,每个通道有两个多功能I/O引脚–倍速PWM发生功能,捕捉/波形模式,递增/递减计数2AT91SAM7S64 Preliminary6070A–ATARM–07-Jun-05•一个4通道的16位PWM 控制器(PWMC)•一个两线接口(TWI)–只支持主机模式,支持所有的Atmel 两线EEPROM•一个8通道的10位模数转换器,其中4个通道与数字I/O 复用•IEEE 1149.1 JTAG 边界扫描支持所有的数字引脚•5V 兼容的I/O ,包括4个高达16 mA 的大电流驱动I/O •电源–片上1.8V 电压调节器,可以为内核及外部元件提供高达100 mA 的电流–为I/O 口线提供电源的3.3V VDDIO ,以及独立的为Flash 供电的3.3V VDDFLASH –内核电源为1.8V VDDCORE ,并具有掉电检测(BoD )功能•全静态操作:极限条件下(1.65V ,85°C )高达55 MHz •封装为64脚的LQFP描述AT91SAM7S64是Atmel 32位ARM RISC 处理器小引脚数Flash 微处理器家族的一员。

如何烧录at91SAM7S, SAM7X芯片

为什么能使用samba软件下载? 为什么能使用samba软件下载?

在芯片(at91sam7s/7x)ROM中内嵌SAM在芯片(at91sam7s/7x)ROM中内嵌SAM-BA Boot固件。SAM- Boot完成必要的初始化 Boot固件。SAM-BA Boot完成必要的初始化 • ——启动PLL输出,为USB外设提供一个 ——启动PLL输出,为USB外设提供一个 48MHz的 48MHz的 工作频率, • ——连接USB外设, ——连接USB外设, • ——连接USART外设, ——连接USART外设, • ——等待一个来自于USB或者COM的主机连 ——等待一个来自于USB或者COM的主机连 接(PC)。 接(PC)。

谢谢!

• ——强制AT91SAM7S从内部ROM启动(第一次上电, ——强制AT91SAM7S从内部ROM启动(第一次上电, • • • • •

TST=1), TST=1), ——解锁FLASH的头两个区, ——解锁FLASH的头两个区, ——擦除FLASH的头两个区(8KB), ——擦除FLASH的头两个区(8KB), ——复制SAM——复制SAM-BA Boot到FLASH空间的头4.5KB空间, Boot到FLASH空间的头4.5KB空间, ——锁定FLASH头两个区。第一次运行结束 ——锁定FLASH头两个区。第一次运行结束 ——启动SAM——启动SAM-BA Boot(第二次上电,TST=0)此时运行 Boot(第二次上电,TST=0)此时运行 即是samba-boot代码。 即是samba-boot代码。

FLASH写入后SAM-BA会询问是否对写入的区加锁 FLASH写入后SAM-BA会询问是否对写入的区加锁

下载完毕显示

从何处得到samba? 从何处得到samba?

AT91SAM7x256_128+参考手册(EMAC部分)

前 言Atmel公司去年八月(2005年)发布了最新的AT91SAM7X256/128芯片,该芯片实现了一个与IEEE 802.3标准兼容的以太网MAC,这引起了本人极大的兴趣。

为了能够让自己深入了解MAC模块的技术细节,同时提升自己的英文阅读及翻译水平,本人特意把该芯片携带的技术手册中对EMAC部分的介绍翻译成中文,为了方便中英文对照,文中仍然采用了英文版章节序号:第38节,与英文版一致。

38以太网MAC(EMAC)38.1 概览EMAC模块使用一个地址检查器,统计与控制寄存器组,接收与传输部件以及一个DMA 接口实现了一个与IEEE 802.3标准兼容的以太网MAC。

地址检查器识别四个特殊的48位地址,还包含一个匹配多播与单播地址的64位哈希(hash)寄存器。

它可以识别所有的广播地址,复制所有帧,还可以作用于一个外部地址匹配信号。

统计寄存器部件包含的寄存器组对传输接及收操作相关的不同的事件类型计数。

这些寄存器连同存储在接收缓冲区列表里的状态字一起,允许软件生成与IEEE 802.3兼容的网络管理统计表。

38.2 结构图图38-1 EMAC结构图38.3 功能描述图38-1显示了EMAC模块的不同部件。

控制寄存器组驱动MDIO(MDIO,数据输入/输出管理的简称,译注)接口,设置DMA行为,启动帧传输,选择像双工或半双工这样的操作模式。

接收部件检查前导字段的有效性,FCS(Frame Check Sequence,帧校验序列的简称,译注),对齐和长度,以及把接收到的帧交给地址检查部件和DMA接口。

传输部件从DMA接口取出数据,添加前导字段,并且,如果必要,填充数据(如果发送一个长度小于64个字节的数据包,MAC会生成填充字节将这个数据包扩展到64个字节的最小限制,译注)和FCS,然后按照CSMA/CD(carrier sense multiple access with collision detect,载波监听多路访问/冲突检测,译注)协议传输数据。

AT91SAM库函数 文档

1.//*----------------------------------------------------------------------------2.//* File Name : usart.c3.//* Object : main application written in C4.//* Creation : zzf 2005-12-305.//*----------------------------------------------------------------------------6.// Include Standard files7.#include "usart.h"8.#include "project.h"9.10.#define DBGU_SYS_LEVEL 6 //宏定义DBGU的中断优先级(DBUG属于系统中断)11.#define US0_SYS_LEVEL 5 //宏定义USAR0的中断优先级12.#define US1_SYS_LEVEL 4 //宏定义USAR1的中断优先级13.14.#define BufferLength 128 //宏定义接收与发送数据包的长度15.16.17.char ReceiveBuffer[BufferLength]; //定义接收字符串缓冲区18.19.char SentBufferString[BufferLength+1]; //定义发送字符串缓冲区20.char SentBufferData[BufferLength]; //定义发送数据缓冲区21.22.23.//###########################定义公有函数######################################24.//*----------------------------------------------------------------------------25.//* 函数名: AT91F_DBGU_GetStatus_zzf26.//* 功能:获得USART(DBGU,US0,US1)通道状态寄存器的值,供中断程序用27.//*----------------------------------------------------------------------------28.unsigned int AT91F_USART_GetStatus_zzf(AT91PS_USART pUSART )29.{30.return(pUSART->US_CSR);31.}32.33.//*----------------------------------------------------------------------------34.//* 函数名: AT91F_DBGU_GetInterruptMaskStatus_zzf35.//* 功能:中断屏蔽寄存器的值,供中断程序使用36.//*----------------------------------------------------------------------------37.unsigned int AT91F_USRT_GetInterruptMaskStatus_zzf(AT91PS_USART pUSART)38.{39.return(pUSART->US_IMR);40.}41.42.//*----------------------------------------------------------------------------43.//* 函数名:AT91F_USRT_FrameReceive44.//* 功能:利用PDC(直接传输控制)接收数据45.//*----------------------------------------------------------------------------46.47.void AT91F_USRT_FrameReceive(AT91PS_USART pUSART,char *buffer,unsignedint luffer_length)48.{49.//调用库函数50. AT91F_US_ReceiveFrame(pUSART, buffer,luffer_length,0,0);51.}52.53.//*----------------------------------------------------------------------------54.//* 函数名:AT91F_USRT_FrameSendData55.//* 功能:通过指定的USART发送数据56.//* 参数:1。

ATMEL - AT91SAM7A3-EK Evaluation Board User 说明书