MB90V495G中文资料

史上最有用最全的注册码的

史上最有用最全的注册码的(序列号)Panasonic MPEG Encoder Plugin For Adobe Premiere v2.1--sn:900-4018000 Password:8762NGC4594Panopticum Fire for Adobe After Effects v1.1--FirstName:SiEGE LastName:1999 sn:37991555Pantone HexImage for Adobe Photoshop--Name:PWA sn:C077ADC599F540AD Panopticum Fire for Adobe Photoshop v1.0--FirstName:SiEGE LastName:1999 sn:68716Panopticum Fire for Adobe Photoshop v2.0--NameAnything)sn:F2P-90327-1975Absolute security pro 3.9--Name: CROSSFIRE ROCKER s/n: JDHULALBFRHMLQY or Name: FIREANGEL [EVD] s/n: NVMFTMKNPTUCHJAAcdSee 3.1 build 921 Retail--sn:243478918944730541安全之星XP正式版--SN:CHR-SSV456-9985303DSK-3或者CHR-SSV234-9913220CHR-3Adobe After Effects V5.0--sn:EWE780A7645038-389-588或者SN:EWW471R7080005-040-498Adobe After Effects V4.1--sn:EWW400R4000123-666-922Adobe Acrobat 5.0.1 简体中文版--SN:KWC500R6538415-885Adobe Acrobat 5.0 正式完全版--sn:AEB100R3498245-291或者sn:KWW500R7150122-128Adobe Acorobat full 4.0--sn:AOW301R7136978-298Adobe Acorobat read 1.2--sn:ARM100R3100034-100-397Adobe Acorobat distiller 2.1--snEE100R3001172-010-496Adobe Acorobat capture--sn:WCW100R3101909-171Adobe Dimission 3.01--snJW301R2100011-348Adobe Genesis--sn::44444 autoriznatincode:2077229778Adobe Illustrator 9.0繁体中文版--sn:ABT800R7100102-625Adobe Illustrator 8.0中文版--sn:ABW800X7102095-685或者sn:EXX500R5900103198-517Adobe PageMaker.v7.0--S/N:1039-1121-2998-7586-7388-7545Adobe Pagemaker 6.0--sn:03W600R1124621-479Adobe Pagemaker NL v5.0--sn: 03-5025-303224614Adobe Premiere 6.0 final--sn:MBF500B7205104-998Adobe Premiere 5.1--sn:MXX500R145503-500-448Adobe Premiere RT 5.1 for 9x/NT--sn: MBF420U3000205-940Adobe PhotoShop v6.01 中文版--PWC601R3382269-296或者PWC601R4999617-923或者PWW600R7105467-948或者PWW550R7162534-100 Adobe Photoshop 6.0--sn:PWW600R7105467-948或者EXX600B6311279-428 Adobe Photoshop 5.0--sn:PWW400R7106337-339Adobe Photoshop 4.0--sn:PWW250R3107069-312Adobe Photo deluxe--sn:HTW200R7100048-493Adobe Streamline v4.0--sn:SBW400U7102000-766或者SBW400U7100000-392 Adobe Streamline v3.0--sn:SBW300S1100640-184Adobe Type manager--sn:AWW400P0101591-292Adobe Wild type--sn:FHW251R31003373OFFICE XP 简体中文正式版--序列号:P2KDC-9HMXH-9QFVK-PMQCB-V2XMM Office 2000 简体中文企业版--序列号:J2MV9-JYYQ6-JM44K-QMYTH-8RB2W office 2000 Full--s/n: GC6J3-GTQ62-FP876-94FBR-D3DX8office 2000 Permium--s/n: DT3FT-BFH4M-GYYH8-PG9C3-8K2FJoffice 2000 Porfessional--s/n: XVG79-Q2WK3-JRPMD-9H26V-7TBYToffice 2000 Small Buiness Edition--s/n: TW2RX-PPYX4-MW4FQ-YVYDQ-7CCCQ office 2000 Upgrade--s/n: RMYXR-DJ6FK-M8WBR-FKMB4-JXCCCP TOP翩跹压缩 v3.0--注册名:jieao 注册码:85DA9113F0C377Panda Antivirus Titanium熊猫钛金零售版--name:U38V92LK3Hpassword:2a16sd7xekx79PartitionMagic Pro6.01 for Win9x 精简汉化版--注册码:PP601CDSP1-12345678PartitionMagic Pro6.01 for NT/2000 精简汉化版--注册码:PP601CDSP1-12345678PartitionMagic 6.0 for NT/2000--sn:PM600ENSP1-11111131Particle Fire 2(火焰屏保)--注册码:2222222222Panasonic MPEG Encoder Plugin For Adobe Premiere v2.1--sn:900-4018000 Password:8762NGC4594Panopticum Fire for Adobe After Effects v1.1--FirstName:SiEGE LastName:1999 sn:37991555Pantone HexImage for Adobe Photoshop--Name:PWA sn:C077ADC599F540AD Panopticum Fire for Adobe Photoshop v1.0--FirstName:SiEGE LastName:1999 sn:68716Panopticum Fire for Adobe Photoshop v2.0--NameAnything)sn:F2P-90327-1975PageMaker.v7.0--S/N:1039-1121-2998-7586-7388-7545Pagemaker 6.0--sn:03W600R1124621-479Pagemaker NL v5.0--sn: 03-5025-303224614Premiere 6.0 final--sn:MBF500B7205104-998Premiere 5.1--sn:MXX500R145503-500-448Premiere RT 5.1 for 9x/NT--sn: MBF420U3000205-940PhotoShop v6.01 中文版--PWC601R3382269-296或者PWC601R4999617-923或者PWW600R7105467-948或者PWW550R7162534-100Photoshop 6.0--sn:PWW600R7105467-948或者EXX600B6311279-428 Photoshop 5.0--sn:PWW400R7106337-339Photoshop 4.0--sn:PWW250R3107069-312Photo deluxe--sn:HTW200R7100048-493PC-Cillin 2001 V8.05 英/日文版--sn:PCEW-0011-4881-2059-1555PC-Cillin 2001 V8.04--Code:OSJF-9999-6388-8759-0082PC-Cillin 2001 V8.02-- sn:OSJF-9999-6388-8759-0082PC-Cillin 2001 V8.0-- SN:OSJF-9999-6388-8759-0082PCGhost 4.0 Beta 2(电脑幽灵)--SN:abc-2972178Panda Antivirus Platinum熊猫卫士白金版--注册号:4nzdcdpb6j5Painter 6(自然画笔)--SN:PF60WRZ-0015375-WRBPictureMore 2.30--Name:teamORiON2000 Code:gqm8kGirPolyView 3.61--Name:Mr.Grey [WkT!] SN:3049316813PolyView 3.54--Name:Mr.Grey [WkT!] SN:3049316813Power DVD 3.0.1114 For WiN9X/NT 正式零售版--CD-key:AM12112110760255 PowerDVD 3.0 简体中文正式版--SNV29795362671898PowerQuest DataGone v2.4--注册码2553-0000-1355-5571PowerQuest Server Magic V4.0 For WinNT/2K 简体中文版--username:leggylady@,password:tightsPro Magic 5.12--sn:513001023001DPL8K14W 或者 sn:SCHINA030904TFHDVMWA ProtectX 4.16专业版--Name:Mackoi SN:5AG4ACC41DA56D1Private Pix 2.51--Name:PIX Code:06C6BD3710Process Manager(Windows进程管理)3.01--注册名:Nicsoft 注册码:11064 或者 name:sunfeng SN:EG12376Process Manager(Windows进程管理)3.0--name:dyiyd [CCG] code:CCG15688 Q TOPQuickTime 5.02 完全版--Name:Luke Key:UEAU-TMXW-REME-3UAW-5678或者Name:microke s/n:PMME-GGQM-EMRU-UPE3-5678QuickTime 5 Preview 3--Name:Anonymous Code:0DB4-DD8B-19DB-58B8-6969 R TOPRealPlayer v8.0 Basic Build 6.0.9.584中文版--sn:0444-90-4466 或者sn:0094-32-4766RealPlayer V8.0 Basic Build 6.0.9.450中文版--sn:0094-32-4766 或者SN:1356-04-4068RealPlay助理 1.0.0--name:2000yeah code:0411225518Real 格式文件压缩至尊 v1.3 --注册码:TianYusoftware is good RealProducer Plus 8.51--sn:212-09483-1266 或 212-15087-3664 RealProducer Plus 8.5--SN:212-08976-3639RegRun v2.90--SN:Neme:CZY Last Name: E-mail:REG@ Code:424798RichWin2000(四通利方中文平台2000)--SN:PF00-7WLX-0001-0000273或者SN:RNA0-5GXO-0001-0000108瑞星杀毒软件千禧世纪版--序列号:I49ISF-RUNLD3-OV3CD1-S30000 或者CRMLLL-518AI4-H20JII-640000瑞星千禧世纪版升级序列号--name:qdj pass:1789882 n:csxk p:2298915 n:a p:2671367 n:b p:2570049 n:cq p: 2547100瑞星千禧世纪版ID:TAIHN5YJ TAK4KTNK TAK4N5AV TAPJ5UBU TAQ484SF TA94DIZKTA54HA2E TALIVVR8 TA6HM4J1 TAGIYWCQ TAZ4MDK7 TAWI5LL9TAEIM62X TAP4IED4 TAVHMEUY TAQ4726Q TABH9K1Q TAQHPJYVTA6IX48P TAU4ED8B TAU4GVRJ TA74IQ26 TA7IJF9W TAVIFUMZTA1ISG6F TAB417N2 TAHIW2PB TA1IPVRT TA64G64K TA24HC33TA64FJLN TAS444VN TASHT5MX TAR42DEC TAXIXHBR TAMIKJTQTAB4NJUS TAZI69Y7 TAV43UWK TAUJM6AT TARIRBK6 TA54HA2ES TOPSystem Commander Pro 2000 V5.04正式版--serial:SC2K5-ENE-1013673-XRRT SyGate Home Network v4.0 Build 727--Name:anythingSerial:44D46441-3127CFBA Code:BCF3D581Sygate Personal Firewall--序列号为:H1001001Screen Saver Toolbox v3.3 汉化专业版--Name:Gmwz.FreeUserSN:755310-15066738SmartDraw Professional 5.50 正式版--SN:SD-00-207514-000A-00000-50-45711Snappy Fax 2000 V2.11.5.1--Name:Free User Code:8B4D0AF5CFC821E413S-Spline 2.04--序列号:314AR-JVC65-JXFVO-VW6NG-PPVVE-4KHIASuper Tools v1.0--用户名: 密码:gOJnrcmotrpjOr76ZgM SuperCleaner 2.00--Name: ReanimatoR^LasH Code:2034-76128-1644-20496 SuperCleaner 2.00 Beta 1--注册码:1175-43316-941-11662Super magic 2000(超极兔子魔法设置魔2000)简体中文版--SN:SM2003-KOP8J3-YJ0YH1-HY5Q45Swish 1.5 beta 3--用户名: 注册号:CmR9qXxp15zOZbd0mxiqDQxAMkFesGgHqcWitM73XSmUG5K5Streamline v4.0--sn:SBW400U7102000-766或者SBW400U7100000-392 Streamline v3.0--sn:SBW300S1100640-184数据备份专家2.0--用户码:121212 注册码:YanZhiYang1998神奇注册表 0.5版--用户名:copyyour 注册码:12070019神奇注册表 0.4版--用户名:copyyour 注册码:12070019四通利方中文平台2000(RichWin2000)--SN:PF00-7WLX-0001-0000273或者SN:RNA0-5GXO-0001-0000108四川省麻将(Kyodai Mahjongg) v15.25--注册名: 注册码:002805471661672810617 或者注册名:Free User 注册码:445237065T TOPTransMac 4.2--Name:Free User Code:K7E7PAAM6SF2Trojan Remover 4.3.0--number:22222 key:875873717Trojan Remover 4.3.0--Number:189891 Key:46339488573227112Trojan Remover 4.2.2--SN: 12345678 / 376003664581841Trojan Remover 4.1.7--Name:[eGIS! '98] Company:UCF/PCE '98Code:3743079544TuneSpark.CD.Maker.v1.1.214--Name:stcsr SN:870648E6044E75E3Tweaki for Power Users 3.0.12--sn:YOQNPGTWTxEdit 4.7--Name:LwAkUsChI Org:cOoL Code:4015466477Type manager--sn:AWW400P0101591-292听网 1.0--SN:41EF-2645-04560647天网防火墙 v2.0.3.102-v2.3通用--用户名:evrybody 注册号:582f 或者注册名:microke 注册码:3d8f天音怒放 V2.15--用户名:fpxfpx 注册码:505-0853-45天音怒放 V2.14--Name: SN:443-7672-13天音怒放 V2.13b--Name: SN:443-7672-13天音怒放 V2.13--注册名:世纪动力注册码:999-1962-28 或者注册名:师大附中注册码:974-8525-71 或者注册名:RIRI 注册码:632-0390-88天音怒放2.1修正版--用户名:密码:685-4091-45U TOPUlead Photo Express(我形我速) 4.0 Trial-sn:12903-54000-87045955 Ulead Photo Explorer Pro 7.0 iso--sn:11103-67000-00262910Ulead PhotoImpact V6.0 ESD--sn:11103-06000-00085757Ulead VideoStudio 5.0正式版--SN:11102-85000-00015330Ulead COOL 3D 3.0 简体中文正式版--SN:12905-03000-00381553V TOPVirtual Drive(虚拟光驱) 2001 个人版--安装序列号:FSX31000000VRV北信源杀毒专家2001 正式零售版--序列号:FJDLKICPEAEVoptMe 6.20--Name:0000000000 Location:0000000000 PersonalKey:CE9391A5GCOBR6F00000或者Name:w Location:[CCG]Code:C7D6623C37O2R16WSMKSVisualRoute 5.2c--CLIENT KEY: VISUALROUTE-PWV5C1-5A3245-4A61 SERVER KEY: VISUALROUTE-PWV5S10-FBA833-95E4VuePrint Pro 7.7b--Code:11168520W TOP网络小吸星 v1.0--用户名: 密码:N89HN4WN3J五子棋大战--注册码: g216lab031b5xup376我形我素 4.0--sn:12903-54000-87045955WPS Office 金山办公组合(企业版)--SN:KSW026-110000-428123-807600 Wps2000序列号--KSW00-13328-76201 或者 KSW00-42712-80739WPS2000万能序列号--KSW00-00000-00000WinISO 4.0.0.103 注册码--Name:fixdownCode:9988c3cad629cd2d0000006b00000000WinISO V3.9.0.100正式版注册码--user:winiso sn:998814fe1ad423ec0000005f00000000或者Name:Free UserCode:9988be39150d1ffa0000006d00000000WinISO 3.X通用注册码--Name:Free UserCode:9988be39150d1ffa0000006d00000000Winmsg 消息精灵3.13 v3.13.3649--用户名:白菜乐园注册码:58-F0-89-58-06-53-53-2AWinmsg 消息精灵3.00 v3.12.3472--注册名: 注册码:09-2B-79-43-B5-1E-24-0CWinImage V5.00.5009 Beta--Name:CrazyKnight [ORiON] CN:E3744D08或者Name:The Netmech^LasH Regcode: 44C66A34WinImage V5.00.5007--Name:John Hunt sn:122CA601Windows Power Tools 2.85--Code:b87d789wnfijwefh87eyf87hWindows进程管理(Process Manager) v3.0.1--注册名:Nicsoft 注册码:11064 或者 name:sunfeng SN:EG12376Windows进程管理(Process Manager) v3.0--name:dyiyd [CCG]code:CCG15688Wild type--sn:FHW251R31003373WinImp 1.21--Name:IMP Key1:3E8FC381 Key2:6884663CWinZip 8.1 beta Build 4180--Name:x SN:00020000或者Name:cTRLdSN:1D4C036CWinzip v8.0 build3105--注册名:among 注册码:514A0431 或者注册名:wang qiang 注册码:c97b0c33 或者注册名:ldr 注册码:77940148或者name:wangds code:529c0641WinZip v7.0 SR-1--注册码:Name:The Krazy Nomad [DEViANT] sn:0BB3629F WinDVD v2.3 DTS ISO--sn:4432GHT7C7R84E0万能五笔2000+通用注册码--用户名:shenwei168 PASSWORD: 2546781324578124(可以是十六个任意数字)万能五笔注册码--用户名:cniti 用户码:3821-076433-0764WebZip 4.1.0.657--Name:among s/n:1981862877 Key:A7BB94087900 WebZip 4.1.0.654--Name:among s/n:1981862877 Key:A7BB94087900 WebZip 4.10 Build 624--Name:among Seria Numberl:1981862877 Reg Key:A7BB94087900WebZip 4.00版本通用注册码--name:among Seria Numberl:1981862877 Reg Key:A7BB94087900 或者 name:1key serial:love1key code:6ED1140C1600 或者姓名:sNoOFy [AmoK] 序列号:nICE tO sEE yOU! 注册码:A8EF3C7C1A00 WinGate 4.4.0(0728)--Name:oDDiTy PHEAR Code:666CA61E5DDB490FE6D07C12 Wingate Pro v4.40--name: oDDiTy PHEAR key: 666CA61E5DDB490FE6D07C12 或者name: ODDITY BASTARD key: CA160578A130655A442D34F9WinGate 4.4 Beta A--用户名: MFD Corp. 注册码:36BF3E69EEAEE1E83E36132E 或者NameDDiTy PHEAR s/n:666CA61E008F4E0F86D07C12WinGate vx.x--Name: United Cracking Force - QTsn:419764B050C2EF1DD21CAB12WinGate v4.3--Name:Boy SN:AE5F56E5D95781E99FCEA546 或者 Name: DFA OWNZ SN:666CA61E008F4E0F86D07C12WinGate V4.2--Name:MFD Corp.sn:36BF3E69EEAEE1E83E36132EWinRescue 98 5.04--注册:Code:SvetCHRISTAWinRescue 95 V10.04--注册:msR3I8aUi9y2E84LWinRescue Me 1.04--注册:Code:myONEthingWinRescue 2000 2.04--注册:Code:NashBOGvseMogysheeWinRescue NT V2.04--Code:IBNTB-IMN4KJOWinRescue 98 V5.03--Code:SvetCHRISTAWinRescue 95 V10.03--Code:msR3I8aUi9y2E84LWinRescue Me 1.03--Code:myONEthingWinRescue 2K V2.03--Code:NashBOGvseMogysheeWinRescue NT V2.03--Code:IBNTB-IMN4KJOWindowsXP可以无限次激活的号码:CXGDD-GP2B2-RKWWD-HG3HY-VDJ7J或者RK7J8-2PGYQ-P47VV-V6PMB-F6XPQWindowsXP 2520 Pro 英文版--60天免激活序列号:RK7J8-2PGYQ-P47VV-V6PMB-F6XPQWindows XP 2505 RC1--序列号:DTWB2-VX8WY-FG8R3-X696T-66Y46Q3R8Y-MP9KD-3M6KB-383YB-7PK9Q 411Y0-URB45-34R3B-310N6-70U51F0R6R-347JU-57IC3-M0V34-11Z16 50M38-0DY53-7UPU5-7H380-M8111 WindowXP(windows whistler) Beta2 build 2428--CD Key:RBDC9-VTRC8-D7972-J97JY-PRVMGWindows Mellinium(Windows Me)简体中文最终正式版--s/n:B6BYC-6T7C3-4PXRW-2XKWB-GYV33Windows2000 Professional 中文版--SN:PQHKR-G4JFW-VTY3P-G4WQ2-88CTW Windows2000 Professional英文正式版--s/n:RBDC9-VTRC8-D7972-J97JY-PRVMGWindows2000 Server 简体中文完全正式版--S/N:XF7DK-7X2WM-2QRCT-Y9R23-4BHDGWindows2000 Server--CD-KEY:H6TWQ-TQQM8-HXJYG-D69F7-R84VMWindows 98 SE 标准正式版--s/n: HMTWJ-VPPWP-9BXP8-WD73Y-GGT6M Windows98序列号--K4HVD-Q9TJ9-6CRX9-C9G68-RQ2D3X TOP熊猫钛金零售版Panda Antivirus Titanium--name:U38V92LK3Hpassword:2a16sd7xekx79熊猫卫士白金版Panda Antivirus Platinum--注册号:4nzdcdpb6j5熊猫卫士白金版Panda Antivirus Platinum 6.30--Code:4nzdcdpb6j5虚拟光驱(Virtual Drive) 2001 个人版--安装序列号:FSX31000000现在就打字1.2注册号--姓名: 密码:105277772612 下载软件管理盒(FlashSoft) V1.06--用户名: 注册码:873359396Y TOP鹦鹉螺网络助手(Nautilus NetKit)v2.20中文版--Name:husoftCode:rkdwpibung 或者 Name:nicsoft code:mfyrkdwpib鹦鹉螺网络助手(Nautilus NetKit)v2.11中文版--注册名:dyiyd [CCG] 注册码exqjcvohat友情强档 5.82.0999(08.01)--Name:getfox SN:172392-EIVJYH友情强档5.82.999国际版--Name:getfox SN:172392-EIVJYH友情强档5.80.978国际版--Name:getfox SN:172392-EIVJYH友情强档 V5.63国际版--Name:wind[CCG] SN:196350-XIEVVQVIR音画时尚(ICE Player) v2.6--注册码:PL68A-yhss-style-98566-55860或者6615-FCJX-LDgs-155868-ice260a音画时尚(ICE Player) v2.18--注册码:TD98c-00ip-Q65Z-4129C-8521 或者fyal-WMCZ-LDco-slyy-ice218音乐贝贝(CDOK)--姓名:洋白菜公司:Email:yang119@ sn:CA9C8419 或者注册名:copyyour 公司:CCG信箱:cncrack@ 注册码:7E868430Z TOP中文版拼图游戏1.0--注册码:ffrjj_196418中华压缩(ChinaZip) 6.02--用户名: 注册码:AKEM9752 自然画笔(Painter) 6.0--SN:PF60WRZ-0015375-WRB智能陈桥五笔5.03正式版--注册信息码:CCJXQ7X5S智能狂拼II正式版--序列号:350-00161634365653智能狂拼完全正式版--sn:300-812522036449中文之星 2001--SN:310-1219640374430-9 TOP32-bit FTP f9.31.1--Name:stcs Code:3033353B353932-bit FTP f9.28.01--Name:FTP Code:30323B373D3B32-bit FTP f9.26.15--Name:FTP Code:30323B373D3B32-bit Fax x9.31.1--Name:stcsr Code:3034323B373832-bit Fax x9.28.01--Name:CZY Code:3033373C383A3DS MAX R4 最终零售版软件预安装密码为--cdkey:226-19791979 &key:XLSQBQ3DS MAX 3.1--Serial: 110-12345678 CDKey: S4ED6W Authorization Code: a84983813D Morfit 3D WorldBuilder v3.9--SN:M-2000-MVR-1737Galley Master MM for Adobe PageMaker--sn:50336-150-77196444Galley Master XD for Adobe PageMaker--sn:70336-150-97196444 ACDsee SR1 PowerPack Retail--sn:243478918944730541ACDsee 3.1--sn:132728175249781441AceFTP V2.01--Name: Free User s/n: A333U4-4XZ7PK-TTMDZC-WMBHAU AceHTML Pro 4.30.1--Name:Free User Code:Q4LB-KG9X-Q8PB-3TN6 AceHTML Pro 4.22.2--Name:Free User Code:Q4LB-KG9X-Q8PB-3TN6 AceHTML Pro 4.22.1--Name:Free User Code:Q4LB-KG9X-Q8PB-3TN6 Advanced Gif Animator 2.2 中文注册版--注册码:0qT+7ks91OS6TwwuLvuwXOgnH9C1VS Eo9HIWngLCMBIuHEWyJzuGuNjjAVvsQIf8lo8MhU4c6QZfVgfvrKE7u6ZOsd sLI8UGMKEK3nDr1cRHcvufQ9LTGS3Bz16BSbF7c7cd7gkAFbooFcHO/P8lPf FRTTAg+2Mnrz28OeYhZSIk=Advanced PDF Password Recovery 1.33--注册码:PDFP-99322-EYSVY-886 Advanced Archive Password Recovery 1.01--NAME:Juan Lozada SERIAL:ARCHPR-TBHW5SSMYGQS-CUQ9SNYDE59T4KMMAdvanced ZIP Password Recovery v3.11--sn:00003112193920061941Nqu5h797f6cAjz4UAltoMP3 Maker 2.2--Name:Free User SN:1LfDE2UKh1F5i9fCAlgolab_photo_vector_v1.01--Name:stcsr Companv: Email:stcsr@ Serial:ALPVHFCHINCTMGOPQRSAqua 3D Screen Saver 1.5 汉化破解版--name:任意Code:1234-6789-1234-67C2(程序运行时按空格键即可输入注册码)AutoCAD 2002 最终零售版--Serial:400-12345678 CD-KEY:T4ED6P 找E8B2FEFFFF 85C0 744F 8D4DF0 改为 E8B2FEFFFF 85C0 754F 8D4DF0 就可以用了Audio Converter 3.0(0402)特别版--Use Name:chaoruan Company:china Licenses:1 Serial key:08199-04923680536126119550AudioCD MP3 Studio 2000 V2.3--SN:CSN77B-174094802faB TOP冰雨音画(音画时尚)ICE Player 2.6--注册码:PL68A-yhss-style-98566-55860 6615-FCJX-LDgs-155868-ice260a北信源杀毒专家VRV2001 正式零售版--序列号:FJDLKICPEAEBlindWrite v0.99.1.4--sn:GOLXB3GJE4S46LFJBlindRead v3.0.1.4--sn:KSI1G8JT32UXBAFJ卜算子.天问体育彩票摇奖预测器 v1.20--姓名:白菜乐园密码:ShuanglongDKSF卜算子.三颂个人人气运势分析预测 v1.20--姓名:白菜乐园密码:ShuanglongJWKD卜算子权谋 5.8--Name:洋白菜 SN:EricFuminFHMIOAC TOP彩票点金术2.0--注册邮箱 fpx 注册码 w>]_>KVk卡丽来相片VCD制作系统心动版--SN:CHAMP-9C05EF50-2000词痴 1.5--注册名: 注册码:194394184064284305784305284064105105105CyberLink PowerVCR II v3.0 PRO 简体中文正式版--sn:PD7000EPS0000453 4.0A--Name: Company: UnlockKey:9130D087-C2FD21AA-6312FA87-FE3636FE CheckKey:6F06E679-53CDF12D-A1EFDB2D-9D24CC79 或者 Name: CoKeBoTtLe99 Company/Email: Cokebottle@ Unlock Code:60D015F4-600893EB-BEFF5755-53E4E943 Check Code:3334FCB7-00D8861F-DEF7C4BE-ED1BBE16Clean Disk Security 4.9 --Code:deepgreenChinaZip(中华压缩) 6.02--用户名: 注册码:AKEM9752 CDOK音乐贝贝--姓名:洋白菜公司:Email:yang119@ sn:CA9C8419或者注册名:copyyour 公司:CCG 信箱:cncrack@ 注册码:7E868430Copernic 2001 Pro 5.0 完全版--sn:7336-791157997CPU Cool v6.1.1--Code:7398356CPUCool V6.0.0 Beta--sn:4337148超级兔子魔法设置(Magic Set)3.91简体中文版--Name: Sun Bird Code: CXM-AYYABBXDSPG超级兔子魔法设置(Magic Set) 3.9简体中文版---Name: Sun Bird Code: CXM-AYYABBXDSPG 或者用户名:我爱蔡兔子密码:CX-BBBAWBETUVB超级兔子注册表优化v4.12增强版--Name:Only For ChineseCode:AFABXBCVWXB或者Name:conanxu[BCG] Code:conanxu[BCG]超级兔子魔法设置v3.88简体中文版完美注册--Name: Sun Bird [CCG] Sn: CX-AYYABBPDOLG超级兔子魔法设置v3.88中文版--Name:swnetcn17 Code:SPQHQRSWOXW或者Name:Only For Chinese Code:AFABXBCVWXB或者Nameurewom Code:2Y2PMEFG3或者Name:Al Gore Code:1W1IFHIJ8或者Name:Bauer Lindemann Code:3U5YVLMN6或者Name:蔡旋 Code:ABASGBCXMCB超级兔子魔法设置v3.86中文版--Name:Only For Chinese Code:AFABXBCVWXB 或者Nameurewom Code:2Y2PMEFG3或者Name:Al Gore Code:1W1IFHIJ8或者Name:Bauer Lindemann Code:3U5YVLMN6超级兔子魔法设置V3.85多语言版--注册码:NAME:swnetcn17 CODE:SPQHQRSWOXW(适用于简体中文版的超级兔子魔法设置),注册表优化可以用conanxuBCG的注册码:AFABXBCVWXB,注册名任意。

MB91155中文资料

DS07-16306-3EFUJITSU SEMICONDUCTORDATA SHEET32-bit Proprietary MicrocontrollersCMOSFR30 Family MB91150 SeriesMB91F155A/MB91155/MB91154s DESCRIPTIONThe MB91F155A/MB91155/MB91154 is a single-chip microcontroller using a RISC-CPU (FR 30 series) as its core. It contains peripheral I/O resources suitable for audio, MD and so on which are required to operate at low power consumption.s FEATURES1.CPU•32-bit RISC (FR30) , load/store architecture, 5-stage pipeline •General-purpose registers : 32 bits × 16•16-bit fixed-length instructions (basic instructions) , 1 instruction/ 1 cycle•Memory-to-memory transfer, bit processing, barrel shift processing : Optimized for embedded applications •Function entrance/exit instructions, and multiple load/store instructions of register contents, instruction systems supporting high level languages•Register interlock functions, efficient assembly language description•Branch instructions with delay slots : Reduced overhead time in branching executions •Internal multiplier/supported at instruction level Signed 32-bit multiplication : 5 cycles Signed 16-bit multiplication : 3 cycles•Interrupt (PC and PS saving) : 6 cycles, 16 priority levels(Continued)MB91F155A/MB91155/MB9115422.Bus Interface•16-bit address output, 8/16-bit data input and output•Basic bus cycle : 2-clock cycle•Support for interface for various types of memory•Unused data/address pins can be configured us input/output ports•Support for little endian mode3.Internal ROMMB91F155AFLASH products : 510 KbytesMB91155Mask product : 510 KbytesMB91154Mask product : 384 Kbytes4.Internal RAMMask, FLASH products : 2 Kbytes5.Internal Data RAMMB91F155, MB91155FLASH, Mask products : 32 KbytesMB91154FLASH, Mask product : 20 Kbytes6.DMACDMAC in descriptor format for placing transfer parameters on to the main memory.Capable of transferring a maximum of eight internal and external factors combined.Three channels for external factors7.Bit Search ModuleSearches in one cycle for the position of the bit that changes from the MSB in one word to the initial I/O.8.Timers•16-bit OCU × 8 channels, ICU × 4 channels, Free-run timer × 1 channel•8/16-bit up/down timer/counter (8-bit × 2 channels or 16-bit × 1 channel)•16-bit PPG timer × 6 channels. The output pulse cycle and duty can be varied as desired•16-bit reload timer × 4 channels9.D/A Converter•8-bit × 3 channels10.A/D Converter (Sequential Comparison Type)•10-bit × 8 channels•Sequential conversion method (conversion time : 5.0 µs@33 MHz)•Single conversion or scan conversion can be selected, and one-shot or continuous or stop conversion mode can be set respectively.•Conversion starting function by hardware/software.(Continued)MB91F155A/MB91155/MB91154(Continued)11.Serial I/O•UART × 4 channels. Any of them is capable of serial transfer in sync with clock attached with the LSB/MSB switching function.•Serial data output and serial clock output are selectable by push-pull/open drain software.•A 16-bit timer (U-timer) is contained as a dedicated baud rate generator allowing any baud rate to be generated. 12.I2C Bus Interface•One channel master/slave send and receive•Arbitration and clock synchronization functions(The product is licensed with the Philips I2C patent to support those customers who intend to use this product in an I2C system in compliance with the standard I2C specification stipulated by Philips.)13.Clock Switching Function•Gear function : Operating clock ratios to the basic clock can be set independently for the CPU and peripherals from four types, 1 : 1, 1 : 2, 1 : 4 or 1 : 8.14.Clock Function (Calendar Macro)•Internal 32 kHz clock function•It is possible to perform the clock function (oscillation frequency: 32 kHz) even in a stop mode. (The oscillation does not suspend during a stop mode.)15.Interrupt ControllerExternal interrupt input (16 channels in total) :•Allows the rising edge/falling edge/H level/L level to be set.Internal interrupt factors :•Interrupt by resources and delay interrupt16.Others•Reset cause : Power on reset/watchdog timer/software reset/external reset•Low power consumption mode : Sleep/stop•Package : 144-pin LQFP•CMOS technology (0.35 µm)•Power supply voltage : 3.15 V to 3.6 V•MB91F155 is to be MB91F155A.3MB91F155A/MB91155/MB911544MB91F155A/MB91155/MB911545s PIN DESCRIPTION(Continued)Pin No.Pin name Circuit typeFunction12345678D16/P20D17/P21D18/P22D19/P23D20/P24D21/P25D22/P26D23/P27CBit 16 to bit 23 of external data busThese pins are enabled only in 16-bit external bus mode.These pins are available as ports in single-chip and 8-bit external bus modes.1011121314151617D24/P30D25/P31D26/P32D27/P33D28P34D29/P35D30/P36D31/P37CBit 24 to bit 31 of external data busThese pins are available as ports in single-chip mode.18192021222324252829303132333435A00/P40A01/P41A02/P42A03/P43A04/P44A05/P45A06/P46A07/P47A08/P50A09/P51A10/P52A11/P53A12/P54A13/P55A14/P56A15/P57FBit 0 to bit 15 of external address busThese pins are enabled in external bus mode.These pins are available as ports in single-chip mode.3637383940414243A16/P60A17/P61A18/P62A19/P63A20/P64A21/P65A22/P66A23/P67OBit 16 to bit 23 of external address busThese pins are available as ports when the address bus is not in use.45RDY/P80CExternal RDY inputThis function is enabled when external RDY input is allowed.Input “0” when the bus cycle being executed does not end.This pin is available as a port when external RDY input is not in use.MB91F155A/MB91155/MB911546(Continued) Pin No.Pin nameCircuittypeFunction46BGRNT/P81FExternal bus release acceptance outputThis function is enabled when external bus release acceptance output isallowed.Output “L” upon releasing of the external bus.This pin is available as a port when external bus release acceptance out-put is not allowed.47BRQ/P82CExternal bus release request inputThis function is enabled when external bus release request input is al-lowed.Input “1” when the release of the external bus is desired.This pin is available as a port when external bus release request input isnot in use.48RD/P83FExternal bus read strobe outputThis function is enabled when external bus read strobe output is allowed.This pin is available as a port when external bus read strobe output is notallowed.49WR0/P84FExternal bus write strobe outputThis function is enabled in external bus mode.This pin is available as a port in single chip mode.50WR1/P85FExternal bus write strobe outputThis function is enabled in external bus mode when the bus width is 16bits.This pin is available as a port in single chip mode or when the external buswidth is 8 bits.51CLK/P86FSystem clock outputThe pin outputs the same clock as the external bus operating frequency.The pin is available as a port when it is not used to output the clock.525354MD2MD1MD0GMode pinsTo use these pins, connect them directly to either V CC or V SS.Use these pins to set the basic MCU operating mode.55RST B External reset input5758X1X0A High-speed clock oscillation pins (16.5 MHz)60616263INT0/PC0INT1/PC1INT2/PC2INT3/PC3HExternal interrupt request input 0-3Since this input is used more or less continuously when the correspondingexternal interrupt is allowed, output by the port needs to be stopped ex-cept when it is performed deliberately.Since this port is allowed to input also in standby mode, it can be used toreset the standby state.These pins are available as ports when external interrupt request input isnot in use.MB91F155A/MB91155/MB911547(Continued)Pin No.Pin nameCircuit typeFunction64656667INT4/PC4/CS0INT5/PC5/CS1INT6/PC6/CS2INT7/PC7/CS3HThese pins also serve as the chip select output and external inter-rupt request input 4-7.When the chip select output is not allowed, these pins are available as external interrupt requests or ports.Since this input is used more or less continuously when the corre-sponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.Since this port is also allowed to input in standby mode, the port can be used to reset the standby state.These pins are available as ports when external interrupt request input and chip select output are not in use.697071727374PD0/AIN0/INT8/TRG0PD1/BIN0/INT9/TRG1PD2/AIN1/INT10/TRG2PD3/BIN1/INT11/TRG3PD4/ZIN0/INT12/TRG4PD5/ZIN1/INT13/TRG5HExternal interrupt request input 8-13Since this input is used more or less continuously when the corre-sponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.[AIN, BIN] Up/down timer input.[TRG] PPG external trigger input.Since this input is used more or less continuously while input is al-lowed, output by the port needs to be stopped except when it is per-formed deliberately.These pins are available as ports when the external interrupt re-quest input, up timer counter input, and PPG external trigger input are not in use.75PD6/DEOP2/INT14HExternal interrupt request input 14Since this input is used more or less continuously when the corre-sponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.[DEOP2] DMA external transfer end output.This function is enabled when DMAC external transfer end output is allowed.This pin is available as a port when it is not in use as the external interrupt request input or DMA external transfer end output.76PD7/ATG/INT15HExternal interrupt request input 15Since this input is used more or less continuously when the corre-sponding external interrupt is allowed, output by the port needs to be stopped except when it is performed deliberately.[ATG] A/D converter external trigger input.Since this input is used more or less continuously when selected as an A/D activation factor, output by the port needs to be stopped ex-cept when it is performed deliberately.This pin is available as a port when it is not in use as the external interrupt request input or A/D converter external trigger input.MB91F155A/MB91155/MB911548(Continued) Pin No.Pin nameCircuittypeFunction7879808182838485PE0/OC0PE1/OC1PE2/OC2PE3/OC3PE4/OC4PE5/OC5PE6/OC6PE7/OC7FOutput compare outputThese pins are available as ports when output compare output is not al-lowed.86878889PF0/IN0PF1/IN1PF2/IN2PF3/IN3FInput capture inputThis function is enabled when the input capture operation is input.These pins are available as ports when input capture input is not in use.90PF4F General purpose I/O port919293949596PG0/PPG0PG1/PPG1PG2/PPG2PG3/PPG3PG4/PPG4PG5/PPG5FPPG timer outputThis function is enabled when PPG timer output is allowed.These pins are available as ports when PPG timer output is not allowed.99PJ1/SDA QI2C interface I/O pinThis function is enabled when the I2C interface is allowed to operate.While the I2C interface is in operation, keep the port output set to Hi-Z.This pin is available as a port when the I2C interface is not in use.100PJ0/SCL QI2C interface I/O pinThis function is enabled when the I2C interface is allowed to operate.While the I2C interface is in operation, keep the port output set to Hi-Z.This pin is available as a port when the I2C interface is not in use.102PI5/SCK3/TO3PUART3 clock I/O, Reload timer 3 outputWhen UART3 clock output is not allowed, reload timer 3 can be output byallowing it.This pin is available as a port when neither UART3 clock output nor reloadtimer output is allowed.103PI4/SOT3PUART3 data outputThis function is enabled when UART3 data output is allowed.This pin is available as a port when UART3 clock output is not allowed. 104PI3/SIN3PUART3 data inputSince this input is used more or less continuously while UART3 is en-gaged in input operations, output by the port needs to be stopped exceptwhen it is performed deliberately.This pin is available as a port when UART3 output data input is not in use.MB91F155A/MB91155/MB911549(Continued)Pin No.Pin nameCircuit typeFunction105PI2/SCK2/TO2PUART2 clock I/O, Reload timer 2 outputWhen UART2 clock output is not allowed, reload timer 2 can be output by allowing it.This pin is available as a port when neither UART2 clock output nor reload timer output is allowed.106PI1/SOT2PUART2 data outputThis function is enabled when UART2 data output is allowed.This pin is available as a port when UART2 clock output is not allowed.107PI0/SIN2PUART2 data inputSince this input is used more or less continuously while UART2 is en-gaged in input operations, output by the port needs to be stopped except when it is performed deliberately.This pin is available as a port when UART2 data input is not in use.108PH5/SCK1/TO1PUART1 clock I/O, Reload timer 1 outputWhen UART1 clock output is not allowed, reload timer 1 can be output by allowing it.This pin is available as a port when neither UART1 clock output nor reload timer output is allowed.109PH4/SOT1PUART1 data outputThis function is enabled when UART1 data output is allowed.This pin is available as a port when UART1 clock output is not allowed.110PH3/SIN1PUART1 data inputSince this input is used more or less continuously while UART1 is en-gaged in input operations, output by the port needs to be stopped except when it is performed deliberately.This pin is available as a port when UART1 data input is not in use.111PH2/SCK0/TO0PUART0 clock I/O, Reload timer 0 outputWhen UART0 clock output is not allowed, reload timer 0 can be output by allowing it.This pin is available as a port when neither UART0 clock output nor reload timer output is allowed.112PH1/SOT0PUART0 data outputThis function is enabled when UART0 data output is allowed.This pin is available as a port when UART0 clock output is not allowed.113PH0/SIN0PUART0 data inputSince this input is used more or less continuously while UART0 is en-gaged in input operations, output by the port needs to be stopped except when it is performed deliberately.This pin is available as a port when UART0 data input is not in use.114DREQ0/PL0FDMA external transfer request inputSince this input is used more or less continuously when selected as a DMAC transfer factor, output by the port needs to be stopped except when it is performed deliberately.This pin is available as a port when DMA external transfer request input is not in use.MB91F155A/MB91155/MB9115410(Continued) Pin No.Pin nameCircuittypeFunction115DACK0/PL1FDMA external transfer request acceptance outputThis function is enabled when the DMAC external transfer request accep-tance is allowed to be output.This pin is available as a port when the DMAC transfer request accep-tance is not allowed to be output.116DEOP0/PL2FDMA external transfer end outputThis function is enabled when the end of DMAC external transfer is al-lowed to be output.117DREQ1/PL3FDMA external transfer request inputSince this input is used more or less continuously when selected as aDMAC transfer factor, output by the port needs to be stopped except whenit is performed deliberately.This pin is available as a port when DMA external transfer request input isnot in use.118DACK1/PL4FDMA external transfer request acceptance outputThis function is enabled when the DMAC external transfer request accep-tance is allowed to be output.This pin is available as a port when DMAC transfer request acceptanceoutput is not allowed.119DEOP1/PL5FDMA external transfer end outputThis function is enabled when the end of DMAC external transfer is al-lowed to be output.120DREQ2/PL6FDMA external transfer request inputSince this input is used more or less continuously when selected as aDMAC transfer factor, output by the port needs to be stopped except whenit is performed deliberately.This pin is available as a port when DMA external transfer request input isnot in use.121DACK2/PL7FDMA external transfer request acceptance outputThis function is enabled when the DMAC external transfer request accep-tance is allowed to be output.This pin is available as a port when DMAC transfer request acceptanceoutput is not allowed.123124125DA2DA1DA0D/A converter outputThis function is enabled when D/A converter output is allowed.126DAVS Power supply pin for the D/A converter127DAVC Power supply pin for the D/A converter128AV CC Vcc power supply for the A/D converter129AVRHA/D converter reference voltage (high potential side)Be sure to turn on/off this pin with potential higher than AVRH applied toV CC.130AVRL A/D converter reference voltage (low potential side)131AV SS V SS power supply for the A/D converter11(Continued)Note : On the majority of pins listed above, the I/O port and the resource I/O are multiplexed, such as XXXX/Pxx.When the port and the resource output compete against each other on these pins, priority is given to the resource.Pin No.Pin name Circuit typeFunction132133134135136137138139AN0/PK0AN1/PK1AN2/PK2AN3/PK3AN4/PK4AN5/PK5AN6/PK6AN7/PK7NA/D converter analog inputThese pins are enabled when the AIC register is designated for analog input.These pins are available as ports when A/D converter analog input is not in use.141TEST G The TEST pin must be connected to the power supply (V CC ) 142143X0A X1A K Low-speed clock (32 kHz) oscillation pin27, 56, 68, 77, 97, 122, 140V CCPower supply pin (V CC ) for digital circuitAlways power supply pin (V CC ) must be connected to the power supply9, 26, 44, 59, 98, 101, 144V SSEarth level (V SS ) for digital circuitAlways power supply pin (V SS ) must be connected to the power supplys I/O CIRCUIT TYPE(Continued) 121314s HANDLING DEVICES1.Preventing LatchupIn CMOS ICs, applying voltage higher than V CC or lower than V SS to input/output pin or applying voltage over rating across V CC and V SS may cause latchup.This phenomenon rapidly increases the power supply current, which may result in thermal breakdown of the device. Make sure to prevent the voltage from exceeding the maximum rating.2.Treatment of Pins•Treatment of unused pinsUnused pins left open may cause malfunctions. Make sure to connect them to pull-up or pull-down resistors.•Treatment of open pinsBe sure to use open pins in open state.•Treatment of output pinsShortcircuiting an output pin with the power supply or with another output pin or connecting a large-capacity load may causes a flow of large current. If this conditions continues for a lengthy period of time, the device deteriorates. T ake great care not to exceed the absolute maximum ratings.•Mode pins (MD0-MD2)These pins should be used directly connected to either V CC or V SS. In order to prevent noise from causing accidental entry into test mode, keep the pattern length as short as possible between each mode pin and V CC or V SS on the board and connect them with low impedance.•Power supply pinsWhen there are several V CC and V SS pins, each of them is equipotentially connected to its counterpart inside of the device, minimizing the risk of malfunctions such as latch up. T o further reduce the risk of malfunctions, to prevent EMI radiation, to prevent strobe signal malfunction resulting from creeping-up of ground level and to observe the total output current standard, connect all V CC and V SS pins to the power supply or GND.It is preferred to connect V CC and V SS of MB91F155/MB91154 to power supply with minimal impedance possible.It is also recommended to connect a ceramic capacitor as a bypass capacitor of about 0.1 µF between V CC and V SS at a position as close as possible to MB91F155/MB91154.•Crystal oscillator circuitNoises around X0, X1, X0A, and X1A pins may cause malfunctions of MB91F155/MB91154. In designing the PC board, layout X0, X1 (X0A, X1A) and crystal oscillator (or ceramic oscillator) and bypass capacitor for grounding as close as possible.It is strongly recommended to design PC board so that X0, X1, X0A, and X1A pins are surrounded by grounding area for stable operation.The MB91F155A, MB91155 and MB91154 devices do not contain a feedback resistor. T o use the clock function,3.Precautions•External Reset Input•External ClocksWhen using an external clock, normally, a clock of which the phase is opposite to that of X0 must be supplied to the X0 and X1 pins simultaneously. However, when using the clock along with STOP (oscillation stopped)15mode, the X1 pin stops when “H” is input in STOP mode. T o prevent one output from competing against another, an external resistor of about 1 kΩ should be provided.The following figure shows an example usage of an external clock.4.Care During Powering Up•When powering upWhen turning on the power supply, never fail to start from setting the RST pin to “L” level. And after the power supply voltage goes to V CC level, at least after ensuring the time for 5 machine cycle, then set to “H” level.•Source oscillation inputAt turning on the power supply, never fail to input the clock before cancellation of the oscillation stabilizing waiting.•Power on resettingWhen powering up or when turning the power back on after the supply voltage drops below the operation assurance range, be sure to reset the power.•Power on sequenceT urn on the power in the order of V CC, AV CC and AVRH. The power should be disconnected in inverse order.•Even when an AD converter is not in use, connect AV CC to the V CC level and AV SS to the V SS level.•Even when a DA converter is not in use, connect DAVC to the V CC level and DAVS to the V SS level.5.When the Clock Function (Calendar Macro) Is Not in Use16s BLOCK DIAGRAM1718s CPU CORE1.Memory SpaceThe FR family has a logical address space of 4 Gbytes (232 bytes) and the CPU linearly accesses the memory space.•Direct addressing areaThe following area in the address space is used for I/O.This area is called direct addressing area and an operand address can be specified directly in an instruction.The direct addressing area varies with the data size to be accessed as follows :→ byte data access : 0-0FF H→ half word data access : 0-1FF H→ word data access : 0-3FF H19203.RegistersThe family of FR microcontrollers has two types of registers : the registers residing in the CPU which are dedicated to applications and the general-purpose registers residing in the memory.•Dedicated registers :Program counter (PC) :A 32-bit register to indicate the location where an instructions is stored.Program status (PS) :A 32-bit register to store a register pointer or a condition code.Tablebase register (TBR) :Holds the vector table lead address used when EIT (exceptions/interrupt/trap) is processed.Return pointer (RP) :Holds the address to return from a subroutine to.System stack pointer (SSP) :Points to the system stack space.User stack pointer (USP) :Points to the user stack space.Multiplication and division result register (MDH/MDL) : A 32-bit multiplication and division register.•Program status (PS)The PS register holds program status and is further divided into three registers which are a Condition Code•Condition Code Register (CCR)S flag :Designates the stack pointer for use as R15.I flag :Controls enabling and disabling of user interrupt requests.N flag :Indicates the sign when arithmetic operation results are considered to be an integer represented by 2’s complement.Z flag :Indicates if arithmetic results were “0.”V flag :Considers the operand used for an arithmetic operation to be an integer represented by 2’s com-plement and indicates if the operation resulted in an overflow.C flag :Indicates whether or not an arithmetic operation resulted in a carry or a borrow from the most sig-nificant bit.•System condition Code Register (SCR)T flag :Designates whether or not to enable step trace trap.•Interrupt Level Mask register (ILM)ILM4 to ILM0 :Holds an interrupt level mask value to be used for level masking.An interrupt request is accepted only if the corresponding interrupt level among interruptrequests input to the CPU is higher than the value indicated by the ILM register.ILM4ILM3ILM2ILM1ILM0Interrupt level High-Low 000000Higher01000151111131Lowers GENERAL-PURPOSE REGISTERSGeneral-purpose registers are CPU registers R0 through R15 and used as accumulators during various oper-Of the 16 general-purpose registers, the following registers are assumed for specific applications. For this reason, some instructions are enhanced.R13 : Virtual accumulator (AC)R14 : Frame pointer (FP)R15 : Stack pointer (SP)Initial values to which R0 through R14 are reset are not defined. The initial value of R15 is 0000 0000H (the SSP value) .s SETTING MODE1.Mode PinsAs shown in T able 1 three pins, MD2, 1, and 0 are used to indicate an operation.Table 1 Mode pins and set modes2.Mode DataThe data which the CPU writes to “0000 07FF H ” after reset is called mode data.It is the mode register (MODR) that exists at “0000 07FF H .” Once a mode is set in this register, operations will take place in that mode. The mode register can be written only once after reset.[bits 7 and 6] : M1, M0These are bus mode setting bits. Specify the bus mode to be set to after writing to the mode register.[bits 5 to 0] : ∗These bits are reserved for the system.Mode pin Mode nameReset vector access area External databus width MD2MD1MD0000External vector mode 0External 8 bits External ROM bus mode 001External vector mode 1External 16 bits 010External vector mode 2External 32 bitsNot available on thisproduct type 011External vector modeInternal (Mode register) Single-chip mode1Not availableM1M0Function Remarks00Single-chip mode01Internal ROM-external bus mode 10External ROM-external bus mode11Setting not allowed“0” should be written to these bits at all times.[Precautions When Writing to the MODR]Before writing to the MODR, be sure to set AMD0 through 5 and determine the bus width in each CS (Chip Select) area.The MODR does not have bus width setting bits.The bus width value set with mode pins MD2 through 0 is enabled before writing to the MODR and the bus width value set with BW1 and 0 of AMD0 through 5 is enabled after writing to the MODR.For example, the external reset vector is normally executed with area 0 (the area where CS0 is active) and the bus width at that time is determined by pins MD 2 through 0. Suppose that the bus width is set to 32 or 16 bits in MD2 though 0 but no value is specified in AMD 0. If the MODR is written in this state, area 0 then switches to 8-bit bus mode and operates the bus since the initial bus width in AMD0 is set to 8 bits. This causes a malfunction.。

MAX485中文资料

本文是Maxim 正式英文资料的译文,Maxim 不对翻译中存在的差异或由此产生的错误负责。

请注意译文中可能存在文字组织或翻译错误,如需确认任何词语的准确性,请参考Maxim 提供的英文版资料。

索取免费样品和最新版的数据资料,请访问Maxim 的主页: 。

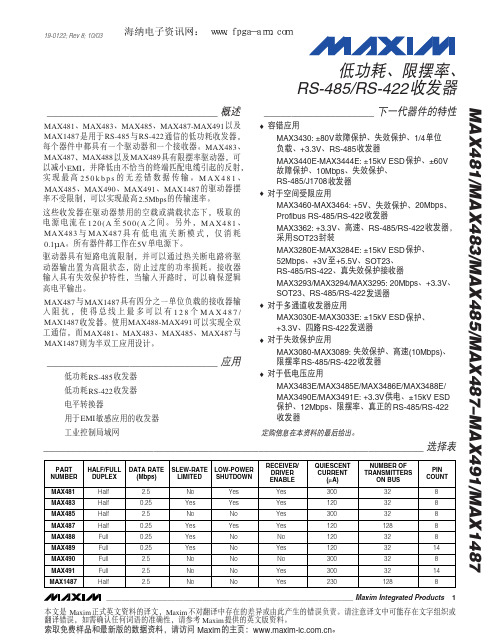

_______________________________概述MAX481、MAX483、MAX485、MAX487-MAX491以及MAX1487是用于RS-485与RS-422通信的低功耗收发器,每个器件中都具有一个驱动器和一个接收器。

MAX483、MAX487、MAX488以及MAX489具有限摆率驱动器,可以减小EMI ,并降低由不恰当的终端匹配电缆引起的反射,实现最高250k b p s 的无差错数据传输。

M A X 481、MAX485、MAX490、MAX491、MAX1487的驱动器摆率不受限制,可以实现最高2.5Mbps 的传输速率。

这些收发器在驱动器禁用的空载或满载状态下,吸取的电源电流在120(A 至500(A 之间。

另外,MAX481、MAX483与MAX487具有低电流关断模式,仅消耗0.1µA 。

所有器件都工作在5V 单电源下。

驱动器具有短路电流限制,并可以通过热关断电路将驱动器输出置为高阻状态,防止过度的功率损耗。

接收器输入具有失效保护特性,当输入开路时,可以确保逻辑高电平输出。

MAX487与MAX1487具有四分之一单位负载的接收器输入阻抗,使得总线上最多可以有128个M A X 487/MAX1487收发器。

使用MAX488-MAX491可以实现全双工通信,而MAX481、MAX483、MAX485、MAX487与MAX1487则为半双工应用设计。

_______________________________应用低功耗RS-485收发器低功耗RS-422收发器电平转换器用于EMI 敏感应用的收发器工业控制局域网____________________下一代器件的特性♦容错应用MAX3430: ±80V 故障保护、失效保护、1/4单位负载、+3.3V 、RS-485收发器MAX3440E-MAX3444E: ±15kV ESD 保护、±60V 故障保护、10Mbps 、失效保护、RS-485/J1708收发器♦对于空间受限应用MAX3460-MAX3464: +5V 、失效保护、20Mbps 、Profibus RS-485/RS-422收发器MAX3362: +3.3V 、高速、RS-485/RS-422收发器,采用SOT23封装MAX3280E-MAX3284E: ±15kV ESD 保护、52Mbps 、+3V 至+5.5V 、SOT23、RS-485/RS-422、真失效保护接收器MAX3293/MAX3294/MAX3295: 20Mbps 、+3.3V 、SOT23、RS-485/RS-422发送器♦对于多通道收发器应用MAX3030E-MAX3033E: ±15kV ESD 保护、+3.3V 、四路RS-422发送器♦对于失效保护应用MAX3080-MAX3089: 失效保护、高速(10Mbps)、限摆率RS-485/RS-422收发器♦对于低电压应用MAX3483E/MAX3485E/MAX3486E/MAX3488E/MAX3490E/MAX3491E: +3.3V 供电、±15kV ESD 保护、12Mbps 、限摆率、真正的RS-485/RS-422收发器MAX481/MAX483/MAX485/MAX487–MAX491/MAX1487低功耗、限摆率、RS-485/RS-422收发器_____________________________________________________________________选择表19-0122; Rev 8; 10/03定购信息在本资料的最后给出。

M-AUDIO OXYGEN 49用户指南(中文)

4.Press“+”和继续下去,直到你找到你想要的乐器演奏音符。 如果你想循环通过不同的手段,看看这听起来最好在你的歌声此方法非常有用。 快速选择程序变化: 1.Press 的高级功能按钮。 2.Press 黑键代表“PGM#。” 3.Press 键“3”,“2”,“Enter”键。 如果你想选择一个特定的号码这个方法是有用的,因为是这里的情况。 如果在八度“+”和“-”键被选择为不同的程序号(方法 1),在按钮上方的指示灯也不会 改变,因为它是不可能有负值的项目。同时按下“+”和“-”按钮将共同召回计划 0,即选 择一台三角钢琴的声音。 音色库 MSB 计划变更最常用来改变乐器和人声。然而,通过程序变更访问工具的数目限制为 128。某些 器件具有超过 128 的声音和需要不同的方法来访问这些额外的声音。一般情况下,这些设备 使用音色库 MSB 的消息。 增加/减少的音色库 MSB 的变化: 1.Press 的高级功能按钮。 2.Press 黑键代表“银行 LSB”或“银行 MSB”,分别。 3.Now 八度“+”和“-”键可以用来改变银行的 LSB。 4.Press“+”和继续下去,直到你找到你想要的乐器演奏音符。 使用快速选择方法: 1.Press 的高级功能按钮。 2.Press 黑键代表“银行 LSB”或“银行 MSB,”分别。 3.Press 键“3”,“2”,“Enter”键。 与程序变更,如果八度“+”和“-”键选择不同的银行低位或高位数(方法 1),上面的按 钮的指示灯也不会改变,因为它是不可能有一个与银行负值。同时按下“+”和“-”按钮将

虽然keystation49级标准在windowsxp中windowsvista中windows7windows的功能真正的即插即用和播放操作以及macosx我们建议您花几分钟时间阅读本手册以了解正确的操作先进的功能和可编程性

MB90945资料

DS07-13741-2EFUJITSU SEMICONDUCTORDATA SHEET16-bit Proprietary MicrocontrollerCMOSF 2MC-16LX MB90945 SeriesMB90F946A/947A/F947/F947A/F949/F949A/V390HA/V390HB■DESCRIPTIONThe MB90945 series with one FULL-CAN* interface and FLASH ROM is especially designed for automotive HVAC applications. Its main feature is the on board CAN* Interface, which conform to V2.0 Part A and Part B, while supporting a very flexible message buffer scheme and so offering more functions than a normal FULL-CAN*approach. With the new 0.35 µm CMOS technology, Fujitsu now offers on-chip FLASH-ROM program memory up to 384 K bytes. An internal voltage booster removes the necessity for a second programming voltage. An on board voltage regulator provides 3 V to the internal MCU core. This creates a major advantage in terms of EMI and power consumption.The internal PLL clock frequency multiplier provides an internal 42 ns instruction cycle time from an external 4 MHz clock.The unit features a 4-channel Output Compare Unit and a 6-channel Input Capture Unit with two separate 16-bit free running timers. Up to 3 UARTs, one Serial I/O and one I 2C constitute additional functionality for communication purposes.* : Controller Area Network (CAN) - License of Robert Bosch GmbHMB90945 Series2■FEATURES•16-bit core CPU; 4 MHz external clock (24 MHz internal, 42 ns instr. cycle time)•New 0.35 µm CMOS Process T echnology•Internal voltage regulator supports 3 V MCU core, offering low EMI and low power consumption figures •One FULL-CAN interface; conforming to Version 2.0 Part A and Part B, flexible message buffering (mailbox and FIFO buffering can be mixed)•Powerful interrupt functions (8 progr. priority levels; 8 external interrupts)•EI2OS - Automatic transfer function independant of CPU; 16 channels of intelligent I/O Services•18-bit Time-base counter•Watchdog Timer•1 full duplex UART; support 10.4 KBaud (USA standard)•up to 2 full duplex UARTs (LIN/SCI/SPI)•1 Serial I/O (SPI)•1I2C interface•A/D Converter : 15 channels analog inputs (Resolution 10-bit or 8-bit)•16-bit reload timer × 1channel•ICU (Input capture) 16-bit × 6 channels•OCU (Output compare) 16-bit × 4 channels•16-bit free running timer × 2 channels (FRT0 : ICU 0/1, OCU 0/1/2/3, FRT1 : ICU 2/3/4/5)•8/16-bit Programmable Pulse Generator 6 channels × 8/16-bit•Optimized instruction set for controller applications (bit, byte, word and long-word data types; 23 different addressing modes; barrel shift; variety of pointers)•4-byte instruction execution queue•signed multiply (16-bit × 16-bit) and divide (32-bit/16-bit) instructions available•Program Patch Function (3 address match registers)•Fast Interrupt processing•Low Power Consumption modeSleep modeTimebase timer modeStop modeCPU intermittent mode•Automotive input levels•Package : 100-pin plastic QFPMB90945 Series3■PRODUCT LINEUP(Continued)Part NumberParameter MB90947AMB90F946AMB90F947, MB90F947A MB90F949, MB90F949AMB90V390HA MB90V390HBCPU F 2MC-16LX CPUSystem clockOn-chip PLL clock multiplier (×1, ×2, ×3, ×4, ×6, 1/2 when PLL stops)Minimum instruction execution time : 42 ns (4 MHz oscillation clock, PLL clockmultiplied by 6)ROMROM memory 128 KbytesBoot-block Flash memory 384 KbytesBoot-block Flash memory256 Kbytes: MB90F949MB90F949A128 Kbytes: MB90F947MB90F947A ExternalRAM6 Kbytes 16 Kbytes 12 Kbytes: MB90F949MB90F949A6 Kbytes: MB90F947MB90F947A30 KbytesEmulator-specific power supply *1⎯YesTechnology0.35 µm CMOS with on-chip voltage regulator for internal power supply0.35 µm CMOS with on-chip voltage regulator for internal power supply + Flash memory with on-chip charge pump for programming voltage0.35 µm CMOS with on-chip voltageregulator for internal power supplyOperating voltage range 3.5 V to 5.5 V : other than conditions listed below 4.0 V to 5.5 V : when writing to Flash 4.5 V to 5.5 V : if A/D Converter is used5 V ± 10%Temperature range −40 °C to +105 °C⎯PackageQFP-100P PGA-299C UART1 channel2 channelsFull duplex double bufferSupports asynchronous/synchronous (with start/stop bit) transferBaud rate : 4808/9615/10417/19230/38460/62500/500000 bps (asynchronous)500 K/1 M/2 Mbps (synchronous) at System clock = 20 MHzUART(LIN/SCI/SPI)1 channel2 channels1 channel2 channelsSerial I/O1 channelTransfer can be started from MSB or LSBSupports internal clock synchronized transfer and external clock synchronized transfer Supports positive-edge and negative-edge clock synchronizationBaud rate : 31.25 K/62.5 K/125 K/500 K/1 Mbps at System clock = 20 MHzI 2C (400 Kbps)1 channelMB90945 Series4(Continued) Part NumberParameterMB90947A MB90F946AMB90F947, MB90F947AMB90F949, MB90F949AMB90V390HAMB90V390HBA/D Converter(15 input channels)10-bit or 8-bit resolutionConversion time : Min 4.9 µs includes sample time (per one channel, only at certainmachine clock frequencies)16-bit Reload Timer1 channel2 channelsOperation clock frequency : fsys/21, fsys/23, fsys/25 (fsys = System clock frequency)Supports External Event Count function16-bitI/O Timer(2 channels)Signals an interrupt when overflowingSupports Timer Clear when a match with Output Compare (ch0)Operation clock freq. : fsys, fsys/21, fsys/22, fsys/23, fsys/24, fsys/25, fsys/26, fsys/27(fsys = System clock freq.)I/O Timer 0 (clock input FRCK0) corresponds to ICU 0/1, OCU 0/1/2/3I/O Timer 1 (clock input FRCK1) corresponds to ICU 2/3/4/516-bitInput Capture(6 channels)Rising edge, falling edge or rising & falling edge sensitiveSix 16-bit Capture registersSignals an interrupt upon external event⎯ICU 3/5 inputs areshared with OCU 6/7outputs16-bitOutput Compare4 channels8 channelsSignals an interrupt when a match with 16-bit I/O TimerEight 16-bit compare registers.A pair of compare registers can be used to generate an output signal.⎯ICU 3/5 inputs areshared with OCU 6/7outputs8/16-bitProgrammablePulse Generator(6 channels)Supports 8-bit and 16-bit operation modesTwelve 8-bit reload countersTwelve 8-bit reload registers for L pulse widthTwelve 8-bit reload registers for H pulse widthA pair of 8-bit reload counters can be configured as one 16-bit reload counter or as8-bit prescaler plus 8-bit reload counterOperation clock freq. : fsys, fsys/21, fsys/22, fsys/23, fsys/24 or 102.4 µs (fosc = 5 MHz)(fsys = System clock frequency, fosc = Oscillation clock frequency)CAN Interface1 channel 5 channelsConforms to CAN Specification Version 2.0 Part A and BAutomatic re-transmission in case of errorAutomatic transmission responding to Remote FramePrioritized 16 message buffers for data and ID’sSupports multiple messagesFlexible configuration of acceptance filtering :Full-bit compare/Full-bit mask/Two partial bit masksSupports up to 1 MbpsMB90F947/F949/V390HA: Do not use clock modulation and CAN at the same timeMB90945 Series5(Continued)Part NumberParameter MB90947AMB90F946AMB90F947, MB90F947A MB90F949, MB90F949A MB90V390HA MB90V390HBExternal Interrupt (8 channels) Can be programmed edge sensitive or level sensitiveStepping motor controller ⎯ 2 channels Watch Timer ⎯ 1 channel Sound generator ⎯ 1 channel Machine clock out-put⎯2 channels(non-inverted and in-verted) Program patch function3 address match registers5 address matchregistersI/O PortsVirtually all external pins can be used as general purpose I/O All push-pull outputsBit-wise programmable as input/output or peripheral signalAutomotive input level (P21/RX1, P42/SDA, P43/SCL have CMOS Schmitt input level) Port-wise program-mable as Automotive (default) or CMOSSchmitt input levelI/O Ports with 4 mA CMOS output All ports except P42, P43All ports except P80, P81, PA0 to PA7, P42, P43I/O Ports with 3 mA CMOS output P42, P43P42, P43I/O Ports with 30 mA CMOS output with slewrate control⎯P80, P81, PA0 to PA7Clock ModulatorPhase modulation modePhase modulation modeFrequency and phasemodulation modeMB90F947/F949/V390HA :Do not use clock modulation and CAN at the same timeReduces EMI by modulating the PLL clockStart-up time at power-on reset3 × 216 oscillation cycles (49.152 ms at4 MHz oscillation) + oscilla-tion time of oscillator*2218 oscillation cycles (65.536 ms at 4 MHzoscillation) +oscillation time of os-cillator*2MB90945 Series6(Continued)*1 : It is setting of Jumper switch SI when Emulation Pod (MB2147) is used.Please refer to the Emulator hardware manual about details.*2 : Oscillation time of the oscillator is the time that the amplitude reaches 90%.*3 : Embedded Algorithm is a trade mark of Advanced Micro Devices Inc.*4 : Data is based on reliability tests during process qualification (the value for T A=+ 85 °C is calculated via the Arrenhius formula from data of accelerated measurements at elevated temperature) .Part NumberParameterMB90947A MB90F946AMB90F947, MB90F947AMB90F949, MB90F949AMB90V390HAMB90V390HBFlashMemory⎯Supports automatic programming, EmbeddedAlgorithm TM*3Write/Erase/Erase-Suspend/Resume com-mandsA flag indicating completion of the algorithmNumber of erase cycles : 10,000 timesData retention time : 20 years*4Hard-wired reset vector available in order topoint to a fixed boot sector in Flash Memory(address FFA000H, mode data 00H)Boot block configurationErase can be performed on each blockBlock protection with external programmingvoltageWrite and erase at F max= 20 MHz⎯MB90945 Series ■PIN ASSIGNMENTS7MB90945 Series8MB90945 Series9■PIN DESCRIPTION(Continued)Pin no.Pin nameCircuit typeFunction92X1A Pin for oscillation 93X0Pin for oscillation 54RST B Reset input77 to 82P00 to P05DGeneral purpose I/OIN0 to IN5Inputs for the Input Captures 0-583 to 86P06, P07P10, P11DGeneral purpose I/OOUT0 to OUT3Outputs for the Output Compares 87, 88P12, P13D General purpose I/O 89P14D General purpose I/OTIN0TIN0 input for the 16-bit Reload Timer 094P15D General purpose I/OTOT0TOT0 output for the 16-bit Reload Timer 095, 96P16, P17D General purpose I/O 97P20D General purpose I/OTX1TX output for CAN Interface 198P21F General purpose I/O RX1RX input for CAN Interface 199, 1001 to 4P22 to P27D General purpose I/OINT2 to INT7External interrupt inputs for INT2 to INT75 to 8P30 to P33D General purpose I/O 9P34D General purpose I/O SOT0SOT output for UART010P35D General purpose I/O SCK0SCK input/output for UART011P36D General purpose I/O SIN0SIN input for UART012P37D General purpose I/O 13P44D General purpose I/O 14P45D General purpose I/OADTG External trigger input of the A/D Converter 18, 19P40, P41D General purpose I/O 20P42F General purpose I/O SDASerial data for I 2C interfaceMB90945 Series10(Continued) Pin no.Pin name Circuit type Function21P43FGeneral purpose I/OSCL Serial clock for I2C interface22, 23P46, P47DGeneral purpose I/OINT0, INT1External interrupt inputs for INT0, INT124P50DGeneral purpose I/OPPG10Output for the PPG125 to 28PB0 to PB3EGeneral purpose I/OPPG02 to PPG05Outputs for the PPG4, 6, 8, AAN8 to AN11Inputs for the A/D Converter29PB4EGeneral purpose I/OSIN4SIN input for Serial I/OAN12Input for the A/D Converter30PB5EGeneral purpose I/OSCK4SCK input/output for Serial I/OAN13Input for the A/D Converter31PB6EGeneral purpose I/OSOT4SOT output for Serial I/OAN14Input for the A/D Converter36 to 43P60 to P67EGeneral purpose I/OAN0 to AN7Inputs for the A/D Converter45 to 48P51 to P54DGeneral purpose I/OPPG11 to PPG14Outputs for the PPG3, 5, 7, 949PB7DGeneral purpose I/OFRCK0FRCK0 input for the 16-bit I/O Timer 050P97DGeneral purpose I/OFRCK1FRCK1 input for the 16-bit I/O Timer 155P55DGeneral purpose I/OPPG15Outputs for the PPGB56, 57P56, P57DGeneral purpose I/OPPG00, PPG01Outputs for the PPG0, PPG258P90DGeneral purpose I/OSIN2SIN input for UART 2 (LIN/SCI/SPI) (only MB90V390HA,MB90V390HB and MB90F946A)59P93DGeneral purpose I/OSIN3SIN input for UART3 (LIN/SCI/SPI)(Continued)Pin no.Pin name Circuit type Function60P95DGeneral purpose I/OSOT3SOT output for UART3 (LIN/SCI/SPI)61P94DGeneral purpose I/OSCK3SCK input/output for UART3 (LIN/SCI/SPI)62P91DGeneral purpose I/OSCK2SCK input/output for UART 2 (LIN/SCI/SPI) (only MB90V390HA,MB90V390HB and MB90F946A)63P92DGeneral purpose I/OSOT2SOT output for UART 2 (LIN/SCI/SPI) (only MB90V390HA,MB90V390HB and MB90F946A)64P96D General purpose I/O67 to 74PA0 to PA7H General purpose I/O. For the EVA device, these pins are high current outputs.75, 76P80, P81H General purpose I/O. For the EVA device, these pins are high current outputs.32AV CC⎯Dedicated power supply pin (5 V) for the A/D converter33AVRH⎯Dedicated pos. reference voltage pin for the A/D converter 34AVRL⎯Dedicated neg. reference voltage pin for the A/D converter 35AVss⎯Dedicated power supply pin (0 V) for the A/D converter52, 53MD1, MD0C These are input pins used to designate the operating mode. They should be connected directly to V CC or V SS.51MD2G This is an input pin used to designate the operating mode. It should be connected directly to V CC or V SS.1565 90Vcc⎯These are power supply (5 V) input pins. For the EVA device, pin65 is the DV CC supply pin for the high current outputs.1644 66 91Vss⎯These are power supply (0 V) input pins. For the EVA device, pin66 is the DV SS supply pin for the high current outputs.17C⎯This is the power supply stabilization capacitor pin. It should be connected to higher than or equal to 0.1 µF ceramic capacitor.■I/O CIRCUIT TYPE(Continued)■HANDLING DEVICESSpecial care is required for the following when handling the device :•Preventing latch-up•Stabilization of supply voltage•T reatment of unused pins•Using external clock•Power supply pins (V CC/V SS)•Pull-up/pull-down resistors•Crystal Oscillator Circuit•T urning-on Sequence of Power Supply to A/D Converter and Analog Inputs•Connection of Unused Pins of A/D Converter if A/D Converter is unused.•Caution on Operations during PLL Clock Mode1.Preventing latch-upCMOS IC chips may suffer latch-up under the following conditions :•A voltage higher than V CC or lower than V SS is applied to an input or output pin.•A voltage higher than the rated voltage is applied between V CC and V SS.•The AV CC power supply is applied before the V CC voltage.Latch-up may increase the power supply current drastically, causing thermal damage to the device.In using the devices, take sufficient care to avoid exceeding maximum ratings.For the same reason, also be careful not to let the analog power-supply voltage (AV CC, AVRH) exceed the digital power-supply voltage.2.Stabilization of supply voltageA sudden change in the supply voltage may cause the device to malfunction even within the specified V CC supplyvoltage operation range. Therefore, the V CC supply voltage should be stabilized.For reference, the supply voltage should be controlled so that V CC ripple variations (peak-to-peak values) at commercial frequencies (50 Hz to 60 Hz) fall below 10 % of the standard V CC supply voltage and the coefficient of fluctuation does not exceed 0.1 V/ms at instantaneous power switching.3.Treatment of unused pinsLeaving unused input pins open may result in misbehavior or latch up and possible permanent damage of the device. Therefore they must be pulled up or pulled down through resistors. In this case those resistors should be more than 2 kΩ .Unused bidirectional pins should be set to the output state and can be left open, or the input state with the above described connection.ing external clock5.Power supply pins (V CC/V SS)•If there are multiple V CC and V SS pins, from the point of view of device design, pins to be of the same potential are connected the inside of the device to prevent such malfunctioning as latch up.T o reduce unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level, and observe the standard for total output current, be sure to connect the V CC and V SS pins to the power supply and ground externally.•Connect V CC and V SS to the device from the current supply source at a low impedance.•As a measure against power supply noise, connect a capacitor of about 0.1 µF as a bypass capacitor between6.Pull-up/pull-down resistorsThe MB90945 series does not support internal pull-up/pull-down resistors option. Use external components where needed.7.Crystal Oscillator CircuitNoises around X0 or X1 pins may be possible causes of abnormal operations. Make sure to provide bypass capacitors via shortest distance from X0, X1 pins, crystal oscillator (or ceramic oscillator) and ground lines, and make sure, to the utmost effort, that lines of oscillation circuit not cross the lines of other circuits while you designa printed circuit.It is highly recommended to provide a printed circuit board art work surrounding X0 and X1 pins with a ground area for stabilizing the operation.8.Turning-on Sequence of Power Supply to A/D Converter and Analog InputsMake sure to turn on the A/D converter power supply (AV CC, AVRH, AVRL) and analog inputs (AN0 to AN14) after turning-on the digital power supply (V CC) .T urn-off the digital power after turning off the A/D converter supply and analog inputs. In this case, make sure that the voltage not exceed AVRH or AV CC (turning on/off the analog and digital power supplies simultaneously is acceptable) .9.Connection of Unused Pins of A/D Converter if A/D Converter is unusedConnect unused pins of A/D converter to AV CC= V CC, AV SS= AVRH = AVRL = V SS.10.Notes on During Operation of PLL Clock ModeIf the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even when there is no external oscillator or external clock input is stopped. Performance of this operation, however, cannot be guaranteed.■BLOCK DIAGRAMS■MEMORY MAPNote : The high-order portion of bank 00 gives the image of the FF bank ROM to make the small model of the Ccompiler effective. Since the low-order 16 bits are the same, the table in ROM can be referenced without using the far specification in the pointer declaration.For example, an attempt to access 00C000H accesses the value at FFC000H in ROM.The ROM area in bank FF exceeds 32/48 K bytes, and its entire image cannot be shown in bank 00.The image between FF4000H /FF8000H and FFFFFF H is visible in bank 00, while the image between FF0000H and FF3FFF H /FF7FFF H is visible only in bank FF .MB90947A FFFFFF HFF0000H FEFFFF H FE0000H0018FF H 000100H 0000BF H 000000HROM (FF bank)ROM (FE bank)RAM 6 Kbytes PeripheralPeripheralROM (Image of FF bank) 004000H /003FFF H003500H00FFFF H008000H: No accessMB90F949FFFFFF HFF0000H FEFFFF H FE0000H 0030FF H000100H 0000BF H 000000HROM (FF bank)ROM (FE bank)RAM 12 KbytesPeripheralPeripheralROM (Image of FF bank) 004000H /003FFF H 003500H 00FFFF H008000HFDFFFF H FD0000H FCFFFF H FC0000HROM (FD bank)ROM (FC bank)FFFFFF H FF0000H FEFFFF H FE0000H FDFFFF H FD0000H FCFFFF H FC0000H 008000H 0070FF H003FFF H 003500H 0030FF H000100H0000BF H 000000HMB90V390HA ROM (FF bank)ROM (FE bank)ROM (FD bank)ROM (FC bank)PeripheralRAM 12 KbytesPeripheralROM (FB bank)FBFFFF H FB0000H FAFFFF H FA0000H F9FFFF H F90000H ROM (F9 bank)ROM (FA bank)00FFFF H 004100H RAM 12 KbytesROM (Image of FF bank)8017FF H 800000HRAM 6 Kbytes MB90F947MB90F949AMB90F947AFFFFFF H FF0000H FEFFFF H FE0000H 0030FF H000100H 0000BF H 000000HROM (FF bank)ROM (FE bank)RAM 12 KbytesPeripheralPeripheralROM (Image of FF bank)008000H003FFF H 003500H 00FFFF H FDFFFF H FD0000HFBFFFF H FB0000H ROM (FD bank)ROM (FA bank)MB90F946AROM (FB bank)ROM (F9 bank)FAFFFF H FA0000H F9FFFF H F90000HRAM 4 Kbytes004100H 0050FF H MB90V390HB■I/O MAP(Continued)Address RegisterAbbrevia-tion AccessResource nameInitial value 00H Port 0 data register PDR0R/W Port 0XXXXXXXX 01H Port 1 data register PDR1R/W Port 1XXXXXXXX 02H Port 2 data register PDR2R/W Port 2XXXXXXXX 03H Port 3 data register PDR3R/W Port 3XXXXXXXX 04H Port 4 data register PDR4R/W Port 4XXXXXXXX 05H Port 5 data register PDR5R/W Port 5XXXXXXXX 06H Port 6 data registerPDR6R/WPort 6XXXXXXXX07H Reserved 08H Port 8 data register PDR8R/W Port 8XXXXXXXX 09H Port 9 data register PDR9R/W Port 9XXXXXXXX 0A H Port A data register PDRA R/W Port A XXXXXXXX 0B H Port B data register PDRB R/W Port B XXXXXXXX 0C H Analog Input Enable 0ADER0R/W Port 6, A/D 111111110D H Analog Input Enable 1/ ADC Select ADER1R/W Port B, A/D 011111110E H Input Level Select Register(MB90V390HA/MB90V390HB only) ILSR R/W Ports 000000000F H Input Level Select Register(MB90V390HA/MB90V390HB only) ILSR R/W Ports 0000000010H Port 0 direction register DDR0R/W Port 00000000011H Port 1 direction register DDR1R/W Port 10000000012H Port 2 direction register DDR2R/W Port 20000000013H Port 3 direction register DDR3R/W Port 30000000014H Port 4 direction register DDR4R/W Port 40000000015H Port 5 direction register DDR5R/W Port 50000000016H Port 6 direction registerDDR6R/WPort 60000000017H Reserved 18H Port 8 direction register DDR8R/W Port 8XXXXXX0019H Port 9 direction register DDR9R/W Port 9000000001A H Port A direction register DDRA R/W Port A 000000001B H Port B direction register DDRB R/WPort B000000001C H to 1F HReservedAddress Register Abbrevia-tionAccess Resource name Initial value20H Serial Mode Control 0UMC0R/WUART00000010021H Status 0USR0R/W0001000022H Input/Output Data 0UIDR0/UODR0R/W XXXXXXXX23H Rate and Data 0URD0R/W0000000X 24H to 2B H Reserved2C H Serial Mode Control 4SMCS4R/WSerial I/OInterface XXXX00002D H Serial Mode Control 4SMCS4R/W00000010 2E H Serial Data 4SDR4R/W XXXXXXXX 2F H Serial I/O Prescaler/Edge Selector 4CDCR4R/W0X0X000030H External Interrupt Enable ENIR R/WExternal Interrupt 0000000031H External Interrupt Request EIRR R/W XXXXXXXX 32H External Interrupt Level ELVR R/W00000000 33H External Interrupt Level ELVR R/W0000000034H A/D Control Status 0ADCS0R/WA/D Converter 0000000035H A/D Control Status 1ADCS1R/W00000000 36H A/D Data 0ADCR0R XXXXXXXX 37H A/D Data 1ADCR1R/W000000XX38H PPG0 operation mode control register PPGC0R/W16-bit ProgramablePulseGenerator 0/10X000XX139H PPG1 operation mode control register PPGC1R/W0X000001 3A H PPG0 and PPG1 clock select register PPG01R/W000000XX 3B H Reserved3C H PPG2 operation mode control register PPGC2R/W16-bit ProgramablePulseGenerator 2/30X000XX13D H PPG3 operation mode control register PPGC3R/W0X000001 3E H PPG2 and PPG3 clock select register PPG23R/W000000XX 3F H Reserved40H PPG4 operation mode control register PPGC4R/W16-bit ProgramablePulseGenerator 4/50X000XX141H PPG5 operation mode control register PPGC5R/W0X000001 42H PPG4 and PPG5 clock select register PPG45R/W000000XX 43H Reserved44H PPG6 operation mode control register PPGC6R/W16-bit ProgramablePulseGenerator 6/70X000XX145H PPG7 operation mode control register PPGC7R/W0X000001 46H PPG6 and PPG7 clock select register PPG67R/W000000XX 47H Reserved(Continued)Address Register Abbrevia-tionAccess Resource name Initial value48H PPG8 operation mode control register PPGC8R/W16-bit ProgramablePulseGenerator 8/90X000XX149H PPG9 operation mode control register PPGC9R/W0X000001 4A H PPG8 and PPG9 clock select register PPG89R/W000000XX 4B H Reserved4C H PPGA operation mode control register PPGCA R/W16-bit ProgramablePulseGenerator A/B 0X000XX14D H PPGB operation mode control register PPGCB R/W0X000001 4E H PPGA and PPGB clock select register PPGAB R/W000000XX 4F H Reserved50H Timer Control Status 0TMCSR0R/W16-bit Reload Timer00000000051H Timer Control Status 0TMCSR0R/W XXXX0000 52H to 53H Reserved54H Input Capture Control Status 0/1ICS01R/W Input Capture 0/100000000 55H Input Capture Control Status 2/3ICS23R/W Input Capture 2/300000000 56H Input Capture Control Status 4/5ICS45R/W Input Capture 4/500000000 57H Reserved58H Output Compare Control Status 0OCS0R/WOutput Compare 0/10000XX0059H Output Compare Control Status 1OCS1R/W0XX000005A H Output Compare Control Status 2OCS2R/WOutput Compare 2/30000XX005B H Output Compare Control Status 3OCS3R/W0XX00000 5C H to6E HReserved6F H ROM Mirror ROMM W ROM Mirror XXXXXXX1 70H to 7F H Reserved80H to 8F H Reserved for CAN Interface 1. Refer to “■ CAN CONTROLLER”90H to 9D H Reserved9E H ROM Correction Control Status 0PACSR0R/W ROM Correction 000000000 9F H Delayed Interrupt/release DIRR R/W Delayed Interrupt XXXXXXX0A0H Low-power Mode LPMCR R/W Low PowerController00011000A1H Clock Selector CKSCR R/W Low PowerController11111100A2H to A7H ReservedA8H Watchdog Control WDTC R/W Watchdog Timer XXXXX111 A9H Timebase timer Control TBTC R/W Timebase timer1XX00100 AA H toAD HReserved(Continued)Address Register Abbrevia-tionAccess Resource name Initial valueAE H Flash Control Status(Flash devices only. Otherwise reserved)FMCS R/W Flash memory000X0000AF H ReservedB0H Interrupt control register 00ICR00R/WInterrupt controller 00000111B1H Interrupt control register 01ICR01R/W00000111 B2H Interrupt control register 02ICR02R/W00000111 B3H Interrupt control register 03ICR03R/W00000111 B4H Interrupt control register 04ICR04R/W00000111 B5H Interrupt control register 05ICR05R/W00000111 B6H Interrupt control register 06ICR06R/W00000111 B7H Interrupt control register 07ICR07R/W00000111 B8H Interrupt control register 08ICR08R/W00000111 B9H Interrupt control register 09ICR09R/W00000111 BA H Interrupt control register 10ICR10R/W00000111 BB H Interrupt control register 11ICR11R/W00000111 BC H Interrupt control register 12ICR12R/W00000111 BD H Interrupt control register 13ICR13R/W00000111 BE H Interrupt control register 14ICR14R/W00000111 BF H Interrupt control register 15ICR15R/W00000111 C0H toFF HReserved(Continued)Address Register Abbrevia-tionAccess Resource name Initial value3500H Reload L PRLL0R/W16-bit ProgramablePulseGenerator 0/1XXXXXXXX3501H Reload H PRLH0R/W XXXXXXXX 3502H Reload L PRLL1R/W XXXXXXXX 3503H Reload H PRLH1R/W XXXXXXXX3504H Reload L PRLL2R/W16-bit ProgramablePulseGenerator 2/3XXXXXXXX3505H Reload H PRLH2R/W XXXXXXXX 3506H Reload L PRLL3R/W XXXXXXXX 3507H Reload H PRLH3R/W XXXXXXXX3508H Reload L PRLL4R/W16-bit ProgramablePulseGenerator 4/5XXXXXXXX3509H Reload H PRLH4R/W XXXXXXXX 350A H Reload L PRLL5R/W XXXXXXXX 350B H Reload H PRLH5R/W XXXXXXXX350C H Reload L PRLL6R/W16-bit ProgramablePulseGenerator 6/7XXXXXXXX350D H Reload H PRLH6R/W XXXXXXXX 350E H Reload L PRLL7R/W XXXXXXXX 350F H Reload H PRLH7R/W XXXXXXXX3510H Reload L PRLL8R/W16-bit ProgramablePulseGenerator 8/9XXXXXXXX3511H Reload H PRLH8R/W XXXXXXXX 3512H Reload L PRLL9R/W XXXXXXXX 3513H Reload H PRLH9R/W XXXXXXXX3514H Reload L PRLLA R/W16-bit ProgramablePulseGenerator A/B XXXXXXXX3515H Reload H PRLHA R/W XXXXXXXX 3516H Reload L PRLLB R/W XXXXXXXX 3517H Reload H PRLHB R/W XXXXXXXX3518H Serial Mode Register SMR3R/WUART3000000003519H Serial Control Register SCR3R/W00000000351A H Reception/Transmission Data Register RDR3/TDR3R/W00000000351B H Serial Status Register SSR3R/W00001000 351C H Extended Communication Control Reg.ECCR3R/W000000XX 351D H Extended Status/Control Register ESCR3R/W00000100 351E H Baud Rate Register 0BGR03R/W00000000 351F H Baud Rate Register 1BGR13R/W00000000(Continued)。

MB90F546GSPF中文资料

2

MB90540/540G/545/545G Series

(Continued) • UART 1 With full-duplex double buffer (8-bit length) Clock asynchronized or clock synchronized serial (extended I/O serial) can be used. • External interrupt circuit (8 channels) A module for starting an extended intelligent I/O service (EI2OS) and generating an external interrupt which is triggered by an external input. • Delayed interrupt generation module Generates an interrupt request for switching tasks. • 8/10-bit A/D converter (8 channels) 8/10-bit resolution can be selectively used. Starting by an external trigger input. Conversion time : 26.3 µs • FULL-CAN interfaces MB90540 series : 2 channel MB90545 series : 1 channel Conforming to Version 2.0 Part A and Part B Flexible message buffering (mailbox and FIFO buffering can be mixed) • External bus interface : Maximum address space 16 Mbytes • Package: QFP-100, LQFP-100

MB90F562BPFM中文资料

The MB90560/565 series is a general-purpose 16-bit microcontroller designed for industrial, OA, and process control applications that require high-speed real-time processing. The device features a multi-function timer able to output a programmable waveform. The microcontroller instruction set is based on the same AT architecture as the F2MC-8L and F2MC-16L families with additional instructions for high-level languages, extended addressing modes, enhanced signed multiplication and division instructions, and a complete range of bit manipulation instructions. The microcontroller has a 32-bit accumulator for processing long word (32-bit) data.

s FEATURES

• Clock • Internal oscillator circuit and PLL clock multiplication circuit • Oscillation clock Clock speed selectable from either the machine clock, main clock, or PLL clock. The main clock is the oscillation clock divided into 2 (0.5 MHz to 8 MHz for a 1 MHz to 16 MHz base oscillation) . The PLL clock is the oscillation clock multiplied by one to four (4 MHz to 16 MHz for a 4 MHz base oscillation) . • Minimum instruction execution time : 62.5 ns (for oscillation = 4 MHz, PLL clock setting = × 4, VCC = 5.0 V) • Maximum CPU memory space : 16 MB • 24-bit addressing • Bank addressing (Continued)

MB90F387S资料

CPU functions

Minimum instruction execution time : 62.5 ns (at 16-MHz machine clock) Interrupt processing time : 1.5 µs at minimum (at 16-MHz machine clock) Low power consumption (standby) mode I/O port Sleep mode/Clock mode/Time-base timer mode/ Stop mode/CPU intermittent General-purpose input/output ports (CMOS output) : 34 ports (36 ports*2) including 4 high-current output ports (P14 to P17) 18-bit free-run counter Interrupt cycle : 1.024 ms, 4.096 ms, 16.834 ms, 131.072 ms (with oscillation clock frequency at 4 MHz) Reset generation cycle: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (with oscillation clock frequency at 4 MHz) 16-bit free-run timer Input capture Number of channels: 1 Interrupt upon occurrence of overflow Number of channels: 4 Retaining free-run timer value set by pin input (rising edge, falling edge, and both edges) Number of channels: 2 16-bit reload timer operation Count clock cycle: 0.25 µs, 0.5 µs, 2.0 µs (at 16-MHz machine clock frequency) External event count is allowed. 15-bit free-run counter Interrupt cycle: 31.25 ms, 62.5 ms, 12 ms, 250 ms, 500 ms, 1.0 s, 2.0 s (with 8.192 kHz sub clock) Number of channels: 2 (four 8-bit channels are available also.) PPG operation is allowed with four 8-bit channels or one 16-bit channel. Outputting pulse wave of arbitrary cycle or arbitrary duty is allowed. Count clock: 62.5 ns to 1 µs (with 16 MHz machine clock)

序列号大全