加法器

数字电路的基础知识 几种常用的组合逻辑组件

(2-1)

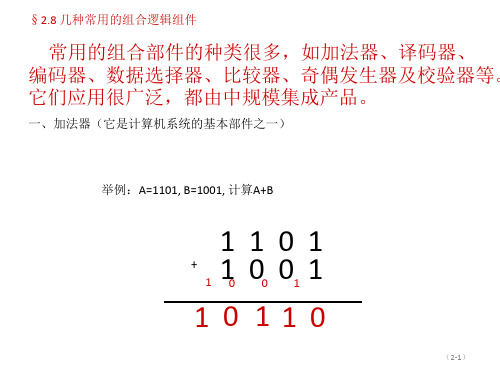

加法运算的基本规则: (1)逢二进一。 (2)最低位是两个数最低位的叠加,不需考虑进位。 (3)其余各位都是三个数相加,包括加数、被加数和低位来的进位。 (4)任何位相加都产生两个结果:本位和、向高位的进位。

(2-2)

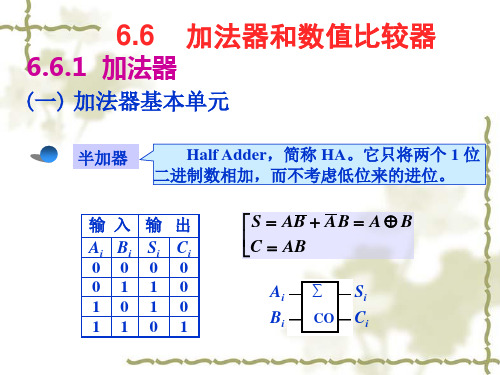

(1)半加器:

半加运算不考虑从低位来的进位

A---加数;B---被加数;S---本位和; C---进位。

设ABC每个输出代表一种组合。 b.由状态表写出逻辑式 c.由逻辑式画出逻辑图

(2-23)

2-4线译码器74LS139的内部线路

A1

A0 输入

S

控制端

&

Y3

&

Y2

输出

&

Y1

&

Y0

(2-24)

74LS139的功能表

S

A1 A0

Y0

Y1

Y2

Y3

1XX 1 1 1 1

0000111

0011011

0101101

(2-36)

0111110

“—”表示低电平有效。

(2-25)

74LS139管脚图

Ucc 2S 2A0 2A1 2Y0 2Y1 2Y2 2Y3

2S 2A0 2A1 2Y0 2Y1 2Y2 2Y3

1S

1A0 1A1 1Y0 1Y1 1Y2 1Y3

1S 1A0 1A1 1Y0 1Y1 1Y2 1Y3 GND

一片139种含两个2-4译码器

(2-26)

例:利用线译码器分时将采样数据送入计算机。

总 线

三态门

EA 三态门

EB 三态门

EC 三态门

ED

A

B

C

加法器实训实验报告

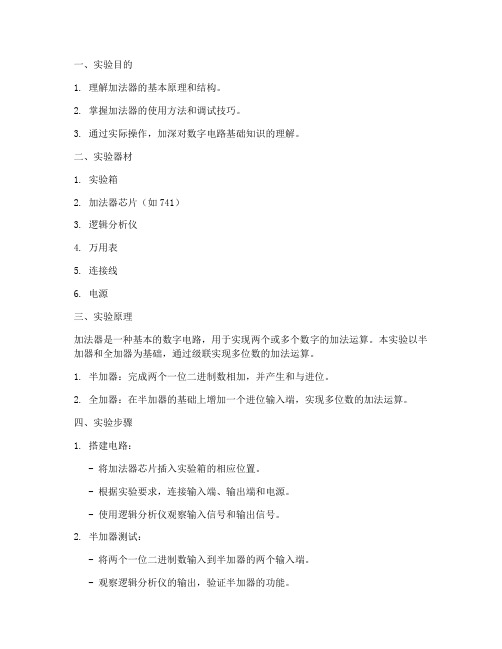

一、实验目的1. 理解加法器的基本原理和结构。

2. 掌握加法器的使用方法和调试技巧。

3. 通过实际操作,加深对数字电路基础知识的理解。

二、实验器材1. 实验箱2. 加法器芯片(如741)3. 逻辑分析仪4. 万用表5. 连接线6. 电源三、实验原理加法器是一种基本的数字电路,用于实现两个或多个数字的加法运算。

本实验以半加器和全加器为基础,通过级联实现多位数的加法运算。

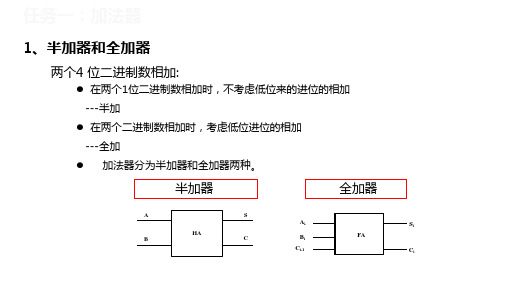

1. 半加器:完成两个一位二进制数相加,并产生和与进位。

2. 全加器:在半加器的基础上增加一个进位输入端,实现多位数的加法运算。

四、实验步骤1. 搭建电路:- 将加法器芯片插入实验箱的相应位置。

- 根据实验要求,连接输入端、输出端和电源。

- 使用逻辑分析仪观察输入信号和输出信号。

2. 半加器测试:- 将两个一位二进制数输入到半加器的两个输入端。

- 观察逻辑分析仪的输出,验证半加器的功能。

3. 全加器测试:- 将两个一位二进制数和一个进位信号输入到全加器的三个输入端。

- 观察逻辑分析仪的输出,验证全加器的功能。

4. 多位数加法测试:- 将多位二进制数输入到全加器的相应输入端。

- 观察逻辑分析仪的输出,验证多位数的加法运算。

5. 实验结果分析:- 对比理论计算结果和实验结果,分析实验误差原因。

五、实验结果与分析1. 半加器测试:- 输入:A=0, B=0- 输出:和=0,进位=0- 输入:A=1, B=0- 输出:和=1,进位=0- 输入:A=0, B=1- 输出:和=1,进位=0- 输入:A=1, B=1- 输出:和=0,进位=12. 全加器测试:- 输入:A=0, B=0, 进位=0- 输出:和=0,进位=0- 输入:A=1, B=0, 进位=0- 输出:和=1,进位=0- 输入:A=0, B=1, 进位=0- 输出:和=1,进位=0- 输入:A=1, B=1, 进位=0- 输出:和=0,进位=13. 多位数加法测试:- 输入:A=1010,B=1101,进位=0- 输出:和=10111,进位=1实验结果表明,加法器能够实现预期的功能,实验结果与理论计算基本一致。

加法器实验总结

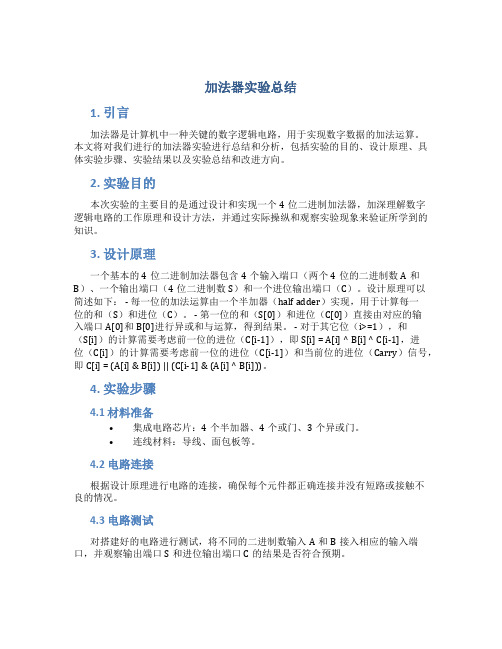

加法器实验总结1. 引言加法器是计算机中一种关键的数字逻辑电路,用于实现数字数据的加法运算。

本文将对我们进行的加法器实验进行总结和分析,包括实验的目的、设计原理、具体实验步骤、实验结果以及实验总结和改进方向。

2. 实验目的本次实验的主要目的是通过设计和实现一个4位二进制加法器,加深理解数字逻辑电路的工作原理和设计方法,并通过实际操纵和观察实验现象来验证所学到的知识。

3. 设计原理一个基本的4位二进制加法器包含4个输入端口(两个4位的二进制数A和B)、一个输出端口(4位二进制数S)和一个进位输出端口(C)。

设计原理可以简述如下: - 每一位的加法运算由一个半加器(half adder)实现,用于计算每一位的和(S)和进位(C)。

- 第一位的和(S[0])和进位(C[0])直接由对应的输入端口A[0]和B[0]进行异或和与运算,得到结果。

- 对于其它位(i>=1),和(S[i])的计算需要考虑前一位的进位(C[i-1]),即S[i] = A[i] ^ B[i] ^ C[i-1],进位(C[i])的计算需要考虑前一位的进位(C[i-1])和当前位的进位(Carry)信号,即C[i] = (A[i] & B[i]) || (C[i-1] & (A[i] ^ B[i]))。

4. 实验步骤4.1 材料准备•集成电路芯片:4个半加器、4个或门、3个异或门。

•连线材料:导线、面包板等。

4.2 电路连接根据设计原理进行电路的连接,确保每个元件都正确连接并没有短路或接触不良的情况。

4.3 电路测试对搭建好的电路进行测试,将不同的二进制数输入A和B接入相应的输入端口,并观察输出端口S和进位输出端口C的结果是否符合预期。

5. 实验结果根据我们的实验步骤,我们成功完成了一个4位二进制加法器的设计和实现。

通过输入不同的二进制数A和B,我们观察到输出端口S和进位输出端口C都能正确地计算出4位二进制数的和。

8bit 符号数加法器

8bit符号数加法器一、概述8bit符号数加法器是一种用于实现两个8位二进制数相加的硬件或软件设备。

在数字电路和计算机编程中,这种加法器对于各种应用和计算任务非常有用。

二、设计原理符号数加法器基于二进制数的加法原理进行设计。

当两个二进制数相加时,我们需要考虑的是每一位上的数值相加的结果,以及最高位的进位问题。

对于负数,我们还需要考虑到符号位的问题。

为了处理这些情况,符号数加法器设计为可以识别输入数字的符号,并根据不同的符号采取不同的加法策略。

三、硬件实现8bit符号数加法器的硬件实现方法多种多样,具体实现方式取决于所使用的硬件平台和设计要求。

常见的实现方式包括微处理器、FPGA(现场可编程门阵列)以及其他数字逻辑设备。

微处理器通常具有专门的硬件模块或软件算法来实现加法运算,而FPGA则允许根据需要进行自定义设计。

在FPGA实现中,可以使用计数器或寄存器来存储输入数字的数值位,以及查找表来存储输入数字的符号位。

此外,可能需要使用额外的逻辑和寄存器来处理溢出和下溢情况。

四、软件实现8bit符号数加法器的软件实现方法也很多样化,具体实现方式取决于所使用的编程语言和设计要求。

常见的编程语言如Python、C++、Java等都可以方便地实现这个功能。

在软件实现中,可以通过编写程序代码来实现8bit符号数加法器的功能,并进行相应的测试和验证。

五、应用场景8bit符号数加法器可以应用于各种数字系统和计算机编程模型中,例如数字信号处理、嵌入式系统、游戏开发、人工智能等。

它提供了高效、可靠的数字运算功能,对于这些应用中的计算任务至关重要。

除此之外,它还可以用于数据校验、加密解密、科学计算等领域。

六、总结8bit符号数加法器是一种重要的数字电路组件,它能够将两个8位的二进制数相加,并对负数的符号进行特殊处理。

通过不同的硬件和软件实现方法,我们可以方便地设计和使用这个加法器。

它的应用范围广泛,为各种数字系统和计算任务提供了有力的支持。

加法器

Y(A<B)

Y(A=B)

B

B AB

Y(A>B)

(二) 多位数值比较器 可利用 1 位数值比较器构成

比较原理:从最高位开始逐步向低位进行比较。

例 比较 A = A3A2A1A0 和 B = B3B2B1B0 的大小:

若 A3 > B3,则 A > B;若 A3 < B3,则 A < B; 若 A3 = B3,则需比较次高位。 若次高位 A2 > B2,则 A > B;若 A2 < B2,则 A < B; 若 A2 = B2,则再去比较更低位。 依次类推,直至最低位比较结束。

四位数字比较器功能表

A3B3

A2B2 A1B1 A0B0

IA>B

IA<B

IA=B

A3>B3 ×

×

A3<B3 ×

×

A3=B3 A2>B2 ×

A3=B3 A2<B2 ×

A3=B3 A2=B2 A1>B1

A3=B3 A2=B2 A1<B1

A3=B3 A2=B2 A1=B1

A3=B3 A2=B2 A1=B1

YA<B YA>B YA=B

两片CC14585组成8位数值比较器

பைடு நூலகம்

6.7 组合逻辑电路中的竞争冒险

一、竞争冒险现象及其危害

当信号通过导线和门电路时,将产生时间延迟。 因此,同一个门的一组输入信号,由于它们在此前通 过不同数目的门,经过不同长度导线的传输,到达门 输入端的时间会有先有后,这种现象称为竞争。

逻辑门因输入端的竞争而导致输出产生不应有的尖峰 干扰脉冲的现象,称为冒险。

可能导致错误动作

二、竞争冒险的产生原因及消除方法

负尖峰脉冲冒险举例

第2章 加法器

3.5 定点运算器的组成 1)定点运算器的基本结构 • 不同的计算机其运算器的组成结构是不同的, 但一般都包含以下几部分。 1.算术逻辑运算单元ALU • 在计算机中,通常具体实现算术运算和逻辑 运算的部件称为算术逻辑运算单元 (Arithmetic and Logic Unit),简称ALU, 它是加法器、乘法器和逻辑运算器的集成, 是运算器的核心。ALU通常表示为两个输入 端,一个输出端和多个功能控制信号端的一 个逻辑符号。加法器是ALU的核心,是决定 ALU运算速度的主要因素。

第2 章 加法器

• 计算机要对各种信息进行加工和处理。 • 如对数值数据进行加、减、乘、除的数 值运算,对非数值数据进行与、或、非 的逻辑运算。 • 在计算机中必须有对数据进行处理的部 件,这个部件就是运算器。 • 目前,大多数计算机都将运算器和控制 器集成在一个芯片上,也就是我们常说 的CPU。

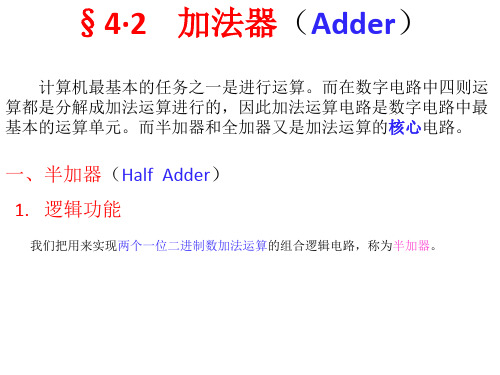

二进制加法器 1.半加器 • 两个一位二进制数相加(不考虑低位的进 位),称为半加。实现半加操作的电路称 为半加器。 • 半加器的真值表、逻辑图和逻辑符号。 2.全加器 • 在实现多位二进制数相加时,不仅考虑本 位,还要考虑低位来的进位,这种考虑低 位的进位加法运算就是全加运算, • 实现全加运算的电路称为全加器。

A8 A7A6A5 B8B7B6B5

A4 A3A2A1B4B3B2B1

16位行波进位加法器

• 在这种结构中,由于组间进位C4、C8、 C12、C16仍然是串行产生的,最高进位 的产生时间为4×(2.5ty)=10ty。 • 采用这种结构,在大大地缩短了进位延迟 时间的同时兼顾了电路设计的复杂性。 • 如果还需要进一步提高速度,可以采用两 级先行进位结构。

• 4)附加的控制线路 运算器要求运算速度快,运算精度高。为 了达到这一目的,通常还在运算器中附加 一些控制线路。 i -i • 如:运算器中的乘2 或乘2 运算和某些逻 辑运算是通过移位操作来实现的。这通常 是在ALU的输出端设置移位线路来实现。 移位包括左移,右移和直送。移位线路也 是一个多路选择器。 • 定点运算器的组成

9、加法器有哪些,如何使用

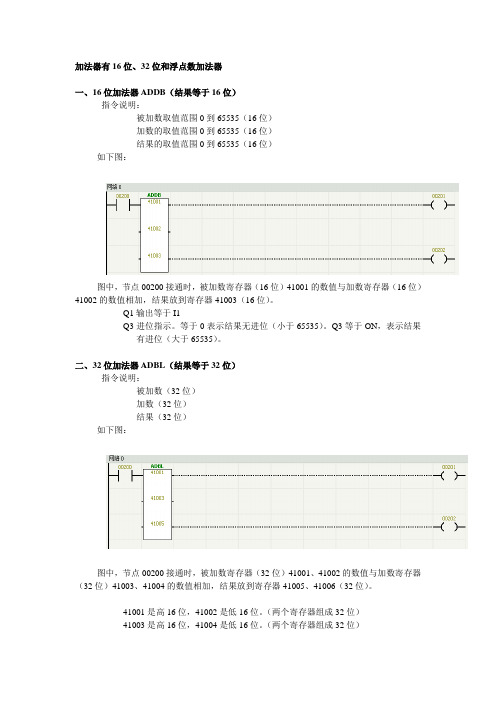

加法器有16位、32位和浮点数加法器一、16位加法器ADDB(结果等于16位)指令说明:被加数取值范围0到65535(16位)加数的取值范围0到65535(16位)结果的取值范围0到65535(16位)如下图:图中,节点00200接通时,被加数寄存器(16位)41001的数值与加数寄存器(16位)41002的数值相加,结果放到寄存器41003(16位)。

Q1输出等于I1Q3进位指示。

等于0表示结果无进位(小于65535)。

Q3等于ON,表示结果有进位(大于65535)。

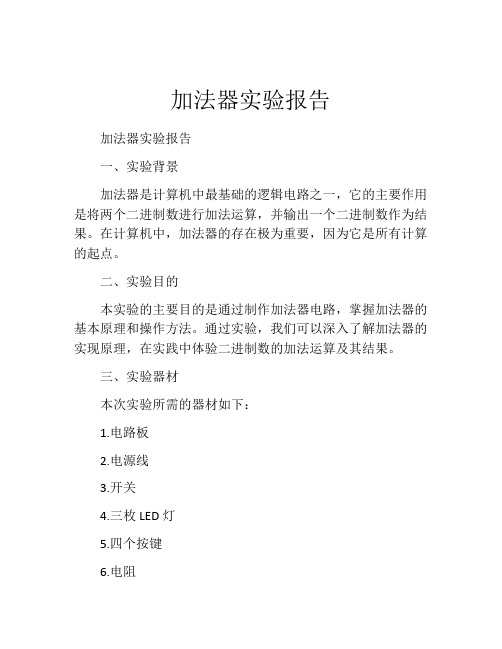

二、32位加法器ADBL(结果等于32位)指令说明:被加数(32位)加数(32位)结果(32位)如下图:图中,节点00200接通时,被加数寄存器(32位)41001、41002的数值与加数寄存器(32位)41003、41004的数值相加,结果放到寄存器41005、41006(32位)。

41001是高16位,41002是低16位。

(两个寄存器组成32位)41003是高16位,41004是低16位。

(两个寄存器组成32位)41005是高16位,41006是低16位。

(两个寄存器组成32位)Q3进位指示。

三、浮点加法器FADD(结果等于浮点数)指令说明:被加数是浮点数(32位)加数是浮点数(32位)结果是浮点数(32位)如下图:图中,节点00200接通时,被加数寄存器(浮点数)41001、41002的数值与加数寄存器(浮点数)41003、41004的数值相加,结果放到寄存器41005、41006(浮点数)。

41001和41002两个寄存器组成浮点数41003和41004两个寄存器组成浮点数41005和41006两个寄存器组成浮点数Q1等于I1。

加法器实验报告

加法器实验报告加法器实验报告一、实验背景加法器是计算机中最基础的逻辑电路之一,它的主要作用是将两个二进制数进行加法运算,并输出一个二进制数作为结果。

在计算机中,加法器的存在极为重要,因为它是所有计算的起点。

二、实验目的本实验的主要目的是通过制作加法器电路,掌握加法器的基本原理和操作方法。

通过实验,我们可以深入了解加法器的实现原理,在实践中体验二进制数的加法运算及其结果。

三、实验器材本次实验所需的器材如下:1.电路板2.电源线3.开关4.三枚LED灯5.四个按键6.电阻7.逻辑门SN74008.引线等四、实验步骤1.将电路板和电源线取出并清洗干净。

2.将电阻固定在电路板上。

3.将逻辑门SN7400安装到电路板上,并连接引线。

4.安装开关、LED灯和按键。

5.进行电路连接,注意避免短路和错接。

6.检查出错情况,重新调整电路连接。

7.开启电源并进行测试。

五、实验结果经过多次调整,我们成功地制作出了加法器电路,并进行了测试。

实验的结果显示:当我们同时按下两个按键时,相应的LED灯会点亮,从而输出结果。

六、实验误差及分析在实验过程中,我们发现有时LED灯不能很好地显示结果,这可能是由于电路连接不良或电阻的阻值不准确造成的。

在检查出错情况时,我们需要细心认真,尤其是对于电路连接的质量非常重要。

七、实验心得通过本次实验,我们深入了解了加法器的基本原理和操作方法。

同时,我们也掌握了电路连接和调试的技巧,认识到了实验中心细节的重要性。

通过实践,我们加深了对计算机逻辑电路的理解和应用,也提升了我们的创新能力和动手实践能力。

总之,本次实验让我们得到了很大的收获,不仅增强了我们对计算机逻辑电路的认识,也提高了我们的实验技能和科学素质。

我们相信,在今后的学习和实践中,这次实验的经验和教训将对我们有很大的帮助。

组合逻辑电路—加法器(电子技术课件)

例. 用74283构成将8421BCD码转换为余3码的码制转换电路 。

8421码

0000 0001 0010

+0011 +0011 +0011

余3码

0011 0100 0101

8421码输入 0011

A3 A2 A1 A0 B3 B2 B1 B0

CCO

O

S3

74283 S2 S1 S0

C–1 0

余3码输出

A B Ci Co AB + ABCi + ABCi

AB + (A B)Ci

A

A B A B Ci S

B

AB CO

CO ( A B)Ci

Ci

≥1 Co

A S B Ci C I C O CO

任务一:加法器

加法器的应用

全加器真值表

AB C SC 0 0 00 0 0 0 11 0 0 1 01 0 0 1 101 1 0 01 0 1 0 10 1 1 1 00 1 1 1 11 1

➢ 不考虑低位进位,将两个1位二进制数A、B相加的器件。

• 半加器的真值表 • 逻辑表达式

S AB+ AB C = AB

如用与非门实现最少要几个门?

A

半加器的真值表

=1

S

A

B

BA

B

S

C

0000

1010

& C=AB

0110

1101

• 逻辑图

任务一:加法器

(2) 全加器(Full Adder)

全加器能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出

余 3 码输出

A3 B3 A2 B2 A1 B1 A0 B0

加法器(Adder) 数电课件

2. 分析

半加器有两个输入:加数 、被加数Ai ;两个输出:B和i 输出 、进位输出 。

Si

Ci

3. 真值表

半加器的真值表如表4.2.1—1所示。

表4.2.1—1

4. 逻辑函数表达式

半加器的逻辑函数表达式为

Si Ai Bi Ai Bi Ai Bi Ci Ai Bi

5. 逻辑电路图

定

。

An1 An、2 L A2 A1 A0 Cn1Cn2 L C2C1C0

B和n1Bn给2出L,B便2可B1以B直0 接C确01

方法二

C0 P0C01 G0

C1 P1C0 G1

P1 P0C01 G0 G1

C2 P2C1 G2

P2 P1 P0C01 G0 G1 G2

图4.2.5—3 Ⅰ. 加减控制输入为0时,该电路实现加法运算; Ⅱ. 加减控制输入为1时,该电路实现减法运算(补码加法)。

返回

半加器的逻辑函数表达式为

Si Ai Bi Ai Bi Ai Bi Ci Ai Bi

5. 逻辑电路图

半加器的逻辑电路图如图4.2.1—1所示。

(公式4.2.1) (公式4.2.2)

图4.2.1—1

6. 逻辑符号

半加器的逻辑符号如图4.2.1—2所示。

图4.2.1—2

二、全加器(Full Adder)

依次递推可知,只要

定

。

An1 An、2 L A2 A1 A0 Cn1Cn2 L C2C1C0

B和n1Bn给2出L,B便2可B1以B直0 接C确01

四位超前进位加法器的逻辑电路图如图4.2.3—2所示。 图4.2.3—2

四、中规模集成加法器

加法器

加法器一、什么是加法器加法器是为了实现加法的。

即是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

对于1位的二进制加法,相关的有五个的量:1,被加数A,2,被加数B,3,前一位的进位CIN,4,此位二数相加的和S,5,此位二数相加产生的进位COUT。

前三个量为输入量,后两个量为输出量,五个量均为1位。

对于32位的二进制加法,相关的也有五个量:1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。

这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。

而最后的第32位必须在前31位全部计算出结果后,才能开始计算。

这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

基本方法可以看出,上法是将32位的加法1位1位串行进行的,要缩短进行的时间,就应设法使上叙进行过程并行化。

类型以单位元的加法器来说,有两种基本的类型:半加器和全加器。

半加器有两个输入和两个输出,输入可以标识为 A、B 或 X、Y,输出通常标识为合 S 和进制 C。

A 和 B 经 XOR 运算后即为 S,经 AND 运算后即为 C。

全加器引入了进制值的输入,以计算较大的数。

为区分全加器的两个进制线,在输入端的记作 Ci 或 Cin,在输出端的则记作 Co 或 Cout。

半加器简写为 H.A.,全加器简写为 F.A.。

半加器:半加器的电路图半加器有两个二进制的输入,其将输入的值相加,并输出结果到和(Sum)和进制(Carry)。

加法器电路原理

加法器电路原理加法器电路是数字电子技术中常见的一种电路,它可以将多个输入信号相加,并输出它们的和。

在数字系统中,加法器电路是非常基础且重要的一部分,它广泛应用于计算机、通信系统、数字信号处理等领域。

本文将介绍加法器电路的原理及其实现方法。

加法器电路的原理基于二进制加法运算。

在二进制系统中,加法器电路可以将两个二进制数相加得到它们的和,并且可以处理进位的情况。

在实际的数字电路中,加法器电路通常由多个逻辑门组成,包括与门、或门、异或门等。

通过这些逻辑门的组合,可以实现不同位数的加法运算。

一般来说,加法器电路可以分为半加器和全加器两种。

半加器用于处理两个单独位的加法运算,它可以得到两个输入位的和以及进位输出。

而全加器则可以处理三个输入位的加法运算,包括两个输入位和一个来自上一位的进位,它可以得到三个输入位的和以及进位输出。

通过多个全加器的级联,可以实现多位数的加法运算。

在实际的电路设计中,加法器电路的实现方式多种多样。

最常见的是采用逻辑门的组合来实现加法器电路,例如使用异或门来实现不带进位的加法运算,再结合与门来处理进位的情况。

此外,还可以使用集成电路芯片或者可编程逻辑器件来实现加法器电路,这样可以提高电路的集成度和性能。

除了基本的加法器电路外,还可以通过增加控制信号或者引入特定的逻辑结构来实现更复杂的加法器电路。

例如,可以设计带有溢出检测功能的加法器电路,以便在加法运算溢出时给出相应的标志信号。

此外,还可以设计带有输入输出端口的加法器电路,以实现与其他模块的接口和数据交换。

总之,加法器电路是数字电子技术中非常重要的一部分,它可以实现数字系统中的加法运算,并且具有广泛的应用。

通过深入理解加法器电路的原理及其实现方法,可以更好地应用它们于实际的数字系统中,从而提高系统的性能和可靠性。

希望本文能够对读者对加法器电路有所帮助,并且能够在实际应用中发挥作用。

数字电子技术-加法器

• 74LS283电路是一个四位加法器电路,可实现两个四位二进制 数的你相加,其逻辑符号如图2-23所示。

CO是向高位的进位

S3、S2、S1、S0是对应各位的和 CI是低位的进位

A3A2A1A0和B3B2B1B0是两个二进制待加

加法器

2.3 加法器(Accumulator)

算术运算是数字系统的基本功能,更是计算机中不可缺少的 组成单元。

本节介绍实现加法运算的逻辑电路。

完成加法运算的逻辑器件称为加法器。 加法器分为半加器和全加器。

2

2.3.1 全加器

在第1章中,我们讨论了半加运算电路

该电路实现两个一位二进制数相加的功能。S是它们的本位和,C是向高位的进位。 由于这一加法器电路没有考虑低位的进位,所以称该电路为半加器。

输 输出 入

AB SC

00 00 01 10 10 10 11 01

半加器的逻辑符号

在第1章中,我们还讨论了全加运算电路。

电路实现全加器FA(Full

全加器的逻辑符号

输入

AnBnCn-1

000 001 010 011 100 101 110 111

输出 Sn Cn

00 10 10 01 10 01 01 11

Adder)的逻辑功能。输入An 和Bn为一位二进制数,Cn-1 为低位的进位,输出Sn为本 位和,Cn为本位的进位。全

加器能把本位两个一位二进 制加数和来自低位的进位三 者相加,得到求和结果和该 位的进位信号。

由多个全加器,可构成多位加法运算电路。

2.3 加法器(Accumulator)

2.3.2 多位加法器

4.3 加法器解析

功能:实现两个四位二进制数相加。 特点:电路结构简单,但运算速度慢。

2.超前进位加法器

第四章 组合逻辑电路

通过逻辑电路事先得出每一位全加器的进位输入信号。 C3

超前进位电路

A3 B3 A2 B2 A1 B1 A0 B0 C0-1

CI

Σ

S3 S2 S1 S0

CI Σ

Σ CI

CI Σ

超前进位电路图

特点:运算速度快,电路比较复杂。

S i Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1

( Ai Bi )Ci 1 ( Ai Bi )Ci 1 Ai Bi Ci 1

Ci Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1

第四章 组合逻辑电路

4.3 加法器

• 定义

能够实现二进制加法运算的逻辑电路称为加法器。

• 分类

加法器 一位加法器

多位加法器

半加器 全加器

第四章 组合逻辑电路

4.3.1 半加器和全加器

• 定义 半加器:只能进行本位加数、被加数的加法运算 而不考虑相邻低位进位的逻辑部件。 全加器:能同时进行本位加数、被加数和相邻 低位的进位信号的加法运算的逻辑部件。

4.多位加法器的应用举例

例4.3.1 设计一个代码转换电路,将8421BCD码转换为 余3码,用74HC283实现。 解: (1) 依据逻辑功能,确定输入、输出变量 输入变量:8421BCD码DCBA 输出变量:余3码Y3Y2Y1Y0

第四章 组合逻辑电路

(2)真值表

例4.3.1的逻辑真值表 输入8421BCD码 输出余3码

Ai Bi ( Ai Bi )Ci-1

逻辑电路中加法器的概念

逻辑电路中加法器的概念逻辑电路中的加法器是一种将两个二进制数相加的电路。

它被广泛应用于计算机、数字信号处理和通信系统等领域。

在计算机中,加法器用于执行整数运算,并且是所有算术操作的基础。

因此,对于理解和设计逻辑电路来说,加法器的概念至关重要。

加法器的基本原理是将两个二进制数的对应位相加,并得到相应的和与进位。

在加法器中,输入位称为"被加数"和"加数",输出位称为"和"和"进位"。

加法器可以分为半加器和全加器两种类型。

半加器只能处理一位的二进制加法,而全加器可以处理两位的二进制加法。

半加器的原理很简单,它有两个输入位(被加数和加数)和两个输出位(和和进位)。

和的输出位等于两个输入位的异或运算结果,进位的输出位等于两个输入位的与运算结果。

全加器是由两个半加器和一个或门组成的。

它有三个输入位(被加数、加数和进位)和两个输出位(和和进位)。

和的输出位等于三个输入位的异或运算结果,进位的输出位等于三个输入位的与运算结果与进位输入位的异或运算结果进行或运算得到的值。

在实际应用中,为了进行更高位数的加法运算,可以将多个全加器连接起来形成级联的加法器。

这种级联的加法器称为Ripple Carry Adder(串行进位加法器)。

其中,每个全加器的进位输入位是上一个全加器的进位输出位,从而实现了加法器的级联操作。

此外,为了提高计算速度和减少器件的数量,还可以使用并行进位加法器(Carry Lookahead Adder)或进位选择加法器(Carry Select Adder)。

这些高级加法器利用了更复杂的电路结构来预先计算出进位,从而减少了级联操作所需的时间。

总的来说,加法器是逻辑电路中的一种基本组件,用于将两个二进制数相加。

它可以使用半加器、全加器或其它高级加法器来实现。

加法器的设计取决于所需的位数和性能要求。

在计算机和数字电路中,加法器是执行算术操作和实现数字逻辑功能的重要组成部分。

三种加法器——精选推荐

三种加法器加法器在微机中是十分重要的,加法器是产生数的和的装置。

加数和被加数为输入,和数与进位为输出的装置为半加器。

若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。

常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

在电子学中,加法器是一种数位电路,其可进行数字的加法计算。

在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。

加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。

由于负数可用二的补数来表示,所以加减器也就不那么必要。

加法器有很多种,下面选择其中的三个进行比较:半加器、逐位进位加法器、超前进位加法器。

半加器不考虑由低位来的进位,只有本位两个数相加,称为半加器。

图1(a)为半加器的方框图。

其中:A、B分别为被加数与加数,作为电路的输入端;S为两数相加产生的本位和,它和两数相加产生的向高位的进位C一起作为电路的输出。

图1 半加器框图、逻辑图和符号根据二进制数相加的原则,得到半加器的真值表如表1所列。

表1 半加器的真值表由真值表可分别写出和数S,进位数C的逻辑函数表达式为:(1)C=AB (2)由此可见,式(1)是一个异或逻辑关系,可用一个异或门来实现;式(2)可用一个与门实现。

其逻辑电路如图1(b)所示。

逐位进位加法器逐位进位加法器的结构:a)四个求和输入端(2、3、4、5),用于接收有效性为w的要进行求和的四个输入比特(A、B、C、N);b)三个进位输入端(6、7、8),用于接收有效性为w的三个输入进位比特(C0IN、C1IN、C2IN);c)总和输出端,用于输出有效性为w的输出总和比特(S);d)三个进位输出端(10、11、12),用于输出有效性为2w的三个输出进位比特(C0OUT、C1OUT、C2OUT)。

它的优点是电路比较简单,但也有它的缺点:加法运算是逐位进行的,每一位的加法运算必须等低位送来进位之后才能进行,运算速度较慢。

超前进位加法器超前进位加法器的思想:三步运算,1,由输入的A,B算出每一位的G,P;2,由各位的G,P算出每一位的GN:0,PN:0;3,由每一位的GN:0,PN:0与CIN算出每一位的COUT,S。

课件:加法器结构

用传输门实现全加器

S (AB)C (A B)C CO (A B)C (AB)A

只有20个MOSFET构成!

A B

VDD A

B

Y

AB AB

AB

15

全加器

AB

Cin

Full adder

Cout

Sum

16

多位二进制加法器

两个n位二进 制数据与进位 输入信号进行 加法运算,产 生1个n位的加 法和与一个进 位输出信号

第五章 数字集成电路基本模块

5.2 加法器

1

IN PU T -OU T PU T

计算机组成

MEM ORY

C ON T RO L

D AT AP A TH

运算器 控制器、运算器、存储器、输入输出接口 运算器:也称为算术逻辑单元(ALU),负责指令执行 运算器由加法器、移位器、逻辑模块等组成,加法器是

ci aibici1 aibici1 aibi gi pici1

ci1 gi1 pi1ci gi1 pi1(gi pici1) gi1 pi1gi pi1 pici1

ci 2 gi 2 pi 2ci 1 gi 2 pi 2(gi 1 pi 1(gi pici 1)) gi 2 pi 2gi 1 pi 2pi 1gi pi 2pi 1pici 1

当Gi=1时不管低位的 进位是什么值,本位 的进位输出都是“1”; 当Pi=1时则把低位的 进位输出Ci-1直接作为 本位的进位输出传送 下去。

24

Generate (G) = AB

Propagate (P) = A⊕B

行波进位加法器-串行进位链

Sn

求和 逻辑

Si

求和 逻辑

S1

数字逻辑课件——加法器

综上所述,接法如图3-3-23(b)所示。与方法1比 较,多用了一个与非门,却省去两个“四选一” 选择器。“选择输入”端A1,A0,可接C,D, 也可接A,B或A,C或B,D或A,D或B,C, 相应的卡诺图略加变动,所得的D0,D1, D2, D3的表达式各不相同。经过各种方案的比较, 可得最佳的简化结构。

例3-6 用74153实现逻辑函数Z F (A, B) m(1, 3)

解:由最小项表达式得该函数的真值表,如表 3-3-12所示,用半片74153即可实现该逻辑函数, 接法如图3-3-20。

输入变量A,B分别送选择输入端A1,A0选通输 入,ST 应接0,数据输入D0,D1,D2,D3根据 真值表分别接0,1,0,1。这样,74153的输 出端Y 即逻辑函数Z。

逻辑图可以看出,数据输出Y 的逻辑表达 式为

Y ST[D0 ( A1 A0 ) D1( A1 A0 ) D2 ( A1 A0 ) D3 ( A1 A0 )]

即当选通输入 ST 0 时,若将选择输入A1,

A0分别为00,01,10,11则相应地把D0,D1,

D2,D3送到数据输出端Y去, 当

图3-3-21 例3-7图

25

①B当C BC =00时,Z = D0 ;由卡诺图可见,Z 此时 不②不A管管当01 AAB0000等 等C 于 于=01110001或 或时111011,, ,Z1ZZ001 =都都D等等1 于于;01由,,卡因因B0C 诺此此图以以S可AAT0110 输 输见D012入 入,7DY411DD此53D012。 。时D3

从图3-3-22可以发现,下层的片0和片3, 输出分别恒为0和1,故可省去片0和片3, 同时,片4的D0和D3分别改接0和1。因此, 在用74153实现逻辑函数时,必须根据具 体情况考虑简化结构的可能性。

加法器工作原理

加法器工作原理

加法器是计算机中常见的一种算术逻辑单元,用于实现对数字的加法运算。

加法器通常由多个位级别的二进制加法器组成。

其工作原理是将输入的二进制数按位进行加法运算,并将运算结果输出。

每个位级别加法器有两个输入引脚,分别为A和B,一个输出引脚S和一个进位引脚C。

当两个二进制数第i位上的数分别为Ai和Bi时,第i位级别加法器的输出Si和进位Ci的计算方式为:

Si = Ai ⊕ Bi,其中⊕ 表示异或运算

Ci+1 = Ai · Bi + Ai · Ci + Bi · Ci,其中· 表示与运算其中Ci作为进位引脚的输入,也作为下一位级别加法器的进位引脚的输出。

最高位级别加法器的进位引脚可以直接被设置为0。

加法器是计算机中最基本的算术逻辑单元之一,广泛应用于CPU、内存以及其他数字电路中。

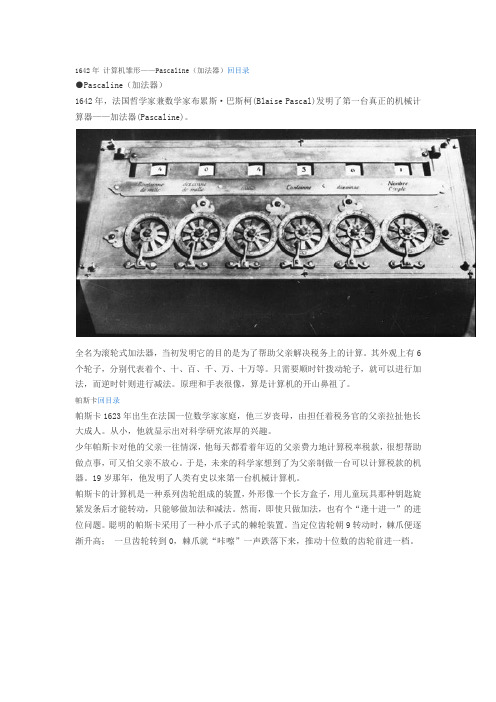

1642年 计算机雏形——Pascaline(加法器)

1642年计算机雏形——Pascaline(加法器)回目录●Pascaline(加法器)1642年,法国哲学家兼数学家布累斯·巴斯柯(Blaise Pascal)发明了第一台真正的机械计算器——加法器(Pascaline)。

全名为滚轮式加法器,当初发明它的目的是为了帮助父亲解决税务上的计算。

其外观上有6个轮子,分别代表着个、十、百、千、万、十万等。

只需要顺时针拨动轮子,就可以进行加法,而逆时针则进行减法。

原理和手表很像,算是计算机的开山鼻祖了。

帕斯卡回目录帕斯卡1623年出生在法国一位数学家家庭,他三岁丧母,由担任着税务官的父亲拉扯他长大成人。

从小,他就显示出对科学研究浓厚的兴趣。

少年帕斯卡对他的父亲一往情深,他每天都看着年迈的父亲费力地计算税率税款,很想帮助做点事,可又怕父亲不放心。

于是,未来的科学家想到了为父亲制做一台可以计算税款的机器。

19岁那年,他发明了人类有史以来第一台机械计算机。

帕斯卡的计算机是一种系列齿轮组成的装置,外形像一个长方盒子,用儿童玩具那种钥匙旋紧发条后才能转动,只能够做加法和减法。

然而,即使只做加法,也有个“逢十进一”的进位问题。

聪明的帕斯卡采用了一种小爪子式的棘轮装置。

当定位齿轮朝9转动时,棘爪便逐渐升高;•一旦齿轮转到0,棘爪就“咔嚓”一声跌落下来,推动十位数的齿轮前进一档。

Pascaline calculating machine of Blaise Pascal (1623-62),帕斯卡发明成功后,一连制作了50台这种被人称为“帕斯卡加法器”的计算机,至少现在还有5台保存着。

•比如,在法国巴黎工艺学校、英国伦敦科学博物馆都可以看到帕斯卡计算机原型。

据说在中国的故宫博物院,也保存着两台铜制的复制品,是当年外国人送给慈僖太后的礼品,“老佛爷”哪里懂得它的奥妙,只把它当成了西方的洋玩具,藏在深宫里面。

帕斯卡是真正的天才,他在诸多领域内都有建树。

后人在介绍他时,说他是数学家、物理学家、哲学家、流体动力学家和概率论的创始人。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL语言实验报告

实验名称:加法器

姓名:王标标

学号:100405250

班级:电气二班

实验时间:2010.10.29

南京理工大学紫金学院电光系

一、实验目的

1、采用自顶向下的方法设计4位加法器。

2、学习使用VHDL语言进行电路设计。

二、实验原理

4位全加器工作原理:4位串行进位并行加法器由4个一位全加器构成,而一位全加器可以由两个半加器和一个2输入端或门组成

三、实验内容

1·用VHDL语言描述半加器

2·用VHDL语言描述全加器

3·用VHDL语言描述四位全加器

4·半加器仿真结果与电路图

5·全加器仿真结果与电路图

6·四位全加器仿真结果与电路图

四、小结与体会

本次实验使我学会的如何使用Quartus II软件和试验箱。

掌握软件使用过程中工程建立、原理图输入方法、编译、仿真、管教配置等,学会了采用自顶向下的方法设计4位加法器。

熟悉了使用VHDL语言进行电路设计。