PCIE---论坛

EC3-1816CLD2NA-中英文说明书-C00-2413-023681

EVOC产品 请注意下列说明:

警告 EVOC产品只允许用于目录和相关技术文件中规定的使用情况。如果要使用其他 公司的产品和组件,必须得到EVOC推荐和允许。正确的运输、储存、组装、装 配、安装、调试、操作和维护是产品安全、正常运行的前提。必须保证允许的环 境条件。必须注意相关文件中的提示。

危险 表示如果不采取相应的小心措施,将会导致死亡或者严重的人身伤害。

警告 表示如果不采取相应的小心措施,可能导致死亡或者严重的人身伤害。

小心 带有警告三角,表示如果不采取相应的小心措施,可能导致轻微的人身伤害。

注意 表示如果不注意相应的提示,可能会出现不希望的结果或状态。

合格的专业人员 本文件所属的产品/系统只允许由符合各项工作要求的合格人员进行操作。

约定 在本文档中,术语“本板”或“产品”有时特指EVOC EC3-1816CLD2NA产品。

说明 安全相关注意事项 为避免财产损失以及出于个人安全方面的原因,请注意本入门指南中关于安 全方面的信息。 文中使用警告三角来指示这些安全信息,警告三角的出现 取决于潜在危险的程度。

目录 1. 产品介绍 .................................................................................................................1

1.1 简介 .................................................................................................... 1

EC20_Mini_PCIe(Audio版本)_硬件设计手册_V1.0

1 引言 ........................................................................................................................................................ 7 1.1. 安全须知..................................................................................................................................... 7

adm-pcie-7v3 user manual

ADM-PCIE-7V3 User ManualDocument Revision: 1.43rd June 2016ADM-PCIE-7V3 User ManualV1.4 - 3rd June 2016© 2016 Copyright Alpha Data Parallel Systems Ltd.All rights reserved.This publication is protected by Copyright Law, with all rights reserved. No part of this publication may be reproduced, in any shape or form, without prior written consent from AlphaData Parallel Systems Ltd.Head OfficeAddress: 4 West Silvermills Lane,Edinburgh, EH3 5BD, UK Telephone:+44 131 558 2600Fax:+44 131 558 2700 email:sales@ website: US Office3507 Ringsby Court Suite 105, Denver, CO 80216(303) 954 8768(866) 820 9956 toll freesales@All trademarks are the property of their respective owners.ADM-PCIE-7V3 User ManualV1.4 - 3rd June 2016Table Of Contents1 Introduction (1)1.1 Key Features (1)1.2 Order Code (1)2 PCB Information (2)2.1 Physical Specifications (2)2.2 Chassis Requirements (2)2.2.1 PCI Express (2)2.2.2 Mechanical Requirements (2)2.2.3 Power Requirements (3)2.2.4 VCC_INT Limits (3)2.3 Thermal Characterization (5)3 Functional Description (6)3.1 Overview (6)3.1.1 Switches (6)3.1.2 LEDs (7)3.2 Clocking (8)3.2.1 PCIe Reference Clocks (8)3.2.2 Fabric Clocks (9)3.2.3 Programming Clock (EMCCLK) (9)3.2.4 Cabled HSSIO (SFP+/SATA) (9)3.2.5 DDR3 SDRAM Reference Clocks (9)3.3 PCI Express (10)3.4 DDR3 SDRAM SODIMMs (10)3.5 SFP+ (11)3.6 SATA (12)3.7 System Monitor (12)3.8 Configuration (13)3.8.1 Configuration From Flash Memory (13)3.8.1.1 Building Configuration Images (14)3.8.2 Configuration via JTAG (14)List of TablesTable 1 Mechanical Dimensions (2)Table 2 Power Supply Enables (3)Table 3 Power OK Pins (3)Table 4 VCC_INT Limits (4)Table 5 SW1 Switch Functions (6)Table 6 LED Details (7)Table 7 PCIe Reference Clocks (8)Table 8 Fabric CLocks (9)Table 9 EMCCLK (9)Table 10 SFP+ and SATA Reference Clocks (9)Table 11 Memory Reference Clocks (9)Table 12 PCI Express Pin Assignments (10)Table 13 SFP+ Control Signals (11)Table 14 SFP+ Transceiver Signals (11)Table 15 SATA Signals (12)Table 16 Flash Configuration Region Selection (13)ADM-PCIE-7V3 User ManualV1.4 - 3rd June 2016List of FiguresFigure 1 ADM-PCIE-7V3 Product Photo (1)Figure 2 FPGA Theta-JA vs LFM (5)Figure 3 ADM-PCIE-7V3 Block Diagram (6)Figure 4 LEDs (7)Figure 5 Clock Topology (8)Figure 6 Flash Address Map (13)ADM-PCIE-7V3 User ManualV1.4 - 3rd June 20161 IntroductionThe ADM-PCIE-7V3 is a high-performance reconfigurable computing card intended for Data Center applications, featuring a Xilinx Virtex-7 FPGA.Figure 1 : ADM-PCIE-7V3 Product Photo1.1 Key FeaturesKey Features•Compatible with Xilinx OpenCL compiler•Supported by ADM-XRC Gen 3 SDK 1.7.0 or later and ADB3 Driver 1.4.15 or later.•PCIe Gen1/2/3 x1/2/4/8 capable•Half-length, low-profile x8 PCIe form factor•Two banks of DDR3 SDRAM SODIMM memory with ECC, rated at 1333MT/s•Two right angle SATA connectors (SATA3 capable)•Two SFP+ sites capable of data rates up to 10 Gbps•FPGA configurable over JTAG and BPI Flash•XC7VX690T-2FFG1157C FPGA•Voltage, current, and temperature monitoring1.2 Order CodeADM-PCIE-7V3/VX690T-2ADM-PCIE-7V3 User ManualV1.4 - 3rd June 2016 2 PCB Information2.1 Physical SpecificationsThe ADM-PCIE-7V3 complies with PCI Express CEM revision 3.0.Table 1 : Mechanical Dimensions2.2 Chassis Requirements2.2.1 PCI ExpressThe ADM-PCIE-7V3 is capable of PCIe Gen 1/2/3 with 1/2/4/8 lanes, using the Xilinx Integrated Block for PCI Express.2.2.2 Mechanical RequirementsAn 8-lane or 16-lane physical PCIe slot is required for mechanical compatibility.Each ADM-PCIE-7V3 is shipped with a full height PCIe card bracket attached. Each shipment also contains a low-profile PCIe card bracket so that users with a low-profile chassis can replace the card bracket in order to suit their chassis.Because most PC chassis do not provide sufficient airflow to cool the FPGA, the ADM-PCIE-7V3 is shipped witha fan on the heatsink. This fan and heatsink assembly consumes part of the adjacent PCIe slot, so the cardsmust have an unpopulated PCIe slot between them.If sufficient airflow is available, the fan can be removed so that the ADM-PCIE-7V3 can be placed immediately adjacent to a populated PCIe slot. This requires that the ADM-PCIE-7V3 is only adjacent to other ADM-PCIE-7V3 cards, and that the system provides sufficient airflow to keep the FPGA of the ADM-PCIE-7V3 below 85 degrees Celsius.ADM-PCIE-7V3 User ManualV1.4 - 3rd June 20162.2.3 Power RequirementsNOTEBy default, SODIMM and SFP power supplies are disabled.The PCIe Specification permits a standard low-profile, half-length PCIe card to dissipate up to 25 W of power, drawn from the PCIe slot. The ADM-PCIE-7V3 may consume more than 25 W of power for worst-case userFPGA designs. Power estimation requires the use of the Xilinx XPE spreadsheet and/or a power estimator tool available from Alpha Data. Please contact support@ to obtain this tool.To save power, certain power supplies that are not required by all FPGA designs are disabled on power-up. To enable these supplies, drive the corresponding enable pin high ('1'):Table 2 : Power Supply EnablesThere are two options to confirm that a power supply has been enabled and is operating properly. First, the user can check illumination of the LED power indicators (see LEDs). Additionally, the state of the Power OK pins at the FPGA can be checked. A logical '1' at the pins in the table below indicates that the supply voltage is operating within tolerance.Table 3 : Power OK PinsWhe using an interface that was initially powered down at startup, logically AND the Power OK signal with the interface reset to ensure that all communication attempts occur after power is stable.NOTEAs a precaution against latchup-type phenomena, do not power down the SFP+ Power Supply if the FPGAdrives any of its pins related to SFP+ functionality. Similarly, do not power down the DDR3 SDRAM SODIMM power supply if the FPGA drives any of its pins related to DDR3 SDRAM functionality.2.2.4 VCC_INT LimitsFor ADM-PCIE-7V3 designs should limit the VCC_INT usage as shown in the table below. If this limit isexceeded the VCC_INT voltage may drop below the FPGA recommended range. While the FPGA may continue to function nominally at higher current draws, this is not recommended. For SN 319 and newer, if the current on VCC_INT reaches 30A the board will power down to protect from damaging onboard components.ADM-PCIE-7V3 User ManualV1.4 - 3rd June 2016ADM-PCIE-7V3 User ManualV1.4 - 3rd June 20162.3 Thermal CharacterizationThe theta junction-to-ambient (Theta-JA) for the FPGA as related to air flow in linear feet per minute (LFM) is specified in the graph below. Use the Xilinx Power Estimator (XPE) to determine the expected power of your FPGA design (/products/design_tools/logic_design/xpe.htm)Figure 2 : FPGA Theta-JA vs LFMADM-PCIE-7V3 User ManualV1.4 - 3rd June 2016 3 Functional Description3.1 OverviewThe ADM-PCIE-7V3 is a versatile reconfigurable computing platform with a Virtex-7 VX690T-2 FPGA, a Gen3x8 PCIe interface, two slots for DDR3-1333 SDRAM SODIMMs (64 bits with 8 bits ECC), two SFP+ cages capable of 10G Ethernet, two SATA3 connectors, and a robust system monitor.Figure 3 : ADM-PCIE-7V3 Block Diagram3.1.1 SwitchesThe ADM-PCIE-7V3 has a quad DIP switch SW1, located on the rear side of the board near the card bracket.The function of each switch in SW1 is detailed below:3.1.2 LEDsThere are 12 LEDs on the ADM-PCIE-7V3, 6 of which are general purpose and whose meaning can be defined by the user. The other five have fixed functions such as power supply status and the configuration status of the FPGA.DONE D1D2D3D4D7D6D5D8D9D1D16D12POK_DRAMPOK_SFPSYS_POKCLOCK_LOSINIT_BUSR_LED0USR_LED1USR_LED2USR_LED5USR_LED4USR_LED3Figure 4 : LEDsFunction ON State OFF StateDONE FPGA is configured FPGA is not configuredUSR_LED0User defined '1' pin AC33User defined '0' pin AC33USR_LED1User defined '1' pin V32User defined '0' pin V32USR_LED2User defined '1' pin V33User defined '0' pin V33USR_LED5User defined '1' pin U30User defined '0' pin U30USR_LED4User defined '1' pin AB32User defined '0' pin AB32USR_LED3User defined '1' pin AB31User defined '0' pin AB31INIT_B Error during configuration No error during configuration POK_SFP SFP+ power supply OK SFP+ power supply OFF or out of rangeSYS_POK All FPGA power rails OK One or more FPGA power rails out ofrangePOK_DRAM SODIMM power supply OK SODIMM power supply OFF or out ofrangeCLOCK_LOS Clocks not operating normally Clocks operating normallyTable 6 : LED Details3.2 ClockingThe ADM-PCIE-7V3 provides reference clocks for the DDR3 SDRAM banks and the I/O interfaces available to the user.Figure 5 : Clock Topology3.2.1 PCIe Reference ClocksThe 8 MGT lanes connected to the PCIe card edge use MGT tiles 117 and 118. There are two clocking options available: (i) the internally generated 100 MHz reference clock with a tight 20 ppm tolerance (REFCLK100M_5), and (ii) the system 100 MHz clock (PCIE_REFCLK1).The other reference clocks (PCIE_REFCLK0 and REFCLK100M_4) are connected to a unused MGT tiles and can be used for fabric clocking.Table 7 : PCIe Reference Clocks3.2.2 Fabric ClocksThe design offers 3 fabric clocks: REFCLK200M is a 200 MHz clock intended to be used for IDELAY elements in FPGA designs. REFCLK100M and REFCLK250M run at 100 MHz and 250 MHz respectively and can be used to drive internal PLLs and other clocking resources. Each fabric clock is connected to a Multi-Regional Clock Capable (MRCC) pin.3.2.3 Programming Clock (EMCCLK)An 80MHz clock is fed into the EMCCLK pin to drive the BPI flash device during configuration of the FPGA.Table 9 : EMCCLK3.2.4 Cabled HSSIO (SFP+/SATA)The SATA and SFP+ cages share MGT tile 116. The reference clocks for both the SATA and SFP+ interfaces are input into the FPGA at this tile.3.2.5 DDR3 SDRAM Reference ClocksThe two banks of DDR3 SDRAM memory each require a separate reference clock, as per Xilinx Virtex-7 MIG design guidelines. The reference clocks for these interfaces are detailed below:3.3 PCI ExpressThe ADM-PCIE-7V3 is capable of PCIe Gen 1/2/3 with 1/2/4/8 lanes. The FPGA drives these lanes directly using the Integrated PCI Express block from Xilinx. Negotiation of PCIe link speed and number of lanes used is generally automatic and does not require user intervention.PCI Express reset (PERST#) is buffered, level shifted, and connected to the FPGA at pin W27.The other pin assignments for the high speed lanes are provided in the table below:Table 12 : PCI Express Pin Assignments3.4 DDR3 SDRAM SODIMMsTwo DDR3 SDRAM SODIMM connectors can accommodate up to two SODIMMs with 72-bit wide data (64 data + 8 ECC). Maximum signaling rate is 1333 MT/s, and maximum memory capacity is 8 GiB per SODIMM. Peak theoretical memory bandwidth for both banks combined is approximately 165 Gbps.Memory solutions are available from the Xilinx Memory Interface Generator (MIG) tool. Both the Xilinx OpenCL development tools and the ADM-XRC Gen 3 SDK include memory interface examples and constraint files for reference when implementing a new FPGA design.3.5 SFP+Two SFP+ cages are available at the front panel. Both cages are capable of housing either active optical or passive copper SFP+ compatible components. The communication interface can run at speeds capable of handing 10G Ethernet or any other protocol supported by the Xilinx MGT Transceivers. Please see Xilinx User Guide UG476 for more details on the capabilities of the transceivers.If the SFP+ cages are unused, or using copper cabling, it is recommended that the 3.3V power supply for the transceivers is disabled to save power. Please see Power Requirements for more details.Both SFP+ cages have all control signals connected to the FPGA. Their connectivity is described in the table below. The I/O standard used by these pins is LVCMOS18.Table 13 : SFP+ Control SignalsNote:SFP+0/1_TX_DISABLE is pulled up be default and must be driven low to enable most optical modules.*The rate select pins are connected in parallel between the cagesThe data path for the two modules is shown in the table below:Table 14 : SFP+ Transceiver Signals3.6 SATATwo SATA receptacles along the top of the board allow for internal chassis SATA management. The SATA interface can support the third generation SATA specification operating at 6 Gbps. Alpha Data can provide IP to manage the SATA devices connected at this interface. Please contact sales@ for moreinformation regarding SATA IP.Both RX and TX lines are AC coupled with 10nF capacitors. The pin assignments for this interface are detailed below:Table 15 : SATA Signals3.7 System MonitorSystem Monitor Fault ResponsesTI Fusion Communication ComponentsAll power rails are sequenced and monitored by a system monitor IC. The device used in this design is a TI Fusion UCD90120A. The TI Fusion controller monitors certain voltage readings, current readings, and Power OK signals to determine the state of the system. D10 SYS_POK lights if all values are nominal (see Section LEDs for LED Location).If the system monitor detects an inappropriate voltage, temperature, or current, it takes the following actions:•FPGA Core Temperature above operating max (85 degC): Reconfigure FPGA from failsafe region.•Voltage rail outside recommended values in Virtex 7 Datasheet (DS183): Log Fault•Voltage rail outside maximums specified Virtex 7 Datasheet (DS183): Power down board.•Rail current exceeds supply maximum: Power down board.A PC can directly interact with the TI Fusion IC via the PMBUS header in the design. This requires the followingitems:•Programing Box: TI part number "USB-TO-GPIO"•TI Digital Power Designer software (/tool/fusion_digital_power_designer)•xml configuration file from Alpha Data (contact support@)3.8 ConfigurationThere are two main ways of configuring the FPGA on the ADM-PCIE-7V3:•From Flash memory, at power-on, as described in Section 3.8.1•Using a Xilinx JTAG platform cable connected to J1, as described in Section 3.8.23.8.1 Configuration From Flash MemoryThe FPGA can be automatically configured at power-on from a 1 Gbit BPI flash memory device (Micron part number PC28F00AG18). This Flash device is divided into four regions of 32 MiByte each, where each region is sufficiently large to hold an uncompressed bitstream for a 7VX690T FPGA.The ADM-PCIE-7V3 is shipped with a bitstream, corresponding to the "simple" FPGA design from the ADM-XRC Gen 3 SDK, programmed into regions 0 and 1. This permits basic confidence testing to be performed on a board without needing to program anything into the Flash memory. Alpha Data recommends that region 0 is never overwritten; this permits relatively simple recovery, without requiring a Xilinx Platform USB JTAG cable to be attached, in the event of programming a "bad" bitstream into region 1.The flash address map is as detailed below:At power-on, the FPGA attempts to configure itself automatically in BPI mode from one of the four regions of the Flash, determined by SW1-1 and SW-3 (see Section 3.1.1) as follows:Table 16 : Flash Configuration Region SelectionThe Lockdown function of the Flash device is controlled via switch SW1-2. When SW1-2 is ON, any blocks in the Flash whose Lockdown flag is set are write-protected. The factory default for the Lockdown flag of all Flash blocks is clear, so that any block in the Flash can be written.3.8.1.1 Building Configuration ImagesGenerate a bitfile with these constraints (see XAPP587):•set_property PRESS {TRUE} [ current_design ]•set_property BITSTREAM.CONFIG.EXTMASTERCCLK_EN {DIV-1} [current_design]•set_property BITSTREAM.CONFIG.BPI_SYNC_MODE {TYPE1} [current_design]•set_property BITSTREAM.CONFIG.UNUSEDPIN {Pullnone} [current_design]•set_property BITSTREAM.CONFIG.BPI_PAGE_SIZE {1} [ current_design ]•set_property BITSTREAM.CONFIG.CONFIGRATE {3} [ current_design ]•set_property CONFIG_MODE {BPI16} [current_design]•set_property CFGBVS GND [ current_design ]•set_property CONFIG_VOLTAGE 1.8 [ current_design ]Generate an MCS file with these properties (write_cfgmem):•-format MCS•-size 128•-interface BPIx16•-loadbit "up 0x0000000 <directory/to/file/filename.bit>" (failsafe location)•-loadbit "up 0x1000000 <directory/to/file/filename.bit>" (default location)Program with vivado hardware manager with these settings:•BPI part number: mt28gu01gaax1e-bpi-x16•RS bits: 25:243.8.2 Configuration via JTAGA Xilinx Platform USB Cable may be attached to connector J1. This permits the FPGA to be reconfigured usingthe IMPACT tool from Xilinx ISE, or using the Xilinx Vivado Hardware Manager.Revision HistoryPage Intentionally left blankAddress: 4 West Silvermills Lane,Address:3507 Ringsby Court Suite 105,。

PCIE简介

PCI ExpressPCI Express ,简称PCI-E ,是电脑总线PCI 的一种,它沿用了现有的PCI 编程概念及通讯标准,但建基于更快的串行通信系统。

英特尔是该接口的主要支援者。

PCIe 仅应用于内部互连。

由于PCIe 是基于现有的PCI 系统,只需修改物理层而无须修改软件就可将现有PCI 系统转换为PCIe 。

PCIe 拥有更快的速率,以取代几乎全部现有的内部总线(包括AGP 和PCI )。

英特尔希望将来能用一个PCIe 控制器和所有外部设备交流,取代现有的南桥/北桥方案。

除了这些,PCIe 设备能够支援热拔插以及热交换特性,支援的三种电压分别为+3.3V 、3.3Vaux 以及+12V 。

考虑到现在显卡功耗的日益增加,PCIe 而后在规范中改善了直接从插槽中取电的功率限制,16x 的最大提供功率达到了75W ,比AGP 8X 接口有了很大的提升。

基本可以满足当时(2004年)中高阶显卡的需求。

这一点可以从AGP 、PCIe 两个不同版本的6600GT 显卡上就能明显地看到,后者并不需要外接电源。

PCIe 只是南桥的扩展总线,它与操作系统无关,所以也保证了它与原有PCI 的兼容性,也就是说在很长一段时间内在主板上PCIe 接口将和PCI 接口共存,这也给用户的升级带来了方便。

由此可见,PCIe 最大的意义在于它的通用性,不仅可以让它用于南桥和其他设备的连接,也可以延伸到芯片组间的连接,甚至也可以用于连接图形芯片,这样,整个I/O 系统重新统一起来,将更进一步简化计算机系统,增加计算机的可移植性和模块化。

历史在2001年的春季英特尔开发者论坛(IDF )上Intel 公布了取代PCI 总线的第三代I/O 技术,被称为“3GIO ”。

该总线的规范由Intel 支持的AWG (Arapahoe Work Group )负责制定。

2002年4月17日,AWG 正式宣布3GIO 1.0规范草稿制定完毕,移交PCI 特殊兴趣组织(PCI-SIG )进行审核,2002年7月23日经过审核后正式公布,改名为“PCI Express ”,并根据开发蓝图2006年正式推出Spec2.0(2.0规范)。

曙光天阔A840r-G用户手册V1.1

硬件及数据损坏负责; 8、 当服务器出现故障时,如果您不能确定故障的原因,请及时与曙光技术支持部门联系以

获得帮助; 9、 如主板 CMOS 电池失效,请使用与本机配备的电池相同型号的电池进行更换,替换下的

的稳定运行,并将可以延长服务器的使用寿命; 2、 请使用带接地保护的三芯电源线与插座,并使用220V 交流电,不正确的电源设置可能

会导致漏电、烧毁、爆炸甚至人身伤害; 3、 请不要在服务器正在运行时插拔背板连线或是移动服务器,否则将可能造成服务器当机

或是部件损坏; 4、 请尽量避免频繁重启或开关机,以延长服务器的使用寿命; 5、 请用户及时备份重要数据,曙光信息产业有限公司不为任何情况导致的数据丢失负责; 6、 请使用正版操作系统及软件,并进行正确配置。曙光信息产业有限公司对由于操作系统

声明及注意事项

感谢您选用曙光服务器!

曙光服务器将给您带来强大的应用支持和全新的性能体验。为了您能够更安全、方便的 使用曙光服务器,在使用之前,请详细阅读本节所提示的信息。

曙光服务器在设计和制造过程中均遵循了严格的标准,以保证您所使用的服务器拥有卓 越的品质和完美的“SUMA”特性。但是服务器属于精密电子设备,在使用过程中仍然可能因 为各种原因而导致异常,所以请务必明确以下事项: 1、 请将服务器放置在阴凉、干燥、通风、洁净、无强磁场的环境中使用,这有助于服务器

电池请妥善回收处理。 曙光信息产业有限公司保留对以上条款的解释权。

再次感谢您选用曙光服务器!

-3-

曙光天阔 A840r-G 服务器用户手册 V1.1

目录

第一章 系统简介 ........................

OXuPCI954_DS

External—Free ReleaseOxford Semiconductor, Inc.1900 McCarthy Boulevard, Suite 210 © Oxford Semiconductor, Inc. 2007F EATURES• Four 16C950 High performance UART channels • 8-bit Pass-through Local Bus (PCI Bridge )• IEEE1284 Compliant SPP/EPP/ECP parallel port (with external transceiver)• Efficient 32-bit, 33 MHz, multi-function target-only PCIcontroller, fully compliant to PCI Local Bus Specification 3.0 and PCI Power Management Specification 1.1 • Software compatible with OXmPCI954• UARTs fully software compatible with 16C550-type devices • UART operation up to 60 MHz via external clock source. Up to 20 MHz with the crystal oscillator• Baud rates up to 60 Mbps in external 1x clock mode and 15 Mbps in asynchronous mode• 128-byte deep FIFO per transmitter and receiver • Flexible clock prescaler, from 1 to 31.875• Automated in-band flow control using programmable Xon/Xoff in both directions•Automated out-of-band flow control using CTS#/RTS# and/or DSR#/DTR#• Programmable RS485 turnaround delay• Arbitrary trigger levels for receiver and transmitter FIFO interrupts and automatic in-band and out-of-band flow control• Infra-red (IrDA) receiver and transmitter operation • 9-bit data framing, as well as 5, 6, 7, and 8 bits • Detection of bad data in the receiver FIFO• Global Interrupt Status and readable FIFO levels to facilitate implementation of efficient device drivers.• Local registers to provide status/control of device functions • 11 multi-purpose I/O pins, which can be configured as input interrupt pins or ‘wake-up’• Auto-detection of a wide range of optional MICROWIRE TM compatible EEPROMs, to re-configure device parameters • Function access , to pre-configure each function prior to handover to generic device drivers • Operation via I/O or memory mapping• 3.3 V or 5 V operation (PCI Universal Voltage)• Extended operating temperature range: -40° C to 85° C •176-pin LQFP packageD ESCRIPTIONThe OXuPCI954 is a single chip solution for PCI-based serial and parallel expansion add-in cards. It is a dual function PCI device, where function 0 offers four ultra-high performance OX16C950 UARTs, and function 1 is configurable either as an 8-bit local bus or a bi-directional parallel port.Each UART channel in the OXuPCI954 is the fastest available PC-compatible UART, offering data rates up to 15 Mbps and 128-byte deep transmitter and receiver FIFOs. The deep FIFOs reduce CPU overhead and allow utilization of higher data rates. Each UART channel is software compatible with the widely used industry-standard 16C550 devices (and compatibles), as well as the OX16C95x family of high performance UARTs. In addition to increased performance and FIFO size, the UARTs also provide the full set of OX16C95x enhanced features including automated in-band flow control, readable FIFO levels, etc.To enhance device driver efficiency and reduce interrupt latency, internal UARTs have multi-port features such as shadowed FIFO fill levels, a global interrupt source register and Good-Data Status, readable in four adjacent DWORD registers visible to logical functions in I/O space and memory space.Expansion of serial ports beyond four channels is possible using the 8-bit pass-through Local Bus function. This provides a general address/data bus and interrupt capability to a discrete UART part, such as the Oxford SemiconductorOX16C954. Other controllers could be used to provide capabilities beyond additional UART ports. The addressable space provided by the Local Bus can be increased up to 256 bytes, and divided into four chip-select regions. This flexible expansion scheme caters for cards with up to 20 serial ports using external 16C950, 16C954 or compatible devices, or composite applications such as combined serial and parallel port expansion cards. Serial port cards with up to 20 ports (or with 4 serial ports and a parallel port) can be designed without redefining any device or timing parameters.The parallel port is an IEEE 1284 compliant SPP/EPP/ECP parallel port that fully supports the existing Centronics interface. The parallel port can be enabled in place of the local bus. A n external bus transceiver is required for 5V parallel port operation if device is 3.3V sourced.For full flexibility, all the default configuration register values can be overwritten using an optional M ICROWIRE compatibleserial EEPROM. This EEPROM can also be used to provide function access to pre-configure devices on the local bus/parallel port, prior to any PCI configuration accesses and before control is handed to (generic) device drivers.The OXuPCI954 can be used to replace the OXmPCI954 in a PCI application where quad UARTs and a local bus/parallel port functionality are required.OXuPCI954 DATA SHEETIntegrated High Performance Quad UARTs,8-bit Local Bus/Parallel Port,3.3 V and 5 V (Universal Voltage) PCI Interface .Improvements of the OXuPCI954 over Discrete SolutionsHigher degree of integrationThe OXuPCI954 device offers four internal 16C950 high-performance UARTs and an 8-bit local bus or abi-directional parallel port.Multi-function deviceThe OXuPCI954 is a multi-function device to enable users to load individual device drivers for the internal serial ports, drivers for the peripheral devices connected to the local bus or drivers for the internal parallel port.Quad Internal OX16C950 UARTsThe OXuPCI954 device contains four ultra-high performance UARTs, which can increase driver efficiency by using features such as the 128-byte deep transmitter and receiver FIFOs, flexible clock options, automatic flow control, programmable interrupt and flow control trigger levels and readable FIFO levels. Data rates are up to 60 Mbps.Improved access timingAccess to the internal UARTs require zero or one PCI wait state. A PCI read transaction from an internal UART can complete within five PCI clock cycles and a write transaction to an internal UART can complete within four PCI clock cycles. Reduces interrupt latencyThe OXuPCI954 device offers shadowed FIFO levels and Interrupt status registers on the internal UARTs and the MIO pins. This reduces the device driver interrupt latency. Power managementThe OXuPCI954 device complies with the PCI Power Management Specification 1.1 and the Microsoft Communications Device-class Power Management Specification 2.0 (2000). Both functions offer the extended capabilities for Power Management. This achieves significant power savings by enabling device drivers to power down the PCI functions. For function 0, this is through switching off the channel clock, in power state D3. Wake-up (PME# generation) can be requested by either functions. For function 0, this is via the RI# inputs of the UARTs in the power-state D3 or any modem line and SIN inputs of the UARTs in power-state D2. For function 1, this is via the MIO[2] input.Optional EEPROMThe OXuPCI954 device can be reconfigured from an external EEPROM to the end-user’s requirements. However, this is not required in many applications as the default values are sufficient for typical applications. An overrun detection mechanism built into the EEPROM controller prevents the PCI system from ‘hanging’ due to an incorrectly programmed EEPROM.R EVISION H ISTORYRevision Modification May 2007 First publication.Sep 2007 Feature revision, including removal of D3coldT ABLE OF C ONTENTS1OXuPCI954 Device Modes (6)2Block Diagram (7)3Pin Information—176-Pin LQFP (8)3.1Mode ‘0’ Quad UARTs + 8-bit Local Bus (8)3.1.1Mode ‘1’ : Quad UARTs + Parallel Port (9)3.2Pin Descriptions (10)4Configuration and Operation (16)5PCI Target Controller (17)5.1Operation (17)5.2Configuration Space (17)5.2.1PCI Configuration Space Register Map (18)5.3Accessing Logical Functions (20)5.3.1PCI Access to Internal UARTs (21)5.3.2PCI Access to 8-bit Local Bus (22)5.3.3PCI Access to Parallel Port (22)5.4Accessing Local Configuration Registers (23)5.4.1Local Configuration and Control Register ‘LCC’ (Offset 0x00) (23)5.4.2Multi-purpose I/O Configuration Register ‘MIC’ (Offset 0x04) (24)5.4.3Local Bus Timing Parameter Register 1 ‘LT1’ (Offset 0x08) (26)5.4.4Local Bus Timing Parameter Register 2 ‘LT2’ (Offset 0x0C) (27)5.4.5UART Receiver FIFO Levels ‘URL’ (Offset 0x10) (28)5.4.6UART Transmitter FIFO Levels ‘UTL’ (Offset 0x14) (29)5.4.7UART Interrupt Source Register ‘UIS’ (Offset 0x18) (29)5.4.8Global Interrupt Status and Control Register ‘GIS’ (Offset 0x1C) (30)5.5PCI Interrupts (31)5.6Power Management (32)5.6.1Power Management of Function 0 (32)5.6.2Power Management of Function 1 (33)5.6.3Universal Voltage (34)5.7Unique Bar Option – for Function 0 (35)6Internal OX16C950 UARTs (36)6.1Operation – Mode Selection (36)6.1.1450 Mode (36)6.1.2550 Mode (36)6.1.3Extended 550 Mode (36)6.1.4750 Mode (36)6.1.5650 Mode (36)6.1.6950 Mode (37)6.2Register Description Tables (38)6.3UART Reset Configuration (41)6.3.1Hardware Reset (41)6.3.2Software Reset (41)6.4Transmitter and Receiver FIFOs (42)6.4.1FIFO Control Register ‘FCR’ (42)6.5Line Control and Status (43)6.5.1False Start Bit Detection (43)6.5.2Line Control Register ‘LCR’ (43)6.5.3Line Status Register ‘LSR’ (44)6.6Interrupts and Sleep Mode (45)6.6.1Interrupt Enable Register ‘IER’ (45)6.6.2Interrupt Status Register ‘ISR’ (46)6.6.3Interrupt Description (46)6.6.4Sleep Mode (47)6.7Modem Interface (47)6.7.1Modem Control Register ‘MCR’ (47)6.7.2Modem Status Register ‘MSR’ (48)6.8Other Standard Registers (48)6.8.1Divisor Latch Registers ‘DLL and DLM’ (48)6.8.2Scratch Pad Register ‘SPR’ (48)6.9Automatic Flow Control (49)6.9.1Enhanced Features Register ‘EFR’ (49)6.9.2Special Character Detection (50)6.9.3Automatic In-band Flow Control (50)6.9.4Automatic Out-of-band Flow Control (50)6.10Baud Rate Generation (51)6.10.1General Operation (51)6.10.2Clock Prescaler Register ‘CPR’ (51)6.10.3Times Clock Register ‘TCR’ (51)6.10.4External 1x Clock Mode (53)6.10.5Crystal Oscillator Circuit (53)6.11Additional Features (54)6.11.1Additional Status Register ‘ASR’ (54)6.11.2FIFO Fill Levels ‘TFL and RFL’ (54)6.11.3Additional Control Register ‘ACR’ (54)6.11.4Transmitter Trigger Level ‘TTL’ (55)6.11.5Receiver Interrupt. Trigger Level ‘RTL’ (55)6.11.6Flow Control Levels ‘FCL’ and ‘FCH’ (56)6.11.7Device Identification Registers (56)6.11.8Clock Select Register ‘CKS’ (56)6.11.9Nine-bit Mode Register ‘NMR’ (57)6.11.10Modem Disable Mask ‘MDM’ (57)6.11.11Readable FCR ‘RFC’ (58)6.11.12Good-data Status Register ‘GDS’ (58)6.11.13Port Index Register ‘PIX’ (58)6.11.14Clock Alteration Register ‘CKA’ (58)6.11.15RS485 Delay Enable ‘RS485_DLYEN’ (58)6.11.16RS485 Delay Count ‘RS485_DLYCNT’ (59)7Local bus (60)7.1Overview (60)7.2Operation (60)7.3Configuration and Programming (61)8Bidirectional Parallel Port (62)8.1Operation and Mode Selection (62)8.1.1SPP Mode (62)8.1.2PS2 Mode (62)8.1.3EPP Mode (62)8.1.4ECP Mode (62)8.2Parallel Port Interrupt (63)8.3Register Description (63)8.3.1Parallel Port Data Register ‘PDR’ (64)8.3.2ECP FIFO Address / RLE (64)8.3.3Device Status Register ‘DSR’ (64)8.3.4Device Control Register ‘DCR’ (64)8.3.5EPP Address register ‘EPPA’ (65)8.3.6EPP Data Registers ‘EPPD1-4’ (65)8.3.7ECP Data FIFO (65)8.3.8Test FIFO (65)8.3.9Configuration A Register (65)8.3.10Configuration B Register (65)8.3.11Extended Control Register ‘ECR’ (65)9Serial EEPROM (66)9.1Specification (66)9.1.1Zone 0: Header (67)9.1.2Zone 1: Local Configuration Registers (68)9.1.3Zone 2: Identification Registers (69)9.1.4Zone 3: PCI Configuration Registers (69)9.1.5Zone 4: Power Management DATA (and DATA_SCALE Zone) (70)9.1.6Zone 5: Function Access (70)10Operating Conditions (72)10.1DC Electrical Characteristics (72)11AC Electrical Characteristics (76)11.1PCI Bus Timings (76)11.2Local Bus (77)11.3Serial Ports (79)12Timing Waveforms (80)13Package Information (95)13.1176-Pin LQFP (95)14Ordering Information (96)1OX U PCI954D EVICE M ODESThe OXuPCI954 supports two modes of operation. These modes are summarized in the following table.Device Mode Mode Pin Selection Functionality0 MODE = 0 Function 0 : Quad UARTs Function 1 : 8-bit local bus1 MODE = 1 Function 0 : Quad UARTs Function 1 : Parallel Port* The OXuPCI954 is not pin-compatible with the OX16PCI954 or the OXmPCI954, but is the same in all other aspects.2B LOCK D IAGRAMFIFOSELMODEAD[31:0]C/BE[3:0]#PCI_CLKFRAME#DEVSEL#IRDY#TRDY#STOP#PARPERR#IDSELRST#INTA#PME#XTLIXTLOUART_Clk_Out Local_Bus ClkEE_DIEE_CSEE_CKEE_DOSOUT[3:0]SIN[3:0]RTS[3:0]DTR[3:0]CTS[3:0]DSR[3:0]DCD[3:0]RI[3:0]MIO[10:0]PD[7:0]ACK#PEBUSYSLCTERR#SLIN#INIT#AFD#STB#LBA[7:0]LBD[7:0]LBCS[3:0]LBWR#LBRD#LBRSTDATA_DIR OXuPCI954 Block DiagramOSCDIS XTLSEL3P IN I NFORMATION—176-P IN LQFP 3.1Mode ‘0’ Quad UARTs + 8-bit Local Bus7 NC. Do not connect these pins:23, 40, 41, 136, 137, 138, 1393.1.1Mode ‘1’ : Quad UARTs + Parallel Port15 NC. Do not connect these pins:23, 40, 41, 74, 112, 113, 114, 115, 116, 117, 124, 136, 137, 138, 1393.2Pin DescriptionsFor the actual pinouts of the OXuPCI954 device (for the various modes), refer to the Section 3, Pin Information. The I/O direction key table is on page 15.PCI Interface – All ModesPin Dir1Name Description149, 150, 151, 154, 155,157, 158, 160, 164, 165,167, 168, 169, 170, 171,174, 13, 14, 15, 17, 18, 20,24, 25, 27, 28, 31, 32, 33,34, 35, 39P_I/O AD[31:0] Multiplexed PCI Address/Data bus161, 175, 12, 26 P_I C/BE[3:0]# PCI Command/Byte enable146 P_I CLK PCI system clock (33MHz)176 P_IFRAME#CycleFrame5 P_ODEVSEL#DeviceSelect1 P_IIRDY#Initiatorready2 P_OTRDY#Targetready6 P_O STOP# Target Stop request10 P_I/OPAR Parity8 P_OSERR#Systemerror7 P_I/OPERR#Parityerror163 P_I IDSEL Initialization device select144 P_I RST# PCI system reset142 P_ODINTA# PCIinterrupt147 P_OD PME# Power management eventSerial Port Pins – All ModesPin Dir1Name Description50 I FIFOSEL FIFO select. For backward compatibility with 16C550,16C650 and 16C750 devices the UARTs’ FIFO depth is 16when FIFOSEL is low. The FIFO size is increased to 128when FIFOSEL is high. The unlatched state of this pin isreadable by software. The FIFO size may also be set to 128by setting FCR[5] when LCR[7] is set, or by putting thedevice into Enhanced mode.82, 81, 63, 62 O(h)SOUT[3:0]IrDA_Out[3:0] These four pins are present in all modes but they can serve one of two functions, as follows:UART serial data outputs.UART IrDA data output when MCR[6] of the corresponding channel is set in Enhanced mode.91, 73, 72, 55I(h) I(h) SIN[3:0]IrDA_In[3:0]These four pins are present in all modes but they can serveone of two functions, as follows:UART serial data inputs.UART IrDA data input when IrDA mode is enabled (seeabove).Serial Port Pins – All ModesPin Dir1Name Description89, 76, 71, 57 I(h) DCD[3:0]# Active-low modem data-carrier-detect input 84, 79, 65, 60O(h) O(h) O(h) DTR[3:0]#485_En[3:0]Tx_Clk_Out[3:0]These four pins are present in all modes but they can serveone of three functions, as follows:Active-low modem data-terminal-ready output. If automatedDTR# flow control is enabled, the DTR# pin is asserted anddeasserted if the receiver FIFO reaches or falls below theprogrammed thresholds, respectively.In RS485 half-duplex mode, the DTR# pin may beprogrammed to reflect the state of the transmitter empty bitto automatically control the direction of the RS485transceiver buffer (see register ACR[4:3]).Transmitter 1x clock (baud rate generator output). Forisochronous applications, the 1x (or Nx) transmitter clockmay be asserted on the DTR# pins (see register CKS[5:4]).83, 80, 64, 61 O(h) RTS[3:0]# Active-low modem request-to-send output. If automatedRTS# flow control is enabled, the RTS# pin is deassertedand reasserted whenever the receiver FIFO reaches or fallsbelow the programmed thresholds, respectively.85, 78, 67, 59 I(h) CTS[3:0]# Active-low modem clear-to-send input. If automated CTS#flow control is enabled, upon deassertion of the CTS# pin,the transmitter will complete the current character and enterthe idle mode until the CTS# pin is reasserted. Note: any in-band flow control characters are transmitted regardless ofthe state of the CTS# pin.86, 77, 66, 58I(h) I(h) DSR[3:0]#Rx_Clk_In[3:0]These four pins are present in all modes but they can serveone of two functions, as follows:Active-low modem data-set-ready input. If automated DSR#flow control is enabled, upon deassertion of the DSR# pin,the transmitter will complete the current character and enterthe idle mode until the DSR# pin is reasserted. Note: any in-band flow control characters are transmitted regardless ofthe state of the DSR# pin.External receiver clock for isochronous applications. TheRx_Clk_In is selected when CKS[1:0] = ‘01’.90, 75, 70, 56 I(h)I(h) RI[3:0]#Tx_Clk_In[3:0]Active-low modem Ring-Indicator inputExternal transmitter clock. This clock can be used by thetransmitter (and indirectly by the receiver) when CKS[6]=’1’.Clock Interface Pins – All ModesPin Dir 1 Name Description49 I/OXTLOCrystal oscillator output when OSCDIS = ‘0’.External clock source input when OSCDIS = ‘1’48 I XTLI Crystal oscillator input when OSCDIS = ‘0’, up to 20MHz.N/C when OSCDIS = ‘1’45 I OSCDIS Oscillator disable.When 0, the internal crystal oscillator is enabled and a crystal needs to be attached to XTLI/XTLO.XTLSEL must be set according to the crystal frequency that is used (up to 20Mhz).When 1, the internal crystal oscillator is disabled and an external oscillator source (up to 60MHz) can be input to XTLO. XTLI is N/C and XTLSEL must be 0130 I XTLSEL Defines the frequency of the crystal attached to XTLI/XTLO(when OSCDIS = ‘0’)0 = 1 MHz – 12 MHz 1 = 12 MHz – 20 MHz8-bit Local Bus – Mode 0Pin Dir 1 Name Description 111O UART_CLK_Out Buffered crystal output. This clock can drive external UARTsconnected to the local bus. Can be enabled / disabled by software.123 O(h) LBRST Local bus active-high reset. 124 O LBRST# Local bus active-low reset. 104 O LBDOUT Local bus data out enable. This pin can be used by externaltransceivers; it is high when LBD[7:0] are in output mode and low when they are in input mode.74 O LBCLK Buffered PCI clock. Can be enabled / disabled by software. 114, 115, 116, 117 O(h) O(h) LBCS[3:0]# LBDS[3:0]# Local bus active-low Chip-Select (Intel mode).Local bus active-low Data-Strobe (Motorola mode).112 O O LBWR# LBRDWR# Local bus active-low write-strobe (Intel mode).Local bus Read-not-Write control (Motorola mode).113 O Z LBRD# Hi-Z Local bus active-low read-strobe (Intel mode).Permanent high impedance (Motorola mode).105, 106, 108, 109 118, 119, 120, 122 O(h) LBA[7:0] Local bus address signals. 96, 97, 98, 99 100, 101, 102, 103I/O(h) LBD[7:0] Local bus data signals.Parallel Port – Mode 1Pin Dir 1 NameDescription123 I(h) I(h) ACK#INTR#Acknowledge (SPP mode). ACK# is asserted (low) by the peripheral to indicate that a successful data transfer has taken place.Identical function to ACK# (EPP mode).122 I(h) PEPaper Empty. Activated by printer when it runs out of paper. 120 I(h) I(h) BUSYWAIT#Busy (SPP mode). BUSY is asserted (high) by the peripheral when it is not ready to accept data.Wait (EPP mode). Handshake signal for interlocked IEEE 1284 compliant EPP cycles.109 OD(h) O(h) SLIN#ADDRSTB#Select (SPP mode). Asserted by host to select the peripheral.Address strobe (EPP mode) provides address read and write strobe.119 I(h) SLCT Peripheral selected. Asserted by peripheral when selected. 118 I(h) ERR#Error. Held low by the peripheral during an error condition. 108 OD(h) O(h) INIT#INIT#Initialize (SPP mode). Commands the peripheral to initialize.Initialize (EPP mode). Identical function to SPP mode. 106 OD(h) O(h) AFD#DATASTB# Auto Feed (SPP mode, open-drain).Data strobe (EPP mode) provides data read and write strobe.105 OD(h) O(h) STB#WRITE#Strobe (SPP mode). Used by peripheral to latch data currently available on PD[7:0].Write (EPP mode). Indicates a write cycle when low and a read cycle when high . 96, 97, 98, 99, 100, 101, 102, 103I/O(h) PD[7:0] Parallel data bus.104OPDOUTParallel port data out enable. This pin should be used by external transceivers for 5 V signaling; it is high when PD[7:0] are in output mode and low when they are in input mode.Multi-purpose and External Interrupt Pins – All ModesPin Dir1Name DescriptionMODE0 1135 --135I/O(h)OMIO0NCMulti-purpose I/O 0. Can drive high or low, or assert a PCIinterrupt.Output Driving ‘0’. Can be left as a No-connect.134 134 134134I/O(h)MIO1NCMulti-purpose I/O 1. Can drive high or low, or assert a PCIinterrupt (as long as LCC[6:5] = “00”).Output Driving ‘0’ (when LCC[6:5] ≠ ‘00’)Can be left as a No-Connect.133 133 133133I/O(h)IMIO2PME_InMulti-purpose I/O 2. When LCC[7] = 0, this pin can drive highor low, or assert a PCI interrupt.Input power management event. When LCC[7] is set thisinput pin can assert a function 1 PME#.93, 94, 95, 125, 126, 127, 128, 132 I/O(h) MIO[10:3] Multi-purpose I/O pins. Can drive high or low, or assert a PCIinterrupt.EEPROM Pins – All ModesPin Dir1Name Description53 OEE_CKEEPROMclock.52 O EE_CS EEPROM active-high Chip Select.54 IU(h) EE_DI EEPROM data in, with internal pull-up.When the serial EEPROM is connected, this pin should bepulled up using a 1-10k resistor. When the EEPROM is notused the internal pull-up is sufficient.Pin to be connected to the external EEPROM’s EE_DO pin(if used).51 O EE_DO EEPROM data out.Pin to be connected to the external EEPROM’s EE_DI pin(if used).Table 1: Pin DescriptionsI/O Direction Key P_I PCI input 3.3 V Only P_O PCI output / PCITristates 3.3 V Only P_I/O PCI bi-directional 3.3 V Only P_OD PCI open drain 3.3 V OnlyI Input LVTTL level I(h) Input LVTTL level, 5 V tolerant IU(h) Input with internal pull-up LVTTL level, 5 V tolerant I/O(h) Bi-Directional LVTTL level, 5 V tolerantO Output Standard Output O(h) Output 5 V tolerant (High Voltage BI-Direct in output mode) OD Open drain Standard Open-drain Output OD(h) Open drain 5 V tolerant (High Voltage BI-Direct in open-drain mode) NC No connectG Ground V VoltageMiscellaneous PinsPin Dir 1 NameDescription44 IMODEMode selector Pin0 : Function 0 : Quad UART. Function 1 : 8-bit local bus.1 : Function 0 : Quad UART. Function 1 : Parallel port.Power and GroundPinType Name Description19, 42, 47, 69, 88, 107, 131, 148VVDDPower Supply (3.3 V)11, 22, 36, 140, 156, 162, 173 V VIOPCI I/O Universal VoltageDefines the (clamping) voltage of the PCI I/O Buffers.To be connected to the VIO pin of the PCI connector. 3, 4, 9, 16, 21, 29, 30, 37, 38, 43, 46, 68, 87, 92, 110, 121, 129, 141, 143, 145, 152, 153, 159, 166, 172G GNDPower Supply Ground (0 V)4C ONFIGURATION AND O PERATIONThe OXuPCI954 is a multi-function, target-only PCI device, compliant with the PCI Local Bus Specification, Revision 3.0 and the PCI Power Management Specification, Revision 1.1.The OXuPCI954 affords maximum configuration flexibility by treating the internal UARTs, the local bus and the parallel port as separate logical functions. Each function has its own configuration space and is therefore recognized and configured by the PCI BIOS separately. The functions used are configured by the Mode Selection Pin as shown in Section 1 OXuPCI954 Device Modes.The OXuPCI954 is configured by system start-up software during the bootstrap process that follows bus reset. The system scans the bus and reads the vendor and device identification codes from any devices it finds. It then loads device-driver software according to this information and configures the I/O, memory and interrupt resources. Device drivers can then access the functions at the assigned addresses in the usual fashion, with the improved data throughput provided by PCI.Each function operates as though it was a separate device. However there are a set of Local Configuration Registers that can be used to enable signals and interrupts, configure timings, and improve the efficiency of multi-port drivers. This architecture enables separate drivers to be installed for each function. Generic port drivers can be hooked to use the functions individually, or more efficient multi-port drivers can hook both functions, accessing the Local Configuration Registers from either.All registers default after reset to suitable values for typical applications such a 4/8 port serial, or combo 4-port serial/1-port parallel add-in cards. However, all identification, control and timing registers can be redefined using an optional serial EEPROM.5PCI T ARGET C ONTROLLER5.1OperationThe OXuPCI954 responds to the following PCI transactions:-•Configuration access: The OXuPCI954 responds to type 0 configuration reads and writes if the IDSELsignal is asserted and the bus address is selecting theconfiguration registers for function 0 or 1. The devicewill respond to the configuration transaction by asserting DEVSEL#. Data transfer then follows. Anyother configuration transaction will be ignored by theOXuPCI954.•I/O reads/writes: The address is compared with the addresses reserved in the I/O Base Address Registers(BARs). If the address falls within one of the assignedranges, the device will respond to the I/O transactionby asserting DEVSEL#. Data transfer follows thisaddress phase. For the UARTs and 8-bit local buscontroller, only byte accesses are possible. For I/Oaccesses to these regions, the controller comparesAD[1:0] with the byte-enable signals as defined in thePCI specification. The access is always completed;however if the correct BE signal is not present thetransaction will have no effect.•Memory reads/writes: These are treated in the same way as I/O transactions, except that the memoryranges are used. Memory access to single-byte regions is always expanded to DWORDs in theOXuPCI954. In other words, OXuPCI954 reserves aDWORD per byte in single-byte regions. The deviceallows the user to define the active byte lane usingLCC[4:3] so that in Big-Endian systems the hardwarecan swap the byte lane automatically. For Memorymapped access in single-byte regions, the OXuPCI954 compares the asserted byte-enable withthe selected byte-lane in LCC[4:3] and completes theoperation if a match occurs, otherwise the access willcomplete normally on the PCI bus, but it will have noeffect on either the internal UARTs or the local buscontroller.•All other cycles (64-bit, special cycles, reserved encoding etc.) are ignored.The OXuPCI954 will complete all transactions as disconnect-with-data, i.e. the device will assert the STOP# signal alongside TRDY#, to ensure that the Bus Master does not continue with a burst access. The exception to this is Retry, which will be signaled in response to any access while the OXuPCI954 is reading from the serial EEPROM.The OXuPCI954 performs medium-speed address decoding as defined by the PCI specification. It asserts the DEVSEL# bus signal two clocks after FRAME# is first sampled low on all bus transaction frames which address the chip. The internal UARTs are accessed with zero wait states inserted. Fast back-to-back transactions are supported by the OXuPCI954 as a target, so a bus master can perform faster sequences of write transactions to the UARTs or local bus when an inter-frame turn-around cycle is not required.The device supports any combination of byte-enables to the PCI Configuration Registers and the Local Configuration Registers. If a byte-enable is not asserted, that byte is unaffected by a write operation and undefined data is returned upon a read.The OXuPCI954 performs parity generation and checking on all PCI bus transactions as defined by the standard. Note this is entirely unrelated to serial data parity which is handled within the UART functional modules themselves. If a parity error occurs during the PCI bus address phase, the device will report the error in the standard way by asserting the SERR# bus signal. However if that address/command combination is decoded as a valid access, it will still complete the transaction as though the parity check was correct.The OXuPCI954 does not support any kind of caching or data buffering in addition to that already provided within the UARTs by the transmit and receive data FIFOs. In general, registers in the UARTs and on the local bus can not be pre-fetched because there may be side-effects on read.5.2Configuration SpaceThe OXuPCI954 is a dual-function device, where each logical function has its own configuration space. All required fields in the standard header are implemented, plus the Power Management Extended Capability register set. The format of the configuration space is shown in the following tables.In general, writes to any registers that are not implemented are ignored, and all reads from unimplemented registers return 0.。

ilo pcie additionacorrected error -回复

ilo pcie additionacorrected error -回复[在计算机中,PCIe卡添加错误的修正方法]在计算机领域中,PCIe(Peripheral Component Interconnect Express)卡是一种常见的扩展卡接口,用于连接各种外部设备和扩展功能。

然而,有时在安装PCIe卡时可能会发生错误。

本文将一步一步介绍如何纠正PCIe卡添加错误。

第一步:识别错误类型第一步是识别PCIe卡添加错误类型。

在大多数情况下,错误类型可以归类为以下几种:1. 物理连接错误:这种错误发生在PCIe卡与计算机主板插槽之间的物理连接上。

可能由于插槽松动、不完全插入或脏污尘等原因导致。

2. 驱动程序错误:在一些情况下,正确安装了PCIe卡,但没有正确安装或更新相应的驱动程序。

这可能导致计算机无法识别PCIe卡或无法正确使用其功能。

3. 冲突错误:当已经在计算机中安装了其他设备或组件时,可能会出现PCIe卡和其他设备之间的冲突。

这可能导致系统不稳定或PCIe卡无法正常工作。

第二步:检查物理连接在第一步中,如果错误类型被识别为物理连接错误,那么第二步就是检查物理连接。

1. 关闭计算机电源并卸下所有外部电源连接。

确保你仔细查看并了解计算机的内部工作方式(如果你不确定,可以查看计算机主板的用户手册)。

2. 打开计算机机箱,并找到PCI或PCIe插槽。

这些插槽通常位于计算机主板的底部。

3. 检查PCIe卡和插槽是否干净,并确保没有任何灰尘或污垢。

4. 按照PCIe卡的指示将其正确插入到插槽中。

确保插头完全插入插槽,并确保PCIe卡的金属接点与插槽的金属接点相连接。

5. 重新连接计算机的外部电源,重新启动计算机并查看是否解决了物理连接错误。

第三步:驱动程序安装和更新如果在第一步中发现错误类型为驱动程序错误,那么第三步是安装或更新相应的驱动程序。

1. 在互联网上找到适用于你的PCIe卡的最新驱动程序。

uboot pcie驱动原理

uboot pcie驱动原理摘要:1.介绍uboot pcie 驱动2.详述uboot pcie 驱动的原理3.总结uboot pcie 驱动的重要性正文:1.介绍uboot pcie 驱动Uboot 是一种通用的bootloader,广泛应用于各种嵌入式系统中。

它可以从NAND flash、NOR flash 或硬盘启动系统,并支持多种文件系统。

在嵌入式系统中,PCIe(Peripheral Component Interconnect Express)是一种常见的高速串行计算机扩展总线标准,用于连接主板上的中央处理器(CPU)和各种外部设备,如显卡、声卡、硬盘等。

Uboot pcie 驱动就是用于支持PCIe 设备的驱动程序。

2.详述uboot pcie 驱动的原理Uboot pcie 驱动的原理主要基于PCIe 协议。

PCIe 协议是一种点对点(peer-to-peer)的串行通信协议,通过数据传输和数据校验来实现设备之间的通信。

Uboot pcie 驱动的工作流程如下:(1)初始化:首先,Uboot 将PCIe 设备添加到系统中,并初始化相关硬件资源。

(2)配置:Uboot 根据PCIe 设备的类型和配置空间,生成相应的配置空间表。

配置空间表包含了设备的基本信息,如设备类型、设备地址、设备配置空间等。

(3)数据传输:Uboot 通过PCIe 协议,实现与PCIe 设备的数据传输。

数据传输过程中,Uboot 将设备所需的启动代码、设备驱动等文件传输到PCIe 设备中。

(4)设备启动:Uboot 将PCIe 设备的控制权交给操作系统,由操作系统完成后续的设备驱动加载和设备启动。

3.总结uboot pcie 驱动的重要性Uboot pcie 驱动在嵌入式系统中具有重要作用,主要表现在以下几点:(1)支持PCIe 设备的启动:Uboot pcie 驱动支持各种PCIe 设备的启动,使得嵌入式系统能够兼容更多的外部设备。

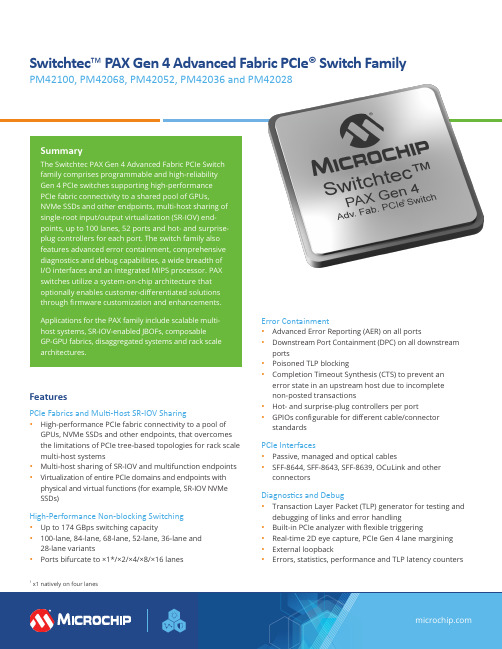

Switchtec PAX Gen 4高性能PCIe交换器系列说明书

Switchtec™ PAX Gen 4 Advanced Fabric PCIe® Switch Family PM42100, PM42068, PM42052, PM42036 and PM42028FeaturesPCIe Fabrics and Multi-Host SR-IOV Sharing• High-performance PCIe fabric connectivity to a pool of GPUs, NVMe SSDs and other endpoints, that overcomes the limitations of PCIe tree-based topologies for rack scale multi-host systems• Multi-host sharing of SR-IOV and multifunction endpoints • Virtualization of entire PCIe domains and endpoints with physical and virtual functions (for example, SR-IOV NVMeSSDs)High-Performance Non-blocking Switching• Up to 174 GBps switching capacity• 100-lane, 84-lane, 68-lane, 52-lane, 36-lane and 28-lane variants• Ports bifurcate to ×1*/×2/×4/×8/×16 lanes1 x1 natively on four lanes Error Containment• Advanced Error Reporting (AER) on all ports• Downstream Port Containment (DPC) on all downstream ports• Poisoned TLP blocking• Completion Timeout Synthesis (CTS) to prevent an error state in an upstream host due to incompletenon-posted transactions• Hot- and surprise-plug controllers per port• GPIOs configurable for different cable/connector standardsPCIe Interfaces• Passive, managed and optical cables• SFF-8644, SFF-8643, SFF-8639, OCuLink and other connectorsDiagnostics and Debug• Transaction Layer Packet (TLP) generator for testing and debugging of links and error handling• Built-in PCIe analyzer with flexible triggering• Real-time 2D eye capture, PCIe Gen 4 lane margining • External loopback• Errors, statistics, performance and TLP latency countersThe Microchip name and logo and the Microchip logo are a registered trademarks and Switchtec is a trademark of MicrochipTechnology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies.© 2021, Microchip Technology Incorporated. All Rights Reserved. 7/21 DS00002987DHighlights• High-reliability PCIe: robust error containment, hot- andsurprise-plug controllers per port, end-to-end data in-tegrity protection, ECC protection on RAMs, high-quality, low-power SerDes• PAX Software Development Kit (SDK): enables sup-port for vendor-specific SR-IOV endpoint sharing and virtualization• Integrated processor, I/O interfaces, and SDK for enclo-sure management firmware development•Comprehensive diagnostics and debugging: PCIe gen-erator and analyzer, per-port performance and error counters, multiple loopback modes and real-time eye capture•Significant power, cost and board space savings with support for:• Up to 52 ports• Flexible ×1*, ×2, ×4, ×8, and ×16 port bifurcation with no restrictions on configuring ports as either up -stream or downstream• Secure system solution with boot image authentication • No external CPU required for fabric management or SR-IOV sharing•Simple fabric management API for configuration and management over in-band PCIe, UART, TWI or EthernetPeripheral I/O Interfaces• Up to 11 two-wire interfaces (TWIs) with SMBus support • Up to 4 SFF-8485-compliant SGPIO ports • Up to 103 parallel GPIO pins• 10/100 Ethernet MAC port (MII/RMII) (PAX 100x/84x/68xG4)• 16-bit local bus interface with ECC protection • Up to 4 UARTs•JTAG and EJTAG interfaceHigh-Speed I/O• PCIe Gen 4 16 GT/s• Supports optional PCIe-compliant link training andmanual PHY configuration that supports OCuLink cabling, CEM ×16 slots and other interfacesChipLink Diagnostic Tools• Extensive debug, diagnostics, configuration and analysis tools with an intuitive GUI• Access to configuration data, management ca -pabilities and signal integrity analysis tools (such as real-time eye capture)•Connects to device over in-band PCIe or sideband signals (UART and EJTAG)Evaluation KitsThe PM42100-KIT Switchtec Gen 4 PCIe switch evaluation kit is a device evaluation environment that supports multiple interfaces including optical PCIe-compliant link training and manual PHY configuration.Example ApplicationOrdering Information。

教你怎么查看电脑配置

教你怎么查看电脑配置篇一:教你如何看电脑配置现今社会,电脑已经成人们生活中不可或缺的一种工具,几乎所有的办公和生活都需要电脑的帮助,可是种类繁多,琳琅满目各品牌电脑中如何选择适合自己的电脑却已经成为困扰人们的一大难题,下面就上述问题,我给大家做一些摘要.电脑的配置,主要看CPU.显卡.主板.内存.硬盘.显示器等,而笔记本的话就看它的品牌就行了.国外的有HP.apple.松下.东芝等,不过顾客口碑和质量比较硬的是DELL和HP这两个品牌;国产的有:宏基.清华紫光.清华同方.神州.海尔.联想.八亿时空等.软件方面评价标准:1.操作系统:简单举个例子说明一下:电脑的同等配置,运行原版Windows 98肯定比运行原版Windows _P要快,而原版_P肯定又比运行原版的Windows Vista 速度要快,这就说明,同等配置情况下,软件占用的系统资源越大,速度越慢,反之越快.还有,英文原版的操作系统运行英文版程序比运行中文版的程序稳定性及速度都有是关系的.所以,这里特别强调是原版的系统,也就是没有精简过的系统.同理,精简过的Windows _P一般来说,会比原版的_P速度快些,因为精简掉一些不常用的程序,占用的系统资源少了,所以速度有明显提升.2.软件(包括硬件)都可以适当优化,以适合使用者,如:一般办公文员,配置一般的电脑,装个精简版的_P和精简版的Office _就足以应付日常使用了.但如果是图形设计人员,就需要专业的配置,尤其对显卡的要求,所以,升级软件:Microsoft Direct_ 9.0 或以上版本是很有必要的.哪些能软件查看电脑配置:1.EVEREST2.鲁大师+优化大师3.硬件快捕4.cpu-z5.gpu-z新版本都支持最新的酷睿i5.酷睿i7等新品硬件反面评价标准:1.CPU,这个主要取决于频率和二级缓存,频越高.二级缓存越大,速度越快,未来CPU会有三级缓存.四级缓存等,都影响响应速度.2.内存,内存的存取速度取决于接口.颗粒数量多少与储存大小(包括内存的接口,如:SDRAM_3,DDR233,DDR2-533,DDR3-8_),一般来说,内存越大,处理数据能力越强,速度就越快.3.主板,主要还是处理芯片,如:笔记本i965比i945芯片处理能力更强,i945比i9_芯片在处理数据的能力又更强些,依此类推.4.硬盘,硬盘在日常使用中,考虑得少一些,不过也有是有一些影响的,首先,硬盘的转速(分:高速硬盘和低速硬盘,高速硬盘一般用在大型服务器中,如:1__转,__0转;低速硬盘用在一般电脑中,包括笔记本电脑),台式机电脑一般用7_转,笔记本电脑一般用54_转,这主要是考虑功耗和散热原因.硬盘速度又因接口不同,速率不同,一般而言,分IDE和SATA(也就是常说的串口)接口,早前的硬盘多是IDE接口,相比之下,存取速度比SATA接口的要慢些.硬盘也随着市场的发展,缓存由以前的2M升到了8M或更大,就像CPU一样,缓存越大,速度会快些.5.显卡:这项对运行超大程序软件的响应速度有着直接联系,如运行CAD_,3DStudio.3DMA_等图形软件.显卡除了硬件级别上的区分外,也有〝共享显存〞技术的存在,和一般自带显存芯片的不同,就是该〝共享显存〞技术,需要从内存读取显存,以处理相应程序的需要.或有人称之为:动态显存.这种技术更多用在笔记本电脑中.6.电源,这个只要功率足够和稳定性好,也就OK啦.7.显示器:显示器与主板的接口也一样有影响,只是人们一般没有太在乎(请查阅显示设备相关技术资料).详细配置:CPU主流桌面级CPU厂商主要有INTEL和AMD两家.Intel平台的低端是赛扬和奔腾系列,高端是酷睿2(已成功代替酷睿1)_年作为下一代更先进的CPU I7也上市了,在此不久后32NM6核心I9也可能于_年上市.AMD平台的低端是闪龙,高端是速龙,皓龙.最常用的是两者的中低端.INTEL 处理器方面,在中高端有e74_,可以搭配频率更高的DDR2内存,这一点是AMD中高端平台中难以实现的.AMD64bitSP25_+虽然超值,但缺少了对内存双通道的支持,这一点让许多玩家感觉不爽.Intel和AMD市面上的主流配置有两种.一种是Intel配置一种是AMD配置.其主要区别在于cpu的不同,顾名思义Intel配置的cpu是Intel品牌的,AMD配置的cpu是AMD品牌的.产品的市场定位和性能基本相同.价格不同,主要性能倾向有所区别.可根据需要和价位而定.主板配置常用的比较好的牌子其实不止intel,华硕(ASUS).技嘉(GIGABYTE).精英(ECS).微星(MSI).磐正(EPO_).双敏(UNIKA).映泰(BIOSTAR).硕泰克(SOLTEK).捷波(JETWAY).钻石(DFI)这些,还有一些二线牌子象斯巴达克这些也比较好.内存配置常用内存条有3种型号:一)SDRAM的内存金手指(就是插入主板的金色接触部分)有两个防呆缺口,_8针脚.SDRAM的中文含义是〝随机动态储存器〞.二)DDR 的内存金手指只有一个防呆缺口,而且稍微偏向一边,_4针脚.DDR中文含义是〝双倍速率随机储存器〞.三)DDR2的内存金手指也只有一个防呆缺口,但是防呆缺口在中间,240针脚.DDR2SDRAM内存的金手指有240个接触点.内存条_年最新的内存已经升级到DDR3代,DDR3内存向DDR2内存兼容,同样采用了240针脚,DDR3是8bit预取设计,而DDR2为4bit预取,这样DRAM内核的频率只有接口频率的1/8,DDR3-8_的核心工作频率只有1_MHz.主流DDR3的工作频率是_33MHz.在面向64位构架的DDR3显然在频率和速度上拥有更多的优势,此外,由于DDR3所采用的根据温度自动自刷新.局部自刷新等其它一些功能,在功耗方面DDR3也要出色得多.一线内存品牌厂家均推出了自己的DDR3内存,如金士顿.宇瞻.威刚.海盗船.金邦等.在价格上,DDR3的内存仅比DDR2高出几十块,在内存的发展道路上,DDR3内存的前途无限.硬盘配置硬盘按接口来分:PATA这是早先的硬盘接口,_年新生产的台式机里基本上看不到了;SATA这是主流的接口也就是平常说的串行接口,市面上的硬盘普遍采用这种接口;SATAII这是SATA接口的升级版,市面上这种硬盘有是也有,就是不多,主要就是缓存和传输速度的提高;SCSI这是一种在服务器中采用的硬盘接口,它的特点是转动速度快可以达到1__转,这样读写速度就可以加快而且还支持热插拔.显卡配置显卡作为电脑主机里的一个重要组成部分,对于喜欢玩游戏和从事专业图形设计的人来说显得非常重要.民用显卡图形芯片供应商主要包括ATI和nVIDIA 两家.显卡的基本构成GPU全称是Graphic Processing Unit,中文翻译为图形处理器 .NVIDIA公司在发布GeForce 256图形处理芯片时笔记本电脑首先提出的概念.GPU使显卡减少了对CPU的依赖,并进行部分原本CPU的工作,尤其是在3D图形处理时.GPU所采用的核心技术有硬件T l.立方环境材质贴图和顶点混合.纹理压缩和凹凸映射贴图.双重纹理四像素256位渲染引擎等,而硬件T l技术可以说是GPU的标志.显示卡显示卡(Display Card)的基本作用就是控制计算机的图形输出,由显示卡连接显示器,才能够在显示屏幕上看到图象,显示卡有显示芯片.显示内存.RAMDAC 等组成,这些组件决定了计算机屏幕上的输出,包括屏幕画面显示的速度.颜色,以及显示分辨率.显示卡从早期的单色显示卡.彩色显示卡.加强型绘图显示卡,一直到VGA(Video Graphic Array)显示绘图数组,都是由IBM主导显示卡的规格.VGA在文字模式下为7__4_分辨率,在绘图模式下为640_480__色,或3____256色,而此256色显示模式即成为后来显示卡的共同标准,因此通称显示卡为VGA.而后来各家显示芯片厂商更致力把VGA的显示能力再提升,而有SVGA(SuperVGA)._GA(e_tended Graphic Array)等名词出现,显示芯片厂商更把3D功能与VGA整合在一起, 即成为所贯称的3D加速卡,3D绘图显示卡.像素填充率像素填充率的最大值为3D时钟乘以渲染途径的数量.如NVIDIA的GeForce 2 GTS芯片,核心频率为_ MHz,4条渲染管道,每条渲染管道包含2个纹理单元.那么它的填充率就为4_2像素_2亿/秒=_亿像素/秒.这里的像素组成了在显示屏上看到的画面,在8__6_分辨率下一共就有8__6_=480,_0个像素,以此类推1_4_768分辨率就有1_4_768=786,432个像素.在玩游戏和用一些图形软件常设置分辨率,当分辨率越高时显示芯片就会渲染更多的像素,因此填充率的大小对衡量一块显卡的性能有重要的意义.上面计算了GTS的填充率为_亿像素/秒,再看看M__.它的标准核心频率为_5,渲染管道只有2条,那么它的填充率为2_2 像素_1.75亿/秒=7亿像素/秒,这是它比GTS的性能相差一半的一个重要原因.显存显示内存的简称.顾名思义,其主要功能就是暂时储存显示芯片要处理的数据和处理完毕的数据.图形核心的性能愈强,需要的显存也就越多.以前的显存主要是SDR的,容量也不大.而市面上基本采用的都是DDR规格的,在某些高端卡上更是采用了性能更为出色的DDRII或DDRIII代内存(DDRIII已不是更为出色的,而是最差的那种了).两大接口技术AGP接口Accelerate Graphical Port是Intel公司开发的一个视频接口技术标准, 是为了解决PCI总线的低带宽而开发的接口技术.它通过把图形卡与系统主内存连接起来,在CPU和图形处理器之间直接开辟了更快的总线.其发展经历了AGP1.0(AGP1_/2_).AGP2.0(AGP4_).AGP3.0(AGP8_).最新的AGP8_其理论带宽为2.1Gbit/秒.PCI E_press接口PCI E_press是新一代的总线接口,而采用此类接口的显卡产品,已经在_年正式面世.早在_年的春季〝英特尔开发者论坛〞上,英特尔公司就提出了要用新一代的技术取代PCI总线和多种芯片的内部连接,并称之为第三代I/O总线技术.随后在_年底,包括Intel.AMD.DELL.IBM在内的_多家业界主导公司开始起草新技术的规范,并在_年完成,对其正式命名为PCI E_press.理论速度达_Gbit以上,如此在的差距,AGP已经被PCIE打击的差不多了,但是就像PCI取代ISA一样,它需要一定的时间,而且必须是9_以上的北桥才支持PCIE,所以,可以预见PCIE取代AGP还需好长时间.显示器市面上有纯屏显示器和液晶显示器两种.随着液晶显示器的价格下降,已经成为显显示器示器的主流种类.常见的液晶显示器有_寸._寸._寸.24寸等.价格不一,性能差别很大.可根据需要和价位而定.好坏大部分看1)亮度\对比度. 常用5_NIT,对比度1_0左右.2)可视角.IPS屏水平和垂直都可达到_8度.3)是否有亮点\坏点\全黑是否有漏光.4)背光均不均匀.5)功耗. 单屏功耗包括逻辑板部分和背光部分.电脑配置注意事项电脑真正开始进入平常百姓家,对于电脑,DIY是一个很不错的选择,但是对于初接触电脑的朋友来说,双核笔记本电脑组装电脑是一个很复杂的事情,其实组装电脑并不复杂,真正复杂的是选择电脑的配置,对于组装电脑的原则,应秉承〝适用为好〞的原则,因为想追求最好配置,永远也不会追上!下面为大家讲解电脑配置选择过程中应当注意的五点!篇二:教你怎么看电脑配置教你怎么看电脑配置电脑的配置一般是指电脑的硬件配件的高档程度.性价比等,电脑的性能好坏主要决定于:1.CPU:决定运行速度,比如赛扬D2.66G,其中〝2.66G〞是指它的运算速度,但是这里的单位〝G〞跟硬盘的〝G〞不同,不是大小,CPU的〝G〞是〝GHZ〞是频率,就是每秒可以运算2.66G次.2.主板:决定运算速度和稳定性,由于主板应用的芯片不同,可分为很多种,如845.865.895.8_等.3.硬盘:决定读.存数据速度和大小,如80G/7_/0.8M,其中80G是大小,7_是转速,转速决定读存数据的速度,还有0.8M是硬盘的缓存,还决定速度.4. 显卡:决定画面显示效果的好坏与显示速度,它的性能指数一般看它的显存及位数,如人们常说的双_8,就是说内存和位数都是_8的.上面几项最能决定配置高档的程度,其它的就都是次要的,而且现在一般的主板都集成网卡.声卡等,都影响不大!我们该怎么看电脑配置呢,单击〝开始〞→〝程序〞→〝附件〞→〝系统工具〞→〝系统信息〞里面包括硬件版本,性能指数,软件版本信息等,都在里面了!一般来讲,电脑的速度的响应并不能说某单个硬件对它的影响,它们之间需要相互匹配(下同此理),当然,硬件占主要因素,二是软件的优化设置: 硬件部分1.CPU,这个主要取决于频率和二级缓存,频越高.二级缓存越大,速度越快,未来CPU将有三级缓存.四级缓存等,都影响响应速度.2.内存,内存的存取速度取决于接口.颗粒数量多少与储存大小(包括内存的接口,如:SDRAM_3,DDR233,DDR2-533,DDR3-8_),一般来说,内存越大,处理数据能力越强,速度就越快.3.主板,主要还是处理芯片,如:笔记本i965比i945芯片处理能力更强,i945比i9_芯片在处理数据的能力又更强些,依此类推.4.硬盘,硬盘在日常使用中,考虑得少一些,不过也有是有一些影响的,首先,硬盘的转速(分:高速硬盘和低速硬盘,高速硬盘一般用在大型服务器中,如:1__转,__0转;低速硬盘用在一般电脑中,包括笔记本电脑),台式机电脑一般用7_转,笔记本电脑一般用54_转,这主要是考虑功耗和散热原因.硬盘速度又因接口不同,速率不同,一般而言,分IDE和SATA(也就是我们常说的串口)接口,早前的硬盘多是IDE接口,相比之下,存取速度比SATA接口的要慢些.硬盘近年来也随着市场的发展,缓存由以前的2M升到了8M或更大,就像CPU 一样,缓存越大,速度将会快些.5.显卡:这项对运行超大程序软件的响应速度有着直接联系,如运行CAD_,3DStudio.3DMA_等图形软件.显卡除了硬件级别上的区分外,也有〝共享显存〞技术的存在,和一般自带显存芯片的不同,就是该〝共享显存〞技术,需要从内存读取显存,以处理相应程序的需要.或有人称之为:动态显存.这种技术更多用在笔记本电脑中.6.电源,这个只要功率足够和稳定性好,也就OK.7.显示器:显示器与主板的接口也一样有影响,只是人们一般没有太在乎(请查阅显示设备相关技术资料).软件部分:1.操作系统:简单举个例子说明一下:就现在的电脑,同等配置,运行原版Windows 98肯定比运行原版Windwos _P要快,而原版_P肯定又比运行原版的Windows Vista速度要快,这就说明,同等配置情况下,软件占用的系统资源越大,速度越慢,反之越快.还有,英文原版的操作系统运行英文版程序比运行中文版的程序稳定性及速度都有是关系的. 所以,这里特别强调是原版的系统,也就是没有精简过的系统.同理,精简过的Windows _P一般来说,会比原版的_P速度快些,因为精简掉一些不常用的程序,占用的系统资源少了,所以速度有明显提升.2.软件(包括硬件)都可以适当优化,以适合使用者,如:一般办公文员,配置一般的电脑,装个精简版的_P和精简版的Office _就足以应付日常使用了.但如果是图形设计人员,就需要专业的配置,尤其对显卡的要求,所以,升级软件:Microsoft Direct_ 9.0 或以上版本是很有必要的.篇三:怎么看电脑配置?购机必备知识,教你如何查看电脑配置一.如果你已经买了电脑,想知道怎么看电脑配置参数.电脑配置高低,那么可以通过以下的这些方法来了解自己的计算机配置:1.右键〝我的电脑〞--属性(打开系统属性)--〝硬件〞选项下的〝设备管理器〞,里面就是电脑配置了. 但请注意:这里的配置属性是可以通过特殊软件修改的,比如有些JS拿一些打磨品,修改为好的cpu,这种情况会出现二手电脑市场.2.通过查看电脑的〝系统信息〞:a)开始/所有程序/附件/系统工具/系统信息;b)点击〝开始〞-- 〝运行〞,在弹出的对话框中键入〝cmd〞进入系统命令行窗口,在命令行中输入〝systeminfo〞也可以查看系统信息;c)利用〝Direct_诊断工具〞:开始—运行—输入d_diag,也可以看一些.3.借助第三方软件,比如著名的硬件检测软件 Everest (Everest下载地址),它可以详细的显示出电脑硬件的信息,Everest 软件非常的强大,是电脑装机必备的一个软件,Everest 截图如下:其他还有一些比较好的电脑配置信息检测软件比如优化大师.鲁大师等可以用来帮助你了解怎么看电脑配置.另外,专门检测cpu的软件:CPU-Z,专门检测显卡的软件:GPU-Z,专门检测硬盘的软件:HDTune,专门检测内存的软件:memtest,专门检测LCD显示器的软件:Display_,专家检测笔记本电脑电池的软件:BatteryMon 等等,大家可以下载这些软件来获取怎么看电脑配置的知识.如果你还没有买电脑,想提前了解怎么看电脑的配置好坏,那当然要先了解电脑配件的基本硬件常识,比如CPU.主板.内存.显卡.硬盘等.下面介绍怎么看电脑配置的一些前提知识:二)电脑配置一般是指电脑的硬件配件的高档程度.性价比等,电脑的性能好坏主要决定于以下配件:(1)CPU:决定运行速度,如Intel 奔腾双核 E63_(盒)2.8GHz,其中〝2.8G〞是指它的运算速度,但这里的单位〝G〞跟硬盘的〝G〞不同,不是大小,CPU的〝G〞是〝GHZ〞是频率,就是每秒可以运算2.8G次.(2)主板:决定运算速度和稳定性,由于主板应用的芯片不同,可分为很多种,最新的芯片组有下面几种:Intel H55 | AMD 880G | AMD 785G | Intel P55 | AMD 790G_ ,按主板接口:LGA 775 | LGA _66 | LGA _56 | Socket AM2/AM2+ | Socket AM3 等.(3)硬盘:决定读.存数据速度和大小,如希捷 5_GB 7_._ _M(串口/散)ST3,其中5_G是大小,7_是转速,转速决定读存数据的速度,还有_M是硬盘的缓存,也决定速度 .(4)显卡:决定画面显示效果的好坏与显示速度,它的性能指数一般看它的显存及位数,如人们常说的双256,就是说显卡的内存和带宽位数都是256位的.(5)内存: 内存对于操作系统来说很重要,随着越来越多的软件越耗资源,我们目前来说,一般需要让电脑配置2G内存或以上._P系统,1G的内存也够用了,但新的win7操作系统至少需要2G内存.比如金士顿 2GB DDR3 _33.上面几项最能决定配置高档的程度,其它的就都是次要的啦,而且现在一般的主板都集成网卡.声卡等,影响不大!。

ALTERA的PCI_IP Core问答集

PCI Bus ArchitectureQ1 What is PCI? What are the typical applications of a PCI bus?Q2 Who governs the PCI Specification?Q3 What level of participation does Altera have in developing PCI standards?Q4 What does the designer need to know about PCI to design with our IP core?Q5 What is the bandwidth of PCI?Q6 What signal levels does PCI support?Q7 What is a “North Bridge and a South Bridge”?Q8 My customer is asking for Medium Decode. What is this and do we support it?Q9 How does latency affect PCI designs? What factors create the trade off for low latency? What is our latency in the PCI cores?Q10 What is the local side design?Q11 What is “CompactPCI”?Q12 What is “CardBus?”Q13 What is “PMC?”Obtaining the PCI CoreQ14 How does a customer get our PCI cores?Q15 What features are in our version 2.0.0 PCI cores?Device Selection and Constraint FilesQ16 Do some devi ces “work‟ better than others when implementing PCI? What Altera devices work with PCI?Q17 Does a device have …special‟ PCI pins?Q18 How many pins do I need to implement PCI?Q19 What is a constraint file? When does a customer get a constraint file? How does a customer get a constraint file?Q20 Is there a charge for constraint files?Q21 Why do constraint files change from versions to version?HardwareQ22 What types of PCI Boards are available from Altera?Q23 Why doesn‟t the APEX PCI Board fit into my PC?Q24 What‟s the difference between 5V and 3.3V PCI?PCI Bus ArchitectureWhat is PCI? What are the typical applications of a PCI bus?The PCI Local bus is a high performance 32-bit or 64-bit bus with multiplexed address and data lines. The bus is intended for use as an interconnect mechanism between highly integrated peripheral controller components, peripheral add-on boards, and processor/memory systems.Who governs the PCI Specification?The PCI Special Interest Group (PCI-SIG, ) controls the PCI specification. Altera is a member of the PCI-SIG.What level of participation does Altera have in developing PCI standards?As a member of the PCI-SIG, Altera ensures that the specification is appropriate for PLD implementation and submits recommendations to enhance support for PCI. However, as conventional PCI is reaching maturity, it is not expected that the specification will change dramatically. Altera is also actively involved in various other high performance bus interface standards such as HyperTransport, RapidIO, and Araphahoe.What does the designer need to know about PCI to design with our IP core?The PCI Compiler products (pci_mt64, pci_mt32, pci_t64, pci_t32) are high-performance, low latency cores which have raw, native local-side interfaces. Designers should expect to invest some time to understand the PCI protocol to properly design PCI into their system.What is the bandwidth of PCI?Standard PCI performance levels are:What signal levels does PCI support?PCI 2.2 supports both 3.3V and 5V signaling. PCI 2.3 (early 2002) will support 3.3V and 5V signaling, but no 5V-only cards. PCI 3.0 (late 2002) will support 3.3V signaling only.What is a “North Bridge and a South Bridge”?Simply, the host processor-to-PCI bridge is called the North Bridge. The PCI-to-ISA (or expansion bus) bridge is called the South Bridge.My customer is asking for Medium Decode. What is this and do we support it?Slow/Medium/Fast decode refers to the number of clock cycles (3/2/1) latency between a PCI command and the resulting data on the local side. Altera‟s MegaCore and devices support slow decode only.How does latency affect PCI designs? What factors create the trade off for low latency? What is our latency in the PCI cores?Latency through Altera‟s PCI MegaCore core is up to 4 cycles. This depends on the number of registers in the datapath. Registering the datapath may help increase the fmax of customer designs, however, it will increase the latency.What is the local side design?The local side design is typically the user application. There is a reference design included with the PCI Compiler which interfaces PCI through a DMA engine to SDRAM.What is “CompactPCI”?CompactPCI uses the PCI protocol in a VMA form factor.What is “CardBus?”CardBus uses the PCI protocol in a PCMCIA form factor.What is “PMC?”PCI Mezzanine Connector (PMC) is a daughtercard connector for the PCI protocol.Obtaining the PCI CoreHow does a customer get our PCI cores?Altera has 4 native PCI cores:pci_mt64: 64-Bit, 66-Mhz PCI Master/Targetpci_mt32: 32-bit, 66-Mhz PCI Master/Targetpci_t64: 64-bit, 66-Mhz PCI Targetpci_t32: 32-bit, 33-Mhz PCI TargetThese four cores are available through the PCI Compiler, a complete design environment with behavioral simulation models, a PCI bus functional model, source code reference design, and documentation. The PCI Compiler is available for download off the IP MegaStore website: /IPmegastore.Also available is the PCI32 Nios target MegaCore, supporting 32-bit, 33-Mhz PCI with an Avalon local side for use with the Nios embedded processor.What features are in our version 2.0.0 PCI cores?Simple, integrated MegaWizard user interface∙Behavioral simulation models for all 2.0 PCI Cores∙Open source PCI testbench in Verilog & VHDL∙Reference design in open source VHDL∙PCI Compiler includes constraint files for the following device/package combinations:∙EPF10K100EFC484, EP1K100FC484, EP20K400FC672, EP20K400EFC672∙Custom constraint files are available, please contact pci@Device Selection and Constraint FilesDo some devices “work‟ better than others when implementing PCI? What Altera dev ices work with PCI? Device selection for PCI designs requires a careful understanding of the customer‟s requirements. PCI device compliance for 33-Mhz and 66-Mhz systems, 5V and 3.3V systems, as well as the recommended devices list (called the “A-runner l ist”) is available in the Altera PCI Device Selection Matrix on Molson. Customers are highly encouraged to use A-runner device/packages for their PCI designs. A-runner constraint file requests will receive priority in the queue for custom PCI Constraint Files (see below). Does a device have …special‟ PCI pins?Customers should use the pinouts in the Altera PCI Recommended Pin-Out document on Molson for all PCI designs. Any deviations to this pinout will require subsequent modifications to the constraints file, and must be supported by the customer.How many pins do I need to implement PCI?Approximately 60 pins are needed for 32-bit PCI, and 100 pins for 64-bit PCI.What is a constraint file? When does a customer get a constraint file? How does a customer get a constraint file?Due to the strict timing requirements required by the PCI specification, Altera provides constraint files (.acf for MAX+PLUS II, .csf/.esf or .tcl for Quartus II) that are recommended for use by customers to ensure PCI compliant timing. The device speed grades necessary for 66-Mhz or 33-Mhz performance are available in the PCI Device Support Matrix.There is a list of available constraint files on Molson, Sales should use the feedback box at the bottom of this page, include the Device and Core, and the file will be sent back within 24 hours.Custom constraint files are available, please fill out the PCI Constraint File request form on Molson and follow the directions. Custom constraint files typically take between 2-3 weeks turnaround time. A-runners will be prioritized first.Note that constraint files are generated for PCI Compiler and for the pci_mt32, pci_t32, pci_mt64, andpci_t64 MegaCores (there are no constraint files for PCI32 Nios as it supports 33-Mhz only).Is there a charge for constraint files?There is no charge for constraint files.Why do constraint files change from versions to version?Constraint files are dependant on:∙core (pci_mt64, pci_mt32, pci_t32, pci_t64)∙core version (1.3, 1.4, 2.0.0, 2.1.0)∙tool (Quartus/ MAX+PLUS II)∙tool version (1.1, 1.1 SP2, 2.0)∙device (family, density, package, speed grade)These dependencies are because of uncertainties in the manner which Quartus handles node names, constraint syntax, tcl scripting syntax, and timing model changes. A customer can use an old version of a constraint file with the newer version of the core, but they will run into timing violations. The solution is either to fix the existing constraint file to solve all the timing violations, or to request a new constraint file from the factory.HardwareWhat types of PCI Boards are available from Altera?The following boards are available from Altera:∙FLEX 10K200S PCI Development Kit∙APEX PCI Development Kit (available with a 20K400E or 20K1000E device)The above kits come with Windows 98/NT/2000 device drivers and driver source code, a ByteBlasterMV download cable, and a PCI reference design (MegaCore license sold separately).Why doesn‟t the APEX PCI Board fit into my PC?The APEX PCI Board is a full length PCI card and will require a full length slot in a PC to fit.What‟s the difference between 5V and 3.3V PCI?The difference between 5V and 3.3V PCI Hardware is the keying pattern on the PCI edge connector. There are 3 different keying patterns for PCI: 5V only, 3.3V only, and a “Universal” card which supports 5V and 3.3V levels.。

HPE ProLiant DL380 Gen10 服务器用户指南

HPE ProLiant DL380 Gen10 服务器用户指南摘要本文档适合那些安装、管理服务器和存储系统以及排除其故障的人员使用。

Hewlett Packard Enterprise 假定您有资格维修计算机设备,并经过培训能够识别高压带电危险品。

部件号:868990-AA4出版日期:2018 年12 月版次:4©Copyright 2017, 2018 Hewlett Packard Enterprise Development LP通知本文档中包含的信息如有更改,恕不另行通知。

随Hewlett Packard Enterprise 产品和服务提供的明确保修声明中阐明了此类产品和服务的全部保修服务。

此处的任何内容都不应视作额外的担保信息。

对于本文档中包含的技术或编辑方面的错误或疏漏,Hewlett Packard Enterprise 不承担任何责任。

保密的计算机软件。

必须具有Hewlett Packard Enterprise 颁发的有效许可证,方可拥有、使用或复制本软件。

按照FAR 12.211 和12.212 的规定,可以根据供应商的标准商业许可证授权美国政府使用商用计算机软件、计算机软件文档以及商业编号的技术数据。

单击指向第三方网站的链接将会离开Hewlett Packard Enterprise 网站。

Hewlett Packard Enterprise 无法控制Hewlett Packard Enterprise 网站之外的信息,也不对这些信息承担任何责任。

目录组件标识 (8)前面板组件 (8)前面板LED 指示灯和按钮 (10)UID 按钮功能 (13)前面板LED 指示灯电源故障代码 (13)Systems Insight 显示屏LED 指示灯 (14)Systems Insight 显示屏组合LED 指示灯说明 (15)后面板组件 (17)后面板LED 指示灯 (17)主板组件 (19)系统维护开关说明 (20)DIMM 标签识别 (21)DIMM 插槽位置 (22)NVDIMM 识别 (22)NVDIMM 二维码 (23)识别NVDIMM LED 指示灯 (24)NVDIMM-N LED 指示灯组合 (24)NVDIMM 功能LED 指示灯运行模式.....................................................................24 处理器、散热片和插槽组件 (25)驱动器 (25)SAS/SATA 驱动器组件和LED 指示灯 (26)NVMe SSD LED 指示灯定义 (26)uFF 驱动器组件和LED 指示灯 (28)风扇托架编号 (29)驱动器盒识别 (29)驱动器托架编号 (31)驱动器托架编号:Smart Array 控制器 (31)驱动器托架编号:SAS 扩展卡 (33)驱动器托架编号:NVMe 驱动器 (35)uFF 驱动器托架编号 (36)转接卡组件 (37)带集成备用电池装置组件和LED 指示灯的HPE Flex 插槽电源 (41)检查备用电池电量 (41)H PE 12G SAS 扩展卡端口编号 (42)H PE Smart Array P824i-p MR Gen10 控制器 (42)操作 (44)打开服务器电源 (44)关闭服务器电源 (44)从机架中拉出服务器 (44)从机架中卸下服务器 (45)使用理线臂固定电缆 (45)卸下检修面板 (46)安装检修面板 (47)卸下风扇笼 (47)安装风扇笼 (48)。

基于WDF的PCI—E驱动设计和实现

基于WDF的PCI—E驱动设计和实现-权威资料本文档格式为WORD,若不是word文档,则说明不是原文档。

最新最全的学术论文期刊文献年终总结年终报告工作总结个人总结述职报告实习报告单位总结【摘要】简要介绍了基于PCI-E的数据采集系统构成、开发工具选择、WDF对象模型及特点,重点介绍了WDF开发PCI-E驱动程序的主要方法步骤、DMA方式进行数据传输和事件通知的实现方法。

经过现场实际测试,该系统高效稳定可靠,所开发的驱动程序完全可以实现数据的高速传输。

【关键词】PCI-E总线;WDF模型;驱动程序;直接存储器访问1.引言PCI-Express是一种最具发展前景的总线和接口标准,早在2001年的春季英特尔开发者论坛(IDF)上,Intel公布了第三代I/O互联技术(3GIO),用以取代PCI总线和多种芯片的内部连接。

2001年底,包括Intel、AMD、Dell、IBM等20多家业界主导公司起草了新技术的规范,对其正式命名为PCI Express,简称PCI-E,代表着下一代I/O接口标准。

PCI-E采用与全双工通信技术类似的双通道传输模式,具有速度快、点对点串行传输,是两端设备可以独享带宽,扩展灵活方便,支持热插拔以及服务质量(QoS)的优点。

PCI-E总线具有极高的传输速率,规格从x1通道到x32通道,其中x1通道双向传输速度为5Gbps,而PCI-E 3.0规范中x32通道双向传输速度可达320Gbps,满足目前绝大部分场合的需要。

PCI-E设备连接到计算机系统必须有相应的驱动程序才能在计算机系统上正常工作。

PCI-E驱动程序的优劣直接关系到整个系统的性能和稳定性,因此,设计和开发稳定高效的PCI-E驱动程序具有重要意义。

2.硬件系统在设计PCI-E驱动程序之前,先对要控制的硬件系统和工作流程做简要的分析介绍。

硬件系统的基本结构框图如图1所示。

这是一套自行开发的基于PCI-E接口的分布式数据采集系统,主要实现了分布式高速数据采集及传输。

PCIE基础知识

PCIe总线概述随着现代处理器技术的发展,在互连领域中,使用高速差分总线替代并行总线是大势所趋。

与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线,完成之前需要许多单端并行数据信号才能达到的总线带宽。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe 总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

PCIe总线的基础知识与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。

PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。

PCIe 总线使用的层次结构与网络协议栈较为类似。

1.1 端到端的数据传递PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。

其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。

该电容也被称为AC 耦合电容。

PCIE接口介绍-修改

PCIe接口介绍PCIe接口简介PCIe(Peripheral Component Interconnect Express)总线的诞生与PC(Personal Computer)的蓬勃发展密切相关,是由PCISIG (PCI Special Interest Group,主要是intel)推出的一种局部并行总线标准,主要应用于电脑和服务器的主板上(目前几乎所有的主板都有PCIe 的插槽),功能是连接外部设备(如显卡、存储、网卡、声卡、数据采集卡等)。

PCI总线规范最早在上世纪九十年代提出,属于单端并行信号的总线,目前已淘汰,被PCIe总线(在2001年发布,采用点对点串行连接)替代。

目前PCIe的主流应用是3.0,4.0还没正式推出,但标准已经制定的差不多了。

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Quality of Service)问题。

每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

不相同。

PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10 bit中含有8 bit的有效数据;而V3.0规范使用128/130b编码方式,即在PCIe链路上的130 bit中含有128 bit的有效数据。

实际使用中,PCIe无法一直维持在峰值传输状态,因为编码方式、链路管理消耗、存储时间延迟等原因,一般只有50%~60%的效率。

PCIe接口原理连接方式PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图一。

代码主板芯片级维修论坛

代码Awrard(厂家)AMI(厂家)Phoenix/Tandy3000(厂家)00同FF 同FF 同FF01 处理器测试1,处理器状态核实,如果测试失败循环是无限的。

试换CPU,查CPU跳线或CPU设置处理器寄存器的测试即将开始,非屏蔽中断即将停用。

排除方法同左CPU寄存器测试正在进行或都失败。

排除方法同左02 确定诊断的类型(正常或制造)。

如果键盘缓冲器含有数据就会失效。

试查主板中与键盘相关电路及键盘本身使用非屏蔽中断:通过延迟开始。

查主板和CPUCMOS写入/读出正在进行或者失灵。

试查主板电池03清除8042键盘控制器,发出TEST-KBRD命令(AAH)。

查键盘内部电路及软件通电延迟已完成ROM BIOS检查部件正在进行或者失灵。

查主板电池04使8042键盘控制器复位,核实TESTKBRD。

查键盘接口电路键盘控制器软复位/通电测试,查键盘控制部分电路可编程间隔计时器的测试正进行或失灵。

查主板中与定时器相关的电路05如果不断重复制造测试1至5,可获得8042控制状态。

查主板键盘控制电路已确定软复位/通电;妈将启动ROM。

查主板ROM芯片及支持电路DMA初始准备正在进行或失灵。

查主板中与DMA有关的芯片及其外围电路06 使电路片作初始准备,停用视频,奇偶性,DMA电路片以及清除DMA电路片,所有页面寄存器和CMOS寄存器的工作。

已启动ROM计算ROM BIOS检查总和,以及检查键盘缓冲器是否清除。

查主板ROM芯片及其支持电路DMA初始页面寄存器读/写测试正进行或失灵。

查主板中与DMA有关芯片及其外围电路查主板中与DMA相关的电路07处理器测试2,核实CPU 寄存器的工作。

查CPU是否插好,或CPU坏,或CPU跳线等设置出错ROM BIOS检查总和正常,键盘缓冲器已清除,向键盘发出BAT(基本保证测试)命令。

查主板中键盘接口电路或更换键盘08 使CMOS计时器作初始准备,正常地更新计时器的特环。

如何进行 PCI Express 的一致性测试和分析

如何进行PCI-Express的一致性测试和分析泰克(中国)有限公司高级应用工程师 曾志摘要:PCI-Express串行标准越来越广泛地在计算机行业应用,作为芯片与芯片之间,系统与插卡之间,系统与系统之间的高速连接,由于不同设备可能由不同的厂商提供,为了保证设备之间可靠的互联互通,必须对其接口进行一致性测试。

同时高速串行信号容易对系统内部或者外部产生EMI辐射和干扰,PCIE标准定义了SSC(扩频时钟)来减少EMI,但是SSC如果使用不当的话也可能会影响接口互联的可靠性。

本文介绍如何根据PCIE的标准及其众多的子标准定义的测试规范和分析方法进行一致性测试,同时讨论如何对SSC(扩频时钟)进行验证和分析。

关键词:PCI-Express,PLL(锁相环),时钟恢复,眼图,抖动,模板,SSC(扩频时钟)。

引言:随着计算机及通讯设备的性能要求越来越高,传统的低速的并行总线如PCI等的数据吞吐量已经无法满足要求,PCI Sig组织联合了一线的芯片厂商和测试测量仪器厂商制定了PCI-Express Rev1.0的规范,将串行数据速率提高到2.5Gbps,数据带宽提高到32个Lane即80Gbps,而且明确要求对宣称支持该规范的芯片和接口进行一致性测试,在PCI-Express Rev1.0A的规范实施后,PCI Sig 又对规范进行了更新,Release了PCI-Express Rev1.1的规范,对抖动测试方法作了修改。

同时,对于PCI-Express在不同环境上的实现,又制定了相应的子规范,如Base,CEM,Express module,cable 等。

最近,PCI Sig组织在讨论和制定PCIE 2.0的规范,将数据速率提高到5Gbps.并制定了相应的眼图和抖动分析方法. PCI-Express规范的不同版本及其子规范有合起来有9个以上,往往使测试工程在对不同的PCIE实现选择何种标准无所适从。

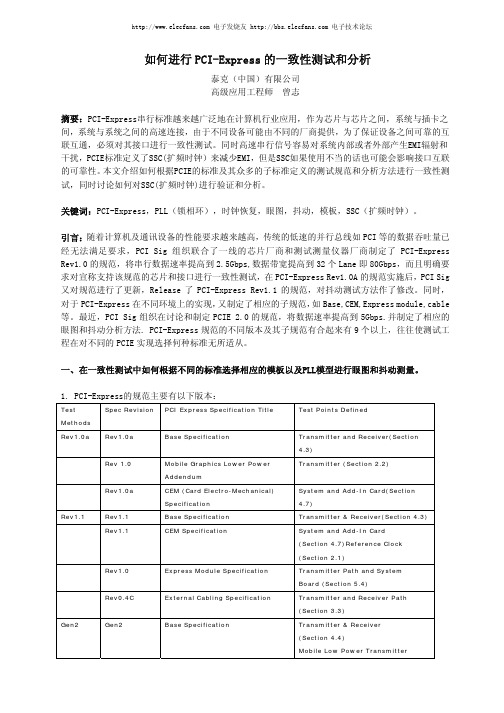

一、在一致性测试中如何根据不同的标准选择相应的模板以及PLL模型进行眼图和抖动测量。

pcie gen4与gen3 编码方式 -回复

pcie gen4与gen3 编码方式-回复题目: PCIe Gen4与Gen3编码方式摘要: 本文将深入探讨PCIe Gen4和Gen3的编码方式。

首先,我们将介绍PCIe架构以及其在计算机系统中的重要性。

然后,我们将详细讨论PCIe Gen4和Gen3的编码方式,并比较它们之间的差异。

最后,我们将讨论这些编码方式对数据传输速度和性能的影响。

通过本文,读者将对PCIe Gen4和Gen3的编码方式有一个全面的了解。

引言PCIe(Peripheral Component Interconnect Express)是一种计算机总线标准,用于在计算机系统中传输数据。

它在现代计算机中起着至关重要的作用,可以连接各种外部设备,如显卡、网卡和存储设备等。

PCIe使用高速的串行通信接口,依靠编码方式来确保数据的准确传输。

本文将关注PCIe Gen4和Gen3的编码方式,这两个版本都是较为常见的。

PCIe Gen4编码方式PCIe Gen4是目前最新的PCIe标准,提供了比之前的版本更高的带宽和速度。

它采用了64b/66b的编码方式,其中每个时钟周期传输64位数据,并使用2位保护码来实现错误检测和纠正。

64b/66b编码方式是一种带有数据保护功能的编码方式。

它通过将每个64位的数据块分为66位,并对其中的两位进行保护码计算。

这种编码方式允许在数据传输过程中检测和修复少量的错误。

此外,64b/66b编码方式还提供了对时钟恢复的支持,通过在数据流中插入控制字符来保证接收端可以正确地解析数据。

PCIe Gen3编码方式PCIe Gen3是较新的PCIe标准之一,在许多计算机系统中仍然被广泛使用。

与PCIe Gen4相比,它的带宽和速度较低。

PCIe Gen3采用了128b/130b的编码方式,每个时钟周期传输128位数据,并使用2位保护码。

128b/130b编码方式是一种更高效的编码方式,它比64b/66b编码方式多传输了更多的数据位。

PCIe当今的发展状况如何?

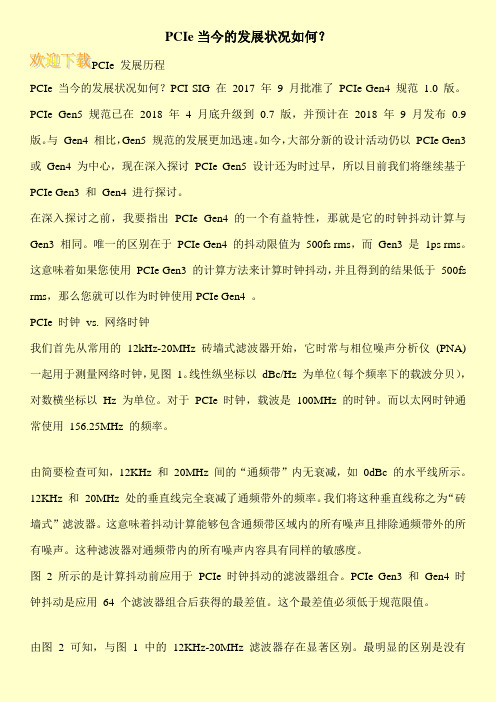

PCIe当今的发展状况如何?PCIe 发展历程PCIe 当今的发展状况如何?PCI SIG 在2017 年9 月批准了PCIe Gen4 规范1.0 版。

PCIe Gen5 规范已在2018 年4 月底升级到0.7 版,并预计在2018 年9 月发布0.9 版。

与Gen4 相比,Gen5 规范的发展更加迅速。

如今,大部分新的设计活动仍以PCIe Gen3 或Gen4 为中心,现在深入探讨PCIe Gen5 设计还为时过早,所以目前我们将继续基于PCIe Gen3 和Gen4 进行探讨。

在深入探讨之前,我要指出PCIe Gen4 的一个有益特性,那就是它的时钟抖动计算与Gen3 相同。

唯一的区别在于PCIe Gen4 的抖动限值为500fs rms,而Gen3 是1ps rms。

这意味着如果您使用PCIe Gen3 的计算方法来计算时钟抖动,并且得到的结果低于500fs rms,那么您就可以作为时钟使用PCIe Gen4 。

PCIe 时钟vs. 网络时钟我们首先从常用的12kHz-20MHz 砖墙式滤波器开始,它时常与相位噪声分析仪(PNA) 一起用于测量网络时钟,见图1。

线性纵坐标以dBc/Hz 为单位(每个频率下的载波分贝),对数横坐标以Hz 为单位。

对于PCIe 时钟,载波是100MHz 的时钟。

而以太网时钟通常使用156.25MHz 的频率。

由简要检查可知,12KHz 和20MHz 间的“通频带”内无衰减,如0dBc 的水平线所示。

12KHz 和20MHz 处的垂直线完全衰减了通频带外的频率。

我们将这种垂直线称之为“砖墙式”滤波器。

这意味着抖动计算能够包含通频带区域内的所有噪声且排除通频带外的所有噪声。

这种滤波器对通频带内的所有噪声内容具有同样的敏感度。

图2 所示的是计算抖动前应用于PCIe 时钟抖动的滤波器组合。

PCIe Gen3 和Gen4 时钟抖动是应用64 个滤波器组合后获得的最差值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

//------------------------------------------------------------------------------------------------------------------------

成存储器或IO读写事物,访问外部设备的存储器或IO空间。由于我们只讨论x86和windows系统,所以使用IO指令访问外设。而访问机制

一般有两种,即: 1.PCI兼容的配置访问机制; 2.PCI Express增强的配置机制 不过,使用PCI兼容的配置访问机制只能访问到功能

的4KB配置空间中的PCI兼容配置寄存器区(256B),PCI Express增强配置访问机制可以访问到整个4KB配置空间。两者访问方法的不同之

//2 配置空间问题

继续配置空间:提出一个问题,配置空间是不是一般是我们在FPGA例化pcie核的时候分配的BAR0?或者说是BAR0的一部分呢?

继续:配置空间的层次以及大小, 在PCI Express系统中,总线号(8位)、设备号(5位)和功能号(3位)组成了每一功能的16位地址,