跨导放大器的设计考虑

具有恒定跨导的RAIL-TO-RAILCMOS运算放大器设计指导

具有恒定跨导的Rail-to-Rail CMOS运算放大器设计指导陈斯(徐州师范大学物理系电子科学教研室)注:文章中有很多关于MOS方面的基础知识,可能对于你们来说比较陌生,可以去找一些关于这方面的书籍看看。

下学期我会给你们做专门的讲解的。

你们先作个大概的了解,并确定具体的方向。

1引言近年来,随着集成电路工艺尺寸的不断减小,低电压的发展趋势越来越快。

下图为半导体工艺与电源电压的关系。

从图中可以看出,电压随着工艺最小尺寸的减小而不断降低。

电压减小的原因是因为尺寸的减小导致了器件的击穿电压的减小。

此外数字电路的功耗正比于电源电压的平方,因此,为了减小功耗必须降低电源的电压。

但是从模拟电路设计者来看,电源电压的减小会导致模拟信号动态范围的减小。

如果MOS管的域值电压随着电源的降低而等比减小的话,动态范围就不会受到严重的影响。

但由于数字逻辑的原因,域值电压不能大幅地减小,所以低电压会对电路的设计带来一定的影响。

2 一般原理在模拟电路和数模混合电路中,对于低电压的追求逐渐成为集成电路的一种时尚。

然而低电压导致了运算放大器输入共模范围的降低,传统的PMOS或NMOS差分对输入已不能满足大的输入共模范围的要求。

为解决这一瓶颈,rail-to-rail运算放大器随之而产生。

通常的Rail-to-Rail运放采用两级结构,运放的输出级可以采用简单的class-A或class-AB来实现,难点在于输入级的设计。

输入级一般采用PMOS和NMOS并联的互补差分结构,但其跨导在整个共模输入范围内变化两倍。

这种跨导的变化不仅影响环路的增益, 也会影响运放的频率补偿。

同时,由于输入信号是rail-to-rail ,具有很高的信噪比,因此要求整个rail-to-rail 运放的输入级保持恒定的跨导(g m )。

一般来说,运算放大器的输入级都采用差分放大器的输入模式。

在CMOS 工艺中,差分放大器可以通过PMOS 或NMOS 的差分对来实现。

(完整word版)跨导运算放大器的设计

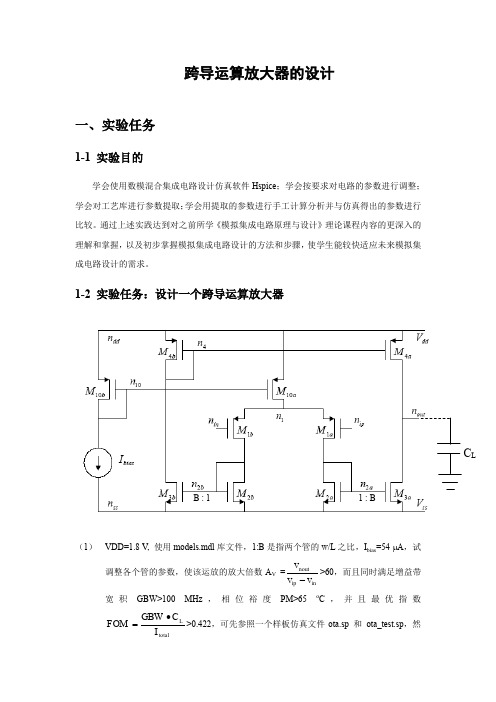

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

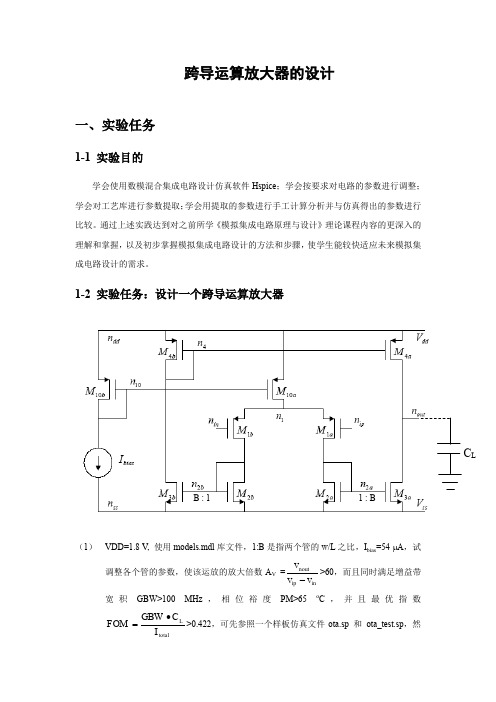

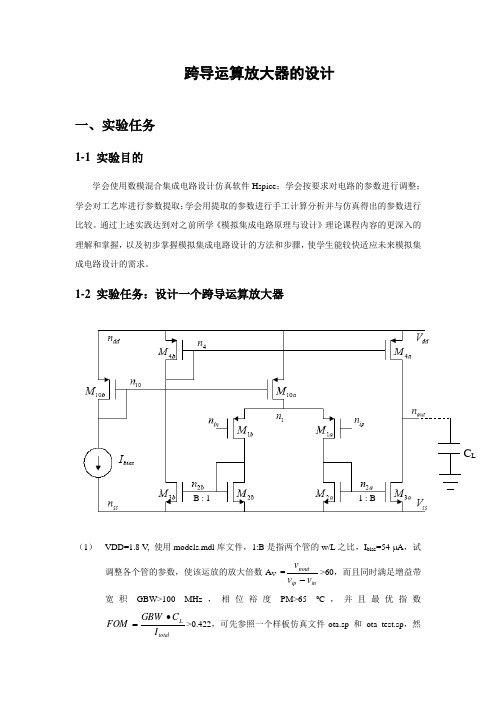

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

跨导放大器的设计考虑

跨导放大器的设计考虑

采用电压反馈放大器(VFA) 来设计一个优质的电流到电压(跨导放大器) 转换器是一项重大的挑战。

本文将会探讨一个用345 MHz 的轨到轨输出,电压反馈放大器(例如是美国国家半导体的LMH6611)来实现的简单TIA 设计,并提供TIA 设计所必需的信息,讨论TIA 的补偿和性能结果,以及分析TIA 输出端的噪声。

由于LMH6611 工作在较大增益(RF) 时,其输入偏置电流便较低,故可容许电路工作在低光强度的条件下。

运算放大器反向端上的总电容(Cr) 包括光二极管的电容(CPD) 和输入电容(CIN),Cr 在电路稳定性方面扮演着很重要的角色,而稳定性则取决于这个电路的噪声增益(NG),其定义为:

为了保持稳定性,需要加入一个反馈电容(CF) 与RF 并联以便在噪声增益函数中的fP 处构建一个极点。

通过选用合适容值的CF,便可使噪声增益的斜坡变平从而获取最佳的性能,这样使得频率fP 点的噪声增益等于运算放大器的开环增益。

这个在AOL 和噪声增益交点以上的噪声增益斜率平坦化会得到一个45 度的相位余量(PM)。

这是因为在交点处,fP 点的噪声增益极点会贡献一个45 度的相位超前,因此给出了一个45 度的相位余量(假设fP 和fZ 之间最少有10 MHz 的距离)。

公式3 和4 理论上可计算出CF 的最优值和期望的-3 dB 带宽:。

跨导放大器的分析与设计2

增加第一级或者第二级的输出阻抗:通过特定的技 术来提高输出阻抗(Cascode技术)

采用Cascode技术的单级OTA --Telescopic OTA

单纯考察OTA的特性,应用在反馈环路中的分析 同两级基本OTA

小信号特性

输出阻抗为:

Rout (gm4 Aro4 Aro4 ) || (gm2 Aro2 Aro2 )

偏置VBB2的产生电路

VBB2 VGS1A,2 A Vin,CM Vtn1,2

VBB2 Vx Vov1,2 VGS1A,2 A Vx Vt 2Vov

采用类似于低压电流镜中偏置的设 计方案,MB1工作于线性区,尺寸为 MB2尺寸的1/3,为留有设计余量, 一般取为1/5,可采用晶体管单元串 联来实现,避免MB1的宽度太小gm1,2 Rout

具有与两级基本OTA相似的增 益,在某些场合可以作OTA使 用:telescopic OTA(单级放大 器)

输出极点是主极点

p1

GBW Av

1 Rout Cout

输入共模范围

共模范围:所有晶体管都工作于饱 和区时输入共模电压的范围,这时 放大器具有最大的小信号增益

跨导放大器的分析与设计(2)

提要

两级基本OTA存在的问题及改善办法 Cascode技术

单级放大器

➢Telescopic ➢折叠Cascode技术 ➢单级OTA的频率补偿 ➢Gain Boosting:有源Cascode技术

共模反馈环路

两级基本OTA存在的问题

存在的问题

OTA低频电压增益:(gmro)2 Miller补偿,稳定性要求非主极点位于离单位

采用Cascode技术的单级OTA --折叠Cascode技术

跨导放大器设计实例

模拟集成电路实验——跨导放大器设计实验报告学院:电信学院班级:微电子23班姓名:游晓东学号:2120503069一、设计指标二、电路结构确定电路结构的原因: ① 根据设计指标② 电路结构对称,匹配度高,,Offset CMRR 性能指标好③ 电路稳定性好,只有一个主极点④ 该电路为差分输入,单端输出,共模抑制比大,输出共模点较稳定三、电路原理概述该电路主要由三部分组成:带隙基准电流源、偏置电路、跨导放大器9~21M M 构成一个跨导放大器,其中13M 为尾电流源,向输入的差动对管提供电流偏置。

11,12M M 为输入差分对管,将小信号电压转换成小信号电流。

9,14M M 和10,17M M 为两个对称的电流镜,比例复制小信号电流。

14,15M M 与16,17M M 为共源共栅结构,可以提高输出阻抗和开环增益。

18,19,20,21M M M M 为低压共源共栅电流镜,可以作为单端输出并且提高输出摆幅。

0~8M M 构成偏置电路部分,为跨导放大器提供偏置电流。

22~34,0~2,0~2M M Q Q R R 构成带隙基准电流源部分,为电路提供基准电流源。

四、设计过程1. 分配电流根据静态电流250A μ限制,分配带隙基准电流源部分20A μ,偏置电路部分10A μ(其中每一路2A μ),跨导放大器部分210A μ。

分配14,17M M 的偏置电流14M I 时主要考虑三个指标:,,GBW SR GMGM 要求900~1100/A V μ,因此GM 取1000/A V μ。

由于11GM B gm =⋅,B为14,9M M 的偏置电流之比,因此111000/B gm A V μ⋅= (1)GBW 要求大于3MHZ 。

112LB gm GBWC π⋅=⋅,因此11566/B gm A V μ⋅> (2)SR 要求大于3/V S μ。

92M LB I SRC ⋅=,因此9290M B I A μ⋅> (3)由于9112M ODI gm V =,若OD V 取0.2V ,则由(1)得9100M B I A μ⋅=,由(2)得956.6M B I A μ⋅>,由(3)得945M B I A μ⋅>。

跨导放大器的分析与设计1

流进或者流出输入端 的电流为0

运算放大器与跨导放大器(1)

运算放大器与跨导放大器(2)

运算放大器(Opamp) 跨导放大器(OTA)

通用放大器 电压控制电压源(VCVS) 低输出阻抗

能驱动电阻性负载或电容性 负载

OTA+Buffer

缓冲器增加了电路的复杂度 和功耗

差分对Cgd的Miller效应消除办法:

使用Cascode结构(可提高增益) 使用中和(Neutralization)电容

提要

跨导放大器的基本概念 单级跨导放大器 两级OTA的基本特性 两级OTA的频率补偿:Miller补偿 反馈型OTA中的噪声 两级OTA的设计 阶跃响应:线性建立过程 阶跃响应:放大器中的压摆问题

单级OTA:最大输出摆幅

调节输入/输出共模电 平,使得可获得的输 出电压摆幅达到最大

使用长沟道平方律方 程很容易确定优化的 输入/输出共模电平

受到短沟道效应的影 响

差分 摆幅

单端 摆幅

SW

2 min[Vout(max) Voc ,Voc Vout(min) ]

实际电路中输入/输出 共模电平是由跨导放 大器的接口电路(前 后级电路)决定的

跨导放大器的分析与设计(1)

提要

跨导放大器的基本概念 单级跨导放大器 两级OTA的基本特性 两级OTA的频率补偿:Miller补偿 反馈型OTA中的噪声 两级OTA的设计 阶跃响应:线性建立过程 阶跃响应:放大器中的压摆问题

理想运算放大器

差分输入端 差模电压增益为无穷

大 输入阻抗为无穷大 输出阻抗为0

单级OTA:输出摆幅

Vout(max) VDD Vminp

单

端

Vout(min) (Vic Vt Vov ) Vminn

第八讲 跨导运放的分析与设计讲解

由于零点的作用,相位裕度 从60多度减小至39度!

交流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

分析miller补偿效应

.probe ac v(vo1) v(vo) vp(vo)

.op

*.dc v_vdc 2.48 2.495 0.0001

失调分析

在MOS晶体管的参数中考虑失配 例:原有的 W=12u, M=2 修改为 W=‘12u+12u*0.04u*alfa/sqrt(2*12um*5um)’ M=2 delvto=‘12.5n*alfa/sqrt(2*12um*5um)’ 这里alfa为(0,1)高斯分布变量 依次将网表的内容按照上面的方法修改

.lib ‘LIB_PATH\csmc.lib’ tt

.unprot

.option post probe

.probe dc v(vo1) v(vo)

.op .dc v_vdc 2.48 2.495 0.0001

精扫

*.trans 10ns 200ns 20ns 0.1ns

*.ac dec 10 1k 100meg $sweep rzv 0 2k 0.2k

耗,因此可查得电路功耗为2.47mW • 对于MOS管,注意各参量的含义:region、id、vgs、

vds、vth、vdsat、gm、gmb、gds……可查得流过 M_U3的偏置电流为149.8uA,并注意到M_M3的 region为Linear

直流扫描

Ota simulation

.prot

.lib ‘LIB_PATH\csmc.lib’ tt

CMOS恒跨导运算放大器设计

(2)跨导运算放大器模型 ● OTA的符号如图所示,它有两个输入端,一个输出端,一个控制端。符号上的 “+”号表示同相输入端,“一”表示反相输入端, I O 是输出电流, I B 是偏置电流,即外 部控制电流。 I O G(V V ) GVid ● OTA的传输特性用下列方程式描述:

lim Rnn ( ) 0 此外,若时延足够大,则

所以时延足够大时,只输出信号自身的相关函数 R( ) Rss ( )

三、互相关检测

1、基本原理:

若已知发送信号的重复周期或频率,就可在接收端发 出一个与发送信号周期相同的“干净的”重复周期信 号,称为本地信号,将它与混有噪声的输入信号进行 互相关,即可除去噪声的影响,提高电路的抗干扰能 力。

OTA的小信号理想模型

2 CMOS恒跨导运算放大器的设计

(1)设计指标

● 工作电压: 2.7V

● 直流开环增益:90dB

● 相角裕度: 70 ● 增益带宽积:1.4MHz ● 负载电容:25pF

(2)运算放大器原理框图

● 输入级采用互补差分对结构, 使共模输入电压范围达到轨到轨,

通过3倍电流镜控制尾电流使输

U s1 (t )

窄带滤波 放大 输入信号

U 1 (t )

×

U 2 (t ) 参考信号

U O (t )

锁定放大器原理

锁定放大器理论推导

设输入信号: X (t ) S (t ) N (t )

A sin(t ) N (t )

S (t ) 为有用信号,A为其幅值, 角频率为,初相角为 其中, N (t ) 为随机噪声,

由上式可以得到输出阻抗:Zout ( A 1) gmro1ro2 而单共源共栅电路的输出阻抗为: gmro1ro2 电路的小信号分析表明输出阻抗 Z out值增大。

(完整word版)跨导运算放大器的设计

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 oC ,并且最优指数totalLI C GBW FOM ∙=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

高增益跨导性运算放大器设计

10212020059 赵琦

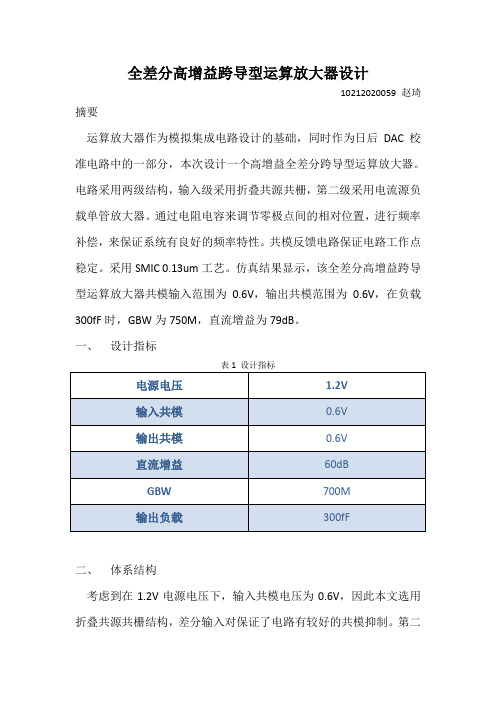

摘要 运算放大器作为模拟集成电路设计的基础,同时作为日后 DAC 校 准电路中的一部分,本次设计一个高增益全差分跨导型运算放大器。 电路采用两级结构,输入级采用折叠共源共栅,第二级采用电流源负 载单管放大器。通过电阻电容来调节零极点间的相对位置,进行频率 补偿,来保证系统有良好的频率特性。共模反馈电路保证电路工作点 稳定。采用 SMIC 0.13um 工艺。仿真结果显示,该全差分高增益跨导 型运算放大器共模输入范围为 0.6V,输出共模范围为 0.6V,在负载 300fF 时,GBW 为 750M,直流增益为 79dB。 一、 设计指标

GBW

gm

g m1、 2 2 Cc

2I Vgs Vth

其中补偿电容粗略估算,留有余量取 300fF。 Vgs Vth 取 0.2V。可以粗

略估算 I 为 120uA,本设计中取为 150uA。 通过简单 miller 补偿,主极点

P 1

C 为 miller 补偿电容, 次级点

表 1 设计指标

电源电压 输入共模 输出共模 直流增益 GBW 输出负载

1.2V 0.6V 0.6V 60dB 700M 300fF

二、 体系结构 考虑到在 1.2V 电源电压下,输入共模电压为 0.6V,因此本文选用 折叠共源共栅结构,差分输入对保证了电路有较好的共模抑制。第二

级采用了电流源负载的单管放大器。电阻 R2 和电容 C 用来调节零极 点的位置进行频率补偿,以保证系统的稳定性。基本原理是增加一个 左半平面 (LHP) 零点来抵消次级点对相位的影响, 同时会把主极点推 向原点。最左边部分是共模反馈电路。

50 0 -50

-100 0 10

跨导运算放大器的设计

跨导运算放大器的设计一、实验任务1-1 实验目的学会使用数模混合集成电路设计仿真软件Hspice ;学会按要求对电路的参数进行调整;学会对工艺库进行参数提取;学会用提取的参数进行手工计算分析并与仿真得出的参数进行比较。

通过上述实践达到对之前所学《模拟集成电路原理与设计》理论课程内容的更深入的理解和掌握,以及初步掌握模拟集成电路设计的方法和步骤,使学生能较快适应未来模拟集成电路设计的需求。

1-2 实验任务:设计一个跨导运算放大器(1) VDD=1.8 V , 使用models.mdl 库文件,1:B 是指两个管的w/L 之比,I bias =54 μA ,试调整各个管的参数,使该运放的放大倍数A V =inip noutv v v ->60,而且同时满足增益带宽积GBW>100 MHz ,相位裕度PM>65 o C,并且最优指数totalLI C GBW FOM •=>0.422,可先参照一个样板仿真文件ota.sp 和 ota_test.sp ,然C LB : 1 1 : B后自己调整;(2) 仿真各指标满足要求后,自行设计参数提取电路进行电路中的各个部分晶体管的参数提取,然后进行手算分析。

将分析结果与实际仿真结果进行比较; (3) 尽你所能调整除 VDD 之外的其他参数,包括I bias 来提高FOM ,最高能提高到多少? 最后提交一个word 电子文档,包括参数提取过程、手算分析过程、电路图(带管子参数)、仿真波形图、及相关详尽的说明。

二、实验内容2-1 问题12-1-1参数分析•增益Av由out m V BR g A 10=,m g = 34||out o o R r r = ,333,EN o d V L r I =444EP o d V Lr I =B= (W 3/L 3)/(W 2/L 2)则43432233111//)/(2d d PN EN d ox out m v I I L L V V L W L W I L W uC BR g A ⨯⨯==所以,可通过增大M1的宽长比,增大L4的大小,以及提高M3和M2的沟道宽长比之比B 来提高放大增益V A 。

跨导运算放大器原理与应用

realize independence

adjustment

oscillator

about frequency and condition of oscillation.All filter

and

proposed

aro

all

proved

by

the

PSpiee

simulation,the

simulation results have been consistent witll the theoretical results.

1、保密口,在……年解密詹适用本授权书。

2、不保密翅。

(请在以上相成方框内打“ ̄/”)

作者签名:

曾毳羡

,

嚣巅:砷每参曩三鑫

导师签名:莨长五日期:弧心产6月罗日

f

跨导运算放大器原理与应用

第一章绪论 引言

世界上第一块集成电路,是1958年美国德克萨斯仪器公司的基 尔比和仙童公司的诺伊斯同时制作出来的(中国的第一块集成电路是

mode

and

circuit and OTA are briefly introduced.Secondly,some basic theories classical methods of

analog

filter

ale

introduced in this the principle of

paper.With the

Amplifier(abbreviation:OTA),it has very 900d performance and obvious practical and theoretical value,the huge

高增益恒跨导低失调轨至轨运算放大器的设计

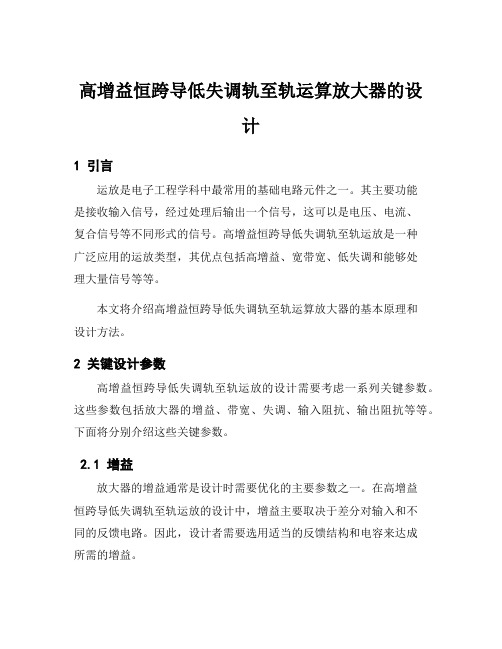

高增益恒跨导低失调轨至轨运算放大器的设计1 引言运放是电子工程学科中最常用的基础电路元件之一。

其主要功能是接收输入信号,经过处理后输出一个信号,这可以是电压、电流、复合信号等不同形式的信号。

高增益恒跨导低失调轨至轨运放是一种广泛应用的运放类型,其优点包括高增益、宽带宽、低失调和能够处理大量信号等等。

本文将介绍高增益恒跨导低失调轨至轨运算放大器的基本原理和设计方法。

2 关键设计参数高增益恒跨导低失调轨至轨运放的设计需要考虑一系列关键参数。

这些参数包括放大器的增益、带宽、失调、输入阻抗、输出阻抗等等。

下面将分别介绍这些关键参数。

2.1 增益放大器的增益通常是设计时需要优化的主要参数之一。

在高增益恒跨导低失调轨至轨运放的设计中,增益主要取决于差分对输入和不同的反馈电路。

因此,设计者需要选用适当的反馈结构和电容来达成所需的增益。

2.2 带宽高增益恒跨导低失调轨至轨运放的带宽通常被设计为大于几百Mhz,这是因为其应用涉及高速信号处理和光纤通信业等领域。

带宽取决于放大器的极点,因此,在设计时需要确保放大器的布局和电气特性能够支持所选的带宽,以避免输出失真和衰减。

2.3 失调失调是指差分输入信号被误差放大,产生输出偏移的情况。

失调可由差分对的非对称性引起,因此,设计时需要确保差分对的匹配性,以减小失调。

2.4 输入阻抗放大器的输入阻抗取决于前级电阻和差分对的电阻。

输入阻抗影响放大器的干扰抗性和电路的灵敏度。

设计时需要选择合适的前级电阻和差分对的电阻,以实现所需的输入阻抗。

2.5 输出阻抗放大器的输出阻抗通常很低,这是因为高输出阻抗可能会导致信号变形。

输出阻抗与两级输出级的负载电阻有关。

设计时需要选择合适的负载电阻和输出级的电路结构,以实现所需的输出阻抗。

3 设计方法高增益恒跨导低失调轨至轨运算放大器的设计方法包括:3.1 选择运放类型选择合适的高增益恒跨导低失调轨至轨运放类型取决于应用需求。

常用的类型包括单放大器、差动放大器和多级放大器等。

跨导运算放大器,跨导运算放大器是什么意思_1

跨导运算放大器,跨导运算放大器是什么意思跨导运算放大器,跨导运算放大器是什么意思跨导运算放大器的定义运算放大器可以置于传感器/信号源与模数转换器之间,将两者连接在一起,负责处理来自接收器信号路径的信号;也可置于数模转换器与模拟输出之间,将两者连接在一起,负责驱动发送器信号路径的信号无论是接收还是发送信号,运算放大器主要负责处理模拟信号,以便将模拟信号的重要信息传送至下一环节作进一步处理。

换言之,置于输入路径的运算放大器负责为模数转换器提供经过处理的输入信号,而置于输出路径的运算放大器则负责为发送器提供经过数模转换器处理的输出信号。

这个处理过程并不简单,因为系统采用的传感器、模数转换器、数模转换器及发送器都各不相同,为它们提供信号的信号源必须在电子特性方面能够满足它们的特殊要求,才可以充分发挥其性能。

什么是跨导放大器(Transconductance Amplifier)将电压转换为电流的放大器, 另外还有其它几个名称(请参考同义词列表)。

其中一个同义词是OTA,或称为运算跨导放大器,从运算放大器和跨导放大器派生而来。

该术语源于“传输电导”,以西门子(S)为单位,1西门子= 1安培/伏特,通常用符号gm表示。

真空管和FET的基础增益用跨导表示。

例如,PH测量仪表的PH电极所发出的信号需要经过高阻抗运算放大器的处理,才可传送至模数转换器,因为一般来说,PH电极的输出阻抗都很高。

输入阻抗不足的运算放大器便无法充分利用PH电极的电能,以至模数转换器也无法获得足够的PH电极电能。

系统处理模拟信号时如果不得其法,即使所采用的数字处理系统非常先进、强劲,系统的整体性能也会受到严重影响。

所谓“接收的是垃圾、输出的也是垃圾(Garbage in, garbage out)”,便是这个意思。

模拟集成电路设计(跨导运算放大器)

模拟集成电路课程设计跨导放大器学院:电信学院班级:微电子92组长:曾云霖(09053057)组员:黄雄(09053042)蒋仪(09053043)跨导放大器设计设计题目:基于所给的CMOS工艺设计一款跨导放大器。

跨导放大器的特点是具有非常大的输出阻抗,将输入电压转换成电流输出,相当于压控电流源。

该电路的设计同样需要包括偏置电压电流产生电路。

设计指标:设计指标:(供参考)性能参数测试条件参数指标负载电容30pF电源电压范围 2.5~5.5V静态电流VDD=3.6V,Temp=27℃<250μA输出摆幅输入共模电压VDD =3.6V,Temp=27℃VDD =3.6V,Temp=27℃0.6~1.2V0.1~1V开环增益(低频)VDD =3.6V,Temp=27℃1800~2200单位增益带宽VDD =3.6V,Temp=27℃>3MHz相位裕度VDD =3.6V,Temp=27℃>60°PSRR(低频)VDD =3.6V,Temp=27℃>65dB跨导(低频)VDD =3.6V,Temp=27℃(900~1100)μA /V 转换速率VDD =3.6V,Temp=27℃>3V/μs设计要求:1.确定设计指标(以上指标供参考,可以进行适当修改,但需说明原因);2.根据设计指标,可以在参考电路结构基础上确定参数和改进设计,也可以查找文献采用其它结构的电路或创造新的电路结构进行设计;3.阅读模型文件,了解可以选用的器件类型与尺寸范围;4.手工设计:根据拟定的设计指标,初步确定满足指标的各元件的模型与参数:MOS:沟道长度与宽度,并联个数;电阻:宽度、长度、串并联个数;电容:宽度、长度、并联个数;三极管:并联个数。

5.采用全典型模型, 27℃,验证电路是否满足设计指标;6.设计偏置电路:a) 选定电路结构;b) 手工设计:确定各元件的模型与尺寸;c) 采用全典型模型,仿真验证偏置电流源的性能;7.将偏置电路和主体电路合在一起仿真,采用全典型模型,27℃,VDD=3.6V,要求电路达到“设计指标”要求,否则应对电路结构和参数进行修改与优化,直至满足要求(可能需要多次调整),并应包括以下内容:a) 一输入端固定为0.6V参考电压,另一输入端从0V上升到3.6V(电源电压)时的输出电压曲线与静态电流曲线,确定低频增益;以输出0.9V为输出参考电压,确定输入失调电压(直流扫描);b) 一输入端固定为0.6V参考电压,另一输入端为信号输入,输出工作点为0.9V时的放大特性:增益、相位、带宽、相位裕量等(交流扫描,);c) 输出工作点为0.9V时,PSRR对于频率(1Hz~100KHz)的特性曲线(交流扫描)电路参考图:原理图分析说明:根据题目说明和参考电路可知,跨导放大器(OTA)是一种电压输入、电流输出的放大器、放大倍数为跨导Gm。

标准工艺的低压跨导放大器设计

北京信息科技大学毕业设计(论文)题目:标准工艺的低压跨导放大器设计摘要(中文)由于跨导放大器技术的飞速进步,CMOS电路向着低压、低功耗、小尺寸方向发展,使得电压低、功率小CMOS电路成为目前研究的热点。

CMOS跨导运算放大器的特点是电路结构简单,输出阻抗高,输出量是电流且不随负载变化;高频性能好,带通宽,增益通过控制端连续可调,所以基于CMOS电流输出的跨导运算放大器的仿真设计研究具有重要现实意义和应用价值。

本次毕业设计要求是基于中芯国际SMIC0.18微米标准工艺实现一个低压跨导运算放大器电路,以Cadence virtuso平台下完成电路原理图搭建、理论推导结果、电路仿真、电路调试以及最终后端版图生成相关工作,最终电路在1.8V电源电压下实现电压增益大于20dB,静态功耗小于300微瓦,达到了毕业设计要求。

关键词:跨导放大器;电路图;版图;Cadence摘要(英文)Because of transconductance technology rapid progress,Generation of operational transconductance amplifiers are faster, bigger range of input and output speeds toward a better high-frequency performance, lower power consumption and other direction. The transconductance operational amplifier circuit is characterized by simple structure, high output impedance, the output does not change with the load current, high-frequency performance, wide pass band, the gain continuously adjustable via the control terminal, the study has a transconductance amplifier becomes important practical significance and value.The graduation requirements are based on SMIC SMIC0.18 micron standard process to achieve a low transconductance operational amplifier circuit to be completed under the Cadence virtuso platform to build circuit schematics, the theoretical findings, circuit simulation, circuit debugging and final back-end layout generate relevant work, the final circuit at 1.8V supply voltage for voltage gain greater than 20dB, the static power consumption of less than 300 microwatts, reaching graduation requirements.Keywords: Operational transconductance amplifier to; circuit diagram; layout; Cadence目录摘要(中文) (Ⅰ)摘要(英文) (Ⅱ)第一章:放大器的历史发展.............................................- 1 -1.1 毕业设计的相关背景及研究现状 .................................. - 1 -1.2 课题研究重要意义及目的 ........................................ - 3 -1.3 论文结构和主要内容 ......................................... - 3 -第二章跨导运算放大器的基本原理.....................................- 4 -2.1 OTA的基本概念和理想模型....................................... - 4 -2.2 CMOS-OTA基本电路模型及工作原理................................ - 5 -2.3本章小结........................................................ - 6 -第三章CMOS跨导运算放大器电路设计及模拟仿真..........................- 6 -3.1 放大器的电路设计 ............................................... - 6 -3.1.1 参数设定....................................................................................................................... - 8 -3.2 放大器电路的模拟仿真........................................ - 12 -3.2.1 理论推导结果(放大器电压增益,输入噪声及静态功耗) ............................. - 12 -3.2.2 仿真波形....................................................................................................................... - 13 -3.2.3 SPICE网表及分析...................................................................................................... - 14 -3.3 本章小结...................................................... - 21 -第四章CMOS跨导运算放大器的版图设计................................. - 22 -4.1 版图设计规则 ................................................. - 22 -4.2 具体版图的设计 ............................................... - 22 -4.3 本章小结 ...................................................... - 23 -结论 .............................................................. - 23 - 结束语:............................................................ - 24 -参考文献............................................................ - 26 -致谢:.............................................................. - 27 -第一章放大器的历史发展1.1 毕业设计的相关背景及研究现状从20世纪末期开始,科学技术的发展有了一个质的飞越,而其中运算放大器的快速崛起更是使电子信息产业的发展上升到了一个新的高度。

跨阻放大器电路设计原理

跨阻放大器电路设计原理跨阻放大器电路设计原理跨阻放大器(TIA)是光学传感器(如光电二极管)的前端放大器,用于将传感器的输出电流转换为电压。

跨阻放大器的概念很简单,即运算放大器(op amp)两端的反馈电阻(RF)使用欧姆定律VOUT= I × RF将电流(I)转换为电压(VOUT)。

在这一系列博文中,我将介绍如何补偿TIA,及如何优化其噪声性能。

对于TIA带宽、稳定性和噪声等关键参数的定量分析,请参见标题为“用于高速放大器的跨阻抗注意事项”的应用注释。

在实际电路中,寄生电容会与反馈电阻交互,在放大器的回路增益响应中形成不必要的极点和零点。

寄生输入和反馈电容的最常见来源包括光电二极管电容(CD)、运算放大器的共模(CCM)和差分输入电容(CDIFF),以及电路板的电容(CPCB)。

反馈电阻RF并不理想,并且具有可能高达0.2pF的寄生并联电容。

在高速TIA应用中,这些寄生电容相互交互,也与RF交互生成一个不理想的响应。

在本篇博文中,我将阐述如何来补偿TIA。

图1显示了具有寄生输入和反馈电容源的完整TIA电路。

图1:含寄生电容的TIA电路三个关键因素决定TIA的带宽: Ÿ 总输入电容(CTOT)。

Ÿ 由RF设置理想的跨阻增益。

Ÿ 运算放大器的增益带宽积(GBP):增益带宽越高,产生的闭环跨阻带宽就越高。

这三个因素相互关联:对特定的运算放大器来说,定位增益将设置最大带宽;反之,定位带宽将设置最大增益。

无寄生的单极放大器这一分析的第一步假定在AOL响应和表1所示的规格中有一个单极的运算放大器。

DC、AOL(DC)时运算放大器的开环增益 120dB 运算放大器GBP 1GHz 反馈电阻RF 159.15kW 表1:TIA规格放大器的闭环稳定性与其相位裕度ΦM有关,相位裕度由定义为AOL× β的环路增益响应来确定,其中β是噪声增益的倒数。

针对跨阻放大器的设计考虑

30055201图1. 具有容性元件的光电二极管的建模由于可使用较大增益值(RF)下的低输入偏流LMH6611可在低照度下运行。

运算放大器反相端上的总电容(CT )包含光电二极管电容(CPD)和输入电容(CIN)。

在电路的稳定性上总电容扮演了重要的角色。

这个电路的噪声增益(NG)取决于稳定性,并定义为:(1)(2)图2所示是噪声增益与运算放大器的开环增益(AOL)相交的波特图。

在较大的增益(RF )下,CT和RF在转移函数中AN-1803© 2008 National Semiconductor Corporation 300552针对跨阻放大器的设计考虑30055204图2. 噪声增益与运算放大器开环增益相交的波特图为了维持放大器的稳定性,在RF两端跨接一个反馈电容器,这会在噪声增益函数中的fP处产生一个极点。

为优化性能,选择适当的CF数值能使噪声增益斜率变得平坦,这样噪声增益就等于运算放大器在fP处的开环增益。

这一噪声增益斜率的“平坦部分”超过AOL的截止点,结果使噪声增益得到45°的相位裕量(PM)。

因为噪声增益的fP极点会在截止点有一个45°的超前相位,其贡献了45°相位裕量(假定fP和fZ少相距一个十倍频程)。

等式3和等式4在理论上计算了最佳CF值和期望的-3 dB宽。

(3)(4)等式4表示跨阻放大器的-3 dB带宽与反馈电阻值成反比。

因此,如果带宽是重要的性能,那么最好的方法是采用一个适中的跨阻增益级,后接一个宽带电压增益级。

表1是对带有不同容值的各种光电二极管在1 kΩ跨阻增益(RF)下测量LMH6611的结果。

CF和f-3dB的值由等式3和等式4计算得到。

2A N -1803表1 跨阻放大器(图1)的补偿和性能结果C PD C T C F 计算值C F 使用值F -3dB 计算值F -3dB 测量值峰值(pf )(pf )(pf )(pf )(MHz )(MHz )(dB )2224 5.42 5.629.327.10.547497.75820.5210.510010211.151214.215.20.522222420.39189.610.70.533033220.2227.990.8注意:Vs= +/-2.5V GBW = 130 MHz C T = C PD + C IN C IN = 2pf图3是使用表1中不同光电二极管时放大器的频率响应。

跨阻放大器的计算

跨阻放大器的计算跨阻放大器是一种常用的电路,用于放大输入电压信号。

在设计跨阻放大器时,需要考虑到电路的放大倍数、输入阻抗和输出阻抗等关键参数。

本文将介绍如何计算跨阻放大器的放大倍数和输入输出阻抗。

一、跨阻放大器的定义跨阻放大器是一种使用跨导放大模式的放大器电路。

它由一个输入端、一个输出端和一个反馈电阻组成。

输入信号通过输入端进入电路,经过放大后从输出端输出。

反馈电阻则通过反馈回路连接输入端和输出端,用于调节电路的放大倍数。

二、跨阻放大器的放大倍数计算跨阻放大器的放大倍数可以通过计算电路的反馈系数来得到。

反馈系数是指输入信号经过反馈回路形成的反馈信号与输入信号的比值。

在跨阻放大器中,反馈系数可以由反馈电阻和负载电阻来决定。

假设反馈电阻为Rf,负载电阻为Rl,则跨阻放大器的放大倍数Av可以表示为:Av = Rf / Rl这意味着放大倍数可以通过调节反馈电阻和负载电阻的比例来实现。

通常情况下,我们可以根据需要的放大倍数来选取合适的电阻数值。

三、跨阻放大器的输入阻抗计算输入阻抗是指输入端电路对外界信号源的阻抗特性。

在跨阻放大器中,输入阻抗可以由输入电阻和反馈电阻来共同决定。

假设输入电阻为Rin,则跨阻放大器的输入阻抗Zin可以表示为:Zin = Rin || Rf这里的||表示并联。

通过并联两个电阻,可以得到输入阻抗的数值。

四、跨阻放大器的输出阻抗计算输出阻抗是指输出端电路对外界负载的阻抗特性。

在跨阻放大器中,输出阻抗可以由负载电阻和反馈电阻来共同决定。

假设输出电阻为Rout,则跨阻放大器的输出阻抗Zout可以表示为:Zout = (Rl || Rf) + Rout这里的+表示串联。

通过串联两个电阻,可以得到输出阻抗的数值。

五、实例分析为了更好地理解跨阻放大器的计算方法,下面我们以一个具体的实例来进行分析。

假设需要设计一个跨阻放大器,要求放大倍数为20倍,输入阻抗为10kΩ,输出阻抗为1kΩ。

我们可以先根据放大倍数的定义,得到反馈电阻和负载电阻之间的比值为20。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

图 1 所示为一个用电压反馈放大器构建的带有光电二极管等效电容和运放输入电容的 TIA 模型。

由于 LMH6611 工作在较大增益 (RF) 时,其输入偏置电流便较低,故可容许电路工作在低光强度的条件下。运算放大器反向端上的总电容 (Cr) 包括光二极管的电容 (CPD) 和输入电容 (CIN),Cr 在电路稳定性方面扮演着很重要的角色,而稳定性则取决于这个电路的噪声增益噪声增益 (NG),其定义为:

跨导放大器的设计考虑

采用电压反馈放大器 (VFA) 来设计一个优质的电流到电压 (跨导跨导放大器) 转换器是一项重大的挑战。理论上,一个光电二极管当曝露在光线中时可产生一个电流或电压输出,而跨导放大器 (TIA) 便是将这个很弱的电流转换成一个可用的电压信号,通常跨导放大器均需经过补偿才能正常工作。本文将会探讨一个用 345 MHz 的轨到轨输出,电压反馈放大器 (例如是美国国家半导体的 LMH6611)来实现的简单 TIA 设计,并提供 TIA 设计所必需的信息,讨论 TIA 的补偿和性能结果,以及分析 TIA 输出端的噪声。

公式 3 和 4 理论上可计算出 CF 的最优值和期望的 -3 dB 带宽:

公式 4 指出 TIA 的 -3 dB 带宽与反馈电适度的跨导增益级后跟随一个宽带电压增益级。

表 1 示出在不同光电二极管下的 LMH6611的测量结果,这些光电二极管在 1 kΩ 的跨导增益 (RF) 下有不同的电容值 (CPD)。至于 CF 和 f-3 dB 则是分别通过公式 3 和 4计算出来。

点和极点之间的区域被放大,而 RF 和 CT的数值越高,则噪声增益的峰值便越早出现,从而对整体输出噪声的贡献亦越大。

通过计算 TIA 输出处所有有贡献的噪声电压之方均根值,便可得出等效的总噪声电压值。

总括来说,总电容 (CT) 对于 TIA 的稳定性起了很重要的作用,CT 愈小那稳定性便愈高,而把 CT 尽量降低有两个方法,一是选择合适的运算放大器,二是施加一个反向偏压给光二极管,但这会引致有过量的电流和噪声出现。本文证实从实验中不同光二极管和补偿方法得出来的测量结果与理论非常吻合。

图 2 所示为噪声增益与运算放大器开环增益开环增益 (AOL)交点的波特图。当增益较大时,CT 和 RF 在传递函数中产生了一个零点。在较高的频率下,在环路附近会出现过大的相移,使得跨导放大器绝对不稳定。

为了保持稳定性,需要加入一个反馈电容 (CF) 与RF 并联以便在噪声增益函数中的 fP 处构建一个极点。通过选用合适容值的 CF,便可使噪声增益的斜坡变平从而获取最佳的性能,这样使得频率 fP 点的噪声增益等于运算放大器的开环增益。这个在 AOL和噪声增益交点以上的噪声增益斜率“平坦化”会得到一个 45 度的相位余量 (PM)。这是因为在交点处,fP 点的噪声增益极点会贡献一个 45 度的相位超前,因此给出了一个 45 度的相位余量 (假设 fP 和fZ之间最少有 10 MHz 的距离)。

图 3 示出对应于表 1 中不同光电二极管的频率响应。当全部所需的增益都放置到TIA 级时,信噪比便得以改善,原因是由RF 产生的噪声频谱密度会随着 RF 的平方根而增加,而且信号也会线性增加。

毫无疑问,在设计时必须考虑所有的噪声来源。当分析 TIA 输出的噪声时,必须注意运算放大器噪声电压噪声电压、反馈电阻器热噪声、输入噪声电流和光电二极管噪声电流都不是全部工作在同一个频率范围。运算放大器的噪声电压将会在噪声增益的零