硬件描述语言及器件实验指导实验指导书最终版

硬件描述语言实验

《硬件描述语言》实验指导书南通大学电子信息学院2008 年 2 月1、目的和任务《硬件描述语言》是一门侧重于数字电子系统的设计和测试方法的课程,它的上机实验是教学中的一个重要环节。

通过上机学习,学生不仅可以系统地复习、巩固该课程的基本理论,而且培养学生解决问题能力和创新能力,同时为该课程的课程设计作准备。

2、教学基本要求(1)、熟练使用 EDA 软件(Quartus II、ModelSim);(2)、掌握用 Verilog HDL 实现组合逻辑电路和时序逻辑电路的方法。

3、实验条件(1)、PC 机、Quartus Ⅱ软件和 ModelSim软件(2)、GW48型 EDA 实验开发系统(EP1K30TC144-3)4、实验内容序号实验内容1 实验一设计工具的使用2 实验二组合逻辑电路设计(一)3 实验三组合逻辑电路设计(二)4 实验四总线与总线操作5 实验五时序逻辑电路设计(一)6 实验六时序逻辑电路设计(二)5、实验成绩实验成绩的评定由实验的验收等级和实验报告等级两个部分组成,各占50%。

实验的验收等级和实验报告等级均采用 5 个等级,即优、良、中、及格和不及格。

实验成绩占本课程平时成绩的50%。

实验一设计工具的使用1、实验目的与要求掌握在 Quartus Ⅱ开发环境下,运用硬件描述语言输入法对“三人表决器”进行设计输入、编译、调试和仿真的方法。

“三人表决器”电路的输入为 SW1、SW2 和 SW3,输出为 L3 和 L4,位宽均为 1 位。

当SW1、SW2 和 SW3中有超过2个以上的输入为1时,要求熟悉整个设计流程,从打开、建立文档、编辑、编译、建立激励信号波形及最后仿真的整个过程。

2、实验内容(1)在Quartus Ⅱ开发环境下,建立工程,并将三人表决器的硬件描述语言程序输入;(2)完成编译、调试和仿真,分析实验仿真结果,并判断其正确性。

3、教学形式(1)本实验为验证型实验,学生在实验前预习实验指导书;(2)指导教师应该在实验前阐述实验目的、内容、方法和步骤,并且就实验中的难点和注意事项进行一定的说明;(3)实验结束之后,学生按照实验报告的书写格式自行完成实验报告。

VHDL硬件描述语言实验指导书(部分)

列位置映射了实际器件管脚,简单的鼠标拖放即可完成底层编辑。

2、持的器件更多:除了支持MAX3000、MAX7000、FLEX6000、FLEX10KE、ACEX1K 等

MAX+PLUSⅡ已支持的器件外,还支持PEX20K、APEX20KE,APEXⅡ、EXCALIBUR-ARM、

实验 8 计数器设计...............................44

实验 9 可预置数的计数器设计.....错误!未定义书签。

第三部分 设计型实验...............错误!未定义书签。

实验 1 频率计设计...............错误!未定义书签。

件。具有许多优良的特性。

1、承了MAX+PLUSⅡ的优点:图形输入依然形象,图形符号与MAX+PLUSⅡ符号一样符

合数字电路的特点,大量74 系列器件符号使初学者在较短的时间内利用图形编辑

设计出需要的电路。文本输入几乎与MAX+PLUSⅡ相同,而且在文本的每一行都有

使用。其设置界面如图1-4 所示:

3

----------------------- Page 5-----------------------

实验 1 译码器及译码显示电路设计.................16

实验 2 编码器及数据选择器设计...................20

实验 3 加法器设计...............................23

实验 4 乘法器设计...............................26

(2013)硬件描述语言上机操作指导书

硬件描述语言及应用实验指导书河南科技大学电子信息工程学院VHDL语言及应用实验指导书宋潇主编齐晶晶副主编电工电子实验教学中心2010年3月目录实验一MAX+PLUSⅡ基本应用练习 (1)实验二VHDL基本结构设计练习 (6)实验三基本语句编程练习一 (8)实验四基本语句编程练习二 (10)实验五VHDL组合逻辑电路设计 (12)实验六VHDL时序逻辑电路设计 (14)实验七VHDL有限状态机设计 (16)附录各种下载板与主板主要器件连接关系表 (18)I实验一MAX+PLUSⅡ基本应用练习为了使读者快速学会使用Altera公司的EDA工具软件MAX+PLUSⅡ,下面将以简单组合逻辑的设计为例,讲解如何利用MAX+PLUSⅡ软件进行设计和测试的全过程。

一、实验目的1、初步了解VHDL语言;2、了解VHDL语言的编程环境及开发软件MAX+PLUSⅡ的运行;3、了解开发软件MAX+PLUSⅡ的编译、仿真等。

二、实验环境本指导书中的VHDL语言均在MAX+PLUSⅡ中进行编译仿真,有需要实验箱的情况下使用SE-5型实验箱,管脚的连接参照附录中《各种下载板与主板主要器件连接关系表》。

三、预习要求初步掌握VHDL语言的基本结构,熟悉该数据类型与运算操作符,了解MAX+PLUSⅡ的运行过程。

四、实验内容及步骤简单组合逻辑包括两个输入、三个输出,如下表1-1。

11、原理图设计图1-1简单组合逻辑的原理图设计2、VHDL源程序(1)创建新目录及启动MAX+PLUSⅡa、建立新目录在创建新项目之前,首先要为该设计(项目)建立一个新目录,如“e:\example”。

b、启动MAX+PLUSⅡ软件从“开始”菜单选择“程序”中的MAX+PLUSⅡ项,或双击桌面上“max2win.exe”图标,就进入到MAX+PLUSⅡ软件的集成环境界面。

(2)创建源文件a、生成一个新的文本文件选择菜单“File”→“New ”或单击工具条中的图标,出现如图1-2所示的对话框。

集成电路设计硬件描述语言实验指导书

集成电路设计硬件描述语言实验指导书实验一Verilog HDL程序结构与ModelSim、Quartus II软件的使用一、实验目的初步掌握Verilog HDL程序基本结构,编制简单的Verilog程序,掌握ModelSim、Quartus II软件的使用,掌握用Quartus II软件对Verilog程序进行编译仿真下载的基本方法。

二、实验内容1、编写Verilog程序描述一个电路,实现以下功能:该电路具有一个输入端口a,一个输出端口b,电路的作用是把输入到a的信号传送给b。

2、编写Verilog程序描述一个电路,实现以下功能:该电路具有两个输入端口a,b一个输出端口c,电路的作用是:c的输出是a 和b的“与”。

三、实验步骤1、编写Verilog程序,两个文件名分别为ex1.v和ex2.v,使用ModelSim的force命令进行仿真。

2、编写测试平台(testbench),对程序进行仿真。

3、启动Quartus II软件,建立工程(第一个工程名为ex1,顶层文件名为ex1.v;第二个工程名为ex2,顶层文件名为ex2.v)。

器件选择Cyclone系列中的EP1C3T144C8。

4、编写Verilog程序,存盘编译。

5、通过编译后,建立波形文件,设置仿真输入信号,存盘。

6、进行仿真,分析结果。

7、进行引脚锁定,重新编译。

对于ex1:a 对应引脚号1(PIO0)b 对应引脚号11(PIO8)对于ex2:a 对应引脚号1(PIO0)b 对应引脚号2(PIO1)c 对应引脚号11(PIO8)8、下载到EDA实验系统上的FPGA中,进行实际测试。

选用实验电路结构图NO.5。

四、实验报告要求实验目的,实验内容,设计的Verilog程序,实验结果,结果分析,心得与体会。

实验二异步清零十进制计数器的设计一、实验目的熟悉时序逻辑电路Verilog程序的设计,掌握计数器的设计方法。

二、实验内容编写Verilog程序描述一个电路,实现以下功能:具有2个输入端口clk和clr,clk输入时钟信号,clr起异步清零作用,‘1’有效,两个输出端口,c和q,q的位宽为4,输出计数值,从0到9,c的位宽为1,每当q为9时输出一个高电平脉冲。

《计算机硬件性能检测》实验指导书

《计算机硬件性能检测》实验指导书一、实验目的:1、熟练掌握通过测试软件在不拆机情况下了解计算机硬件参数信息及性能检测方法;2、掌握常用CPU、内存、显卡、硬盘、光驱等计算机性能指标。

3、了解计算机组装优选配件方法。

二、实验性质:验证性实验。

三、实验学时:4学时。

四、实验仪器和设备:1、硬件要求:计算机配置不低于:2.5GMHz的CPU、1GB内存、2GB可用硬盘空间、dvd光驱、LCD显示器。

2、软件要求安装Windows XP操作系统,预装下列计算机测试软件:1、CPU测试:Cpu-Z 1.54 、Hot CPU Tester Pro V4.412、内存测试:MemTest 4.03、显卡测试:3DMark 2005 Free Edition4、显示器测试:DisplayX 1.2 、Nokia Monitor Test 2.05、声卡测试:Audio WinBench996、硬盘测试:HD Tune 4.50 Pro7、光驱测试:Nero CD-DVD Speed V4.78、键鼠测试:PassMark KeyboardTest V3.09、计算机整机性能综合测试软件:EVEREST Ultimate Edition 5.50 Final 、鲁大师2.66五、实验内容:安装应用上述计算机测试软件对实验用计算机硬件性能全面检测。

六、实验步骤:1.计算机配件参数信息及检测。

1)使用Cpu-Z 1.54检测计算机CPU参数。

CPU-Z是一个检测CPU信息的免费软件,这些信息包括:CPU 名称、厂商、性能、当前电压、L1 L2 cache情况;内核进程;内部和外部时钟等。

支持全系列的Intel以及AMD品牌的CPU。

CPU-Z能提供全面的CPU相关信息报告,包括有处理器的名称、厂商、时钟频率、核心电压、超频检测、CPU所支持的多媒体指令集,并且还可以显示出关于CPU的L1、L2的资料(大小、速度、技术),支持双处理器。

《数字逻辑与硬件描述语言》实验指导书-003293007

数字逻辑与硬件描述语言实验指导书(适用于通信工程以及电子信息工程专业)信息学院技术中心1目录第一部分基础知识(一)MAXPLUSII基本使用 (1)(二)VHDL简明教程 (10)第二部分基础实验实验一门电路功能测试 (37)实验二编码器、译码显示器的功能测试 (40)实验三触发器及其应用 (44)实验四移位寄存器功能测试 (47)第三部分综合选做实验实验五秒表的设计 (50)实验六数字钟的设计 (52)2第一部分基础知识(一)MAXPLUSII 基本使用设计流程图一、图形输入的设计过程在本节将以图形输入法为例讲述图形方法设计的整个过程。

在MAX—PLUSII中,用户的每个独立设计都对应一个项目,每个项目可饮食一个或多个设计文件,其中有一个是顶层文件,顶层文件的名字必须与项目名相同。

编译器是对项目中的顶层文件进行编译。

项目还管理所有中间文件,所有项目的中间文件的文件名相同,仅后缀名(扩展名)不同,对于每个部的项目最好建立一个单独的子目录。

(一)项目建立1.启动MAX+PLUSII 10.0从“开始”菜单“程序”中的“MAX+PLUSII 10.0 Baseline”组中的“MAX+PLUSII 10.0 Baseline”,单击“MAX+PLUSII 10.0 Baseline”项。

2.在File菜单中选择Project的Name项,输入设计项目的名字。

3.启动菜单File\New,选择Graphic Editor File,打开原理图编译器,进行原理图设计输入。

(如图1-1)图1-1 原理图设计界面(二)设计的输入1、放置器件在原理图上(1)在原理图的空白出双击鼠标左键,出现图1-2。

图1-2 选取元件菜单图(2)在光标处输入元件或用鼠标点击选取元件,按下OK即可。

(3)安放同样的元件,选取该元件,按住Ctrl键,同时用鼠标拖动该元件。

(4)建立图1-3 的实验原理图。

2、连线如果需要连接元件的两个端口,则将鼠标移到其中的一个端口上,这时鼠标指示符会自动变为“+”形,然后(1)按住鼠标左键并拖动鼠标至第二个端口(或其他地方);(2)松开鼠标左键后,则可画好一条连线;(3)若想删除一条连线,只需用鼠标左键点中该线,被点中的线会变为高亮线(为红色),此时按“Delete”键即可删除。

硬件描述语言及器件实验指导实验指导书最终版

硬件描述语言及器件实验指导书电子科学与技术专业组实验一用硬件描述语言的方法设计一个三输入与门电路一、实验目的1、掌握MAX+plusII的使用方法。

2、掌握VHDL语言程序的基本结构。

2、掌握使用硬件描述语言设计数字电路的方法和步骤。

3、掌握用硬件描述语言设计三输入与门电路的方法。

二、实验器材1.台式计算机 1台。

2.可编程逻辑逻辑器件实验软件1套。

3.下载电缆一套。

4.示波器一台。

三、实验说明1.台式计算机用于向可编程逻辑逻辑器件实验软件提供编程、仿真、下载的平台,供用户使用。

2.可编程逻辑逻辑器件实验软件向原理图的设计提供平台,并将调试好的原理图下载到可编程逻辑逻辑器件中。

3.下载电缆是可编程逻辑器件软件和可编程逻辑逻辑器件之间的接口电缆,为了便于区别,用不同颜色导线区分下载电缆的电源、地和信号,一般用红色导线接电源,用黑色导线接地。

4.示波器用于观察可编程逻辑器件执行程序时输出信号的变化。

四、实验内容与要求用硬件描述语言的方法设计一个三输入与门电路,要求:(1)根据三输入与门的逻辑表达式,在构造体中直接使用并行赋值语句实现,并进行仿真;(2)根据三输入与门的真值表,在构造体中使用进程语句实现,并进行仿真;五、实验步骤(下面七个的实验的软件的使用具体步骤跟本次试验一样不再详述)1.打开新建菜单选择“text edtior file”,这个文件是写程序编程用的。

2.程序写完后点“保存”,注意(1)保存的格式是.vhd,(2)保存的位置不能是桌面和硬盘的根目录,否则在后面的编程将出现错误。

3.在file→projectset→ project to current file ,这步是将文件设置在工程里,能够正常编译和下载。

4.在“assign→device”选择下载设备的芯片型号,如果芯片型号选错将导致以后能编译成功但下载到实验箱时无法正常工作。

5.在“max+plux”中选择“compiler”进行编译。

硬件描述语言及器件实验指导

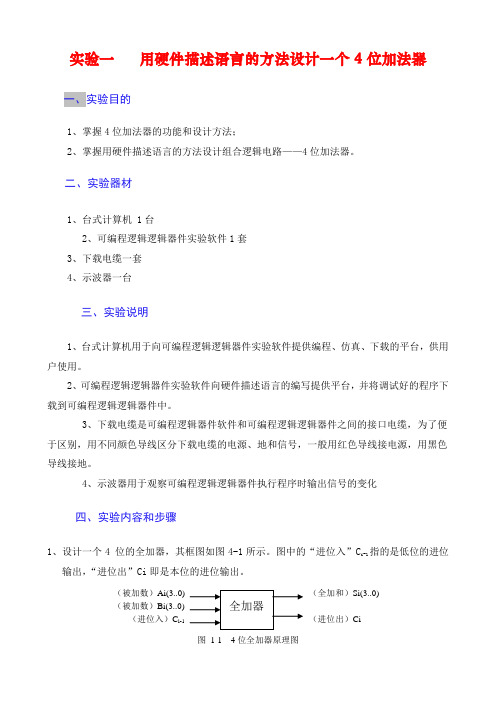

实验一用硬件描述语言的方法设计一个4位加法器一、实验目的1、掌握4位加法器的功能和设计方法;2、掌握用硬件描述语言的方法设计组合逻辑电路——4位加法器。

二、实验器材1、台式计算机 1台2、可编程逻辑逻辑器件实验软件1套3、下载电缆一套4、示波器一台三、实验说明1、台式计算机用于向可编程逻辑逻辑器件实验软件提供编程、仿真、下载的平台,供用户使用。

2、可编程逻辑逻辑器件实验软件向硬件描述语言的编写提供平台,并将调试好的程序下载到可编程逻辑逻辑器件中。

3、下载电缆是可编程逻辑器件软件和可编程逻辑逻辑器件之间的接口电缆,为了便于区别,用不同颜色导线区分下载电缆的电源、地和信号,一般用红色导线接电源,用黑色导线接地。

4、示波器用于观察可编程逻辑逻辑器件执行程序时输出信号的变化四、实验内容和步骤1、设计一个4 位的全加器,其框图如图4-1所示。

图中的“进位入”Ci-1指的是低位的进位输出,“进位出”Ci即是本位的进位输出。

(被加数)Bi(3..0)(被加数)Ai(3..0) (进位入)C i-1(全加和)Si(3..0)(进位出)Ci图1-1 4位全加器原理图2、全加器的9个输入所对应的管脚同9位拨码开关相连,9个输入管脚是a0~a3、b0~b3和C i-1,a0~a3、b0~b3代表两个4位二进制数,cin代表进位位;5个输出所对应的管脚同5位发光二极管相连,5个输出管脚是si0~si3和ci,si0~si3代表相加结果,Ci代表进位位。

3、将设计好的逻辑功能转为硬件描述语言的描写4、将设计好的硬件描述语言进行仿真5、将仿真好的硬件描述语言下载到可编程逻辑逻辑器件中五、实验报告要求1、整理实验结果,填写实验报告。

2、小结实验心得体会。

3、回答思考题什么叫全加器,它的作用是什么? 4位加法器和全加器的区别和联系是什么?实验二用硬件描述语言的方法设计一个分频器一、实验目的1、掌握各种分频器的设计思路2、掌握用硬件描述语言的方法设计各种分频器二、实验器材1、台式计算机 1台2、可编程逻辑逻辑器件实验软件1套3、下载电缆一套4、示波器一台三、实验说明1、台式计算机用于向可编程逻辑逻辑器件实验软件提供编程、仿真、下载的平台,供用户使用。

硬件描述语言与数字系统设计实验指导书_lab1

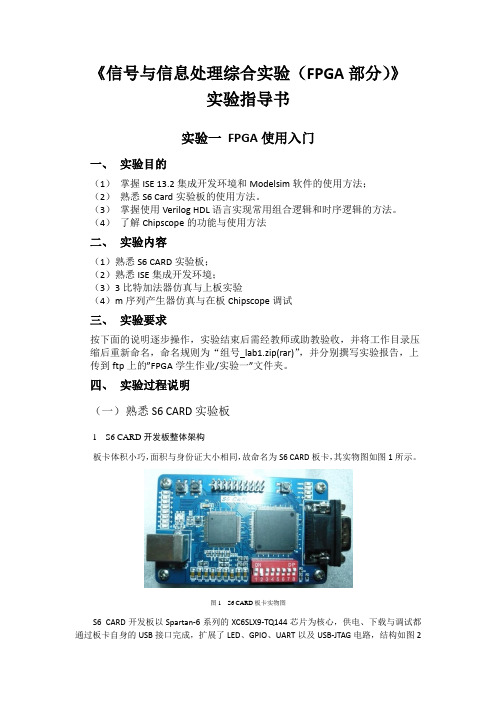

《信号与信息处理综合实验(FPGA部分)》实验指导书实验一FPGA使用入门一、实验目的(1)掌握ISE 13.2集成开发环境和Modelsim软件的使用方法;(2)熟悉S6 Card实验板的使用方法。

(3)掌握使用Verilog HDL语言实现常用组合逻辑和时序逻辑的方法。

(4)了解Chipscope的功能与使用方法二、实验内容(1)熟悉S6 CARD实验板;(2)熟悉ISE集成开发环境;(3)3比特加法器仿真与上板实验(4)m序列产生器仿真与在板Chipscope调试三、实验要求按下面的说明逐步操作,实验结束后需经教师或助教验收,并将工作目录压缩后重新命名,命名规则为“组号_lab1.zip(rar)”,并分别撰写实验报告,上传到ftp上的”FPGA学生作业/实验一”文件夹。

四、实验过程说明(一)熟悉S6 CARD实验板1 S6 CARD开发板整体架构板卡体积小巧,面积与身份证大小相同,故命名为S6 CARD板卡,其实物图如图1所示。

图1 S6 CARD板卡实物图S6 CARD开发板以Spartan-6系列的XC6SLX9-TQ144芯片为核心,供电、下载与调试都通过板卡自身的USB接口完成,扩展了LED、GPIO、UART以及USB-JTAG电路,结构如图2所示。

此外,S6 CARD通过USB线完成板卡供电和调试,便于使用。

图2 S6 CARD板卡结构图其中,Flash芯片使用了32Mb的SPI Flash M25P32,容量大,也适合于嵌入式系统开发。

系统时钟由外部晶振给入,频率为50MHz。

2 S6 CARD开发板驱动电路1、LED驱动电路LED是最基本的电路组件,给高电平就发光,且发光的程序和驱动电流有关。

板卡的LED 电路如图3所示。

图3 S6 CARD LED电路2、按键和拨码开关电路LED、按键以及拨码开关本质上属于同一类设备,LED为输出设备,而按键和拨码开关属于输入设备。

按键为瞬时输入设备,仅在按下时维持一个固定输入,松开则返回到固定的逻辑相反状态。

《计算机硬体基础》实训指导书

《计算机硬件基础》实训指导书实验教学指导书前言《计算机硬件基础》是一门实践性很强的课程,只有让学生自己多动手进行实验,才能熟练把握计算机组装方法与维护技术,才能培养学生良好的用机习惯和维修习惯,才能把握pc系统故障的排解原则、维修流程及维修中的常用方法,逐步培养学生理论联络实际,认真观察思索,综合分析判断的力量及实际动手力量,才能真正学好本课程。

因此,实验是巩固和发展课堂知识的一个重要环节。

但因为《计算机硬件基础》这门课没有现成的实验指导书,为了高效地利用有限的上机时间,提高上机效率,保证实验效果,根据以往教学经验和学生的现状,特自己编写这门课程的实验指导书。

本实验手册是我系计算机硬件基础课程上机实验指导的主要依据。

根据实验大纲要求,共包含11个实训。

1.了解微型机系统的硬件组成与配置2.培养对微型机硬件各组成部件的识别力量开机观察机箱内的计算机硬件配置,到网上查询最新硬件情况,初步把握配机方案。

1.留意开机后系统自检的荧幕提示和系统配置表(可按pause键暂停),将该微型机的硬件配置如:显示卡的型号和显示快取的容量、存储器容量、cpu型别、硬盘容量、软盘机型别和界面情况等记录下来。

假如不能正确启动系统,记下故障现象。

2.开启太平洋计算机网:和中关村**:(1)了解机箱重点认识机箱的作用、分类;机箱的内部、外部结构和机箱前、后面板的结构等。

(2)了解电源重点认识电源的作用、分类、结构、型号、电源输出/输入电压和电源联结器等。

(3)了解cpu主要包括cpu的型号、型别、主频、电压、厂商标志、封装形式,以及cpu效能等。

(4)了解存储器认识了解微型机系统中常用的ram,rom,cache等不同的功能特点和容量的大小,并进一步加深对存储器在微型机系统中的重要性的认识。

(5)了解认识主机板了解并认识微型机主机板的生产厂商、型号、结构、功能组成、采用的芯片组、界面标准、跳线设定、在机箱中的固定方法,及其与其他部件连线情况等。

EDA实验指导书_实验指导06_EDA_硬件综合实验

“电子设计自动化(EDA)”实验指导书(六)一、实验课程编码:105009二、实验课程名称:电子设计自动化(EDA)三、实验项目名称:综合硬件实验二(带时分秒按键调整和静态数码管显示的数字钟)四、实验目的1)学会看硬件原理图,2)掌握FPGA硬件开发的基本技能3)培养EDA综合分析、综合设计的能力五、主要设备1)PC机,2)硬件实验箱,3)Max plusII软件开发平台。

六、实验内容1.6个数码管静态显示驱动2.按键模式选择(时\分\秒)与调整控制3.用硬件描述语言(或混合原理图)设计时、分、秒计数器模块、按键控制状态机模块、显示译码模块、顶层模块。

要求使用实验箱右下角的6个静态数码管(DS8C, DS7C, DS4B, DS3B, DS2B, DS1B)显示时、分、秒;要求模式按键和调整按键信号都取自经过防抖处理后的按键跳线插孔。

七、实验步骤1.打开Max plusII ,连接实验箱上的相关硬件资源,如下图1所示。

2.建立新文件,选择文本类型或原理图类型。

3.编写程序。

4.编译5.仿真,加载程序到芯片,观察硬件输出结果(数码管显示)6.结果正确则完成。

若结果不正确,则修改程序,再编译,直到正确。

图1 综合硬件实验二对应的硬件资源连接八、实验结果直接观察实验箱的数码管显示、操作按键进行控制和调整。

数字钟包括正常的时分秒计时,DS2B DS1B.125 H z.25 H z.5 H zH zH zH zH z4 H z56 H z024 H z096 H z6384 H z2768 H z5536 H z50 K H z.5 M H zM H zM H z2 M H z4 M H zHour 00-23 Minute 00-59Second 00-59实验箱右下角的6个静态数码管(DS8C, DS7C, DS4B, DS3B, DS2B, DS1B)显示时、分、秒。

adjust 递增调整时分秒,mode按键循环调整模式。

硬件描述语言实验指导

选择执行Tools→Netlist Viewers →RTL Viewer命令。

显示逻辑电路图。

5 仿真

选择执行File→New命令。 选择Other Files→VectorWaveform File,单击OK按钮。

sert→Insert Node or Bus 命令。

单击“是”改变数据表示格式。

此时间段总线数据编辑完成。其他总线信号和其他时间 段用同样方法编辑。

编辑完成的输入波形图。保存后仿真。

仿真结果。

单击Node Finder按钮。

单击下图所示下拉按钮,选择Pins: all;单击List按钮。

单击下图所示图标按钮

单击OK按钮。

单击OK按钮。

单击下图所示图标按钮。

在下图所示区域,单击鼠标右键,使时间轴压缩。

单击下图所示图标按钮。按住鼠标左键,在下图所示右 侧区域信号波形上拖动以编辑波形。波形编辑完成后存盘。

单击下图所示浏览按钮。

找到并打开已更改过的License.DAT文件。

下图所示区域软件版本有效日期为将来日期,说明破解 成功。单击OK结束破解。

2 建立工程

新建一个文件夹,其文件夹名称应符合VHDL命名规则。 这个文件夹的名称也是工程名、顶层实体名。

选择执行File→New Project Wizard 命令。

单击下图所示Next按钮。

单击击下图所示浏览按钮。

找到并进入已建好的工程文件夹,单击打开按钮。

如下图所示,第一个显示窗中应出现工程文件夹路径, 后两个显示窗应出现工程名。如没有显示,可手动填入。然 后单击Next按钮。

单击下图所示Next按钮。

单击下图所示下拉按钮选择芯片族,例如选择Cyclone II 芯片族。

硬件技术实验指导书1.docx

计算机硬件技术基础实验指导书计算机科学与技术学院软件学院2012年3月实验一硬件基础实验一、 实验目的:1. 掌握运算器的组成及工作原理;2. 了解4位函数发生器74LS181的组合功能,熟悉运算器执行算术操作和逻辑操作的具体实现过 程;3. 验证带进位控制的74LSI81的功能。

二、 预习要求:1复习本次实验所用的各种数字集成电路的性能及工作原理; 2预习实验步骤,了解实验屮要求的注意之处。

三、 实验设备:EL-JY-II 型计算机组成原理实验系统一套,排线若干。

四、 电路组成:本模块由算术逻辑单元 ALU 74LS181 (U7、U8、U9、U10)、暂存器 74LS273 (U3、U4、U5、 U6)、三态门74LS244 (Ull 、U12)和控制电路(集成TEP1K10内部)等组成。

电路图见图l ・l (a )、M(b)oTOULS244HDBIC >cut I CLKI Hw “inn at2 ILDO LDATAO 32Qi ILDl 6 ILS xLPATAl ♦ IP an A A9 133 JDADQ ' JP 賀» SQU IL3 K LDATAJ 815 1LDJ 、LDAYM B •P <r> A16 1LM 、LDATA5 1419 \Lt>tX LDATA617XDATA7 18CLR 1eg n■QM HL$2T3cut »er ■ m2 2LD0 、、LDATAO 3‘ wMk ly 2Q m itc5 2LDI6 2U>2 ^LDATAl ♦ IP 珂M> 4Q 9 233 K LPATAJ rn 2LP4 、LDATA3 815 2LD5 \LDAT" Bw <T\ aC 16 2LD6 K LDATA5 14 go%ac19 2LD7、LDAYM 17\LDATA7 1886si S$2 4 H 3 M • CH OUTaslGnMgMfe_7llai2_aB3U12LDO -2^LD1 4 LD2 6 LD38 1—1OA122M2OB1环B3B474LSU10174LSI8118 LDATAO 16 LDATA1 14 I^>ATA2 12 LDATA39 LDATA4 7 LDATA5 5 LDATA6 3 LDATA7•snnnvbnnn\Jg>AyO > \HDATA1 4\Kt>ATA) I_ \WATA5 14_\®ATM _I F2ZCUt ] cuo n1$ n 14 Ts no0 LXM io u>, H LD6 B W7s 2HD1 6 2lO>2 9 2HD3 U 2HTX 15 2HP5 16 2HW P2Hi>r■2JI .^.n.n.n 必・*>*L>als-2nMLS MlHD1 4 HD2 6 HD381 j HD4 11〜HD5 13 HD6 15 HD7 17-P-OA-B* ・iehnhHD410 HD5 n HD6 13 HD7"ISIS IIO1Y1 Al 1Y2 2 1Y3 A31Y4202Y1Bl mB2 2Y3 B3 2Y4B4< Lt»U$G LD4 H LD5 13 LD6 15LD7方IUX 2 2LD< 1 1U>S U 2LI>5刃1LD€ 21 24 30 14 19 5EF5 isux>SO$1 S'm ML»B\HDATAO ? \M>ATA1 4 \g>ATA2 f \HDATA3 t \HDATM 13 \HI>ATA5 14 \HDATA6 17 \HDAIA7 18HDO15T"Uli18 HDATAO 16 HDATA1 14 HDATA2 12 HDATA39 HDATA4 7 HDATA5 5 HDATA6 3 HDATA7o图1・1 (a) ALU电路图1-1 (b ) ALU 控制电路算术逻辑单元ALU 是由四}\ 74LS18I 构成。

计算机硬件技术实验指导书

计算机硬件技术实验指导书计算机硬件技术实验课程组编计算机技术基础实验室2008-5目录实验一存储器实验 (1)实验二运算器实验 (7)实验三:模型机实验 (12)实验四控制器实验 (21)实验五微程序实验 (31)实验六指令系统实验 (34)实验七多级流水线系统实验 (41)实验八8255A并行实验(一) (47)实验九8255A并行实验(二) (53)实验十8259中断实验 (57)实验十一定时/计数实验(一) (62)实验十二定时/计数实验(二) (67)实验十三8251串口实验(一) (73)实验十四8251串口实验(二) (80)实验十五A/D转换实验 (93)实验十六D/A转换实验 (99)实验一存储器实验(1)实验类别:综合性实验一、实验目的:1、熟悉存储器的组成结构、工作原理和工作流程;2、学会简单存储器的设计。

二、实验内容:1、认识存储器的组成结构和工作原理。

2、从输入设备输入数据和存储单元地址,将数据存储到指定地址单元。

3、从输入设备输入地址,将该地址的数据,发送到输出设备。

4、设计一个简单的存储器系统,完成基本的读写操作。

(要求有设计思路或原理,结构图,硬件设计,软件设计)三、实验要求1、了解只读存储器ROM的工作特性,掌握FPGA中lpm_ROM的设置和配置方法。

2、在QuartusII环境下编辑ROM配置文件“文件名.mif”,学习将程序代码以.mif格式文件加载于lpm_ROM中;3、在初始化存储器编辑窗口编辑mif文件配置ROM;4、验证FPGA中mega_lpm_ROM的功能。

5.掌握FPGA中存储器的设计方法和对存储器进行读写操作。

四、实验原理FPGA中有许多参数可设置的LPM (Library Parameterized Modules)参数化的模块库,可构成如lpm_rom、lpm_ram_io、lpm_fifo、lpm_ram_dq等存储器结构。

CPU中的重要部件,如RAM、ROM 可直接调用这些存储器。

第二节硬件实验指导书.docx

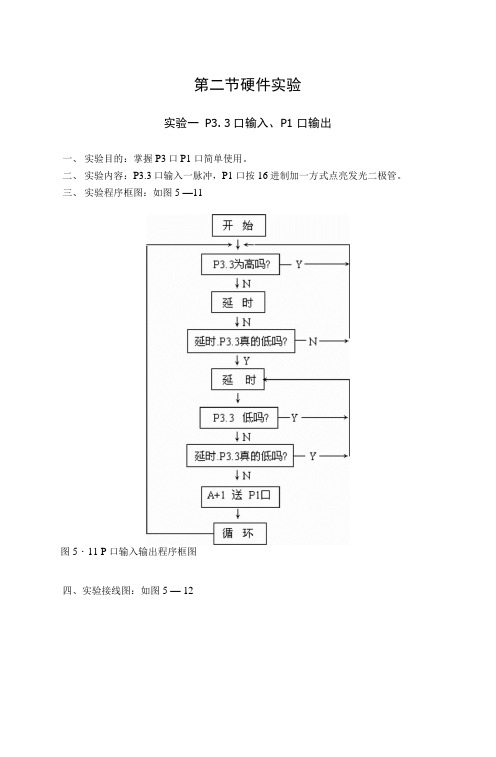

第二节硬件实验实验一P3. 3口输入、P1 口输出一、实验目的:掌握P3口P1 口简单使用。

二、实验内容:P3.3口输入一脉冲,P1 口按16进制加一方式点亮发光二极管。

三、实验程序框图:如图5 —11图5・11 P 口输入输出程序框图四、实验接线图:如图5 — 128031图5 — 12 P 口输入输出程序框图五、实验步骤:1.P3. 3 (即X10)用插针连至KI. P1. 0〜P1. 7用插针连至L8〜LI (P1.0〜P1. 7, 对应信号插孔为XO, X2, X3, X4, X5, X7, X8, X6)。

2.从起始地址0540H开始连续运行程序(输入0540后按EXEC键)。

3.开关K1每拨动一次,I」〜L8发光二极管接16进制方式加一点亮。

I」〜L8发光二极管按16进制方式加一闪亮。

实验二工业顺序控制一、实验目的:掌握工业顺序控制程序的简单编程,中断的使用。

二、实验预备知识:在工业控制屮,象冲压.注塑.轻纺.制瓶等生产过程,都是些断续牛产过程,按某种顺序有规律地完成预定的动作.対这类断续牛产过程的控制顺序控制,例注塑机工艺过程大致按“合模一注射一延时一开模一产伸一产退”顺序动作, 用单片机最易实现。

三、实验内容:8032的P1.0〜P1. 6控制注塑机的七道工序,现模拟控制七只发光二极管点亮,低电平有效,设定每道工序时间转换为延时,P3.4为开工启动开关,高电平启动。

P3. 3为外部故障输入模拟开关P3. 3为不断告警。

P1.7为报警声音输出,设定6道工序只有一位输出,第七道工序三位有输出。

四、实验程序框图:如图5—13 (a)、(b)关输出中断.P1.P3Q初化保护现场等开工工序1延时故障消除了吗?-N工序2延时恢复现场工序7延时返回图5-13(a)工业顺序控制主程序框图图5-13(b)中断服务子程序框图五、实验接线图:如图5 — 148831图5-14工业顺序控制实验接线图六、实验步骤:1.P3. 4(X18)连KI, P3. 3(X10)连K2, P1.0〜P1. 6(X0, X2, X3, X4, X5, X7, X8)分别连到L1〜L7, P1.7(X6)连VIN (电子音响输入端,即SIN)。

硬件描述语言实验报告

北京科技大学计算机与通信工程学院硬件描述语言实验报告专业:计算机科学与技术班级:学生姓名:学号:指导教师:实验地点:实验时间:2017 年月日~ 月日实验成绩:________________________________一、实验目的与实验要求1 实验目的(1)熟悉常用的EDA设计工具、设计流程,掌握前端设计要点;(2)通过简单的逻辑功能模块的设计,加深对硬件描述语言的理解和对逻辑设计的认识;(3)理解逻辑综合的概念,熟悉V erilog的编码风格,掌握可综合的逻辑设计;(4)训练组合逻辑设计、时序逻辑设计的能力,以及基本的设计验证能力。

2 实验要求(1)在有限的实验课内学时可能难以较好完成所有实验内容,因此将实验板分组下发,要求在实验课之外抽时间完成剩余实验内容;(2)对于每个实验都需要完成逻辑电路设计以及TestBench模块的编写,能够根据前仿真的波形图给粗结果分析;针对需要板子上验证的题目,需进一步给出相关控制逻辑的设计及板级验证说明。

(3)完成的每个实验需要在实验课内经指导教师或助教现场检查、解释波形及验证逻辑,回答指导教师提出的问题,以确保实验完成的质量;二、实验设备(环境)及要求实验室提供Windows 7操作系统下的Xilinx开发平台vivado2015.4环境,以及EGO开发板。

三、实验内容、步骤与结果分析1 实验11.1 实验内容设计一个周期为40个时间单位的时钟信号,其占空比为25%。

使用always和initial块进行设计。

将其在仿真0时刻的值初始化为0。

1.2 实验步骤源代码:`timescale 1ns / 1psmodule clock_40();output clock;endmodule1.3 结果分析Text bench 设计:module clock_40_tb();reg clock;initialclock<=0;alwaysbegin#30 clock<=1;#10 clock<=0;endendmodule周期为40个时间单位的时钟信号仿真波形截图验证说明:可以由图中看出该时钟产生占空比为25%的时钟波形。

可编程逻辑器件与硬件描述语言实验报告

可编程逻辑器件与硬件描述语言实验报告分组:第()组班级:学号:姓名:地点:时间:实验一:3-8译码器设计实验目的:1)掌握ISE开发工具的使用,掌握FPGA开发的基本步骤;2)掌握组合逻辑电路设计的一般方法;3)掌握程序下载方法,了解UCF文件的格式;4)初步了解开发板资源,掌握开发板使用方法。

重点了解滑动开关和LED显示灯的使用方法。

实验内容:用VHDL实现3-8译码器模块将程序下载到FPGA并进行检验实验步骤:1)启动ISE,新建工程文件,编写3-8译码器的VHDL模块;2)新建UCF文件,输入位置约束;3)完成综合、实现,生成下载文件;4)连接开发板USB下载线,开启开发板电源;5)下载到FPGA;6)拨动开关,验证结果是否正确。

实验代码:-- Company:-- Engineer:---- Create Date: 19:03:03 10/01/2011-- Design Name:-- Module Name: decoder38 - Behavioral-- Project Name:-- Target Devices:-- Tool versions:-- Description:---- Dependencies:---- Revision:-- Revision 0.01 - File Created-- Additional Comments:------------------------------------------------------------------------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;-- Uncomment the following library declaration if using-- arithmetic functions with Signed or Unsigned values--use IEEE.NUMERIC_STD.ALL;-- Uncomment the following library declaration if instantiating-- any Xilinx primitives in this code.--library UNISIM;--use UNISIM.VComponents.all;entity decoder38 isPort ( A : in STD_LOGIC;B : in STD_LOGIC;C : in STD_LOGIC;EN : in STD_LOGIC;Y : out STD_LOGIC_VECTOR (7 downto 0));end decoder38;architecture Behavioral of decoder38 issignal din: std_logic_vector(2 downto 0);begindin <= A&B&C;PROCESS(din,EN)beginif (EN='1') THENY <= "00000000";elsecase din iswhen "000" => y<="00000001";when "001" => y<="00000010";when "010" => y<="00000100";when "011" => y<="00001000";when "100" => y<="00010000";when "101" => y<="00100000";when "110" => y<="01000000";when "111" => y<="10000000";when others => y<="00000000";end case;end if;end process;end Behavioral;1.2、UCF文件:NET "y<7>" LOC = "F9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ; NET "y<6>" LOC = "E9" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ; NET "y<5>" LOC = "D11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ; NET "y<4>" LOC = "C11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;NET "y<3>" LOC = "F11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;NET "y<2>" LOC = "E11" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;NET "y<1>" LOC = "E12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;NET "y<0>" LOC = "F12" | IOSTANDARD = LVTTL | SLEW = SLOW | DRIVE = 8 ;NET "EN" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP ;NET "C" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP ;NET "B" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP ;NET "A" LOC = "N17" | IOSTANDARD = LVTTL | PULLUP ;实验结果:用滑动开关SW3~SW1作为输入A,B,C;滑动开关SW0控制EN;8个LED灯表示8个输出。

计算机硬件实验指导书

第一部分 EL实验系统的结构EL-l微机实验教学系统由功能实验板、可选的CPU板、二块小面包板三部分构成,可安装在45*30*10cm的实验箱内。

总框图如下:面包板:1)通用面包板2)金属圆孔组成的通用实验板CPU板:1)8086 PC总线板2)8086 CPU板3)8051 CPU板4)8098 CPU板5)80C198 CPU板功能实验板:由若干相对独立的功能接口电路组成,它们是:D/A电路、A/D 电路、发光二极管电路、开关量输入电路、RAM/ROM电路、简单I/O电路、 8253可编程定时器/计数器电路、8255并行接口电路、总线驱动电路、8279接口电路、单脉冲发生器、LED显示电路、键盘电路、复位电路、8250串行接口电路。

(一)功能实验板结构1、输出显示电路1)数码显示电路。

该电路由6位共阴极数码管,3片75452,2片74SL07组成, 74LS07为段驱动器,相应输入插孔为CZ4。

75452为位驱动器,相应输入插控为CZ3(LD1,LD2,LD3,LD4,LD5,LD6)。

2)LED灯显示电路。

该电路由2片74LS04,12只发光二极管(红、绿、黄各4只)组成。

12只二极管相应的输人插孔为CZ2(LI1,LI2,LI3,LI4,LI5,LI6,LI7,LI8,LI9,LI10,LIl1,LIl2)2、信号发生电路1)开关量输入电路:该电路由8只开关组成,每只开关有两个位置,一个位置代表高电平,一个位置代表低电平。

该电路的输出插孔为CZl(Kl,K2,K3,K4,K5,K6,K7,K8)。

2)时钟输入电路:该电路由1片74LSl6l组成:·当CPU为PC总线时,输入时钟为AT总线的CLK,·当CPU为805l、8098、80C198时,CLK的输入时钟为晶振频率,·当CPU为8086时,CLK是2MHz。

输出时钟为该CLK的2分频(CLK0),4分频(CLKI),8分频(CLK2),16分频(CLK3),相应输出插孔CZ47(CLK0,CLKl,CLK2,CLK3)。

硬件描述语言与EDA技术实验指导书

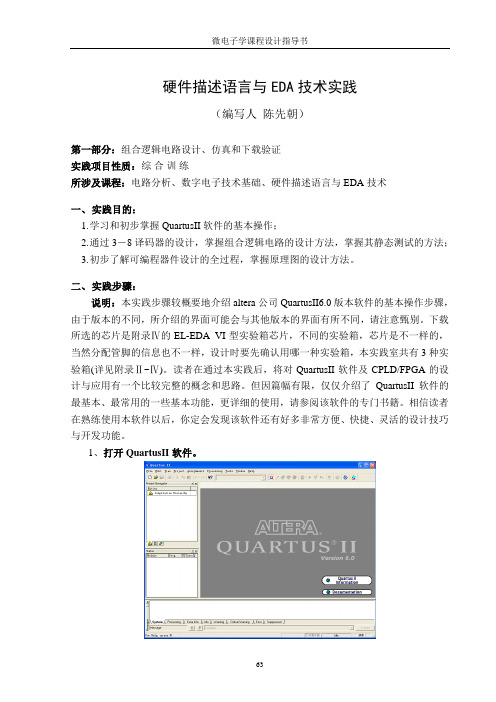

硬件描述语言与EDA技术实践(编写人陈先朝)第一部分:组合逻辑电路设计、仿真和下载验证实践项目性质:综合训练所涉及课程:电路分析、数字电子技术基础、硬件描述语言与EDA技术一、实践目的:1.学习和初步掌握QuartusII软件的基本操作;2.通过3-8译码器的设计,掌握组合逻辑电路的设计方法,掌握其静态测试的方法;3.初步了解可编程器件设计的全过程,掌握原理图的设计方法。

二、实践步骤:说明:本实践步骤较概要地介绍altera公司QuartusII6.0版本软件的基本操作步骤,由于版本的不同,所介绍的界面可能会与其他版本的界面有所不同,请注意甄别。

下载所选的芯片是附录Ⅳ的EL-EDA_VI型实验箱芯片,不同的实验箱,芯片是不一样的,当然分配管脚的信息也不一样,设计时要先确认用哪一种实验箱,本实践室共有3种实验箱(详见附录Ⅱ~Ⅳ)。

读者在通过本实践后,将对QuartusII软件及CPLD/FPGA的设计与应用有一个比较完整的概念和思路。

但因篇幅有限,仅仅介绍了QuartusII软件的最基本、最常用的一些基本功能,更详细的使用,请参阅该软件的专门书籍。

相信读者在熟练使用本软件以后,你定会发现该软件还有好多非常方便、快捷、灵活的设计技巧与开发功能。

1、打开QuartusII软件。

2、选择路径。

选择File/New Project Wizard,指定工作目录,指定工程和顶层设计实体名称。

每设计一个项目,都应指定一个相应的目录,便于管理,因为在后面的编译、仿真与验证过程中,会产生许多相关文件。

单击“Next”。

注意:工作目录名、工程名、文件名不能有中文,也不能与库中已有的基本器件名相同,否则编译会出错。

3、添加设计文件。

如果有已经建立好的VHDL或者原理图等文件可以在File name中选择路径然后添加,或者选择Add All添加所有可以添加的设计文件(.VHDL,.Verilog,原理图等)。

如果没有直接点击“Next”,等建立好工程后再添加也可。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

硬件描述语言及器件实验指导书电子科学与技术专业组实验一用硬件描述语言的方法设计一个三输入与门电路一、实验目的1、掌握MAX+plusII的使用方法。

2、掌握VHDL语言程序的基本结构。

2、掌握使用硬件描述语言设计数字电路的方法和步骤。

3、掌握用硬件描述语言设计三输入与门电路的方法。

二、实验器材1.台式计算机 1台。

2.可编程逻辑逻辑器件实验软件1套。

3.下载电缆一套。

4.示波器一台。

三、实验说明1.台式计算机用于向可编程逻辑逻辑器件实验软件提供编程、仿真、下载的平台,供用户使用。

2.可编程逻辑逻辑器件实验软件向原理图的设计提供平台,并将调试好的原理图下载到可编程逻辑逻辑器件中。

3.下载电缆是可编程逻辑器件软件和可编程逻辑逻辑器件之间的接口电缆,为了便于区别,用不同颜色导线区分下载电缆的电源、地和信号,一般用红色导线接电源,用黑色导线接地。

4.示波器用于观察可编程逻辑器件执行程序时输出信号的变化。

四、实验内容与要求用硬件描述语言的方法设计一个三输入与门电路,要求:(1)根据三输入与门的逻辑表达式,在构造体中直接使用并行赋值语句实现,并进行仿真;(2)根据三输入与门的真值表,在构造体中使用进程语句实现,并进行仿真;五、实验步骤(下面七个的实验的软件的使用具体步骤跟本次试验一样不再详述)1.打开新建菜单选择“text edtior file”,这个文件是写程序编程用的。

2.程序写完后点“保存”,注意(1)保存的格式是.vhd,(2)保存的地址不能是桌面和硬盘的根目录,否则在后面的编程将出现错误。

程里,能够正常编译和下载。

4.在“assign→device”选择下载设备的芯片型号,如果芯片型号选错将导致以后能编译成功但下载到实验箱时无法正常工作。

5.在“max+plux”中选择“compiler”进行编译。

“MAX+PLUS—waveform editor”做波形仿真7.点击鼠标右键选择“enter nodes from SNF”,选择输入A,B,C和输出管脚F,点击8.在file→projectset→ project to current file ,这步是将文件设置在工程里,能够进行正常的仿真,否则后面的过程将不能进行9.点击如图所示按键设置输入管脚A,B,C的时钟周期,点击“MAX+PLUS”中simulator 进行仿真,观察结果是否和预设的一样。

将输入管脚A,B,C和输出管脚F拖到芯片管脚中的I/O管脚中11.点击“MAX+PLUS”中programmer,在hardware type 中选择byte blaster (mv),parallel port 选择LPT1 进行下载。

其他方式都会出现错误。

六、实验报告要求1、整理实验结果,填写实验报告。

2、小结实验心得体会。

实验二用硬件描述语言的方法设计一个三-八译码器一、实验目的1.掌握IF语句和CASE语句的使用方法。

2.掌握用硬件描述语言设计三-八译码器的方法。

二、实验器材1.台式计算机 1台。

2.可编程逻辑逻辑器件实验软件1套。

3.下载电缆一套。

4.示波器一台。

三、实验说明1.台式计算机用于向可编程逻辑逻辑器件实验软件提供编程、仿真、下载的平台,供用户使用。

2.可编程逻辑逻辑器件实验软件向原理图的设计提供平台,并将调试好的原理图下载到可编程逻辑逻辑器件中。

3.下载电缆是可编程逻辑器件软件和可编程逻辑逻辑器件之间的接口电缆,为了便于区别,用不同颜色导线区分下载电缆的电源、地和信号,一般用红色导线接电源,用黑色导线接地。

4.示波器用于观察可编程逻辑器件执行程序时输出信号的变化。

四、实验内容与要求根据三-八译码器的真值表,用硬件描述语言的方法设计一个三-八译码器,要求:(1)使用IF语句实现,并进行仿真;(2)使用CASE语句实现,并进行仿真;五、实验步骤1.打开MAX+PLUS软件,点击“file”中“new”建立“text edtior file”文档并输入该实验的程序。

2.选择菜单“File”→“Save As”,选择为自己建立的工程文件夹,将已编程好的程序保存(注意后缀是.vhd)在此文件夹内。

注意:文件夹名不能用中文,且不可带空格。

3.在“project”中设置“set project to current file”把文档设置在工程下,否则会在时出现错误。

4.选择“Assign”菜单中“Device”项,弹出Device对话框,在Device对话框中选择实验箱上的芯片型号。

注意如果芯片型号选择错误,后面的过程一定会出现错误。

5.选择“max+plus”菜单中“complier”对实验程序进行编译,检查程序是否有错误。

出现warning时有时可以忽略不计,但出现错误一定要及时修改直至无错误出现。

6.选择“max+plus”菜单中“waveform editor”,将设置输入、输出管脚的初值和其周期,观察结果是否符合实验要求,如不符合要修改程序来满足实验要求。

7.在“project”中设置“set project to current file”把文档设置在程序编程所在的工程下,否则会在时出现错误。

8.选择“MAX+PLUS”中“Floorplan editor”,设置输入、输出管脚在芯片I/O 上。

9.选择菜单MAX+plus中“Programmer”,同时在Options菜单上选中 Hardware Setup,在Hardware Type 中,选择ByteBlaster,在Parallel Port中,选择LPT1,然后按OK,此时硬件连接完毕。

观察实验箱结果是否符合实验要求,并记录实验结果。

六、实验报告要求1、整理实验结果,填写实验报告。

2、小结实验心得体会。

实验三用硬件描述语言的方法设计一个D触发器一、实验目的1、掌握同步复位和异步复位的实现方法。

2、掌握用硬件描述语言表示上升沿和下降沿的方法。

3、掌握用硬件描述语言设计D触发器的方法。

二、实验器材1.台式计算机 1台。

2.可编程逻辑逻辑器件实验软件1套。

3.下载电缆一套。

4.示波器一台。

三、实验说明1.台式计算机用于向可编程逻辑逻辑器件实验软件提供编程、仿真、下载的平台,供用户使用。

2.可编程逻辑逻辑器件实验软件向原理图的设计提供平台,并将调试好的原理图下载到可编程逻辑逻辑器件中。

3.下载电缆是可编程逻辑器件软件和可编程逻辑逻辑器件之间的接口电缆,为了便于区别,用不同颜色导线区分下载电缆的电源、地和信号,一般用红色导线接电源,用黑色导线接地。

4.示波器用于观察可编程逻辑器件执行程序时输出信号的变化。

四、实验内容与要求用硬件描述语言的方法设计一个D触发器,要求:(1)实现异步复位/置位、上升沿触发的D触发器,并进行仿真;(2)实现同步复位/置位、下降沿触发的D触发器,并进行仿真;五、实验步骤1.打开MAX+PLUS软件,点击“file”中“new”建立“text edtior file”文档并输入该实验的程序。

2.选择菜单“File”→“Save As”,选择为自己建立的工程文件夹,将已编程好的程序保存(注意后缀是.vhd)在此文件夹内。

注意:文件夹名不能用中文,且不可带空格。

3.在“project”中设置“set project to current file”把文档设置在工程下,否则会在时出现错误。

4.选择“Assign”菜单中“Device”项,弹出Device对话框,在Device对话框中选择实验箱上的芯片型号。

注意如果芯片型号选择错误,后面的过程一定会出现错误。

5.选择“max+plus”菜单中“complier”对实验程序进行编译,检查程序是否有错误。

出现warning时有时可以忽略不计,但出现错误一定要及时修改直至无错误出现。

6.选择“max+plus”菜单中“waveform editor”,将设置输入、输出管脚的初值和其周期,观察结果是否符合实验要求,如不符合要修改程序来满足实验要求。

7.在“project”中设置“set project to current file”把文档设置在程序编程所在的工程下,否则会在时出现错误。

8.选择“MAX+PLUS”中“Floorplan editor”,设置输入、输出管脚在芯片I/O 上。

9.选择菜单MAX+plus中“Programmer”,同时在Options菜单上选中 Hardware Setup,在Hardware Type 中,选择ByteBlaster,在Parallel Port中,选择LPT1,然后按OK,此时硬件连接完毕。

观察实验箱结果是否符合实验要求,并记录实验结果。

六、实验报告要求1、整理实验结果,填写实验报告。

2、小结实验心得体会。

实验四用硬件描述语言的方法设计一个分频器一、实验目的1、掌握各种分频器的设计思路2、掌握用硬件描述语言设计各种分频器的方法二、实验器材1.台式计算机 1台。

2.可编程逻辑逻辑器件实验软件1套。

3.下载电缆一套。

4.示波器一台。

三、实验说明1.台式计算机用于向可编程逻辑逻辑器件实验软件提供编程、仿真、下载的平台,供用户使用。

2.可编程逻辑逻辑器件实验软件向原理图的设计提供平台,并将调试好的原理图下载到可编程逻辑逻辑器件中。

3.下载电缆是可编程逻辑器件软件和可编程逻辑逻辑器件之间的接口电缆,为了便于区别,用不同颜色导线区分下载电缆的电源、地和信号,一般用红色导线接电源,用黑色导线接地。

4.示波器用于观察可编程逻辑器件执行程序时输出信号的变化。

四、实验内容与要求用硬件描述语言的方法设计一个分频器,要求:(1)实现四分频器,并进行仿真;(2)实现五分频器,并进行仿真;五、实验步骤1.打开MAX+PLUS软件,点击“file”中“new”建立“text edtior file”文档并输入该实验的程序。

2.选择菜单“File”→“Save As”,选择为自己建立的工程文件夹,将已编程好的程序保存(注意后缀是.vhd)在此文件夹内。

注意:文件夹名不能用中文,且不可带空格。

3.在“project”中设置“set project to current file”把文档设置在工程下,否则会在时出现错误。

4.选择“Assign”菜单中“Device”项,弹出Device对话框,在Device对话框中选择实验箱上的芯片型号。

注意如果芯片型号选择错误,后面的过程一定会出现错误。

5.选择“max+plus”菜单中“complier”对实验程序进行编译,检查程序是否有错误。

出现warning时有时可以忽略不计,但出现错误一定要及时修改直至无错误出现。

6.选择“max+plus”菜单中“waveform editor”,将设置输入、输出管脚的初值和其周期,观察结果是否符合实验要求,如不符合要修改程序来满足实验要求。