直接数字频率合成器quartus

直接数字频率合成器quartus

电子线路课程设计直接数字频率合成器学号::2011年11月摘要本篇论文主要讲了用eda设计dds。

用quartus 软件模拟仿真电路,并下载到芯片。

使电路能输出正余弦波,并可调节频率和相位。

并在这根底上进展一局部扩展,如能输入矩形三角形波。

关键词eda设计 dds quartusAbstract:This report introduces the EDA design is pleted with Direct DigitalSynthesis DDS process. This design uses DDS QuartusII 7.0 software design, and downloads SmartSOPC experimental system hardware.Key word eda design dds quartus目录设计要求 (4)方案论证 (4)各子模块设计原理 (6)调试,仿真与下载 (12)结论 (13)一.设计要求根本要求:1、利用QuartusII软件和SmartSOPC实验箱实现DDS的设计;2、DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的RAM 实现,RAM结构配置成212×10类型;3、具体参数要求:频率控制字K取4位;基准频率fc=1MHz,由实验板上的系统时钟分频得到;4、系统具有使能功能;5、利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正弦波形;6、过开关〔实验箱上的Ki〕输入DDS的频率和相位控制字,并能用示波器观察加以验证;提高局部:1、通过按键〔实验箱上的Si〕输入DDS的频率和相位控制字,以扩大频率控制和相位控制的围;(注意:按键后有消颤电路)2、能够同时输出正余弦两路正交信号;3、在数码管上显示生成的波形频率;4、充分考虑ROM结构与正弦函数的特点,进展合理的配置,提高计算精度;5、设计能输出多种波形〔三角波、锯齿波、方波等〕的多功能波形发生器;6、基于DDS的AM调制器的设计;7、自己添加其他功能。

直接数字频率合成器原理

直接数字频率合成器原理直接数字频率合成器(Direct Digital Frequency Synthesizer,简称DDFS)是一种用于产生高精度、稳定的频率信号的电子设备。

它通过数字电路实现频率的直接合成,可以产生任意频率的信号,并且具有快速调谐、高精度以及低相位噪声等优点。

本文将介绍DDFS的工作原理及其在实际应用中的重要性。

一、工作原理DDFS的核心组成部分是相位累加器(Phase Accumulator)、频率控制字(Frequency Control Word)和查表器(Look-up Table)。

相位累加器通过不断累加频率控制字的值,从而产生一个随时间线性增加的相位值。

查表器中存储了正弦波的采样值,通过查表器可以根据相位值得到对应的正弦波样本。

最后,通过数模转换器将数字信号转换为模拟信号输出。

具体来说,DDFS的工作原理如下:1. 频率控制字:频率控制字是一个二进制数,用于控制相位累加器的累加速度。

频率控制字的大小决定了相位累加器每个时钟周期累加的值,从而决定了输出信号的频率。

2. 相位累加器:相位累加器是一个寄存器,用于存储当前的相位值。

相位累加器的值会在每个时钟周期根据频率控制字的大小进行累加。

相位累加器的位数决定了相位的分辨率,位数越多,相位分辨率越高,输出信号的频率分辨率也越高。

3. 查表器:查表器中存储了一个周期内的正弦波样本值(或余弦波样本值),通过查表器可以根据相位累加器的值得到对应的正弦波样本值。

4. 数模转换器:数模转换器将数字信号转换为模拟信号输出。

通常使用的是高速数模转换器,能够将数字信号以高速率转换为模拟信号输出。

二、应用领域DDFS在许多领域中都有广泛的应用,其中包括通信、雷达、测量、音频处理等。

1. 通信领域:在通信系统中,DDFS被广泛应用于频率合成器、频率调制器和频率解调器等模块中。

通过DDFS可以快速、精确地合成所需的信号频率,实现高速数据传输和频谱分析等功能。

DDS实验报告

电子线路课程设计 --直接数字频率合成器(DDS)2014 年 11 月摘要本实验通过使用 QuartusⅡ软件,并结合数字逻辑电路的知识设计,使用DDS 的方法设计一个任意频率的正弦信号发生器,要求具有频率控制、相位控制、以及使能开关等功能。

在此基础上,本实验还设计了扩展功能,包括测频、切换波形,动态显示。

在控制电路的作用下能实现保持、清零功能,另外还能同时显示输出频率、相位控制字、频率控制字。

在利用 QuartusⅡ进行相应的设计、仿真、调试后下载到SmartSOPC实验实现 D/A转换,验证实验的准确性,并用示波器观察输出波形。

关键词:SmartSOPC实验箱 QUARTUSⅡ数字频率合成仿真AbstractThis experiment is based on QuartusⅡ,with the help of knowledge relating to the digital logic circuits and system design,to design a sine signal generator which generates any frequency by the method of DDS. This generator is provided with the functions of frequency control,phase control and switch control. Based on the basic design,I also design extra functions,including frequency measurement,changes of wave forms and dynamic display.The control circuit can be maintained time clearing and time keeping functions,and also shows the output frequency,phase control characters,frequency control word. All the designing and simulating work are based on QuartusⅡ. After all the work finished on computer, I downloaded the final circuit to SmartSOPC experiment system to realize the transformation of D/A ,and then test the accuracy of the design by means of oscilloscope observing the wave forms.Key words: SmartSOPC QUARTUSⅡ DDS Simulation目录摘要 (1)目录 (2)一、设计要求 (3)二、方案论证 (3)三、直接数字频率合成器总电路图 (4)四、各子模块设计原理及分析说明 (5)4.1、脉冲发生电路 (5)4.2、频率相位预置与调节电路 (9)4.3、累加器电路 (10)4.4、相位控制电路 (11)4.5、波形存储器ROM电路 (12)4.6、测频电路 (14)4.7、不同波形选择电路 (15)4.8、动态译码显示电路 (16)五、程序下载、仿真与调试 (17)六、实验结果 (18)七、实验总结与感想 (23)八、参考文献 (23)一、设计要求1、利用QuartusII软件和SmartSOPC实验箱实现直接数字频率合成器(DDS)的设计;2、DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的RAM 实现,RAM结构配置成212×10类型;3、具体参数要求:频率控制字K取4位;基准频率fc=1MHz,由实验板上的系统时钟分频得到;4、系统具有使能功能;5、利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正弦波形;6、通过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证;7、可适当添加其他功能二、方案论证直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

直接数字频率合成芯片-概述说明以及解释

直接数字频率合成芯片-概述说明以及解释1.引言1.1 概述在概述部分,我们将介绍直接数字频率合成芯片的基本概念和作用。

直接数字频率合成芯片(Direct Digital Frequency Synthesizer,DDS)是一种用于产生不同频率信号的集成电路。

基于数字信号处理技术,DDS 芯片可以精确地生成各种频率和相位的信号。

相较于传统的模拟频率合成方法,DDS芯片具有更高的稳定性、精度和灵活性。

DDS芯片的工作原理基于数学算法和数字信号处理技术。

通过将数字信息转换为模拟信号输出,DDS芯片可以产生具有精确频率和相位的信号波形。

其核心部件包括相位积累器、数字控制振荡器和数模转换器。

相位积累器负责积累相位信息,数字控制振荡器则通过控制相位积累器的速率来实现不同频率信号的生成。

最后,数模转换器将数字信号转换为模拟信号输出。

直接数字频率合成芯片具有广泛的应用领域。

在通信系统中,DDS芯片被广泛应用于频率合成器、频率调制器、信号发生器等设备中。

其高精度和频率可调性使其成为无线通信、雷达、医学成像以及科学研究等领域的重要组成部分。

此外,DDS芯片还可以用于频率跟踪和频率锁定的系统中,提供更好的稳定性和精度。

总而言之,直接数字频率合成芯片通过数字信号处理技术实现高稳定性、精确性和灵活性的频率合成。

它在通信系统、科学研究和医学成像等领域具有广泛的应用前景。

随着科技的不断进步,我们可以期待直接数字频率合成芯片在未来的发展中发挥更重要的作用。

1.2 文章结构本文的结构主要分为引言、正文和结论三个部分。

在引言部分,我们将概述直接数字频率合成芯片,解释其基本原理和应用领域,并阐述本文的目的。

接着,在正文部分,首先我们将详细介绍直接数字频率合成芯片的原理,包括其工作原理、数字信号处理流程以及关键技术。

其次,我们将探讨直接数字频率合成芯片的应用领域,包括通信、雷达、电子音乐等方面,并论述其在各个领域中的优势和局限性。

最后,在结论部分,我们将总结直接数字频率合成芯片的优势,包括其高精度、灵活性强以及节省硬件开销等方面,并展望其未来的发展方向,包括对数字信号处理算法的优化、功耗降低以及更广泛的应用领域等方面的潜力。

直接数字频率合成器(DDS)总结

直接数字频率合成器(直接数字频率合成器(DDS DDS DDS)总结)总结知识收集2008-07-2113:45:46阅读128评论0字号:大中小订阅直接合成法是用一个或多个石英晶体振荡器的振荡频率作为基准频率,由这些基准频率产生一系列的谐波,这些谐波具有与石英晶体振荡器同样的频率稳定度和准确度;然后,从这一系列的谐波中取出两个或两个以上的频率进行组合,得出这些频率的和或差,经过适当方式处理(如经过滤波)后,获得所需要的频率。

DDS 是直接数字式频率合成器(Direct Digital Synthesizer )的英文缩写。

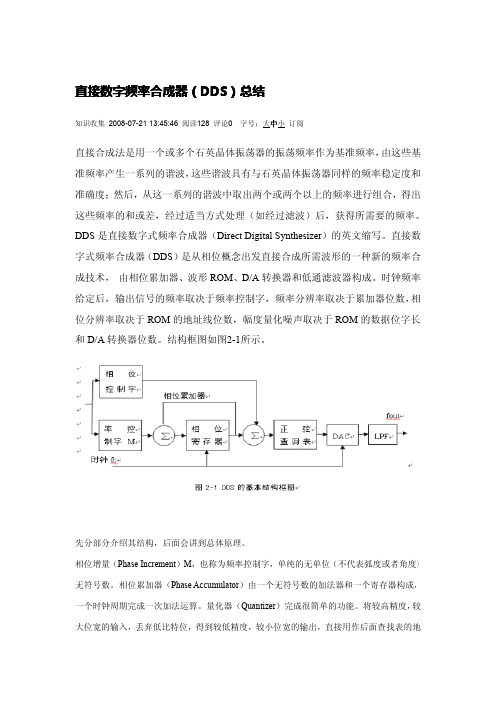

直接数字式频率合成器(DDS )是从相位概念出发直接合成所需波形的一种新的频率合成技术,由相位累加器、波形ROM 、D/A 转换器和低通滤波器构成。

时钟频率给定后,输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM 的地址线位数,幅度量化噪声取决于ROM 的数据位字长和D/A 转换器位数。

结构框图如图2-1所示。

先分部分介绍其结构,后面会讲到总体原理。

相位增量(Phase Increment )M ,也称为频率控制字,单纯的无单位(不代表弧度或者角度)无符号数。

相位累加器(Phase Accumulator )由一个无符号数的加法器和一个寄存器构成,一个时钟周期完成一次加法运算。

量化器(Quantizer )完成很简单的功能。

将较高精度,较大位宽的输入,丢弃低比特位,得到较低精度,较小位宽的输出,直接用作后面查找表的地址。

正余弦查找表(Sine/Cosine Lookup Table)存放正余弦数值。

DDS的工作原理:DDS的基本原理是利用采样定理,通过查表法产生波形[2]。

由于,(2-1)其中Δθ为一个采样间隔ΔT之间的相位增量,采样周期,即:(2-2)控制Δθ就可以控制不同的频率输出。

Δθ是由频率控制字M控制的,即:(2-3)所以改变M就可以得到不同的输出频率。

直接数字频率合成器的优化技术研究

直接数字频率合成器的优化技术研究郑利文【摘要】详细阐述了利用QuartusⅡ实现直接数字频率合成器(DDS)的方法和步骤.分析了DDS的设计原理,采用多级流水线控制技术对DDS相位累加器进行了优化,利用存储对称波形方法对波形存储表进行了优化,并在开发环境下进行了功能仿真,选用现场可编程器件FPGA作为目标器件,得到了可以重构的IP核,实现了复杂的调频功能.利用该方法实现的DDS模块具有更广泛的实际意义和更良好的实用性.【期刊名称】《现代电子技术》【年(卷),期】2010(033)018【总页数】3页(P143-144,159)【关键词】DDS;相位累加器;波形存储表;Quartus Ⅱ【作者】郑利文【作者单位】中国中铁一局有限责任公司,陕西,西安,710054【正文语种】中文【中图分类】TN74-34直接数字频率合成技术(direct digital frequency synthesize,DDS或DDFS)是第三代频率合成技术。

它采用全数字技术,并从相位角度进行频率合成。

DDS具有相对带宽宽,频率转换时间短,频率分辨率高,输出相位连续,可产生宽带正交信号以及其他多种调制信号,控制灵活方便,性价比高等特点[1]。

本文采用多级流水线控制技术对DDS相位累加器进行了优化,利用存储对称波形方法对波形存储表进行了优化,并在开发环境下对其进行了功能仿真,选用现场可编程器件FPGA作为目标器件,得到可以重构的IP核,实现了复杂的调频功能。

1 DDS基本原理目前,常用的直接数字频率合成器是波形存储DDS [2-10]。

它不同于以前的频率合成概念,即不是从对频率进行加、减、乘、除运算的角度进行频率合成的,而是从相位的概念根据式(1)进行频率合成的。

(1)式(1)中将2π的相位均匀量化M份,实际中,M=2N;fc为采样频率;K为常量,满足K/M,M<1/2。

2 相位累加器的优化设计相位累加器用来实现线性数字信号的逐级累加,信号范围从0加到累加器的满偏值。

毕业设计(论文)-直接数字频率合成器设计[管理资料]

![毕业设计(论文)-直接数字频率合成器设计[管理资料]](https://img.taocdn.com/s3/m/fe683c28ce2f0066f433225f.png)

直接数字频率合成器设计The Design of Direct Digital Frequency Synthesizer摘要利用可编程逻辑阵列FPGA(Field Programmable Gate Array)实现DDS专用电路芯片,主要特点是能满足用户对特殊功能的要求,而且在使用过程中也灵活地改变系统结构。

,并不能满足所有的要求。

本文在对现有DDS技术的大量文献调研的基础上,提出了符合FPGA结构的DDS设计。

方案利用QuartusⅡ开发工具在ALTERA FLEX10K系列器件上进行了实现。

关键词直接数字频率合成器单片机数模转换温度漂移补偿AbstractThe main features of realization of dedicated direct digital frequency synthesizer circuit chips using FPGA are the ability to meet user requirements for special functions, but also flexibility change structural of the system in the use of the process. Although commercial DDS dedicated chip circuit provide a lot of opportunities for the designers and meet the needs of many occasions, there are its limitations and cannot meet all the requirements. On a large number of investigation of existing research literature,the papers involves the proposed structure of the direct digital frequency synthesizer FPGA design. The Programmer uses the Quartus II development tool for designing the Altera FLEX10K series devices.Keywords DDS MCU DAC Temperature drift compensation目录前言 (1)第1章设计思路及原理 (2)研究意义 (2)总体设计任务 (2)设计思路及原理 (3)DDS工作原理框图 (3)具体工作过程 (3)第2章系统电路的设计及原理 (5)系统框图 (5)各模块具体实现原理分析和说明 (5)相位累加器模块 (5)ROM查找表模块 (10)单片机输入输出控制模块 (12)温漂误差补偿 (13)D/A转换模块 (18)滤波输出电路模块 (19)软件仿真结果 (19)第3章硬件电路的构建 (21)FPGA芯片的选择与使用 (21)硬件连接电路图 (23)第4章实验开发系统系统 (25)实验开发系统的选择与使用 (25)实验过程与结果分析 (27)总结....................................................................................... 错误!未定义书签。

FPGA技术-直接数字频率合成器

COMPONENT REG32B PORT ( LOAD : IN STD_LOGIC; DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0); DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END COMPONENT; COMPONENT REG10B

接下页

PORT ( LOAD : IN STD_LOGIC;

DIN : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );

END COMPONENT;

COMPONENT ADDER32B

PORT ( A : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

B : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

S : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END COMPONENT;

COMPONENT SIN_ROM

PORT ( address : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

inclock

: IN STD_LOGIC ;

接下页

q

: OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );

END COMPONENT;

SIGNAL F32B,D32B,DIN32B : STD_LOGIC_VECTOR(31 DOWNTO 0);

为了对进行数字量化,把切割成2N份,由此每个clk周期的 相 为整数

实现直接数字频率合成器的种技术方案

实现直接数字频率合成器的种技术方案数字频率合成器是指一种非常重要的电子技术设备,其可以将高精度的数字信号转化为高质量的模拟信号,并通过模拟电路将这些信号输出,使得它们可以被人类感知。

实现直接数字频率合成器的技术方案有很多,本文将会详细介绍其中几种方案。

首先,最基本的方案是采用数字锁相环(,简称PLL)来实现直接数字频率合成器。

PLL技术已经被广泛应用于数字电路中,不仅可以实现同步,还可以通过比较、过滤和放大的方式将输入信号与参照信号进行比较,从而实现频率合成。

在此方法中,数字信号由一个ARB(任意波形发生器)产生,然后通过一个分频器进行分频,得到一个低频数字信号。

然后,这个低频数字信号以作为输入信号,通过两个锁相环(一个主锁相环,一个辅助锁相环)进行比较和过滤,最终输出高质量的数字信号。

这种方案非常简单,低成本、功耗低,适用于低频合成,但缺点是精度较低。

第二种方案是数字信号处理器(DSP)。

为了实现更高精度和更高的频率合成,可以采用DSP来实现。

首先,数字信号由一个ARB产生,并通过高速ADC进行采样。

然后,DSP通过数字滤波器等技术将这些数字信号进行处理,最终输出精度高、频率高的数字信号。

这种方案的优点是可以实现高精度、高频率的数字信号合成,但缺点是复杂度高、功耗大。

第三种方案是FPGA(现场可编程门阵列)。

FPGA相当于一个可编程的芯片,在硬件上实现数字信号处理和频率合成这两个功能。

这种方案的优点是高度灵活、可修改、功耗低,可实现多路复用,缺点是工程量大、难度较高。

总的来说,实现直接数字频率合成器的技术方案有很多,具体的方案应根据具体的应用场景和需要来确定。

如果需要实现低成本、低功耗的低频率合成,则可以采用PLL技术的方案。

如果需要实现高精度、高频率的数字信号合成,则可以采用DSP的方案。

如果需要更高的灵活性和可修改性,则可以采用FPGA的方案。

数字频率合成器原理

数字频率合成器原理

数字频率合成器(DigitalFrequencySynthesizer)是一种电子设备,用于产生高精度和可调节的频率信号。

其原理基于数字信号处理技术和参考时钟信号。

数字频率合成器的工作原理如下:

1.参考时钟:数字频率合成器首先接收一个高精度稳定的参考时钟信号,通常是一个晶体振荡器提供的恒定频率信号。

这个参考时钟作为系统的时基。

2.相位积累器:参考时钟信号经过相位积累器,对其相位进行连续的积累。

相位积累器根据所需输出频率的要求,按照一定的步进值或相位增量来累加相位。

每个时钟周期,相位积累器的相位都会根据步进值逐渐增加,并形成一个随时间线性增长的相位。

3.相位加法器:相位积累器的输出与一个可编程的相位加法器进行相位叠加。

该相位加法器接收用户输入的频率控制字(FrequencyControlWord),用于设定所需频率的分辨率和范围。

在每个时钟周期中,相位加法器将相位积累器的输出相位与频率控制字相加,得到一个新的相位。

4.数字到模拟转换器(DAC):经过相位加法器得到的新相位被输

入到数字到模拟转换器中,将其转换为连续的模拟信号。

这个模拟信号的频率由相位积累器的输出相位和频率控制字来决定。

5.滤波器:通过一个低通滤波器对模拟信号进行滤波,去除高频噪声,得到所需频率信号的纯净输出。

滤波后的信号即为数字频率合成器的输出信号。

由于数字频率合成器采用数字信号处理技术,可以精确控制输出频率,并具有较低的抖动和相位噪声。

它在电子通信、射频信号生成、音频合成等领域有广泛应用。

EDA 课程设计 江西理工 应科院 直接数字频率合成器(DDS)

SOPC/EDA综合课程设计直接数字频率合成器学院:江西理工大学应用科学学院指导老师:王忠峰专业班级:电气081姓名:qq411523540学号:时间:2011年1月目录第一章直接数字频率合成器与设计任务 (3)1.1关于直接数字频率合成器 (3)1.2直接数字频率合成器的设计要求 (3)第二章系统设计方案 (4)2.1 DDS的工作原理 (4)2.2模块的功能 (6)2.3选择器件 (7)2.4功能模块 (8)2.5系统的整体组装 (13)第三章设计的心得体会 (16)附录一参考文献 (17)第一章直接数字频率合成器与设计任务1.1 关于直接数字频率合成器1971年,美国学者J.Tierncy、C.M.Reader和B.Gold提出了以全数字技术从相位概念出发直接合成所需波形的一种新的频率合成原理。

随着技术和水平的提高,一种新的频率合成技术——直接数字频率合成(DDS,Direct Digital Synthesis)技术得到了飞速发展。

DDS技术是一种把一系列数字形式的信号通过DAC转换成模拟形式的信号合成技术,目前使用最广泛的一种DDS方式是利用高速存储器作查找表,然后通过高速DAC输出已经用数字形式存入的正弦波。

DDS技术具有频率切换时间短(<20 ns),频率分辨率高(0.01 Hz),频率稳定度高,输出信号的频率和相位可以快速程控切换,输出相位可连续,可编程以及灵活性大等优点,它以有别于其他频率合成方法的优越性能和特点成为现代频率合成技术中的佼佼者。

DDS广泛用于接受机本振、信号发生器、仪器、通信系统、雷达系统等,尤其适合跳频无线通信系统。

1.2 直接数字频率合成器的设计要求直接数字频率综合技术,即DDS技术,是一种新型的频率合成技术和信号产生方法。

利用EDA技术和FPGA实现直接数字频率合成器DDS的设计。

设计要求:1.利用QuartusII软件实验箱实现DDS的设计;2.通过实验箱上的开关输入DDS的频率和相位控制字,并能用示波器观察加以验证;3.系统具有清零和使能的功能;4.DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的ROM实现。

直接数字频率合成器的CPLD设计及QuartusⅡ与MATLAB联合仿真

( 渭南师范学院 物理与 电子工程系 , 陕西 渭南 74 0 ) 10 0

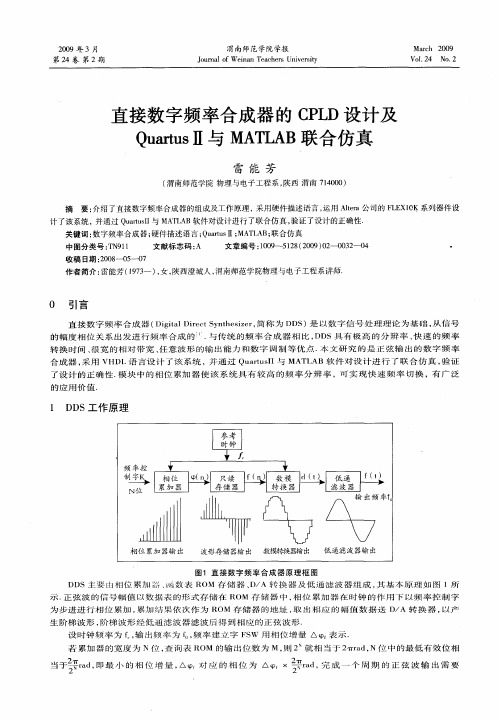

摘 要: 介绍了直接数字频率合成器 的组成及工作原理 ,采用 硬件描述语 言 , 运用 A e hr a公司的 F E O L XIK系列器件设

计了该系统 , 并通过 Q ats 与 M T A ur l uI A L B软件对设计进行 了联合仿真 , 验证 了设计 的正确性. 关键词 : 数字频率合成器 ; 硬件描述语言 ; u ̄ s MA L B 联合仿真 Q a u Ⅱ; T A ;

—

LI R A R Y i B eee:

64 U SE e i ee.s d l t ogi l1 c .A LL ;

_ _

US i e . t o i — rt ALL ; E e e sdJ g c a ih.

E N' TY f FI un t I ext S

_

GENERI I TH :I EGER : = 1 ; 一一 B twi t C fW D NT 0) i dh P l ( M OlT :I T L N S D— OGI VE TOR( I H — l DOW NT C— C W DT O 0);

0 引言

直 接 数 字 频 率 合 成 器 ( gtl rc y te ie , 称 为 DDS)是 以 数 字 信 号 处 理 理 论 为 基 础 , 信 号 Dii e t n h sz r 简 a Di S 从

的 幅 度 相 位 关 系 出发 进 行 频 率 合 成 的 . 传 统 的 频 率 合 成 器 相 比 , DS具 有 极 高 的 分 辨 率 、 速 的 频 率 与 D 快 转换 时 间 、 宽 的相 对带 宽 、 意 波形 的输 出能力 和数 字调 制 等优 点. 文 研 究 的是 正 弦输 出 的数 字频 率 很 任 本 合 成 器 , 用 VHD 采 L语 言 设 计 了 该 系 统 ,并 通 过 Qu ru l at sI与 MAT AB 软 件 对 设 计 进 行 了 联 合 仿 真 , 证 L 验

基于FPGA的直接数字频率合成器的设计和实现

基于FPGA的直接数字频率合成器的设计和实现基于FPGA的直接数字频率合成器的设计和实现摘要:介绍了利用Altera的FPGA器件(ACEX EP1K50)实现直接数字频率合成器的工作原理、设计思想、电路结构和改进优化方法。

关键词:直接数字频率合成(DDS)现场可编程门阵列(FPGA)直接数字频率合成(Direct Digital Fraquency Synthesis,即DDFS,一般简称DDS)是从相位概念出发直接合成所需要波形的一种新的频率合成技术。

目前各大芯片制造厂商都相继推出采用先进CMOS工艺生产的高性能和多功能的DDS芯片(其中应用较为广泛的是AD公司的AD985X系列),为电路设计者提供了多种选择。

然而在某些场合,专用的DDS芯片在控制方式、置频速率等方面与系统的要求差距很大,这时如果用高性能的FPGA器件设计符合自己需要的DDS电路就是一个很好的解决方法。

ACEX 1K是Altera公司着眼于通信、音频处理及类似场合的应用而推出的FPGA器件芯片系列,总的来看将会逐步取代FLEX 10K系列,成为首选的中规模器件产品。

它具有如下特点:(1)ACEX 1K采用查找表(LUT)和EAB(嵌入式阵列块)相结合的结构,特别适用于实现复杂逻辑功能存储器功能,例如通信中应用的数字信号处理、多通道数据处理、数据传递和微控制等。

(2)典型门数为1万到10万门,有多达49152位的RAM(每个EAB有4096位RAM)。

(3)器件内核采用2.5V电压,功耗低,能够提供高达250MHz 的双向I/O功能,完全支持33MHz和66MHz的PCI局部总线标准。

(4)具有快速连续式延时可预测的快速通道互连(Fast Track);具有实现快速加法器、计数器、乘法器和比较器等算术功能的专用进位链和实现高速多扇入逻辑功能的专用级连接。

ACEX EP1K50具有典型门数50000门,逻辑单元2880个,嵌入系统块10个,完全符合单片实现DDS电路的要求。

DDS_直接数字频率合成器

南京理工大学直接数字频率合成器实验报告作者: 学号:学院(系):专业:指导老师:实验日期:2013年11月直接数字频率合成器(DDS)摘要本次课程设计的主要目的是学习使用FPGA设计直接数字频率合成器(DDS)。

实验的主要容是使用DDS的方法设计一个具有清零、使能频率相位控制、输出多种波形等功能任意频率的信号发生器,在设计之余,还完成了ROM空间的节省、提高等设计,并设计了一个基于DDS的AM调制电路。

利用Quartus II完成设计、仿真等工作,并下载至smart SOPC实验平台进行硬件测试,通过示波器观察输出信号波形。

实验结果与理论值相符,证明了DDS技术是一项非常实用的技术,它可以广泛应用于数字通信系统。

关键词:DDS ROM 正弦波AM调制AbstractThe main purpose of this curriculum design is encouraging us to learn to design a direct digital frequency synthesizer by using FPGA. The report mainly talks about how to design a direct digital frequency synthesizer with the function of resetting, frequency and phase controlling , multiple waves output . In addition, I also complete the design of ROM space saving ,and I design an AM modeling circuit based on DDS . The design and simulation work is completed with the help of QuartusII. The final system circuit is downloaded to the smart SOPC platform to undergo hardware test. And the output wave can be seen through oscilloscope. The experiment result is close to the theoretical result. DDS is proved to be a quite useful technology which can be widely applied in digital communication system.Keywords:Direct digital synthesizer ROM Sine wave AM module目录一、实验目的 (1)二、实验容和设计要求 (1)2.1实验容 (1)2.2设计要求 (1)三、直接频率合成器(DDS) (2)3.1实验原理 (2)3.2脉冲发生电路 (3)3.3消颤电路 (4)3.4频率和相位调节电路 (5)3.5累加器 (6)3.6波形存储器(ROM表)设计 (8)3.7测频电路 (11)3.8显示电路 (13)3.9总电路图(1) (14)四、节省ROM空间 (17)4.1设计思路 (17)4.2正弦波的计算 (18)4.3三角波计算 (20)4.4锯齿波计算 (20)4.5方波计算 (22)4.6四种计算波形合并 (22)4.7总电路图(2) (23)五、基于DDS的AM调制器的设计 (24)5.1AM调制原理 (24)5.2调制信号与载波信号的产生 (25)5.3波形存储器(ROM表)设计 (29)5.4调制度的确立 (30)5.5加法器与乘法器 (30)5.6显示电路 (30)5.7AM调制电路总图 (31)六、节省电路的改进 (32)七、实验中遇到的问题及解决办法 (33)八、实验收获和感受 (33)九、致 (34)十、参考文献 (34)十一、附录 (35)一、实验目的1.学习使用QuartusII软件做复杂逻辑电路的设计。

基于VHDL的DDS频率合成器的设计

摘要本文以FPGA为硬件平台,基于EDA工具quartus II为软件平台上对DDS进行实现。

用VHDL语言进行系统建模,对DDS进行参数设计,实现可重构的频率合成技术。

能够依照需要方便的修改参数以实现期间的通用性,同时利用MAXPALLS编译平台完成一个具体的DDS设计仿真,详细论述了基于VHDL编程的DDS设计方式步骤。

直接数字频率合成信号发生器(Direct Digital Synthesize)以其利用方便和频率分辨率高等优势,在现代通信领域取得愈来愈普遍的应用。

用VHDL语言对DDS进行功能描述,方便在不同的实现方式下移植和修改参数,因此慢慢成为DDS设计主流。

而且在Alter公司开发的quartus II中,提供了方便的VHDL编译和综合平台,大大缩短了DDS的设计和开发周期。

与传统的频率合成器相较,DDS具有低本钱、低功耗、高分辨率和快速转换时刻等优势,普遍利用在电信与电子仪器领域,是实现设备全数字化的一个关键技术。

DDS是现今一种重要的设计手腕,高速集成电路的进展进一步改善了DDS的性能,它与传统技术相结合,组成的各类混合方案将频率源的性能提高到一个新的水平,因此以后的DDS不仅应用于传统上需要利用信号源的领域,而且必将开拓许多新的应用领域。

关键词:DDS、建模、VHDL、D/A、quartus IIThe DDS-based frequency synthesis VHDL DesignAbstrac tBased on FPGA for the hardware platform, based on EDA tools for quartus II software platform for the realization of the DDS. System using VHDL language modeling, the design parameters of the DDS, the realization of reconfigurable frequency synthesis. To facilitate the changes necessary parameters in order to achieve a common period, while the use of compiler MAXPALLS platform DDS completed the design of a specific simulation, detailed programming of the DDS-based VHDL design steps. Direct Digital Synthesis Signal Generator (Direct Digital Synthesize) its ease of use and high frequency resolution, in the field of modern communications has been more and more widely. Using VHDL language to describe the features of DDS to facilitate the realization of different modes and modify the parameters of transplantation, which has gradually become the mainstream of DDS design. Alter developed in the M quartus II provide a convenient VHDL compiler and integrated platform, greatly reducing the DDS design and development cycle. Traditional compared to the frequency synthesizer, DDS has a low-cost, low-power, high-resolution and fast switching time, etc., widely used in the field of telecommunications and electronic equipment is all digital equipment to achieve a key technology. DDS is an important design today means the development of high-speed integrated circuits to further improve the performance of the DDS, which is a combination of traditional techniques, the composition of the various hybrid program will improve the performance of the frequency source to a new level, so the future The DDS is traditionally used not only need to use the area of the signal source, and will open up many new fields of application.Keywords: DDS, modeling, VHDL, D / A, quartus II、EDA目录第一章绪论 (5)DDS引言............................................................................................................ .5直接数字合成器的概念及其进展 (5)DDS技术在国内研究状况及其进展趋势 (6)频率合成器种类与技术进展趋势 (6)DDS优势 (7)课题要紧研究内容 (7)第二章超大规模集成电路设计介绍 (8)引言 (8)2.1.1 EDA技术的含义及特点............................................................................. ..8 2.1.2 EDA技术的要紧内容 (9)大规模可编程逻辑器件 (9)FPGA的介绍 (10)CPLD的介绍 (11)FPGA/CPLD对照 (11)硬件描述语言(HDL) (12)VHDL简介 (12)VHDL要紧特点 (13)VHDL语言的优势 (13)软件开发工具 (14)第三章 DDS 工作原理和要紧特点 (16)DDS的大体工作原理 (16)DDS采样量化 (16)DDS的大体参数推导 (17)DDS的要紧特点 (18)DDS建模 (19)第四章用VHDL来编程实现和仿真 (21)VHDL编程实现……......................................................................................... ..2132位加法器的VHDL实现程序 (21)32位加法器的生成模块 (22)32位寄放器的VHDL实现 (22)32位寄放器的生成模块 (23)波形数据ROM的VHDL实现 (23)波形数据ROM的生成模块 (25)整体模块设计 (25)用Quartus II进行DDS仿真 (26)4.2 .1 Quartus II软件简介 (26)用quartus II的仿真步骤和图像 (28)注意事项 (31)第五章终止语 (33)总结 (33)参考文献 (33)致谢 (33)附录 (35)第一章绪论DDS引言频率合成技术是将一个(或多个)基准频率变换成另一个(或多个)合乎质量要求的所需频率的技术。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电子线路课程设计直接数字频率合成器学号:姓名:2011年11月摘要本篇论文主要讲了用eda设计dds。

用quartus 软件模拟仿真电路,并下载到芯片。

使电路能输出正余弦波,并可调节频率和相位。

并在这基础上进行一部分扩展,如能输入矩形三角形波。

关键词eda设计 dds quartusAbstract:This report introduces the EDA design is completed with Direct Digital Synthesis DDS process. This design uses DDS QuartusII 7.0 software design, and downloads SmartSOPC experimental system hardware.Key word eda design dds quartus目录设计要求 (4)方案论证 (4)各子模块设计原理 (6)调试,仿真及下载 (12)结论 (13)一.设计要求基本要求:1、利用QuartusII软件和SmartSOPC实验箱实现DDS的设计;2、DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的RAM 实现,RAM结构配置成212×10类型;3、具体参数要求:频率控制字K取4位;基准频率fc=1MHz,由实验板上的系统时钟分频得到;4、系统具有使能功能;5、利用实验箱上的D/A转换器件将ROM输出的数字信号转换为模拟信号,能够通过示波器观察到正弦波形;6、过开关(实验箱上的Ki)输入DDS的频率和相位控制字,并能用示波器观察加以验证;提高部分:1、通过按键(实验箱上的Si)输入DDS的频率和相位控制字,以扩大频率控制和相位控制的范围;(注意:按键后有消颤电路)2、能够同时输出正余弦两路正交信号;3、在数码管上显示生成的波形频率;4、充分考虑ROM结构及正弦函数的特点,进行合理的配置,提高计算精度;5、设计能输出多种波形(三角波、锯齿波、方波等)的多功能波形发生器;6、基于DDS的AM调制器的设计;7、自己添加其他功能。

二、方案论证直接数字频率合成器(Direct Digital Frequency Synthesizer)是一种基于全数字技术,从相位概念出发直接合成所需波形的一种频率合成技术。

dds的组成及工作原理:每来一个CLOCK,加法器就将频率控制字f与累加寄存器输出的累加相位数据相加,相加的结果又反馈送至累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。

这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。

由此,相位累加器在每一个时钟脉冲输入时,把频率控制字累加以此,相位累加器输出的数据作为波形存储器的相位取样地址,这样就可把存储在波形存储器内的波形抽样值进行找表查出,完成相位到幅值的转换。

由于相位累加器为N位,相当于把正弦信号在相位上的精度定为N位,所以分辨率为1/2N。

若系统时钟频率为fc ,频率控制字k为1,则输出频率为fOUT=fC/2N,这个频率相当于"基频"。

若f为K,则输出频率为:f out =K* fC/2N当系统输入时钟频率fC不变时,输出信号的频率由频率控制字K所决定。

由上式可得:K=2N*fout /fC其中,K为频率字,注意K要取整,有时会有误差。

DSS工作流图:三、各子模块设计原理1、分频器实验中需要有1mhz,1khz,2hz,0.5hz的输入信号,而实验像仅能提供48mhz 的输入信号,故需要分频。

实验中拟用74163制作3分频,3片74160分别制作1k分频与500分频,用4片触发器做16分频。

16分频:3分频:1k分频:500分频:2、加法器加法器的目的,其一是作为累加器的一部分,将k进行累加,其二是作为频率控制与相位控制电路的一部分,调整输入给rom的12位地址。

3、寄存器寄存器的目的,是使加法器出来的结果稍作停留,以便传递给rom的地址位或者是回传给加法器成为加数。

4、累加器相位累加器的组成= N位加法器+N位寄存器相位累加器的作用:在时钟的作用下,进行相位累加注意:当相位累加器累加满量时就会产生一次溢出,完成一个周期性的动作。

5、rom的制作作用:进行波形的相位—幅值转换。

原理:ROM的N位地址把0O—360O的正弦角度离散成具有2N个样值的序列ROM的D位数据位则2N个样值的幅值量化为D位二进制数据以正弦为例:首先用VC程序产生rom数据值,程序如下:#include"stdio.h"#include"math.h"int main(int argc,char*argv[]){int i;double s;for(i=0;i<4096;i++){s=sin(atan(1)*8*i/4096);printf("%d:%x;\n",i,(int)((s+1)*1023/2));}return 0;}上述程序编译后,生成一个可执行文件rogen.exe,在DOS命令下执行: rogen>sine.mif生成sine.mif文件,再加上*.mif文件的头部说明即可,格式如下: DEPTH=4096;WIDTH=10;ADDRESS_RADIX=DEC;DATA_RADIX=HEX;CONTENTBEGIN...... -----ROM中的数据,每个占用一行......END然后设定LPM-ROM在元器库中选取LPM-ROM,设置ROM的信息,数据宽度为10bits,数据个数为4096;设置ROM为寄存器输出,不需要时钟和异步清零信号;指定ROM的初始化数据来源,选择刚刚所生成的mif文件。

然后点击“finish”即可生成ROM 单元了。

器件图如下:6、显示电路由于译码器一次只能输入一个数字的7位控制信号进入系统,为了使8个数字同时亮,则需要用到计数器与若干选择器,将想要输入系统的信号轮流送入。

电源接通,1khz的clk接入,计数器开始工作,产生0—7以控制8个数字同时亮。

7、测频电路测频就是计算1秒钟内脉冲的个数。

我们利用计数器和锁存器实现这一功能。

由于累加器以频率控制字K为间隔,当累加器满量时就会产生一次溢出,完成一次周期性的动作,这个周期也就是DDS信号的一个频率周期,所以将累加器的最高位作为测频电路技术器的脉冲。

将1HZ的时钟信号二分频,得到0.5Hz。

将0.5Hz脉冲送入锁存器的时钟端,0.5Hz反相延时后的脉冲送入计数器的清零端。

这样就使计数器在2s的脉冲周期内,1s内清零,1s内计数。

由于锁存器的脉冲和计数器的脉冲是反相的,且有一定的延时,所以当锁存器有效脉冲来到时,计数器是清零状态,锁存器就锁存前1s内计数器的计数信号。

这样就完成了1s内的脉冲计数,再将锁存器的输出送入译码显示电路,就可以在数码管上显示波形频率了。

原理图如下:电路图如下:8、总电路将累加器所得与k与p进行处理,以实现对相频的控制,再送入rom地址端,为了实现多波形输出,对开关输入信号进行判别,根据不同情况送入不同rom以实现多波形输出。

最后再合并上显示电路与测频电路。

四、调试,仿真及下载调试先保存,将上述电路以字母输入方式输入并保存在工程文件夹中。

再将文件置顶,最后进行编译,在主菜单中选择processing项,在弹出的对话框中选择Start complication键,则编译开始。

在编译过程中,若有任何信息、错误和警告消息,都将显示在自动打开的Message-Compiler窗口中;若由于文件出错而没有通过,则需要返回原文件进行修改,修改后存盘,再编译直至文件通过。

仿真新建一个“Vector Waveform file”文件,并在下拉列表中选.vwf扩展名,生成波形文件。

右键单击,在弹出的菜单中选Enter Nodes Frome SNF,在弹出的对话框中选择要观测的节点。

选Option\Grid Size和File\End Time,设置相应选项,并给输入引脚加上适当的信号。

然后,选File\Save保存。

接着选择主菜单中的Simulator项,打开模拟器,点击Start开始仿真。

其中dds的cos部分仿真结果如下图所示:Sin部分如下图所示:下载1.在device&pin中,configuration标签页,采用串行配置器件EPCS4的主动配置方式。

在unused pins标签页,进行没有使用管脚的配置,设置为高阻输入,避免损坏。

2.选择processing-start compilation进行全程编译。

五、结论同时输入正弦余弦波:同时输入正弦波与方波:同时输入正弦波与三角波:相位改变功能演示:测频功能检测:(单位hz)频率控制字理论输出频率示波器显示频率测频显示频率1 244.1 244.032 2446 1464.8 1464.239 146415 3662.1 3662.091 3661误差均在允许范围内。

六、遇到的问题和解决方法想做位相控制的位拓展,将原模16换成模64,原是低四位或者高四位相加,改为低8位或者高8位相加,实现了功能拓展。

七、实验感想本次实验是对我们数电能力实际应用的一次考验,通过这次实验我们灵活运用了我们所学习过的知识,尝试了自主探究与创新。

这是我们经历过的最长的一个单项实验,整整一周的时间里我们独立设计出了一个dds,遇到很多问题,通过独立探索或者与他人的交流讨论我们克服了困难并作出了成果。

本次实验里我学习到了创新的精神以及活学活用的道理。

参考文献1.蒋立平编著.《数字电路》.南京理工大学出版社2.南京理工大学电子技术中心编.《EDA设计实验指导书》3.付文红、花汉兵编著.《EDA技术与实验》.机械工业出版社。