计算机设计与实践——32位先行进位加法器

VLSI电路系统与设计_32bit移位相加乘法器

《VLSI电路系统与设计》课程设计报告——32bit_32bit移位相加乘法器A 移位相加乘法器原理无符号二进制移位相加乘法器的基本原理是通过逐项移位相加来实现相乘的,从被乘数的最低为开始,若为1,则乘法左移后与上一次的和相加;若为0,左移后以全零相加,直至被乘数的最高位。

以下以4位二进制数为例进行说明:图1 移位相加乘法器原理图如图所示,就可以实现4位二进制数的相乘。

B 电路结构方案根据移位相加乘法器的基本原理,可以将整个电路划分为四个部分:32右移寄存器,32位加法器,乘1模块,64位锁存器。

原理框图如下所示:图2 移位相加乘法器原理框图在上图中,START信号的上跳沿及其高电平有两个功能,即32位寄存器清零和被乘数A[32:0]向移位寄存器SREG32B加载;它的低电平则作为乘法使能信号。

CLK为乘法时钟信号。

当被乘数被加载于32位右移寄存器SREG32B后,随着每一时钟节拍,最低位在前,由低位至高位逐位移出。

当为1时,与门ANDARITH打开,32位乘数B[32:0]在同一节拍进入32位加法器,与上一次锁存在64位锁存器REG16B中的高32位进行相加,其和在下一时钟节拍的上升沿被锁进此锁存器。

而当被乘数的移出位为0时,与门全零输出。

如此往复,直至32个时钟脉冲后,乘法运算过程中止。

此时REG64B的输出值即为最后的乘积。

此乘法器的优点是节省芯片资源,它的核心元件只是一个32位加法器,其运算速度取决于输入的时钟频率。

一、32位加法器模块的设计加法器模块是由8个四位全加器构成的,4位全加器是采用1位全加器构成的。

对于1位全加器,采用门级描述语言,使用了3个异或门和2个与门来实现的。

(1)1位加法器是采用门级描述语言,生成的库文件如图:仿真结果:图1 功能仿真图2 时序仿真(2)32位全加器32位全加器是采用8个4位全加器构成的,其电路原理图如下:图3-32位全加器原理图仿真结果:图4 功能仿真图5 时序仿真由以上的仿真结果可以看出,所设计电路在在功能上能满足要求,在时序上存在一定的时间延迟。

数字系统设计实验---32位串行加法器实验综述

深圳大学实验报告课程名称:_________ 数字系统设计________________________ 实验项目名称: 32位串行加法器______________________ 学院_______________________ 专业_______________________ 指导教师: ______________________________________________报告人: ________ 学号:20091000000班级:1班实验时间:__________ 2011-12-4 ________________________实验报告提交时间:______________________教务处制一、实验目的与要求:实验目的:1、掌握串行加法器的原理和设计。

2、熟悉VHDL状态机的设计。

3、学会分析波形图。

实验要求:设计一个用一个1位加法器构建的一个32位串行加法器。

重点是算法状态机的实现还有系统的时序分析;输出和整理VHDL源代码;输出和整理电路结构图;输出和整理仿真波形图二、实验原理1、设计原理图:本图参考课本2、流程图:针对以上流程图,其中,Sh为控制移位寄存器的使能信号,k为工作状态指示信号,load为加载信号,counter为运算计数器,N为系统工作控制信号。

从流程图中可以看出加法器的整个工作流程是怎么样子的,具体工作情况如下面的设计。

三、实验内容与步骤1、VHDL代码的编写:----------- 控制器--------------------------------------------- library IEEE;use IEEE.STD_LOGIC_1164.ALL;use ieee.std_logic_ un sig ned.all;en tity con troller isPort ( clk : in STD_LOGIC;N : in STD_LOGIC;K,Sh,load : out STD_LOGIC);end con troller;architecture Behavioral of con troller issig nal state ,n extstate:i nteger range 0 to 2; ---设置状态sig nal coun ter:std_logic_vector(4 dow nto 0);beginprocess(clk)beginif(clk'event and clk='1') thenstate<=n extstate;end if;end process;process(clk,N)beginif(clk'event and clk='1') thencase state is ---设置各状态when 0 =>sh<='0';K<='0';load<='0';cou nter<="00000"; if N='1' the nload<='1';n extstate<=1;elsen extstate<=0;end if;when 1 =>sh<='1';K<='0';load<='0';if cou nter="11110" thencoun ter<=co un ter+1;n extstate<=2;elsecoun ter<=co un ter+1;n extstate<=1;end if;when 2 =>sh<='0';K<='1';load<='0:if N='0' the nn extstate<=0;elsen extstate<=2;end if;end case;end if;end process;end Behavioral;-------------- 加数寄存器 -------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;en tity registers_jiashu isPort ( in put : in STD_LOGIC_vector(31 dow nto 0);Sh,load,clk: in STD_LOGIC; SO : out STD_LOGIC);end registers_jiashu;architecture Behavioral of registers_jiashu is sig nal x:std_logic_vector(31 dow nto 0); begin process(clk) beginif(clk'event and clk='1') thenif (load='1‘)then x<=in put;elsif (sh='1') the n ---:x(30 dow nto 0)<=x(31 dow nto 1);end if;end if;end process;so<=x(0);end Behavioral;-------------- 累加器 ---------------------library IEEE;use IEEE.STD_LOGIC_1164.ALL;en tity registers_add isPort ( in put : in STD_LOGIC_vector(31 dow nto 0);clk : in STD_LOGIC;load,Sh,Si: in STD_LOGIC;SO : out STD LOGIC;output:out std_logic_vector(31 dow nto 0));end registers_add;architecture Behavioral of registers_add issig nal x:std_logic_vector(31 dow nto 0);beginprocess(clk)N<='0';wait for 10*clk_period; --延时10个时钟周期,进入下一轮仿真调试in putA<="01010101010101010101010101010101"; -- i nputa= 1431655765,in putB<="00110000000000000000000010101000"; -- i nputb= 805306536,N<='1'; --N=1时开始计时,并开始下载数据wait for 32*clk_period;--32 个时钟周期之后N<='0:--N=0,停止数据下载,得出相加后的结果wait for 10*clk_period; --延时10个时钟周期,进入下一轮仿真调试wait;end process;END;四、实验数据与分析1、综合的电路:设计图外观1 :adder 32l设计图外观2:adder_32oiJtputA(31:0)incl kNadder_321、控制器:2、全加器:情况二:in puta= 1431655765, in putb=805306536,outputa=2236962301Q- /adder _3 2_tE5tbendn /inputa EJ- /adder _32_te5tbenefi /inputb/adder _32_te£tbencfi /dk/adder_32Jbestberdn /n Q-」/adder_32_tEstberidi/outputa/addcr_32_testberidiA 731381211114 J1>55765805^)65363i ・i i17B957306J22369623012、仿真的波形图如下:情况一:in puta二 73,i nputb二 138,outputa=211/adder _32_t)&stlbench/inpLi taD- /adder _3 2_te&tbendi/inp*j thJ/ adder _32_testben 击/die /adder_32_testbendiAi/adder_3Z_testbendi/outputaJ/adder _32_testbench 4cD- /adder _3 2_testbendi^nputa73Q- .. add er 2_test±)endi /inpu tb133/adder _32_tes±>erKh/dk1/adder_32_testbendi /h0C- /adder _32_testberKhAxjtpu ta211/adder_32_testbencti 水1数据处理分析:每次从N=1开始,加法器进行数据下载,32个时钟周期之后,当N=0时, 输出k=1,表示串行累加的过程结束,此时输出的结果即为加法器的最后结果。

计算机设计与实践——MIPS基本指令

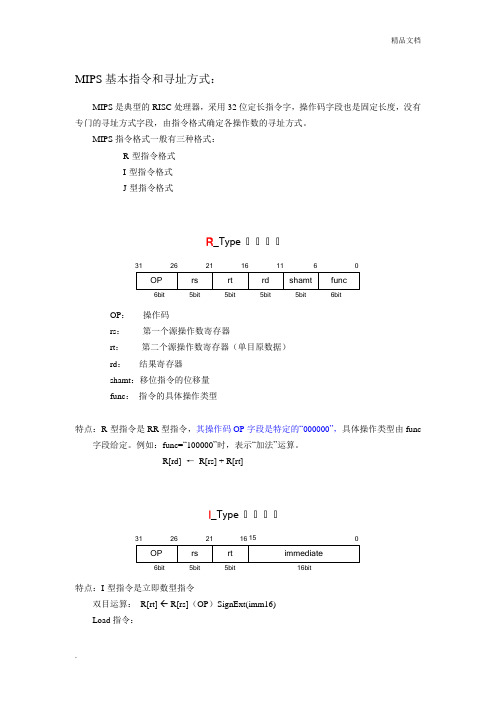

MIPS 基本指令和寻址方式:MIPS 是典型的RISC 处理器,采用32位定长指令字,操作码字段也是固定长度,没有专门的寻址方式字段,由指令格式确定各操作数的寻址方式。

MIPS 指令格式一般有三种格式: R-型指令格式 I-型指令格式 J-型指令格式R _Type 指指指指262116116316bit6bit5bit5bit5bit5bitOP : 操作码rs : 第一个源操作数寄存器rt : 第二个源操作数寄存器(单目原数据) rd : 结果寄存器 shamt :移位指令的位移量 func : 指令的具体操作类型特点:R-型指令是RR 型指令,其操作码OP 字段是特定的“000000”,具体操作类型由func字段给定。

例如:func=“100000”时,表示“加法”运算。

R[rd] ← R[rs] + R[rt]I _Type 指指指指2621163115特点:I-型指令是立即数型指令双目运算: R[rt] R[rs](OP )SignExt(imm16) Load 指令:Addr ← R[rs] + SignExt(imm16) 计算数据地址 (立即数要进行符号扩展) R[rt] ← M[Addr] 从存储器中取出数据,装入到寄存器中Store 指令:Addr ← R[rs] + SignExt(imm16) M[Addr] ← R[rt]J _Type 指令格式26316bit26bit25特点:J-型指令主要是无条件跳转指令,将当前PC 的高4位拼上26位立即数,后补两个“0”,作为跳转目标地址。

j L //goto L 指指指指指指指指指jal L //$ra 指PC+4;goto L 指指指指指指指指指R 型指令:定点运算: add / addu , sub / subu , sra , mult/multu , div/divu 逻辑运算: and / or / nor , sll / srl 比较分支: beq / bne / slt / sltu 跳转指令: jrI 型指令:定点运算: addi / addiu 逻辑运算: andi / ori 比较分支: slti / sltiu数据传送: lw / sw / lhu / sh / lbu / sb / luiJ 型指令: j / jal设计模块划分,教学安排1、MIPS格式指令系统设计2、指令存储器设计3、寄存器堆设计4、ALU设计——基本算术、逻辑单元的设计32位超前进位加法器的设计32位桶式移位寄存器的设计5、取指令部件的设计6、立即数处理单元设计7、单周期处理器设计——R型指令的数据通路设计I型指令的数据通路设计Load/Store指令的数据通路设计分支指令/转移指令的数据通路设计综合12条指令的完整数据通路设计8、ALU控制单元设计9、主控制单元的设计10、单周期处理器总体验证11、异常和中断处理及其电路实现12、带有异常和中断处理功能的处理器的设计设计示例1:指令存储器设计1、 指令存储器模块定义:指令存储器用于存放CPU 运算的程序指令和数据等,采用单端口存储器设计,设计最大为64个存储单元,每个存储单元数据宽度为32bit 。

计算机组成原理实验报告_32位ALU设计实验

实验三32位ALU设计实验一、实验目的学生理解算术逻辑运算单元(ALU)的基本构成,掌握Logisim 中各种运算组件的使用方法,熟悉多路选择器的使用,能利用前述实验完成的32位加法器、Logisim 中的运算组件构造指定规格的ALU 单元。

二、实验原理、内容与步骤实验原理、实验内容参考:1、32位加法功能的原理与设计1)设计原理1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。

这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。

而最后的第32位必须在前31位全部计算出结果后,才能开始计算。

这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

2)电路设计32位加法功能2、32位减法功能的原理与实现1)变减法为加法的原理1.在Y引脚处使用求补器(32位),即可变减法为加法2.用构造好的32位加法器。

Y各位取反,C0取1,即可达到减法变加法。

无符号数的减法溢出,带加减功能的ALU的进位取反后表示,有符号数的减法溢出,仍然用最高位和符号位是否相等来判断2)电路设计32位减法功能3、加减溢出检测的设计(不考虑乘除法)1)有符号数溢出的设计有符号数溢出的设计2)无符号数溢出的设计无符号数溢出的设计4、移位的原理与设计1)逻辑移位逻辑移位2)算术移位算术移位5、逻辑运算功能的原理与设计2)与、或、异或、或非逻辑6、大于、等于、小于功能设计大于、等于、小于功能设计7、AluOP的控制原理与设计1)原理:AluOP的控制原理与设计8、总电路设计图算术逻辑运算单元ALU三、实验结论及分析(实验完成功能情况、存在问题分析或改进思路、自己的心得体会等。

先行进位加法器的名词解释

先行进位加法器的名词解释先行进位加法器(Carry Lookahead Adder,CLA)是一种高速的二进制加法器,在计算机的数字电路中得到广泛应用。

它通过提前计算进位信号,实现了快速的加法运算,极大地提高了计算速度。

先行进位加法器的工作原理基于二进制加法的规律。

在二进制加法中,每一位的运算结果由两个输入位和进位信号决定。

如果只有两个输入位,那么进位信号则是根据相加的结果判断的,并且需要等待结果出来后才能计算。

而先行进位加法器通过提前计算进位信号,将加法的计算和进位信号的生成分离开来,大大缩短了计算时间。

先行进位加法器的一个重要组成部分是生成器和传递器。

生成器(G)用来判断两个输入位是否都为1,如果是,则生成进位信号;否则,不生成进位信号。

传递器(P)则是判断两个输入位中是否有一个或两个位都为1,如果是,则传递进位信号;否则,不传递进位信号。

通过这样的组合,可以得到一个高效的进位信号生成和传递机制。

先行进位加法器的优势在于其快速的计算速度和高效的硬件实现。

不需要等待结果的同时,可以并行地计算多个位的运算,并通过树状结构组合起来,进一步减小了延迟。

在图像处理、语音识别、数据压缩等需要大量运算的应用领域,先行进位加法器是不可或缺的重要组件。

然而,先行进位加法器也存在一些不足之处。

首先,它的硬件实现较为复杂,需要大量的逻辑门和电路,占用更多的面积和功耗。

其次,随着位数的增加,进位信号的生成和传递的延迟也会增大,加法器的性能将会受到限制。

因此,在对于大规模的计算,可以考虑使用其他更加高级的加法器结构。

总的来说,先行进位加法器是一种高速的二进制加法器,通过提前计算进位信号,实现了快速的加法运算。

它在计算机的数字电路中得到广泛应用,具有较高的效率和性能。

随着科技的发展,我们期待更加先进的加法器结构的涌现,为计算领域带来更大的突破。

先行进位加法器

实验四32位先行进位加法器一、功能概述串行进位加法器延时很大,每级的输出结果都要等上一级的进位到来才可以求和算出结果,这次实验对普通全加器进行改良,改良为先行进位加法器。

先行进位加法器,各级的进位彼此是独立产生,只与输入数据A,B和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减小进位产生的延时。

每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。

通过这种进位方式实现的加法器称为超前进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

二、实验原理1、设二进制加法器第i位为A i,B i,输出为S i,进位输入为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1,产生进位C i+1 = 1当A i和B i有一个为1时,P i = 1,传递进位C i+1= C i因此G i定义为进位产生信号,P i定义为进位传递信号。

G i的优先级比P i高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i是多少;当G i=0而P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下面推导4位超前进位加法器。

设4位加数和被加数为A 和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i·B i ,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inC1=G0 + P0·C0C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0▪C0C3=G2+ P2·C2= G2+ P2·G1+ P2·P1·G0+P2·P1·P0·C0C4=G3+ P3·C3= G3+ P3·G2+ P3·P2·G1+P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)C out=C4由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关。

计算机设计与实践——32位先行进位加法器

assign c1=g[1]|p[1]&ciii; assign c2=g[2]|p[2]&g[1]|p[2]&p[1]&ciii; endmodule

module alu_16(gmm,pmm,f16,x16,y16,cii);//16位加法器先行进位加法器 input [16:1]x16; input [16:1]y16; input cii; output [16:1]f16; output gmm,pmm; wire [4:1]c; wire [4:1]p; wire [4:1]g; jiafaqi_4 alu_4_1(g[1],p[1],f16[4:1],x16[4:1],y16[4:1],cii); jiafaqi_4 alu_4_2(g[2],p[2],f16[8:5],x16[8:5],y16[8:5],c[1]); jiafaqi_4 alu_4_3(g[3],p[3],f16[12:9],x16[12:9],y16[12:9],c[2]); jiafaqi_4 alu_4_4(g[4],p[4],f16[16:13],x16[16:13],y16[16:13],c[3]); cla_4 cl_4_1(c,p,g,cii); assign pmm=p[4]&p[3]&p[2]&p[1]; assign gmm=g[4]|p[4]&g[3]|p[4]&p[3]&g[2]|p[4]&p[3]&p[2]&g[1]; endmodule

数字系统设计32位进位选择加法器设计

1、12进位选择加法器原理图32位进位选择加法器原理图仅仅是将12位进位选择加法器原理图中虚线框内的模块再向后重复5次,这就构成了32位进位选择加法器原理图。

2、Verilog模块根据上图可以将进位选择加法器在结构上分为四个模块:①四位先行进位加法器adder_4bits②四位数据选择器mux_2to1③高四位选择加法器(虚线框内部分)adder_high_4bits④顶层设计32位进位选择加法器adder_32_bits3、Verilog代码# 四位先行进位加法器module adder_4bits(a,b,s,ci,co);parameter N=4;input[N-1:0] a;input[N-1:0] b;input ci;output[N-1:0] s;output co;wire [N-1:0] c;wire [N-1:0] g;wire [N-1:0] p;assign g=a&b;assign p=a|b;assign c[0]=g[0]||(p[0]&&ci);assign c[1]=g[1]||(p[1]&&g[0])||(p[1]&&p[0]&&ci);assign c[2]=g[2]||(p[2]&&g[1])||(p[2]&&p[1]&&g[0])||(p[2]&&p[1]&&p[0]&&ci);assignc[3]=g[3]||(p[3]&&g[2])||(p[3]&&p[2]&&g[1])||(p[3]&&p[2]&&p[1]&&g[0])||(p[3]&&p[2]&&p[1]&&p[0]&&ci);assign s[0]=p[0]&~g[0]^ci;assign s[1]=p[1]&~g[1]^c[0];assign s[2]=p[2]&~g[2]^c[1];assign s[3]=p[3]&~g[3]^c[2];assign co=c[3];endmodule# 四位数据选择器module mux_2to1 (out,in0,in1,sel);parameter N=4;output[N:1] out;input[N:1] in0,in1;input sel;assign out=sel?in1:in0;endmodule# 高四位选择加法器module adder_high_4bits(a,b,ci,co,s);parameter N=4;input[N-1:0] a;input[N-1:0] b;input ci;output[N-1:0] s;output co;wire [N-1:0] sum1,sum0;wire co1,co0,cand;adder_4bits #(4) adder_1(.a(a),.b(b),.s(sum1),.ci(1'b1),.co(co1)); adder_4bits #(4) adder_2(.a(a),.b(b),.s(sum0),.ci(1'b0),.co(co0)); mux_2to1 #(4) mux1(.in0(sum0),.in1(sum1),.sel(ci),.out(s)); and G1(cand,ci,co1);or G2(co,cand,co0);endmodule# 顶层设计32位进位选择加法器module adder_32bits(a,b,s,ci,co);parameter N=32;input [N-1:0] a;input [N-1:0] b;input ci;output [N-1:0] s;output co;wire co1,co2,co3,co4,co5,co6,co7;adder_4bits #(4) adder1(.a(a[3:0]),.b(b[3:0]),.ci(ci),.s(s[3:0]),.co(co1));adder_high_4bits #(4) adder2(.a(a[7:4]),.b(b[7:4]),.ci(co1),.s(s[7:4]),.co(co2));adder_high_4bits #(4) adder3(.a(a[11:8]),.b(b[11:8]),.ci(co2),.s(s[11:8]),.co(co3));adder_high_4bits #(4) adder4(.a(a[15:12]),.b(b[15:12]),.ci(co3),.s(s[15:12]),.co(co4));adder_high_4bits #(4) adder5(.a(a[19:16]),.b(b[19:16]),.ci(co4),.s(s[19:16]),.co(co5));adder_high_4bits #(4) adder6(.a(a[23:20]),.b(b[23:20]),.ci(co5),.s(s[23:20]),.co(co6));adder_high_4bits #(4) adder7(.a(a[27:24]),.b(b[27:24]),.ci(co6),.s(s[27:24]),.co(co7));adder_high_4bits #(4) adder8(.a(a[31:28]),.b(b[31:28]),.ci(co7),.s(s[31:28]),.co(co)); endmodule4、仿真结果①四位先行进位加法器进行仿真,结果如下如图所示,a=0101,b=1010,ci=1;sum=0000,cout=1;仿真正确。

位可控加减法器设计32位算术逻辑运算单元

位可控加减法器设计32位算术逻辑运算单元标题:深入探讨位可控加减法器设计中的32位算术逻辑运算单元一、引言在计算机系统中,算术逻辑运算单元(ALU)是至关重要的部件,用于执行数字运算和逻辑运算。

而在ALU中,位可控加减法器设计是其中的重要部分,尤其在32位算术逻辑运算单元中更是不可或缺。

本文将深入探讨位可控加减法器设计在32位算术逻辑运算单元中的重要性,结构特点以及个人观点和理解。

二、位可控加减法器设计的重要性位可控加减法器是ALU中的重要组成部分,它具有对加法和减法操作进行控制的能力,可以根据输入信号来实现不同的运算操作。

在32位算术逻辑运算单元中,位可控加减法器的设计要考虑到对每一位进行并行操作,并且要保证高速、低功耗和稳定性。

位可控加减法器设计在32位算术逻辑运算单元中具有非常重要的意义。

三、位可控加减法器设计的结构特点在32位算术逻辑运算单元中,位可控加减法器的设计需要考虑到以下几个结构特点:1. 并行运算:位可控加减法器需要能够实现对32位数据的并行运算,以提高运算速度。

2. 控制信号:设计需要合理的控制信号输入,来实现不同的运算模式和操作类型。

3. 进位传递:保证进位信号能够正确传递和计算,以确保运算的准确性。

4. 低功耗:设计需要考虑到低功耗的特点,以满足现代计算机系统对能源的需求。

四、个人观点和理解在我看来,位可控加减法器设计在32位算术逻辑运算单元中扮演着十分重要的角色。

它不仅需要具备高速、稳定和精确的运算能力,还需要考虑到功耗和控制信号的合理设计。

只有兼具这些特点,才能更好地满足现代计算机系统对于高效、可靠和低功耗的需求。

五、总结和回顾通过本文对位可控加减法器设计在32位算术逻辑运算单元中的深入探讨,我们可以看到它在计算机系统中的重要性和结构特点。

而个人观点也表明了它需要具备高速、低功耗和稳定性等特点,才能更好地满足现代计算机系统的需求。

在写作过程中,我对位可控加减法器设计在32位算术逻辑运算单元中的重要性和结构特点进行了深入探讨,并分享了个人观点和理解。

先行进位加法器课件

实验四32位先行进位加法器一、功能概述串行进位加法器延时很大,每级的输出结果都要等上一级的进位到来才可以求和算出结果,这次实验对普通全加器进行改良,改良为先行进位加法器。

先行进位加法器,各级的进位彼此是独立产生,只与输入数据A,B 和C_in有关,将各级间的进位级联传播给去掉了,这样就可以减小进位产生的延时。

每个等式与只有三级延迟的电路对应,第一级延迟对应进位产生信号和进位传递信号,后两级延迟对应上面的积之和。

通过这种进位方式实现的加法器称为超前进位加法器。

因为各个进位是并行产生的,所以是一种并行进位加法器。

二、实验原理1、设二进制加法器第i位为A i,B i,输出为S i,进位输入为C i,进位输出为C i+1,则有:S i=A i⊕B i⊕C i(1-1)C i+1 =A i * B i+ A i *C i+ B i*C i =A i * B i+(A i+B i)* C i(1-2)令G i = A i * B i , P i = A i+B i,则C i+1= G i+ P i *C i当A i和B i都为1时,G i = 1,产生进位C i+1 = 1当A i和B i有一个为1时,P i = 1,传递进位C i+1= C i因此G i定义为进位产生信号,P i定义为进位传递信号。

G i的优先级比P i高,也就是说:当G i = 1时(当然此时也有P i = 1),无条件产生进位,而不管C i是多少;当G i=0而P i=1时,进位输出为C i,跟C i之前的逻辑有关。

下面推导4位超前进位加法器。

设4位加数和被加数为A和B,进位输入为C in,进位输出为C out,对于第i位的进位产生G i = A i·B i,进位传递P i=A i+B i , i=0,1,2,3。

于是这各级进位输出,递归的展开Ci,有:C0 = C inC1=G0 + P0·C0C2=G1 + P1·C1 = G1 + P1·G0 + P1·P0▪C0C3=G2 + P2·C2 = G2 + P2·G1 + P2·P1·G0 + P2·P1·P0·C0C4=G3 + P3·C3 = G3 + P3·G2 + P3·P2·G1 + P3·P2·P1·G0 + P3·P2·P1·P0·C0 (1-3)C out=C4由此可以看出,各级的进位彼此独立产生,只与输入数据Ai、Bi和Cin有关。

32位异步加法单元的设计与实现

32位异步加法单元的设计与实现32位异步加法单元是一种电路设计,可以用于执行32位二进制数据的加法运算。

本文将介绍32位异步加法单元的设计原理和实现方法。

设计原理32位异步加法单元由两个主要部分组成:加法器和延迟元件。

加法器的功能是执行32位二进制数的加法运算。

在加法器中,每个二进制位都有一个半加器,用于计算该位的进位和本位之和。

这些半加器通过级联连接,形成32位加法器。

延迟元件的功能是保证加法器能够正确地执行加法运算。

由于每个二进制位的计算都需要依赖前一位的进位信号,因此在加法器中,每个二进制位的计算必须等待前一位的计算完成。

为了实现这种等待,需要在每个半加器的进位输入处添加一个延迟元件,使得进位信号延迟一个时钟周期再输入到下一位的半加器中。

这样,每个半加器的计算就能够保证在正确的时序下进行。

实现方法32位异步加法单元的实现方法包括电路设计和仿真验证两个步骤。

电路设计在32位异步加法单元的电路设计中,需要考虑以下几个方面:1. 加法器的设计加法器的设计采用级联结构,由32个半加器组成。

每个半加器由两个输入端口和两个输出端口组成,其中一个输入端口用于输入本位的两个二进制数和进位信号,另一个输入端口用于输入上一位的进位信号。

两个输出端口分别为本位的和和进位信号。

2. 延迟元件的设计延迟元件的设计可以采用D触发器或JK触发器。

在每个半加器的进位输入处添加一个延迟元件,使得进位信号可以延迟一个时钟周期再输入到下一位的半加器中。

这样就能保证每个半加器的计算在正确的时序下进行。

3. 输出的设计输出端口为32位二进制数的和,可以通过级联加法器的输出端口组成。

进位信号可以通过最后一个半加器的进位输出端口获得。

仿真验证完成电路的设计后,需要进行仿真验证。

在Verilog语言中,可以通过模块实例化的方式对电路进行仿真。

在仿真中,可以输入32位二进制数进行加法运算,并对输出进行验证。

结论32位异步加法单元是一种用于执行32位二进制数据加法运算的电路设计。

32位浮点加法器设计

32位浮点加法器设计一、基本原理浮点数加法运算是在指数和尾数两个部分进行的。

浮点数一般采用IEEE754标准表示,其中尾数部分采用规格化表示。

浮点加法的基本原理是将两个浮点数的尾数对齐并进行加法运算,再进行规格化处理。

在加法运算过程中,还需考虑符号位、指数溢出、尾数对齐等特殊情况。

二、设计方案1. 硬件实现方案:采用组合逻辑电路实现浮点加法器,以保证运算速度和实时性。

采用Kogge-Stone并行加法器、冒泡排序等技术,提高运算效率。

2.数据输入:设计32位浮点加法器,需要提供两个浮点数的输入端口,包括符号位、指数位和尾数位。

3.数据输出:设计32位浮点加法器的输出端口,输出相加后的结果,包括符号位、指数位和尾数位。

4.控制信号:设计合适的控制信号,用于实现指数对齐、尾数对齐、规格化等操作。

5.流程控制:设计合理的流程控制,对各个部分进行并行和串行处理,提高加法器的效率。

三、关键技术1. Kogge-Stone并行加法器:采用Kogge-Stone并行加法器可以实现多位数的并行加法运算,提高运算效率。

2.浮点数尾数对齐:设计浮点加法器需要考虑浮点数尾数的对齐问题,根据指数大小进行右移或左移操作。

3.溢出判断和处理:浮点加法器需要判断浮点数的指数是否溢出,若溢出需要进行调整和规格化。

4.符号位处理:设计浮点加法器需要考虑符号位的处理,确定加法结果的符号。

四、性能评价性能评价是衡量浮点加法器设计好坏的重要指标。

主要从以下几个方面进行评价:1.精度:通过与软件仿真结果进行比较,评估加法器的运算精度,误差较小的加法器意味着更高的性能。

2.速度:评估加法器的运行速度,主要考虑延迟和吞吐量。

延迟越低,意味着加法器能够更快地输出结果;吞吐量越高,意味着加法器能够更快地处理多个浮点加法运算。

3.功耗:评估加法器的功耗情况,低功耗设计有助于提高整个系统的能效。

4.面积:评估加法器的硬件资源占用情况,面积越小意味着设计更紧凑,可用于片上集成、嵌入式系统等场景。

基于RISC指令系统的32位浮点加减法运算器设计

基于RISC指令系统的32位浮点加减法运算器设计摘要:浮点运算部件一直是限制微处理器性能的一个关键因素。

在分析了浮点运算器的结构和算法,提出了一种支持IEEE-754标准的浮点加减法运算器的实现方案,并详细介绍了该运算器的结构和算法。

方案采用了四级流水线的结构,即:0操作数检查、对阶、尾数运算、结果规格化及舍入处理。

每个步骤可以单独作为一个模块,在每个模块之间增加了寄存器,利用这些寄存器可以为下一个操作准备正确的数据。

关键词:流水线,IEEE-754标准,警戒位,舍入法32 bit Floating-Point Addition and Subtraction ALU Design Based onRISC StructureABSTRACT:Floating-Point arithmetic unit is always key factor of restricting microprocessor performance.This paper analyses structure and algorithm of Floating-Point ALU and brings forward a scenario about Floating-Point addition and subtraction ALU which supports IEEE-754 standard. The scenario adopts 4-Level pipelining structure: 0 operation numbers check、match exponent、fraction arithmetic、result normalization and rounding. Each step can be act as a single module. Among these modules, there are some registers which can prepare correct data for next operation.Keywords: pipelining, IEEE-754 Standard, Guard Digit, Rounding Method1 引言随着SOC技术、IP技术以及集成电路技术的发展,RISC软核处理器的研究与开发设计开始受到了人们的重视。

16位快速加法器32位快速加法器(运算器设计)

16位快速加法器32位快速加法器(运算器设计)快速加法器的设计基于全加器和半加器的组合。

全加器可以实现对两个二进制位的相加,并且可以处理进位。

半加器只能处理两个二进制位的相加,但不能处理进位。

快速加法器通过使用多个全加器和半加器的级联来实现对多个二进制位的相加,并处理进位。

一个16位快速加法器通常由16个全加器组成,每个全加器对应一个二进制位的相加。

输入端包括两个16位的二进制数A和B,以及一个进位输入Cin。

输出端包括一个16位的二进制数S和一个进位输出Cout。

快速加法器的设计中还考虑了进位的传递问题。

通常情况下,每个全加器的进位输入都连接到前一个全加器的进位输出。

这样,在相加的过程中,进位会从低位传递到高位。

为了提高运算器的效率,可以采用并行运算的方式。

32位快速加法器可以通过将两个16位快速加法器并联来实现。

其中,一个加法器负责处理前16位,另一个加法器负责处理后16位。

这样可以同时进行两个16位数的相加,大大提高了加法操作的速度。

快速加法器的工作原理如下:1.将输入的两个16位二进制数A和B送入第一个全加器,通过16个全加器的级联实现对各位的相加,并处理进位。

2.每个全加器的输出与相应的进位输入连线,以实现进位的传递。

3.得到的16位二进制数S作为输出。

对于32位快速加法器,它由两个16位快速加法器组成,其中第一个加法器处理低16位,第二个加法器处理高16位。

输入的两个32位二进制数A和B被拆分为两个16位数,并分别送入两个加法器进行相加。

最后,两个相加的结果通过一个与门来判断是否有进位,进一步得到32位的二进制数S和进位输出Cout。

快速加法器是计算机中常用的运算器,它在高速计算和数据处理方面具有重要的作用。

通过合理的设计和优化,可以实现更高效的加法操作,提高计算机的性能。

同时,快速加法器的设计还需要考虑功耗和面积等因素,以实现更好的综合性能。

一种基于FPGA的32位快速加法器设计

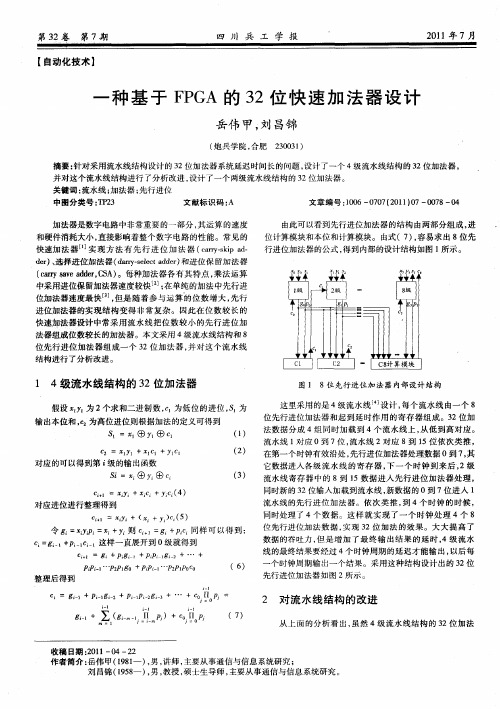

由此可 以看到先行进位加法器 的结 构由两部分组 成 ,进 位计算模块和本位和计算模块。由式 (7),容易求 出 8位先 行进位加法器的公式 ,得到内部 的设计结构如 图 1所示 。

1 4级流 水 线 结 构 的 32位 加 法 器

图 1 8位 先 行 进位 加 法 器 内部 设 计 结构

并 对 这 个 流 水线 结 构 进 行 了分 析改 进 ,设 计 了一 个 两 级 流水 线 结 构 的 32位加 法 器 。

关 键 词 :流水 线 ;an法 器 ;先 行 进位

中图 分 类号 :TP23

文 献 标 识 码 :A

文 章 编 号 :1006—0707(2011)07—0078—04

刘 昌锦 (1958一 ),男 ,教授 ,硕士生导师 ,主要从事通信与信息系统研究 。

岳伟 甲 ,等 :一 种基 于 FPGA 的 32位 快速 加 法器设计

79

器 平 均 每 个 系 统 时 钟 完 成 一 次 32位 加 运 算 ,但 是 系 统 的 延 时较 大 为 4个 系 统 时 钟 。不 能 满 足 对 于 转 换 速 度 要 求 较 高 的场合 。因此采用一种新的方式 ,综合 流水线技术 和先行进

第 32卷 第 7期 【自动化 技术 】

四 川 兵 工 学 报

2011年 7月

一 种 基 于 FPGA 的 32位 快 速 加 法 器 设 计

岳 伟 甲 ,刘 昌锦

(炮 兵 学 院 ,合 肥 230031)

摘要 :针对采用流水线结构设计的 32位 加法器系统延迟 时间长 的问题 ,设计 了一个 4级流水线结构 的 32位加法器 ,

2 对流水线结构 的改进

g +∑ (gl-m-l I I PJ) +c0 B

快速加法器与32位ALU设计

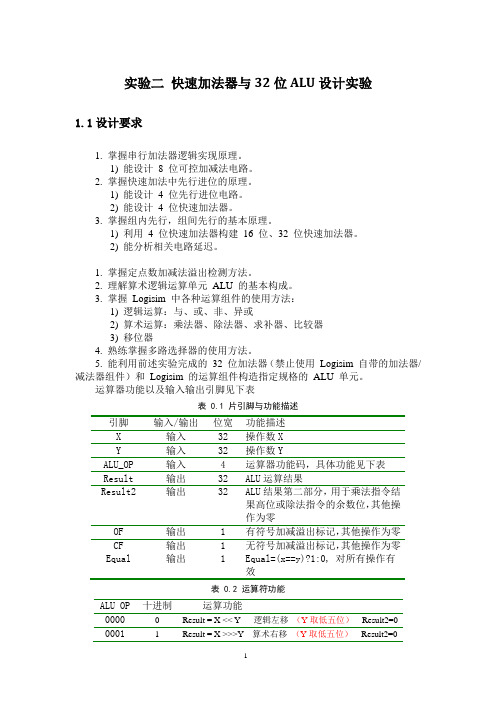

实验二快速加法器与32位ALU设计实验1.1设计要求1. 掌握串行加法器逻辑实现原理。

1) 能设计8 位可控加减法电路。

2. 掌握快速加法中先行进位的原理。

1) 能设计4 位先行进位电路。

2) 能设计4 位快速加法器。

3. 掌握组内先行,组间先行的基本原理。

1) 利用4 位快速加法器构建16 位、32 位快速加法器。

2) 能分析相关电路延迟。

1. 掌握定点数加减法溢出检测方法。

2. 理解算术逻辑运算单元ALU 的基本构成。

3. 掌握Logisim 中各种运算组件的使用方法:1) 逻辑运算:与、或、非、异或2) 算术运算:乘法器、除法器、求补器、比较器3) 移位器4. 熟练掌握多路选择器的使用方法。

5. 能利用前述实验完成的32 位加法器(禁止使用Logisim 自带的加法器/减法器组件)和Logisim 的运算组件构造指定规格的ALU 单元。

运算器功能以及输入输出引脚见下表表 0.1 片引脚与功能描述引脚输入/输出位宽功能描述X 输入32 操作数XY 输入32 操作数YALU_OP 输入 4 运算器功能码,具体功能见下表Result 输出32 ALU运算结果Result2 输出32 ALU结果第二部分,用于乘法指令结果高位或除法指令的余数位,其他操作为零OF 输出 1 有符号加减溢出标记,其他操作为零CF 输出 1 无符号加减溢出标记,其他操作为零Equal 输出 1 Equal=(x==y)?1:0, 对所有操作有效表 0.2 运算符功能ALU OP 十进制运算功能0000 0 Result = X << Y 逻辑左移(Y取低五位)Result2=00001 1 Result = X >>>Y 算术右移(Y取低五位)Result2=00010 2 Result = X >> Y 逻辑右移(Y取低五位)Result2=00011 3 Result = (X * Y)[31:0]; Result2 = (X *Y)[63:32] 有符号0100 4 Result = X/Y; Result2 = X%Y 无符号0101 5 Result = X + Y Result2=0 (Set OF/CF)0110 6 Result = X - Y Result2=0 (Set OF/CF)0111 7 Result = X & Y Result2=01000 8 Result = X | Y Result2=01001 9 Result = X⊕Y Result2=01010 10 Result = ~(X |Y) Result2=01011 11 Result = (X < Y) ? 1 : 0 Signed Result2=01100 12 Result = (X < Y) ? 1 : 0 Unsigned Result2=01101 13 Result = Result2=01110 14 Result = Result2=01111 15 Result = Result2=01.2方案设计1.2.1 八位可控加减法器原理:补码减法变加法原理减法变加法原因:负数的减法运算也要设法化为加法来做,其所以使用这种方法而不使用直接减法,是因为它可以和常规的加法运算使用同一加法器电路,从而简化了计算机的设计。

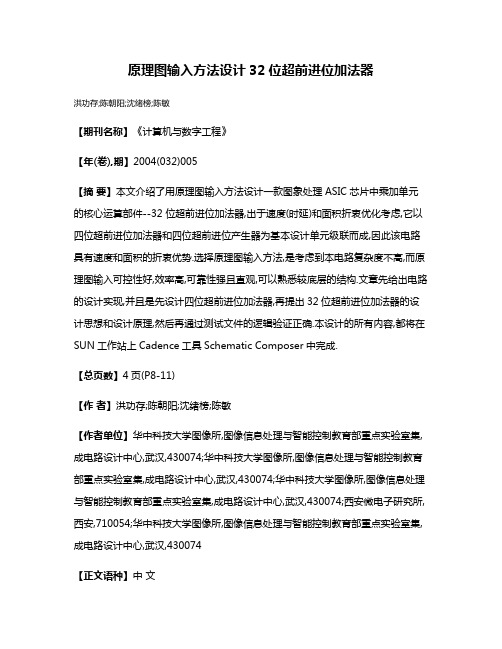

原理图输入方法设计32位超前进位加法器

原理图输入方法设计32位超前进位加法器洪功存;陈朝阳;沈绪榜;陈敏【期刊名称】《计算机与数字工程》【年(卷),期】2004(032)005【摘要】本文介绍了用原理图输入方法设计一款图象处理ASIC芯片中乘加单元的核心运算部件--32 位超前进位加法器,出于速度(时延)和面积折衷优化考虑,它以四位超前进位加法器和四位超前进位产生器为基本设计单元级联而成,因此该电路具有速度和面积的折衷优势.选择原理图输入方法,是考虑到本电路复杂度不高,而原理图输入可控性好,效率高,可靠性强且直观,可以熟悉较底层的结构.文章先给出电路的设计实现,并且是先设计四位超前进位加法器,再提出32位超前进位加法器的设计思想和设计原理,然后再通过测试文件的逻辑验证正确.本设计的所有内容,都将在SUN工作站上Cadence工具Schematic Composer中完成.【总页数】4页(P8-11)【作者】洪功存;陈朝阳;沈绪榜;陈敏【作者单位】华中科技大学图像所,图像信息处理与智能控制教育部重点实验室集,成电路设计中心,武汉,430074;华中科技大学图像所,图像信息处理与智能控制教育部重点实验室集,成电路设计中心,武汉,430074;华中科技大学图像所,图像信息处理与智能控制教育部重点实验室集,成电路设计中心,武汉,430074;西安微电子研究所,西安,710054;华中科技大学图像所,图像信息处理与智能控制教育部重点实验室集,成电路设计中心,武汉,430074【正文语种】中文【中图分类】TN402【相关文献】1.基于方块超前进位的快速进位跳跃加法器 [J], 崔晓平;王成华2.基于选择进位32位加法器的硬件电路实现 [J], 高建卫3.基于改进型选择进位加法器的32位浮点乘法器设计 [J], 刘容;赵洪深;李晓今4.32位高速动态CMOS超前进位加法器的研究 [J], 周冬生; 黄令仪; 张福甲5.32位高速动态CMOS超前进位加法器的研究 [J], 周冬生; 黄令仪; 张福甲因版权原因,仅展示原文概要,查看原文内容请购买。

计算机设计与实践——32位ALU设计ppt课件

if(Sub==1) alu_db_mux=alu_db_n; else alu_db_mux=alu_db;

8

end alu_32 alu_32_1(alu_add,alu_da,alu_db_mux,Sub,c2); assign overflow=alu_da[31]&alu_db_mux[31]&~alu_add[31]|~alu_da[31]&~alu_db_mux[31]&alu_add[31]; assign

6

21:alu_srl<=alu_da>>21; 22:alu_srl<=alu_da>>22; 23:alu_srl<=alu_da>>23; 24:alu_srl<=alu_da>>24; 25:alu_srl<=alu_da>>25; 26:alu_srl<=alu_da>>26; 27:alu_srl<=alu_da>>27; 28:alu_srl<=alu_da>>28; 29:alu_srl<=alu_da>>29; 30:alu_srl<=alu_da>>30; 31:alu_srl<=alu_da>>31; default:alu_srl<=alu_da; endcase end always@(*) begin case(alu_shift) 0:alu_sra<=alu_da; 1:alu_sra<={{alu_da[31]},alu_da[31:1]}; 2:alu_sra<={{2{alu_da[31]}},alu_da[31:2]}; 3:alu_sra<={{3{alu_da[31]}},alu_da[31:3]}; 4:alu_sra<={{4{alu_da[31]}},alu_da[31:4]}; 5:alu_sra<={{5{alu_da[31]}},alu_da[31:5]}; 6:alu_sra<={{6{alu_da[31]}},alu_da[31:6]}; 7:alu_sra<={{7{alu_da[31]}},alu_da[31:7]}; 8:alu_sra<={{8{alu_da[31]}},alu_da[31:8]}; 9:alu_sra<={{9{alu_da[31]}},alu_da[31:9]}; 10:alu_sra<={{10{alu_da[31]}},alu_da[31:10]}; 11:alu_sra<={{11{alu_da[31]}},alu_da[31:11]}; 12:alu_sra<={{12{alu_da[31]}},alu_da[31:12]};

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

jiafaqi_4 alu_4_2(g[2],p[2],f16[8:5],x16[8:5],y16[8:5],c[1]);

jiafaqi_4 alu_4_3(g[3],p[3],f16[12:9],x16[12:9],y16[12:9],c[2]);

jiafaqi_4 alu_4_4(g[4],p[4],f16[16:13],x16[16:13],y16[16:13],c[3]);

input [4:1]x;

//四位x值

input [4:1]y;

//四位y值

output [4:1]f;

//四位加和f

output gm,pm;

input c0;

//上一的级进位

wire [3:1]c;

//超前进位

wire [4:1]p;

wire [4:1]g;

assign p=x|y;

assign g=x&y;

x32 = 32

ciii = 0;

#100;

x32 = 32'h10000000;

y32 = 32'h10000000;

ciii = 1;

end

endmodule

精选ppt

8

此课件下载可自行编辑修改,供参考! 感谢您的支持,我们努力做得更好!

output f;

assign f=(x^y)^c0;

endmodule

module cla_4(c,p,g,c0);//4位CLA部件

input [4:1]p;

input [4:1]g;

input c0;

output [4:1]c;

assign c[1]=g[1]|p[1]&c0;

assign c[2]=g[2]|p[2]&g[1]|p[2]&p[1]&c0;

input [16:1]x16;

input [16:1]y16;

input cii;

output [16:1]f16;

output gmm,pmm;

wire [4:1]c;

wire [4:1]p;

wire [4:1]g;

jiafaqi_4 alu_4_1(g[1],p[1],f16[4:1],x16[4:1],y16[4:1],cii);

assign c[1]=g[1]|p[1]&c0;

assign c[2]=g[2]|p[2]&g[1]|p[2]&p[1]&c0;

assign c[3]=g[3]|p[3]&g[2]|p[2]&p[3]&g[1]|p[3]&p[2]&p[1]&c0;

assign c4=g[4]|p[4]&g[3]|p[4]&p[3]&g[2]|p[4]&p[3]&p[2]&g[1]|p[4]&p[3]&p[2]&p[1]&c0;

assign c[3]=g[3]|p[3]&g[2]|p[2]&p[3]&g[1]|p[3]&p[2]&p[1]&c0;

assign c[4]=g[4]|p[4]&g[3]|p[4]&p[3]&g[2]|p[4]&p[3]&p[2]&g[1]|p[4]&p[3]&p[2]&p[1]& c0;

endmodule

精选ppt

7

initial begin

x32 = 0;

y32 = 0;

ciii = 0;

#100;

x32 = 32'haaaaaaaa;

y32 = 32'h55555555;

ciii = 0;

#100;

x32 = 32'haaaaaaaa;

y32 = 32'h55555555;

ciii = 1;

#100;

cla_4 cl_4_1(c,p,g,cii);

assign pmm=p[4]&p[3]&p[2]&p[1];

assign gmm=g[4]|p[4]&g[3]|p[4]&p[3]&g[2]|p[4]&p[3]&p[2]&g[1];

endmodule

精选ppt

4

module jiafaqi_4(gm,pm,f,x,y,c0); //四位超前进位加法器

assign pm=p[4]&p[3]&p[2]&p[1];

assign gm=g[4]|p[4]&g[3]|p[4]&p[3]&g[2]|p[4]&p[3]&p[2]&g[1];

jiafaqi_1 jia1(x[1],y[1],c0,f[1]);

jiafaqi_1 jia2(x[2],y[2],c[1],f[2]);

jiafaqi_1 jia3(x[3],y[3],c[2],f[3]);

jiafaqi_1 jia4(x[4],y[4],c[3],f[4]);

endmodule

精选ppt

5

module jiafaqi_1(x,y,c0,f); //一位加法器模块

input x;

input y;

input c0;

精选ppt

6

测试代码:

module test;

reg [32:1] x32;

reg [32:1] y32;

reg ciii;

wire c2;

wire [32:1] f32;

alu_32 uut (

.c2(c2),

.f32(f32),

.x32(x32),

.y32(y32),

.ciii(ciii)

);

input [32:1]x32;

input [32:1]y32;

input ciii;

output [32:1]f32;

output c2;

wire c1;

wire [2:1]p;

wire [2:1]g;

精选ppt

3

module alu_16(gmm,pmm,f16,x16,y16,cii);//16位加法器先行进位加法器

32位先行进位加法器

——Verilog HDL语言

精选ppt

1

32位超前进位加法器的进位是并 行同时产生的,能够极大的减 少加法器由进位引起的延时。 增加了逻辑器件,但有效的减 少的延迟。进位是由cla部件超 前算出,本位是由不含进位的 加法器算出。

精选ppt

2

Verilog HDL代码如下:

module alu_32(c2,f32,x32,y32,ciii);//32位加法 器先行进位加法器