LTC4444HMS8E-5#PBF;LTC4444HMS8E-5#TRPBF;中文规格书,Datasheet资料

MEMORY存储芯片LTC4054ES5-4.2中文规格书

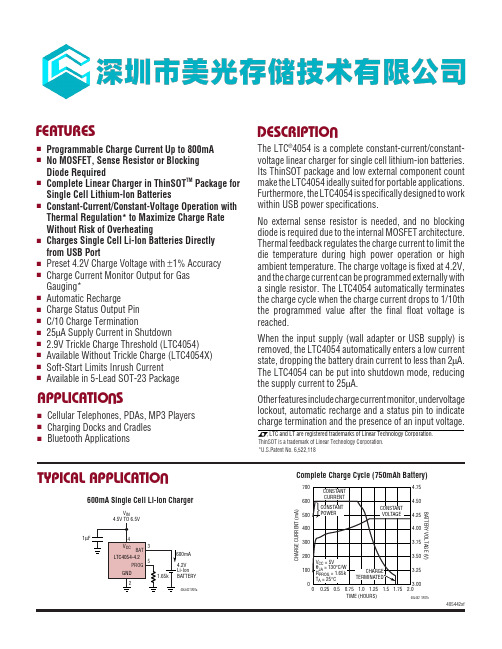

LTC4054-4.2/LTC4054X-4.2OPERATIOUThe LTC4054 is a single cell lithium-ion battery charger using a constant-current/constant-voltage algorithm. It can deliver up to 800mA of charge current (using a good thermal PCB layout) with a final float voltage accuracy of ±1%. The LTC4054 includes an internal P-channel power MOSFET and thermal regulation circuitry. No blocking diode or external current sense resistor is required; thus,the basic charger circuit requires only two external com-ponents. Furthermore, the LTC4054 is capable of operat-ing from a USB power source.Normal Charge CycleA charge cycle begins when the voltage at the V CC pin rises above the UVLO threshold level and a 1% program resistor is connected from the PROG pin to ground or when a battery is connected to the charger output. If the BAT pin is less than 2.9V, the charger enters trickle charge mode.In this mode, the LTC4054 supplies approximately 1/10the programmed charge current to bring the battery volt-age up to a safe level for full current charging. (Note: The LTC4054X does not include this trickle charge feature).When the BAT pin voltage rises above 2.9V, the charger enters constant-current mode, where the programmed charge current is supplied to the battery. When the BAT pin approaches the final float voltage (4.2V), the LTC4054enters constant-voltage mode and the charge current begins to decrease. When the charge current drops to 1/10 of the programmed value, the charge cycle ends.Programming Charge CurrentThe charge current is programmed using a single resistor from the PROG pin to ground. The battery charge current is 1000 times the current out of the PROG pin. The program resistor and the charge current are calculated using the following equations:R V I I VR PROG CHG CHG PROG==10001000,The charge current out of the BAT pin can be determinedat any time by monitoring the PROG pin voltage using the following equation:I V R BAT PROGPROG=•1000Charge TerminationA charge cycle is terminated when the charge current falls to 1/10th the programmed value after the final float voltage is reached. This condition is detected by using an internal,filtered comparator to monitor the PROG pin. When the PROG pin voltage falls below 100mV 1 for longer than t TERM (typically 1ms), charging is terminated. The charge current is latched off and the LTC4054 enters standby mode, where the input supply current drops to 200µA.(Note: C/10 termination is disabled in trickle charging and thermal limiting modes).When charging, transient loads on the BAT pin can cause the PROG pin to fall below 100mV for short periods of time before the DC charge current has dropped to 1/10th the programmed value. The 1ms filter time (t TERM ) on the termination comparator ensures that transient loads of this nature do not result in premature charge cycle termi-nation. Once the average charge current drops below 1/10th the programmed value, the LTC4054 terminates the charge cycle and ceases to provide any current through the BAT pin. In this state, all loads on the BAT pin must be supplied by the battery.The LTC4054 constantly monitors the BAT pin voltage in standby mode. If this voltage drops below the 4.05V recharge threshold (V RECHRG ), another charge cycle be-gins and current is once again supplied to the battery. To manually restart a charge cycle when in standby mode, the input voltage must be removed and reapplied, or the charger must be shut down and restarted using the PROG pin. Figure 1 shows the state diagram of a typical charge cycle.Charge Status Indicator (CHRG)The charge status output has three different states: strong pull-down (~10mA), weak pull-down (~20µA) and high impedance. The strong pull-down state indicates that the LTC4054 is in a charge cycle. Once the charge cycle has terminated, the pin state is determined by undervoltageNote 1: Any external sources that hold the PROG pin above 100mV will prevent the LTC4054from terminating a charge cycle.LTC4054-4.2/LTC4054X-4.2。

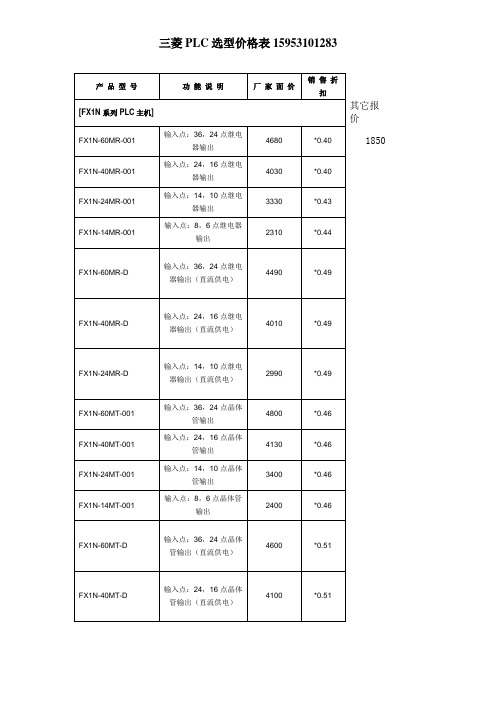

三菱变频器PLC选型价格表

0.6

FX-EEPROM-8

8K EEPROM MEMORY CASSETTE

620

0.6

FX-EEPROM-16

16K EEPROM MEMORY CASSETTE

1020

0.6

[通讯模块]

FX2NC-232-ADP

RS232通讯模块

1230

*0.60

FX2NC-485-ADP

RS485通讯模块

输入点:16,16继电器输出(直流供电)

5180

*0.49

FX2N-128MT-001

输入点:64,64点晶体管输出

10330

*0.44

FX2N-80MT-001

输入点:40,40点晶体管输出

7180

*0.42

FX2N-64MT-001

输入点:32,32点晶体管输出

6410

*0.42

FX2N-48MT-001

输入点:36,24点晶体管输出

4800

*0.46

FX1N-40MT-001

输入点:24,16点晶体管输出

4130

*0.46

FX1N-24MT-001

输入点:14,10点晶体管输出

3400

*0.46

FX1N-14MT-001

输入点:8,6点晶体管输出

2400

*0.46

FX1N-60MT-D

输入点:36,24点晶体管输出(直流供电)

4通道D/A

3270

*0.46

FX2N-5A

4通道A/D, 1通道D/A

3400

*0.53

FX2N-8AD

8通道A/D

7630

*0.46

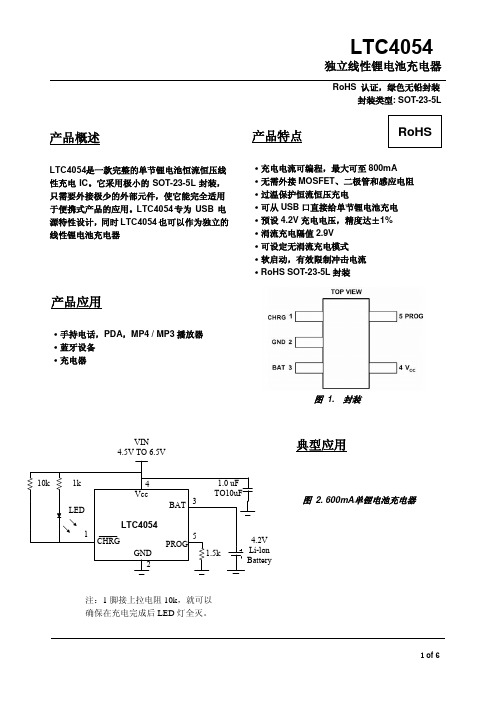

LTC4054

通过热反馈减小充电电流的条件可以近似地估算芯片的耗散功率。几乎所有的功率损耗均是由内部 MOSFET 产生的,有如下近似计算公式:

= PD (VCC −VBAT )IBAT

热保护时芯片周围温度为:

TA = 120°C − PDθJA = 120°C − (VCC −VBAT )I θ BAT JA

产品应用

·充电电流可编程,最大可至 800mA ·无需外接 MOSFET、二极管和感应电阻 ·过温保护恒流恒压充电 ·可从 USB 口直接给单节锂电池充电 ·预设 4.2V 充电电压,精度达±1% ·涓流充电隔值 2.9V ·可设定无涓流充电模式 ·软启动,有效限制冲击电流 ·RoHS SOT-23-5L 封装

充电电流编程脚

CHRG(1):开漏极充电状态输出脚。当对电池充电时,内部 NMOS 管高阻态,LED 灭。

GND(2):电源地。 BAT(3):充电电流输出脚。向电池提供充电电流,同时控制充电完成电压为 4.2V。内部精确电阻分压

0.35

V

二次充电隔值电压

△VRECHRG VFLOAT - VRECHRG

200

mV

恒温下结温

T LIM

120

°C

软启动时间

tSS

IBAT =0至1000V/RPROG

115

μs

二次充电比较器的滤波 器滞后时间 终止充电比较器的滤波 器滞后时间

tRECHRG VBAT由高到低 IBAT降至ICHRG /10

3.9

单位

V

μA

V

mA mA μA μA μA mA V V

电压低压关断滞后电压

V UVHYS

250

mV

PROG脚电压上升时

ADI General RoHS Compliance Information说明书

1.RoHS compliant definitionADI defines RoHS compliant to mean Pb, Hg, Cd, Cr (+6), PBB, PBDE, DEHP, BBP, DBP and DIBP are not intentionally added during the manufacturing process and have upper concentration limits as defined below. In addition, RoHS compliant indicates the packages can withstand a peak reflow temperature of 255 +5/-0 deg C.RoHS Banned Substance CAS Number Maximum Concentration ValueHg (Mercury) 7439-92-1 1000 ppmPb (Lead) 7439-97-6 1000 ppmCd (Cadmium) 7440-43-9 100 ppmCr(+6) (Hexavalent Chromium) 18540-29-9 1000 ppmPBB (Polybrominated Biphenyl) - 1000 ppmPBDE (Polybrominated Diethyl Ether) - 1000 ppmDEHP (Bis(2-Ethylhexyl) phthalate ) - 1000 ppmBBP (Benzyl butyl phthalate) - 1000 ppmDBP (Dibutyl phthalate) - 1000 ppmDIBP (Diisobutyl phthalate) - 1000 ppm2.RoHS compliant package materials and terminal finishesADI offers RoHS compliant solutions for most of its products. Material sets have been qualified to withstand a +255°C (+5/-0°C) peak reflow temperature. The primary terminal finishes for plastic encapsulated and hermetic products are matte Sn plating with a post plating bake (1 hour at 150°C within 24 hours of plating, implemented between EIA date code 0518-0522), SnAgCu solder spheres, and Au plating. NiPdAu is also available for select products.3.Part naming convention for RoHS complianceThe ADI legacy standard naming convention for RoHS compliant products requires the letter "Z" as a suffix to the existing part number.All Hittite legacy products are RoHS Compliant. However, the Hittite Federal products standard naming convention for RoHS compliant products requires the letter "E" as a suffix to the existing part number.All LTC legacy products bearing the suffix "#PBF OR #TRPBF” after the part number are RoHS compliant.The suffix “Z”, “E” and "#PBF or #TRPBF" generally appears at the end of the part name (i.e. after the character that denotes the package style). For example:Standard Part Name RoHS Compliant Part NameADI Legacy Products ADM1024ARU-REEL ADM1024ARUZ-REELAD648KR AD648KRZHittite Legacy Products HMC6407LP5 HMC6407LP5EHMC199AMS8TR HMC199MS8ETRLTC Legacy Products LTC1517CS5-3.3 LTC1517CS5-3.3#PBFLTC6993MPS6-4#TR LTC6993MPS6-4#TRPBFCertain products introduced to the market as RoHS compliant only (i.e. there is no standard SnPb or SnPbAg finish on these parts) do not carry a "Z" suffix, but the data sheet, web product page, part marking, and labeling clearly indicate these products as RoHS compliant.All models intended to be offered as RoHS compliant are visible to customers through the WWW ordering guide.Customers should contact Local Sales or Distributors with any new product transition requests.4.Part marking convention for RoHS complianceRoHS compliant devices have a "#" symbol marked on the top or bottom of the package. Smaller packages, such as SOT23, SC70 and TSOT, are too small to accommodate an additional character, and as a result, there is no "#" marking on the package. For these smaller packages, a unique brand code is used to denote RoHS compliance.5.China RoHSAnalog Devices products considered as EU RoHS Compliant part, do not contain any China RoHS substance above the indicated levels set forth in the People’s Republic of China Electronic Industry Standard SJ/T 11364-2006 for theRequirements for Concentration Limits for Certain Hazardous Substances in Electronic Information Product.beling for RoHS complianceShipping containers for products compliant with RoHS regulations are labeled with “RoHS Compliant” and Chinaenvironment-friendly logos. The labels also contain the Pb free external finish code (i.e., e3, e1, etc) as specified in JEDEC JESD97 standard and MSL ratings.Shipping LabelLOGOS RoHS China Environment-Friendly Use Period or EFUP *RoHSCompliantRoHS ExemptSOT23 FCOL, , Flip chip CSP BGA and Flip chip BGA_ED labeled as “RoHS with Exemption” use lead contained solder bumps that fall under Exemption 15 Lead in solders to complete a viable electrical connection between semiconductor die and carrier within integrated circuit flip chip packages9.Reflow ProfileADI advises reflow profiles should conform to JEDEC J-STD-020 standard which can be downloaded from the JEDEC website under “Free Standards”./9.Backward and forward compatibilityBackward compatibility for matte Sn, NiPdAu and Au: ADI products with matte Sn, NiPdAu, and Au finishes are backward compatible with optimized SnPb reflow processes.Backward compatibility for SnAgCu: ADI products with SnAgCu solder finishes are not backward compatible with SnPb reflow processes.Forward compatibility for SnPb: ADI products with SnPb finish are not forward compatible with +255°C (+5/-0°C) reflow processes. Concerns include weak solder joints caused by Bi in the solder paste reacting with Pb delamination resulting from package material sets that are not +255°C (+5/-0°C) compatible, and solder ball voiding caused by Pb free solder paste outgassing into the solder ball.10.Matte Sn whisker dataMatte Sn is a widely available industry standard that has been in production for many years with excellent quality and reliability. All matte Sn plated devices undergo a post plating bake for 1 hour at 150 degrees C within 24 hours of plating to mitigate Sn whisker growth. Sn whisker testing is done based on the test methodology outlined in JEDEC JESD22A121 standard (Test Method for Measuring Whisker Growth on Tin and Tin Alloy Surface Finishes) with read-point intervals of 1000 hours or 500 cycles. Test results are in the table below.Criteria Maximum 20 um(Class 1a) Maximum 40 um(Class 2)Maximum 45 um(Class 2)Package Preconditioning Temperature HumidityStorage(30/60%RH, 4000 Hrs)High TemperatureHumidity Storage(55'C/85%RH, 4000 Hrs)Temperature Cycle(-55/+85'C,1500 Cyc)LFCSPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableLQFPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableMQFPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableMINISONo precon See QSOP results See QSOP results See QSOP results Precon @ 215-220'C See QSOP results See QSOP results See QSOP results Precon @ 260'C Acceptable Acceptable AcceptablePDIPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableCriteria Maximum 20 um(Class 1a) Maximum 40 um(Class 2)Maximum 45 um(Class 2)Package Preconditioning Temperature HumidityStorage(30/60%RH, 4000 Hrs)High TemperatureHumidity Storage(55'C/85%RH, 4000 Hrs)Temperature Cycle(-55/+85'C,1500 Cyc)PLCCNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptablePSOPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableQSOPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSC70/ SOT143/ SOT23-3LdNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSOIC_NNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSOIC_WNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSOT223No precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableSOT23No precon See QSOP results See QSOP results See QSOP results Precon @ 215-220'C See QSOP results See QSOP results See QSOP results Precon @ 260'C Acceptable Acceptable AcceptableSSOPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableTQFPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable AcceptableTSSOPNo precon Acceptable Acceptable Acceptable Precon @ 215-220'C Acceptable Acceptable Acceptable Precon @ 260'C Acceptable Acceptable Acceptable11. RoHS Compliance for Evaluation BoardsAnalog Devices evaluation boards are specifically designed for the purpose of research and development and are made available solely on a business-to-business basis and are therefore excluded from the scope of the RoHS 2 Directive.。

MAX4445ESE中文资料

元器件交易网

Gain

Gain Error

Gain-Error Drift

Output Voltage Swing

Output Current Drive Power-Supply Rejection Ratio Common-Mode Rejection Ratio Disable Output Resistance EN Logic Low Threshold EN Logic High Threshold EN Logic Input Low Current EN Logic Input High Current

Current to 3.5mA

Applications

Differential-to-Single-Ended Conversion Twisted-Pair to Coaxial Converter High-Speed Instrumentation Amplifier Data Acquisition Medical Instrumentation High-Speed Differential Line Receiver

元器件交易网

MAX4444/MAX4445

Ultra-High Speed, Low-Distortion, Differentialto-Single-Ended Line Receivers with Enable

AC ELECTRICAL CHARACTERISTICS

瑞萨芯片选型

SuperH RISC engine 族产品概要:SuperH是具有高性能价格比、小型化和高性能功耗比(MIPS/W)特性的嵌入式RISC单片机。

我们正在开发具有广泛的应用范围和多种功能的CPU内核,并提供有强大的产品阵容。

产品系列包含具有CPU内核、内部大容量快速擦写存储器和定时器、串行接口、AD转换器等外围功能的SH-2系列;具有能进行高速数据处理的CPU内核、高速缓冲存储器和MMU的SH-3系列或SH-4系列;具有全DSP功能和以多媒体处理/通信处理为主的CPU内核的SH2-DSP系列或SH3-DSP系列。

现在提供的产品还具有低功率模式、低功耗和小型化等许多特点。

改善了各种通用操作系统和开发工具,从而保证能实现更有效的开发。

主要应用•MPUo汽车导航系统、CIS、娱乐设备和多媒体设备。

o宽带路由器、防火墙、网络设备和因特网设备。

o小型打印机、直接打印机、POS终端、便携式终端和网络终端。

o DVC、DSC和图像处理设备等。

•MCUo空调、电冰箱和洗衣机。

o打印机、传真机和复印机。

o工业设备和机床。

o汽车引擎和动力转向系统。

.瑞萨MCU选型指南有想法吗?请使用我们的,为您寻找最合适的瑞萨产品。

Lineup:SH7780系列SH7780系列是搭载SH-4A CPU内核的高端SuperH处理器。

SH-4A的指令集是完全向上兼容的。

SH-4A的工作频率比已有的SH-4 CPU内核高的多。

并且SH-4A CPU内核具有支持单精度和双精度算术运算的FPU。

SH7722 | SH7723 | SH7724 | SH7730 | SH7731 | SH7763 | SH7764 | SH7780 | SH7781 | SH7785 | SH7786SH7450 系列SH7450系列高性能微控制器配有SH-4A CPU内核。

SH7450系列整合了大容量Flash存储器和SRAM,使其能够适用于汽车主动安全系统,如驱动支持。

LTTJ资料

2 0.02 0.02 0.2

(Notes 6, 7, 10) (Note 11)

q

1 0.2 5 1 0 5 100 50 250 1.05

q q

V+

V MΩ MΩ

400 5 600

µV/V mV µV/V

1967f

元器件交易网

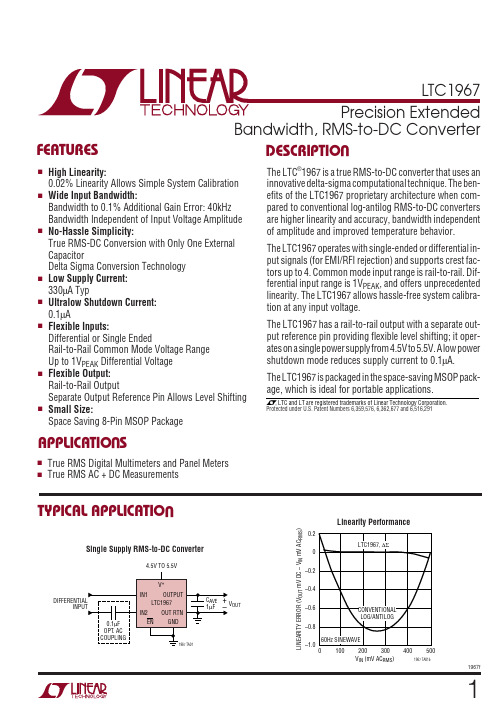

LTC1967

ELECTRICAL CHARACTERISTICS

CONDITIONS 50Hz to 5kHz Input (Notes 6, 7)

q

Additional Error vs Crest Factor (CF) 60Hz Fundamental, 200mVRMS 60Hz Fundamental, 200mVRMS Accuracy = 1% (Note 14) Average, Differential (Note 12) Average, Common Mode (Note 12) (Note 13) (Note 9)

, LTC and LT are registered trademarks of Linear Technology Corporation. Protected under U.S. Patent Numbers 6,359,576, 6,362,677 and 6,516,291

s

s

s

s

s

s

U APPLICATIO S

0.2 LTC1967, ∆Σ 0 –0.2 –0.4 –0.6 –0.8 –1.0 60Hz SINEWAVE 0 100 200 300 VIN (mV ACRMS) 400 500

1967 TA01b

Single Supply RMS-to-DC Converter

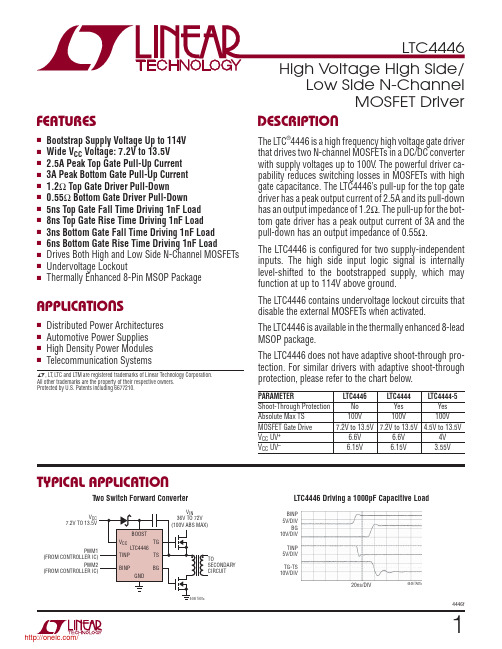

LTC4446EMS8E#PBF;LTC4446EMS8E#TRPBF;LTC4446IMS8E#PBF;LTC4446IMS8E#TRPBF;中文规格书,Datasheet资料

14446fTYPICAL APPLICATIONFEATURESAPPLICATIONSDESCRIPTIONLow Side N-ChannelMOSFET DriverThe L TC ®4446 is a high frequency high voltage gate driver that drives two N-channel MOSFETs in a DC/DC converter with supply voltages up to 100V . The powerful driver ca-pability reduces switching losses in MOSFETs with high gate capacitance. The L TC4446’s pull-up for the top gate driver has a peak output current of 2.5A and its pull-down has an output impedance of 1.2Ω. The pull-up for the bot-tom gate driver has a peak output current of 3A and the pull-down has an output impedance of 0.55Ω.The L TC4446 is confi gured for two supply-independent inputs. The high side input logic signal is internally level-shifted to the bootstrapped supply, which may function at up to 114V above ground.The L TC4446 contains undervoltage lockout circuits that disable the external MOSFETs when activated. The L TC4446 is available in the thermally enhanced 8-lead MSOP package.The L TC4446 does not have adaptive shoot-through pro-tection. For similar drivers with adaptive shoot-through protection, please refer to the chart below.PARAMETER L TC4446L TC4444L TC4444-5Shoot-Through Protection No Yes Yes Absolute Max TS 100V 100V 100V MOSFET Gate Drive 7.2V to 13.5V 7.2V to 13.5V 4.5V to 13.5VV CC UV +6.6V 6.6V 4V V CC UV– 6.15V 6.15V 3.55V nBootstrap Supply Voltage Up to 114V n Wide V CCVoltage: 7.2V to 13.5V n 2.5A Peak Top Gate Pull-Up Current n 3A Peak Bottom Gate Pull-Up Current n 1.2Ω Top Gate Driver Pull-Down n 0.55Ω Bottom Gate Driver Pull-Down n 5ns Top Gate Fall Time Driving 1nF Load n 8ns Top Gate Rise Time Driving 1nF Load n 3ns Bottom Gate Fall Time Driving 1nF Load n 6ns Bottom Gate Rise Time Driving 1nF Loadn Drives Both High and Low Side N-Channel MOSFETs n Undervoltage Lockoutn Thermally Enhanced 8-Pin MSOP PackagenDistributed Power Architecturesn Automotive Power Supplies n High Density Power Modules n Telecommunication SystemsT wo Switch Forward ConverterL TC4446 Driving a 1000pF Capacitive LoadL , L T , L TC and L TM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 6677210.V BINP 5V/DIVBG 10V/DIV TINP 5V/DIV TG-TS 10V/DIV20ns/DIV4446 TA01b/24446fPIN CONFIGURATIONABSOLUTE MAXIMUM RATINGSSupply VoltageV CC.........................................................–0.3V to 14V BOOST – TS ...........................................–0.3V to 14V TINP Voltage .................................................–2V to 14V BINP Voltage .................................................–2V to 14V BOOST Voltage ........................................–0.3V to 114V TS Voltage ...................................................–5V to 100V Operating Temperature Range (Note 2)....–40°C to 85°C Junction Temperature (Note 3) .............................125°C Storage Temperature Range ...................–65°C to 150°C Lead Temperature (Soldering, 10 sec) ..................300°C(Note 1)1234TINP BINP V CC BG8765TS TG BOOST NCTOP VIEW9MS8E PACKAGE 8-LEAD PLASTIC MSOPT JMAX = 125°C, θJA = 40°C/W , θJC = 10°C/W (NOTE 4)EXPOSED PAD (PIN 9) IS GND, MUST BE SOLDERED TO PCBORDER INFORMATIONELECTRICAL CHARACTERISTICSSYMBOL PARAMETER CONDITIONSMIN TYP MAX UNITS Gate Driver Supply, V CC V CC Operating Voltage7.213.5V I VCCDC Supply Current TINP = BINP = 0V350550μA UVLO Undervoltage Lockout ThresholdV CC Rising V CC Falling Hysteresis l l6.005.606.606.154507.206.70V V mV Bootstrapped Supply (BOOST – TS)I BOOSTDC Supply Current TINP = BINP = 0V 0.12μA Input Signal (TINP , BINP)V IH(BG)BG Turn-On Input Threshold BINP Ramping High l 2.25 2.75 3.25V V IL(BG)BG Turn-Off Input Threshold BINP Ramping Low l 1.85 2.3 2.75V V IH(TG)TG Turn-On Input Threshold TINP Ramping High l 2.25 2.75 3.25V V IL(TG)TG Turn-Off Input Threshold TINP Ramping Lowl 1.852.3 2.75V I TINP(BINP)Input Pin Bias Current ±0.01±2μA High Side Gate Driver Output (TG)V OH(TG)TG High Output Voltage I TG = –10mA, V OH(TG) = V BOOST – V TG 0.7V V OL(TG)TG Low Output Voltage I TG = 100mA, V OL(TG) = V TG –V TSl 120220mV I PU(TG)TG Peak Pull-Up Current l 1.72.5A R DS(TG)TG Pull-Down Resistance l1.22.2ΩThe l denotes the specifi cations which apply over the full operating temperature range, otherwise specifi cations are at T A = 25°C. V CC = V BOOST = 12V , V TS = GND = 0V , unless otherwise noted.LEAD FREE FINISH TAPE AND REEL PART MARKING*PACKAGE DESCRIPTION TEMPERATURE RANGE L TC4446EMS8E#PBF L TC4446EMS8E#TRPBF L TDPZ 8-Lead Plastic MSOP –40°C to 85°C L TC4446IMS8E#PBFL TC4446IMS8E#TRPBFL TDPZ8-Lead Plastic MSOP–40°C to 85°CConsult L TC Marketing for parts specifi ed with wider operating temperature ranges. *The temperature grade is identifi ed by a label on the shipping container .Consult L TC Marketing for information on non-standard lead based fi nish parts.For more information on lead free part marking, go to: http://www.linear .com/leadfree/ For more information on tape and reel specifi cations, go to: http://www.linear .com/tapeandreel//34446fNote 1: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: The L TC4446E is guaranteed to meet specifi cations from 0°C to 85°C. Specifi cations over the –40°C to 85°C operatingtemperature range are assured by design, characterization and correlationELECTRICAL CHARACTERISTICS The l denotes the specifi cations which apply over the full operatingtemperature range, otherwise specifi cations are at T A = 25°C. V CC = V BOOST = 12V , V TS = GND = 0V , unless otherwise noted.SYMBOL PARAMETERCONDITIONSMINTYP MAXUNITS Low Side Gate Driver Output (BG)V OH(BG)BG High Output Voltage I BG = –10mA, V OH(BG) = V CC – V BG0.7VV OL(BG)BG Low Output Voltage I BG = 100mAl 55110mV I PU(BG)BG Peak Pull-Up Current l 23A R DS(BG)BG Pull-Down Resistance l0.55 1.1ΩSwitching Time (BINP (TINP) is Tied to Ground While TINP (BINP) is Switching. Refer to Timing Diagram)t PLH(TG)TG Low-High (Turn-On) Propagation Delay l 2545ns t PHL(TG)TG High-Low (Turn-Off) Propagation Delay l 2240ns t PLH(BG)BG Low-High (Turn-On) Propagation Delay l 1935ns t PHL(BG)BG High-Low (Turn-Off) Propagation Delay l 1430ns t DM(BGTG)Delay Matching BG Turn-Off and TG Turn-On l –151035ns t DM(TGBG)Delay Matching TG Turn-Off and BG Turn-On l –25–325ns t r(TG)TG Output Rise Time 10% – 90%, C L = 1nF 10% – 90%, C L = 10nF880ns ns t f(TG)TG Output Fall Time 10% – 90%, C L = 1nF 10% – 90%, C L = 10nF550ns ns t r(BG)BG Output Rise Time 10% – 90%, C L = 1nF 10% – 90%, C L = 10nF660ns ns t f(BG)BG Output Fall Time 10% – 90%, C L = 1nF 10% – 90%, C L = 10nF 330ns nswith statistical process controls. The L TC4446I is guaranteed over the full –40°C to 85°C operating temperature range.Note 3: T J is calculated from the ambient temperature T A and power dissipation P D according to the following formula: T J = T A + (P D • θJA °C/W)Note 4: Failure to solder the exposed back side of the MS8E package to the PC board will result in a thermal resistance much higher than 40°C/W .TYPICAL PERFORMANCE CHARACTERISTICSV CC Supply Quiescent Current vs VoltageBOOST-TS Supply Quiescent Current vs VoltageV CC Supply Current vs TemperatureV CC SUPPL Y VOL TAGE (V)00Q U I E S C E N T C U R R E N T (μA )501502002506789101112134504446 G011001234514300350400BOOST SUPPL Y VOL TAGE (V)00Q U I E S C E N T C U R R E N T (μA )501502002506789101112134004446 G021001234514300350TEMPERATURE (°C)V C C S U P P L Y C U R R E N T (μA )3503603704446 G03330300–40–25–105203550658095110125380340320310/44446fTYPICAL PERFORMANCE CHARACTERISTICSBoost Supply Current vs TemperatureOutput Low Voltage (V OL ) vs Supply VoltageOutput High Voltage (V OH ) vs Supply VoltageInput Thresholds (TINP , BINP) vs Supply VoltageInput Thresholds (TINP , BINP) vs TemperatureInput Thresholds (TINP , BINP) Hysteresis vs VoltageInput Thresholds (TINP , BINP) Hysteresis vs TemperatureV CC Undervoltage Lockout Thresholds vs TemperatureRise and Fall Time vs V CC Supply VoltageTEMPERATURE (°C)B O O S T S U P P L YC U R R E N T (μA )2503003504446 G041500–40–25–10520355065809511012540020010050SUPPL Y VOL TAGE (V)7O U T P U T V O L T A G E (m V )140104446 G058040891120016012010060121314SUPPL Y VOL TAGE (V)75T G O R B G O U T P U T V O L T A G E (V )689101512911124446 G0671314118101314SUPPL Y VOL TAGE (V)72.1T G O R B G I N P U T T H R E S H O L D (V )2.22.42.52.63.12.8911124446 G072.32.93.02.78101314TEMPERATURE (°C)–25T G O R B G I N P U T T H R E S H O L D (V )2.62.83.0954446 G082.42.22.52.72.92.32.12.053565–10–40110205080125SUPPL Y VOL TAGE (V)78375T G O R B G I N P U T T H R E S H OL D H Y S T E R E S I S (m V )425500911124446 G09400475450101314TEMPERATURE (°C)–40–25375T G O R B G I N P U T T H R E S H O L D H Y S T E R E S I S(m V )425500–105205065804446 G104004754503511095125TEMPERATURE (°C)–406.0V C C S U P L L Y V O L T A G E (V )6.16.36.46.56.7–2535654446 G116.26.62095125110–1055080SUPPL Y VOL TAGE (V)7R I S E /F A L L T I M E (n s )122830222632911124446 G12820161024618148101314/54446fTYPICAL PERFORMANCE CHARACTERISTICSRise and Fall Time vs Load CapacitancePeak Driver (TG, BG) Pull-Up Current vs TemperatureOutput Driver Pull-Down Resistance vs TemperaturePropagation Delay vs V CC Supply VoltagePropagation Delay vs TemperatureLOAD CAPACITANCE (nF)1R I S E /F A L L T I M E (n s )40506094445 G1330200357210468108070TEMPERATURE (°C)–402.0P U L L -U P C U R R E N T (A )2.22.62.83.03.4–2535654446 G142.43.22095125110–1055080TEMPERATURE (°C)–25O U T P U T D R I V E R P U L L -D O W N R E S I S T A C N E (Ω)1.21.62.0954446 G150.80.41.01.41.80.60.253565–10–40110205080125SUPPL Y VOL TAGE (V)710P R O P A G A T I O N D E L A Y (n s )121618203024911124444 G16142628228101314TEMPERATURE (°C)–402P R O P A G A T I O N D E L A Y (n s )717222737–2535654446 G1712322095125110–1055080Switching Supply Current vs Input FrequencySwitching Supply Current vs Load CapacitanceSWITCHING FREQUENCY (kHz)S U P P L Y C U R R E N T (m A )1.52.02.560010004446 G181.00.502004008003.03.54.0LOAD CAPACITANCE (nF)1S U P P L Y C U R R E N T (m A )1010013450.127896104446 G19/64446fPIN FUNCTIONSBLOCK DIAGRAMTINP (Pin 1): High Side Input Signal. Input referenced to GND. This input controls the high side driver output (TG).BINP (Pin 2): Low Side Input Signal. This input controls the low side driver output (BG).V CC (Pin 3): Supply. This pin powers input buffers, logic and the low side gate driver output directly and the high side gate driver output through an external diode con-nected between this pin and BOOST (Pin 6). A low ESR ceramic bypass capacitor should be tied between this pin and GND (Pin 9).BG (Pin 4): Low Side Gate Driver Output (Bottom Gate). This pin swings between V CC and GND.NC (Pin 5): No Connect. No connection required.BOOST (Pin 6): High Side Bootstrapped Supply. An ex-ternal capacitor should be tied between this pin and TS (Pin 8). Normally, a bootstrap diode is connected between V CC (Pin 3) and this pin. Voltage swing at this pin is from V CC – V D to V IN + V CC – V D , where V D is the forward volt-age drop of the bootstrap diode.TG (Pin 7): High Side Gate Driver Output (Top Gate). This pin swings between TS and BOOST .TS (Pin 8): High Side MOSFET Source Connection (Top Source).Exposed Pad (Pin 9): Ground. Must be soldered to PCB ground for optimal thermal performance.TIMING DIAGRAMTINP (BINP)BG (TG)BINP (TINP)TG (BG)/OPERATIONOverviewThe L TC4446 receives ground-referenced, low voltage digi-tal input signals to drive two N-channel power MOSFETs in a synchronous buck power supply confi guration. The gate of the low side MOSFET is driven either to V CC or GND, depending on the state of the input. Similarly, the gate of the high side MOSFET is driven to either BOOST or TS by a supply bootstrapped off of the switching node (TS). Input StageThe L TC4446 employs CMOS compatible input thresholds that allow a low voltage digital signal to drive standard power MOSF ETs. The LTC4446 contains an internal voltage regulator that biases both input buffers for high side and low side inputs, allowing the input thresholds (V IH = 2.75V, V IL = 2.3V) to be independent of variations inV CC. The 450mV hysteresis between V IH and V IL eliminates false triggering due to noise during switching transitions. However, care should be taken to keep both input pins (TINP and BINP) from any noise pickup, especially in high frequency, high voltage applications. The L TC4446 input buffers have high input impedance and draw negligible input current, simplifying the drive circuitry required for the inputs.Output StageA simplifi ed version of the L TC4446’s output stage is shown in Figure 1. The pull-up devices on the BG and TG outputs are NPN bipolar junction transistors (Q1 and Q2). The BG and TG outputs are pulled up to within an NPN V BE (~0.7V) of their positive rails (V CC and BOOST, respectively). Both BG and TG have N-channel MOSFET pull-down devices (M1 and M2) which pull BG and TG down to their nega-tive rails, GND and TS. The large voltage swing of the BG and TG output pins is important in driving external power MOSFETs, whose R DS(ON) is inversely proportional to the gate overdrive voltage (V GS − V TH).Rise/Fall TimeThe L TC4446’s rise and fall times are determined by the peak current capabilities of Q1 and M1. The predriver that drives Q1 and M1 uses a nonoverlapping transition scheme to minimize cross-conduction currents. M1 is fully turned off before Q1 is turned on and vice versa.Since the power MOSFET generally accounts for the ma-jority of the power loss in a converter, it is important to quickly turn it on or off, thereby minimizing the transition time in its linear region. An additional benefi t of a strong pull-down on the driver outputs is the prevention of cross- conduction current. For example, when BG turns the low side (synchronous) power MOSFET off and TG turns the high side power MOSFET on, the voltage on the TS pin will rise to V IN very rapidly. This high frequency positive voltage transient will couple through the C GD capacitance of the low side power MOSFET to the BG pin. If there is an insuffi cient pull-down on the BG pin, the voltage on the BG pin can rise above the threshold voltage of the low side power MOSFET, momentarily turning it back on. With Figure 1. Capacitance Seen by BG and TG During Switching/74446fOPERATIONboth the high side and low side MOSFETs conducting, signifi cant cross-conduction current will fl ow through the MOSFETs from V IN to ground and will cause substantial power loss. A similar effect occurs on TG due to the C GS and C GD capacitances of the high side MOSFET.The powerful output driver of the L TC4446 reduces the switching losses of the power MOSFET, which increase with transition time. The L TC4446’s high side driver is capable of driving a 1nF load with 8ns rise and 5ns fall times using a bootstrapped supply voltage V BOOST-TS of 12V while its low side driver is capable of driving a 1nF Power DissipationTo ensure proper operation and long-term reliability, the L TC4446 must not operate beyond its maximum tem-perature rating. Package junction temperature can be calculated by:T J = T A + P D (θJA)where:T J = Junction temperatureT A = Ambient temperatureP D = Power dissipationθJA = Junction-to-ambient thermal resistance Power dissipation consists of standby and switching power losses:P D = P DC + P AC + P QGwhere:P DC = Quiescent power lossP AC = Internal switching loss at input frequency, f INP QG = Loss due turning on and off the external MOSFET with gate charge QG at frequency f IN load with 6ns rise and 3ns fall times using a supply volt-age V CC of 12V.Undervoltage Lockout (UVLO)The L TC4446 contains an undervoltage lockout detector that monitors V CC supply. When V CC falls below 6.15V, the output pins BG and TG are pulled down to GND and TS, respectively. This turns off both external MOSFETs. When V CC has adequate supply voltage, normal operation will resume.APPLICATIONS INFORMATIONThe L TC4446 consumes very little quiescent current. TheDC power loss at V CC = 12V and V BOOST-TS = 12V is only(350μA)(12V) = 4.2mW.At a particular switching frequency, the internal power lossincreases due to both AC currents required to charge anddischarge internal node capacitances and cross-conduc-tion currents in the internal logic gates. The sum of thequiescent current and internal switching current with noload are shown in the Typical Performance Characteristicsplot of Switching Supply Current vs Input Frequency.The gate charge losses are primarily due to the large ACcurrents required to charge and discharge the capacitanceof the external MOSFETs during switching. For identicalpure capacitive loads C LOAD on TG and BG at switchingfrequency f IN, the load losses would be:P CLOAD = (C LOAD)(f)[(V BOOST-TS)2 + (V CC)2]In a typical synchronous buck confi guration, V BOOST-TSis equal to V CC – V D, where V D is the forward voltagedrop across the diode between V CC and BOOST. If thisdrop is small relative to V CC, the load losses can beapproximated as:P CLOAD = 2(C LOAD)(f IN)(V CC)2/84446fAPPLICATIONS INFORMATIONUnlike a pure capacitive load, a power MOSF ET’s gate capacitance seen by the driver output varies with its V GS voltage level during switching. A MOSFET’s capacitive load power dissipation can be calculated using its gate charge, Q G. The Q G value corresponding to the MOSFET’s V GS value (V CC in this case) can be readily obtained from the manufacturer’s Q G vs V GS curves. For identical MOSFETs on TG and BG:P QG = 2(V CC)(Q G)(f IN)To avoid damage due to power dissipation, the L TC4446 includes a temperature monitor that will pull BG and TG low if the junction temperature rises above 160°C. Normal operation will resume when the junction temperature cools to less than 135°C.Bypassing and GroundingThe LTC4446 requires proper bypassing on the V CC and V BOOST-TS supplies due to its high speed switching (nanoseconds) and large AC currents (Amperes). Careless component placement and PCB trace routing may cause excessive ringing.To obtain the optimum performance from the L TC4446: A. Mount the bypass capacitors as close as possible between the V CC and GND pins and the BOOST and TS pins. The leads should be shortened as much as possible to reduce lead inductance.B. Use a low inductance, low impedance ground plane to reduce any ground drop and stray capacitance. Remember that the L TC4446 switches greater than 3A peak currents and any signifi cant ground drop will degrade signal integrity.C. Plan the power/ground routing carefully. Know where the large load switching current is coming from and going to. Maintain separate ground return paths for the input pin and the output power stage.D. Keep the copper trace between the driver output pin and the load short and wide.E. Be sure to solder the Exposed Pad on the back side of the L TC4446 package to the board. Correctly soldered to a 2500mm2 doublesided 1oz copper board, the L TC4446 has a thermal resistance of approximately 40°C/W for the MS8E package. Failure to make good thermal contact between the exposed back side and the copper board will result in thermal resistances far greater than 40°C/W./94446f104446fTYPICAL APPLICATIONL T C 3722/L T C 4446 420W 36V -72V I N t o 12V /35A I s o l a t e d F u l l -B r i d g e S u p p l yL 1V I –V I 36V T /分销商库存信息:LINEAR-TECHNOLOGYLTC4446EMS8E#PBF LTC4446EMS8E#TRPBF LTC4446IMS8E#PBF LTC4446IMS8E#TRPBF。

74ls373中文资料

型号

tPd

54S373/74S373

7ns

54LS373/74LS373

17ns

PD 525mW 120mW

373 的输出端 O0~O7 可直接与总线相连。

当三态允许控制端 OE 为低电平时,O0~O7 为正常逻辑状态,可用来驱动负载或总

线。当 OE 为高电平时,O0~O7 呈高阻态,即不驱动总线,也不为总线的负载,但

ic中文-17IC中文资料网 - IC中文资料-IC渠道网 IC中文资料 - 电源 - 嵌入式 - 电路图 - 单片机 - 应用方案 - 技术文章

首 页 IC库存 电子资讯 技术资料

IC

非IC

求购信息

PDF 资料

IC库存搜索: 请输入IC型号

搜索

最新搜索: VN2406LZL1 MAX881REUB+T IC42S16400-6TG LTC2230IUP MSR320 HLMP-2700 GS-R405S EPF10K10LI84 …

IC中文资料

型号A开头

型号B 开头

型号C开头

·MCP1316中文资料MCP1317应用MCP1318 MCP1319封装图MC... ·MCP111 中文资料 MCP112 应用 pdf 封装图 管脚说明... ·MCP102中文资料MCP103应用MCP111 MCP121封装图MCP131... ·MCP41010 中文资料 MCP41050 应用 pdf MCP41100 封... ·MCP40D17中文资料 MCP40D18应用 pdf MCP40D19 封装图... ·DS12R885 中文资料 DS12CR887 应用 pdf DS12R887封... ·MAX6972ATJ 中文资料 MAX6973ATJ 应用 pdf 封装图 管脚... ·MCP14E3中文资料MCP14E4 应用 pdf 封装图 MCP14E5管脚说... ·MCP6V06中文资料 MCP6V07应用 pdf 封装图 MCP6V08管脚说... ·MCP6V01中文资料MCP6V02应用 pdf 封装图MCP6V03 管脚说明...

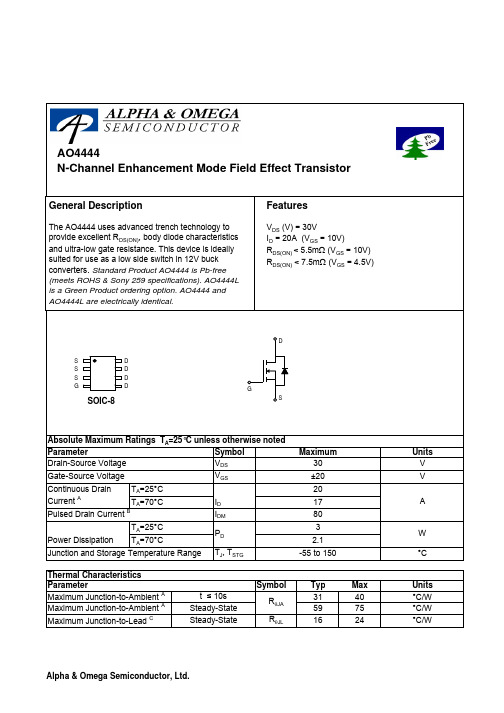

AO4444中文资料

SymbolTyp Max 31405975R θJL 1624Maximum Junction-to-Ambient A Steady-State °C/W Maximum Junction-to-Lead CSteady-State°C/WThermal Characteristics ParameterUnits Maximum Junction-to-Ambient A t ≤ 10s R θJA °C/W AO4444AO4444SymbolMin TypMaxUnits BV DSS 30V 1T J =55°C5I GSS 100nA V GS(th)1 1.83V I D(ON)60A 3.9 5.5T J =125°C5.16.25.17.5m Ωg FS 106S V SD 0.721V I S4A C iss 32003840pF C oss 590pF C rss 414pF R g0.540.7ΩQ g (10V)6376nC Q g (4.5V)3340nC Q gs 8.6nC Q gd 17.6nC t D(on)12ns t r 15.5ns t D(off)40ns t f 14ns t rr 3441ns Q rr30nCTHIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN,FUNCTIONS AND RELIABILITY WITHOUT NOTICE.Body Diode Reverse Recovery Charge I F =20A, dI/dt=100A/µsGate Source Charge V GS =0V, V DS =15V, f=1MHz SWITCHING PARAMETERS Total Gate Charge Total Gate Charge Gate resistanceV GS =0V, V DS =0V, f=1MHzV GS =4.5V, V DS =15V, I D =20ATurn-On DelayTime Turn-On Rise Time Turn-Off DelayTime Gate Drain Charge Maximum Body-Diode Continuous CurrentInput Capacitance Output Capacitance DYNAMIC PARAMETERS m ΩV GS =4.5V, I D =15AI S =1A,V GS =0V V DS =5V, I D =20AR DS(ON)Static Drain-Source On-ResistanceForward TransconductanceDiode Forward Voltage I DSS µA Gate Threshold Voltage V DS =V GS I D =250µA V DS =24V, V GS =0VV DS =0V, V GS = ±20V Zero Gate Voltage Drain Current Gate-Body leakage current Electrical Characteristics (T J =25°C unless otherwise noted)STATIC PARAMETERS ParameterConditions Turn-Off Fall TimeBody Diode Reverse Recovery TimeI F =20A, dI/dt=100A/µsDrain-Source Breakdown Voltage On state drain currentI D =250µA, V GS =0V V GS =10V, V DS =5V V GS =10V, I D =20AReverse Transfer Capacitance V GS =10V, V DS =15V, R L =0.75Ω, R GEN =3ΩA: The value of R θJA is measured with the device mounted on 1in 2 FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The value in any given application depends on the user's specific board design. The current rating is based on the t ≤ 10s thermal resistance rating.B: Repetitive rating, pulse width limited by junction temperature.C. The R θJA is the sum of the thermal impedence from junction to lead R θJL and lead to ambient.D. The static characteristics in Figures 1 to 6 are obtained using 80 µs pulses, duty cycle 0.5% max.E. These tests are performed with the device mounted on 1 in 2FR-4 board with 2oz. Copper, in a still air environment with T A =25°C. The SOA curve provides a single pulse rating. Rev 1 : June 2005AO4444AO4444。

FS FORTH-SYSTEME GmbH Mod520C_2 产品说明书

Mod520C_2P.O. Box 11 03l D-79200 Breisach, Germany Kueferstrasse 8l D-79206 Breisach, Germany (+49 (7667) 908-0 l Fax +49 (7667) 908-200 l e-mail:****************Mod520C_2© Copyright 2004:FS FORTH-SYSTEME GmbHPostfach 1103, D-79200 Breisach a. Rh., GermanyRelease of Document:May 27, 2004Filename:Mod520C_2.docAuthor:Hans-Peter SchneiderAll rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of FS FORTH-SYSTEME GmbH.2Mod520C_2 Table of Contents1.Introduction (4)2.Features (5)3.Functional Description (6)3.1.1.CPU AMD ÉlanSC520 (6)3.1.2.SDRAM stage (6)3.1.3.ROM stage (6)3.1.4.SRAM stage (6)3.1.5.32 I/O Ports (7)3.1.6.256 Byte EEPROM for BIOS and Applications on PIO30,31 (7)3.1.7.On-board Power Supply (7)3.1.8.Voltage Supervision, RESET Generation (7)3.1.9.Serial Ports (7)3.1.10.Fast Ethernet Controller Stage (8)3.1.11.Dual CAN Controller Stage (8)3.1.12.GP Bus used for ISA Bus (9)4.Connectors Of MOD520C (10)4.1.System Connector X2 (10)4.2.System Connector X4 (12)5.Application Notes (14)5.1.Power Supply (14)5.2.Important Signals (14)5.2.13.PCICLKRTN PCICLK PCICLKETHER (14)5.2.14.ISA-Bus Signals (14)5.2.15.CAN-Interrupt IRQ11 (15)6.Members of the MOD520C family (16)3Mod520C_21. IntroductionThe module MOD520C with its integrated and optional peripherals, based on the 32 Bit AMD ÉlanSC520 microcontroller, is designed for medium to high performance applications in telecommunication, data communication and information appliances on the general embedded market. It can easily be designed in customized boards.The AMD ÉlanSC520 microcontroller combines a low voltage 586 CPU running on 133 MHz, including FPU (Floating Point Unit) with a set of integrated peripherals: 32 Bit PCI controller, SDRAM controller for up to 256 MByte, GP (General Purpose) bus with programmable timing and ROM/Flash controller. Enhanced PC compatible peripherals like DMA controller, two UARTs and battery buffered RTC and CMOS, watchdog and software timers make this device a very fast system for both real time and PC/AT compatible applications. Insyde Software’s Mobile BIOS is available which offers serial and parallel remote features (video, keyboard, floppy). Furthermore FS FORTH-SYSTEME has adapted Datalight Sockets (TCP/IP Stack), ROM-DOS and the Flash File System FlashFX to this environment.The MOD520C offers the software engineer the possibility to reduce the time-to-market phase even more. FS FORTH-SYSTEME added several features on-board as SDRAM (up to 64 MByte), PCI Fast Ethernet controller to facilitate networking and remote control. A Strata-FLASH for booting and data is included on board. Two CAN Ports are additionally available for communication. 512 Kbyte SRAM is available for battery buffered data. The enhanced JTAG port for low-cost debugging is supported. This allows instruction tracing during execution. FS FORTH-SYSTEME has adapted Windows CE 3.0 to this platform and offers drivers and support. With Ethernet debugging the software designer has powerful means for fast debugging his applications.Due to the 16 MByte FLASH it is possible to build larger, complete systems on this module like Linux, QNX or VxWorks.4Mod520C_252. Features• 16 MByte STRATA-FLASH or 2 MByte AMD FLASH • 64 MByte or 16 MByte SDRAM • 512 KByte battery buffered SRAM• PCI Ethernet controller with EEPROM. Rx and Tx signals are providedon the System Connectors • Two CAN-Buses.• Enhanced JTAG port available on System Connector.• GP-Bus signals available on System Connector • PCI-Bus signals available on System Connector• BIOS for ÉlanSC520 by Insyde Software Inc. Including serial or parallelremote features (Video, Keyboard, Floppy).Mod520C_23. Functional Description3.1.1. CPU AMD ÉlanSC520The CPU AMD ÉlanSC520 is powered with 2.5V (core and analog path) and 3.3V (all other voltages) except VRTC, which is powered with about 3V either from battery or from on-board 3.3V. This voltage is limited to 3.3V, the other 3.3V power planes have a limit of 3.6V.The CPU is clocked with a 32.768 kHz quartz. An internal PLL derives from this frequency the RTC clock and DRAM refresh clock and the clocks for PC/AT compatible PIT (1.1882 MHz) and UARTs (18.432 MHz). All other stages (CPU, PCI, GP bus, GP DMA, ROM, SSI, timers) are fed from the second clock generator driven by a 33.33 MHz clock oscillator. SDRAM is clocked with 66.66 MHz.3.1.2. SDRAM stageThe SDRAM (up to 128 MByte on-board) has its own DRAM bus containing memory addresses MA0..12, memory data MD0..31 and control signals for up to four banks. Due to small load no buffering of clocks and signals is necessary.3.1.3. ROM stageROM or FLASH are driven by the general purpose address bus GPA0..25. It has three programmable chip selects with each up to 64 MByte range. The ROM Data bus is either the 32 bit general purpose bus GPD0..31 or the memory data bus MD0..31. Configuration pins decide, which bus at boot time is used. The bus size is selectable with 8, 16 or 32 bit. The MOD520C has a FLASH IC for up to 16 MByte 16 bit ROM or FLASH selected by BOOTCS# connected to MD0..15. 3.1.4. SRAM stageThe SRAM (512 KByte on-board) is buffered by VBAT. The Memory Location is defined in the System BIOS. ROMCS1# is used to access the SRAM.6Mod520C_23.1.5. 32 I/O PortsThe ÉlanSC520 CPU has 32 I/O ports. They have alternate functions. Most of them are control signals for GP bus (PIO0..26) used as ISA-bus. PIO27 (GPCS0#) is used as a programmable external chip select and PIO28,29 are not connected. PIO30,31 are used to drive a serial parameter EEPROM on-board. 3.1.6. 256 Byte EEPROM for BIOS and Applications on PIO30,31An on-board serial EEPROM with 256 byte and I2C bus is controlled by PIO30 (I2CDAT) and PIO31 (I2CCLK). 128 byte are used for non-volatile BIOS defaults, the remaining range may contain application specific data and parameters. The BIOS contains calls to read and write to this memory (see BIOS documentation).3.1.7. On-board Power SupplyThe 2.5V on-board voltage is generated from +5V.An external battery may be connected to the signal VBATIN. Battery status is controlled by BBATSEN, which sets a power fail bit in a status register for RTC, if BBATSEN is low at power-up.3.1.8. Voltage Supervision, RESET GenerationThree voltages are used on board: +2.5V, +3.3V and +5V. U2 controls +5V and U10 controls +3.3V. LBOUT or PWRGOOD will become low, if these voltages are out of tolerance. An external SRESET# is wired or-ed to U10. It can also be activated from extended JTAG signal SRESET# via X1. The wired OR of 1RESET# and 2RESET# control U10. Its output PWRGOOD is low (not active), if either the signals described above from U10 are low or +5V is out of tolerance. Typical length of PWRGOOD low is longer than 1 sec (minimum 790 msec).3.1.9. Serial PortsThe AMD ÉlanSC520 CPU has two internal asynchronous ports and one synchronous serial port. Both of this ports are available at the System Connectors.7Mod520C_23.1.10. Fast Ethernet Controller StageConnected to the PCI bus device 0 (REQ/GNT0#) of the Élan SC520 CPU, a Fast Ethernet Controller U7 supports 10/100Mbps transfer depending on driver software. X3 is a JST B5B-PH-SM3 5 pin connector. Parameters as physical address and power down modes are stored in a 64X16 bit Serial EEPROM controlled by U7. 2 status LEDs LE1, LE2 show the state of the Ethernet connection. For a more detailed hardware and software description see Intel 82559ER manual.3.1.11. Dual CAN Controller StageThe CAN Controller is selected via ROMCS1# and the Memory location is selectable in the BIOS Setup Screen. The CAN Interrupt provided by 82C900 is inverted by the onboard Lattice CPLD. Since the Interrupt asserted by the 82C900 is only a low active pulse of 0.2µs the CPLD holds the interrupt active until the software accesses the Memory at the location CAN-Base+1xxh. The BIOS routes this interrupt to IRQ11.8Mod520C_2 3.1.12. GP Bus used for ISA BusThe AMD ÉlanSC520 CPU contains an 8/16bit General Purpose Bus (GP bus) with 26 address lines (GPA0..25), 16 data lines (GPD0..15) and different control lines using PIO ports in their alternate GP bus function. Its timing is programmable for speeds up to 33MHz. This bus is to emulate a 16 bit ISA bus (PC/104) running with 8 MHz. ISA bus signal are connected without buffers directly to the lines of the CPU due to the 5V tolerance of the 3.3V signals.8 bit signals SMEMRD# and SMEMWR# (active only at addresses beyond 1 MByte) are not supported (GPMEM_RD# and GPMEM_WR# used).The AMD ÉlanSC520 CPU has only 4 DMA channels on GP bus. DMA channel 2 is used for Super-I/O (U2) on EVAMOD520. All four channels are connected to edge connector X2.Not supported ISA bus signals 0WS#, IOCHK#, IRQ15, REFRESH#, 8MHz and 14.318 MHz clocks, MASTER#.9Mod520C_24. Connectors Of MOD520C4.1. System Connector X2Pin Function I/O Pin Function I/O1+3.3V power2GND power 3+3.3V power4GND power 5GPD0I/O6TDP O7GPD1I/O8TDN O9GPD2I/O10not connected11GPD3I/O12RDP I13GPD4I/O14RDN I15GPD5I/O16not connected17GPD6I/O18DRQ0I19GPD7I/O20DRQ2I21GPD8I/O22DRQ5I23GPD9I/O24DRQ7I25GPD10I/O26DACK0#O27GPD11I/O28DACK2#O29GPD12I/O30DACK5#O31GPD13I/O32DACK7#O33GPD14I/O34GND power 35GPD15I/O36GPRESET O37GND power38GPIORD#O39GPA0O40GPIOWR#O41GPA1O42GPALE O43GPA2O44GPBHE#O45GPA3O46GPRDY I47GPA4O48GPAEN O49GPA5O50GPTC O51GPA6O52GPDBUFOE#O53GPA7O54GPIO_CS16#O55GPA8O56GPMEM_CS16#O57GPA9O58GPCS0#O59GPA10O60GPMEM_RD#O61GPA11O62GPMEM_WR#O63GPA12O64GND power 10Pin Function I/O Pin Function I/O65GPA13O66EXTRES#I67GPA14O68PWRGOOD O69BUFA15O70CLKTEST71BUFA16O72PRG_RESET73BUFA17O74GND power75BUFA18O76GPCS1#O77BUFA19O78GPCS2#O79BUFA20O80GPCS3#O81BUFA21O82GPCS4#O83BUFA22O84GPCS5#O85BUFA23O86GPCS6#O87BUFA24O88GPCS7#O89BUFA25O90VBATIN power91GND power92GND power93IRQ1I94RSTLD0I95IRQ3I96RSTLD1I97IRQ4I98RSTLD2I99IRQ5I100RSTLD3I101IRQ6I102RSTLD4I103IRQ7I104RSTLD5I105IRQ9I106RSTLD6I107IRQ10I108RSTLD7I109CANINT I110DBGDIS I111IRQ12I112INSTRC I113IRQ14I114DBGENTR I115SPEAKER O116not connected117+5V power118GND power119+5V power120GND power114.2. System Connector X4Pin Function I/O Pin Function I/O1PCICLKRTN I2GND power 3PCICLK O4PCICLKETHER I5AD0I/O6CBE0#I/O7AD1I/O8CBE1#I/O9AD2I/O10CBE2#I/O11AD3I/O12CBE3#I/O13AD4I/O14not connected15AD5I/O16not connected17AD6I/O18not connected19AD7I/O20not connected21AD8I/O22GND power 23AD9I/O24RXD1I25AD10I/O26TXD1O27AD11I/O28CTS1#I29AD12I/O30DCD1#I31AD13I/O32DSR1#I33AD14I/O34RIN1#I35AD15I/O36DTR1#O37AD16I/O38RTS1#O39AD17I/O40RXD2I41AD18I/O42TXD2O43AD19I/O44CTS2#I45AD20I/O46DCD2#I47AD21I/O48DSR2#I49AD22I/O50RIN2#I51AD23I/O52DTR2#O53AD24I/O54RTS2#O55AD25I/O56CANH1/TXD157AD26I/O58CANL1/RXD159AD27I/O60CANH2/TXD261AD28I/O62CANL2/RXD263AD29I/O64GND power 12Pin Function I/O Pin Function I/O65AD30I/O66SRESET#I67AD31I/O68GPRESET#O69GND power70TCK O71INTA#I72TMS73INTB#I74TDI I75INTC#I76TDO O77INTD#I78TRST#I79REQ0#I80CMDACK81REQ1#I82BR/TC83REQ2#I84GND Power85REQ3#I86STOP/TX87REQ4#I88TRIG/TRACE89GNT0#O90not connected91GNT1#O92ACTLED#O93GNT2#O94LILED#O95GNT3#O96SPEEDLED#O97GNT4#O98not connected99GND power100GND power101PAR I/O102SSI_CLK O103PERR#I/O104SSI_DO O105SERR#I106SSI_DI I107FRAME#I/O108not connected109TRDY#I/O110ISP_TDI I111IRDY#I/O112ISP_TDO O113STOP#I/O114ISP_TMS115DEVSEL#I/O116ISP_TCK I117RST#O118BSCAN#119GND power120GND power135. Application Notes5.1. Power SupplyThe MOD520C needs +3.3V and 5V power supply.3.3V worst case supply current is 1130 mA5V worst case supply current is 550 mABe sure to design your power supply for this current including large load transients.5.2. Important Signals5.2.13. PCICLKRTN PCICLK PCICLKETHERPCICLK is the clock source for the PCI-Bus. PCICLKETHER is the clock input for the Ethernet Controller. PCICLKRTN is the clock input of the AMD Élan Sc520. This pin is used to synchronize the CPU with the external PCI-Bus. Therefore it is important that all clock traces have the same length to provide each PCI-Target with the clock at the same time. Trace length of each of this clocks is 68mm on the module. If you do not plan to connect an additional PCI-Target on your board you just add a serial resistor 33R between PCICLK and PCICLKRTN and one between PCICLK and PCICLKETHER.5.2.14. ISA-Bus SignalsIf you use the ISA-Bus Signals you have to add some resistors to the following Signals:GPD0 – GPD15 4k7 pull upGPRDY1k pull downIRQ´s10k pull upDRQ´s10k pull down145.2.15. CAN-Interrupt IRQ11IRQ11 is used for the CAN-Controller 82C900 and is not sharable. Since the interrupt provided by 82C900 is a low active pulse with a length of 0.2µs the CPLD inverts this signal and holds it until the software acknowledges the interrupt. To acknowledge this interrupt the software has to access a memory location with the offset 1xxh to the CAN-Base. This memory access is just an access of the system memory, not an access of the CAN-Controller.156. Members of the MOD520C familyNumbe r Variant Flash SDRAM SRAM CAN CAN-DriverTemp.320MOD520C_0_V018M*16, Strata(=16 Mbyte)1*TM014452*4M*16(=16 Mbyte)2*TM01519512k*8Yes Yes0..70°321MOD520C_0_V021M*16, AMD(=2 Mbyte)1*TM015202*4M*16(=16 Mbyte)2*TM01519512k*8Yes Yes0..70°322MOD520C_0_V038M*16, Strata(=16 Mbyte)1*TM014452*16M*16(=64 Mbyte)2*TM01249512k*8Yes Yes0..70°334MOD520C_1_V01MOD520C_2_V018M*16, Strata(=16 Mbyte)1*TM014452*4M*16(=16 Mbyte)2*TM01519512k*8TM0Yes no0..70°335MOD520C_1_V02MOD520C_2_V021M*16, AMD(=2 Mbyte)1*TM015202*4M*16(=16 Mbyte)2*TM01519512k*8TM0Yes no0..70°336MOD520C_1_V03MOD520C_2_V038M*16, Strata(=16 Mbyte)1*TM014452*16M*16(=64 Mbyte)2*TM01249512k*8TM0Yes no0..70°184MOD520C_1_V048M*16, Strata(=16 Mbyte)1*TM014452*4M*16(=16 Mbyte)2*TM01519No No No0..70°16。

LTC1569-7 低通滤波器商品说明书

LTC1569CS8-7#PBF LTC1569IS8-7#PBF LTC1569CS8-6#PBF.12LTC1569-7PARAMETER CONDITIONSMIN TYP MAX UNITS Filter GainV S = 5V, f CLK = 8.192MHz,f IN = 5120Hz = 0.02 • f CUTOFF q –0.100.000.10dB f CUTOFF = 256kHz, V IN = 2.5V P-P ,f IN = 51.2kHz = 0.2 • f CUTOFF q –0.25–0.15–0.05dB R EXT = 5k, Pin 5 Shorted to Pin 4f IN = 128kHz = 0.5 • f CUTOFF q –0.50–0.41–0.25dB f IN = 204.8kHz = 0.8 • f CUTOFFq –1.1–0.65–0.40dB f IN = 256kHz = f CUTOFF , LTC1569C q –5.7–3.8–2.3dB f IN = 256kHz = f CUTOFF , LTC1569I q –6.2–3.8–2.0dB f IN = 384kHz = 1.5 • f CUTOFF q –58–48dB f IN = 512kHz = 2 • f CUTOFF q –62–54dB f IN = 768kHz = 3 • f CUTOFFq –67–64dB V S = 2.7V, f CLK = 1MHz,f IN = 625Hz = 0.02 • f CUTOFFq –0.080.000.12dB f CUTOFF = 31.25kHz, V IN = 1V P-P ,f IN = 6.25kHz = 0.2 • f CUTOFF q –0.25–0.15–0.05dB Pin 6 Shorted to Pin 4, External Clock f IN = 15.625kHz = 0.5 • f CUTOFFq –0.50–0.40–0.30dB f IN = 25kHz = 0.8 • f CUTOFF q –0.75–0.65–0.50dB f IN = 31.25kHz = f CUTOFFq –3.3–3.15–3.0dB f IN = 46.875kHz = 1.5 • f CUTOFF q –57–52dB f IN = 62.5kHz = 2 • f CUTOFF q –60–54dB f IN = 93.75kHz = 3 • f CUTOFFq –66–58dB Filter PhaseV S = 2.7V, f CLK = 4MHz,f IN = 2500Hz = 0.02 • f CUTOFF –11Deg f CUTOFF = 125kHz, Pin 6 Shorted to f IN = 25kHz = 0.2 • f CUTOFF q –114–112–110Deg Pin 4, External Clockf IN = 62.5kHz = 0.5 • f CUTOFF q 788082Deg f IN = 100kHz = 0.8 • f CUTOFF q –85–83–81Deg f IN = 125kHz = f CUTOFFq155158161Deg f IN = 187.5kHz = 1.5 • f CUTOFF–95DegFilter Cutoff Accuracy R EXT = 10.24k from Pin 6 to Pin 7,125kHz ±1%when Self-Clocked V S = 3V, Pin 5 Shorted to Pin 4Filter Output DC SwingV S = 3V, Pin 3 = 1.11V2.1V P-P q1.9V P-P V S = 5V, Pin 3 = 2V3.9V P-P q3.7V P-P V S = ±5V8.6V P-P LTC1569C q 8.4V P-P LTC1569Iq8.0V P-PA U G WA W U W A R BSOLUTEXI TI S W U UPACKAGE/ORDER I FOR ATIO(Note 1)Total Supply Voltage................................................11V Power Dissipation..............................................500mW Operating TemperatureLTC1569C ...............................................0°C to 70°C LTC1569I............................................–40°C to 85°C Storage Temperature............................–65°C to 150°C Lead Temperature (Soldering, 10 sec)..................300°CThe q denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T A = 25°C.V S = 3V (V + = 3V, V – = 0V), f CUTOFF = 128kHz, R LOAD = 10k unless otherwise specified.ELECTRICAL C C HARA TERISTICSConsult factory for Military grade parts.3LTC1569-7Output DC Offset R EXT = 10k, Pin 5 Shorted to Pin 4V S = 3V ±2±5mV (Note 2)V S = 5V ±6±12mV V S = ±5V ±15mV Output DC Offset DriftR EXT = 10k, Pin 5 Shorted to Pin 4V S = 3V –25µV/°C V S = 5V –25µV/°C V S = ±5V ±25µV/°CClock Pin Logic Thresholds V S = 3V Min Logical “1” 2.6V when Clocked ExternallyMax Logical “0”0.5V V S = 5V Min Logical “1” 4.0V Max Logical “0”0.5V V S = ±5VMin Logical “1” 4.0V Max Logical “0”0.5VPower Supply Current f CLK = 1.028MHz (10k from Pin 6 to Pin 7,V S = 3V68mA (Note 3)Pin 5 Open, ÷ 4), f CUTOFF = 32kHzq9mA V S = 5V79mA q10mA V S = 10V913mA q14mA f CLK = 4.096MHz (10k from Pin 6 to Pin 7,V S = 3V 9.5mA Pin 5 Shorted to Pin 4, ÷ 1), f CUTOFF = 128kHz q14mA f CLK = 8.192MHz (5k from Pin 6 to Pin 7,V S = 5V20mA Pin 5 Shorted to Pin 4, ÷ 1), f CUTOFF = 256kHzq30mA V S = 10V27mA q37mA Power Supply Voltage where Pin 5 Shorted to Pin 4, Note 3q3.74.2 4.6V Low Power Mode is Enabled Clock Feedthrough R EXT = 10k, Pin 5 Open 0.4mV RMS Wideband Noise Noise BW = DC to 2 • f CUTOFF 125µV RMSTHDf IN = 10kHz, 1.5V P-P74dBClock-to-Cutoff 32Frequency Ratio Max Clock Frequency V S = 3V 5MHz (Note 4)V S = 5V 9.6MHz V S = ±5V13MHz Min Clock Frequency 3V to ±5V, T A < 85°C 3kHz (Note 5)Input Frequency RangeAliased Components <–65dB 0.9 • f CLKHzThe q denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T A = 25°C.V S = 3V (V + = 3V, V – = 0V), f CLK = 4.096MHz, f CUTOFF = 128kHz, R LOAD = 10k unless otherwise specified.ELECTRICAL C C HARA TERISTICSPARAMETER CONDITIONSMINTYP MAX UNITS Note 1: Absolute maximum ratings are those values beyond which the life of a device may be impaired.Note 2: DC offset is measured with respect to Pin 3.Note 3: There are several operating modes which reduce the supply current. For V S < 4V, relative to divide-by-1 mode, the current is typically reduced by 50% relative to V S = 5V. If the internal oscillator is used as the clock source and the divide-by-4 or divide-by-16 mode is enabled, the supply current is typically reduced by 60%,relative to divide-by-1 mode,independent of the value of V S .Note 4: The maximum clock frequency is arbitrarily defined as thefrequency at which the filter AC response exhibits >1dB of gain peaking.Note 5: The minimum clock frequency is arbitrarily defined as the frequecy at which the filter DC offset changes by more than 5mV.Note 6: Thermal resistance varies depending upon the amount of PC board metal attached to the device. θJA is specified for a 2500mm 2 test board covered with 2oz copper on both sides.4LTC1569-7TYPICAL PERFOR A CE CHARACTERISTICSU WTHD vs Input VoltageTHD vs Input FrequencyINPUT VOLTAGE (V P-P )12345T H D (d B )1569-7 G02–50–60–70–80–90INPUT FREQUENCY (kHz)201030507090406080100T H D (d B )1569-7 G01–68–70–72–74–76–78FREQUENCY (kHz)L O G M A G (10d B /D I V )10–901569-7 G03FREQUENCY (kHz)G A I N (d B )DELAY (µs)1–1–2–3–420191817161514131211101569-7 G04Gain vs FrequencyPassband Gain and Group Delayvs Frequencyf CUTOFF (kHz)1I S U P P L Y (m A )1010010001569-7 G05121110987654f CUTOFF (kHz)1IS U P P L Y (m A )1010010001569-7 G06232119171513119755V Supply Current3V Supply CurrentfCUTOFF (kHz)1I S U P P L Y (m A )1010010001569-7 G0735322926232017141185± 5V Supply CurrentLTC1569-756LTC1569-7reduced. This results in a 60% power savings with a single 5V supply.Table1. f CUTOFF vs R EXT , V S = 3V, T A = 25°C, Divide-by-1 ModeR EXT Typical f CUTOFFTypical Variation of f CUTOFF3844Ω320kHz ±3.0%5010Ω256kHz ±2.5%10k 128kHz ±1%20.18k 64kHz ±2.0%40.2k32kHz±3.5%The power reduction in the divide-by-4 and divide-by-16modes, however, effects the fundamental oscillator fre-quency. Hence, the effective divide ratio will be slightly different from 4:1 or 16:1 depending on V S , T A and R EXT .Typically this error is less than 1% (Figures 4 and 6).Self-Clocking OperationThe LTC1569-7 features a unique internal oscillator which sets the filter cutoff frequency using a single external resistor . The design is optimized for V S = 3V, f CUTOFF =128kHz, where the filter cutoff frequency error is typically <1% when a 0.1% external 10k resistor is used. With different resistor values and internal divider settings, the cutoff frequency can be accurately varied from 2kHz to 150kHz/300kHz (single 3V/5V supply). As shown in Figure 1, the divider is controlled by the DIV/CLK (Pin 5).Table 1 summarizes the cutoff frequency vs external resistor values for the divide-by-1 mode.In the divide-by-4 and divide-by-16 modes, the cutoff frequencies in Table 1 will be lowered by 4 and 16respectively. When the LTC1569-7 is in the divide-by-4and divide-by-16 modes the power is automaticallyAPPLICATIO S I FOR ATIO W UU U Figure 4. Typical Divide Ratio in the Divide-by-4 Mode, T A = 25°CFigure 3. Filter Cutoff vs Temperature,Divide-by-1 Mode, R EXT = 10kFigure 2. Filter Cutoff vs V SUPPLY,Divide-by-1 Mode, T A = 25°CFigure 1V SUPPLY (V)2N O R M A L I Z E D F I L T E R C U T O F F1569-7 F021.041.031.021.011.000.990.980.970.9646810TEMPERATURE (°C)–50N O R M A L I Z E D F I L T E R C U T O F F1569-7 F031.0101.0081.0061.0041.0021.0000.9980.9960.9940.9920.990–250255075100V SUPPLY (V)2D I V I D E R A T I O1569-7 F044.084.044.003.9646810+–f 1569-7 F01LTC1569-778LTC1569-7input signal at IN + should be centered around the DC voltage at IN –. The input can also be AC coupled, as shown in the Typical Applications section.For inverting single-ended filtering, connect IN + to GND or to quiet DC reference voltage. Apply the signal to IN –. The DC gain from IN – to OUT is –1, assuming IN – is referenced to IN + and OUT is reference to GND.Refer to the Typical Performance Characteristics section to estimate the THD for a given input level.Dynamic Input ImpedanceThe unique input sampling structure of the LTC1569-7 has a dynamic input impedance which depends on the con-figuration, i.e., differential or single-ended, and the clock frequency. The equivalent circuit in Figure 8 illustrates the input impedance when the cutoff frequency is 128kHz. For other cutoff frequencies replace the 125k value with 125k • (128kHz/f CUTOFF ).When driven with a single-ended signal into IN – with IN +tied to GND, the input impedance is very high (~10M Ω).When driven with a single-ended signal into IN + with IN –tied to GND, the input impedance is a 125k resistor to GND.When driven with a complementary signal whose com-mon mode voltage is GND, the IN + input appears to have 125k to GND and the IN – input appears to have –125k to GND. To make the effective IN – impedance 125k when driven differentially, place a 62.5k resistor from IN – to GND. For other cutoff frequencies use 62.5k • (128kHz/f CUTOFF ), as shown in the Typical Applications section. The typical variation in dynamic input impedance for a given clock frequency is ±10%.Wideband NoiseThe wideband noise of the filter is the RMS value of the device’s output noise spectral density. The wideband noise data is used to determine the operating signal-to-noise at a given distortion level. The wideband noise is nearly independent of the value of the clock frequency and excludes the clock feedthrough. Most of the wideband noise is concentrated in the filter passband and cannot be removed with post filtering (Table 2). Table 3 lists the typical wideband noise for each supply.APPLICATIO S I FOR ATIO W UU U The oscillator is sensitive to transients on the positive supply. The IC should be soldered to the PC board and the PCB layout should include a 1µF ceramic capacitor be-tween V + (Pin 7) and V – (Pin 4) , as close as possible to the IC to minimize inductance. Avoid parasitic capacitance on R X and avoid routing noisy signals near R X (Pin 6). Use a ground plane connected to V – (Pin 4) for single supply applications. Connect a ground plane to GND (Pin 3) for dual supply applications and connect V – (Pin 4) to a copper trace with low thermal resistance.Input and Output RangeThe input signal range includes the full power supply range. The output voltage range is typically (V – + 50mV)to (V + – 0.8V) when V S = 3V. To maximize the undistorted peak-to-peak signal swing of the filter, the GND (Pin 3)voltage should be set to 2V (1.11V) in single 5V (3V)supply applications.The LTC1569-7 can be driven with a single-ended or differential signal. When driven differentially, the voltage between IN + and IN – (Pin 1 and Pin 2) is filtered with a DC gain of 1. The single-ended output voltage OUT (Pin 8) is referenced to the voltage of the GND (Pin 3). The common mode voltage of IN + and IN – can be any voltage that keeps the input signals within the power supply range.For noninverting single-ended applications, connect IN –to GND or to a quiet DC reference voltage and apply the input signal to IN +. If the input is DC coupled then the DC gain from IN + to OUT will be 1. This is true given IN + and OUT are referenced to the same voltage, i.e., GND, V – or some other DC reference. To achieve the distortion levels shown in the Typical Performance Characteristics theFigure 8OUTLTC1569-7910LTC1569-7Single 3V Operation, AC Coupled Input,128kHz Cutoff Frequencyf CUTOFF =n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V +128kHz n = 1()10k R EXT()n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V +n = 4R EXTSingle 3V Supply Operation, DC Coupled,32kHz Cutoff FrequencySingle 5V Operation, 300kHz Cutoff Frequency,DC Coupled Differential Inputs with Balanced Input ImpedanceFf CUTOFF ~n = 1, 4, 16 FOR PIN 5 ATGROUND, OPEN, V +128kHz n = 1()10k 4.1k()TYPICAL APPLICATIO SUSingle 3V, AC Coupled Input,128kHz Cutoff FrequencyFREQUENCY (Hz)G A I N (d B )GROUP DELAY 1569-7 TA02a0–10–20–30–40–50–60–70–80–90µs µsµsevery clock period. Therefore, the sampling frequency is twice the clock frequency and 64 times the filter cutoff frequency. Input signals with frequencies near 2 • f CLK ± f CUTOFF will be aliased to the passband of the filter and appear at the output unattenuated.Power Supply CurrentThe power supply current depends on the operating mode.When the LTC1569-7 is in the divide-by-1 mode, or whenclocked externally, the supply current is reduced by 50%for supply voltages below 4V. For the divide-by-4 and divide-by-16 modes, the supply current is reduced by 60% relative to the current when clocked externally,independent of the power supply voltage. Power supply current versus cutoff frequency for various operating modes is shown in the “Typical Performance Characteris-tics” section.APPLICATIO S I FOR ATIO WUU ULTC1569-711 Information furnished by Linear Technology Corporation is believed to be accurate and reliable.However, no responsibility is assumed for its use. Linear Technology Corporation makes no represen-tation that the interconnection of its circuits as described herein will not infringe on existing patent rights.12LTC1569-7PART NUMBER DESCRIPTIONCOMMENTSLTC1064-3Linear Phase, Bessel 8th Order Filter f CLK /f CUTOFF = 75/1 or 150/1, Very Low Noise LTC1064-7Linear Phase, 8th Order Lowpass Filter f CLK /f CUTOFF = 50/1 or 100/1, f CUTOFF(MAX) = 100kHzLTC1068-x Universal, 8th Order Filterf CLK /f CUTOFF = 25/1, 50/1, 100/1 or 200/1, f CUTOFF(MAX) = 200kHz LTC1069-7Linear Phase, 8th Order Lowpass Filter f CLK /f CUTOFF = 25/1, f CUTOFF(MAX) = 200kHz, SO-8LTC1164-7Low Power, Linear Phase Lowpass Filter f CLK /f CUTOFF = 50/1 or 100/1, I S = 2.5mA, V S = 5V LTC1264-7Linear Phase, 8th Order Lowpass Filter f CLK /f CUTOFF = 25/1 or 50/1, f CUTOFF(MAX) = 200kHz LTC1562/LTC1562-2Universal, 8th Order Active RC Filterf CUTOFF(MAX) = 150kHz (LTC1562)f CUTOFF(MAX) = 300kHz (LTC1562-2)© LINEAR TECHNOLOGY CORPORA TION 1998sn15697 15697fs LT/TP 0300 4K • PRINTED IN THE USALinear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 q FAX: (408) 434-0507 q RELATED PARTSTYPICAL APPLICATIOSUµF1569-7 TA09µF1569-7 TA10D D Pulse Shaping Circuit for Single 3V Operation, 300kbps2 level data, 150kHz Cutoff FilterPulse Shaping Circuit for Single 3V Operation, 400kbps(200ksps) 4 Level Data, 128kHz Cutoff Filter1569-7 TA070.25V /D I V1µs/DIV1569-7 TA080.3V /D I V1µs/DIV2-Level, 300kbps Eye Diagram4-Level, 400kbps (200ksps)Eye DiagramLTC1569CS8-7#PBF LTC1569IS8-7#PBF LTC1569CS8-6#PBF.。

BOSCH LTC8500系列Allegiant 矩阵 控制系统-模块化 说明书

LTC 8500 系列 Allegiant 视频切换台/控制系统同时结合了切换和计算机技术,可为安防用户提供强大的性能和独特的系统功能。

凭借全面的矩阵切换能力,这些系统能够按任意顺序(无论是手动调序还是独立的自动切换顺序)将任何摄像机所拍摄的视频显示在任意一台监视器上。

LTC 8500 系列采用通用的模块化结构,可以容纳多达 64 路摄像机输入、8 路监视器输出、8 个键盘、128 个报警点、一个计算机接口以及一个日志打印机端口。

基本功能排序功能这些系统通过编程可设置多达 60 种顺序。

这些顺序相互独立,能够正向或反向运行。

任何一种顺序均可利用 SalvoSwitching (组同步切换)功能,该功能允许用户选择任意数目的系统监视器作为一组进行切换。

使用可选的 LTC 8559/00 主控软件包或LTC 8850/00 GUI Allegiant Server ,系统可以根据时间和工作日来自动激活和停止这些顺序。

摄像机控制现场接收器/驱动器可使操作员控制摇摄、俯仰、变焦、多个预定位置、四个辅助触点、自动摇摄和随机扫描。

完整的本地测试功能也是一项标准特性。

此外,LTC 8500 系列还支持 AutoDome 系列球型摄像机的变速操作和完整编程功能。

Bilinx ® 功能当与 LTC 8016 Allegiant Bilinx 数据接口装置组合使用时,这些切换台/控制器还支持通过 Bilinx 通讯功能进行操作。

借助Bilinx ,可用嵌入博世 Dinion 和 AutoDome ® CCTV 摄像机视频信号的双向通信协议来实现云台控制。

此外,Bilinx 可以使用标准视频电缆传输来自摄像机的报警和状态消息,因此无需专用数据传输电缆即可提供优异的性能。

宏功能LTC 8500 系统提供了强大的宏功能。

用户可以通过 Allegiant 系统键盘、系统定时事件功能、报警激活操作以及通过 LTC 8850/00 GUI 软件中的特殊功能图标来启动宏。

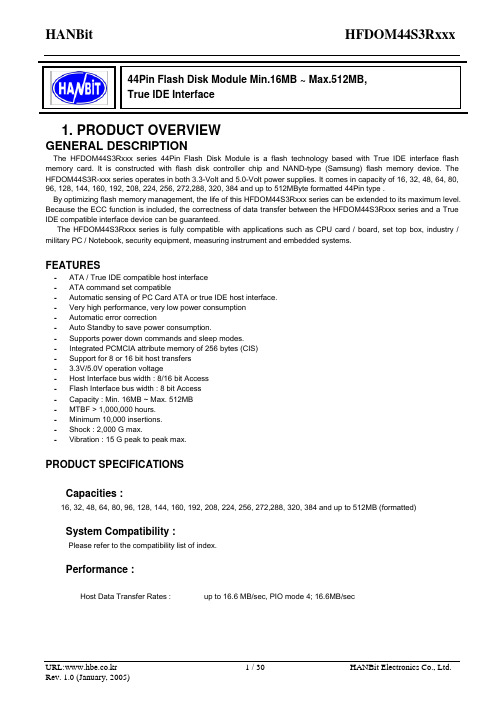

DOM44S3R288资料