第2章 TMS320C54x的硬件结构18

合集下载

第2讲 TMS320C54x的硬件结构

第3章 TMS320C54x的硬件结构

3.1 TMS320C54x的内部结构和主要特性

3.1.2 TMS320C54x的主要特性

2.存储器 16位192K字的可寻址存储空间(64K字的程序存储空间、 64K字的数据存储空间和64K字的I/O空间),此外, C549、VC5402、VC5409、VC5410和VC5416等带有扩展 程序存储器,程序存储空间最大可扩展至8M字。 片内ROM,可配置为程序存储器和数据存储器。

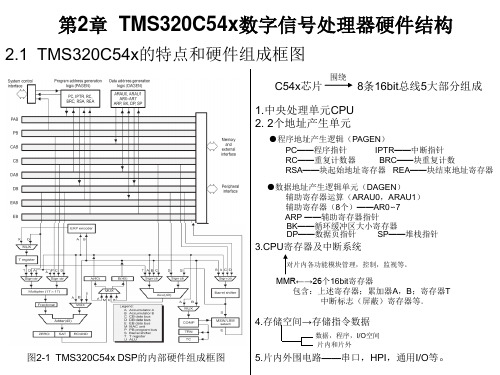

TMS320C54x(简称C54x)系列DSP是TI公司推出的低功 耗、高性能的16位定点数字信号处理器,具有很好的操作 灵活性和很高的运行速度。由于TMS320C54x使用CPU的 并行运行、特殊硬件逻辑、特定的指令系统和多总线技术 等来提高运算速度,并使用高级的IC硬件设计技术来提高 处理器工作速度及降低功耗,使其具有功耗小、高度并行 等优点,可以满足众多领域实时处理的要求。 本章详细介绍TMS320C54x的硬件结构,主要包括总线结 构、中央处理单元、存储器、片内外设、复位电路、中断 和流水线、引脚功能。

3.1.1 TMS320C54x的内部结构

TMS320C54x内部结构基本上可以分为3大部分:

CPU:包括算术逻辑运算单元、乘法器、累加器、移位寄存 器、各种专用用途的寄存器、地址生成器及内部总线。 片内存储器系统:包括片内的程序ROM、片内单访问的数据 RAM和双访问的数据RAM、外部存储器接口。 片内外设与专用硬件电路:包括片内定时器、各种类型的串 口、主机接口、片内锁相环(PLL)时钟发生器及各种控制 电路。 此外,在DSP处理器中还包含有仿真功能及其IEEE 1149.1标 6 准接口(JTAG),用于处理器开发应用时的仿真。

第2章__TMS320C54x的硬件结构

DROM=1 内部ROM FF00H DROM=0 外部存储器 DROM=0 外部存储器

FFFFH

DROM=1 保留 DROM=0 外部存储器 FFFFH

DROM控制的 数据存储空间

DROM=1

保留

MP/MC=0 微计算机模式

MP/MC=1 微处理器模式

第2 章

TMS320C54x的硬件结构

2.6 ’C54x的片内外设电路 ’C54x器件除了提供哈佛结构的总线、功能强大 的CPU以及大容量的存储空间外,还提供了必要的片 内外部设备。 不同型号的’C54x芯片,所配置的片内外设有所 不同,这些片内外设主要包括: ① ② ③ ④ 通用I/O引脚 定时器 时钟发生器 主机接口HPI ⑤ 串行通信接口 ⑥ 软件可编程等待 状态发生器 ⑦ 可编程分区转换逻辑

来自A T ’C54x 的乘法 累加单元 MAC 是由乘法器、加法器、 A D D C A P T X MUX Y MUX 符号控制、小数控制、零检测器、舍入器、饱和逻辑 符号控制 和暂存器几部分组成。 符号控制 0

来自B

XM YM MAC单元具有强大的乘法 -累加运算功能,可在一 乘法器(17 17) A B

CB和DB用来传送从数据存储器读出的数据;

EB用来传送写入存储器的数据。

3.地址总线PAB、CAB、DAB和EAB 用来提供执行指令所需的地址。

第2 章

TMS320C54x的硬件结构

’C54x读/写操作占用总线情况

读/写方式

PAB

地址总线

CAB DAB EAB

程序总线

PB

数据总线

CB DB EB

CPU是DSP器件的核心部件,它的性能直接关系

到DSP器件的性能。

第二章_TMS320C54x的硬件结构

0000H — 001FH :存储器映射CPU寄存器 0020H — 005FH :存储器映射外围电路寄存器 0060 H — 007 FH:暂存寄存器;

☉为了提高处理器的性能,片内RAM也细分为若干块。 分块以后,用户可以在同一周期内从同一DARAM中取出两

个操作数,将数据写入另一块DARAM中。--p41

2.3.3 处理单元

(1)算术逻辑单元(ALU)

功能:① C54X使用40bit的ALU和2个40bit累加器 (A、B)完成二进制补码的算术运算: ② ALU可完成布尔运算; ③ 同时完成两个16bit运算

(2)累加器

功能:存放参加运算的数据或运算结果 组成:三个部分 (保护位作用:防止溢出)

☉片内高2 K字ROM中的内容是由TI公司定义的,这

2K字程序空间(F800h~FFFFh)中包含的内容: 自举加载程序 (从串行口、外部存储器、I/O接口自举加载) 256字A律压扩表 256字µ 律压扩表 256字正弦函数值查找表 中断向量表

☉MP/MC硬件复位时,CPU从FF80H单元开始执行。

发出的地址处在片内存储器地址范围以外,处理器就能自

动地对外部寻址。

(1)程序存储器---片内程序存储器

☉片内存储器是否作为程序存储器,取决 于软件对PMST的状态位 MP/MC和OVLY的 编程。

☉TMS320C54X片内ROM容量范围2K~ 48K字;

☉ 为了增强处理器的性能,对片内ROM 再细分为若干块,这样就可以在片内ROM的 一个块内取指的同时,又在别的块中读取数 据。--p37

行指令所需的地址

2.3 中央处理单元(CPU)

C54X的CPU由运算部件、控制部件和各种寄存器组成。

☉为了提高处理器的性能,片内RAM也细分为若干块。 分块以后,用户可以在同一周期内从同一DARAM中取出两

个操作数,将数据写入另一块DARAM中。--p41

2.3.3 处理单元

(1)算术逻辑单元(ALU)

功能:① C54X使用40bit的ALU和2个40bit累加器 (A、B)完成二进制补码的算术运算: ② ALU可完成布尔运算; ③ 同时完成两个16bit运算

(2)累加器

功能:存放参加运算的数据或运算结果 组成:三个部分 (保护位作用:防止溢出)

☉片内高2 K字ROM中的内容是由TI公司定义的,这

2K字程序空间(F800h~FFFFh)中包含的内容: 自举加载程序 (从串行口、外部存储器、I/O接口自举加载) 256字A律压扩表 256字µ 律压扩表 256字正弦函数值查找表 中断向量表

☉MP/MC硬件复位时,CPU从FF80H单元开始执行。

发出的地址处在片内存储器地址范围以外,处理器就能自

动地对外部寻址。

(1)程序存储器---片内程序存储器

☉片内存储器是否作为程序存储器,取决 于软件对PMST的状态位 MP/MC和OVLY的 编程。

☉TMS320C54X片内ROM容量范围2K~ 48K字;

☉ 为了增强处理器的性能,对片内ROM 再细分为若干块,这样就可以在片内ROM的 一个块内取指的同时,又在别的块中读取数 据。--p37

行指令所需的地址

2.3 中央处理单元(CPU)

C54X的CPU由运算部件、控制部件和各种寄存器组成。

第2章TMS320C54x的硬件结构

测试位Tc ALU CSSU

写选择 写选择 MSW/LSW MSW/LSW

EB15~EB0

24

第2章 TMS320C54x的硬件结构 2.桶形移位寄存器的输入 ① 取自DB数据总线的16位

DB15~DB0 A B MUX 符号控制SC 测试位Tc ALU CSSU 写选择 MSW/LSW EB15~EB0 SXM CB15~CB0

DB15~DB0 A B MUX 符号控制 符号控制SC SC 移位寄存器 移位寄存器 (-16~31) (-16~31) SXM T ASM(4~0) 指令寄存器 立即数 -16~15 0~15 CB15~CB0

用于对输入数据进 行符号位扩展。

③ 移位寄存器 用来对输入的数据 进行定标和移位。 ④ 写选择电路 用来选择最高有效 字和最低有效字。

P

X MUX

符号控制 XM

Y MUX

符号控制 YM A B MUX YA 40位加法器 OVM

来自B

0

乘法器(17 17) 取整 XA

FRCT

OVA/OVB 零检测 舍入器 饱和逻辑 ZA/ZB 至A/B 27

MAC单元具有强大的乘法-累加运算功能,可在

一个流水线周期内完成1次乘法运算和1次加法运算。

● 配有两个地址生成器,包括8个辅助寄存器和 2个辅助寄存器算术运算单元(ARAU)。

10

2.存储器

● 可访问的最大存储空间为192K×16位,即64K 字的程序存储器、64K字的数据存储器以及64K字的 I/O空间。 ● 片内ROM,可配置为程序存储器和数据存储器。 ● 片内RAM有两种类型,即双寻址RAM(DARAM) 和单寻址RAM(SARAM)。

STH STL A,-8 8, 8, TT

写选择 写选择 MSW/LSW MSW/LSW

EB15~EB0

24

第2章 TMS320C54x的硬件结构 2.桶形移位寄存器的输入 ① 取自DB数据总线的16位

DB15~DB0 A B MUX 符号控制SC 测试位Tc ALU CSSU 写选择 MSW/LSW EB15~EB0 SXM CB15~CB0

DB15~DB0 A B MUX 符号控制 符号控制SC SC 移位寄存器 移位寄存器 (-16~31) (-16~31) SXM T ASM(4~0) 指令寄存器 立即数 -16~15 0~15 CB15~CB0

用于对输入数据进 行符号位扩展。

③ 移位寄存器 用来对输入的数据 进行定标和移位。 ④ 写选择电路 用来选择最高有效 字和最低有效字。

P

X MUX

符号控制 XM

Y MUX

符号控制 YM A B MUX YA 40位加法器 OVM

来自B

0

乘法器(17 17) 取整 XA

FRCT

OVA/OVB 零检测 舍入器 饱和逻辑 ZA/ZB 至A/B 27

MAC单元具有强大的乘法-累加运算功能,可在

一个流水线周期内完成1次乘法运算和1次加法运算。

● 配有两个地址生成器,包括8个辅助寄存器和 2个辅助寄存器算术运算单元(ARAU)。

10

2.存储器

● 可访问的最大存储空间为192K×16位,即64K 字的程序存储器、64K字的数据存储器以及64K字的 I/O空间。 ● 片内ROM,可配置为程序存储器和数据存储器。 ● 片内RAM有两种类型,即双寻址RAM(DARAM) 和单寻址RAM(SARAM)。

STH STL A,-8 8, 8, TT

第2章 TMS320C54xx硬件系统

★程序存储器空间包括程序指令和程序

中所需的常数表格;数据存储器空间 用于存储需要程序处理的数据或程序 处理后的结果;I/O空间用于与存储器 映像外围设备相连接,也可以作为附 加的数据存储空间使用。

★ 所 有 的 C54x 片 内 都 有 随 机 存 储 器

(RAM)和只读存储器(ROM)。RAM有 两种:单寻址RAM(SARAM)和双寻址 RAM(DARAM) 。 用 户 可 以 配 置 DARAM和SARAM为数据存储器或程 序/数据存储器。 ★ C54x DSP体系结构的并行特性和片 内RAM的双访问功能,允许在任何一 个给定的指令周期内同时执行4次存储 器操作:1次取指、读2个操作数和写1 个操作数。

(1)程序总线(PB)传送从程序存储器来 的指令代码和立即数。 (2)三组数据总线(CB,DB和EB)连接 各种元器件,如CPU、数据地址产生 逻辑、程序地址产生逻辑,片内外设 和数据存储器。 CB和DB总线传送从数据存储器读出 的操作数。EB总线传送写入到存储器 中的数据。 (3)四组地址总线(PAB,CAB,DAB和 EAB)传送执行指令所需要的地址。

40

40

累加器A

累加器B

17×17位并 行乘法器, 与40位专用 加法器相连, 可用于进行 非流水线的 单周期乘法累加运算。

PB15-PB0

T T D A P A D C

17

Ctr符号位 17 XM 乘法器(17×17)

Ctr符号位 17 YM 0 A Fract/int B 多路开关

FRCT

XA

数据空间 存储器映象 寄存器 暂存器SPRAM 片内DRAM: 16K

3 FFFH 4000H

3 FFFH 4000H EFFFH F000H FEFFH FF00H

第2章TMS320C54x数字信号处理器1

§2.2 TMS320C54x的总线结构(BUS)

4条地址总线(PAB、CAB、DAB、EAB):传送执行指令所需地址。

C54X总线Biblioteka 构(续)图2-1 TMS320C54x DSP的内部硬件组成框图2

§2.3中央处理单元(CPU)

1.40位的算术逻辑单元(ALU);

2.2个40位的累加器(A和B);

乘法器/加法器

乘法器/加法器单元:

乘法器的输入:

XM

T寄存器 DB总线 A的32~16位

YM

DB总线 CB总线 PB总线 A的32~16位

乘法器输出

Adder的XA

Adder(40)

(17*17)

YA

A或B或0

硬件乘法器可以在一个单指令周期中完成17*17bit的二进制补码运算。 例: MPY a1,B ;将a1这个存储器单元中的数与 ;B中的数相乘并将结果放B中 结合DSP的特殊的汇编指令(如MAC),54x可以在一个指令周期内完成乘/累加运算。 例: LD x2,T MAC a2,B ;(a2)*(x2)+BB

Before instruction

After instruction

A

SXM

AR3

0

00 0000 FEDC

0

0300

0300

00 0000 0000

FEDC

FEDC

Data memory 0300h

举例

2.当SXM=1,进行有符号数加载 LD *AR3+,A

Before instruction

输出

ALU的一个输入端 EB总线

功能:

1、在执行ALU操作前预定好一个数据存储器操作 或累加器内容 2、对累加器内容算术或逻辑移位 3、对累加器归一化 4、在将累加器的值存入数据存储器前定标

4条地址总线(PAB、CAB、DAB、EAB):传送执行指令所需地址。

C54X总线Biblioteka 构(续)图2-1 TMS320C54x DSP的内部硬件组成框图2

§2.3中央处理单元(CPU)

1.40位的算术逻辑单元(ALU);

2.2个40位的累加器(A和B);

乘法器/加法器

乘法器/加法器单元:

乘法器的输入:

XM

T寄存器 DB总线 A的32~16位

YM

DB总线 CB总线 PB总线 A的32~16位

乘法器输出

Adder的XA

Adder(40)

(17*17)

YA

A或B或0

硬件乘法器可以在一个单指令周期中完成17*17bit的二进制补码运算。 例: MPY a1,B ;将a1这个存储器单元中的数与 ;B中的数相乘并将结果放B中 结合DSP的特殊的汇编指令(如MAC),54x可以在一个指令周期内完成乘/累加运算。 例: LD x2,T MAC a2,B ;(a2)*(x2)+BB

Before instruction

After instruction

A

SXM

AR3

0

00 0000 FEDC

0

0300

0300

00 0000 0000

FEDC

FEDC

Data memory 0300h

举例

2.当SXM=1,进行有符号数加载 LD *AR3+,A

Before instruction

输出

ALU的一个输入端 EB总线

功能:

1、在执行ALU操作前预定好一个数据存储器操作 或累加器内容 2、对累加器内容算术或逻辑移位 3、对累加器归一化 4、在将累加器的值存入数据存储器前定标

第2章 TMS320C54x数字信号处理器硬件结构汇总

对片内各功能模块管理,控制,监视等。

MMR←→26个16bit寄存器 包含:上述寄存器;累加器A,B;寄存器T 中断标志(屏蔽)寄存器等。

4.存储空间→存储指令数据

数据,程序,I/O空间 片内和片外

5.片内外围电路——串口,HPI,通用I/O等。

2.2 TMS320C54x的总线结构

●地址总线 传送

12

11

10

TC

C

OVA

13

12

11

10

XF

HM

INT

0

M

9 OVB

9

8

7

OV

SXM

C16

M

▲符号扩展位SXM﹕ 清“0”——高位添“0” 置“1”——符号扩展

例:来自DB的16 bit操作数 扩展

40bit ALU输入

▲双字/双精度方式位C16﹕ 置“1”——ALU双精度(32bit)运算 置“0”——ALU双16位运算

10

9

8

7

6

5

4~0

XF

HM

INTM

0

OVM SXM

C16

FRCT

CMP

ASM

T

△小数方式位FRCT 置“1”——乘法结果左移1位(消除多余符号位)

△溢出标志位(OVA/OVB) 发生溢出—— OVA/OVB置“1”

△溢出方式位OVM﹕ 置“0”——ALU运算结果

累加器(A/B)

置“1”

正向溢出,00 7FFF FFFFH 负向溢出,FF 8000 0000H

累加器(A/B)——乘累加运算 “0”——乘法器功能

输出——零检测器,舍入器,溢出饱和逻辑—累加器(A/B)

TMS320C54x硬件系统结构

§2.3 存储器

总存储空间 (192KW)

程序存储空间(64KW) 数据存储空间(64KW) I/O存储空间(64KW)

5、比较、选择和存储单元

如图所示,比较电路COMP将累加器的高16 位与低16位进行比较,比较的结果分别送 入状态转移寄存器TRN和状态比较寄存器 st0的TC位,同时,比较的结果也送入选择 器,选择较大的数,并通过指令执行总线 EB存于指令的存储单元中。

6、指数编码器

指数编码器是个专用硬件,可以求得累加 器中数的指数值,并以2的补码形式存放到 T寄存器中。 累加器的指数值=冗余符号位-8

地址 EAB:传送写数据在数据存储器的目的地址 总之,是传送执行指令所需的地址

以上8条总线都是片内总线,各条总 线访问应用见下表:

片内外设怎么连接到片内的CPU?

C54x还提供了一条在片双向总线(地址、 数据),这条总线把片内的外设通过总线 交换器连到片内总线DB和EB再连接到CPU。 这条总线的读写操作需要更多的机器周期。

8条16位总线:4条地址总线、4条数据总 线

数据总线:

PB:专门用来传送取自程序存储器中的指 令代码或立即数,系数表,一般称为程序 总线

CB、DB:用来传送读自数据存储器中的操 作数

EB:用来传送写到数据存储器中的数据

地址总线:

PAB:传送指令代码所在的地址 CAB、DAB:传送读自数据存储器操作数的

§2.2 中央处理单元(CPU)

CPU的基本组成: 40位算术逻辑运算单元(ALU) 2个40位累加寄存器(ACCA和ACCB) 移位一16~30位的桶形移位寄存器 17×17位乘法器 比较、选择和存储单元(CSSU) 指数编码器 CPU控制和状态寄存器

1、算术逻辑运算单元

第2章 TMS320C54x硬件结构及原理

EXP

ST NORM

A

T,EXPONET A

;(冗余符号位-8)-T寄存器

;指数值保存到数据存储器中 ;累加器值按T中值移位(归一化)

六、比较选择和存储单元(CSSU)

七、CPU的状态和控制寄存器

ST0:

15~13 ARP 12 TC 11 C 10 OVA 9 OVB 8~0 DP

ST1:

15 BRAF 14 CPL 13 XF 12 HM 11 INTM 10 0 9 OVM 8 SXM 7 C16 6 5 4~0 ASM FRCT CMPT

外部 片内ROM 16K 保留 中断字 (片内ROM) MP/MC\=0 OVLY=1

外部 FF7F FF80 FFFF

中断字 (外部) MP/MC\=1 OVLY=0

中断字 (外部) MP/MC\=1 OVLY=1

TMS320C5416程序存储器(第0~127页)结构图

010000h 外部 017FFFh 018000h 027FFFh 028000h 020000h 外部 037FFFh 038000h 030000h 外部 047FFFh 048000h 外部 04FFFFh 第4页 XPC=4 7FFFFFh 第127页 XPC=127 040000h 外部 ... 7F7FFFh 7F8000h 外部 7F0000h 外部

第2章 TMS320C54x的硬件结构及原理

2.1 芯片内部结构及特点 2.2 TMS320C54x的内部总线结构 2.3 TMS320C54x的CPU结构

2.4 TMS320C54x的存储器结构

2.5 复位操作及省电方式

2.6 中断系统

2.7 流水线 2.8 引脚及其功能

2.1 芯片内部结构ARAM只能映射到数据空间

ST NORM

A

T,EXPONET A

;(冗余符号位-8)-T寄存器

;指数值保存到数据存储器中 ;累加器值按T中值移位(归一化)

六、比较选择和存储单元(CSSU)

七、CPU的状态和控制寄存器

ST0:

15~13 ARP 12 TC 11 C 10 OVA 9 OVB 8~0 DP

ST1:

15 BRAF 14 CPL 13 XF 12 HM 11 INTM 10 0 9 OVM 8 SXM 7 C16 6 5 4~0 ASM FRCT CMPT

外部 片内ROM 16K 保留 中断字 (片内ROM) MP/MC\=0 OVLY=1

外部 FF7F FF80 FFFF

中断字 (外部) MP/MC\=1 OVLY=0

中断字 (外部) MP/MC\=1 OVLY=1

TMS320C5416程序存储器(第0~127页)结构图

010000h 外部 017FFFh 018000h 027FFFh 028000h 020000h 外部 037FFFh 038000h 030000h 外部 047FFFh 048000h 外部 04FFFFh 第4页 XPC=4 7FFFFFh 第127页 XPC=127 040000h 外部 ... 7F7FFFh 7F8000h 外部 7F0000h 外部

第2章 TMS320C54x的硬件结构及原理

2.1 芯片内部结构及特点 2.2 TMS320C54x的内部总线结构 2.3 TMS320C54x的CPU结构

2.4 TMS320C54x的存储器结构

2.5 复位操作及省电方式

2.6 中断系统

2.7 流水线 2.8 引脚及其功能

2.1 芯片内部结构ARAM只能映射到数据空间

第2章TMS320C54x硬件结构共59页

算术逻 辑运算Βιβλιοθήκη 桶形 移位器中央处理器

比较器

2.2 TMS320C54x的总线结构

TMS320C54x DSP采用先进的哈佛结构并具有八 组总线,其独立的程序总线和数据总线允许同时 读取指令和操作数,实现高度的并行操作。

采用各自分开的数据总线分别用于读数据和写数 据,允许CPU在同一个机器周期内进行两次读操 作数和一次写操作数。独立的程序总线和数据总 线允许CPU同时访问程序指令和数据。

返回首页

1.总线数目与作用

1条程序总线(PB): 传送取自程序存储器的指令代码和立即操作数

3条数据总线(CB、DB和EB): 将内部各单元连接在一起

4条地址总线(PAB、CAB、DAB和EAB): 传送执行指令所需的地址

图2-1 TMS320C54x DSP的内部硬件组成框图1

返回本节

2. 各种方式所用到的总线

10 10 10 10 10

封装形式

引脚

类型

100 100 128/144 100 128 128 100 100 144 144 144 144 144 144 144 144

TQPF TQPF TQPF TQPF TQPF TQPF TQPF TQPF BGA/TQPF TQPF/BGA TQPF/BGA TQPF/BGA TQPF/BGA TQPF/BGA TQPF/BGA TQPF/BGA

程 序 空 间 :页 0

0000H

007FH 0 0 8 0H

3 FFFH 4000H

保 留 ( O V L Y= 1) 外 部 ( O V L Y= 0 )

片 内DRAM: 16K

( O V L Y= 1) 外 部 ( O V L Y= 0 )

DSP-TMS320C54X的硬件结构-课件

2.1.2 C54X主要特性和外部引脚

⑸ 串行口引脚 C5402器件有两个McBSP串行口,共有12个外部引脚。

2.1.2 C54X主要特性和外部引脚

⑹ 主机接口HPI引脚 C5402的HPI接口是一个8位并行口,用来与主设备或 主处理器接口,实现DSP与主设备或主处理器间的通信。 :8位双向并行数据线; :片选信号,作为HPI的使能端; :地址选通信号; 、 :数据选通信号,由主机控制HPI数据传输; HBIL:字节识别信号,用来判断主机送来的数据是第1 字节还是第2字节。

2.2.1 算术逻辑运算单元ALU

② 若OVM=1,则对ALU的运行结果进行调整。 ■ 当正向溢出时,将32位最大正数00 7FFFFFFFH 装入累加器; ■ 当负向溢出时,将32位最小负数FF 80000000H 装入累加器。 ③状态寄存器ST0中与目标累加器相关的溢出标志OVA或 OVB被置1。 3.进位位C ALU有一个与运算结果有关的进位位C,位于ST0的11位。 进位位C受大多数ALU操作指令的影响,包括算术操作、循 环操作和移位操作。

2.2.1 算术逻辑运算单元ALU

(4) ALU的输出 ALU的输出为40位运算结果,通常被送至累加器A或B。 2.溢出处理 ALU的饱和逻辑可以对运算结果进行溢出处理。当发生溢出 时,将运算结果调整为最大正数(正向溢出)或最小负数 (负向溢出)。 当运算结果发生溢出时: ① 若OVM=0,则对ALU的运算结果不作任何调整,直接送入 累加器;

2.1.3 C54X的内部总线结构

2.2 C54X的中央处理器CPU

CPU是DSP器件的核心部件,它的性能直接关系到DSP器件的性 能。C54X的CPU采用了流水线指令执行结构和相应的并行结构设 计,使其能在一个指令周期内,高速地完成多项算术运算。 CPU包括下列基本部件: ① 40位算术逻辑运算单元ALU; ② 2个40位的累加器A和B; ③ 支持-16~31位移位范围的桶形移位寄存器; ④ 能完成乘法-加法运算的乘法累加器MAC; ⑤ 16位暂存寄存器T;

TMS320C54X的硬件结构

经MSW/LSW选择器输出至EB

总线

功能: 运算前数据定标 A或B进行算术或逻辑移位

A或B归一化处理

A或B—>EB之前定标

移位值三种情况(全部用二进制补

码表示):

立即数(-16—15)

ST1的ASM(5位,-16—15)

TS(6位,-16—31)

例2.4.2:

2.4.4 乘累加单元

SP(CPL=1)或DP(CPL=0)

XF:控制XF通用外部I/O引脚输出状态,

可对XF进行复位和置位

INTM:置1,关闭所有可屏蔽中断 OVM:累加器是否溢出保护,置1(要

保护)。

SXM:符号位扩展方式控制位,控制进

行无符号数运算还是带符号数运算。

C16:双精度/双16位运算方式,

举例

B, A 若A=FF FF8F F302H,

举例:NORM

B =21 0A0A 0A0AH,T= FFF9H

思考:执行后A、B及T的值?

A=00

4214 1414H B =21 0A0A 0A0AH T= FFF9H

2.4.3 40位桶形移位器

图2.4.3

输入: 输出:

ALU

2.4.7 CPU状态和控制寄存器

‘C54x有三个16位的状态和控制寄

存器

状态寄存器ST0 状态寄存器ST1 处理器工作方式状态寄存器PMST

ST0、ST1中包含各种工作条件和

工作方式的状态

PMST中包含存储器的设置状态和

其他控制信息

CPU状态和控制寄存器

ST0 ST1

PMST

数据空间:64K I/O空间:64K

片内、片外程序空间统一编址! 片内、片外数据空间统一编址!

总线

功能: 运算前数据定标 A或B进行算术或逻辑移位

A或B归一化处理

A或B—>EB之前定标

移位值三种情况(全部用二进制补

码表示):

立即数(-16—15)

ST1的ASM(5位,-16—15)

TS(6位,-16—31)

例2.4.2:

2.4.4 乘累加单元

SP(CPL=1)或DP(CPL=0)

XF:控制XF通用外部I/O引脚输出状态,

可对XF进行复位和置位

INTM:置1,关闭所有可屏蔽中断 OVM:累加器是否溢出保护,置1(要

保护)。

SXM:符号位扩展方式控制位,控制进

行无符号数运算还是带符号数运算。

C16:双精度/双16位运算方式,

举例

B, A 若A=FF FF8F F302H,

举例:NORM

B =21 0A0A 0A0AH,T= FFF9H

思考:执行后A、B及T的值?

A=00

4214 1414H B =21 0A0A 0A0AH T= FFF9H

2.4.3 40位桶形移位器

图2.4.3

输入: 输出:

ALU

2.4.7 CPU状态和控制寄存器

‘C54x有三个16位的状态和控制寄

存器

状态寄存器ST0 状态寄存器ST1 处理器工作方式状态寄存器PMST

ST0、ST1中包含各种工作条件和

工作方式的状态

PMST中包含存储器的设置状态和

其他控制信息

CPU状态和控制寄存器

ST0 ST1

PMST

数据空间:64K I/O空间:64K

片内、片外程序空间统一编址! 片内、片外数据空间统一编址!

第2章 TMS320C54x的硬件结构及原理_201109014

②若输入的16位操作数装在ALU的16~31位时,则

当SXM=0时,39~32位和15~0位用0填充;

当SXM=1时,39~32位扩展为符号位,15~0位置0。 (2) ALU的输出

ALU的输出为40位运算结果,通常被送至累加器A或B。

第2章 TMS320C54x的硬件结构及原理

(3) 与算术逻辑运算单元ALU有关的标志位、控制位 反映ALU当前运算结果状态的有4个标志位(ST0内): 进位位C——ST0(D11) 测试位TC——ST0(D12) 溢出标志位OVA——ST0(D10) 溢出标志位OVB ——ST0(D9)

第2章 TMS320C54x的硬件结构及原理 ALU的功能框图

CB15~CB0

16

C B

T A

DB15~DB0

16

D S

40

40

SXM

MUX 符号ctr Y

MUX 符号ctr X

桶形移位 器输出

SXM OVM C16 C OVA/OVB ZA/ZB TC

A

B

40

MUX

A B M U

40

ALU 40

第2章 TMS320C54x的硬件结构及原理

2.1 芯片内部结构及特点 ⑥灵活寻址方式与适于信号处理的指令系统 各种操作类型的指令 硬件重复机制 位倒序寻址方式 循环寻址方式 ⑦ 低功耗工作

节电模式─IDLEl、IDLE2和IDLE3 1.8V内核供电(VC5402)和3.3VI/O口 供电(参照P328-P333设计电源电路)

• (3)电源、时钟与封装

TMS320VC5402芯片的结构及技术性能

型号 频率 MHz 100 MIPS 指令周期 (ns) 寻址空间 程序 数据 (16位) (16位) 64K/8M 64K DMA 通道数 6 Chan Int 片内存储器 RAM ROM (16位) (16位) 16K 4K

第2章 TMS320C54x的硬件结构

6

DSP原理及应用

第2章 TMS320C54x的硬件结构

2. ’C54x的内部结构 TMS320C54x的硬件结构图

系统 控制 接口 系统控制 PAGEN 程序地址生成器 DAGEN 数据地址生成器 特殊功能 寄存器 程序存储器 数据存储器 串行口 并行口 定时器 计数器 中断 乘法 累加器 算术/逻辑 运算单元 比较器 桶形 移位器 外部 设备 接口 外部 存储器 接口

线组成,可在一个指令周期内产生两个数据存储地

址,实现流水线并行数据处理。

2015年6月26日 DSP原理及应用 8

第2章 TMS320C54x的硬件结构

3. 各部分的功能

③ 特殊功能寄存器

共有26个特殊功能寄存器,位于具有特殊功能 的RAM区。主要用来对片内各功能模块进行管理、 控制、监视。 ④ 数据存储器RAM DARAM:在一个指令周期内,可对其进行两次 双寻址数据寄存器DARAM 存取操作,即一次读出和一次写入; 片内数据存储器 SARAM:在一个指令周期内,只能进行一次存 单寻址数据寄存器SARAM 取操作。

脚

2.3 ’C54x的内部总线结构

2.4 ’C54x的中央处理器

2.5 ’C54x的存储空间结构

2.6 ’C54x的片内外设电路

2.7 ’C54x的系统控制

2015年6月26日

2.8 ’C54x的外部总线DSP原理及应用3

第2章 TMS320C54x的硬件结构

2.1 ’C54x的基本结 构

TMS320C54x(简称’C54x)是TI公司为实

第2章 TMS320C54x的硬件结构

2.2.1 ’C54x的主要特性 2.存储器

● 可访问的最大存储空间为192K×16位,即64K 字的程序存储器、64K字的数据存储器以及64K字的 I/O空间。 ● 片内ROM,可配置为程序存储器和数据存储器。 ● 片内RAM有两种类型,即双寻址RAM(DARAM) 和单寻址RAM(SARAM)。

DSP原理及应用

第2章 TMS320C54x的硬件结构

2. ’C54x的内部结构 TMS320C54x的硬件结构图

系统 控制 接口 系统控制 PAGEN 程序地址生成器 DAGEN 数据地址生成器 特殊功能 寄存器 程序存储器 数据存储器 串行口 并行口 定时器 计数器 中断 乘法 累加器 算术/逻辑 运算单元 比较器 桶形 移位器 外部 设备 接口 外部 存储器 接口

线组成,可在一个指令周期内产生两个数据存储地

址,实现流水线并行数据处理。

2015年6月26日 DSP原理及应用 8

第2章 TMS320C54x的硬件结构

3. 各部分的功能

③ 特殊功能寄存器

共有26个特殊功能寄存器,位于具有特殊功能 的RAM区。主要用来对片内各功能模块进行管理、 控制、监视。 ④ 数据存储器RAM DARAM:在一个指令周期内,可对其进行两次 双寻址数据寄存器DARAM 存取操作,即一次读出和一次写入; 片内数据存储器 SARAM:在一个指令周期内,只能进行一次存 单寻址数据寄存器SARAM 取操作。

脚

2.3 ’C54x的内部总线结构

2.4 ’C54x的中央处理器

2.5 ’C54x的存储空间结构

2.6 ’C54x的片内外设电路

2.7 ’C54x的系统控制

2015年6月26日

2.8 ’C54x的外部总线DSP原理及应用3

第2章 TMS320C54x的硬件结构

2.1 ’C54x的基本结 构

TMS320C54x(简称’C54x)是TI公司为实

第2章 TMS320C54x的硬件结构

2.2.1 ’C54x的主要特性 2.存储器

● 可访问的最大存储空间为192K×16位,即64K 字的程序存储器、64K字的数据存储器以及64K字的 I/O空间。 ● 片内ROM,可配置为程序存储器和数据存储器。 ● 片内RAM有两种类型,即双寻址RAM(DARAM) 和单寻址RAM(SARAM)。

TMS320C54x的硬件结构

FLASH: Flash Memory : SmartMedia(SM卡) Compact Flash(CF卡) MultiMediaCard(MMC卡) Secure Digital(SD卡) Memory Stick(记忆棒) XD-Picture Card(XD卡) MICRODRIVE (微硬盘)

Page0 64K

Page1 64K

Page2 64K

…

Page15 64K

… F FFFFH

00 FFFFH

01 FFFFH

02 FFFFH

XPC=0

XPC=1

XPC=2

XPC=15

OVLY=1:片内RAM映射到程序空间。

公共块:32K,所有页享

专用块:32K字、 指定的页号寻址。

XX 0000H

2.4.1 存储空间结构

程序存储器:内部和外部统一编址 数据存储器:内部和外部统一编址 内部RAM:

总是映射到数据存储空间,但也可映 射到程序存储空间

内部ROM:灵活地映射到程序存储空间,也可以部

分地映射到数据存储空间。

存储空间的任何一种存储器都可以驻留在片内或片外

2.4.2 C5402程序存储空间

大小:4K字 MP/MC=0:

ROM被映射到程序空间

地址:F000H~FFFFH F000H~F7FFH:用户专用程序;

在’ C54x系列芯片中,使程序存储空间可扩展到

1M~8M。 ’C5402程序 空间扩展到1M

分页扩展技术的特点:

外部程序地址线:有20或23条,可寻址1M-8M;

程序计数器扩展寄存器XPC:存放页码

6条寻址扩展程序空间的指令:寻址扩展程序空间

第2章 TMS320C54x的硬件结构原理

片内存储器介绍(续)

(2)片内RAM(SARAM,DARAM) SARAM(single access RAM)单操作RAM,

由若干块组成,每个块在一个机器周期只能被访问一 次(读/写),常被安排为数据存储空间,也能被安排为 程序存储空间。 DARAM(double access RAM)双操作RAM,

温度范围: (默认0度~70度) L=0~70 A=-40~85 S=-40~125

工艺:

C=COMS E=COMS+EPROM F=Flash+EPROM LC=低电压(3.3v)+COMS LF=Flash+EPROM(3.3v) VC=COMS(3v)

DSP常见封装形式

DIP(Double In-Line Package)--双列直插式封装。

C54xDSP特点(续)

数据地址发生器(DAG):

❖ 在通用CPU中,数据地址的产生和数据 的处理都由ALU来完成

❖ 在DSP中,设置了专门的数据地址发生 器(实际上是专门的ALU),来产生所 需要的数据地址,节省公共ALU的时间

C54xDSP特点(续)

PLL(phase-locked loop )锁相环 定时器(Timer) 软件可编程等待状态发生器 JTAG(符合IEEE1149.1标准)仿真接口

作电压; 价格便宜,第一款低于5美元的双核DSP; 采用新型生产工艺,芯片体积小。

(3)TMS320C6000系列

(主要包括C62X,C64X,C67X三类)

该系列DSP采用了与上述系列DSP不同的内部 结构设计,使得DSP能够获得极高的运行速度: 指令周期最小为3.3ns,运算能力为2400MIPS。

而ARM处理器负责系统处理及提供外围设备 接口。这样设计的好处是,可选择输入设备较 多,后期升级潜力大。

DSP 第二章 TMS320C54x硬件结构与工作原理—CPU

什么是双16位算术运

算

2013年8月11日 DSP技术与应用基础

输 出 为 40 位 , 被 送 往 累加器A 或B

9

2013年8月11日

DSP技术与应用基础

10

ALU的输入:ALU有两个输入端,X输入端的数据来源于 移位寄存器的输出(32位或16位数据存储器操作数以及累加 器中的数值,经移位寄存器移位后输出)或来自数据总线DB 的数据存储器操作数。 Y输入端的数据来源于累加器A中的数据,或累加器B中 的数据,或来自数据总线CB的数据存储器操作数,或来自T寄 存器中的数据。

2013年8月11日

DSP技术与应用基础

28

要 点

结构 功能 什么是舍入处理 数据流向

2013年8月11日

DSP技术与应用基础

29

要 点

结构 功能 什么是舍入处理 数据流向

输入端 XM来自T寄存 器、累加器A的位 32~16、以及DB总线; 输入端YM来自累加器 A的位32~16、由DB总 线和CB总线以及由PB 总线。 输出加到加法器的输入 端XA,累加器A或B则 是加法器的另一个输入。 最后结果送往目的累加 器A或B。

6 7

ST0 ST1

要 点

1D

PMST

ST0和ST1中包含有各种工作条件和工 作方式的状态;PMST中包含存储器的 设置状态及其它控制信息

2013年8月11日 DSP技术与应用基础

ห้องสมุดไป่ตู้

O页存储器

36

(1)状态寄存器0(ST0)

15~ 13

ARP

12

TC

11

C

10

9

8~ 0

DP

算

2013年8月11日 DSP技术与应用基础

输 出 为 40 位 , 被 送 往 累加器A 或B

9

2013年8月11日

DSP技术与应用基础

10

ALU的输入:ALU有两个输入端,X输入端的数据来源于 移位寄存器的输出(32位或16位数据存储器操作数以及累加 器中的数值,经移位寄存器移位后输出)或来自数据总线DB 的数据存储器操作数。 Y输入端的数据来源于累加器A中的数据,或累加器B中 的数据,或来自数据总线CB的数据存储器操作数,或来自T寄 存器中的数据。

2013年8月11日

DSP技术与应用基础

28

要 点

结构 功能 什么是舍入处理 数据流向

2013年8月11日

DSP技术与应用基础

29

要 点

结构 功能 什么是舍入处理 数据流向

输入端 XM来自T寄存 器、累加器A的位 32~16、以及DB总线; 输入端YM来自累加器 A的位32~16、由DB总 线和CB总线以及由PB 总线。 输出加到加法器的输入 端XA,累加器A或B则 是加法器的另一个输入。 最后结果送往目的累加 器A或B。

6 7

ST0 ST1

要 点

1D

PMST

ST0和ST1中包含有各种工作条件和工 作方式的状态;PMST中包含存储器的 设置状态及其它控制信息

2013年8月11日 DSP技术与应用基础

ห้องสมุดไป่ตู้

O页存储器

36

(1)状态寄存器0(ST0)

15~ 13

ARP

12

TC

11

C

10

9

8~ 0

DP

相关主题

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例如, 桶形移位寄存器和指数译码器可以将累加器中的数值在一个周期内进行归一化处 40位累加器A中的定点数为FF FFFF F001。

理。 ① 先用EXP A指令,求得它的指数为13H,存放在T寄存器中。 ② 然后再执行 NORM A 指令,可在单个周期内将原来的定点数分成尾数 FF 8008 0000和指数13H两个部分。

3

第2章 TMS320C54x的硬件结构

(2) 控制操作数的移位

根据指令中的移位数,控制操作数进行移位操作。移位数用二进制补码表示, 正值时完成左移,负值时完成右移。

移位数的形式: ① 5位立即数,取值范围:-16~15; ② ST1中的ASM位,取值范围:-16~15; ③ 暂存器T中的低6位数值,取值范围:-16~31。(1) 控制操作数的符号位扩展 根据SXM位控制操作数进行符号位的扩展。 若操作数为有符号数,则

当SXM=1时,完成符号位扩展; 当SXM=0时,禁止符号位扩展。

若操作数为无符号数,则不考虑SXM位,不执行符号位的扩展。

如:LDU、ADDS和SUBS指令,操作数为无符号数,不进行符号位扩 展。

这种移位操作能使CPU完成数据的定标、位提取、扩展算术和溢出保护等操作。

4

第2章 TMS320C54x的硬件结构

【例2.4.2】 对累加器A执行不同的移位操作。

ADD A, - 4,B ADD A, NORM A

;A右移4位后加到B中 ASM,B ;A按ASM移位后加到B中 ;按T的数值对A进行归一化

第2章 TMS320C54x的硬件结构

4.桶形移位寄存器的功能

主要用于格式化操作,为输入的数据定标 。 ① 在进行ALU运算之前,对输入数据进行数据定标; ② 对累加器进行算术或逻辑移位; ③ 对累加器进行归一化处理; ④ 在累加器的内容存入数据存储器之前,对存储数 据进行定标。

2

第2章 TMS320C54x的硬件结构