数字设计原理与实践第六章答案

数字设计(Digital Design)习题解答6

119E X E R C I S E S O L U T I O N S SequentialLogic Design Principles77.27.3The latch oscillates if S and R are negated simultaneously. Many simulator programs will exhibit this same behavior when confronted with such input waveforms.S R Q QNS R QQN120DIGITAL CIRCUITS7.57.8Just tie the J and K inputs together and use as the D input. 7.9Excitation and output equations:Excitation/transition table; state/output table:7.15Excitation equations:Excitation/transition table; state table:7.18Excitation and output equations:QNQ Q QTEN J K CLKD1Q1′Q2+=D2Q2′X ⋅=Z Q1Q2′+=ENQ1Q201001011011010100001111010Q1*Q2*ENS1ZA C D 1BC C 0C A B 1DCC1S*D2Q (1Q0)Q1′Q2′⋅()⊕⊕=D1Q2=D0Q1=Q2Q1Q0Q2*Q1*Q0*000100001000010101011001100010101110110111111011S S*A E B A C F D B E C F G G H HDJ0K0EN ==J1K1Q0EN ⋅==MAX EN Q1Q0⋅⋅=EXERCISE SOLUTIONS 121Note that the characteristic equation for a J-K flip-flop is . Thus, we obtain the following transition equations:Transition/output table; state/output table:State diagram:Timing diagram:7.20This can be done algebraically. If all of the input combinations are covered, the logical sum of the expressionson all the transitions leaving a state must be 1. If the sum is not 1, it is 0 for all input combinations that are uncovered. For double-covered input combinations, we look at all possible pairs of transitions leaving a state.The product of a pair of transition equations is 1 for any double-covered input combinations.(a)State D , Y = 0 is uncovered.(b)State A , (X+Z ′) = 0 is uncovered. State B , W = 1 is double-covered; (W+X ) = 0 is uncovered. State C ,(W+X+Y+Z ) = 0 is uncovered; (W ⋅X + W ⋅Y + Z ⋅Y + Z ⋅X ) = 1 is double covered. State D , (X ⋅Y + ⋅X ′⋅Z + W ⋅Z ) = 0is uncovered; (W ⋅X ′⋅Z + W ⋅X ⋅Y ⋅Z ) = 1 is double-covered;Q ∗J Q ′⋅K ′Q ⋅+=Q0∗EN ′Q0⋅EN Q0′⋅+=Q1∗EN ′Q1⋅EN Q0⋅Q1′⋅EN Q0′Q1⋅⋅++=ENQ1Q2010000,001,00101,010,01010,011,01111,000,1Q1*Q2*, MAXENS1A A,0B,0B B,0C,0C C,0D,0DD,0A,1S*, MAXAENEN ENEN ′EN ′EN ′EN ′ENBCDCLK EN Q0Q1MAX122DIGITAL CIRCUITS7.21Table 9–4 on page 804 shows an output-coded state assignment. Here is a corresponding transition list:The excitation equations and circuit diagram follow directly from this transition list.7.25The minimum setup time is the clock period times the duty cycle. That is, the minimum setup time is the timethat the clock is 1.7.27As shown in Section 7.9.1, the excitation equation for the latch of Figure 7–72 is Below, we analyze Figure X7.27 in the same way:The feedback equation isThe feedback equations are the same, and so the circuits have identical steady-state behavior.The circuit in Figure X7.27 is better in two ways. It uses one less gate, and it has one less load on the D input. 7.29The AND gate in the original circuit is replaced with a NAND gate. As a result, the second flip-flop stores theopposite of the value stored in the original circuit; to compensate, swap connections to its Q and QN outputs.SL3Z L2Z L1Z R1Z R2Z R3ZTransition expression S*L3Z *L2Z *L1Z *R1Z *R2Z *R3Z *IDLE 000000(LEFT + RIGHT + HAZ)′IDLE 000000IDLE 000000LEFT ⋅HAZ ′⋅RIGHT ′L1001000IDLE 000000HAZ + LEFT ⋅RIGHT LR3111111IDLE 000000RIGHT ⋅HAZ ′⋅LEFT ′R1000100L1001000HAZ ′L2011000L1001000HAZ LR3111111L2011000HAZ ′L3111000L2011000HAZ LR3111111L31110001IDLE 000000R1000100HAZ ′R2000110R1000100HAZ LR3111111R2000110HAZ ′R3000111R2000110HAZ LR3111111R30001111IDLE 000000LR31111111IDLEY ∗C D ⋅C ′Y ⋅D Y⋅++=D C(C ⋅ D)′((C ⋅ D)′ ⋅ C) + Y ′C ⋅D + (((C ⋅ D)′ ⋅ C) + Y ′)′((C ⋅ D)′ ⋅ C)′QQNY ∗YY ∗C D ⋅C D ⋅()′C ⋅()Y ′+()′+=C D ⋅()C D ⋅()′C ⋅()′Y ⋅+=C D ⋅C D ⋅()(C ′)Y ⋅++=C D ⋅D C ′+()Y ⋅+=C D ⋅D Y ⋅C ′Y⋅++=EXERCISE SOLUTIONS 123The OR gates in the original circuit are also replaced with NAND gates. As a result, each input must be con-nected to a signal of the opposite polarity as before, that is, to the complementary flip-flop output. In the case of connections to the second flip-flop, we swapped outputs twice, so the connections remain the same.The final circuit below uses three 2-input NAND gates.7.45 A transition table corresponding to the state table is shown below:This table leads to the following Karnaugh maps for the excitation logic, assuming a “minimal cost” treatment of unused states.A BQ2Q1Q000011110Z0000010010100100001011011010010001000100110010000110110111100101100001101100100110101101111001011100011011001001Q2*Q1*Q0*D Q Q CLK D QQCLK XZCLK000111100001111000011110A BQ1 Q200011110A B A BA B A BA B A BA B A BABA BA BQ1Q2Q0=0Q1 Q2Q1Q2Q0=1100001111000011110Q1 Q200011110Q1Q2Q0=0Q1 Q2Q1Q2Q0=1000111100001111000011110Q1 Q200011110Q1Q2Q0=0Q1 Q2Q1Q2Q0=1D0D1D21100110011001100001100000000000011000000111111111111000001000010d d d d d d d d d d d d 0000011011101111111A ′0011Q1′⋅ Q2′ ⋅ A Q0Q0′ ⋅ Q1 ⋅ B 01Q0′ ⋅ Q2 ⋅ AQ0′ ⋅ Q1 ⋅ AQ1 ⋅ A ⋅ BQ2 ⋅ A ⋅ B124DIGITAL CIRCUITSThe resulting excitation equations areIgnoring inverters, a circuit realization with the new equations requires one 2-input gate, six 3-input gates, and one 5-input gate. This is more expensive than Figure 7–54, by four gates.7.49The new state assignment yields the followingtransition/excitation table and Karnaugh maps:This yields the following excitation equations:Compared with the results of original state assigment, these equations require two more 3-input AND gates,plus a 6-input OR gate inplace of a 4-input one. However, if we are not restricted to a sum-of-products realiza-tion, using the fact that might make this realization less expensive when discrete gates are used.D0A ′=D1Q1′Q2′⋅A ⋅Q0+=D2Q2A ⋅B ⋅Q0′Q2⋅A ⋅Q0′Q1⋅A ⋅Q1A ⋅B ⋅Q0′Q1⋅B⋅++++=X YQ1Q000011110Z0000011101 1 010******** 11111000100 1010000100Q2*Q1*or D1D20001100001111000011110X YQ1 Q200011110X YQ1Q2D1X YQ1 Q2X Q1Q2D21110101100000101010110101010010111Y Q1 ⋅ Q2′ ⋅ X ′Q1 ⋅ Q2′ ⋅ Y ′Q1′ ⋅ Q2 ⋅ Y Q1′ ⋅ X ⋅ YQ2 ⋅ X ′ ⋅ Y ′Q2 ⋅ X ⋅ YQ2′ ⋅ X ′ ⋅ Y Q2′ ⋅ X ⋅ Y ′Q1 ⋅ X ′ ⋅ Y ′Q1′ ⋅ Q2 ⋅ XD1Q1′Q2X ⋅⋅Q1′Q2Y ⋅⋅Q1′X Y ⋅⋅Q1Q2′X ′⋅⋅Q1Q2′Y ′⋅⋅Q1X ′Y ′⋅⋅+++++=D2Q2X Y ⋅⋅Q2′X Y ′⋅⋅Q2′X ′Y Q2X ′Y ′⋅⋅+⋅⋅++=D2Q2X Y ⊕⊕=EXERCISE SOLUTIONS 1257.57Here is the transition list:The transition/excitation and output equations below follow directly from the transition list.Starting from the IDLE state, the following transitions may be observed:For each input combination, the machine goes to the R1 state, because R1’s encoding is the logical OR of the encodings of the two or three next states that are specified by the ambiguous state diagram.SQ2Q1Q0Transition expressionS*Q2*Q1*Q0*IDLE000(LEFT+RIGHT+HAZ)′IDLE 000IDLE000LEFT L1001IDLE000HAZ LR3100IDLE 000RIGHTR1101L10011L2011L20111L3010L30101IDLE 000R1 1011R2111R2 1111R3110R31101IDLE 000LR311IDLESQ2Q1Q0LEFTRIGHTHAZQ2*Q1*Q0*S*IDLE000101101R1IDLE 000 011101R1IDLE 000 110101R1IDLE11111R1D2Q2∗Q2′Q1′Q0′HAZ ⋅⋅⋅== Q2′Q1′Q0′RIGHT⋅⋅⋅+ Q2Q1′Q0⋅⋅+ Q2Q1Q0⋅⋅+Q2′Q1′Q0′HAZ RIGHT +()⋅⋅⋅Q2Q0⋅+=D1Q1∗Q2′Q1′Q0⋅⋅== Q2′Q1Q0⋅⋅+ Q2Q1′Q0⋅⋅+ Q2Q1Q0⋅⋅+Q0=D0Q0∗Q2′Q1′Q0′LEFT⋅⋅⋅== Q2′Q1′Q0′RIGHT ⋅⋅⋅+ Q2′Q1′Q0⋅⋅+ Q2Q1′Q0⋅⋅+Q2′Q1′Q0′LEFT RIGHT +()⋅⋅⋅Q1′Q0⋅+=126DIGITAL CIRCUITSThe behavior aboveis not so good and is a result of synthesis choices—state encoding and logic synthesis method. If a different state encoding were used for R1, or if a different synthesis method were used (e.g., prod-uct-of-s-terms), then the results could be different. For example, starting with the transition list given earlier,we can obtain the following set of transition equations using the product-of-s-terms method:These equations yield the following transitions:This is obviously different and still not particularly good behavior.7.58Let E(SB), E(SC), and E(SD) be the binary encodings of states SB , SC , and SD respectively. Then, the bit-by-bit logical OR of E(SB) and E(SC). This is true because the synthesis method uses the logical OR of the next values for each state variable and, by extension, the logical OR of the encoded states.SQ2Q1Q0LEFTRIGHTHAZQ2*Q1*Q0*S*IDLE 000 000000IDLE IDLE 000 011100LR3IDLE 000 110001L1IDLE111IDLED2Q2∗Q2Q1Q0LEFT RIGHT HAZ +++++()== Q2Q1Q0LEFT ′+++()⋅ Q2Q1Q0′++()⋅ Q2Q1′Q0′++()⋅ Q2Q1′Q0++()⋅ Q2′Q1′Q0++()⋅ Q2′Q1Q0++()⋅Q2Q1RIGHT HAZ +++()Q2Q1LEFT ′++()Q2Q0′+()Q1′Q0+()Q2′Q0+()⋅⋅⋅⋅=D1Q1∗Q2Q1Q0LEFT RIGHT HAZ +++++()== Q2Q1Q0LEFT ′+++()⋅ Q2Q1Q0HAZ ′+++()⋅ Q2Q1Q0RIGHT ′+++()⋅ Q2Q1′Q0++()⋅ Q2′Q1′Q0++()⋅ Q2′Q1Q0++()⋅Q2Q1Q0++()Q1′Q0+()Q2′Q0+()⋅⋅=D0Q0∗Q2Q1Q0LEFT RIGHT HAZ +++++()== Q2Q1Q0HAZ ′+++()⋅ Q2Q1′Q0′++()⋅ Q2Q1′Q0++()⋅ Q2′Q1′Q0′++()⋅ Q2′Q1′Q0++()⋅ Q2′Q1Q0++()⋅Q2Q0LEFT RIGHT +++()Q2Q0HAZ ′++()Q1′()Q2′Q0+()⋅⋅⋅=E SD ()E SB ()E SC ()+=EXERCISE SOLUTIONS 1277.68As far as I know, I was the first person to propose BUT -flops, and Glenn Trewitt was the first person to analyzethem, in 1982. To analyze, we break the feedback loops as shown in the figure to the right.The excitation and output equations areThe corresponding transition/state table isThe two stable total states are circled. Notice that state 00 is unreachable.When X1 X2 = 00 or 11, the circuit generally goes to stable state 11, with Q1 Q2 = 11. The apparent oscillation between states 01 and 10 when X1 X2 = 11 may not occur in practice, because it contains a critical race that tends to force the circuit into stable state 11.When X1 X2 = 01 or 10, the Q output corresponding to the HIGH input will oscillate, while the other output remains HIGH .Whether this circuit is useful is a matter of opinion.7.71When X =1, the circuit was supposed to “count” through its eight states in Gray-code order. When X =0, itremains in the current state. If this were the case, I suppose it could be used as a 3-bit random number genera-tor. However, I messed up on the logic diagram and the circuit actually does something quite different and completely useless, compared to what I intended when I wrote the problem. Someday I’ll fix this problem.Also, metastability may occur when X is changed from 1 to 0. 7.79Figure X5.59 requires two “hops” for each input change. Figure 7–66 is faster, requiring only one hop for eachinput change. On the other hand, Figure 7–66 cannot be generalized for n >2.7.90Either this exercise is a joke, or a correct answer is much too dangerous to publish. Nevertheless, Earl Levineoffers two possible answers:(Stable output)Was the last answer to this question “yes”?(Oscillating output)Was the last answer to this question “no”?X2X1Q1Q2Y1∗Y2∗Y1Y2Y1X1Y1⋅()X2Y2⋅()′⋅[]′=X1′Y1′X2Y2⋅++=Y2X2Y2⋅()X1Y1⋅()′⋅[]′=X2′Y2′X1Y1⋅++=Q1Y1=Q2Y2=X1X2Y1Y2000111100011111111 0111101011 1111101101 1011110101Y1*Y2*。

数字设计-原理与实践(第四版)课后习题答案

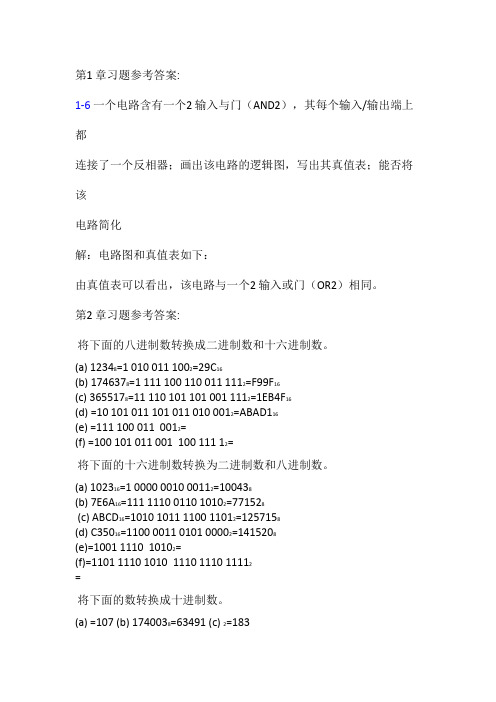

数字设计-原理与实践(第四版)课后习题答案第1 章习题参考答案:1-6 一个电路含有一个2 输入与门(AND2),其每个输入/输出端上都连接了一个反相器;画出该电路的逻辑图,写出其真值表;能否将该电路简化解:电路图和真值表如下:由真值表可以看出,该电路与一个2 输入或门(OR2)相同。

第2 章习题参考答案:将下面的八进制数转换成二进制数和十六进制数。

(a) 12348=1 010 011 1002=29C16(b) 1746378=1 111 100 110 011 1112=F99F16(c) 3655178=11 110 101 101 001 1112=1EB4F16(d) =10 101 011 101 011 010 0012=ABAD116(e) =111 100 011 0012=(f) =100 101 011 001 100 111 12=将下面的十六进制数转换为二进制数和八进制数。

(a) 102316=1 0000 0010 00112=100438(b) 7E6A16=111 1110 0110 10102=771528(c) ABCD16=1010 1011 1100 11012=1257158(d) C35016=1100 0011 0101 00002=1415208(e)=1001 1110 10102=(f)=1101 1110 1010 1110 1110 11112=将下面的数转换成十进制数。

(a) =107 (b) 1740038=63491 (c) 2=183(d) = (e)= (f)F3A516=62373(g) 120103=138 (h) AB3D16=43837 (i) 71568=3694(j) =完成下面的数制转换。

(a) 125= 1 111 1012 (b) 3489= 66418 (c) 209= 11 010 0012(d) 9714= 227628 (e) 132= 10 000 1002 (f) 23851= 5D2B16(g) 727= 104025 (h) 57190=DF6616 (i) 1435=26338(j) 65113=FE5916将下面的二进制数相加,指出所有的进位:(a) S:1001101 C:100100(b) S: 1010001 C: 1011100(c) S: 0 C: 0(d) S: C:利用减法而不是加法重复训练题,指出所有的借位而不是进位:(a) D:011 001 B:110000 (b) D:111 101 B:1110000(c) D: B:00111000 (d) D:1101101 B:写出下面每个十进制数的8 位符号-数值,二进制补码,二进制反码表示。

数字设计原理与实践 第四版 (john F.Wakerly ) 课后答案

3.65 在图 3-32(b)中,有多少电流与功率被浪费了。 解:浪费的电流为流过 4kΩ电阻的电流:

I=(5-0.24)/4=1.19 mA 浪费的功率为上述电流经过两个电阻产生的功率: P = RI2 = 4.2 x (1.19)2 = 5.95 mW

解:由图中可以看到,输出 3.5V 对应的输入为 2.4V,输出 1.5V 对应 的输入为 2.5V; 所以,高态噪声容限为:3.5-2.5=1 V ;低态噪声 容限为:2.4-1.5=0.9 V。

3.26 利用表 3-3 计算 74HC00 的 p 通道和 n 通道的导通电阻。 解:采用极端值计算(对商用芯片,最低电源电压设为 4.75V) 表中所列输出电压与电流关系如图所示:

=157255.5756748 2.5 将下面的数转换成十进制数。

(a) 11010112=107 (b) 1740038=63491 (c) 101101112=183

(d) 67.248=55.3125 (e)10100.11012=20.8125 (f)F3A516=

62373

(g) 120103=138

(h) AB3D16=43837

(i) 71568=3694

(j) 15C.3816=348.21875

2.6 完成下面的数制转换。

(a) 125= 1 111 1012 (b) 3489= 66418 (c) 209= 11 010 0012

(d) 9714= 227628

(e) 132= 10 000 1002 (f) 23851= 5D2B16

(g) 727= 104025

(h) 57190=DF6616 (i) 1435=26338

数字设计原理与实践第四版中文答案

3 8 1 = 21 1 1 0 1 1 0 1 ) c (

701=21101011 )a(

。 数 制 进 十 成 换 转 数 的 面 下 将 5. 2

8

4 7 6 57 5 . 5 52 7 5 1 =

2

1111 0111 0111 1101.1011 0101 0111 1011=6 1110.01101100 0111 1001=61A7.63E9)e(

8

025141=20000 1010 1100 0011=61053C )d( 517521=21011 0011 1101 0101=61DCBA )c(

8

0276 =4x5x6x7x8=N�列排的 5 取中 8 个一是这�态状 5 于对 。 式 形种 8 有 码 编 制 进 二 位 3 � 解 �呢态状 8 者或态状 7 是若 � 式 方 码 编 制 进二 位 3 的 同 不 种 少 多 有 � 器 制 控 的 态 状 5 于 对 3 3 . 2 出 溢 在存 出 溢在 存 出溢在存不 出溢 在 存 不 0000 0001 0 1 1 10 0 0 1 0111 1001 1111 1101 = 1 1 1 1 1 00 0 + 1 0 0 0 0 1 1 0 ) d ( = 1 0 0 0 1 1 00 + 1 0 1 1 1 0 1 0 ) c ( = 1 1 1 1 10 1 1 + 1 1 1 1 1 1 0 1 ) b ( = 1 1 0 1 01 1 1 + 0 0 1 0 1 0 1 1 ) a (

8

3362=5341 )i(

61

6 6 F D =0 9 1 7 5 ) h (

8

5

61

B 2 D 5 = 1 5 8 3 2 ) f ( 2 0 01 00 0 0 1 =2 3 1 ) e(

数字设计原理与实践第四版中文答案

42.E1F=2100 100.011 110 001 111=811.6347 )e(

61

1DABA=2100 010 110 101 110 101 01=81235352 )d(

61

F 4 B E 1 = 2 1 1 1 1 0 0 1 0 1 1 0 1 0 1 1 1 1 = 87 1 5 5 6 3 ) c (

14 66 =9843 ) b(

2

10 1 111 1 =52 1 )a (

。 换 转 制 数的 面 下 成 完 6 . 2

57812.843=6183.C51 )j( 4 9 6 3 = 86 5 1 7 ) i ( 7 3 8 3 4 = 6 1D 3 B A ) h ( 831=301021 )g( 37326 = 615 A 3 F ) f ( 5 2 1 8 . 0 2 =2 1 0 1 1 . 0 0 1 0 1 ) e ( 1 9 4 3 6 = 83 0 0 4 7 1 ) b ( 5213.55=842.76 )d(

') D ⋅ C ⋅ ) B + A (( = Z �解

。 图 辑 逻 的应 对 出 画 V N I , R O � D N A 用 采 � 图 路 电 I A O 的 示 所 � b � 1 1 . 3 X 图对 2 1 . 3

。限容声噪 CD 的态低与态高定确�性特器相反的示所 12.3X 图 对 � V 5 . 3 和 V 5 . 1 为 置 设 别 分值 阈 平 电 高 和 值 阈 平 电 低 出 输 若 1 2 . 3

3 8 1 = 21 1 1 0 1 1 0 1 ) c (

701=21101011 )a(

。 数 制 进 十 成 换 转 数 的 面 下 将 5. 2

数字设计-原理与实践(第四版)课后习题答案

第1 章习题参考答案:1-6 一个电路含有一个2 输入与门(AND2),其每个输入/输出端上都连接了一个反相器;画出该电路的逻辑图,写出其真值表;能否将该电路简化解:电路图和真值表如下:由真值表可以看出,该电路与一个2 输入或门(OR2)相同。

第2 章习题参考答案:将下面的八进制数转换成二进制数和十六进制数。

(a) 12348=1 010 011 1002=29C16(b) 1746378=1 111 100 110 011 1112=F99F16(c) 3655178=11 110 101 101 001 1112=1EB4F16(d) =10 101 011 101 011 010 0012=ABAD116(e) =111 100 011 0012=(f) =100 101 011 001 100 111 12=将下面的十六进制数转换为二进制数和八进制数。

(a) 102316=1 0000 0010 00112=100438(b) 7E6A16=111 1110 0110 10102=771528(c) ABCD16=1010 1011 1100 11012=1257158(d) C35016=1100 0011 0101 00002=1415208(e)=1001 1110 10102=(f)=1101 1110 1010 1110 1110 11112=将下面的数转换成十进制数。

(a) =107 (b) 1740038=63491 (c) 2=183(d) = (e)= (f)F3A516=62373(g) 120103=138 (h) AB3D16=43837 (i) 71568=3694(j) =完成下面的数制转换。

(a) 125= 1 111 1012 (b) 3489= 66418 (c) 209= 11 010 0012(d) 9714= 227628 (e) 132= 10 000 1002 (f) 23851= 5D2B16(g) 727= 104025 (h) 57190=DF6616 (i) 1435=26338(j) 65113=FE5916将下面的二进制数相加,指出所有的进位:(a) S:1001101 C:100100(b) S: 1010001 C: 1011100(c) S: 0 C: 0(d) S: C:利用减法而不是加法重复训练题,指出所有的借位而不是进位:(a) D:011 001 B:110000 (b) D:111 101 B:1110000(c) D: B:00111000 (d) D:1101101 B:写出下面每个十进制数的8 位符号-数值,二进制补码,二进制反码表示。

数字逻辑电路与系统设计第6章习题及解答.docx

第6章题解:6.1试用4个带异步清零和置数输入端的负边沿触发型JK 触发器和门电路设计一个异步余 3BCD 码计数器。

题6・1解:余3BCD 码计数器计数规则为:0011->0100->—1100-0011-*-,由于釆用 异步清零和置数,故计数器应在1101时产生清零和置数信号,所设计的电路如图题解6.1 所示。

题6.2试用中规模集成异步十进制计数器74290实现模48计数器。

题6.2解:图题解6. 16.3试用D触发器和门电路设计一个同步4位格雷码计数器。

题6.3解:根据格雷码计数规则,\Q1Q OQsQ>\00011110000000011000111111100111\QlQoQ.3Q>\00011110000001011111111110100000X^iQoQ3Q>\00011110000111010001110111100001\QlQoQ.3Q>\00011110001100010011111100100011 Qi Qo计数器的状态方程和驱动方程为:er1=D.=+型Q”+Q;莎er1=D2=+Q©+N Q;N QT = D L+ Q;Q;Q;; +Qj = D o = Q^Q;1+按方程画出电路图即可,图略。

6.5试用4位同步二进制计数器74163实现十二进制计数器。

74163功能表如表6.4所示。

题6・5解:可采取同步清零法实现。

电路如图题解6.5所示。

题6.6解:题6.4解:反馈值为1010c卜一进制计数器CLKCLR LD ENT ENP>c a[―<>40) a D DTC=\5图题解6. 5RCO74163当M=1时:六进制计数器八进制计数器6.7试用4位同步二进制计数器74163和门电路设计一个编码可控计数器,当输入控制变 量M=0时,电路为8421 BCD 码十进制计数器,M=1时电路为5421 BCD 码十进制计数器, 5421BCD 码计数器状态图如下图P6.7所示。

VHDL数字电路设计教程第六章习题答案

P6.1library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_1 isport(clk:in std_logic;d_out:out std_logic_vector(5 downto 0)); end;architecture bhv of chp6_1 issignal count: std_logic_vector(5 downto 0); signal temp: std_logic_vector(5 downto 0); beginprocess(clk)beginif clk'event and clk='1' thencount<= count+1;if count="100000" then count<="000000";end if;end if;end process;process(clk)beginif clk'event and clk='0' thentemp<=temp+1;if temp="0111111" then temp<="000000"; end if;end if;end process;d_out<=count+temp;end;P6.3solution1library ieee;use ieee.std_logic_1164.all;entity chp6_3 isport(x:in std_Logic_vector(7 downto 1);y:out std_logic_vector(2 downto 0)); end;architecture bhv of chp6_3 isbeginprocess(x)beginif x(7)='1' then y<="111";elsif x(6)='1' then y<="110";elsif x(5)='1' then y<="101";elsif x(4)='1' then y<="100";elsif x(3)='1' then y<="011";elsif x(2)='1' then y<="010";elsif x(1)='1' then y<="001";else y<="000";end if;end process;end;solution2library ieee;use ieee.std_logic_1164.all;entity chp6_3_2 isgeneric(n:integer:=3);port(x:in std_logic_vector(2**n-1 downto 0);y:out integer range 0 to 2**n-1); end;architecture bhv of chp6_3_2 isbeginprocess(x)variable temp:integer range 0 to 2**n-1; beginfor i in x'range loopif x(i)='1' thentemp:=i;exit;end if;end loop;y<=temp;end process;end;P6.4library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_4 isgeneric (n:integer:=8);port(clk:in std_logic;clk_out:out std_logic);end;architecture bhv of chp6_4 issignal rst:std_logic;signal temp:std_logic_vector(2 downto 0); beginprocess(clk,rst)beginif rst='1' thentemp<="000";elsif clk'event and clk='1' thentemp<=temp+1;end if;end process;rst<='1' when temp="111" else'0';clk_out<=temp(2);end;P6.5library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_5 isgeneric (n:integer:=7);port(clk:in std_logic;clk_out:out std_logic);end;architecture bhv of chp6_5 issignal temp:std_logic_vector(2 downto 0); signal cout:std_logic;beginprocess(clk)beginif clk'event and clk='1' thentemp<=temp+1;if temp="110" then temp<="000";end if;end if;end process;cout<='1' when temp="110" else'0';clk_out<=cout;end;P6.6library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity chp6_6 isport(clk,start,stop,reset:in std_logic;dig1,dig2,dig3:out std_logic_vector(3 downto 0)); end;architecture bhv of chp6_6 issignal sec1:integer range 0 to 10;signal sec2:integer range 0 to 6;signal min:integer range 0 to 10;beginprocess(clk,start, stop,reset)variable count1:integer range 0 to 10;variable count2:integer range 0 to 6;variable count3:integer range 0 to 10;beginif reset='1' thencount1:=0;count2:=0;count3:=0;elsif clk'event and clk='1' thenif start='1' and stop='0' thencount1:=count1+1;if count1=10 thencount1:=0;count2:=count2+1;if count2=6 thencount2:=0;count3:=count3+1;if count3=10 thencount3:=0;end if;end if;end if;end if;end if;sec1<=count1;sec2<=count2;min<=count3;end process;dig1<=conv_std_logic_vector(sec1,4);dig2<=conv_std_logic_vector(sec2,4);dig3<=conv_std_logic_vector(min,4);end;P6.8use ieee.std_logic_1164.all;entity chp6_8 isgeneric(n:integer:=8);port(input:in std_logic_vector(n-1 downto 0);output:out std_logic);end;architecture bhv of chp6_8 isbeginprocess(input)variable temp:std_logic_vector(n-1 downto 0); begintemp(0):=input(0);for i in 1 to n-1 looptemp(i):=input(i) xor temp(i-1);end loop;output<=temp(n-1);end process;end;P6.9library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_9 isgeneric(n:integer:=4);port(input:std_logic_vector(n-1 downto 0);output:out integer range 0 to n);end;architecture bhv of chp6_9 isbeginprocess(input)variable temp:integer range 0 to n;begintemp:=0;for i in 0 to n-1 loopif input(i)='1' thentemp:=temp+1;end if;end loop;output<=temp;end process;end;P6.10use ieee.std_logic_1164.all;entity chp6_10 isgeneric(n:integer :=8);port(din:in integer range 0 to n-1;dout:out std_logic_vector(n-1 downto 0));end;architecture bhv of chp6_10 isbeginprocess(din)beginfor i in 0 to n-1 loopif din=i then dout<=(i=>'1', others=>'0');end if;end loop;end process;end;P6.16library ieee;use ieee.std_logic_1164.all;entity chp6_16 isgeneric (n:integer:=8);port(a,b:in std_logic_vector(n-1 downto 0);cin:in std_logic;s:out std_logic_vector(n-1 downto 0);cout:out std_logic);end;architecture bhv of chp6_16 issignal carry:std_logic_vector(n downto 0);beginprocess(a,b,cin,carry)begincarry(0)<=cin;for i in 0 to n-1 loops(i)<=a(i) xor b(i) xor carry(i);carry(i+1)<=(a(i) and b(i)) or (a(i) and carry(i)) or (b(i) and carry(i));end loop;cout<=carry(n);end process;end;说明:本次答案均为课上讨论过的,P6.11-P6.15均可参考第五章答案,可以利用对应语句将其放入进程中。

数字设计原理与实践 第四版 (john F.Wakerly ) 课后答案

第1章习题参考答案:1-6 一个电路含有一个2输入与门(AND2),其每个输入/输出端上都连接了一个反相器;画出该电路的逻辑图,写出其真值表;能否将该电路简化? 解:电路图和真值表如下:由真值表可以看出,该电路与一个2输入或门(OR2)相同。

第2章习题参考答案:2.2将下面的八进制数转换成二进制数和十六进制数。

(a) 12348=1 010 011 1002=29C 16(b) 1746378=1 111 100 110 011 1112=F99F 16(c) 3655178=11 110 101 101 001 1112=1EB4F 16(d) 25353218=10 101 011 101 011 010 0012=ABAD116(e) 7436.118=111 100 011 110.001 0012=F1E.2416(f) 45316.74748=100 101 011 001 110.111 100 111 12=4ACE.F2C 162.3将下面的十六进制数转换为二进制数和八进制数。

(a) 102316=1 0000 0010 00112=100438(b) 7E6A 16=111 1110 0110 10102=771528(c) ABCD 16=1010 1011 1100 11012=1257158(d) C35016=1100 0011 0101 00002=1415208(e)9E36.7A 16=1001 1110 00110110.0111 10102=117066.3648 (f)DEAD.BEEF 16=1101 1110 1010 1101.1011 1110 1110 11112 =157255.57567482.5将下面的数转换成十进制数。

(a) 11010112=107 (b) 1740038=63491 (c) 101101112=183 (d) 67.248=55.3125 (e)10100.11012=20.8125 (f)F3A516= 62373(g) 120103=138 (h) AB3D 16=43837 (i) 71568=3694 (j) 15C.3816=348.218752.6 完成下面的数制转换。

数字电子技术 第六章习题答案

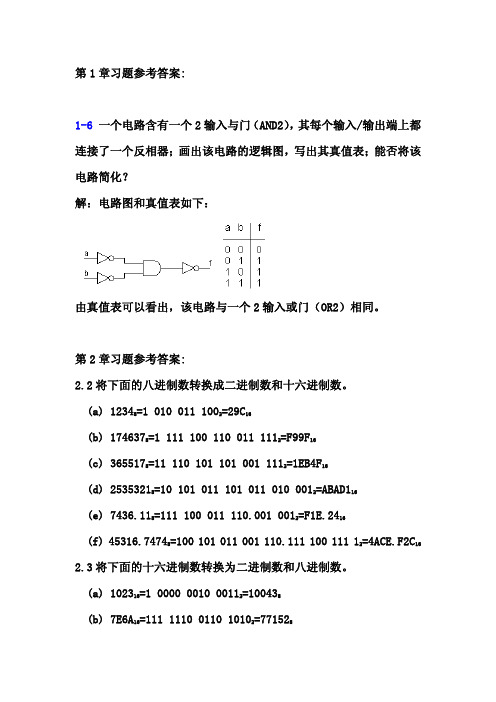

第六章 习题解答6.1. 分析题图P6.1所示电路的功能,列出功能表。

解:图P6.1所示电路的功能表如表6.1所示。

将功能表中各变量数值关系的逻辑函数用对应的“卡诺图”如图6.1所示。

RS 具有约束条件RS =0,触发器的逻辑表达式为⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,根据这一逻辑表达式,P6.1逻辑电路具有基本RS 触发器的逻辑功能,约束条件是SR=0。

6.2同步RS 触发器与基本RS 触发器的主要区别是什么?解:同步RS 触发器与基本RS 触发器的主要区别是基本RS 触发器的RS 输入信号不论任何时刻都是有效的,只要RS 输入的状态组合发生变化,输出Q 的状态跟随发生变化;而同步同步RS 触发器的RS 输入信号只要在CP 时钟脉冲信号有效时段内起作用,只有在这一时段内,输出Q 的状态才跟随RS 输入的状态组合变化而发生变化。

1& & 1QR图 P6.1QR S Q nQ n+1功 能 1 1 1 1 0 1 不用 不用 不允许11 0 0 0 1 0 0 01=+n Q 置0 0 0 1 1 0 1 1 1 11=+n Q 置10 00 00 10 1n n Q Q =+1 保持6.3如图P6.3 (a)所示电路的初始状态为Q =1,R 、S 端和CP 端的信号如图P6.3(b )所示,画出该同步RS 触发器相应的Q 和Q 端的波形。

解:根据图P6.3 (a)所示电路结构,其功能为同步RS 触发器,电路的特性方程为:⎪⎩⎪⎨⎧=+=+0RS Q R S Q n 1n ,若R=S=1,在CP 时钟脉冲信号为“1”的时段内,触发器的两个输出端的状态均输出“1”,此种情况下,若CP 时钟脉冲信号从“1”状态,跳变为“0”的输入状态,则触发器的两个输出状态为不确定状态。

根据特性方程以及电路的初始状态,作出电路的输出端时序图如图6.3所示。

6.4 主从RS 触发器输入信号的波形如图P6.4(a )、(b )所示。

数字设计原理与实践第6章答案

6.20 指出用一块或多块74x138或74x139二进制译码器以及与非门,如何构建下面每个单输出或多输出的逻辑功能(提示:每个实现等效于一个最小项之和)。

解:a )∑=Z Y X F ,,)7,4,2(b )∑∏==C B A C B A F ,,,,)2,1,0()7,6,5,4,3(c) ∑=D C B A F ,,,)12,10,2,0(或d) ∑=Z Y X W F ,,,)14,12,10,8,5,4,3,2(e) ∑=Y X W F ,,)5,4,2,0( ∑=Y X W G ,,)6,3,2,1(f) ∑=C B A F ,,)6,2( ∑=E D C G ,,)3,2,0(6.21 图X5-21电路有什么可怕的错误?提出消除这个错误的方法。

解:该电路中两个2-4译码器同时使能,会导致2个3态门同时导通,出现逻辑电平冲突。

为解决这一问题,在EN_L 至1G (或2G )的线路上加一个反相器,使两路门不可能同时导通。

6.29 二进制加法器的和的第3个数位S 2为输入x 0、x 1、x 2、y 0、y 1、y 2的函数,试写出它的代数表达式:假设c 0=0,不要试图“乘开”或最小化表达式。

解:00000001)(y x c y x y x c ⋅=⋅++⋅=001111111112)()(y x y x y x c y x y x c ⋅⋅++⋅=⋅++⋅= ))((001111222222y x y x y x y x c y x s ⋅⋅++⋅⊕⊕=⊕⊕=6.38 假设要求设计一种新的组件:优化的十进制译码器,它只有十进制输入组合。

与取消6个输出的4-16译码器相比,怎样使这样的译码器价格降至最低?写出价格最低译码器的全部10个输出的逻辑等式。

假设输入和输出高电平有效且没有使能输入。

⋅⋅'C==1ABC=3⋅'Y⋅B⋅'2AY'Y'⋅'⋅'D⋅'AB⋅'CD=CY⋅'0AB⋅=Y'C6A⋅C=7⋅Y⋅BBY'C⋅'BA5A=⋅4A=Y⋅'⋅CBY⋅D98A=ADY'⋅=6.52 画出一个电路的逻辑图,该电路采用74x148判定优先级,要求8个输入I0~I7为高电平有效,I7的优先级最高。

数字设计原理与实践第四版习题答案

04

第三章习题答案

习题一答案

要点一

答案

这道题考查的是二进制数的加法运算,根据二进制数的加 法规则,当两个二进制数的某一位相加和大于等于2时,需 要向高位进位,因此,二进制数10100101与10110000相 加的结果是10110101。

要点二

答案解释

这道题要求计算二进制数10100101与10110000的和。首先, 从最低位开始逐位相加,当某一位的和大于等于2时,需要向 高位进位。具体来说,第一位相加得0,不进位;第二位相加 得0,不进位;第三位相加得1,不进位;第四位相加得1, 进位;第五位相加得0,不进位;第六位相加得1,进位;第 七位相加得1,不进位;第八位相加得1,不进位。因此,最 终结果是10110101。

03

04

05

1.0 互补性:对于任何逻 辑门,其互补门的输出 与原门的输入反相。例 如,AND门的互补是 OR门,OR门的互补是 AND门。

2.0 消抖动性:在输入信 号的上升沿或下降沿, 逻辑门电路的输出不会 发生多次跳变,而是保 持稳定状态。

3.0 扇入扇出系数:一个 逻辑门可以驱动的最大 逻辑门数称为扇出系数; 一个逻辑门可以接收的 最大逻辑门数称为扇入 系数。

习题三答案

•· 数字逻辑门电路的应用

1.0 AND门在数据传输中的应用: 用于控制信号的传输,确保只有 在两个控制信号都有效时,数据 信号才会被传输。

2.0 OR门在报警系统中的应用: 当任何传感器触发时,OR门将输 出高电平,触发报警系统。

3.0 NOT门在时钟信号中的应用: 用于产生与主时钟信号反相的时 钟信号,用于触发边沿触发的数 字逻辑门电路。

THANKS

感谢观看

05

数字设计原理与实践复习总资料

能按选定的方向传输数据.

多路复用器

74x151

8输入1位多路复用器,选择输入为C、B、A,其中C是最高 有效位;使能输入EN_L低电平有效;输出为Y及Y_L。

74x153

4输入2位多路复用器,具有分开的1位使能输入(1G、2G).

多路分配器

多路分配器的功能恰好与多路复用器的功

能相反。 b位、n输出的多路分配器,其有b个

A B C

A B C

i

2 1

n

A B C

如:

4. 且有

Mi m

或

M

i

mi

m 4 = ( A B C ) = A B C = M 4

竞争-冒险产生的原因:电路延时

如何判断与消除冒险。

1、如采用卡诺图法,则判断:观察是否存在 “相切”的卡诺圈, 若存在则可能产生冒险。 2、如采用卡诺图法,则消除:在卡诺图中增 加卡诺圈以消除“相切”现象。

数据输入、s个选择输入选择n=2s个b位数据输

出集合之一。在正常操作中,被选中的输出等

于数据输入,其它输出均为0。

奇偶校验电路

异或(XOR)门: Y X Y X Y X 异或非(XNOR)门: Y X Y X Y X

0 A的个数为偶数 A的个数为奇数 A的个数为偶数 A的个数为奇数

5 1 0 1 0 1 0

6 1 0 1 0 1 0

7 0 0 1 1 0 0

8 1 1 0 0 1 1

CP: x: y2: y1: y2*: y1*: z:

1 0 0 0 0 0 0

2 1 0 0 0 1 0

3 0 0 1 1 0 0

数字设计原理与实践答案整理

1.3ASIC Application-Specific Integrated CircuitCAD Computer-Aided DesignCD Compact DiscCO Central OfficeCPLD Complex Programmable Logic DeviceDIP Dual In-line PinDVD Digital Versatile DiscFPGA Field-Programmable Gate ArrayHDL Hardware Description LanguageIC Integrated CircuitIP Internet ProtocolLSI Large-Scale IntegrationMCM Multichip ModuleMSI Medium-Scale IntegrationNRE Nonrecurring EngineeringPBX Private Branch ExchangePCB Printed-Circuit BoardPLD Programmable Logic DevicePWB Printed-Wiring BoardSMT Surface-Mount TechnologySSI Small-Scale IntegrationVHDL VHSIC Hardware Description LanguageVLSI Very Large-Scale Integration1.4ABEL Advanced Boolean Equation LanguageCMOS Complementary Metal-Oxide SemiconductorJPEG Joint Photographic Experts GroupMPEG Moving Picture Experts GroupOK 据说是Oll Korrect(All Correct)的缩写。

VHDL数字电路设计教程第六章习题答案

VHDL数字电路设计教程第六章习题答案P6.1library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_1 isport(clk:in std_logic;d_out:out std_logic_vector(5 downto 0));end;architecture bhv of chp6_1 issignal count: std_logic_vector(5 downto 0);signal temp: std_logic_vector(5 downto 0);beginprocess(clk)beginif clk'event and clk='1' thencount<= count+1;if count="100000" then count<="000000";end if;end if;end process;process(clk)beginif clk'event and clk='0' thentemp<=temp+1;if temp="0111111" then temp<="000000";end if;end if;end process;d_out<=count+temp;end;P6.3solution1library ieee;use ieee.std_logic_1164.all;entity chp6_3 isport(x:in std_Logic_vector(7 downto 1);y:out std_logic_vector(2 downto 0));end;architecture bhv of chp6_3 isbeginprocess(x)beginif x(7)='1' then y<="111";elsif x(6)='1' then y<="110";elsif x(5)='1' then y<="101";elsif x(4)='1' then y<="100";elsif x(3)='1' then y<="011";elsif x(2)='1' then y<="010";elsif x(1)='1' then y<="001";else y<="000";end if;end process;end;solution2library ieee;use ieee.std_logic_1164.all;entity chp6_3_2 isgeneric(n:integer:=3);port(x:in std_logic_vector(2**n-1 downto 0);y:out integer range 0 to 2**n-1); end;architecture bhv of chp6_3_2 isbeginprocess(x)variable temp:integer range 0 to 2**n-1; beginfor i in x'range loopif x(i)='1' thentemp:=i;exit;end if;end loop;y<=temp;end process;end;P6.4library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_4 isgeneric (n:integer:=8);port(clk:in std_logic;clk_out:out std_logic);end;architecture bhv of chp6_4 issignal rst:std_logic;signal temp:std_logic_vector(2 downto 0);beginprocess(clk,rst)beginif rst='1' thentemp<="000";elsif clk'event and clk='1' thentemp<=temp+1;end if;end process;rst<='1' when temp="111" else'0';clk_out<=temp(2);end;P6.5library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_5 isgeneric (n:integer:=7);port(clk:in std_logic;clk_out:out std_logic);end;architecture bhv of chp6_5 issignal temp:std_logic_vector(2 downto 0); signal cout:std_logic;beginprocess(clk)beginif clk'event and clk='1' thentemp<=temp+1;if temp="110" then temp<="000";end if;end if;end process;cout<='1' when temp="110" else'0';clk_out<=cout;end;P6.6library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity chp6_6 isport(clk,start,stop,reset:in std_logic;dig1,dig2,dig3:out std_logic_vector(3 downto 0)); end;architecture bhv of chp6_6 issignal sec1:integer range 0 to 10;signal sec2:integer range 0 to 6;signal min:integer range 0 to 10;beginprocess(clk,start, stop,reset)variable count1:integer range 0 to 10;variable count2:integer range 0 to 6;variable count3:integer range 0 to 10;beginif reset='1' thencount1:=0;count2:=0;count3:=0;elsif clk'event and clk='1' thenif start='1' and stop='0' thencount1:=count1+1;if count1=10 thencount1:=0;count2:=count2+1;if count2=6 thencount2:=0;count3:=count3+1;if count3=10 thencount3:=0;end if;end if;end if;end if;end if;sec1<=count1;sec2<=count2;min<=count3;end process;dig1<=conv_std_logic_vector(sec1,4);dig2<=conv_std_logic_vector(sec2,4);dig3<=conv_std_logic_vector(min,4);end;P6.8library ieee;use ieee.std_logic_1164.all;entity chp6_8 isgeneric(n:integer:=8);output:out std_logic);end;architecture bhv of chp6_8 isbeginprocess(input)variable temp:std_logic_vector(n-1 downto 0); begintemp(0):=input(0);for i in 1 to n-1 looptemp(i):=input(i) xor temp(i-1);end loop;output<=temp(n-1);end process;end;P6.9library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity chp6_9 isgeneric(n:integer:=4);port(input:std_logic_vector(n-1 downto 0);output:out integer range 0 to n);end;architecture bhv of chp6_9 isbeginprocess(input)variable temp:integer range 0 to n;begintemp:=0;for i in 0 to n-1 loopif input(i)='1' thentemp:=temp+1;end if;end loop;output<=temp;end process;end;P6.10library ieee;use ieee.std_logic_1164.all;entity chp6_10 isgeneric(n:integer :=8);port(din:in integer range 0 to n-1;end;architecture bhv of chp6_10 isbeginprocess(din)beginfor i in 0 to n-1 loopif din=i then dout<=(i=>'1', others=>'0');end if;end loop;end process;end;P6.16library ieee;use ieee.std_logic_1164.all;entity chp6_16 isgeneric (n:integer:=8);port(a,b:in std_logic_vector(n-1 downto 0);cin:in std_logic;s:out std_logic_vector(n-1 downto 0);cout:out std_logic);end;architecture bhv of chp6_16 issignal carry:std_logic_vector(n downto 0);beginprocess(a,b,cin,carry)begincarry(0)<=cin;for i in 0 to n-1 loops(i)<=a(i) xor b(i) xor carry(i);carry(i+1)<=(a(i) and b(i)) or (a(i) and carry(i)) or (b(i) and carry(i));end loop;cout<=carry(n);end process;end;。

Verilog HDL数字设计与综合(第二版) 第六章课后习题答案

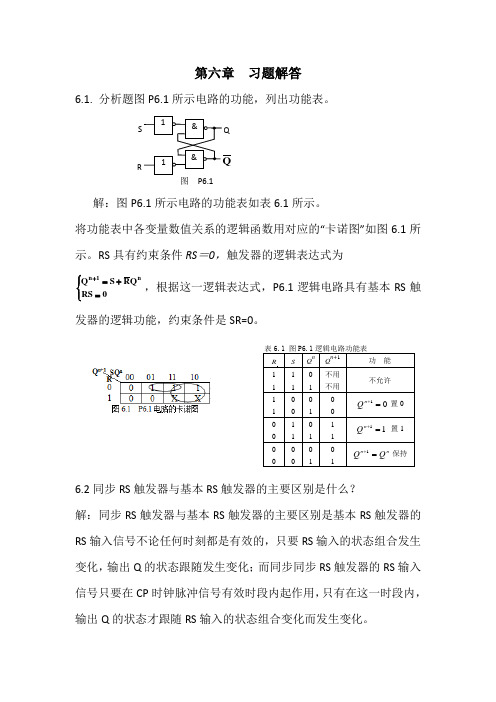

1.一个全减器具有三个一位输入:x,y和z(前面的借位),两个一位输出D(差)和B(借位)。

计算D和B的逻辑等式如下所示:D = x’⋅ y’⋅ z’ + x’⋅ y ⋅ z’ + x ⋅ y’⋅ z’ + x ⋅ y ⋅ zB = x’⋅ y + x’⋅ z + y ⋅ z根据上面的定义写出Verilog描述,包括I/O端口(注意:逻辑等式中的+对应于数据流建模中的逻辑或(| |)操作符)。

编写激励块,在模块中实例引用全减器。

对x,y和z这三个输入的8种组合及其对应的输出进行测试。

x y z B D0 0 0 0 00 0 1 1 10 1 0 1 10 1 1 1 01 0 0 0 11 0 1 0 01 1 0 0 01 1 1 1 1答:代码及测试激励如下:(D 应该= x’⋅y’⋅z + x’⋅ y ⋅z’ + x ⋅y’⋅z’ + x ⋅ y ⋅ z)`timescale 1ns/1nsmodule full_sub(x,y,z,D,B);input x,y,z;output D,B;assign D=((!x)&(!y)&(z))||((!x)&y&(!z))||(x&(!y)&(!z))||(x&y&z);assign B=((!x)&y)||((!x)&z)||(y&z);endmodulemodule test61;reg x,y,z;wire D,B;Verilog HDL数字设计与综合(第二版)58initialbeginx<=0;y<=0;z<=0;#10 x<=0;y<=0;z<=1;#10 x<=0;y<=1;z<=0;#10 x<=0;y<=1;z<=1;#10 x<=1;y<=0;z<=0;#10 x<=1;y<=0;z<=1;#10 x<=1;y<=1;z<=0;#10 x<=1;y<=1;z<=1;#10 $stop;endfull_sub fsubtracter(x,y,z,D,B);initial$monitor($time,"x= %b,y= %b,z= %b,B= %b,D= %b",x,y,z,B,D);endmodule最终输出观测结果:# 0x= 0,y= 0,z= 0,B= 0,D= 0# 10x= 0,y= 0,z= 1,B= 1,D= 1# 20x= 0,y= 1,z= 0,B= 1,D= 1# 30x= 0,y= 1,z= 1,B= 1,D= 0# 40x= 1,y= 0,z= 0,B= 0,D= 1# 50x= 1,y= 0,z= 1,B= 0,D= 0# 60x= 1,y= 1,z= 0,B= 0,D= 0# 70x= 1,y= 1,z= 1,B= 1,D= 1第6章数据流建模592.大小比较器的功能是比较两个数之间的关系:大于、小于或等于。

数字逻辑设计习题参考答案(第6章)

第6章时序逻辑电路6—1 从概念,结构和功能描述等几个方面简述时序逻辑电路和组合逻辑电路的不同。

概念:组合逻辑电路在任一时刻的输出仅由该时刻的输入决定,而与过去的状态无关,电路无记忆功能。

时序逻辑电路任一时刻的输出信号不仅取决于该时刻的输入信号,而且还取决于电路原来的状态。

结构:组合电路都是单纯由逻辑门组成,且输出不存在反馈路径。

时序逻辑电路由组合逻辑电路和存储电路组成,输出和输入之间有反馈。

存储电路一般由触发器构成。

功能描述:组合逻辑电路一般用逻辑图、逻辑表达式和真值表描述。

时序逻辑一般用逻辑图、逻辑方程式(状态方程、输出方程、驱动方程)、状态转换表、状态转换图和时序图来描述。

6—2 作出与表1所示状态表对应的状态图。

6—3 用边沿触发D触发器和与非门设计一个三位右移寄存器,用一控制端X控制,当0=X时能串行输入新数据ID,当1=X时具有自循环功能。

A BD C2111/10X/010/011/010/001/101/010/011/000/001/1QQSETCLRDQQSETCLRDQQSETCLRDXD ID OCP6—4 完成下列设计:1. 画出用J-K 触发器实现的四位右移寄存器的逻辑图(数据向高位移位定义为右移,寄存器的输出1Q 2Q 3Q 4Q ,设4Q 为高位。

2. 用上述四位右移寄存器实现下列计数器,写出设计步骤,画出逻辑图。

CP 1Q 2Q 3Q 4Q0 0 0 0 0 11 0 0 02 0 1 0 0 31 0 1 0 4 0 1 0 1 5 0 0 1 0 6 0 0 0 1 70 0 0 0答:由题意知,计数器是由右移寄存器实现的,所以只要确定第一个JK 触发器的驱动方程即可。

根据给出的状态转换表,可得卡诺图。

化简得43Q Q Q Q Q Q D ++=⋅⋅=6—5 用一片74LS161和必要的门电路构成一个可控计数器。

当控制端C=1时,实现八进制计数;C=0时,实现四进制数。