ADCLK948BCPZ;ADCLK948BCPZ-REEL7;ADCLK948PCBZ;中文规格书,Datasheet资料

数据手册中文版

14位, 165M SPA(采样率)DAC(数模转换器)特性:●单电源供电+5V或+3V●高SFDR (无杂散动态范围): 在100MSPS 64dBc时20MHz输出●低干扰: 3PV -S●低功耗: 170MW (+5 V时)应用●通讯传输通道WLL , 蜂窝基站数字微波链路电缆调制解调器●波形产生直接数字频率合成器(DDS )任意波形发生器(ARB )●医疗/超声●高速仪表和控制●视频, 数字电视说明:DAC904是一款高速数模转换器, 14位分辨率, 引脚兼容DAC908、DAC900、DAC902, 分别提供8-, 10-, 12-位分辨率选择。

该系列DAC支持的所有型号更新率超过165MSPS, 具有优良的动态性能。

DAC904先进分割架构的优化为单音和多频音信号提供高无杂散动态范围(SFDR), 特别是用于通信系统的发送信号电路时。

DAC904具有高阻抗(200KΩ)的电流输出, 标称范围为20mA和一个最多为1.25V的输出。

差分输出允许两个差分或单端模拟信号的接口。

电流输出的匹配保证在差分结构中杰出的动态性能, 它可以与变压器配合使用。

运用一个小的几何CMOS工艺, 单片DAC904可以用在+2.7 V至+5.5 V宽的单电源范围内操作。

其低功耗特性允许它使用在便携式和电池供电系统情况下。

可通过减少输出电流与调整满量程选项实现进一步优化。

DAC904不断运转时, 掉电模式导致其待机功率仅为为45mW 。

DAC904带有一个集成的1.24V带隙基准和边沿触发输入锁存器, 提供完整的转换器解决方案。

+3 V和+5 V CMOS逻辑系列都可以接口到DAC904 。

DAC904的参考结构允许使用芯片上的参考, 或施加外部参考。

通过一个外部电阻, 满量程输出电流可以调整在2 - 20mA, 并保持其指定的动态性能。

DAC904采用SO -28和TSSOP -28封装。

绝对最大额定值+VA到AGND(模拟信号地)......-0.3V至+6V+VD到DGND(数字信号地)......-0.3V到+6VAGND到DGND......-0.3V到+0.3V+VA 到+VD......-6V到+6VCLK, PD到DGND......-0.3V到VD+0.3VD0-D13到DGND......-0.3V到VD+0.3VIOUT, I 到AGND......-1V到VA+0.3VBW,BYP到AGND......-0.3V到VA+0.3VREFIN ,FSA到AGND......-0.3V到VA+0.3VINT/EXT到AGND......-0.3V到VA+0.3V结温度. . . . . . . +150℃存储器温度. . . . . . +125℃防静电敏感度这种集成的电路可以被ESD(静电释放)损坏。

南京凌鸥创芯 LKS580 数据手册说明书

南京凌鸥创芯电子有限公司LKS580数据手册@ 2019, 版权归凌鸥创芯所有机密文件,未经许可不得扩散目录1概述 (1)1.1功能简述 (1)1.2主要指标 (1)1.3控制逻缉 (2)2管脚分布 (3)2.1管脚分布图 (3)2.2管脚说明 (3)3封装尺寸 (4)4应用示例 (5)5电气性能参数 (6)5.1极限参数 (6)5.2建议工况 (6)5.3动态电气参数 (6)5.4静态电气参数 (8)6版本历史 (9)表1-1 主要指标参数 (1)表2-1 LKS580管脚说明 (3)表3-1 LKS580封装尺寸 (4)表5-1 LKS580极限参数表 (6)表5-2 LKS580建议工作参数表 (6)表5-3 LKS580动态电气参数表 (8)表5-4 LKS580 静态电气参数 (8)表6-1 文档版本历史 (9)图1-1 LKS580内部结构框图 (1)图1-2 LKS580控制逻辑时序图 (2)图2-1 LKS580管脚分布图 (3)图3-1 LKS580封装图示 (4)图4-1 典型应用图示 (5)图4-2 大电流负载应用图示 (5)图5-1 时序参数t on/t off/t f定义 (7)图5-2 时序参数MT定义 (7)图5-3 死区时序定义 (7)1 概述1.1 功能简述LKS580是一款用于驱动MOS/IGBT 栅极的集成电路,芯片有高侧驱动输出和低侧驱动输出两组,可同时驱动两个MOS/IGBT 器件,其中高侧器件通过浮动管脚实现电压抬升,最高耐压达+600V 。

输入信号可兼容CMOS 和LSTTL 电平。

HINLINVCCLOCOMVBHO VS图 1-1 LKS580内部结构框图1.2 主要指标高侧驱动采用浮动电源设计,最高耐压+600V 可承受瞬时负压芯片电源供电范围10~25V欠压保护功能输入电平3.3/5/15V 兼容 双通道延时匹配表 1-1 主要指标参数1.3控制逻缉控制逻缉如图1.2所示:高侧控制端HIN高电平有效,低侧控制端LIN低电平有效,当高侧低侧同时有效时,输出禁止。

ILI9488_AN_V0.1_20121116

141

142

VCOM

143

144

VCOM VCOM VCOM TESTP_VGP TESTP_VGP AGND/DGND AGND/DGND DUMMY DUMMY DUMMY DUMMY DUMMY MIPI_LDO DUMMY MIPI_DATA_N/MDDI_DATA_N MIPI_DATA_N/MDDI_DATA_N MIPI_DATA_P/MDDI_DATA_P MIPI_DATA_P/MDDI_DATA_P MIPI_CLOCK_N/MDDI_STB_N MIPI_CLOCK_N/MDDI_STB_N MIPI_CLOCK_P/MDDI_STB_P MIPI_CLOCK_P/MDDI_STB_P DUMMY_TEST0 DB23 DB22 DB21 DB20 DB19 DB18 CABC_PWM IM0 IM1 IM2 RESX VSYNC HSYNC DOTCLK ENABLE DB17 DB16 DB15 DB14 DB13 DB12 DB11 DB10 DB9 DB8 DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 SDO/DOUT SDA/DIN RDX WRX/SCL D/CX CSX TE IOVCC IOVCC VDD VDD DGND DGND DGND VGS AGND AGND AGND VCOM VCOM VCOM C41A/C15A C41A/C15A C41B/C15B C41B/C15B DUMMY_NVCOR DUMMY_NVCOR VCL/DDVDL VCL/DDVDL DDVDH DDVDH DDVDL/VCL DDVDL/VCL VCI VCI VCI C11B_C31B C11B_C31B C11B_C31B C11B_C31B C11A_C31A C11A_C31A C11A_C31A C11A_C31A C12B_C32B C12B_C32B C12B_C32B C12B_C32B C12A_C32A C12A_C32A C12A_C32A C12A_C32A VGL VGL VGL VGL AGND AGND AGND VGH VGH VGH VGH C51B/C11B C51B/C11B C51B/C11B C51A/C11A C51A/C11A C51A/C11A C52B/C12B C52B/C12B C52B/C12B C52B/C12B C52A/C12A C52A/C12A C52A/C12A C52A/C12A C21B C21B C21B C21B C21A C21A C21A C21A VCOM VCOM VCOM

FPGA高速ADC接口实战——250MSPS采样率ADC9481

FPGA⾼速ADC接⼝实战——250MSPS采样率ADC9481⼀、前⾔ 最近忙于硕⼠毕业设计和论⽂,没有太多时间编写博客,现总结下之前在某个项⽬中⽤到的⼀个⾼速ADC接⼝设计部分。

ADC这⼀器件经常⽤于⽆线通信、传感、测试测量等领域。

⽬前数字系统对⾼速数据采集的需求与⽇俱增,本⽂使⽤了⽶联客的⼀款速率较⾼的AD/DA模块ADQ9481来阐述利⽤FPGA设计⾼速ADC接⼝的技术要点。

⼆、ADC硬件特性分析 ⾸先必须通过datasheet分析其核⼼参数、接⼝定义和时序要求。

ADC9481的采样率为250MSPS,精度8bit。

其原理结构图如下: 主要引脚说明: CLK+-:差分时钟输⼊,信号频率为250MHz VIN+-:模拟信号输⼊,范围是1Vpp VREF:电压参考输⼊/输出,这⾥使⽤内部固定参考电压模式 SENSE:参考模式选择 D7A~D0A:通道A数字信号输出 D7B~D0B:通道B数字信号输出 DCO+-:数字差分时钟输出,信号频率为125MHz S1:数据格式选择,该接⼝电压决定数格式时原码还是补码 PDWN:低功耗选通 接下来看看接⼝时序: 很容易看出A和B两个数字输出通道是交替输出的,通道A在DCO+上升沿输出,B在DCO-上升沿输出。

DCO+-的频率仅是采样率250MHz的⼀半,也就是降低了对数字系统处理速率的要求。

三、ADC接⼝设计 根据上述时序关系可知,FPGA端需要在DCO+上升沿采集通道B数据,在DCO-上升沿采集通道A数据。

并且由于在DCO+-同⼀变化沿时刻,通道A为前⼀个数据,因此要注意数据的采集顺序。

这类数据采集的普遍做法是将数据存⼊到RAM中,然后利⽤本地时钟同步。

具体⽅法是:按照两通道的数据顺序对数据进⾏拼接,之后缓存到异步FIFO中。

本地PLL⽣成的125MHz时钟作为读侧和后续处理时钟信号。

这⾥就要利⽤Xilinx FPGA的“原语”中的IBUFDS+BUFG,依次是差分输⼊缓冲器和全局缓冲器。

KDA8路全隔离热电偶采集模块使用说明书

KD AA: 全隔离信号(0.1秒采样)C: 通用隔离输入E: 4-20mA专用输入G: 单热电偶全隔离输入H: 单热电偶非隔离输入J: 隔离输入支持 10A电流输入K: 隔离输入(独立馈电接线)M: 标准信号(独立馈电接线)U: 单热电偶全隔离输入(热电偶专用插头)7-24V 6通道工作电源最大输入7-24V 12通道7-24V7-24V16通道16通道7-24V7-24V16通道6通道7-24V7-24V7-24V8通道8通道8通道RS485输出接口RS485RS485RS485RS485RS485RS485RS485RS485产品尺寸: 187(W)X34(H)mmX112(D)mm 导轨安装或桌面放置KD BA: 全隔离信号(0.1秒采样) B: 标准信号 (0.3秒采样)C: 通用隔离输入D: 经济型标准输入E: 4-20mA专用输入G: 单热电偶全隔离输入H: 单热电偶非隔离输入J: 隔离输入支持 10A电流输入7-24V7-24V6通道6通道工作电源最大输入7-24V7-24V6通道6通道7-24V7-24V6通道8通道7-24V7-24V8通道6通道RS485RS485输出接口RS485RS485RS485RS485RS485RS485产品尺寸: 93(W)X35(H)mmX121(D)mm 导轨安装或桌面放置KD CE: 4-20mA专用输入H: 单热电偶非隔离输入7-24V7-24V1通道1通道工作电源最大输入RS485RS485输出接口产品尺寸: 54(W)X32(H)mmX82(D)mm 导轨安装或桌面放置输入信号选型附表U: 单热电偶全隔离输入(热电偶专用插头)U注 C系列信号板与A系列信号功能接近,C系列信号板不支持NTC输入,不支持0-50V输入C系列热电偶冷端精度为正负0.1度,而A系列冷端精度则为正负0.5度(影响热电偶绝对误差)C系列信号板侧重于热电偶精度,而A系列侧重于兼容性,抗干扰能力区别不大,均为隔离差分186mm前视图后视图186mm34m mR S 485转U S B 通讯接口上图为了看清接线,USB 被放大了,非实物比例在电脑上按装U 盘里的驱动复制电脑在线监控系统到电脑上如果是无线模块,已接好线,分别插在仪表上与电脑上如果是布线的将仪表的485+接转换器直接将热电偶插头插入每个通道B A 24V (不分正负极)-485+模块供电CH01 CH02CH03 CH04CH05 CH06CH07 CH08热电偶插头热电偶插头0008050301ST E J K -200.0~1300.0-200.0~800.0-200.0~1000.0-200.0~400.0-50.0~1650.0输入代码SN 与信号类型接上电源,通过485通讯连接到电脑或PLC 或人机界面 连电脑时我们有配套的监控软件 一台电脑或人机界面可以接64个模块 每个模块可以设置不同的地址或波特率RS48安装软件在电脑上按装盘里的驱动341复制电脑在线监控系统到电脑上如果是无线模块,已接好线,分别插在仪表上与电脑上315转USB 通讯接口24RS 485转US B 通讯接口接仪表RS 485+接仪表RS 485-1台电脑可监控20台无纸记录仪,最大多可达255测试点仪表连接电脑后,扫描电脑二维码,可通过手机远程监控电脑监控软件免费,一台电脑需要一个可根据实际定制电脑上位机软件接仪表RS 485+接仪表RS 485-自定义通道名称及单位名称 上下限电脑报警查询数据只需0.1秒 高速而稳定同时显示所有通道曲线 曲线放大 坐标位移功能视频教程 高效而稳定的上位机软件研发费用至少在数百万元之上无疑给成长中仪器仪表厂商带来困惑;为此科顺仪器愿将上位机软件共享给仪器仪表厂商使用;软件可永久授权软件并提共源代码;具有完全自主知识产权;自绘数据显示控件, 自主研发实时数据库,极小体积;可导出EXCEL软件仅供我司仪器仪表用户免费使用,不支持第三方硬件商业授权主要面向仪器仪表厂商即仪器仪表厂商生产的仪表或采集模块使用我们的软件来监控商业授权提供三年以上技术支持,并提供驱动开发;商业授权提供10种硬件驱动开发,并提供软件所有源码;为我司模块提供量程上下限配置设置模块输入类型如 4-20mA 0-5V Pt100等模块误差修正功能等视频教程 读测量值功能码寄存器地址寄存器说明0400-151~16通道温度值数据类型INT16功能码寄存器地址寄存器说明数据类型读内部寄存器0300-15返回通道1-16mV 值INT160316-311~16通道温度值INT1603254仪表类型INT1603255环境温度INT160332-471~16通道传感器输入类型表INT160348-631-16通道传感器误差修正值INT160364-791~16通道K 型热电偶温度值INT160380-951~16通道E 型热电偶温度值INT160396-1111~16通道N 型热电偶温度值INT1603112-1281~16通道J 型热电偶温度值INT1603128-1431~16通道Wre 3-25热电偶温度值INT1603144-1591~16通道T 型热电偶温度值INT1603160-1751~16通道B 型热电偶温度值INT1603175-1911~16通道R 型热电偶温度值INT1603192-2071~16通道S 型热电偶温度值INT1603208-2231~16通道Wre 5-26热电偶温度值INT1603224-2401~16通道F2型热电偶温度值INT1603253通讯地址INT1603252波特率INT16通讯协议模块适用于标准Modbus RTU 通讯协议,仪表支持下文中所描述的功能码。

AD9480应用于双通道数字化仪中的研究

垂 直 分 辨率 又 决 定 了系 统 的 分辨 率 。 因此 A C的正 确 D

选 择决定着 整个 系统 的技术 性能 。

1 AD 4 0转换器的性能 98

双 通 道 数 字 化 仪 中 的 A D转 换 器 选 用 了 AD 4 0 / 98, ( n lg D vcs Ic,简 称 AD )最 新 推 出的 8 bt 数 A ao eie n . I i模

性 能往往 直接 影 响整个 系 统 的技术 指 标 。 由于 系统 采样

速率 主要 取 决 于 A DC的转换 时 间 和分 相 数 ,而 A DC的

电路 。A 9 8 D 40与 A 94A高 速 A C具 有相 同 的引脚 配 D01 D 置 ,允 许 设 计 工 程 师 通 过 简单 的 电 路 板 修 改 升 级 其 产

特性 指标则 是 由 A C的非 线性 等 因素所产 生的失 真 、噪 D 声 、频 响误 差等 嗍 。所 以 ,两 者是 由高速 A D模 数转换 /

计 考 虑 ,它 还具 有 4 . B信 噪 比 (N )和无 失 码 等 优 6d 4 SR

点 。A 9 8 D 4 0在 一 0I + 5I的整 个工 业 温 度 范 围 内代表 4c- 8c = = 性 地 提 供 ± .5 L B 的 D L 【 03 S N l J 转 换 器 采用 33 V单 。该 . 电源 供 电并 且包 含 一 个 内部基 准 电 压源 和采 样 跟踪 保持

所 以单 片 A 9 8 D 40的输 入最 高 时钟为 20 H 。 0M z

()模拟信号输入 :为了获得最高的指标 ,许多 A 2 / D变换器都采用差分模拟输入。采用差分模拟输入对巩 模 噪声有很好 的抑制作用 阁 D 4 0 。A 98 模拟输入端 向等 效电路如图 3 所示 ,需要提供差分输入信号。如果采用

AD9516-1BCPZ;AD9516-1BCPZ-REEL7;AD9516-1PCBZ;中文规格书,Datasheet资料

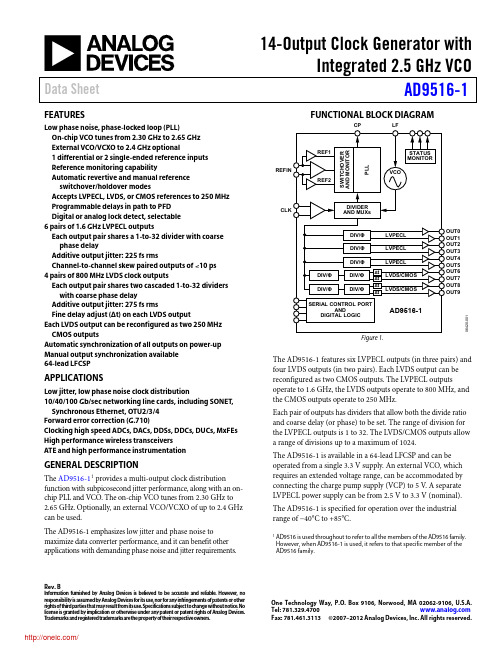

14-Output Clock Generator withIntegrated 2.5 GHz VCO Data Sheet AD9516-1Rev. BInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2007–2012 Analog Devices, Inc. All rights reserved.FEATURESLow phase noise, phase-locked loop (PLL)On-chip VCO tunes from 2.30 GHz to 2.65 GHzExternal VCO/VCXO to 2.4 GHz optional1 differential or2 single-ended reference inputs Reference monitoring capabilityAutomatic revertive and manual referenceswitchover/holdover modesAccepts LVPECL, LVDS, or CMOS references to 250 MHz Programmable delays in path to PFDDigital or analog lock detect, selectable6 pairs of 1.6 GHz LVPECL outputsEach output pair shares a 1-to-32 divider with coarsephase delayAdditive output jitter: 225 fs rmsChannel-to-channel skew paired outputs of <10 ps4 pairs of 800 MHz LVDS clock outputsEach output pair shares two cascaded 1-to-32 dividerswith coarse phase delayAdditive output jitter: 275 fs rmsFine delay adjust (Δt) on each LVDS outputEach LVDS output can be reconfigured as two 250 MHz CMOS outputsAutomatic synchronization of all outputs on power-up Manual output synchronization available64-lead LFCSPAPPLICATIONSLow jitter, low phase noise clock distribution10/40/100 Gb/sec networking line cards, including SONET, Synchronous Ethernet, OTU2/3/4Forward error correction (G.710)Clocking high speed ADCs, DACs, DDSs, DDCs, DUCs, MxFEs High performance wireless transceiversATE and high performance instrumentationGENERAL DESCRIPTIONThe AD9516-11 provides a multi-output clock distribution function with subpicosecond jitter performance, along with an on-chip PLL and VCO. The on-chip VCO tunes from 2.30 GHz to 2.65 GHz. Optionally, an external VCO/VCXO of up to 2.4 GHz can be used.The AD9516-1 emphasizes low jitter and phase noise to maximize data converter performance, and it can benefit other applications with demanding phase noise and jitter requirements.FUNCTIONAL BLOCK DIAGRAMREFINCLKLFCP642-1Figure 1.The AD9516-1 features six LVPECL outputs (in three pairs) and four LVDS outputs (in two pairs). Each LVDS output can be reconfigured as two CMOS outputs. The LVPECL outputs operate to 1.6 GHz, the LVDS outputs operate to 800 MHz, and the CMOS outputs operate to 250 MHz.Each pair of outputs has dividers that allow both the divide ratio and coarse delay (or phase) to be set. The range of division for the LVPECL outputs is 1 to 32. The LVDS/CMOS outputs allow a range of divisions up to a maximum of 1024.The AD9516-1 is available in a 64-lead LFCSP and can be operated from a single 3.3 V supply. An external VCO, which requires an extended voltage range, can be accommodated by connecting the charge pump supply (VCP) to 5 V. A separate LVPECL power supply can be from 2.5 V to 3.3 V (nominal). The AD9516-1 is specified for operation over the industrial range of −40°C to +85°C.1 AD9516 is used throughout to refer to all the members of the AD9516 family. However, when AD9516-1 is used, it refers to that specific member of the AD9516 family.AD9516-1Data SheetRev. B | Page 2 of 80TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 General Description.........................................................................1 Functional Block Diagram..............................................................1 Revision History...............................................................................3 Specifications.....................................................................................4 Power Supply Requirements.......................................................4 PLL Characteristics......................................................................4 Clock Inputs..................................................................................6 Clock Outputs...............................................................................6 Timing Characteristics................................................................7 Clock Output Additive Phase Noise (Distribution Only; VCO Divider Not Used)........................................................................8 Clock Output Absolute Phase Noise (Internal VCO Used)....9 Clock Output Absolute Time Jitter (Clock Generation Using Internal VCO).............................................................................10 Clock Output Absolute Time Jitter (Clock Cleanup Using Internal VCO).............................................................................10 Clock Output Absolute Time Jitter (Clock Generation Using External VCXO).........................................................................10 Clock Output Additive Time Jitter (VCO Divider Not Used).......................................................................................................11 Clock Output Additive Time Jitter (VCO Divider Used).....11 Delay Block Additive Time Jitter..............................................12 Serial Control Port.....................................................................12 PD , RESET , and SYNC Pins.....................................................13 LD, STATUS, and REFMON Pins............................................13 Power Dissipation.......................................................................14 Timing Diagrams............................................................................15 Absolute Maximum Ratings..........................................................16 Thermal Resistance....................................................................16 ESD Caution................................................................................16 Pin Configuration and Function Descriptions...........................17 Typical Performance Characteristics...........................................19 Terminology....................................................................................25 Detailed Block Diagram................................................................26 Theory of Operation......................................................................27 Operational Configurations......................................................27 Digital Lock Detect (DLD).......................................................36 Clock Distribution.....................................................................40 Reset Modes................................................................................48 Power-Down Modes..................................................................49 Serial Control Port.........................................................................50 Serial Control Port Pin Descriptions.......................................50 General Operation of Serial Control Port...............................50 The Instruction Word (16 Bits)................................................51 MSB/LSB First Transfers...........................................................51 Thermal Performance....................................................................54 Register Map Overview.................................................................55 Register Map Descriptions............................................................59 Applications Information..............................................................77 Frequency Planning Using the AD9516..................................77 Using the AD9516 Outputs for ADC Clock Applications....77 LVPECL Clock Distribution.....................................................78 LVDS Clock Distribution..........................................................78 CMOS Clock Distribution........................................................79 Outline Dimensions.......................................................................80 Ordering Guide.. (80)Data SheetAD9516-1Rev. B | Page 3 of 80REVISION HISTORY1/12—Rev. A to Rev. BChanges to 0x232 Description Column, Table 62 (76)12/10—Rev. 0 to Rev. AChanges to Features, Applications, and General Description.....1 Change to CPRSET Pin Resistor Parameter in Table 1................4 Change to P = 2 DM (2/3) Parameter in Table 2..........................5 Changes to Table 4............................................................................6 Changes to V CP Supply Parameter in Table 17.............................14 Change to θJA Value and Endnote in Table 19.............................16 Added Exposed Paddle Notation to Figure 6; Changes toTable 20.............................................................................................17 Added Figure 41; Renumbered Sequentially...............................24 Change to High Frequency Clock Distribution—CLK orExternal VCO > 1600 MHz Section; Change to Table 22..........27 Changes to Table 24........................................................................29 Change to Configuration and Register Settings Section............31 Change to Phase Frequency Detector (PFD) Section................32 Changes to Charge Pump (CP), On-Chip VCO, PLLExternal Loop Filter, and PLL Reference Inputs Sections.........33 Change to Figure 47; Added Figure 48.........................................33 Changes to Reference Switchover and VCXO/VCOFeedback Divider N—P , A, B, R Sections....................................34 Changes to Table 28........................................................................35 Change to Holdover Section..........................................................37 Changes to VCO Calibration Section...........................................39 Changes to Clock Distribution Section........................................40 Added Endnote to Table 34...........................................................41 Changes to Channel Dividers—LVDS/CMOS OutputsSection; Added Endnote to Table 39............................................43 Changes to Write Section...............................................................50 Change to the Instruction Word (16 Bits) Section.....................51 Change to Figure 65........................................................................52 Added Thermal Performance Section..........................................54 Changes to Register Address 0x003 in Table 52..........................55 Changes to Table 53........................................................................59 Changes to Table 54........................................................................60 Changes to Table 55........................................................................66 Changes to Table 56........................................................................68 Changes to Table 57........................................................................71 Changes to Table 58........................................................................73 Changes to Table 59........................................................................74 Changes to Table 60 and Table 61.................................................76 Added Frequency Planning Using the AD9516 Section............77 Changes to Figure 71 and Figure 73; Added Figure 72..............78 Changes to LVPECL Clock Distribution and LVDS ClockDistribution Sections......................................................................78 Updated Outline Dimensions.. (80)4/07—Revision 0: Initial VersionAD9516-1Data SheetRev. B | Page 4 of 80SPECIFICATIONSTypical is given for V S = V S_LVPECL = 3.3 V ± 5%; V S ≤ V CP ≤ 5.25 V; T A = 25°C; R SET = 4.12 kΩ; CP RSET = 5.1 kΩ, unless otherwise noted. Minimum and maximum values are given over full V S and T A (−40°C to +85°C) variation.POWER SUPPLY REQUIREMENTSTable 1.Parameter Min Typ Max Unit Test Conditions/Comments V S 3.135 3.3 3.465 V 3.3 V ± 5% V S_LVPECL 2.375 V S V Nominally 2.5 V to 3.3 V ± 5% V CP V S 5.25 V Nominally 3.3 V to 5.0 V ± 5% RSET Pin Resistor 4.12 kΩ Sets internal biasing currents; connect to ground CPRSET Pin Resistor 2.7 5.1 10 kΩ Sets internal CP current range, nominally 4.8 mA (CP_lsb = 600 μA);actual current can be calculated by: CP_lsb = 3.06/CPRSET; connect to groundBYPASS Pin Capacitor 220 nF Bypass for internal LDO regulator; necessary for LDO stability;connect to groundPLL CHARACTERISTICSData SheetAD9516-1Rev. B | Page 5 of 80Parameter Min Typ Max Unit Test Conditions/Comments CHARGE PUMP (CP) I CP Sink/Source Programmable High Value 4.8 mA With CP RSET = 5.1 kΩ Low Value 0.60 mA Absolute Accuracy 2.5 % CP V = V CP /2 CP RSET Range 2.7/10 kΩ I CP High Impedance Mode Leakage 1 nA Sink-and-Source Current Matching 2 % 0.5 < CP V < V CP − 0.5 V I CP vs. CP V 1.5 % 0.5 < CP V < V CP − 0.5 V I CP vs. Temperature 2 % CP V = V CP /2 PRESCALER (PART OF N DIVIDER) See the VCXO/VCO Feedback Divider N—P , A, B, R section Prescaler Input Frequency P = 1 FD 300 MHz P = 2 FD 600 MHz P = 3 FD 900 MHz P = 2 DM (2/3) 200 MHz P = 4 DM (4/5) 1000 MHz P = 8 DM (8/9) 2400 MHz P = 16 DM (16/17) 3000 MHz P = 32 DM (32/33) 3000 MHz Prescaler Output Frequency 300 MHz A, B counter input frequency (prescaler input frequency dividedby P)PLL DIVIDER DELAYS Register 0x019: R, Bits[5:3]; N, Bits[2:0]; see Table 54 000 Off ps 001 330 ps 010 440 ps 011 550 ps 100 660 ps 101 770 ps 110 880 ps 111 990 ps NOISE CHARACTERISTICS In-Band Phase Noise of the Charge Pump/Phase Frequency Detector (In-Band Is Within the LBW of the PLL) The PLL in-band phase noise floor is estimated by measuring the in-band phase noise at the output of the VCO and subtracting 20log(N) (where N is the value of the N divider) At 500 kHz PFD Frequency −165 dBc/Hz At 1 MHz PFD Frequency −162 dBc/Hz At 10 MHz PFD Frequency −151 dBc/Hz At 50 MHz PFD Frequency −143 dBc/Hz PLL Figure of Merit (FOM) −220 dBc/Hz Reference slew rate > 0.25 V/ns; FOM +10log (f PFD ) is an approxi-mation of the PFD/CP in-band phase noise (in the flat region)inside the PLL loop bandwidth; when running closed-loop, the phase noise, as observed at the VCO output, is increased by 20log(N)PLL DIGITAL LOCK DETECT WINDOW 2Signal available at LD, STATUS, and REFMON pins when selectedby appropriate register settingsRequired to Lock (Coincidence of Edges) Selected by Register 0x017[1:0] and Register 0x018[4] Low Range (ABP 1.3 ns, 2.9 ns) 3.5 ns Register 0x017[1:0] = 00b, 01b,11b; Register 0x018[4] = 1b High Range (ABP 1.3 ns, 2.9 ns) 7.5 ns Register 0x017[1:0] = 00b, 01b, 11b; Register 0x018[4] = 0b High Range (ABP 6.0 ns) 3.5 ns Register 0x017[1:0] = 10b; Register 0x018[4] = 0bTo Unlock After Lock (Hysteresis)2Low Range (ABP 1.3 ns, 2.9 ns) 7 ns Register 0x017[1:0] = 00b, 01b, 11b; Register 0x018[4] = 1b High Range (ABP 1.3 ns, 2.9 ns) 15 ns Register 0x017[1:0] = 00b, 01b, 11b; Register 0x018[4] = 0b High Range (ABP 6.0 ns) 11 ns Register 0x017[1:0] = 10b; Register 0x018[4] = 0b1 REFIN and REFIN self-bias points are offset slightly to avoid chatter on an open input condition.2For reliable operation of the digital lock detect, the period of the PFD frequency must be greater than the unlock-after-lock time.AD9516-1 Data Sheet CLOCK INPUTS1 Below about 1 MHz, the input should be dc-coupled. Care should be taken to match V CM.CLOCK OUTPUTSRev. B | Page 6 of 80Data SheetAD9516-1Rev. B | Page 7 of 80TIMING CHARACTERISTICSTable 5.Parameter Min Typ Max Unit Test Conditions/Comments LVPECLTermination = 50 Ω to V S − 2 V; level = 810 mV Output Rise Time, t RP 70 180 ps 20% to 80%, measured differentially Output Fall Time, t FP70 180 ps 80% to 20%, measured differentially PROPAGATION DELAY, t PECL , CLK-TO-LVPECL OUTPUT High Frequency Clock Distribution Configuration 835 995 1180 ps See Figure 43 Clock Distribution Configuration 773 933 1090 ps See Figure 45 Variation with Temperature 0.8 ps/°C OUTPUT SKEW, LVPECL OUTPUTS 1LVPECL Outputs That Share the Same Divider 5 15 ps LVPECL Outputs on Different Dividers 13 40 ps All LVPECL Outputs Across Multiple Parts 220 ps LVDSTermination = 100 Ω differential; 3.5 mA Output Rise Time, t RL 170 350 ps 20% to 80%, measured differentially 2 Output Fall Time, t FL160 350 ps 20% to 80%, measured differentially 2 PROPAGATION DELAY, t LVDS , CLK-TO-LVDS OUTPUT Delay off on all outputs OUT6, OUT7, OUT8, OUT9 For All Divide Values1.4 1.82.1 ns Variation with Temperature 1.25 ps/°C OUTPUT SKEW, LVDS OUTPUTS 1Delay off on all outputs LVDS Outputs That Share the Same Divider 6 62 ps LVDS Outputs on Different Dividers 25 150 ps All LVDS Outputs Across Multiple Parts 430 ps CMOSTermination = open Output Rise Time, t RC 495 1000 ps 20% to 80%; C LOAD = 10 pF Output Fall Time, t FC475 985 ps 80% to 20%; C LOAD = 10 pF PROPAGATION DELAY, t CMOS , CLK-TO-CMOS OUTPUT Fine delay off For All Divide Values1.62.1 2.6 ns Variation with Temperature2.6 ps/°C OUTPUT SKEW, CMOS OUTPUTS 1F ine delay off CMOS Outputs That Share the Same Divider 4 66 ps All CMOS Outputs on Different Dividers 28 180 ps All CMOS Outputs Across Multiple Parts 675 ps DELAY ADJUST 3LVDS and CMOS Shortest Delay Range 4 Register 0xA1 (0xA4, 0xA7, 0xAA), Bits[5:0] = 101111b Zero Scale 50 315 680 ps Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 000000b Full Scale540 880 1180 ps Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 101111b Longest Delay Range 4 Register 0xA1 (0xA4, 0xA7, 0xAA), Bits[5:0] = 000000b Zero Scale 200 570 950 ps Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 000000b Quarter Scale 1.72 2.31 2.89 ns Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 001100b Full Scale5.7 8.0 10.1 ns Register 0xA2 (0xA5, 0xA8, 0xAB), Bits[5:0] = 101111b Delay Variation with Temperature Short Delay Range 5 Zero Scale 0.23 ps/°C Full Scale−0.02 ps/°C Long Delay Range 5 Zero Scale 0.3 ps/°C Full Scale0.24 ps/°C1 This is the difference between any two similar delay paths while operating at the same voltage and temperature. 2Corresponding CMOS drivers set to A for noninverting and B for inverting. 3The maximum delay that can be used is a little less than one-half the period of the clock. A longer delay disables the output. 4Incremental delay; does not include propagation delay. 5All delays between zero scale and full scale can be estimated by linear interpolation.AD9516-1Data SheetRev. B | Page 8 of 80CLOCK OUTPUT ADDITIVE PHASE NOISE (DISTRIBUTION ONLY; VCO DIVIDER NOT USED)Table 6.Parameter Min Typ Max Unit Test Conditions/Comments CLK-TO-LVPECL ADDITIVE PHASE NOISE Distribution section only; does not include PLL and VCO CLK = 1 GHz, Output = 1 GHz Input slew rate > 1 V/ns Divider = 1 At 10 Hz Offset −109 dBc/Hz At 100 Hz Offset −118 dBc/Hz At 1 kHz Offset −130 dBc/Hz At 10 kHz Offset −139 dBc/Hz At 100 kHz Offset −144 dBc/Hz At 1 MHz Offset −146 dBc/Hz At 10 MHz Offset −147 dBc/Hz At 100 MHz Offset −149 dBc/Hz CLK = 1 GHz, Output = 200 MHz Input slew rate > 1 V/ns Divider = 5 At 10 Hz Offset −120 dBc/Hz At 100 Hz Offset −126 dBc/Hz At 1 kHz Offset −139 dBc/Hz At 10 kHz Offset −150 dBc/Hz At 100 kHz Offset −155 dBc/Hz At 1 MHz Offset −157 dBc/Hz >10 MHz Offset −157 dBc/Hz CLK-TO-LVDS ADDITIVE PHASE NOISE Distribution section only; does not include PLL and VCO CLK = 1.6 GHz, Output = 800 MHz Input slew rate > 1 V/ns Divider = 2 At 10 Hz Offset −103 dBc/Hz At 100 Hz Offset −110 dBc/Hz At 1 kHz Offset −120 dBc/Hz At 10 kHz Offset −127 dBc/Hz At 100 kHz Offset −133 dBc/Hz At 1 MHz Offset −138 dBc/Hz At 10 MHz Offset −147 dBc/Hz At 100 MHz Offset −149 dBc/Hz CLK = 1.6 GHz, Output = 400 MHz Input slew rate > 1 V/ns Divider = 4 At 10 Hz Offset −114 dBc/Hz At 100 Hz Offset −122 dBc/Hz At 1 kHz Offset −132 dBc/Hz At 10 kHz Offset −140 dBc/Hz At 100 kHz Offset −146 dBc/Hz At 1 MHz Offset −150 dBc/Hz >10 MHz Offset −155 dBc/Hz CLK-TO-CMOS ADDITIVE PHASE NOISE Distribution section only; does not include PLL and VCO CLK = 1 GHz, Output = 250 MHz Input slew rate > 1 V/ns Divider = 4 At 10 Hz Offset −110 dBc/Hz At 100 Hz Offset −120 dBc/Hz At 1 kHz Offset −127 dBc/Hz At 10 kHz Offset −136 dBc/Hz At 100 kHz Offset −144 dBc/Hz At 1 MHz Offset −147 dBc/Hz >10 MHz Offset −154 dBc/HzData SheetAD9516-1Rev. B | Page 9 of 80Parameter Min Typ Max Unit Test Conditions/Comments CLK = 1 GHz, Output = 50 MHz Input slew rate > 1 V/ns Divider = 20 At 10 Hz Offset −124 dBc/Hz At 100 Hz Offset −134 dBc/Hz At 1 kHz Offset −142 dBc/Hz At 10 kHz Offset −151 dBc/Hz At 100 kHz Offset −157 dBc/Hz At 1 MHz Offset −160 dBc/Hz >10 MHz Offset −163 dBc/HzCLOCK OUTPUT ABSOLUTE PHASE NOISE (INTERNAL VCO USED)Table 7.Parameter Min Typ Max Unit Test Conditions/Comments LVPECL ABSOLUTE PHASE NOISE Internal VCO; direct to LVPECL output VCO = 2.65 GHz; Output = 2.65 GHz At 1 kHz Offset −46 dBc/Hz At 10 kHz Offset −76 dBc/Hz At 100 kHz Offset −104 dBc/Hz At 1 MHz Offset −123 dBc/Hz At 10 MHz Offset −140 dBc/Hz At 40 MHz Offset −146 dBc/Hz VCO = 2.475 GHz; Output = 2.475 GHz At 1 kHz Offset −47 dBc/Hz At 10 kHz Offset −77 dBc/Hz At 100 kHz Offset −105 dBc/Hz At 1 MHz Offset −124 dBc/Hz At 10 MHz Offset −141 dBc/Hz At 40 MHz Offset −146 dBc/Hz VCO = 2.3 GHz; Output = 2.3 GHz At 1 kHz Offset −54 dBc/Hz At 10 kHz Offset −78 dBc/Hz At 100 kHz Offset −106 dBc/Hz At 1 MHz Offset −125 dBc/Hz At 10 MHz Offset −141 dBc/Hz At 40 MHz Offset −146 dBc/HzAD9516-1Data SheetRev. B | Page 10 of 80CLOCK OUTPUT ABSOLUTE TIME JITTER (CLOCK GENERATION USING INTERNAL VCO)Table 8.Parameter Min Typ Max Unit Test Conditions/Comments LVPECL OUTPUT ABSOLUTE TIME JITTER Application example based on a typicalsetup where the reference source is clean, so a wider PLL loop bandwidth is used; reference = 15.36 MHz; R = 1VCO = 2.46 GHz; LVPECL = 491.52 MHz; PLL LBW = 55 kHz 142 fs rms Integration BW = 200 kHz to 10 MHz 370 fs rms Integration BW = 12 kHz to 20 MHz VCO = 2.46 GHz; LVPECL = 122.88 MHz; PLL LBW = 55 kHz 145 fs rms Integration BW = 200 kHz to 10 MHz 356 fs rms Integration BW = 12 kHz to 20 MHz VCO = 2.46 GHz; LVPECL = 61.44 MHz; PLL LBW = 55 kHz 195 fs rms Integration BW = 200 kHz to 10 MHz 402 fs rms Integration BW = 12 kHz to 20 MHzCLOCK OUTPUT ABSOLUTE TIME JITTER (CLOCK CLEANUP USING INTERNAL VCO)Table 9.Parameter Min Typ Max Unit Test Conditions/Comments LVPECL OUTPUT ABSOLUTE TIME JITTER Application example based on a typicalsetup where the reference source is jittery, so a narrower PLL loop bandwidth is used; reference = 10.0 MHz; R = 20VCO = 2.49 GHz; LVPECL = 622.08 MHz; PLL LBW = 125 Hz 745 fs rms Integration BW = 12 kHz to 20 MHz VCO = 2.49 GHz; LVPECL = 155.52 MHz; PLL LBW = 125 Hz 712 fs rms Integration BW = 12 kHz to 20 MHz VCO = 2.46 GHz; LVPECL = 122.88 MHz; PLL LBW = 125 Hz 700 fs rms Integration BW = 12 kHz to 20 MHzCLOCK OUTPUT ABSOLUTE TIME JITTER (CLOCK GENERATION USING EXTERNAL VCXO)Table 10.Parameter Min Typ Max Unit Test Conditions/Comments LVPECL OUTPUT ABSOLUTE TIME JITTER Application example based on a typicalsetup using an external 245.76 MHz VCXO (Toyocom TCO-2112); reference = 15.36 MHz; R = 1LVPECL = 245.76 MHz; PLL LBW = 125 Hz 54 fs rms Integration BW = 200 kHz to 5 MHz 77 fs rms Integration BW = 200 kHz to 10 MHz 109 fs rms Integration BW = 12 kHz to 20 MHz LVPECL = 122.88 MHz; PLL LBW = 125 Hz 79 fs rms Integration BW = 200 kHz to 5 MHz 114 fs rms Integration BW = 200 kHz to 10 MHz 163 fs rms Integration BW = 12 kHz to 20 MHz LVPECL = 61.44 MHz; PLL LBW = 125 Hz 124 fs rms Integration BW = 200 kHz to 5 MHz 176 fs rms Integration BW = 200 kHz to 10 MHz 259 fs rms Integration BW = 12 kHz to 20 MHz分销商库存信息:ANALOG-DEVICESAD9516-1BCPZ AD9516-1BCPZ-REEL7AD9516-1/PCBZ。

三极管型号

型号功能简述1710 视频信号处理集成电路2274 延迟集成电路2800 红外遥控信号接收集成电路4094 移位寄存串入、并出集成电路4260 动态随机存储集成电路4464 存储集成电路4558 双运算放大集成电路5101 天线开关集成电路15105 充电控制集成电路15551 管理卡升压集成电路31085 射频电源集成电路74122 可重触发单稳态集成电路85712 场扫描信号校正处理集成电路85713 行扫描信号校正集成电路0206A 天线开关集成电路03VFG9 发射压控振荡集成电路1021AC 发射压控振荡集成电路1097C 升压集成电路140N 电源取样比较放大集成电路14DN363 伺服控制集成电路1N706 混响延时集成电路20810-F6096 存储集成电路2252B 微处理集成电路24C01ACEA 存储集成电路24C026 存储集成电路24C04 存储集成电路24C64 码片集成电路24LC16B 存储集成电路24LC65 电可改写编程只读存储集成电路27C1000PC-12 存储集成电路27C2000QC-90 存储集成电路27C20T 存储集成电路27C512 电可改写编程只读存储集成电路28BV64 码片集成电路28F004 版本集成电路32D54 电源、音频信号处理集成电路32D75 电源、音频信号处理集成电路32D92 电源中频放大集成电路4066B 电子开关切换集成电路424260SDJ 存储集成电路4270351/91B9905 中频放大集成电路4370341/90M9919 中频处理集成电路4580D 双运算放大集成电路47C1638AN-U337 微处理集成电路47C1638AU-353 微处理集成电路47C432GP 微处理集成电路47C433AN-3888 微处理集成电路49/4CR1A 中频放大集成电路5G052 发光二极管四位显示驱动集成电路5G24 运算放大集成电路5W01 双运算放大集成电路649/CRIA70612 中频放大集成电路673/3CR2A 多模转换集成电路74HC04 逻辑与非门集成电路74HC04D 六反相集成电路74HC123 单稳态集成电路74HC125 端口功能扩展集成电路74HC14N 六反相集成电路74HC157A 多路转换集成电路74HC165 移相寄存集成电路74HC245 总线收发集成电路74HC32 或门四2输入集成电路74HC374八D 触发集成电路74HC573D 存储集成电路74HCT157 多路转换双输入集成电路74HCT4046A 压控振荡集成电路74HCT4538D 单稳态集成电路74HCT4538N 触发脉冲集成电路74HCT86D 异或门四2输入集成电路74HCU04 与非门集成电路74LS125 端口功能扩展集成电路74LS373 锁存集成电路74LS393 计数双四位二进制集成电路74LS74双D 触发集成电路78014DFP 系统控制处理集成电路811N 伴音阻容偏置集成电路83D33 压控振荡集成电路87C52 微处理集成电路87CK38N-3584 微处理集成电路87CK38N-3627 微处理集成电路89C52 系统控制处理集成电路89C55 系统控制处理集成电路93C66 电可改写编程只读存储集成电路93LC56 电可改写编程存储集成电路9821K03 系统控制集成电路A1642P 背景歌声消除集成电路A701 红外遥控信号接收集成电路A7950 场频识别集成电路A8772AN 色差信号延迟处理集成电路A9109 功率放大集成电路AAB 电源集成电路ACA650 色度信号解调集成电路ACFP2 色度、亮度信号分离集成电路ACP2371 多伴音、多语言改善集成电路ACVP2205 色度、亮度信号分离集成电路AD1853 立体声数/模转换集成电路AD1858 音频解调集成电路AD722 视频编码集成电路ADC2300E 音频数/模转换集成电路ADC2300J 音频数/模转换集成电路ADC2310E 音频数/模转换集成电路ADV7172 视频编码集成电路ADV7175A 视频编码集成电路AE31201 频率显示集成电路AJ7080 射频调制集成电路AK4321-VF-E1 音频数/模转换集成电路AN1319 双高速电压比较集成电路AN1358S 双运算放大集成电路AN1393 双运算放大集成电路AN1431T 稳压电源集成电路AN1452 音频前置放大集成电路AN1458S 双运算放大集成电路AN206 伴音中频及前置放大集成电路AN222 自动频率控制集成电路AN236 副载波信号处理集成电路AN239Q 图像、伴音中频放大集成电路AN247P 图像中频放大、AGC控制集成电路AN253P 调频/调幅中频放大集成电路AN262 音频前置放大集成电路AN2661NK 视频信号处理集成电路AN2663K 视频信号处理集成电路AN272 音频功率放大集成电路AN2751FAP 视频信号处理集成电路AN281 色度解码集成电路AN2870FC 多功能控制集成电路AN295 行、场扫描信号处理集成电路AN301 伺服控制集成电路AN305 视频自动增益控制集成电路AN306 色度自动相位控制集成电路AN318 直流伺服控制集成电路AN320 频率控制、调谐显示驱动集成电路AN3215K 视频信号处理集成电路AN3215S 视频信号处理集成电路AN3224K 磁头信号记录放大集成电路AN3248NK 亮度信号记录、重放处理集成电路AN331 视频信号处理集成电路AN3311K 磁头信号放大集成电路AN3313 磁头信号放大集成电路AN3321S 录像重放信号处理集成电路AN3331K 磁头信号处理集成电路AN3337NSB 磁头信号放大集成电路AN3380K 磁头信号处理集成电路AN3386NK 磁头信号处理集成电路AN3495K 色度、亮度信号降噪集成电路AN355 伴音中频放大、检波集成电路AN3581S 视频驱动集成电路AN366 调频/调幅中频放大集成电路AN3791 移位控制集成电路AN3792 磁鼓伺服控制接口集成电路AN3795 主轴伺服控制接口集成电路AN3814K 电机驱动集成电路AN4265 音频功率放大集成电路AN4558 运算放大集成电路AN5010 电子选台集成电路AN5011 电子选台集成电路AN5015K 电子选台集成电路AN5020 红外遥控信号接收集成电路AN5025S 红外遥控信号接收集成电路AN5026K 红外遥控信号接收集成电路AN5031 电调谐控制集成电路AN5034 调谐控制集成电路AN5036 调谐控制集成电路AN5043 调谐控制集成电路AN5071 频段转换集成电路AN5095K 电视信号处理集成电路AN5110 图像中频放大集成电路AN5130 图像中频、视频检波放大集成电路AN5138NK 图像、伴音中频放大集成电路AN5156K 电视信号处理集成电路AN5177NK 图像、伴音中频放大集成电路AN5179K 图像、伴音中频放大集成电路AN5183K 中频信号处理集成电路AN5195K 中频、色度、扫描信号处理集成电路AN5215 伴音信号处理集成电路AN5222 伴音中频放大集成电路AN5250 伴音中频放大、鉴频及功率放大集成电路AN5262 音频前置放大集成电路AN5265 音频功率放大集成电路AN5270 音频功率放大集成电路AN5273 双声道音频功率放大集成电路AN5274 双声道音频功率放大集成电路AN5275 中置、3D放大集成电路AN5285K 双声道前置放大集成电路AN5295NK 音频信号切换集成电路AN5312 视频、色度信号处理集成电路AN5313NK 视频、色度信号处理集成电路AN5342 图像水平轮廓校正集成电路AN5342FB 水平清晰度控制集成电路AN5344FBP 色度信号处理集成电路AN5348K 人工智能信号处理集成电路AN5385K 色差信号放大集成电路AN5410 行、场扫描信号处理集成电路AN5421 同步检测集成电路AN5422 行、场扫描信号处理集成电路AN5512 场扫描输出集成电路AN5515 场扫描输出集成电路AN5520 伴音中频放大及鉴频集成电路AN5521 场扫描输出集成电路AN5532 场扫描输出集成电路AN5534 场扫描输出集成电路AN5551 枕形校正集成电路AN5560 场频识别集成电路AN5600K 中频、亮度、色度及扫描信号处理集成电路AN5601K 视频、色度、同步信号处理集成电路AN5607K 视频、色度、行场扫描信号处理集成电路AN5615 视频信号处理集成电路AN5620X 色度信号处理集成电路AN5621 场扫描输出集成电路AN5625 色度信号处理集成电路AN5633K 色度信号处理集成电路AN5635 色度解码集成电路AN5635NS 色度解码集成电路AN5637 色度解码、亮度延迟集成电路AN5650 同步信号分离集成电路AN5682K 基色电子开关切换集成电路AN5693K 视频、色度、行场扫描信号处理集成电路AN5712 图像中频放大、AGC控制集成电路AN5722 图像中频放大、检波集成电路AN5732 伴音中频放大、鉴频集成电路AN5743 音频功率放大集成电路AN5750 行自动频率控制及振荡集成电路AN5757S 行扫描电源电压控制集成电路AN5762 场扫描振荡、输出集成电路AN5764 光栅水平位置控制集成电路AN5765 电源稳压控制集成电路AN5767 同步信号处理集成电路AN5768 光栅倾斜校正控制集成电路AN5769 行、场会聚控制集成电路AN5790N 行扫描信号处理集成电路AN5791 同步脉冲相位与脉宽调整集成电路AN5803 双声道立体声解调集成电路AN5836 双声道前置放大集成电路AN5858K 视频信号控制集成电路AN5862 视频信号控制集成电路AN5862S-E1 视频信号开关控制集成电路AN5870K 模拟信号切换集成电路AN5891K 音频信号处理集成电路AN614 行枕形校正集成电路AN6210 双声道前置放大集成电路AN6306S 亮度信号处理集成电路AN6308 模拟电子开关集成电路AN6327 视频重放信号处理集成电路AN6341N 伺服控制集成电路AN6342N 基准分频集成电路AN6344 伺服控制集成电路AN6345 分频集成电路AN6346N 磁鼓伺服控制集成电路AN6350 磁鼓伺服控制集成电路AN6357N 主轴接口集成电路AN6361N 色度信号处理集成电路AN6367NK 色度信号处理集成电路AN6371S 自动相位控制集成电路AN6387 电机伺服控制集成电路AN6550 卡拉OK音频放大集成电路AN6554 四运算放大集成电路AN6561 双运算放大集成电路AN6562SG 双运算放大集成电路AN6609N 电机驱动集成电路AN6612 电机稳速控制集成电路AN6650 电机速度控制集成电路AN6651 电机速度控制集成电路AN6652 电机稳速控制集成电路AN6875 发光二极管五位显示驱动集成电路AN6877 发光二极管七位显示驱动集成电路AN6884 发光二极管五位显示驱动集成电路AN6886 发光二极管五位显示驱动集成电路AN6888 发光二极管显示驱动集成电路AN6914 双电压比较集成电路AN7085N5 单片录、放音集成电路AN7105 双声道音频功率放大集成电路AN7106K 双声道音频功率放大集成电路AN7108 单片立体声放音集成电路AN710S 单片放音集成电路AN7110E 音频功率放大集成电路AN7114 音频功率放大集成电路AN7116 音频功率放大集成电路AN7118 双声道音频功率放大集成电路AN7118S 双声道音频功率放大集成电路AN7120 音频功率放大集成电路AN7124 双声道音频功率放大集成电路AN7145 双声道音频功率放大集成电路AN7148 双声道音频功率放大集成电路AN7158N 音频功率放大7.5W×2集成电路AN7161N 音频功率放大集成电路AN7164 双声道音频功率放大集成电路AN7171NK 音频功率放大集成电路AN7205 调频/调谐及高频放大集成电路AN7220 调频/调幅中频放大集成电路AN7222 调频/调幅中频放大集成电路AN7223 调频/调幅中频放大集成电路AN7226 调频/调幅中频放大集成电路AN7256 调频/调谐及中频放大集成电路AN7311 双声道前置放大集成电路AN7312 双声道前置放大集成电路AN7315 双声道前置放大集成电路AN7315S 双声道前置放大集成电路AN7320 音频前置放大集成电路AN7396K 双声道前置放大集成电路AN7397K 双声道前置放大集成电路AN7410 调频立体声多路解码集成电路AN7414 调频立体声解码集成电路AN7420N 调频立体声解码集成电路AN7470 调频立体声解码集成电路AN7805 三端电源稳压+5V/1A集成电路AN7806 三端电源稳压+6V/1A集成电路AN7807 三端电源稳压+7V/1A集成电路AN7808 三端电源稳压+8V/1A集成电路AN7809 电源稳压+9V/1A集成电路AN7810 三端电源稳压+10V/1A集成电路AN7812 三端电源稳压+12V/1A集成电路AN7815 三端电源稳压+15V/1A集成电路AN7818 三端电源稳压+18V/1A集成电路AN7820 三端电源稳压+20V/1A集成电路AN7824 三端电源稳压+24V/1A集成电路AN78L05 三端电源稳压+5V/0.1A集成电路AN78L06 三端电源稳压+6V/0.1A集成电路AN78L08 三端电源稳压+8V/0.1A集成电路AN78L09 三端电源稳压+9V/0.1A集成电路AN78L10 三端电源稳压+10V/0.1A集成电路AN78L12 三端电源稳压+12V/0.1A集成电路AN78L15 三端电源稳压+15V/0.1A集成电路AN78L18 三端电源稳压+18V/0.1A集成电路AN78L20 三端电源稳压+20V/0.1A集成电路AN78L24 三端电源稳压+24V/0.1A集成电路AN78M05 三端电源稳压+5V/0.5A集成电路AN78M06 三端电源稳压+6V/0.5A集成电路AN78M08 三端电源稳压+8V/0.5A集成电路AN78M09 三端电源稳压+9V/0.5A集成电路AN78M10 三端电源稳压+10V/0.5A集成电路AN78M12 三端电源稳压+12V/0.5A集成电路AN78M15 三端固定式稳压+15V/0.5A集成电路AN78M18 三端电源稳压+18V/0.5A集成电路AN78M20 三端电源稳压+20V/0.5A集成电路AN78M24 三端电源稳压+24V/0.5A集成电路AN7905 三端电源稳压-5V/1A集成电路AN7906 三端电源稳压-6V/1A集成电路AN7908T 三端电源稳压-8V/1A集成电路AN7909T 三端电源稳压-9V/1A集成电路AN7910T 三端电源稳压-10V/1A集成电路AN7912 三端电源稳压-12V/1A集成电路AN7915 三端电源稳压-15V/1A集成电路AN7918 三端电源稳压-18V/1A集成电路AN7920 三端电源稳压-20V/1A集成电路AN7924 三端电源稳压-24V/1A集成电路AN79L05 三端电源稳压-5V/0.1A集成电路AN79L06 三端电源稳压-6V/0.1A集成电路AN79L08 三端电源稳压-8V/0.1A集成电路AN79L09 三端电源稳压-9V/0.1A集成电路AN79L10 三端电源稳压-10V/0.1A集成电路AN79L12 三端电源稳压-12V/0.1A集成电路AN79L15 三端电源稳压-15V/0.1A集成电路AN79L18 三端电源稳压-18V/0.1A集成电路AN79L20 三端电源稳压-20V/0.1A集成电路AN79L24 三端电源稳压-24V/0.1A集成电路AN79M05 三端电源稳压-5V/0.5A集成电路AN79M06 三端电源稳压-6V/0.5A集成电路AN79M08 三端电源稳压-8V/0.5A集成电路AN79M09 三端电源稳压-9V/0.5A集成电路AN79M10 三端电源稳压-10V/0.5A集成电路AN79M12 三端电源稳压-12V/0.5A集成电路AN79M15 三端电源稳压-15V/0.5A集成电路AN79M18 三端电源稳压-18V/0.5A集成电路AN79M20 三端电源稳压-20V/0.5A集成电路AN79M24 三端电源稳压-24V/0.5A集成电路AN8028 自激式开关电源控制集成电路AN8270K 主轴电机控制集成电路AN8280 电机驱动集成电路AN8281S 电机驱动集成电路AN8290S 主轴电机驱动集成电路AN8355S 条形码扫描接收集成电路AN8370S 光电伺服控制集成电路AN8373S 射频伺服处理集成电路AN8375S 伺服处理集成电路AN8389S-E1 电机驱动集成电路AN8480NSB 主轴电机驱动集成电路AN8481SB-E1 主轴电机驱动集成电路AN8482SB 主轴电机驱动集成电路AN8623FBQ 主轴伺服处理集成电路AN8788FB 电机驱动集成电路AN8802CE1V 伺服处理集成电路AN8813NSBS 主轴电机驱动集成电路AN8819NFB 伺服驱动、直流交换集成电路AN8824FBQ 前置放大集成电路AN8825NFHQ-V 聚焦、循迹误差处理集成电路AN8831SC 视频预视放集成电路AN8832SB-E1 射频放大、伺服处理集成电路AN8837SB-E1 伺服处理集成电路AN89C2051-24PC 微处理集成电路APU2400U 音频信号处理集成电路APU2470 音频信号处理集成电路AS4C14405-60JC 动态随机存储1M×4集成电路AS4C256K16ED-60JC 存储集成电路ASD0204-015 图文控制集成电路ASD0204GF 显示控制集成电路AT24C08 存储集成电路AT24C256-10CI 码片集成电路AT27C010 电可改写编程只读存储集成电路AT27C020 存储集成电路ATMEL834 存储集成电路AVM-1 视频信号处理厚膜集成电路AVM-2 音频信号处理厚膜集成电路AVSIBCP08 倍压整流切换集成电路B0011A 存储集成电路B1218 电子快门控制集成电路BA033T 三端电源稳压+3.3V集成电路BA10324 四运算放大集成电路BA10393N 双运算放大集成电路BA1102F 杜比降噪处理集成电路BA1106F 杜比降噪处理集成电路BA12ST 电源稳压集成电路BA1310 调频立体声解码集成电路BA1332L 调频立体声解码集成电路BA1350 调频立体声解码集成电路BA1351 调频立体声解码集成电路BA1356 调频立体声解码集成电路BA1360 调频立体声解码集成电路BA15218N 双运算放大集成电路BA225 可触发双单稳态振荡集成电路BA302 音频前置放大集成电路BA311 音频前置放大集成电路BA313 音频前置放大集成电路BA3283 单片放音集成电路BA328F 双声道前置放大集成电路BA329 双声道前置放大集成电路BA3304F 录放音前置均衡放大集成电路BA3306 音频、前置放大集成电路BA3312N 话筒信号前置放大集成电路BA3313L 自动音量控制集成电路BA3314 话筒信号前置放大集成电路BA335 自动选曲集成电路BA340 音频前置放大集成电路BA3402F 双声道前置放大集成电路BA3404F 自返转放音集成电路BA3416BL 双声道前置放大集成电路BA343 双声道前置放大集成电路BA3503F 双声道前置放大集成电路BA3506 单片放音集成电路BA3513FS 单片放音集成电路BA3516 单片放音集成电路BA3706 自动选曲集成电路BA3707 录音带曲间检测集成电路BA3812L 五频段音调补偿集成电路BA3818F 电压比较运放集成电路BA3822LS 双声道五频段显示均衡集成电路BA3828 电子选台预置集成电路BA3880 音频处理集成电路BA401 调频中频放大集成电路BA402 调频中频放大集成电路BA4110 调频中频放大集成电路BA4234L 调频中频放大集成电路BA4402 调频调谐收音集成电路BA4403 调频高频放大、混频、本振集成电路BA4560 双运算放大集成电路BA5096 数字混响集成电路BA5102A 音频功率放大集成电路BA514 音频功率放大集成电路BA516 音频功率放大集成电路BA5208AF 音频功率放大集成电路BA532 音频功率放大集成电路BA534 音频功率放大集成电路BA5406 双声道音频功率放大集成电路BA5412 音频功率放大集成电路BA547 音频功率放大1.5W集成电路BA5912AFP-YE2 电机驱动、倾斜、加载集成电路BA5981FP-E2 聚焦、循迹驱动集成电路BA5983FB 四通道伺服驱动集成电路BA5983FM-E2 电机驱动集成电路BA6104 发光二极管五位显示驱动集成电路BA6107A 电机伺服控制集成电路BA6109 加载电机驱动集成电路BA6125 发光二极管五位显示驱动集成电路BA6137 发光二极管五位显示驱动集成电路BA6191 音频控制集成电路BA6196FP 伺服驱动集成电路BA6208 电机驱动集成电路BA6208D 电机驱动集成电路BA6209 电机驱动集成电路BA6209N 双向驱动电机集成电路BA6209U 电机双向驱动集成电路BA6218 加载电机驱动集成电路BA6219 电机驱动集成电路BA6219B 电机驱动集成电路BA6227 电机稳速控制集成电路BA6238 电机驱动集成电路BA6239 电机双向驱动集成电路BA6239A 电机双向驱动集成电路BA6246M 加载、转盘电机驱动集成电路BA6248 电机驱动集成电路BA6286 电机驱动集成电路BA6287 电机驱动集成电路BA6290 电机驱动集成电路BA6295AFP-E2 加载、倾斜驱动集成电路BA6296FP 电机速度控制集成电路BA6297AFP 伺服驱动集成电路BA6302A 电机伺服控制集成电路BA6305 控制放大集成电路BA6305F 控制放大集成电路BA6308 电子开关切换集成电路BA6321 电机伺服控制集成电路BA6392 伺服驱动集成电路BA6395 主轴电机驱动集成电路BA6396FP 伺服驱动集成电路BA6411 电机驱动集成电路BA6435S 主轴电机驱动集成电路BA6459P1 电机驱动集成电路BA6570FP-E2 聚焦、循迹驱动集成电路BA6664FM 三相主电机驱动集成电路BA6791FP 四通道伺服驱动集成电路BA6796FP 电机驱动集成电路BA6810S 音频显示驱动集成电路BA6844AFP-E2 三相主电机驱动集成电路BA6849FP 主轴电机驱动集成电路BA689 发光二极管十二位显示驱动集成电路BA6893KE2 直流变换驱动集成电路BA6956AN 加载电机驱动集成电路BA6993 双运算放大集成电路BA7001 音频切换集成电路BA7004 测试信号发生集成电路BA7005AL 射频调制集成电路BA7007 信号检测集成电路BA7021 视频信号选择集成电路BA7024 视频信号测试集成电路BA7025L 信号检测集成电路BA7042 振荡集成电路BA7047 调频检波集成电路BA7048N 包络信号检测集成电路BA7106LS 检测信号控制集成电路BA7180FS 磁头信号放大集成电路BA7212S 磁头信号放大集成电路BA7253S 磁头信号放大集成电路BA7254S 四磁头信号放大集成电路BA7258AS 亮度信号处理集成电路BA7264S 视频信号处理集成电路BA7274S 磁头信号放大集成电路BA7357S 中频放大集成电路BA7604N 电子开关切换集成电路BA7606F 色差信号切换集成电路BA7665FS-E2 视频输出放大集成电路BA7725FS 混响立体声放大集成电路BA7725S 信号压缩及扩展处理集成电路BA7743FS 磁头信号放大集成电路BA7751ALS 音频信号录放处理集成电路BA7752LS 音频信号处理集成电路BA7755 磁头开关集成电路BA7755AF-E2 磁头开关集成电路BA7765AS 音频信号处理集成电路BA7766SA 音频信号处理集成电路BA7767AS 音频信号处理集成电路BA7797F 音频信号处理集成电路BA8420 特技控制处理集成电路BAL6309 场同步信号发生集成电路BH3866AS 音频、色度信号前置放大集成电路BH4001 微处理集成电路BH7331P 音频功率放大集成电路BH7770KS 音频信号处理集成电路BL3207 亮度延时集成电路BL3208B 音频延迟混响集成电路BL5132 中频放大集成电路BL54573 电子调频波段转换集成电路BL5612 视频放大、色差矩阵集成电路BM5060 微处理集成电路BM5061 字符发生集成电路BM5069 微处理集成电路BN5115 图像中频放大集成电路BOC31F 单片微处理集成电路BP5020 视频电源转换集成电路BT852 视频编码集成电路BT864 视频编码集成电路BT866PQFP 微处理集成电路BU12102 时序信号发生解码集成电路BU2092F 扩展集成电路BU2185F 同步信号处理集成电路BU2820 伺服控制集成电路BU2841FS 视频、蓝背景信号发生集成电路BU2872AK 操作系统控制、屏显驱动集成电路BU3762AF 红外遥控信号发射集成电路BU4053B 电子开关切换集成电路BU5814F 红外遥控信号发射集成电路BU5994F 红外遥控信号发射集成电路BU6198F 屏幕显示集成电路BU9252F 音频延时集成电路BU9252S 数/模转换集成电路BU9253FS 话筒音频混响集成电路BX1303 音频功率放大集成电路BX1409 红外遥控信号接收集成电路BX7506 主轴电机电源控制集成电路C1363CA 红外遥控电子选台集成电路C1490HA 红外遥控信号接收集成电路C187 分配、十进制计数集成电路C301 译码BCD-10段集成电路C68639Y 微处理集成电路C75P036 微处理集成电路CA0002 调幅模拟声解调集成电路CA2004 音频功率放大集成电路CA2006 音频功率放大集成电路CA270AW 视频检波放大集成电路CA3075 调频中频放大集成电路CA3089 调频中频放大集成电路CA3120E 视频信号处理集成电路CA3140 运算放大集成电路CA810 音频功率放大集成电路CA920 行扫描信号处理集成电路CAS126 天线开关集成电路CAT24C16 电可改写编程只读存储集成电路CAT35C104HP 存储集成电路CC4000 或非门双3输入集成电路CC4008 计数4位二进制集成电路CC40107 与非双2输入缓冲、驱动集成电路CC40174 六D触发集成电路CC40194 移位寄存集成电路CC4025 或非门3输入集成电路CC4026 译码、驱动、十进制计数集成电路CC4027 上升沿J-K触发集成电路CC4029 可预置4位可逆计数集成电路CC4033 译码、驱动、十进制计数集成电路CC4040 二进制计数、分频、振荡集成电路CC4047 单稳态触发集成电路CC4049 非门触发集成电路CC4051 模拟电子开关切换集成电路CC4053 电子开关切换集成电路CC4060 二进制计数、分频、振荡集成电路CC4067 模拟电子开关切换16选1集成电路CC4068 与非门8输入集成电路CC4069 六非门集成电路CC4098 双单稳态触发集成电路CC4099 寄位锁存8位集成电路CC4504 六非门集成电路CC4508 双四位锁存集成电路CC4518 双BCD同步加法计数集成电路CC4520 双四位二进制同步加法计数集成电路CC4543 锁存、译码、驱动BCD-7段集成电路CCST5007 图文电视汉字存储集成电路CCU2000 微处理集成电路CCU2030 微处理集成电路CCU-FBTV02 微处理集成电路CCU-FDTV06 微处理集成电路CD1130 调频/调谐及中频放大集成电路CD1140 调频/调谐及中频放大集成电路CD1452 双声道前置放大集成电路CD1514 音频功率放大集成电路CD1518 双声道音频功率放大集成电路CD2002 音频功率放大集成电路CD2611GS 音频功率放大集成电路CD3161CS 双声道前置放大集成电路CD3210 音频前置放大集成电路CD3220 音频前置放大集成电路CD4021BCM 移位寄存并入、串出集成电路CD4160 单片录、放音集成电路CD4511 液晶显示驱动集成电路CD5132 图像中频放大、视频检波集成电路CD5435 行、场扫描信号处理集成电路CD5511 直流电机转速控制集成电路CD5522 电机稳速控制集成电路CD7243 伴音信号处理集成电路CD7366 发光二极管五位显示驱动集成电路CD74202CS 音频功率放大集成电路CD74212CS 音频功率放大集成电路CD7629 杜比降噪处理集成电路CD7630 双声道音调、音量、平衡控制集成电路CD7640CP 调频/调幅中频放大集成电路CD7642 单片调幅收音集成电路CD7668AP 双声道前置放大集成电路CD7784GP 双声道前置放大集成电路CD810 场扫描输出集成电路CD8403CS 场扫描输出集成电路CD9608CS 双声道前置放大集成电路CDVS110 数据传输控制集成电路CF70200 字符信号处理集成电路CF72306 制式切换集成电路CH05002 微处理集成电路CH208 数码显示驱动集成电路CH4078 或非门集成电路CH5081 主轴相位伺服控制集成电路CH52010 荧光屏显控制集成电路CH52011 微处理集成电路CH52012 视频编码集成电路CH7001C 视频编码集成电路CH7201 视频编码集成电路CHT0406 微处理集成电路CHT0606 微处理集成电路CHT0803 微处理集成电路CHT0807 微处理集成电路CHT0808 微处理集成电路CHT0818 微处理集成电路CIC1240A 电子振铃集成电路CIC9106 振铃集成电路CIC9145 音频、脉冲拨号集成电路CKP1001S 微处理集成电路CKP1003S 微处理集成电路CKP1004S 微处理集成电路CKP1006S 微处理集成电路CKP1008S 微处理集成电路CKP1009S 微处理集成电路CKP1101S 微处理集成电路CKP1103S 微处理集成电路CKP1105S 微处理集成电路CKP1602S 微处理集成电路CKP1603S 微处理集成电路CL480 音频、视频解码集成电路CL482 音频、视频解码集成电路CL484 音频、视频解码集成电路CL680 音频、视频解码集成电路CL8820 音频、视频解码集成电路CL8830A 系统控制处理、编码、解码集成电路CM006CF 数字会聚校正集成电路CM46745 微处理集成电路CMS80D801 解压集成电路CN9832 语言录、放音处理集成电路CNX82 光电耦合集成电路CNY17-2 光电耦合集成电路CNY71 光电耦合集成电路CR3700 音频解码集成电路CRFU3-BF 射频模块集成电路CS4338K 音频数/模转换集成电路CS5339-KS 数/模转换集成电路。

SAMS70和SAME70微控制器家族概述说明书

SAMS70 and SAME70 Microcontroller FamiliesSummaryThe SAMS70 MCU familiy is based on the ARM ® Cortex ®-M7 core plus FloatingPoint Unit (FPU) extending Microchip's 32-bit microcontroller portfolio with maximum operating speeds of up to 300 MHz, 2 MB of Flash and up to 384 KB of multi-port SRAM, of which up to 256 KB can be assigned to tightly coupled memory (data and instructions) delivering a zero wait state at 300 MHz. The SAMS70 family is able to accelerate execution from on-chip Flash and Non-Volatile Memory (NVM) connectedto Quad-SPI and EBI with 16 KB of data and 16 KB of instruction cache memory.This unique memory architecture enables the SAMS70 family to be optimized for real-time deterministic code execution and low-latency peripheral data access. Additionally, the SAMS70 family includes an extensive peripheral set including high-speed USB host and device with high-speed PHY , up to eight UARTs, five SPI, three I 2C, I 2S™, SD/MMC interface, a CMOS camera interface, twelve 16-bit timers, eight 16-bits PWMs and analog interfaces. The SAME70 family includes similar features as the SAMS70family as well as a 10/100 Ethernet MAC and dual Bosch CAN-FD interfaces with advanced analog features making them ideal forconnectivity applications.Key Features• ARM Cortex-M7 core running at 300 MHz• FPU for high-precision computing and accelerated data processing• High-performance internal-memory architecture with user-configurable tightly coupled memories and system memory/16 KB I and 16 KB D cache • Dual Bosch CAN-FD controller• 10/100 Ethernet MAC with IEEE 1588 and KSZ8061 PHY • Quad-SPI with eXecute-In-Place• High-speed USB host and device with on-chip high-speed PHY• CMOS image sensor interface• AES hardware-encryption engines, TRNG and SHA-based memory integrity checker• Advanced analog front end based on dual 2 Msps, 12-bit ADCs, including 16-bit average, with up to 24 channels, offset error correction and gain control• Dual 2 Msps, 12-bit DAC and analog comparator • 64- to 144-pin package options• Extended industrial temperature range from −40°C to 105°CDevelopment ToolsSAMV71 Xplained Ultra Evaluation Kit (ATSAMV71-XULT)The SAM V71 Xplained Ultra evaluation kit is ideal for evaluating and prototyping with the SAMV71, SAM V70, SAM S70 and SAM E70 MCUs. Extension boards to the SAM V71 Xplained Ultra can be purchased individually. This kit is also compatible with Arduino Shields.SAME70 Xplained Evaluation Kit (ATSAME70-XPLD)The SAME70-Xplained Evaluation Kit is ideal for evaluating and prototyping with the Microchip SAMS70 and SAME70 MCUs. It provides connectivity for Eth-ernet, HS USB and SD Cards as well as2-XPRO extension headers. Extension boards for the SAME70Xplained can be purchased individually.The Microchip name and logo and the Microchip logo are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies. © 2017, Microchip Technology Incorporated. All Rights Reserved. Printed in the U.S.A. 6/17DS60001427CPackage Options*QFN with wettable Flanks。

N8020A 主控卡 硬件手册说明书

N8020A主控卡硬件手册权所有恩智(上海)恩智测控技术有限公司版本V1.002016-10-26前言尊敬的用户:首先,非常感谢您选择本公司N8020A-SWITCH交流电流测量卡。

本手册适用于N8020A-SWITCH交流电流测量卡(下文简称N8020A),内容包括N8020A接口,参数指标,使用方法等详细信息。

为保证安全、正确地使用N8020A,请您在使用前详细阅读本手册,特别是安全方面注意事项。

请妥善保管本手册,以备使用过程中查阅。

通告手册中包含信息仅供用户参考,如有更改,恕不另行通知。

对本手册可能包含错误或由提供、执行与使用本手册所造成损害,本公司恕不负责。

有关产品最新信息,请登录本公司网站查询。

产品保证本公司保证N8020A规格与使用特性完全达到手册中所声称各项技术指标,并对本产品所采用原材料与制造工艺均严格把关,确保产品稳定可靠。

保修服务自购买日起,一年保修期内,产品在正常使用与维护状态下所发生一切故障,本公司负责免费维修。

对于免费维修产品,用户需预付寄送到本公司维修部单程运费,回程运费由本公司承担。

若产品从其它国家返厂维修,则所有运费、关税及其它税费均由用户承担。

保证限制本保证仅限于N8020A(保险管除外)。

对于因错误使用、无人管理、未经授权修改、非正常环境下使用及不可抗力因素所造成损坏,本公司不负责免费维修,并将在维修前提交估价单。

仅作以上保证,不作其它明示或默示性保证,其中包括适销性、某些特定应用合理性与适用性等默示保证,无论在合同中、民事过失上,或为其它方面。

本公司不对任何特殊、偶然或间接损害负责。

安全摘要在操作与维修N8020A过程中,请严格遵守以下安全须知。

不遵守以下注意事项或本手册中其它章节提示特定警告,可能会削弱本控制卡所提供保护功能。

对于用户不遵守这些注意事项而造成后果,本公司不负任何责任。

安全须知◆禁止带电插拔。

◆非专业人员请勿进行维修或调整。

◆开机前,确保已安装了正确保险管,拆装前请断电。

一种新型智能通信与电能脉冲采集单元[实用新型专利]

![一种新型智能通信与电能脉冲采集单元[实用新型专利]](https://img.taocdn.com/s3/m/fef57012770bf78a642954bf.png)

专利名称:一种新型智能通信与电能脉冲采集单元专利类型:实用新型专利

发明人:蔡凯泽,杨林楷,吴志刚

申请号:CN202021168439.2

申请日:20200622

公开号:CN212137668U

公开日:

20201211

专利内容由知识产权出版社提供

摘要:本实用新型公开了一种新型智能通信与电能脉冲采集单元,其包括单片机及与之相连的Fly‑Buck隔离电源、SPI通信接口、串行通信隔离电路、脉冲接收器、差分平衡收发器及ESAM安全加密模块。

上述新型智能通信与电能脉冲采集单元,其可实现多通道多规约长距离串口通信,具有支持多通道多协议的高速通信和数据采集以及数据加密功能,通信效率高,通信稳定性好。

申请人:兰吉尔仪表系统(珠海)有限公司

地址:519000 广东省珠海市南屏科技工业园屏东三路12号三幢

国籍:CN

更多信息请下载全文后查看。

ADC0809介绍

ADC0809介绍1.主要特性1)8路8位A/D转换器,即分辨率8位。

2)具有转换起停控制端。

3)转换时间为100μs4)单个+5V电源供电5)模拟输入电压范围0~+5V,不需零点和满刻度校准。

6)工作温度范围为-40~+85摄氏度7)低功耗,约15mW。

2.内部结构ADC0809是CMOS单片型逐次逼近式A/D转换器,内部结构如图13.22所示,它由8路模拟开关、地址锁存与译码器、比较器、8位开关树型D/A转换器、逐次逼近3.外部特性(引脚功能)ADC0809芯片有28条引脚,采用双列直插式封装,如图13.23所示。

下面说明各引脚功能。

IN0~IN7:8路模拟量输入端。

2-1~2-8:8位数字量输出端。

ADDA、ADDB、ADDC:3位地址输入线,用于选通8路模拟输入中的一路ALE:地址锁存允许信号,输入,高电平有效。

START:A/D转换启动信号,输入,高电平有效。

EOC:A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低电平)。

OE:数据输出允许信号,输入,高电平有效。

当A/D转换结束时,此端输入一个高电平,才能打开输出三态门,输出数字量。

CLK:时钟脉冲输入端。

要求时钟频率不高于640KHZ。

REF(+)、REF(-):基准电压。

Vcc:电源,单一+5V。

GND:地。

ADC0809的工作过程是:首先输入3位地址,并使ALE=1,将地址存入地址锁存器中。

此地址经译码选通8路模拟输入之一到比较器。

START上升沿将逐次逼近寄存器复位。

下降沿启动A/D转换,之后EOC输出信号变低,指示转换正在进行。

直到A/D转换完成,EOC变为高电平,指示A/D转换结束,结果数据已存入锁存器,这个信号可用作中断申请。

当OE输入高电平时,输出三态门打开,转换结果的数字量输出到数据总线上。

DAC0832的中文资料手册典型D/A转换DAC0832芯片8位并行、中速(建立时间1us)、电流型、低廉(10~20元)①引脚和逻辑结构②DAC0832与微机系统的连接③应用举例。

美国模拟器件公司8bit模数转换器(ADC)AD9480

美国模拟器件公司8bit模数转换器(ADC)AD9480

佚名

【期刊名称】《电子产品世界》

【年(卷),期】2004(000)07B

【摘要】美国模拟器件公司(ADI)最新推出的8bit模数转换器(ADC)具有250 MSPS转换速率同时保持优良±0.25LSB微分线性误差(DNL)。

据称该DNL技术指标比具有相同转换速率的同类IC高两倍。

DNL在数字示波器和网络分析仪等要求精确显示小输入信号的应用中至关重要。

这一新款ADC也非常适合要求高采样率和宽带宽的应用场合,例如,

【总页数】1页(P14)

【正文语种】中文

【中图分类】TN792

【相关文献】

1.美国模拟器件公司模数转换器 [J],

2.数字控制PFC中3路8bits时分复用SAR ADC的设计 [J], 王青;汪荣昌

3.数字控制PFC中3路8bits时分复用SAR ADC的设计 [J], 王青[1];汪荣昌[1]

4.AD9480:8位ADC [J],

5.0.13μm CMOS 60dB SFDR的8bit 250MS/s模数转换器(英文) [J], 万培元;方狄;崔伟;John Yu;林平分

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Two Selectable Inputs, 8 LVPECL Outputs, SiGe Clock Fanout Buffer ADCLK948

FEATURES

2 selectable differential inputs 4.8 GHz operating frequency 75 fs rms broadband random jitter On-chip input terminations 3.3 V power supply

ADCLK948

TABLE OF CONTENTS

Features .............................................................................................. 1 Applications....................................................................................... 1 General Description ......................................................................... 1 Functional Block Diagram .............................................................. 1 Revision History ............................................................................... 2 Specifications..................................................................................... 3

7/09—Revision 0: Initial Version

Pin Configuration and Function Descriptions..............................6 Typical Performance Characteristics ..............................................7 Functional Description.....................................................................9

APPLICATIONS

Low jitter clock distribution Clock and data signal restoration Level translation Wireless communications Wired communications Medical and industrial imaging ATE and high performance instrumentation

/

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

Fax: 781.461.3113 ©2009–2010 Analog Devices, Inc. All rights reserved.

GENERAL DESCRIPTION

The ADCLK948 is an ultrafast clock fanout buffer fabricated on the Analog Devices, Inc., proprietary XFCB3 silicon germanium (SiGe) bipolar process. This device is designed for high speed applications requiring low jitter.

Clock Inputs ...................................................................................9 Clock Outputs................................................................................9 Clock Input Select (IN_SEL) Settings...................................... 10 PCB Layout Considerations...................................................... 10 Input Termination Options....................................................... 11 Outline Dimensions ....................................................................... 12 Ordering Guide .......................................................................... 12

/

Rev. A | Page 2 of 12

ADCLK948

SPECIFICATIONS

ELECTRICAL CHARACTERISTICS

Typical (Typ column) values are given for VCC − VEE = 3.3 V and TA = 25°C, unless otherwise noted. Minimum (Min column) and maximum (Max column) values are given over the full VCC − VEE = 3.3 V ± 10% and TA = −40°C to +85°C variation, unless otherwise noted.

The ADCLK948 features eight full-swing emitter coupled logic (ECL) output drivers. For LVPECL (positive ECL) operation, bias VCC to the positive supply and VEE to ground. For ECL operation, bias VCC to ground and VEE to the negative supply.

FUNCTIONAL BLOCK DIAGRAM

ADCLK948

LVPECL Q0

Q0

Q1VREF0

REFERENCE

Q3

VT0

Q4

Q4 CLK0

CLK0

Q5

VT1

Q5

CLK1

Q6

CLK1

Q6

Q7 IN_SEL

Q7

VREF1

REFERENCE

Figure 1.

08280-001

Rev. A

Table 1. Clock Inputs and Outputs

Parameter

Symbol

DC INPUT CHARACTERISTICS

Input Common Mode Voltage VICM

REVISION HISTORY

6/10—Rev. 0 to Rev. A Changed Output Voltage Differential Parameter to Output Voltage, Single Ended Parameter, Table 1 ..................................... 3 Changes to Output Voltage, Single Ended Parameter, Table 1 ... 3

The output stages are designed to directly drive 800 mV each side into 50 Ω terminated to VCC − 2 V for a total differential output swing of 1.6 V.

The ADCLK948 is available in a 32-lead LFCSP and specified for operation over the standard industrial temperature range of −40°C to +85°C.

Determining Junction Temperature .......................................... 5 ESD Caution.................................................................................. 5 Thermal Performance .................................................................. 5