长江大学录井10级数字电子技术试卷

数字电路试题五套(含答案)

《数字电子技术》试卷一一、填空(每空1分,共25分)1、(10110)2=( )10=( )16(28)10=( )2=( )16(56)10=()8421BCD2、最基本的门电路是:、、。

3、有N个变量组成的最小项有个。

4、基本RS触发器的特征方程为_______ ,约束条件是__.5、若存储器的容量是256×4RAM,该RAM有___存储单元,有字,字长_____位,地址线根。

6、用N位移位寄存器构成的扭环形计数器的模是________.7、若令JK触发器的J=K=T则构成的触发器为_______.8、如图所示,Y= 。

9、如图所示逻辑电路的输出Y= 。

10、已知Y=D+,则ACB A+BCY= ,Y/=。

11、组合逻辑电路的特点是_________、___________;与组合逻辑电路相比,时序逻辑电路的输出不仅仅取决于此刻的_______;还与电路有关。

二、化简(每小题5分,共20分)1、公式法化简(1)Y=ABC ABC BC BC A++++(2)Y ABC A B C=+++2、用卡诺图法化简下列逻辑函数(1)Y BCD BC ACD ABD=+++(2)(1,3,4,9,11,12,14,15)(5,6,7,13)Y=∑+∑m d三、设下列各触发器初始状态为0,试画出在CP作用下触发器的输出波形(10分)四、用74LS161四位二进制计数器实现十进制计数器(15分)P Q A Q B Q C Q D CT 74LS161LDCPA B C D CrQ A、Q B 、Q C、Q D:数据输出端;A 、B、C、D:数据输入端;P、T:计数选通端;C:异步复位端;r五、某汽车驾驶员培训班结业考试,有三名评判员,其中A为主评判员,B、C为副评判员,评判时,按照少数服从多数原则,但若主评判员认为合格也可以通过。

试用74LS138和与非门实现此功能的逻辑电路。

(15分)六、试分析如图电路的逻辑功能,设各触发器的初始状态为0(15分)《数字电子技术》试卷一参考答案一、 填空(每空1分,共25分)1、10(22)、16(16);2(11100)、16(1)C ;8421(01010110)BCD 。

数字电子技术试题集及答案

数字电子技术基础试卷试题答案汇总数字电子技术基础试题(二)一、填空题 : (每空1分,共10分)1.八进制数 (34.2 ) 8 的等值二进制数为(11100.01 ) 2 ;十进制数 98 的8421BCD 码为(10011000 ) 8421BCD 。

2 . TTL 与非门的多余输入端悬空时,相当于输入高电平。

3 .下图所示电路中的最简逻辑表达式为。

AB4. 一个 JK 触发器有两个稳态,它可存储一位二进制数。

5. 若将一个正弦波电压信号转换成同一频率的矩形波,应采用多谐振荡器电路。

6. 常用逻辑门电路的真值表如表1所示,则 F 1 、 F 2 、 F 3 分别属于何种常用逻辑门。

表 1A B F 1 F 2 F 30 0 1 1 00 1 0 1 11 0 0 1 11 1 1 0 1F 1 同或;F 2 与非门;F 3 或门。

二、选择题: (选择一个正确答案填入括号内,每题3分,共30分 )1、在四变量卡诺图中,逻辑上不相邻的一组最小项为:(D )A、m 1与m 3B、m 4与m6C、m 5 与m 13D、m 2 与m 82、 L=AB+C 的对偶式为:(B )A 、 A+BC ;B 、( A+B )C ; C 、 A+B+C ;D 、 ABC ;3、半加器和的输出端与输入端的逻辑关系是(D )A、与非B、或非C、与或非D、异或4、 TTL 集成电路 74LS138 是3 / 8线译码器,译码器为输出低电平有效,若输入为 A 2 A 1 A 0 =101 时,输出:为(B )。

A . 00100000 B. 11011111 C.11110111 D. 000001005、属于组合逻辑电路的部件是(A )。

A、编码器B、寄存器C、触发器D、计数器6.存储容量为8K×8位的ROM存储器,其地址线为(C )条。

A、8B、12C、13D、147、一个八位D/A转换器的最小电压增量为0.01V,当输入代码为10010001时,输出电压为(C )V。

数字电子技术试卷试题答案汇总

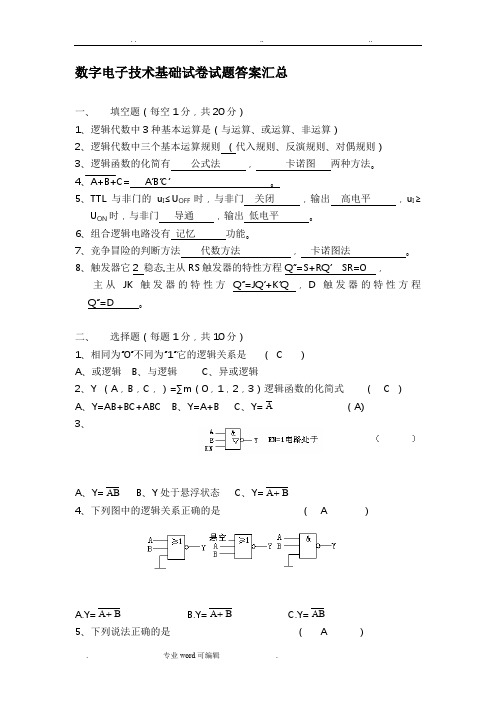

数字电子技术基础试卷试题答案汇总一、填空题(每空1分,共20分)1、逻辑代数中3种基本运算是(与运算、或运算、非运算)2、逻辑代数中三个基本运算规则 (代入规则、反演规则、对偶规则)3、逻辑函数的化简有 公式法 , 卡诺图 两种方法。

4、A+B+C= A ’B ’C ’ 。

5、TTL 与非门的u I ≤U OFF 时,与非门 关闭 ,输出 高电平 ,u I ≥U ON 时,与非门 导通 ,输出 低电平 。

6、组合逻辑电路没有 记忆 功能。

7、竞争冒险的判断方法 代数方法 , 卡诺图法 。

8、触发器它2 稳态,主从RS 触发器的特性方程Q ’’=S+RQ ’ SR=0 ,主从JK 触发器的特性方Q ’’=JQ ’+K ’Q ,D 触发器的特性方程 Q ’’=D 。

二、选择题(每题1分,共10分)1、相同为“0”不同为“1”它的逻辑关系是 ( C ) A 、或逻辑 B 、与逻辑 C 、异或逻辑2、Y (A ,B ,C ,)=∑m (0,1,2,3)逻辑函数的化简式 ( C ) A 、Y=AB+BC+ABC B 、Y=A+B C 、Y=A (A)3、A 、Y=AB B 、Y 处于悬浮状态C 、Y=B A +4、下列图中的逻辑关系正确的是 ( A )A.Y=B A +B.Y=B A +C.Y=AB5、下列说法正确的是 ( A )A、主从JK触发器没有空翻现象B、JK之间有约束C、主从JK触发器的特性方程是CP上升沿有效。

6、下列说法正确的是( C )A、同步触发器没有空翻现象B、同步触发器能用于组成计数器、移位寄存器。

C、同步触发器不能用于组成计数器、移位寄存器。

7、下列说法是正确的是( A )A、异步计数器的计数脉冲只加到部分触发器上B、异步计数器的计数脉冲同时加到所有触发器上C、异步计数器不需要计数脉冲的控制8、下列说法是正确的是(A )A、施密特触发器的回差电压ΔU=U T+-U T-B、施密特触发器的回差电压越大,电路的抗干扰能力越弱C、施密特触发器的回差电压越小,电路的抗干扰能力越强9、下列说法正确的是( C )A、多谐振荡器有两个稳态B、多谐振荡器有一个稳态和一个暂稳态C、多谐振荡器有两个暂稳态10、下列说法正确的是( A )A、555定时器在工作时清零端应接高电平B、555定时器在工作时清零端应接低电平C、555定时器没有清零端三、判断题(每题1分,共10分)1、A+AB=A+B (错)2、当输入9个信号时,需要3位的二进制代码输出。

数字电子技术期末考试试题及答案(试卷一)

、 代入规则 对偶规则 反

演规则

、

。

5、为 了 实 现 高 的 频 率 稳 定 度 , 常 采 用 石英晶体

振荡

器 ; 单 稳 态 触 发 器 受 到 外 触 发 时 进 入 暂稳态 态

6、同步 RS 触发器中 R、S 为 高 电平有效,基本 R、S 触发器中 R、S

为低

电平有效

7、在进行 A/D 转换时,常按下面四个步骤进行, 采样 保持 量化 编

码、

、

、。Βιβλιοθήκη 二、选择题(每题 1 分,共 10 分)

1、有八个触发器的二进制计数器,它们最多有(

)种计数状态。

A、8; B、16; C、256; D、64

2、下列触发器中上升沿触发的是( )。

A、主从 RS 触发器;B、JK 触发器;C、T 触发器;D、D 触发器

3、下式中与非门表达式为( d ),或门表达式为(a )。

数字电子技术期末考试试题及答案(试卷一)

目录

数字电子技术期末考试试题及答案(试卷一) ........................................................................... 1 一、填空题(每空 1 分,共 20 分).............................................................................................2 二、选择题(每题 1 分,共 10 分).............................................................................................2 三、判断(每题 1 分,共 10 分):...............................................................................................3 四、数制转化(每题 2 分,共 10 分):.......................................................................................3 五、逻辑函数化简(每题 5 分,共 10 分):...............................................................................3 六、分析电路:(每题 10 分,共 20 分).....................................................................................4 七、设计电路(共 10 分).............................................................................................................4 试题答案(一)...............................................................................................................................5

【强烈推荐】数字电子技术基础期末考试试卷及 答案

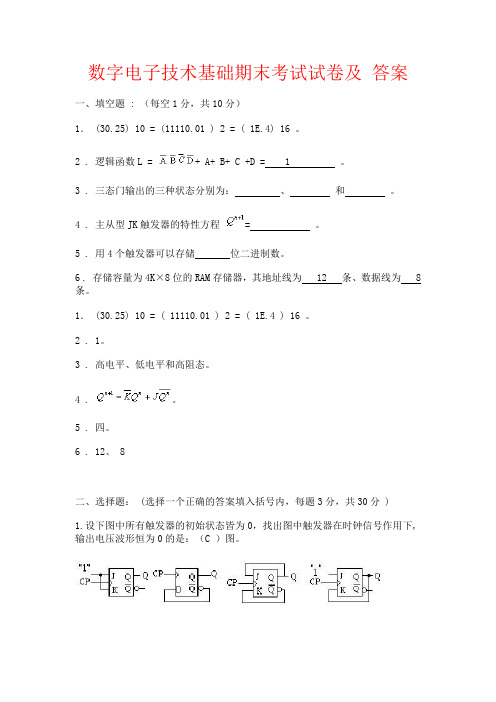

数字电子技术基础期末考试试卷及答案一、填空题 : (每空1分,共10分)1. (30.25) 10 = (11110.01 ) 2 = ( 1E.4) 16 。

2 . 逻辑函数L = + A+ B+ C +D = 1 。

3 . 三态门输出的三种状态分别为:、和。

4 . 主从型JK触发器的特性方程= 。

5 . 用4个触发器可以存储位二进制数。

6 . 存储容量为4K×8位的RAM存储器,其地址线为 12 条、数据线为 8 条。

1. (30.25) 10 = ( 11110.01 ) 2 = ( 1E.4 ) 16 。

2 . 1。

3 . 高电平、低电平和高阻态。

4 . 。

5 . 四。

6 . 12、 8二、选择题: (选择一个正确的答案填入括号内,每题3分,共30分 )1.设下图中所有触发器的初始状态皆为0,找出图中触发器在时钟信号作用下,输出电压波形恒为0的是:(C )图。

2.下列几种TTL电路中,输出端可实现线与功能的电路是( D)。

A、或非门B、与非门C、异或门D、OC门3.对CMOS与非门电路,其多余输入端正确的处理方法是(D )。

A、通过大电阻接地(>1.5KΩ)B、悬空C、通过小电阻接地(<1KΩ)B、 D、通过电阻接V CC4.图2所示电路为由555定时器构成的(A )。

A、施密特触发器B、多谐振荡器C、单稳态触发器D、T触发器5.请判断以下哪个电路不是时序逻辑电路(C )。

A、计数器B、寄存器C、译码器D、触发器6.下列几种A/D转换器中,转换速度最快的是(A )。

A、并行A/D转换器B、计数型A/D转换器C、逐次渐进型A/D转换器B、 D、双积分A/D转换器7.某电路的输入波形 u I 和输出波形 u O 如下图所示,则该电路为( C)。

A、施密特触发器B、反相器C、单稳态触发器D、JK触发器8.要将方波脉冲的周期扩展10倍,可采用(C )。

A、10级施密特触发器B、10位二进制计数器C、十进制计数器B、D、10位D/A转换器9、已知逻辑函数与其相等的函数为( D)。

长江大学数字电子技术期末试卷

长江大学期终考试试题数字电子技术(A卷)一、填空题:(每空2分,共30分)(1)(11100.011)2 =( )10 =( )8421BCD (2)(204.125)10 =( )2=( )8=( )16(3)字母TTL代表( )。

(4)三态门的输出状态共有( )三个状态。

(5)将模拟信号转换为数字信号需经过()四个步骤。

(6)触发器的触发方式可分为电平触发和()触发。

(7)逻辑门电路输出端可驱动同类门电路的个数称为( )。

(8)将)+AY++=化为最小项形式为+A)((CBBC()。

(9)()(译码器,编码器)的特点是在任一时刻只有一个输入有效。

(10)一位半加器具有( )个输入和两个输出。

(11)已知A/D转换器的分辨率为8位,其输入模拟电压范围为0~5V,则当输入电压为 1.96V时,输出数字量为()。

(12)利用双稳态触发器存储信息的RAM称为()RAM。

二、(共10分)(1)(4分) 用代数法化简:CBBCCBABCDAAF++++=(2)(6分) 用卡诺图化简:∑∑+=m d8)4,2,1, (0,6,7,10)5,3,(D)C,B,,Y(A三、(10分)已知逻辑电路如图1所示,试分析其逻辑功能。

(要求:写出简化逻辑表达式、真值表和逻辑功能。

)图1四、(12分)如图2,分别用(1)八选一数据选择器;(2) 3-8线译码器74LS138及其逻辑门;实现逻辑函数: (说明:A 2 为高位) C B A C B A AC F ++=五、(15分)电路和波形如图3 (a ),(b)所示,设Q 0 ,Q 1 的初态均为0。

(1)写出驱动方程,状态方程和输出方程;(2)画出Q 0 ,Q 1和Y 的波形(直接画在本试卷上)。

图3 (a )D 4D 5D 6D7A 0 A 1 A 2 D 0D 1D 2D 3Y … 图2A图3 (b)六、(12分)试利用集成计数器74LS161(图4)和必要的逻辑门,(1)用反馈清零法构成12进制计数器;(2)用反馈置数法构成8进制计数器,要求计数器的初始状态为“0”;( 上述均要求画出状态转换图。

2010长江大学数电答案

2010─2011学年 第1学期《数字电子技术》试卷(A )参考答案及评分标准一、填空题 (共22分)1.(10分)将十进制数(254.25)10化成二进制数(1111 1110.01 )、八进制数 (376.2)、十六进制数(FE.4 ) 、8421BCD 码 (0010 0101 0100.00100101 ) 、5421BCD 码 (0010 1000 0100. 0010 1000 )。

2.(2分)已知D/A转换电路中,当输入数字量为10000000时,输出电压为 6.4V ,则当输入为01010000时,其输出电压为(4V )。

3.(2分)有符号二进制补码0010111所表示的十进制数为( +23 )。

4.(2分)用边沿D 触发器构成二分频电路时的D 输入信号为( Q )。

5.(4分)41⨯K 的存储器有(4 )根数据线,(10 )根地址线,若该存储器的起始地址为00H,则最高地址为(3FFH ),欲将该存储器扩展为82⨯K 的存储系统,需要41⨯K 的存储器(4 )个。

6.(2分)一个可编程逻辑阵列PLA 电路如图1所示,其输出逻辑函数表达式L 0、L 1分别为(BC AC C B A AC B A +++, )。

二、( 8分,每小题4分) (1) B AC ABC C AB C B A F 1A +=++= (2)化简得C B C B D F ++=2三、( 12分)(1)(6分)E D BC AB L =(2)(2分)7、4、9接一起都接Vss ,8、5、12接一起,11接1,2接13,14接VDD ,6、3、10为或非门三输入端。

(3)(4分)(a )第一个555定时器构成多谐振荡电路,第二个555定时器构成单稳态触发电路。

(b )四、(12分)(1)写表达式(4分)AB C B A AB C B A F CB A F +⊕=⊕=⊕⊕=)()(21(2)列真值表(4分)(3)功能(1分):一位二进制全加器。

数字电子技术精彩试题集及问题详解

数字电子技术基础试卷试题答案汇总数字电子技术基础试题(二)一、填空题 : (每空1分,共10分)1.八进制数 (34.2 ) 8 的等值二进制数为(11100.01 ) 2 ;十进制数 98 的8421BCD 码为(10011000 ) 8421BCD 。

2 . TTL 与非门的多余输入端悬空时,相当于输入高电平。

3 .下图所示电路中的最简逻辑表达式为。

AB4. 一个 JK 触发器有两个稳态,它可存储一位二进制数。

5. 若将一个正弦波电压信号转换成同一频率的矩形波,应采用多谐振荡器电路。

6. 常用逻辑门电路的真值表如表1所示,则 F 1 、 F 2 、 F 3 分别属于何种常用逻辑门。

表 1A B F 1 F 2 F 30 0 1 1 00 1 0 1 11 0 0 1 11 1 1 0 1F 1 同或;F 2 与非门;F 3 或门。

二、选择题: (选择一个正确答案填入括号内,每题3分,共30分 )1、在四变量卡诺图中,逻辑上不相邻的一组最小项为:(D )A、m 1与m 3B、m 4与m6C、m 5 与m 13D、m 2 与m 82、 L=AB+C 的对偶式为:(B )A 、 A+BC ;B 、( A+B )C ; C 、 A+B+C ;D 、 ABC ;3、半加器和的输出端与输入端的逻辑关系是(D )A、与非B、或非C、与或非D、异或4、 TTL 集成电路 74LS138 是3 / 8线译码器,译码器为输出低电平有效,若输入为 A 2 A 1 A 0 =101 时,输出:为(B )。

A . 00100000 B. 11011111 C.11110111 D. 000001005、属于组合逻辑电路的部件是(A )。

A、编码器B、寄存器C、触发器D、计数器6.存储容量为8K×8位的ROM存储器,其地址线为(C )条。

A、8B、12C、13D、147、一个八位D/A转换器的最小电压增量为0.01V,当输入代码为10010001时,输出电压为(C )V。

数字电子技术基础试卷及答案8套

数字电子技术基础试卷及答案8套(共29页)--本页仅作为文档封面,使用时请直接删除即可----内页可以根据需求调整合适字体及大小--数字电子技术基础1一.1.(15分)试根据图示输入信号波形分别画出各电路相应的输出信号波形L1、L2、L3、L4、和L5。

设各触发器初态为“0”。

AB二.(15分)已知由八选一数据选择器组成的逻辑电路如下所示。

试按步骤分析该电路在M1、M2取不同值时(M1、M2取值情况如下表所示)输出F的逻辑表达式。

八选一数据选择器输出端逻辑表达式为:Y=Σm i D i,其中m i是S2S1S0最小项。

FM2M1 F0 00 1111三.(8分)试按步骤设计一个组合逻辑电路,实现语句“A>B”,A、B均为两位二进制数,即A (A1、A0),B(B1、B0)。

要求用三个3输入端与门和一个或门实现。

四.(12分)试按步骤用74LS138和门电路产生如下多输出逻辑函数。

23123Y AC Y ABC ABC BC Y BC ABC=⎧⎪=++⎨⎪=+⎩ 74LS138逻辑表达式和逻辑符号如下所示。

五.(15分)已知同步计数器的时序波形如下图所示。

试用维持-阻塞型D 触发器实现该计数器。

要求按步骤设计。

六.(18分)按步骤完成下列两题1.分析图5-1所示电路的逻辑功能:写出驱动方程,列出状态转换表,画出完全状态转换图和时序波形,说明电路能否自启动。

2.分析图5-2所示的计数器在M=0和M=1时各为几进制计数器,并画出状态转换图。

图5-14BCCPAEpE T LDDQ0Q1 Q3Q2 74LS163 Rd1M&1计数脉冲1图5-2七.八.(10分) 电路下如图所示,按要求完成下列问题。

1.指出虚线框T1中所示电路名称.2.对应画出V C、V01、A、B、C的波形。

并计算出V01波形的周期T=。

56数字电子技术基础2一.(20分)电路如图所示,晶体管的β=100,Vbe=。

(1)求电路的静态工作点;(2) 画出微变等效电路图, 求Au 、r i 和r o ;(3)若电容Ce 开路,则将引起电路的哪些动态参数发生变化?并定性说明变化趋势.二.(15分)求图示电路中a U 、bU 、b U 、c U 及L I 。

长江大学非电类2012-2013数电试卷A-推荐下载

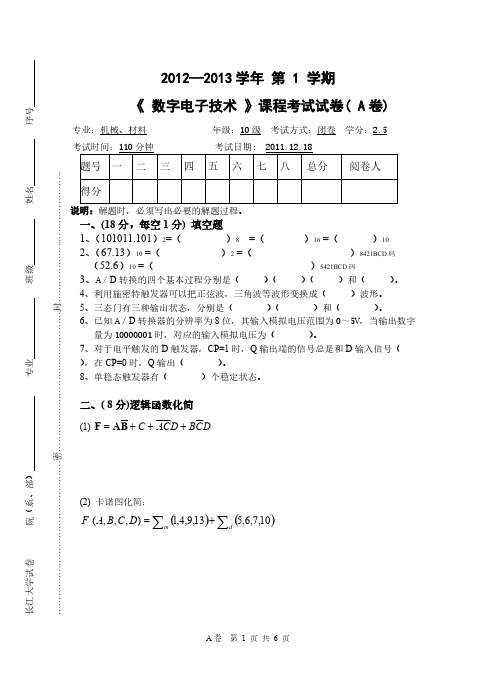

2012─2013学年 第 1 学期《 数字电子技术 》课程考试试卷( A 卷)专业:机械、材料 年级:10级 考试方式:闭卷 学分:2.5考试时间:110分钟 考试日期: 2011.12.18解题时,必须写出必要的解题过程。

一、(18分,每空1分) 填空题 1、(101011.101)2=( )8 =( )16 =( )102、(67.13)10 =( )2 =( )8421BCD 码 (52.6)10 =( )5421BCD 码3、A /D 转换的四个基本过程分别是( )( )( )和( )。

4、利用施密特触发器可以把正弦波,三角波等波形变换成( )波形。

5、三态门有三种输出状态,分别是( )( )和( )。

6、已知A /D 转换器的分辨率为8位,其输入模拟电压范围为0~5V ,当输出数字 量为10000001时,对应的输入模拟电压为( )。

7、对于电平触发的D 触发器,CP=1时,Q 输出端的信号总是和D 输入信号( ),在CP=0时,Q 输出( )。

8、单稳态触发器有( )个稳定状态。

二、( 8分)逻辑函数化简 (1) D C B D C A C +++=B A F (2) 卡诺图化简:()()∑∑+=d m D C B A F 10,7,6,513,9,4,1),,,(题号一二三四五六七八总分阅卷人得分三、(10分)求出并化简下述电路的输出函数表达式,列出真值表并分析其逻辑功能。

四、(14分)(1)用译码器74LS138实现函数F1=AB+AC的逻辑功能;(2)用数据选择器74LS151实现函数F2(A,B,C,D)=∑m(0,2,3,7,9,10,14)的逻辑功能。

五、(12分)用与非门设计一个3变量“多数表决电路”。

六、(20分)74LS161为异步清零、同步置数的集成四位二进制计数器,ET=EP=1时的功能为加计数,RCO 为进位输出。

74LS90为异步清零、异步置9的集成二-五-十进制计数器,其功能表见考卷后面的附录。

大学课程《数字电子技术基础》试题及答案

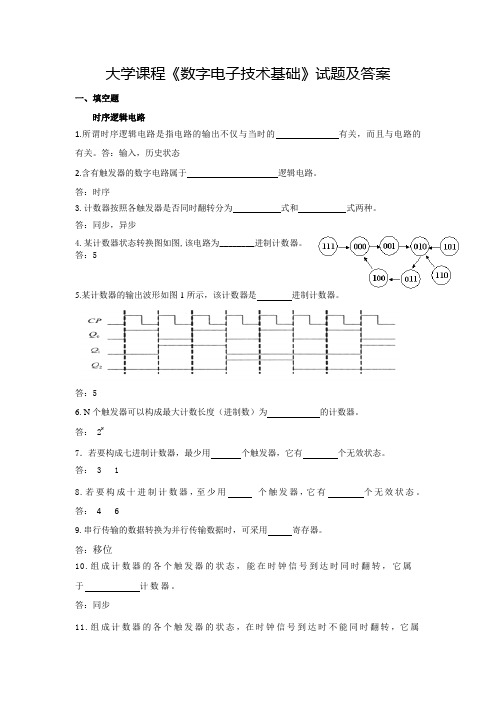

大学课程《数字电子技术基础》试题及答案一、填空题时序逻辑电路1.所谓时序逻辑电路是指电路的输出不仅与当时的有关,而且与电路的有关。

答:输入,历史状态2.含有触发器的数字电路属于逻辑电路。

答:时序3.计数器按照各触发器是否同时翻转分为式和式两种。

答:同步,异步4.某计数器状态转换图如图,该电路为________进制计数器。

答:55.某计数器的输出波形如图1所示,该计数器是进制计数器。

答:56. N个触发器可以构成最大计数长度(进制数)为的计数器。

答: 2N7.若要构成七进制计数器,最少用个触发器,它有个无效状态。

答: 3 18.若要构成十进制计数器,至少用个触发器,它有个无效状态。

答:4 69.串行传输的数据转换为并行传输数据时,可采用寄存器。

答:移位10.组成计数器的各个触发器的状态,能在时钟信号到达时同时翻转,它属于计数器。

答:同步11.组成计数器的各个触发器的状态,在时钟信号到达时不能同时翻转,它属于计数器。

答:异步12.两片中规模集成电路10进制计数器串联后,最大计数容量为()位。

答:10013.驱动共阳极七段数码管的译码器的输出电平为()有效。

答:低二、选择题时序逻辑电路1.时序逻辑电路中一定包含。

A、触发器B、组合逻辑电路C、移位寄存器D、译码器答:A2.在同步计数器中,各触发器状态改变时刻()。

A、相同B、不相同C、与触发器有关D、与电平相同答:A3.同步时序逻辑电路和异步时序逻辑电路比较,其差别在于后者。

A.没有触发器B. 没有统一的时钟脉冲控制C.没有稳定状态D. 输出只与内部状态有关答:B4.有一个左移移位寄存器,当预先置入1011后,其串行输入固定接0,在4个移位脉冲CP 作用下,四位数据的移位过程是()。

A. 1011--0110--1100--1000--0000B. 1011--0101--0010--0001--0000C. 1011--1100--1101--1110--1111D. 1011--1010--1001--1000—0111答:A Array 5.某计数器的状态转换图如右:其计数的容量为( )A.8 B. 5C. 4D. 3答:B6.同步时序逻辑电路和异步时序逻辑电路比较,其差别在于后者。

数字电子技术试卷3套含答案(大学期末复习资料).docx

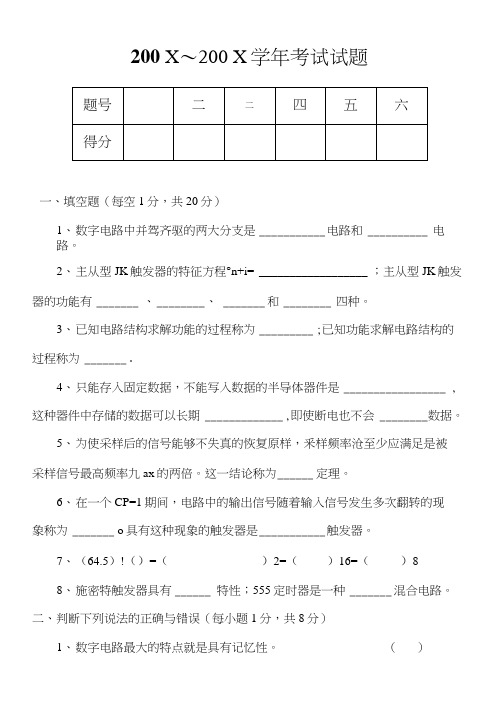

200 X〜200 X学年考试试题一、填空题(每空1分,共20分)1、数字电路中并驾齐驱的两大分支是___________ 电路和 __________ 电路。

2、主从型JK触发器的特征方程°n+i= __________________ ;主从型JK触发器的功能有_______ 、________ 、 _______ 和________ 四种。

3、已知电路结构求解功能的过程称为_________ ;已知功能求解电路结构的过程称为_______ o4、只能存入固定数据,不能写入数据的半导体器件是_________________ , 这种器件中存储的数据可以长期 _____________ ,即使断电也不会 ________ 数据。

5、为使采样后的信号能够不失真的恢复原样,釆样频率沧至少应满足是被采样信号最高频率九ax的两倍。

这一结论称为______ 定理。

6、在一个CP=1期间,电路中的输出信号随着输入信号发生多次翻转的现象称为_______ o具有这种现象的触发器是___________ 触发器。

7、(64.5)!()=()2=()16=()88、施密特触发器具有______ 特性;555定时器是一种_______ 混合电路。

二、判断下列说法的正确与错误(每小题1分,共8分)1、数字电路最大的特点就是具有记忆性。

()2、竞争冒险中凡电压毛刺为高电平时,均称为1冒险。

()3、数值译码器的输入量是十进制,输出量是二进制。

()4、仅具有翻转功能的触发器是T触发器。

()5、74LS90和74LS163都是具有自启动能力的集成计数器。

()6、集成电路74LS138是一个4线-10线的译码器。

()7、多谐振荡器输入三角波,输出可转换成方波。

()8、模5计数器至少需用两位触发器构成。

()三、选择题(每小题2分,共20分)1、由与非门组成的基本RS触发器不允许输入的变量组合g•斥是()A、00B、01C、10D、112、仅具有保持和翻转功能的触发器是()A、JK触发器B、D触发器C、T触发器D、同步触发器3、八输入端的编码器按二进制编码时,其输出端的个数是()A、2个B、3个C、4个D、6个4、用8421 BCD码作为代码的计数器,至少需要的触发器个数是()A、2个B、3个C、4个D、5个5、按触发方式的不同,双稳态触发器可分为()A、高电平触发和低电平触发B、电平触发或边沿触发C、上升沿触发和下降沿触发D、输入触发和时钟触发6、四位移位寄存器构成扭环形计数器时,可构成()计数器。

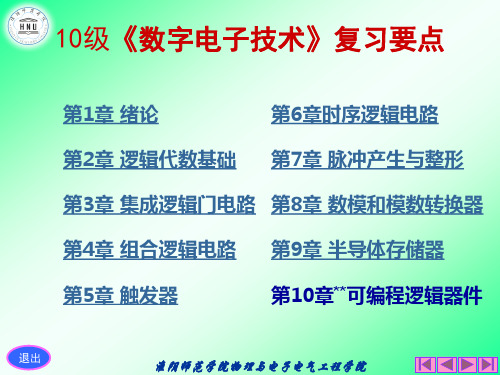

10级《数字电子技术》复习资料

解: (1) 电路是由两个下降沿触

发的JK 触发器、1个异或门、1 个非门与3个与非门组成的同步

时序电路。 (2) 列方程组

输出方程组:

Y AQ1Q2 AQ1Q2 AQ1Q2 AQ1Q2

激励方程组:

JJ12

解: 设三人的意见为变量A、B、C,表决结果为函数L。

对变量及函数进行如下状态赋值:对于变量A、B、C,设

同意为逻辑“1”;不同意为逻辑“0”。对于函数L,设事

情通过为逻辑“1”;没通过为逻辑“0”。显然,当A=0时,

A行使否决权,故L=0。 (1) 建立该逻辑函数的真值表

例4.2.4的真值表

ABC L

例7 将D触发器转换为JK触发器。 解:比较D触发器和JK触发器的特性方程可知

D JQ n KQn JQ n KQn

退出

淮阴师范学院物理与电子电气工程学院

第6章 时序逻辑电路

复习要点

1.了解时序逻辑电路的特点。 2.掌握时序逻辑电路的描述方式。 3.掌握同步、异步时序逻辑电路的分析方法。 4.掌握常用时序逻辑电路——计数器、寄存器、

三、触发器的逻辑功能

用特性表、特性方程、状态转换图、波形图来描述。

(a) RS触发器

退出

或非门组成的基本RS触发器的特性表

R

S

Qn Qn+1

功能

00

0

0

保持

00

1

1

保持

01

0

1

置1

01

1

1

置1

10

0

0

置0

10

1

数字电子技术模拟试题答案20101215

长江大学期终考试模拟试题答案课程 数字电子技术 班级 姓名 学号 2010.12.151.(110101.011)B =( 53.375 )D = (1010011.001101110101 )8421BCD 码 2. (36.625)D =( 100100.101 )B = ( 44.5 )O = ( 24.A )H二、(16分)逻辑函数化简:1.用代数法将下列逻辑函数化简为最简与-或表达式DA D C CB A D A DCD C B D B A D AC C B A D A D C C B D A B A D A D B C A L D A BD C A L ++=+++++=++++=+++=++=))(())()((:11解2.用卡诺图法将下列逻辑函数化简为最简与-或表达式DB C D C B A L dm+=+=∑∑原式解:)10,8,7,3()15,14,11,6,2,0(),,,(3BCA L L D C A CB A DC A L =+++=444:0,:法得再用圈的卡诺图先作出解BC A C A B L C A C A B C A AC B L =⊕+⊕=+++=)(:)()(22解00 01 11 10 00 01 1110 AB CD 1 0 1 11 11 11 1 111 0 1 1L 4三、(12分) 已知4位二进制同步加计数器74161(具有异步清零和同步置数功能),要求: 1. 用反馈清零法设计一个十进制计数器; 2. 用反馈置数法设计一个六进制计数器;3. 用1.和2.的结果异步级联为模60的计数器。

解:1. 因异步清零,计数器模为10故取S N =1010,则 R D =Q D Q B ,其状态图如下:Q D Q C Q B Q A → 0000→0001→0010→0011→0100→0101→0110(1010)←1001←1000←0111← 2. 因同步置数,计数器模为6故取S N-1 =0101译码,则 L D C A , 置数ABCD=0000, 其状态图如下: Q D Q C Q B Q A → 0000→0001→0010→00110101←0100← 3.将十进制计数器作为第一级,六进制计数器作为第二级 进行异步级联,令CP 2 = R D 即可。

数字电子技术10B

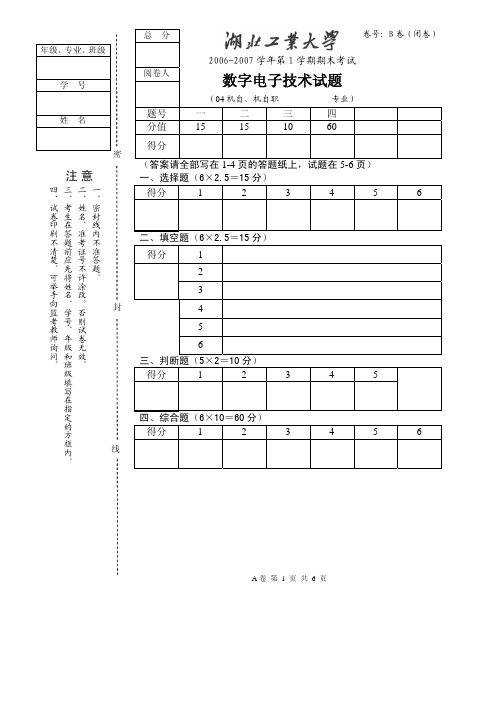

A 卷 第 1 页 共 6 页 卷号:B卷(闭卷)2006-2007学年第1学期期末考试 数字电子技术试题 (04机自、机自职 专业) 题号 一 二 三 四 分值 15 15 10 60 得分 (答案请全部写在1-4页的答题纸上,试题在5-6页) 一、选择题(6×2.5=15分) 得分 1 2 3 4 5 6 二、填空题(6×2.5=15分) 得分 12 3 4 5 6 三、判断题(5×2=10分) 得分 1 2 3 4 5 四、综合题(6×10=60分) 得分 1 2 3 4 5 6总 分 阅卷人A卷第 2 页共 6 页A卷第 3 页共 6 页A卷第 4 页共 6 页A 卷 第 5 页 共 6 页 一、选择题(6×2.5=15分)1.以下代码中为有权码的是( )。

A .8421BCD 码 B. 格雷码 C. 余三码D .ASCII 码2.以下电路中可以实现“线与”功能的有( )。

A .与非门B .非门C .OC 门D .或非门3.以下表达式中符合逻辑运算法则的是( )。

A .C+C=2C B .1+1=1 C .0<1D .A+1=A 4.在何种输入情况下,“或非”运算的结果一定是逻辑1。

( )A .全部输入0B .仅一输入0C .任一输入1D .全部输入1 5.在下列逻辑电路中,不是组合逻辑电路的是( )。

A .译码器B .编码器C .全加器D .寄存器6.多谐振荡器有( )。

A .两个稳态B .两个暂稳态C .一个稳态,一个暂稳态D .以上都不对二、填空题(6×2.5=15分)1.十进制数16用8421BCD 码表示为( )。

2.))()((C A C B B A F +++=,最小项表达式m C B A F ∑=),,(()。

3.用对偶规则写出1)(++=C B A F 的对偶函数是( )。

4.74LS148的EI 端的功能是( )。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

阅卷人 得分

三、 请用卡诺图化简法将下列逻辑函数化简为最简与或式的 形式 (5 分)

F ( A, B, C, D)

m

(0,1,2,3,6,8)

d

(10,11,12,13,14,15)

第 2 页共 5 页

阅卷人 得分

……………..…..…………………….密…………………………………封………………..…………………..线……………………………………..

A、7 B、6 C 、5 D、4 4、对于钟控 RS 触发器,其输出为“0”态,要使其次态保持“0”态不变,则输入 的 RS 信号应为( ) 。 A、RS = 1X B、RS = 0X C、RS = X1 D、RS = X0 5、要将 JK 触发器转换为 D 触发器,应使( ) 。 A、 J D, K D B、 K D, J D C、 J K D 6、下列电路中,能实现逻辑功能 Q n1 Q n 的是( ) 。 D、 J K D

专业

班级

阅卷人 得分

第 1 小题 第 6 小题

二、选择题 (每小题 1 分,共 10 分) 第 2 小题 第 7 小题 第 3 小题 第 8 小题 ) 。 第 4 小题 第 9 小题 第 5 小题 第 10 小题

院(系、部)

1、下列逻辑函数中,F = A 的是(

长江大学试卷

A、 F A 1 B、F = A⊙1 C、 F A 1 D、 F A 0 2、以下电路中可以实现“线与”功能的有( ) 。 A、与非门 B、三态输出门 C、集电极开路门 D、CMOS 传输门 3、发光二极管组成的七段数码管,当采用共阴极接法时,若 g~a=1111100,则 显示的数字是( ) 第 1 页共 5 页

四、简答题(每小题 5 分,共 15 分) 1、下列程序为用 VHDL 语言描述的上升沿触发的 T 触发器,请补全程序。 ⑴ ; USE IEEE.STD_LDGIC_1164.ALL; ENTITY tff IS PORT ( T,CP:IN STD_LOGIC; Q,NQ:OUT STD_LOOIC); END tff: ARCHITECTURE rtl OF tff IS SIGNAL q_temp:STD_LOGIC; BEGIN PROCESS( CP) BEGIN IF(CP 'EVENT AND CP = ' ⑵ ') THEN IF(T = '1') THEN q_temp <= NOT q_temp; ELSE q_temp <= q_temp; END IF; END IF; END PROCESS; Q <= q_temp; NQ <= NOT q_temp; END rtl; 答: (1) : (2) : 2、某 PLD 的内部逻辑阵列结构如图 1 所示,请写出输出端 Y 的函数关系式。 答:

…………….…………………………….密………………………………………封………………..…………………..线……………………………………..

2011─2012 学年 第 二 学期 《 数字电子技术 》课程考试试卷

专业:录井 年级Biblioteka 10 级 考试方式:闭卷 学分:2.5 考试时间: 110 分钟

学号

题号 得分

一

二

三

四

五

六

七

八

总分

姓名

阅卷人 得分

一、填空题 (每空 1 分,共 10 分) , 8421BCD 码表示

1 、十进制数 23.25 对应的十六进制表示为 为 。 2、2002 个“1”异或的结果为 。

'

3、逻辑函数 F AB CD 的对偶函数 F 。 4、时序逻辑电路中,输出信号仅是当前状态的函数,而与 无关的 电路称为 型时序逻辑电路。 5 、 VHDL 设 计 文 件 的 结 构 体 有 三 种 描 述 方 式 , 分 别 是 结 构 化 描 述 法 和 、 。 6、若要使 JK 触发器异步置 1,必须使 S D = 与输入信号 J、K 及时钟无关。 , RD = ,而

3、分析图 4 所示同步时序电路的功能。要求写出驱动方程、状态方程,画出状态转 换图,并检查能否自启动。

4、 74LS161 为四位二进制加法计数器。 请用 74LS161 和与非门设计一个三十二进制 的加法计数器。要求说明设计思路,画出状态转换图和相应的逻辑电路图。74LS161 的外部逻辑图如图 5 所示。

7、组合逻辑电路中的冒险—竞争是由于( )引起的。 A.、电路未达到最简 B、电路中的时延 C、电路有多个输出 D、逻辑门类型不同 8、 VHDL 程序中, 端口说明是对设计实体与外部接口的描述。 端口说明包括端口名、 通信模式和数据类型等三部分。其中,通信模式表明数据或信号通过端口的流动方 向,共有( )种通信模式。 A、2 种 B、3 种 C 、4 种 D、5 种 9、设计一个 8421BCD 码减法计数器,至少需要( )个触发器。 A、3 B、10 C 、6 D、4 10、电擦除、电可编程的可编程逻辑器件,其英文缩写是 ( ) 。 A、PROM B、EPROM C、EEPROM D、FLASH

第 5 页共 5 页

长江大学试卷

院(系、部)

专业

班级

姓名

学号

第 3 页共 5 页

3、已知电路图如图 2 所示,试作出 B、C 端的波形图。

阅卷人 得分

五、分析与设计(每小题 15 分,共 60 分)

1、某个由四选一数据选择器设计的逻辑电路如图 3 所示,请分析该电路实现的逻辑 功能。 (要求写出逻辑表达式,列出真值表,并用文字描述其逻辑功能。 )

2、某一火灾报警系统,设有烟雾、温度和红外光感三种不同类型的火灾探测器。为 了防止误报警,只有当其中两种或两种类型以上的探测器发出火灾探测信号时,报 警系统才产生报警控制信号,试用与非门设计产生报警控制信号的逻辑电路。 (要求 有适当的文字描述,列出真值表,写出逻辑表达式,并画出逻辑电路图。 )

第 4 页共 5 页