基于FPGA的视频信号发生器设计与应用研究

基于FPGA的信号发生器的设计与实现

基于FPGA的信号发生器的设计与实现作者:臧谱阳王正斌来源:《电脑知识与技术》2020年第27期摘要:该文详细介绍了一种通过DDS数字合成器技术,来实现一种频率,幅度,相位可调制的高精度信号发生器。

在FPGA中设计了串口模块和相应的解析模块向DDS发送指令,使其通过读取ROM内的波形数据存储器的数据进而实现对频率和相位的控制。

同时可以根据需要自行更换ROM内存储的波形数据,能够产生正弦波,方波,锯齿波和任意波形信号。

关键词:FPGA;DDS;信号发生器;串口;ROM中图分类号:TP311 文献标识码:A文章编号:1009-3044(2020)27-0220-02开放科学(资源服务)标识码(OSID):1 概述本系统以FPGA为核心控制器,相比于STM32系列单片机的顺序指令队列,FPGA强大的并行能力在处理模拟信号和拓展接口上效率会更高,读写速度也更快。

相比于传统C语言通过FLASH读取数组信息来获取波形数据,本系统通过读取片内ROM并结合DDS进行波形数据采集,设计方法更加简单灵活,波形的显示也会更流畅。

可以输出直流、交流等信号。

2 DDS技术原理与分析DDS(Direct Digital Synthesizer)是一种新型的频率合成技术,其主要组成部分有相位累加器,相位调制器,波形数据表和D/A转换器。

其广泛运用于通信领域,特点是波形选择范围大,可供选择带宽的范围大,可控制时间长,精度高等[1-2]。

对于信号的相位、频率、幅值均可以通过自制的波形编码生成,自由度大。

其基本结构见图1所示。

在每个时钟的上升沿时,加法器会将默认的频率控制字与同步寄存器中的相位值累加,得到的数值是由加法器和寄存器的位数决定的。

累加的值接着在第二个时钟上升沿时反馈至累加寄存器的输入端,重复与设定的频率控制字相加[3-5]。

这样,在每一个时钟周期,对设定的频率控制字不断进行线性累加,这时的累加值输出的数据就是最终处理信号的相位值,也是波形存储器的采样地址。

基于FPGA的函数信号发生器设计毕业设计(论文) 精品

基于FPGA的函数信号发生器设计摘要函数信号发生器是各种测试和实验过程中不可缺少的工具,在通信、测量、雷达、控制、教学等领域应用十分广泛。

随着我国经济和科技的发展,对相应的测试仪器和测试手段也提出了更高的要求,信号发生器己成为测试仪器中至关重要的一类。

本文在探讨函数信号发生器几种实现方式的基础上,采用直接数字频率合成(DDS)技术实现函数信号发生器。

在对直接数字频率合成(DDS)技术充分了解后,本文选择以Altera公司生产的FPGA芯片为核心,以硬件描述语言Verilog HDL为开发语言,设计实现了可以产生任意波形(以正弦波为例)和固定波形的(以方波和锯齿波为例)的函数信号发生器。

文中详细阐述了直接数字频率合成(DDS)、波形产生以及调幅模块的设计,并给出了相应的仿真结果。

本文最后给出了整个系统的仿真结果,即正弦波、方波、锯齿波的波形输出。

实验表明,用现场可编程门阵列(FPGA)设计实现的采用直接数字频率合成(DDS)技术的函数信号发生器,克服了传统方法的局限,实现了信号发生器多波形输出以及方便调频、调幅的功能。

关键词函数信号发生器;直接数字频率合成;现场可编程门阵列;Verilog HDLAbstractFunction Generator is an indispensable tool in a process of various tests and experiments. It is widely used in communication, measurement, radar, control, teaching and other fields. With the development of China's economic and technological, the corresponding test equipment and test methods are also put forward higher requirements, and the signal generator has become a vital test instrument.The article examines the several implementations of the function generator. And it has achieved the function generator which is completed by direct digital frequency synthesis (DDS) technology . Through understanding the direct digital frequency synthesis (DDS) technology, this paper chose to the Altera Corporations’ FPGA chips as the core of design. The function generator which can produce sine, square wave, sawtooth wave was designed. It also used hardware description language Verilog HDL as development language. The paper described the design of the main module, such as direct digital synthesizer (DDS), waveform generation and modulation module. And the corresponding simulation results were also presented.At last, the simulation results of the whole system were presented, that is, sine, square, sawtooth waveform has been carried out. Experiments show that the function generator based on FPGA and direct digital frequency synthesis (DDS)technology has overcame the limitations of traditional methods and achieved a signal generator which can generate multiple waveforms and has facilitate FM, AM function.Keywords Function Genenrator Direct Digital Freguency Synthesizer FPGA Verilog HDL目录1绪论 (1)1.1背景及意义 (1)1.2波形发生器研究现状 (1)1.2.1波形发生器的发展状况 (1)1.2.2国外波形发生器产品介绍 (2)1.3本设计的主要工作 (2)2系统基本原理 (4)2.1函数信号发生器的几种实现方式 (4)2.1.1程序控制输出方式 (4)2.1.2 DMA输出方式 (4)2.1.3可变时钟计数器寻址方式 (4)2.1.4直接数字频率合成方式 (4)2.2频率合成器简介 (5)2.2.1频率合成技术概述 (5)2.2.2频率合成器主要指标 (6)2.3 DDS原理 (6)2.3.1相位累加器 (7)2.3.2波形ROM (8)2.3.3 DDS频率合成器优缺点 (8)2.4现场可编程门阵列(FPGA) (9)2.4.1 FPGA简介 (9)2.4.2 FPGA特点 (9)2.4.3 FPGA工作状态 (10)2.4.4 FPGA的编程技术 (10)2.4.5 FPGA器件配置方式 (10)2.4.6使用FPGA器件进行开发的优点 (11)2.5 Verilog HDL语言简介 (11)3系统软件设计 (13)3.1编程软件的介绍 (13)3.1.1 Quartus II简介 (13)3.1.2 Quartus II设计流程 (13)3.2 Quartus II系统工程设计 (14)3.2.1创建工程 (14)3.2.2新建Verilog源文件 (15)3.2.3工程编译 (15)3.2.4生成模块电路 (15)3.2.5新建Block Diagram/Schematic File并添加模块电路 (16)3.2.6设计Vector Waveform File (16)3.3函数信号发生器的系统设计 (17)3.3.1系统总体设计 (18)3.3.2 FPGA系统设计流程 (18)3.3.3 FPGA系统模块设计 (19)4系统模块设计及仿真 (21)4.1频率寄存器模块设计 (21)4.2 DDS模块设计 (22)4.2.1 32位加法器 (22)4.2.2相位寄存器 (23)4.3波形产生模块设计 (24)4.3.1正弦波形ROM (24)4.3.2方波模块 (26)4.3.3锯齿波模块 (27)4.4调幅模块设计 (28)5系统调试 (30)5.1调试 (30)5.2仿真结果 (30)结论 (32)致谢 (33)参考文献 (34)附录 (35)附录1系统整体设计图 (35)附录2各模块源程序 (35)1绪论1.1背景及意义函数信号发生器是各种测试和实验过程中不可缺少的工具,在通信、测量、雷达、控制、教学等领域应用十分广泛。

基于fpga的信号发生器的设计与实现

科学技术创新2020.01基于FPGA 的信号发生器的设计与实现李岩方彬靳自璇赵勇彪张红岭(河北建筑工程学院电气工程学院,河北张家口075000)1概述现阶段,函数信号发生器已成为现代测试领域应用最为广泛的通用仪器之一。

随着数字技术在仪器仪表和通信系统中的广泛使用,可从参考频率源产生多个频率的数字控制方法诞生了,即直接数字频率合成(DDS)。

FPGA (现场可编程门阵列)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS 技术,极大地提高了函数信号发生器的性能,大大降低了电子系统的生产成本。

传统的信号发生器设计方案是采用模拟电路、单片机或DDS 专用芯片来实现,虽然有着广泛的应用,但仍然存在着许多缺陷,例如,设计方案成本高、输出波形的种类少、输出信号的频率控制不灵活、系统升级困难等。

而且传统的信号发生器还有两个突出问题,一个是通过电位器的调节来实现输出频率的调节,很难将频率调到某一固定值;另一个是脉冲的占空比不可调节。

随着现代科学技术的飞速发展,用户对函数信号发生器提出了越来越高的要求,例如高分辨率、高输出频率等要求,传统的信号发生器已经无法满足这些要求。

不论是在生产、实验还是在科研与教学上,信号发生器都是用于仿真实验的最佳工具。

因此开发新型信号发生器具有重大意义。

本文提出了一种新型的以FPGA 为核心的DDS 信号发生器设计,充分利用uc/GUI 控制方式灵活、FPGA 芯片运算处理速度快的优点,能够通过图形用户界面很好地实现频率、相位、幅度可调、波形变换并且输出信号质量和精确度高于直接模拟频率合成技术和锁相环式频率频率合成技术。

弥补了传统信号发生器设计方案成本高、输出波形的种类少、输出信号的频率控制不灵活、系统升级困难等缺陷。

2信号发生器设计原理2.1直接数字频率合成技术的基本原理DDS 是一种用于通过单个固定频率的参考时钟信号生成任意波形的频率合成器,必须考虑所有与采样相关的问题,包括量化噪声、混叠、滤波等。

基于FPGA的高清视频信号输出扩展卡的设计与实现的开题报告

基于FPGA的高清视频信号输出扩展卡的设计与实现的开题报告一、选题背景与意义随着高清视频技术的不断进步,高清视频已经逐渐普及到人们的生活中,成为人们娱乐和工作中不可或缺的一部分。

同时,随着FPGA技术的不断成熟,FPGA已经广泛应用于高速数据传输、数码信号处理、嵌入式系统等领域,成为具有较高性能和灵活性的硬件设计平台。

本课题旨在研究基于FPGA的高清视频信号输出扩展卡的设计与实现,提供一种高清视频信号输出解决方案,满足高清视频处理的需求,同时也为FPGA技术在高清视频领域的应用提供了一个实践平台。

二、研究目标本课题的主要研究目标如下:1.设计一款基于FPGA的高清视频信号输出扩展卡,能够实现高清视频信号的输出,并具备信号调节、时序处理等功能;2.实现基本的高清视频信号处理算法,包括缩放、裁剪、色彩空间转换、图像滤波等;3.实现基于FPGA的高速数据传输模块,通过高速数据传输模块将处理后的视频信号输出至扩展卡接口,实现高清视频信号的稳定输出。

三、研究内容本课题的主要研究内容如下:1. FPGA技术与高清视频信号处理的理论基础研究,包括高清视频信号的特点、高清视频信号处理技术、FPGA技术的基本原理等;2. 设计高清视频信号输出扩展卡的硬件系统,包括高清视频信号输入模块、显示控制模块、高速数据传输模块等;3.实现高清视频信号处理算法模块,包括图像缩放、裁剪、色彩空间转换、图像滤波等,提高视频信号输出的质量和效率;4.测试和验证实现的高清视频信号输出扩展卡的性能,包括输出信号质量、输出速度、功耗等。

四、研究方法本课题主要采用以下研究方法:1.文献综述法,对相关领域的理论和技术进行梳理和分析,为后续的研究提供基础和指导;2.硬件设计方法,采用模块化设计思想,将高清视频信号处理的各个模块进行分离和设计,最终实现高清视频信号输出扩展卡;3.软件设计方法,利用硬件描述语言(VHDL或Verilog)对设计的各个模块进行编程实现,完成高清视频信号处理算法模块等;4.测试和验证方法,通过实际测试和验证,分析和评估实现的高清视频信号输出扩展卡的性能和效果。

基于FPGA的实用多功能信号发生器的设计与制作

基于FPGA的实用多功能信号发生器的设计与制作基于FPGA的实用多功能信号发生器的设计与制作摘要多功能信号发生器已成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。

直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。

由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。

本文首先介绍了函数信号发生器的研究背景和DDS的理论。

然后详尽地叙述了利用Verilog HDL描述DDS模块的设计过程,以及设计过程中应注意的问题。

文中详细地介绍了多种信号的发生理论、实现方法、实现过程、部分Verilog HDL代码以及利用Modelsim仿真的结果。

文中还介绍了Altera公司的DE2多媒体开发平台的部分功能及使用,并最终利用DE2平台完成了多功能信号发生器的大部分功能。

包括由LCD显示和按键输入构成的人机界面和多种信号的发生。

数字模拟转换器是BURR-BROWN 公司生产的DAC902。

该信号发生器能输出8种不同的信号,并且能对输出信号的频率、相位以及调制信号的频率进行修改设定。

关键词:信号发生器;DDS;FPGA;DE2Practical FPGA-based multi function signal generatordesign and productionAbstractMulti function signal generator has become the most widely used in modern testing field of general instrument, and has represented one of the development direction of the source. Direct digital frequency synthesis (DDS) is a totaly digital frequency synthesis technology, which been put forward in the early 1970s. Using a look-up table method to synthetic waveform, it can satisfy any requirement of waveform produce. Due to the field programmable gates array (FPGA) with high integrity, high speed, and large storage properties, it can realize the DDS technology effectively, increase signal generator’s performance and reduce production costs.Firstly, this article introduced the function signal generator of the research background and DDS theory. Then, it described how to design a DDS module by Verilog HDL, and introduced various signal occurs theory, method and the implementation process, Verilog HDL code and simulation results.This paper also introduces the function of DE2 multimedia development platform, and completed most of the functions of multi-function signal generator on DE2 platform finally. Including the occurrence of multiple signal and the man-machine interface which composed by LCD display and key input. Digital-to-analog converters is DAC902, which produced by company BURR-BROWN.This signal generator can output eight different kinds of signals, and the frequency of the output signal, phase and modulation frequency signal also can be modifyed.Key Words: Signal generator; DDS; FPGA; DE2目录论文总页数:34页1 引言 (1)1.1课题背景 (1)1.2国内外波形发生器的发展现状 (1)1.3本文研究的主要内容 (2)2 信号发生器原理 (2)2.1直接数字频率合成技术的基本原理 (2)2.2相位偏移控制 (3)2.3多种信号的发生 (3)2.3.1方波的发生 (3)2.3.2三角波发生 (4)2.2.3锯齿波发生 (4)2.3.4 PWM信号发生 (4)2.3.5 SPWM信号发生 (5)2.3.6 AM信号发生 (5)2.3.7 FM信号发生 (6)2.4DDS的特点 (7)2.4.1 DDS 的优点 (7)2.4.2 DDS 系统的缺点 (7)3 系统整体设计 (8)3.1硬件部分 (8)3.1.1 DE2实验板 (8)3.1.2 LCD模块 (9)3.1.2 DAC902 (11)3.2基于VERILOG的FPGA设计 (12)3.3软件工具 (12)3.3.1 Modelsim (12)3.3.2 Quartus (12)3.4系统设计 (13)3.4.1 系统初始化模块 (13)3.4.2按键模块和LCD模块 (13)3.4.3 RAM模块 (14)3.4.4数据转换模块 (15)3.4.5 DAC驱动模块 (15)3.4.6系统的运行 (15)4 VERILOG HDL代码实现与仿真 (15)4.1信号发生器模块 (15)4.1.1频率控制字和相位累加器 (15)4.1.2 相位偏移控制 (16)4.1.3正弦波发生模块 (17)4.1.4 方波发生模块 (17)4.1.5 三角波发生模块 (18)4.1.6 锯齿波发生模块 (18)4.1.7 PWM信号发生模块 (19)4.1.8 SPWM信号发生模块 (19)4.1.9 AM信号发生模块 (20)4.1.10 FM信号发生模块 (21)4.2按键输入模块 (22)4.3LCD显示模块 (23)4.4RAM模块 (24)4.5数据转换模块 (25)5 系统测试 (26)5.1控制及显示部分测试 (27)5.2输出频率测试 (27)5.3信号发生测试 (28)5.3.1 正弦波、方波、三角波、锯齿波测试 (28)5.3.2 PWM信号测试 (29)5.3.3 SPWM信号测试 (29)5.3.4 AM信号测试 (29)5.3.5 FM信号测试 (30)结论 (31)参考文献 (32)致谢...................................................... 错误!未定义书签。

基于FPGA的视频信号发生器设计与应用研究

摘

要: 本文介绍 了一种基于 F G P A的新型视频信号发生器 , 它可 以满足 多种被测 系统对 输入视频 信号制 式 的要求 。该 系统

利用 U B总线 与上位机进行通 信 , S 同时解决 了系统供 电的 问题 。在 F G P A内部 , 通过软件编程 的方法生成视频信号 的图像 和时 序控制信号 , 并送入视频 D A模块 。通过实验对该视频信号发生器在 电视跟踪性 能检测 中 的应 用进行研 究 , 取并 分析 了被 / 获

2 T e Sa e K y L b r t r h t t e a o a oy P e i o a u e n e h o o y a d I sr me t ,De a t n r c i n Me s rme tT c n lg n n t s u ns pr e m t P e i o n tu ns rc inI rm t s s e

,

Tig u nvrt, ei 0 0 4 C i ) s ha U i sy B r g1 08 , hn n ei n a

Ab ta t sr c :A e t p fvde in lg n r trb s d o PGA sp e e td. I g n r ts s v r lkid fv d osg n w y e o i o sg a e e ao a e n F i r s ne t e e a e e ea n s o i e i—

n l o me tt n u e ur me so s ie y tmsu d rts .Th sg n r trc mmu ia e t C hr u h a st e hei p tr q ie nt fmo tvd o s se n e e t i e e ao o n c tswi a P t o g h USB po t n hi t o o l lo s le t e p o lm fp we u pl r ,a d t smeh d c u d as o v h r b e o o rs p y.I h GA,t e g n r trc u d g n r t n t e FP h e e a o o l e e ae i g nd s q e c o to sg a tr u h s fwa e r g a ,a d e d t e in l t v d o ma e a e u n e c n r l in l h o g o t r p o r m n s n h sg a s o i e D/A d l T n mo u e. he

基于某FPGA的信号发生器的设计

前言信号发生器是实验室的常用仪器之一,设计信号发生器具有实际应用的意义。

而采用FPGA的方法设计信号发生器可以产生频率比较高的信号,例如频率为几M的正弦波。

通常正弦波产生的方法是采用MCU+DDS的方法,但是由于DDS 的造价比较高,所以在指标要求不高的情况下,可以使用FPGA来实现DDS频率合成的原理来产生较高频率的正弦波,任意波形的信号也是如此。

课题《基于FPGA的信号发生器的设计》主要研究容为DDS基数及其FPGA 的实现。

其目的在于让设计者能掌握DDS的原理及其设计思路,具体的了解EDA 技术流程,熟悉硬件描述语言设计功能电路,并最终检验设计的设计能力。

随着我国的经济日益增长,社会对电子产品的需求量也就越来越大,目前,我国的电子产品市场正在迅速的壮大,市场前景广阔。

FPGA(Field Programmable Gate Array,现场可编程门阵列)在现代数字电路设计中发挥着越来越重要的作用。

FPGA/CPLD(Complex Programmable Logic Device)所具有的静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改,这样就极大地提高了电子系统设计的灵活性和通用性,缩短了产品的上市时间并降低可电子系统的开发成本,且可以毫不夸地讲,FPGA/CPLD能完成任何数字器件的功能,从简单的74电路到高性能的CPU。

它的影响毫不亚于20世纪70年代单片机的发明和使用。

现在随着电子技术的发展,产品的技术含量越来越高,使得芯片的复杂程度越来越高,人们对数万门乃至数百万门设计的需求也越来越多,特别是专用集成电路(ASIC)设计技术的日趋进步和完善,推动了数字系统设计的迅速发展。

仅靠原理图输入方式已不能满足要求,采用硬件描述语言VHDL的设计方式应运而生,解决了传统用电路原理图设计大系统工程时的诸多不便,成为电子电路设计人员的最得力助手。

设计工作从行为、功能级开始,并向着设计的高层次发展。

基于FPGA的信号发生器设计

基于FPGA的信号发生器设计 以FPGA 芯片为载体,通过QuartusII 的LPM_ROM 模块和VHDL 语言为核心设计一个多功能信号发生器,根据输入信号的选择可以输出递增锯齿波、递减锯齿波、三角波、阶梯波和方波等5 种信号,通过QuartusII 软件进行波形仿真、定时分析,仿真正确后,利用实验板提供的资源,下载到芯片中实现预定功能。

信号发生器又称为波形发生器,是一种常用的信号源,广泛应用于电子电路、通信、控制和教学实验等领域。

它是科研及工程实践中最重要的仪器之一,以往多用硬件组成,系统结构比较复杂,可维护性和可操作性不佳。

随着计算机技术的发展,信号发生器的设计制作越来越多的是用计算机技术,种类繁多,价格、性能差异很大。

用FPGA 或CPLD 来实现,它的优点是可以进行功能仿真,而且FPGA 和CPLD 的片内资源丰富,设计的流程简单。

用FPGA 所构成的系统来产生波形信号,这个系统既能和主机系统相连,用相应的上层软件展示波形信号,又方便程序的编写,而且还有A/D0809接口可以产生模拟信号的输出和外面的示波器相连。

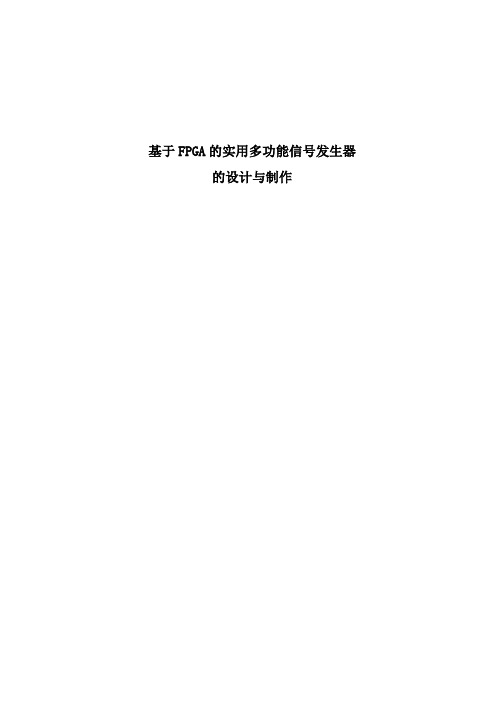

1 正弦信号发生器的LPM 定制 正弦信号发生器由计数器或地址发生器(6 位)、正弦信号数据ROM (6 位地址线,8 位数据线,含有64 个8 位数据,一个周期)、原理图顶层设计和8 位D/A (实验中用DAC0832 代替)。

其框图如图1 所示。

其中信号产生模块将产生所需的各种信号,这些信号的产生可以有多种方式,如用计数器直接产生信号输出,或者用计数器产生存储器的地址,在存储器中存放信号输出的数据。

信号发生器的控制模块可以用数据选择器实现,用8 选1 数据选择器实现对5 种信号的选择。

图1 信号发生器结构框图 最后将波形数据送入D/A 转换器,将数字信号转换为模拟信号输出。

用示波器测试D/A 转换器的输出,可以观测到5 种信号的输出。

1.1 定制初始化数据文件 QuartusII 能接受的LPM_ROM 模块中的初始化数据文件的格式有两种:。

毕业设计(论文)-基于fpga的函数信号发生器的设计与实现[管理资料]

![毕业设计(论文)-基于fpga的函数信号发生器的设计与实现[管理资料]](https://img.taocdn.com/s3/m/e1d8101a81c758f5f61f67f8.png)

基于FPGA的函数信号发生器的设计与实现摘要波形发生器己成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。

直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。

由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。

本文首先介绍了函数波形发生器的研究背景和DDS的理论。

然后详尽地叙述了用FPGA完成DDS模块的设计过程,接着分析了整个设计中应处理的问题,根据设计原理就功能上进行了划分,将整个仪器功能划分为控制模块、外围硬件、FPGA器件三个部分来实现。

最后就这三个部分分别详细地进行了阐述。

本文利用Altera的设计工具QuartuSH并结合VeI’i1og一HDL语言,采用硬件编程的方法很好地解决了这一问题。

论文最后给出了系统的测量结果,并对误差进行了一定分析,结果表明,,、三角波、锯齿波、方波,通过实验结果表明,本设计达到了预定的要求,并证明了采用软硬件结合,利用FPGA技术实现波形发生器的方法是可行的。

关键词:函数发生器,直接数字频率合成,现场可编程门阵列The Design and Realize of DDS Based on FPGAAbstractArbitrary Waveform Generator(AWG) is one of the most popular instruments in modern testing domains,Which represents the developing direction of signal sources· Direct Digital frequency Synthesis(DDS) advance dearly in full digital technology for frequency synthesis,its LUT method for synthes waveform .Adapts togenerate arbitrary Waveform· Field programable GateArray(FPGA)has the feature sof Iargeseale integration,high working frequency and ean realize lal’ge Memory,50FPGAeaneffeetivelyrealizeDDS.The of Corporation Altera ehosen to do the main digitalProcessing work,which based on its large sale and highs Peed. The 53C2440MCU ehosenasa control ehip· Inthisdesign,how to design the fpga chip and theInter faee between the FPGA and the control ehiP the the method ofSoftware and hardware Programming,the design used the software Quartus11 and languageverilog一HDL solves ,the PrineiPle of DDS and Basis of EDA technology introdueed Problem is the design are analyzed and the whole fun into three Parts:masterehiP,FPGA deviee and PeriPheral three Parts are described indetail disadvantage and thing sneed toadv anceareal Of the dissertation,or asquare wave with in the frequency rangeto20MHz .Planed and the way to use software and hardware Programming method and DDS Technology to realize Functional Waveform Generatoravailable.Keywords:DDS;FPGA;Functional Waveform Generator目录第一章绪论 ................................................ IV ............................................................................................................... IV ................................................................................................................. V ......................................................................................................... V....................................................................................................... VI .............................................................................................................. VII ...................................................................................................... VIIDMA输出方式.......................................................................... VII...................................................................................................... VII..................................................................................................... V III 第二章直接数字频率合成器的原理及性能 ................................................ I .................................................................................................................. I .......................................................................................................... I......................................................................................................... I I DDS原理 ............................................................................................. I II 第三章基于FPGA的DDS模块的实现 .......................................................... I (FPGA)简介 ............................................................................................. I II软件并建立工程 ....................................................................... I I新建Block Diagram/Schematic File并添加模块电路。

基于FPGA的数字电视信号发生器的设计与实现.

基于FPGA的数字电视信号发生器的设计与实现电视信号的数字化使得数字电视设备越来越受到广大电子消费者的青睐,如何选择自己理想的数字电视产品,也成了消费者关心的问题,评价、测试电视系统与设备运行的质量状况成为广播电视行业所关注的热点。

而数字电视信号发生器能提供可视的测试图像信号,直观、快捷的测试方法,因此,数字电视信号发生器成为目前电子设计的热门研究课题,他在数字电视节目制作播出、科研、生产以及售后服务过程中起着不可或缺的作用。

本文设计了一种基于FPGA 的数字电视信号友生器,该信号发生器以一种单芯片多配置的方案,针对系统各部分功能特性和性能进行选片没计,并利用FPGA内部存储资源来生成各种测试信号的图像。

1数字电视信号发生器的功能与原理1.1 系统功能数字电视信号发生系统的主要任务是产生符合SMPTE274M系统标准的18种数字信号测试图像,YPbPr,RGB两种视频输出接口符合ITU-R BT.1120-2/GY/T157-2000演播室高清晰度数字视频信号接口标准。

本系统的核心是图像信号的编码发生单元FPGA,采取单芯片多配置方案可使18种图像信号方便地进行配置与加密。

人机界面由单片机控制,可快速地进行图像切换和格式转换。

在普通电源接入下,系统需生成支持SMPTE274M系统标准中的1080I 60 Hz,1080I 50 Hz,1080P 60 Hz、1080P 50 Hz四种标准格式的18种高清晰度电视通用测试图像的数字输出信号和模拟输出信号,其标准测试信号的数码发生内核基于FPGA平台实现。

在此基础上,本系统提供了一个人工可控功能,即用户可根据按键,对以上4种标准的18种测试图案进行切换控制。

考虑到输出信号的实用性,输出的模拟测试信号和数字测试信号都必须满足相应的接口标准。

为满足以上约束条件,系统功能设计如图1所示。

1.2信号产生的原理数字电视也是彩色电视(只是信号的表示形式及信号的处理方法与模拟电视有所不同),因此在考虑数字电视测试信号发生器包含哪些(测试信号)内容时,本文根据彩色电视的基本特点,首先应考虑包含一般彩色电视广播测试图的基本内容,例如观察显示设备扫描非线性失真和几何失真的棋盘信号和圆信号,观察图像清晰度和分辨率的多波群或扫频信号,观察亮度非线性失真情况以及显示器白平衡调整是否正确的灰度级(或阶梯波)信号,观察彩色重现是否正确的彩条信号等;另外还考虑增加了在视频测量中最常用的2T脉冲信号、彩色多波群信号和彩色阶梯波信号,以及更为直观的斜波信号等,以便全面地观察和评价彩色电视系统或设备的基本质量。

基于FPGA的线性调频信号产生器设计

基于FPGA的线性调频信号产生器设计摘要:本文在研究DDWS原理的基础上,给出了一种基于FPGA技术的线性调频信号产生器的设计方案。

采用FPGA技术可以方便地通过修改编程参数,对线性调频信号的起始频率、带宽、频率分辨率进行修改。

仿真结果表明,该设计能够产生符合要求的线性调频信号,并且具有结构简单、集成度高、易于修改等特点。

关键词:FPGA;线性调频;DDWS;线性调频(LFM)信号由于其时宽带宽积远大于1,通过脉冲压缩处理,可以得到良好的距离分辨率和径向速度分辨率,因此在合成孔径雷达、高分辨力雷达、线性调频连续波雷达、雷达高度表等现代雷达系统中得到广泛应用,用于产生LFM 信号的系统称之为线性调频信号产生器。

DDWS技术是近年来采用的生成稳定的点频、线性调频信号的理想方法,具有幅度和相位一致性好、频率转换时间短、频率分辨率高、输出频率相对带宽较宽、输出波形相位连续、电路设计简单、可靠性高等突出的优点。

1 DDWS技术工作原理与特点1.1 DDWS技术工作原理直接数字波形合成技术主要分为两个阶段,存储波形和还原波形。

存储波形是将我们所需要的输出信号波形,由上位机仿真软件按照采样率、带宽和时宽等参数计算出信号波形中各个采样点的值,经量化和编码存储至高速存储器中。

还原波形时,由系统时钟提供一个参考时钟给时钟控制逻辑,时钟控制逻辑分别控制地址控制逻辑和D/A转换。

1.2 DDWS技术的特点1)极高的频率分辨率:在满足奈奎斯特定理情况下,DDWS技术产生信号的频率分辨率仅由D/A转换器件的位宽决定。

D/A转换器的位宽越大,信号的频率分辨率越高。

本文拟产生的LFM信号频率范围是0~150 MHz, 根据奈奎斯特定理,D/A转换器的转换速率应>300 MSPS。

2)极短的频率转换时间:由DDWS技术的原理框图可知,输出信号的波形存储于高速存储器中,切换不同频率的信号时,频率转换时间由高速存储器读取决定,读取时间可达皮秒量级。

基于FPGA的实时视频信号处理系统设计

基于FPGA的实时视频信号处理系统设计随着科技的不断发展,视频信号处理技术变得越来越重要,以满足人们对高清晰度和高数据传输速率的需求。

FPGA是一种灵活性和可编程性非常强的芯片,已经成为设计高性能视频信号处理器的首选工具。

本文将探讨基于FPGA的实时视频信号处理系统设计。

1. FPGA的应用FPGA是Field Programmable Gate Array的缩写,即现场可编程门阵列。

它是由一系列可编程逻辑门和存储单元组成的芯片。

FPGA的灵活性和可重构性使它成为设计高性能数字信号处理器的首选工具之一。

FPGA被广泛应用于通信、计算机视觉、音视频处理、医学图像处理等领域。

在视频处理中,FPGA因其可以同时进行多种操作的能力而备受关注。

同时,FPGA还可以通过并行处理和流水线技术来提高视频处理的速度。

2. 实时视频信号处理系统的需求实时视频信号处理系统需要应对的挑战主要包括:(1)高处理速度:视频信号的数据量非常大,需要高效地处理数据。

(2)低延迟:视频信号需要在接收后立即处理,否则就可能出现冲突,影响传输的质量。

(3)高质量输出:处理后的视频信号需要清晰、流畅地显示。

(4)低成本:由于市场竞争激烈,生产商需要在保证性能的前提下,尽可能降低成本。

以上所有挑战都需要在实时视频信号处理系统的设计中得到充分考虑。

3. 基于FPGA的实时视频信号处理系统构成基于FPGA的实时视频信号处理系统一般由以下组件构成:(1)视频采集器:负责从摄像头、DVD、电视等源设备中采集视频数据。

此时数据是模拟信号,需要进行模数转换。

(2)FPGA:负责处理经过模数转换后的数字信号。

它可以解码、压缩、裁剪和调整视频信号以使其满足各种需求。

(3)视频输出器:处理后的视频信号将被发送到显示设备上,例如电视或计算机监视器。

4. FPGA在实时视频信号处理系统中的应用(1)视频编解码器处理:FPGA可以高效地对视频进行编解码。

视频信号的压缩可以使存储更为轻松,通过解码得到的视频也会更加流畅。

基于FPGA的信号发生器的设计

前言信号发生器是实验室的常用仪器之一,设计信号发生器具有实际应用的意义。

而采用FPGA的方法设计信号发生器可以产生频率比较高的信号,例如频率为几M的正弦波。

通常正弦波产生的方法是采用MCU+DDS的方法,但是由于DDS 的造价比较高,所以在指标要求不高的情况下,可以使用FPGA来实现DDS频率合成的原理来产生较高频率的正弦波,任意波形的信号也是如此。

课题《基于FPGA的信号发生器的设计》主要研究内容为DDS基数及其FPGA 的实现。

其目的在于让设计者能掌握DDS的原理及其设计思路,具体的了解EDA 技术流程,熟悉硬件描述语言设计功能电路,并最终检验设计的设计能力。

随着我国的经济日益增长,社会对电子产品的需求量也就越来越大,目前,我国的电子产品市场正在迅速的壮大,市场前景广阔。

FPGA(Field Programmable Gate Array,现场可编程门阵列)在现代数字电路设计中发挥着越来越重要的作用。

FPGA/CPLD(Complex Programmable Logic Device)所具有的静态可重复编程和动态在系统重构的特性,使得硬件的功能可以像软件一样通过编程来修改,这样就极大地提高了电子系统设计的灵活性和通用性,缩短了产品的上市时间并降低可电子系统的开发成本,且可以毫不夸张地讲,FPGA/CPLD能完成任何数字器件的功能,从简单的74电路到高性能的CPU。

它的影响毫不亚于20世纪70年代单片机的发明和使用。

现在随着电子技术的发展,产品的技术含量越来越高,使得芯片的复杂程度越来越高,人们对数万门乃至数百万门设计的需求也越来越多,特别是专用集成电路(ASIC)设计技术的日趋进步和完善,推动了数字系统设计的迅速发展。

仅靠原理图输入方式已不能满足要求,采用硬件描述语言VHDL的设计方式应运而生,解决了传统用电路原理图设计大系统工程时的诸多不便,成为电子电路设计人员的最得力助手。

设计工作从行为、功能级开始,并向着设计的高层次发展。

基于FPGA的信号发生器的设计

值、 时钟分频等 ; 外围电路主要为波形 、 频率 、 幅值控制 电路和数据转换 电路 , 完成显示信息及控制波形数据

的模块输 出等功能 - 。当波形输出后 , 经过一个 D 转 A

换, 将数字信 号转换为模拟信号的输出信号I 。

3 基 于 F GA的信 号发 生器建 模设 计 P

. .

武晓栋 郑 宾 雷竹峰 , ,

太原 0 0 5 ) 30 1

(. 1 中北大学 电子测试技术 围家重点 实验 室; . 大学 机械丁程与 自动化学院 , 2 中北 山两

摘

要: 文章详 细介 绍 了基 于F G P A的信 号发 生器 系统 的构造及其设 计原理 。 系统基 于模块化 设计 ,ur sI Q a u 1为 t

31 信 号 发 生器设 计 F G . P A内部 的整 体结 构

设 计 采 用 自上 而 下 的切 割 重组 设 计 方 法 。利 用

F G P C Q 4 C 构成的信号发生 器的基本框图 , P AE 1 6 20 8

见图 3

根据本设计的整体结构 , 结合设计 目 和要求 , 标 本 设计的系统工作原理 , 图 1 见 和图 2 。

图 4 初 值模块

2 模块分频程序及功能 : ) 模块 F N A A见图 5 的功 能是将初值对时钟进行分频 , 得到不同的工作频率 , 从 而调节波形频率。本设计选用 5 H 为基准频率 , 0 z M 每

6 个 时 钟为一 个周 期 。 4

. 一三角 I 波

择I

姜I

图 3 E 1 6 4 C 构 成的信 号源的基本框图 P Q2 0 8 C

32 使 用 Qur sI .完成 各模 块设计 与仿 真 . at 0 u I8

基于FPGA的信号发生器

数字信号发生器实验设计报告摘要:使用数字芯片特别是可编程逻辑器件来实现看似复杂的功能电路往往既简单又节省资源。

典型信号如:方波,锯齿波,三角波,正弦波等在实验或工程中应用极广,所以本实验使用VHDL 及原理图相结合的方法在FPGA 上实现数字信号的发生。

关键字:VHDL,FPGA,信号发生 一、设计方案:(1)方波,锯齿波,三角波均由计数器结合条件语句实现; (2)正弦波采用定制ROM,然后通查找表的方法实现; (3)使用多选一选择器选择四种波型之一;(4)输出波型的频率由分频程序对输入波频率进行分频而得,分频数由按键输入二进制数实现。

二、方案实现: ①方波:library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity pulse isport(fclk,reset: in std_logic;d_out: out std_logic_vector(7 downto 0)输入方波信号分频模块方波锯齿波三角波正弦波四选一多路选择器D A 转换模拟 波形分频数2341按键);end pulse;architecture behave of pulse issignal a: std_logic;beginprocess(fclk,reset)variable tmp: std_logic_vector(7 downto 0); beginif reset='1' thena<='0';elsif rising_edge(fclk) thenif tmp="11111111" thentmp:="00000000";elsetmp:=tmp+1;end if;if tmp<="10000000" thena<='1';elsea<='0';end if;end if;end process;process(fclk,a)beginif rising_edge(fclk) thenif a='1' thend_out<="11111111";elsed_out<="00000000";end if;end if;end process;end behave;②锯齿波:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity juchi isport(fclk: in std_logic;reset: in std_logic;d_out: out std_logic_vector(7 downto 0) );end juchi;architecture arch of juchi issignal da: std_logic_vector(7 downto 0);beginprocess(fclk,reset,da)beginif reset='1' thenda<="00000000";elseif fclk='1' and fclk'event thenif da<255 thenda<=da+1;else da<="00000000";end if;end if;end if;end process;d_out<=da;end arch;③三角波:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity rectangle isport(fclk,reset: in std_logic;d_out: out std_logic_vector(7 downto 0));end rectangle;architecture behave of rectangle isbeginprocess(fclk,reset)variable tmp: std_logic_vector(7 downto 0);variable a: std_logic;beginif reset='1' thentmp:="00000000";elsif rising_edge(fclk) thenif a='0' thenif tmp="11111110" thentmp:="11111111";a:='1';elsetmp:=tmp+1;end if;elseif tmp="00000001"thentmp:="00000000";a:='0';elsetmp:=tmp-1;end if;end if;end if;d_out<=tmp;end process;end behave;④正弦波:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity sinadd isport(fclk,reset: in std_logic;address: out std_logic_vector(5 downto 0));end sinadd;architecture behave of sinadd isbeginprocess(fclk,reset)variable cnt: std_logic_vector(5 downto 0):="000000"; beginif reset='1' thencnt:="000000";elseif fclk='1' and fclk'event thencnt:=cnt+1;end if;end if;address<=cnt;end process;end behave;⑤分频:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin isport ( clk: in std_logic;reset: in std_logic;fclk: out std_logic;keyya,keyyb,keyyc,keyyd: in std_logic);end entity;architecture behave of fenpin issignal fclkk:std_logic;signal cnt: std_logic_vector(3 downto 0);signal cntt: std_logic_vector(3 downto 0);begincntt<=keyya&keyyb&keyyc&keyyd;process(clk,reset)variable cnt: std_logic_vector(3 downto 0);beginif(reset='1') thenfclkk<='0';cnt:=(others=>'0');elseif(clk'event and clk='1') thenif(cnt=cntt) thencnt:=(others=>'0');fclkk<= not fclkk;elsecnt:=cnt+1;end if;end if;end if;fclk<=fclkk;end process;end behave;e;⑥波形选择:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity wav_sel isport(keya,keyb: in std_logic;d_in0,d_in1,d_in2,d_in3: in std_logic_vector(7 downto 0); d_out: out std_logic_vector(7 downto 0));end wav_sel;architecture behave of wav_sel issignal key: std_logic_vector(1 downto 0);beginkey<=keya&keyb;with key selectd_out<=d_in0 when "00",d_in1 when "01",d_in2 when "10",d_in3 when "11","00000000" when others;end behave;⑦顶层设计文件(原理图):三、实验现象(使用Signal Tap II):正弦波:方波:锯齿波:三角波:四、实验数据:时钟输入为50MHz:波形参数方波最小频率:最大频率:锯齿最小频率:最大频率:三角最小频率:最大频率:正弦最小频率:最大频率:五、芯片资源占用情况:。

基于FPGA的视频信号发生器设计

基于FPGA的视频信号发生器设计

摘要:目前数字相机逐步取代模拟相机应用在光电测量设备中,因此图像处理器也逐渐转化为接收数字视频的接口,对数字图像处理器检测的信号发生器的研制也变得十分迫切。

本文介绍了一种基于FPGA的两种数字视频格式输出的视频发生器,它可以产生LVDS制式的数字视频信号和CamerLink制式的数字视频信号,而且可以通过串口对产生的视频中的目标大小、运动速度、灰度及背景灰度进行实时更改。

它满足了对数字视频输入的图像处理平台的检测,具有一定应用前景。

关键词:现场可编程门阵列;视频发生器;LVDS;图像处理平台

0 引言

在光电测量系统中,需要图像处理器进行图像采集、处理。

而为了对图像处理器的图像采集能力及处理能力进行评估、检测,常常需要对图像处理器输入特定视频,进行各项功能测试。

目前随着数字化相机的广泛应用,图像处理器多采用数字化接口。

而且对图像处理器的检测要求信号发生器产生的视频内容越来越丰富,帧频越来越高,而目前检测图像处理器的信号发生器多是标准的模拟视频输出,如文献提出的模拟视频发生器,有的虽然能产生数字视频但内容是固定的,如果对内容进行更改则需要对数字视频信号发生器重新编程以达到要求,比较麻烦,不能满足日益复杂的要求。

因此灵活改变视频内容的数字视频信号发生器的研制变得十分迫切。

本文提出一种数字视频信号发生器的设计方法,此方法可以同时得到LVDS和CamerLink制式。

基于FPGA的函数信号发生器设计

基于FPGA的函数信号发生器设计函数信号发生器是一种能够产生不同类型信号的测试设备,通常在电子电路实验中使用。

基于FPGA的函数信号发生器设计利用可编程逻辑器件FPGA,可以实现更高的灵活性和可定制性,同时减少了硬件开发成本。

本文将详细介绍基于FPGA的函数信号发生器的设计原理、主要模块和实现方法。

一、设计原理二、主要模块1.时钟生成器模块:时钟信号是产生各种信号波形的基础,因此需要设计一个时钟生成器模块来产生稳定的时钟信号。

可以使用FPGA内部的锁相环(PLL)或计数器来实现。

2.波形选择模块:为了产生不同类型的信号波形,需要设计一个波形选择模块。

通过该模块,用户可以选择所需的信号波形,如正弦波、方波、三角波等。

3. 波形生成模块:根据用户的选择,使用FPGA内部的逻辑门电路来实现不同类型的信号波形的生成。

可以利用查找表(Look-Up Table,简称LUT)来存储不同波形的采样点数据,并通过控制逻辑将这些数据输出为相应的信号波形。

4.频率控制模块:通过频率控制模块,可以对信号波形的频率进行控制。

可以根据用户的输入,通过改变时钟信号的频率或改变波形采样点的间隔来实现频率的调节。

5.幅值控制模块:通过幅值控制模块,可以对信号波形的幅值进行控制。

可以通过改变逻辑门的阈值电压或者改变DAC(数字模拟转换器)的输出电平来实现幅值的调节。

三、实现方法2.硬件设计:根据设计需求,选择合适的FPGA芯片、外部时钟源、AD/DA转换器等外部器件。

根据电路原理图,进行相应的电路布局和连线。

在确认电路无误后,进行焊接和组装工作。

在软件和硬件设计完成后,可以通过控制板上的按钮、旋钮等输入设备来调节信号波形的频率、幅值等参数,从而实现不同类型的信号波形的生成。

总结:基于FPGA的函数信号发生器设计利用FPGA的可编程特性,可以实现信号波形的灵活生成和控制。

通过设计合适的模块,可以产生多种类型的信号波形,并对其频率、幅值等参数进行调节。

基于FPGA的音视频信号处理系统设计研究

基于FPGA的音视频信号处理系统设计研究随着数字技术的迅速发展,人们对音视频信号处理的要求越来越高,FPGA作为一种高速可编程逻辑器件,在音视频信号处理领域中被广泛使用。

在本文中,我们将探讨基于FPGA的音视频信号处理系统设计研究。

一、FPGA的基本原理FPGA是一种可编程逻辑器件,其包括一系列可编程的逻辑单元以及可编程的互联网络。

FPGA的基本工作原理是通过对其内部的逻辑单元进行编程,实现任意的逻辑功能,在互联网络的支持下,可以实现不同逻辑单元之间的通信和数据传输。

二、音视频信号处理的基本原理音视频信号处理是将音视频信号进行采集、处理、压缩和传输的过程。

其中,信号采集是将模拟信号转化为数字信号的过程,处理是对数字信号进行滤波、降噪等处理的过程,压缩是对信号进行编码压缩的过程,传输是将信号通过网络传输的过程。

三、基于FPGA的音视频信号处理系统设计在音视频信号处理系统中,FPGA作为一个核心芯片,其具有高速、可编程等优势,被广泛应用于信号处理的各个环节。

基于FPGA的音视频信号处理系统设计通常包括以下几个步骤:1. 信号采集在信号采集阶段,需要将模拟信号转化为数字信号,一般采用ADC芯片进行采集。

ADC芯片将模拟信号进行采样和量化,并输出相应的数字信号。

在FPGA中,可通过外部接口或板载A/D转换器来实现信号采集。

2. 信号处理信号处理是对数字信号进行滤波、降噪等处理的过程。

在FPGA中,可通过编写相应的算法来实现信号处理功能,如滤波器、FFT变换等。

3. 数据压缩在数据传输前,需要对信号进行压缩,以减小数据传输的带宽。

基于FPGA的音视频信号处理系统常用的压缩算法有JPEG、MPEG等。

4. 数据传输在数据传输阶段,需要通过网络将信号传输到目标设备。

在FPGA中,可通过以太网接口、串口等方式实现数据传输。

另外,可通过板载SD卡等存储设备实现离线数据传输。

五、基于FPGA的音视频信号处理系统应用基于FPGA的音视频信号处理系统已广泛应用于图像处理、视频监控、音频处理、仪器仪表、医疗设备等领域。

基于FPGA的DVI视频信号发生器设计

基于FPGA的DVI视频信号发生器设计邸兴;张杰【摘要】In order to research portable non⁃standard time⁃sequence DVI video signal applied to industrial video display, STM32 is used to generate DVI video data,(which will be sent to SDRAM plugged in FPGA through the FSMC interface,and then read by the logic generated by the internal video signal in FPGA),the parallel RGB video is generated according to the DVI video signal time⁃sequence,which will be sent to DVI video encoding chipto generate standard TMDS serial DVI video flow. The hardware circuit of non⁃standard video signal generator based on FPGA was designed. DVI video signal was generated which can be used as industrial video source. With a smaller board size and power consumption,a new solution was provided to meet the industrial application of portable non⁃standard DVI video.%为了研究满足工业视频显示应用中需要的便携式非标准时序DVI视频信号。

基于FPGA的智能视频信号处理技术研究的开题报告

基于FPGA的智能视频信号处理技术研究的开题报告一、研究背景随着数字视频技术的快速发展,视频信号的处理技术已成为一个研究热点。

由于视频信号的高速、大容量、高精度和复杂性,传统的处理技术已经难以满足要求,智能视频处理技术成为了一个重要方向。

FPGA 芯片具有可编程性强、存储容量大、运算速度快等特点,尤其适用于视频图像信号的处理。

因此,通过FPGA实现智能视频信号处理已成为当前研究的一个热点。

二、研究内容本文主要研究基于FPGA的智能视频信号处理技术,具体内容为:1.智能视频处理算法的研究:包括视频图像处理算法、运动估计算法、目标检测算法等,以达到对视频图像处理的最优化。

2.FPGA系统的设计与实现:设计并制作基于FPGA的智能视频处理系统,其中包括FPGA芯片的硬件设计、平台搭建等。

3.测试与分析:通过对智能视频处理系统的测试,验证其对视频信号处理的有效性和可靠性。

同时分析不同算法对系统性能的影响,并给出改进方案。

三、研究意义通过本研究,可以深入探究基于FPGA的智能视频信号处理技术,为提升视频处理效率、实现智能化提供重要技术支持。

同时,实现基于FPGA的智能视频处理系统可以在各类视频监控、显像设备等领域得到广泛应用。

四、研究方法本研究采用实验法与理论研究相结合的方法。

首先,对视频处理算法进行研究,再根据算法设计相应的硬件电路,最后对开发出的FPGA智能视频处理系统进行测试与分析。

五、预期结果预计能够设计开发出性能良好、稳定可靠的基于FPGA的智能视频处理系统,提高视频处理的效率和精度,为实现智能化提供重要技术支持。

同时,针对不同的智能算法,预计能够给出相应的实验数据以及改进方案,为建立更完善的智能视频处理技术体系提供支持。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第29卷 第3期2008年3月仪器仪表学报Ch i nese Journa l o f Sc ientific Instru m entV ol 29N o 3M ar .2008收稿日期:2007 04 Recei ved Date :2007 04基于FPGA 的视频信号发生器设计与应用研究刘 杰1,牛燕雄1,2,董 伟1,司宾强1,刘佳栋1(1 解放军军械工程学院光学与电子工程系 石家庄 050003;2 清华大学精密仪器测试技术与仪器国家重点实验室 北京 100084)摘 要:本文介绍了一种基于FPGA 的新型视频信号发生器,它可以满足多种被测系统对输入视频信号制式的要求。

该系统利用U SB 总线与上位机进行通信,同时解决了系统供电的问题。

在FPGA 内部,通过软件编程的方法生成视频信号的图像和时序控制信号,并送入视频D /A 模块。

通过实验对该视频信号发生器在电视跟踪性能检测中的应用进行研究,获取并分析了被测电视跟踪系统的跟踪性能指标。

在使用中发现该系统具有可靠性高、通用性好、集成度高和体积小等特点,具有广泛的应用前景。

关键词:视频信号发生器;FPGA;U SB ;模拟目标;跟踪性能测试中图分类号:TP334.2 文献标识码:A 国家标准学科分类代码:510.8040D esign and application of video si gnal generator based on FPGAL i u Jie 1,N i u Yanx iong 1,2,Dong W e i 1,S iB i n q iang 1,L i u Jiadong1(1D ep t .O p tics and E lectron ic Eng i neering ,O rdnance Engineer i ng Colle g e ,Sh ijiazhuang 050003,China ;2T he State K ey Laboratory of Precision M easure m ent T echnology and Instru m ents,D epart m ent of P recision Ins t ru m ents ,T si nghua Universit y,B eij i ng 100084,China)Abst ract :A ne w type of v i d eo si g nal generator based on FPGA is presen ted .It generates severa lk i n ds o f v i d eo sig nals to m eet the input requ ire m ents o fm ost v i d eo syste m s under tes.t This generator co mm unicatesw it h a PC through USB por,t and this m ethod could also so lve the prob l e m o f po w er supp l y .In the FPGA,the generator cou l d generate i m age and sequence contro l si g na l through so ft w are progra m,and send the signals to v ideo D /A m odu le .Then experi m ents w ere carried out to verify the app lication o f t h e generator i n TV track i n g capability tes.t The track i n g capab ility para m eters w ere obtained and ana l y zed .This generator has the m erits o f h i g h reliability ,good universa li ty ,high i n tegration leve,l s m a ll size and so on ,and has broad applicati o n pr ospects .K ey w ords :v i d eo signal generato r ;FPGA;USB ;si m u lated targe;t track i n g capability test1 引 言目前,对视频信号采集、记录和处理系统(视频采集卡、图像记录仪和电视跟踪系统等)的研究测试已经十分广泛。

在对这些系统进行测试的过程中,需要测试者提供符合该系统输入制式要求的视频信号。

针对多种被测系统及被测指标,测试者应该提供不同种类和制式的视频信号。

以往对这些系统进行测试时,人们经常利用探测器对靶板进行成像,将产生的视频信号送入被测系统。

该测试方法给系统评估引入两方面的误差:一是靶板的制作误差,二是探测器本身的成像质量偏差。

针对这些误差,国内外逐渐使用能够提供模拟图像的视频信号发生器来取代传统的测试装置[1 3]。

现场可编程门阵列(FP GA )具有高集成度、高可靠性以及开发工具智能化等特点,目前逐步成为复杂数字电路设计的理想首选[4]。

考虑到视频信号时序要求严格以第3期刘 杰等:基于FPGA 的视频信号发生器设计与应用研究655及硬件小型化的要求,选用FP GA 来设计视频信号发生器,与其他设计方法相比,极大地缩短了开发周期,提高了测试精度。

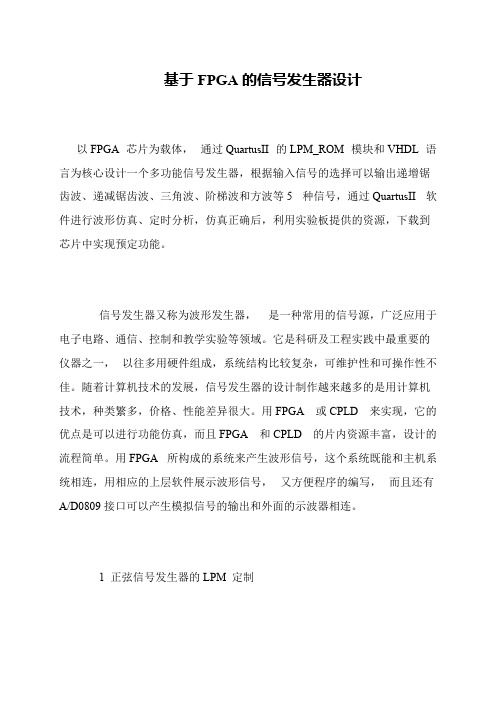

2 硬件实现系统由USB 通信模块、FP GA 控制模块、视频D /A 模块和输出接口模块组成。

硬件组成如图1所示。

图1 系统硬件组成F i g .1H ardware struc t ure of t he system2.1 工作原理上位机经过U SB 总线与FPGA 进行通信,将模拟目标或靶板的信息以及其他控制信号传送给FP GA 。

FPGA对接收到的数据进行判断和计算,最后输出具有时序关系的数字信号。

如果系统需要输出模拟视频信号,那么将数字信号送入视频D /A 转换电路,输出与被测系统制式相符的视频信号;如果被测系统接收数字信号,那么将数字信号进行调理后,直接送入被测系统。

2.2 与上位机通信方式的选择以前我们开发的视频信号发生器选择了串口通信的方式与上位机进行数据传输,该通信方式具有开发简单,成本低的特点。

但是在使用过程中发现了以下问题:一是不支持热插拔,接上视频信号发生器后,主机需要重新启动;二是需要为视频信号发生器单独提供电源;三是数据传输慢,不利于系统的扩展。

针对以上问题,决定采用USB 通信的方式。

U SB 接口具有热插拔、传输速度快以及便携等特点[5],能够完全满足本系统的设计要求。

当本系统接入PC 的USB 接口时,PC 将固件自动下载到U SB 接口芯片中,测试者只需要操作PC 机上的应用程序界面,就可以完成相关的测试工作。

此外,U SB 接口提供的+5V 电源,它的电流可以达到几百mA,完全可以驱动系统进行正常工作(软件仿真得到FP GA 模块在生成某种视频信号时的功耗为100mW 左右),省去了系统供电电源的设计工作,这样缩小了系统体积,提高了系统的便携性能。

2.3 FPGA 控制模块FP GA 控制模块是整个系统的核心。

以生成标准CCI R 制式视频信号为例来介绍该模块的设计方法。

根据CC I R 制式的电视信号标准,它采用隔行扫描的方式,每场312.5行,行频15625H z ,场频50H z ,水平有效像素点768,垂直有效像素点575。

由于采用了隔行扫描的方式,视频信号中就必须包含前后均衡脉冲。

再加上场同步中的开槽脉冲,这些脉冲信号的引入会提高输出视频图像的质量,因此模拟该类信号是该模块设计的关键。

由于CC I R 制式视频信号属于模拟信号,所以FPGA 输出的数据以及控制信号需要进入D /A 转换电路。

这里选用了AD 公司的3路10位视频D /A 芯片,该芯片的输入端是复合同步信号、复合消隐信号、时钟信号、3路(R 、G 、B)图像数据信号以及其他控制信号,最后输出3路模拟视频信号。

因此,FPGA 控制模块需要为视频D /A 转换模块提供以上所需的输入信号。

本文采用了模块化的设计方法,利用V eril og 硬件描述语言生成各种子模块,再将这些子模块进行顶层的连接,最后输出图像数据及控制信号。

模块的总体结构如图2所示。

图2 FPGA 控制模块的总体结构F i g .2G ene ra l structure o f the FPGA contro lm odule在设计各子模块的过程中,充分利用了FP GA 设计软件时序仿真的功能,这给调试以及选取最优模块带来极大的方便。

图3是利用M odel Sm i SE 6.0软件仿真出的开槽脉冲、均衡脉冲、行同步、行消隐和场消隐子模块时序图。

图3 几种子模块的时序仿真F i g .3Sequence si m u lati on p ict u res for severa l sub m odu l es图中,kc mc 是开槽脉冲模块,其中高电平时间是4.7 s ,低电平时间为27.3 s ;j h mc 代表前后均衡脉冲模块,高电平29.65 s ,低电平2.35 s ;hsyn 代表了行同步脉冲模块,周期64 s ,同步脉冲宽度4.7 s ,前肩1.5 s ,后肩5.8 s ;hblnk 是行消隐信号模块,消隐脉冲宽度12 s 。

656 仪 器 仪 表 学 报第29卷在本系统中,利用FPGA 的下载配置软件生成系统的配置文件(M CS 格式),然后经J TAG 口将配置文件下载到FPGA 控制模块的PROM 中。

当系统每次加电后,PRO M 将其存储的文件配置到FPGA 中,FPGA 开始正常工作,实现相应的功能。

针对这个特点,可以根据测试需要随时更新配置文件,完成不同种类被测系统的测试工作,使测试工作更具有灵活性。

2.4 视频D /A 转换模块将系统输出的标准和非标准模拟视频信号进行比较,发现它们有类似的地方,即都包含同步信号,而且对同步信号电平有特定的要求。

标准视频信号中要求同步电平比消隐电平低0.3V ,某型装备输出的非标准视频信号要求同步电平严格控制在-0.3V 。

同步电平的这些特性就要求设计者必须合理选择视频D /A 转换芯片。

在本系统中选取了AD 公司的三路10位视频D /A 芯片。

只要对该芯片的输入端(复合同步、消隐信号、时钟信号,数据信号等)进行编程,系统就可以输出不同制式的模拟视频信号。