VHDL总结

第四讲VHDL语言基础知识

关键词 VHDL 实体 逻辑功能

此两处必须同名

逻辑行为描述

1、实体

格式

ENTITY 实体名 IS [GENERIC ( 类属表 );] [PORT ( 端口表 );] END 实体名;

说明

实体说明所设计的逻辑电路的输入、输 出信号及其特性(输入(in)输出(out)、双向 (inout)、buffer)

•文件(FILES)是传输大量数据的客体,包含一些专门数据 类型的数值。

对象说明的一般格式是: <对象类型> < 标识符表>:<子类型说明> <信号种类>: =<表达式>; 说明 标识符 <子类型说明>是类型名或类型名加限制条件 <信号种类>为BUS或REGISTER,该项为任选项 :=<表达式>为对象赋初值

IS

一个包集合由包集合标题和包集合体两 大部分组成。 包集合体是一个可选项。

5、库

格式

LIBRARY 库名; USE 库名. 程序包名. All;

USE语句的使用有两种常用格式: USE 库名.程序包名.项目名 ; USE 库名.程序包名.ALL ;

VHDL库的种类

• IEEE库:IEEE标准库, 是按IEEE组织制定的 工业标准进行编写的, 是内容丰富的资源库 使用需声明 • •STD_LOGIC_1164 程序包 •STD_LOGIC_ARITH 程序包 •STD_LOGIC_UNSIGNED 程序包

STD库:VHDL标准库,STANDARD和 TEXTIO程序包即收入在STD库中 使用无需声明

VHDL库的种类

• • •

ASIC库:EDA厂商提供库 使用需声明 WORK库:现行作业库,当前工作目录的所有设计 使用无需声明 USER库:用户自定义库 使用需声明

vhdl实验报告

vhdl实验报告VHDL实验报告引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计和仿真。

本篇实验报告将介绍我在VHDL实验中的学习和实践经验,包括实验目的、实验过程、实验结果以及对VHDL的理解和展望。

一、实验目的VHDL实验的主要目的是让我们掌握VHDL语言的基本语法和使用方法,能够利用VHDL描述数字电路,并通过仿真和综合工具进行验证和实现。

通过这些实验,我们可以深入了解数字电路的原理和设计方法,提高我们的逻辑设计能力和工程实践能力。

二、实验过程在实验过程中,我们首先学习了VHDL的基本语法,包括实体声明、端口声明、信号声明等。

然后,我们通过实例学习了VHDL的建模方法,包括组合逻辑电路的建模和时序逻辑电路的建模。

在组合逻辑电路的建模中,我们学习了使用逻辑运算符和条件语句描述电路的功能;在时序逻辑电路的建模中,我们学习了使用过程语句和时钟信号描述电路的状态转换。

在学习了VHDL的基础知识后,我们开始进行实验设计。

我们选择了一个简单的数字电路,如4位加法器,来进行实验验证。

首先,我们通过VHDL语言描述了加法器的功能和结构,包括输入端口、输出端口和中间信号。

然后,我们使用仿真工具进行了功能仿真,验证了加法器的正确性。

接着,我们使用综合工具将VHDL代码综合成门级电路,并进行了时序仿真和时序优化,验证了加法器的时序正确性和性能。

三、实验结果通过实验,我们成功地实现了4位加法器的功能,并验证了其正确性和性能。

在功能仿真中,我们输入了不同的测试数据,观察了输出结果,发现加法器能够正确地进行加法运算,并得到了正确的结果。

在时序仿真中,我们观察了电路的时序行为,包括输入信号的变化、输出信号的响应和中间信号的传播延迟等,发现加法器能够在时序上满足要求,并且具有较好的性能。

vhdl实验报告--蜂鸣器

vhdl实验报告--蜂鸣器VHDL 实验报告蜂鸣器一、实验目的本次实验的主要目的是通过使用 VHDL 语言来设计并实现一个蜂鸣器的控制电路,深入理解数字电路的设计原理和 VHDL 编程的基本方法,掌握硬件描述语言在实际电路设计中的应用,提高自己的逻辑思维和问题解决能力。

二、实验原理蜂鸣器是一种一体化结构的电子讯响器,采用直流电压供电。

常见的蜂鸣器分为有源蜂鸣器和无源蜂鸣器两种。

有源蜂鸣器内部自带了振荡源,只要给其供电就能发出固定频率的声音;无源蜂鸣器则需要外部提供一定频率的脉冲信号才能发声。

在本实验中,我们使用 VHDL 语言来控制一个无源蜂鸣器。

通过编写代码,生成特定频率的脉冲信号,从而驱动蜂鸣器发声。

三、实验设备及工具1、计算机2、 Quartus II 软件3、开发板四、实验内容及步骤1、设计思路首先,需要确定蜂鸣器发声的频率。

通过计算得出所需的时钟周期数。

然后,使用计数器来产生特定频率的脉冲信号。

最后,将脉冲信号输出到蜂鸣器的控制引脚。

2、 VHDL 代码编写```vhdllibrary ieee;use ieeestd_logic_1164all;use ieeenumeric_stdall;entity buzzer_control isport(clk : in std_logic;rst : in std_logic;buzzer : out std_logic);end entity;architecture Behavioral of buzzer_control isconstant CLK_FREQ : integer := 50_000_000; 系统时钟频率constant BUZZER_FREQ : integer := 1000; 蜂鸣器发声频率signal counter : integer range 0 to CLK_FREQ/BUZZER_FREQ 1; signal clk_div : std_logic;beginprocess(clk, rst)beginif rst ='1' thencounter <= 0;clk_div <='0';elsif rising_edge(clk) thenif counter = CLK_FREQ/BUZZER_FREQ 1 thencounter <= 0;clk_div <= not clk_div;elsecounter <= counter + 1;end if;end if;end process;buzzer <= clk_div;end architecture;```3、编译与仿真将编写好的 VHDL 代码在 Quartus II 软件中进行编译。

VHDL知识点

VHDL程序的基本结构一个完整的VHDL语言程序通常包含库(Library):如ieee, std, work等程序包(Package)实体(Entity):I/O 端口结构体或构造体(Architecture):具体描述电路所要实现的功能配置(Configuration)实体:用于描述所设计系统的外部接口特性;即该设计实体对外的输入、输出端口数量和端口特性。

结构体:用于描述实体所代表的系统内部的结构和行为;它描述设计实体的结构、行为、元件及内部连接关系。

库:存放已经编译的实体、结构体、程序包集合和配置。

程序包:存放各设计模块都能共享的数据类型、常数和子程序库;配置:实体对应多个结构体时,从与某个实体对应的多个结构体中选定一个作为具体实现。

保存的文件名与实体名字应该一致PORT(端口)说明PORT ( 端口名: 端口模式数据类型;端口名: 端口模式数据类型;…………) ;端口模式out (输出):只能被赋值,用于不能反馈的输出;in (输入):只能读,用于时钟输入、控制输入单向数据输入;inout(输入输出) :既可读又可被赋值,被读的值是端口输入值而不是被赋值,作为双向端口。

buffer(缓冲):类似于输出,但可以读,读的值是被赋值,用做内部反馈用,不能作为双向端口使用结构体的一般表达如下:ARCHITECTURE 结构体名称OF 实体名称IS[说明语句]可以不要BEGIN(功能描述语句)END ARCHITECTURE 结构体名称;功能描述语句:处于begin 与end 之间,描述结构体的行为与连接关系,它是构成结构体的主体。

描述实体的逻辑行为、以各种不同的描述风格表达的功能描述语句,或针对层次设计中,以元件例化语句为特征的外部元件(设计实体)端口间的连接。

库:是一些常用代码的集合。

库说明总是放在设计单元的最前面将常用代码存放到库中有利于设计的复用和代码共享,也可使代码结构更清晰;(1)IEEE 库IEEE 库定义了四个常用的程序包:std_logic_1164 (std_logic (8值)& std_ulogic (9值)逻辑值的逻辑运算) std_logic_arith (signed 、unsigned 数据类型的(算术、比较运算函数)std_logic_signed (std_logic_vector 类型数据的进行有符号算术、比较运算操作函数) std_logic_unsigned (std_logic_vector 类型数据进行无符号算术、比较运算操作函数)(2)STD 库(默认库)VHDL 的标准资源库,包括数据类型和输入/输出文本等内容。

VHDL实验报告(1)

VHDL 实验报告******班级:电子0701学号:************实验一组合逻辑电路设计一实验目的:1. 熟悉mux+pluxII软件,可以进行新文件的编辑和文件的修改。

2. 掌握门电路VHDL语言程序设计方法。

3. 掌握选择器VHDL语言程序设计方法。

4. 掌握加法器VHDL语言程序设计方法。

5. 熟悉VHDL编程的基本方法。

二实验设备:1.计算机2.Max+PlusII软件三实验原理及内容:1 二输入与门(1)实验原理二输入与门是我们数字电路中的一个基础逻辑门电路,是最基本的逻辑门电路之一,也是最简单的逻辑门之一。

它能实现两个输入端的相与,一般有三个端口。

二输入与门的表达式是:Y=ab二输入与门的逻辑符号如图(1)所示,真值表如表(1)所示。

图(1)与门逻辑符号表(1)与门真值表(2)实验内容a.在mux+pluxII文本编辑环境下,打开新文本,编写两输入与门VHDL语言源程序,程序设计如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY and2 ISPORT(a,b: IN STD_LOGIC;Y: OUT STD_LOGIC);END and2;ARCHITECTURE behave OF and2 ISBEGINY <= a and b;END behave;b.对源程序进行编译,按照提示进行修改,直至编译通过。

c.对编译程序进行仿真,分析并记录仿真波形,其仿真波形图如图(2)所示。

图(2)二输入与门仿真图d.在自己的目录下保存相应的源文件、波形文件。

2 四选一选择器(1)实验原理四选一选择器如图(3)所示,真值表如表(2)所示。

图(3)mux4管脚图表(2)mux4真值表(2)实验内容a.在mux+plusII文本编辑环境下,打开新文件,编辑四选一VHDL源程序文件,其程序设计如下:LIBRARY IEEEUSE IEEE.STD_LOGIC_1164.ALL;ENTITY mux4 ISPORT(A: IN STD_LOGIC_VECTOR (1 DOWNTO 0);D0,D1,D2,D3:IN STD_LOGIC;G:IN STD_LOGIC;Y: OUT STD_LOGIC);END mux4;ARCHITECTURE dataflow OF mux4 ISBEGINPROCESS (A,D0,D1,D2,D3,G)BEGINIF (G ='0') THENIF (A="00")THEN Y <= D0;ELSIF(A="01")THEN Y <= D1;ELSIF(A="10")THEN Y <= D2;ELSE Y <= D3;END IF;ELSE Y <='0';END IF;END PROCESS;END dataflow;b.对源程序进行编译,按照提示进行修改,直到编译通过。

vhdl语言

VHDL语言简介VHDL(VHSIC Hardware Description Language)即可高速集成电路硬件描述语言,是一种用于描述数字系统和电路的硬件描述语言。

它在1981年由美国国防部的高速集成电路联合委员会(VHSIC)开发,用于设计大规模集成电路。

VHDL是一种面向对象的语言,可以用于描述各种数字系统,从简单的逻辑门到复杂的处理器。

它提供了丰富的语法和语义,使得设计人员可以准确地描述他们的电路和系统。

VHDL的优势VHDL作为一种硬件描述语言,在数字系统设计中具有许多优势。

1.可重用性:VHDL允许设计人员创建可重用的模块和子系统,这些模块和子系统可以在不同的项目中重复使用,提高了设计效率和可维护性。

2.仿真和验证:VHDL具有强大的仿真和验证能力,可以在设计之前对系统进行全面的仿真和验证。

这有助于检测和纠正潜在的问题,并确保系统在硬件实现之前达到预期的功能。

3.抽象级别:VHDL允许设计人员在不同的抽象级别上描述系统,从高级的行为级别到底层的结构级别。

这使得设计人员可以根据需要在不同的级别上工作,并且可以更容易地进行系统级别的优化。

4.灵活性和可扩展性:VHDL支持灵活的设计方法和工作流程,并允许设计人员在设计过程中进行迭代和修改。

它还可以与其他常用的设计工具和方法集成,以满足特定的需求。

VHDL语言的基本结构VHDL语言由模块、实体、架构以及信号和过程等基本元素组成。

模块(Module)模块是VHDL中描述数字系统的最基本单位。

一个模块可以包含多个实体和架构,并通过连接信号进行通信。

每个模块都有一个顶层实体和一个或多个架构。

实体(Entity)实体是描述模块的接口和行为的抽象。

它定义了输入输出端口,以及模块对外部环境的接口。

一个实体可以有一个或多个架构。

架构(Architecture)架构描述模块的具体行为和内部结构。

它定义了模块的内部信号和过程,以及对外部信号和过程的接口。

VHDL语法简单情况总结

VHDL语法简单总结一个VHDL程序代码包含实体(entity)、结构体(architecture)、配置(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型上加一些约束条件,可以定义该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型语法结构SIGNAL signal_name: type_name [:= initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数类型定义SIGNAL delay_regs: delay_lines; –信号延迟寄存器声明CONSTANT coef: coeffs := ( ); –常量系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

VHDL语法简单总结

VHDL语法(yǔfǎ)简单总结VHDL语法简单(jiǎndān)总结VHDL语法(yǔfǎ)简单总结一个(yī ɡè)VHDL程序代码包含实体(shítǐ)(entity)、结构(jiégòu)体(architecture)、配置(pèizhì)(configuration)、程序包(package)、库(library)等。

一、数据类型1.用户自定义数据类型使用关键字TYPE,例如:TYPE my_integer IS RANGE -32 TO 32;–用户自定义的整数类型的子集TYPE student_grade IS RANGE 0 TO 100;–用户自定义的自然数类型的子集TYPE state IS (idle, forward, backward, stop);–枚举数据类型,常用于有限状态机的状态定义一般来说,枚举类型的数据自动按顺序依次编码。

2.子类型在原有已定义数据类型(lèixíng)上加一些约束条件,可以定义(dìngyì)该数据类型的子类型。

VHDL不允许不同类型的数据直接进行操作运算,而某个数据类型的子类型则可以和原有类型数据直接进行操作运算。

子类型定义使用(shǐyòng)SUBTYPE关键字。

3.数组(ARRAY)ARRAY是将相同数据类型的数据集合在一起(yīqǐ)形成的一种新的数据类型。

TYPE type_name IS ARRAY (specification) OF data_type;–定义新的数组类型(lèixíng)语法结构SIGNAL signal_name: type_name [:=initial_value];–使用新的数组类型对SIGNAL,CONSTANT, VARIABLE进行声明例如:TYPE delay_lines IS ARRAY (L-2 DOWNTO 0) OF SIGNED (W_IN-1 DOWNTO 0);–滤波器输入延迟链类型定义TYPE coeffs IS ARRAY (L-1 DOWNTO 0) OF SIGNED (W_COEF-1 DOWNTO 0);–滤波器系数(xìshù)类型定义SIGNAL delay_regs: delay_lines; –信号延迟(yánchí)寄存器声明CONSTANT coef: coeffs := ( ); –常量(chángliàng)系数声明并赋初值4.端口数组在定义电路的输入/输出端口时,有时需把端口定义为矢量阵列,而在ENTITY中不允许使用TYPE进行类型定义,所以(suǒyǐ)必须在包集(PACKAGE)中根据端口的具体信号特征建立用户自定义的数据类型,该数据类型可以供包括ENTITY在内的整个设计使用。

(VHDL实验报告)一位半加器,全加器的设计教学总结

五、实验步骤

(一)半加器的设计

4、对设计文件进行仿真

1)选择File--New,在弹出的对话框中选择Vector Waveform File,点击OK按钮,打开进入一个空的波形编辑器窗口。

2)设置仿真结束时间,波形编辑器默认的仿真结束时间为 1µS, 根据仿真需要,可以自由设置仿真的结束时间(本次设置的为1ms)。 选择 QUARTUSII 软件的 Edit--End Time命令,弹出线路束时间对 话框,在 Time框办输入仿真结束时间,点击OK按钮完成设置。如下 图所示:

实验箱上拨动开关档位在下方时表示其输出为低电平,反之

输出市电平;当FPGA与其对应的端口为高电平时LED就会发光,反

之LED灯灭。其拨动开关与FPGA管脚的连接表以及LED灯与FPGA管

脚连接表如下两图所示:

五、实验步骤

(一)半加器的设计

1、建立工程文件

1)运行QUARTUSII 软件。

2)选择软件中的菜单 File>New Project Wizard,新建一个工 程。

3)加入输入、输出端口,在波形编辑器窗口左边的端口名列表 区点击鼠标右键,在弹出的右键菜单中选择 Insert Node or Bus… 命令,在弹出的 Insert Node or Bus 对话框界面中点击 Node Finder…按钮。在出现的 Node Finder 界面中的 Filter 列表中选 择 点击 List,在 Nodes Found 窗口出现所有信号的名称,点击中 间的按钮则 Selected Nodes 窗口下方出现被选择的端口名称。双击 OK按钮,完成设置,回到 Insert Node or Bus 对话框,双击OK按 钮,所有的输入、输出端口将会在端口名列表区内显示出来。

vhdl课程设计设计模为 4、8、12、16的可变计数器实验报告总结

VHDL课程设计 - 可变计数器实验报告总结

一、设计概述

本课程设计的主要目标是设计并实现一个可变计数器,其模(Modulo)值可以在4、8、12、16之间进行选择。

计数器采用VHDL编程语言进行描述,并在FPGA开发板上进行测试验证。

二、设计实现

1. 硬件平台:我们选择了Xilinx的FPGA开发板作为硬件平台,它具有丰富的I/O资源和足够的逻辑单元,可以满足我们的设计需求。

2. VHDL编程:我们采用VHDL语言进行编程,实现了模4、模8、模12和模16的可变计数器。

通过选择不同的计数模式,计数器的模值可以在4、8、12、16之间进行切换。

3. 测试与验证:为了验证计数器的功能,我们编写了测试平台,并通过仿真和实际硬件测试对计数器进行了全面的测试。

三、实验结果与分析

1. 实验结果:通过仿真和实际硬件测试,我们验证了计数器的

功能正确性。

在不同的模值下,计数器都能正确地进行计数操作,并且在达到模值后能正确地回绕到0。

2. 结果分析:实验结果表明,我们的VHDL编程和FPGA开发技能得到了很好的应用和提升。

同时,通过这次课程设计,我们更深入地理解了可变计数器的设计和实现原理,提高了我们的硬件设计能力。

四、总结与展望

本次课程设计让我们深入了解了VHDL编程语言和FPGA开发技术,提高了我们的硬件设计能力。

通过实际的设计和测试,我们成功地实现了一个可变模值的计数器,达到了课程设计的要求。

在未来的学习和工作中,我们将继续深入学习FPGA设计和VHDL编程,不断提高自己的硬件设计能力。

同时,我们也期待将这种技术应用于更多的实际项目中,为工程实践做出贡献。

vhdl课程设计小结

vhdl课程设计小结一、教学目标通过本章的学习,学生应掌握VHDL(Very High Speed Integrated Circuit Hardware Description Language)的基本语法、基本结构和基本用法,能够运用VHDL对简单的数字电路进行描述和仿真。

具体来说,知识目标包括:1.掌握VHDL的基本语法和规则。

2.理解VHDL的基本结构和组成。

3.熟悉VHDL的基本用法和操作。

技能目标包括:1.能够编写简单的VHDL代码,对基本的逻辑门电路进行描述。

2.能够使用至少一种VHDL仿真工具,对编写出的代码进行仿真和测试。

情感态度价值观目标包括:1.培养学生对硬件描述语言的兴趣和好奇心。

2.培养学生独立思考、解决问题的能力。

二、教学内容本章的教学内容主要包括VHDL的基本语法、基本结构和基本用法。

具体安排如下:1.介绍VHDL的基本语法,包括数据类型、信号声明、实体声明、架构声明等。

2.讲解VHDL的基本结构,包括实体、端口、信号、进程等。

3.介绍VHDL的基本用法,包括逻辑门电路的描述、组合逻辑电路的描述、时序逻辑电路的描述等。

4.结合实际案例,讲解如何使用VHDL对数字电路进行描述和仿真。

三、教学方法为了提高学生的学习兴趣和主动性,本章将采用多种教学方法,包括讲授法、讨论法、案例分析法、实验法等。

1.讲授法:用于讲解VHDL的基本语法和基本结构。

2.讨论法:用于探讨VHDL的用法和实际应用问题。

3.案例分析法:通过分析实际案例,让学生掌握VHDL对数字电路的描述和仿真。

4.实验法:让学生动手编写VHDL代码,使用仿真工具进行仿真,巩固所学知识。

四、教学资源为了支持教学内容和教学方法的实施,丰富学生的学习体验,我们将选择和准备以下教学资源:1.教材:《VHDL Primer》(第五版),作者:Peter Flake。

2.参考书:《数字电路设计与VHDL应用》。

3.多媒体资料:VHDL教程视频、实际案例视频等。

vhdl心得体会

vhdl心得体会VHDL是一种硬件描述语言,用于描述数字逻辑电路。

我在学习VHDL过程中,有一些心得体会。

首先,学习VHDL需要有坚实的数字逻辑基础。

VHDL是用于描述数字电路的语言,因此理解数字逻辑的原理和基本概念是非常重要的。

比如理解逻辑门、触发器、多路选择器等基本的数字逻辑元件的工作原理,才能够更好地用VHDL描述这些元件。

其次,学习VHDL需要注重练习和实践。

只是理论的学习是远远不够的,需要通过实践来巩固和应用所学的知识。

可以通过编写小的数字逻辑电路的VHDL代码来实践,比如实现一个简单的加法器、乘法器或者计数器。

通过不断地实践,可以更加熟悉VHDL的语法和规范,并且加深对数字逻辑的理解。

另外,在学习VHDL过程中,需要注重代码的规范和可读性。

VHDL是一种结构化的语言,代码的结构和组织对于后期的维护和调试非常重要。

可以通过使用合适的命名规范、缩进和注释来增加代码的可读性,避免出现混乱和不易理解的情况。

此外,掌握好VHDL的多种建模方法也是很重要的。

VHDL可以使用结构化建模、数据流建模或者行为建模等不同的方法来描述电路。

对不同的电路和设计要求,选择合适的建模方法是关键。

因此,需要深入理解这些建模方法的特点和使用场景,以便更好地应用在实际的设计中。

最后,理解VHDL中的一些高级特性和工具也是很有意义的。

VHDL提供了很多高级特性,比如泛型、过程、状态机等,可以帮助我们更好地描述和优化数字逻辑电路。

同时,VHDL还有一些支持工具,比如仿真工具、综合工具和布局工具等,可以帮助我们验证和优化设计。

掌握这些高级特性和工具,可以提高设计的效率和准确性。

综上所述,学习VHDL需要有坚实的数字逻辑基础,注重实践和练习,注重代码规范和可读性,掌握多种建模方法,了解VHDL中的高级特性和工具。

通过不断地学习和实践,我们可以更好地理解和应用VHDL,更好地完成数字逻辑电路的设计。

VHDL语言的基本知识点罗列

VHDL语言的基本知识点罗列1 VHDL语言的标识符VHDL中的标识符可以是常数、变量、信号、端口、子程序或参数的名字。

使用标识符要遵守如下法则:a)标识符由字母(A…Z;a…z)、数字和下划线字符组成。

任何标识符必须以英文字母开头。

λ末字符不能为下划线。

λb)不允许出现两个连续下划线。

标识符中不区分大小写字母。

λVHDL定义的保留子或称关键字,不能用作标识符。

λc) VHDL中的注释由两个连续的短线(--)开始,直到行尾。

以下是非法标识符:-Decoder —起始不能为非英文字母3DOP —起始不能为数字Large#number —“#”不能成为标识符的构成符号Data__bus —不能有双下划线Copper_ —最后字符不能为下划线On —关键字不能用作标识符。

注:在AHDL语言中标识符要区分大小写,但在VHDL语言中不区分大小写。

所以写程序时,一定要养成良好的书写习惯,应用关键字时用大写,自己定义的标识符用小写。

标识符表示的几种数据对象的详细说明如下:1) 常数(Constant )常数是一个固定的值,主要是为了使设计实体中的常数更容易阅读和修改。

常数一被赋值就不能在改变。

一般格式:CONSTANT 常数名:数据类型:=表达式;例:CONSTANT Vcc: REAL: =5.0;—设计实体的电源电压指定常数所赋得值应与定义的数据类型一致。

常量的使用范围取决于它被定义的位置。

程序包中定义的常量具有最大的全局化特性,可以用在调用此程序包的所有设计实体中;设计实体中某一结构体中定义的常量只能用于此结构体;结构体中某一单元定义的常量,如一个进程中,这个常量只能用在这一进程中。

2) 变量(Variable)变量是一个局部变量,它只能在进程语句、函数语句和进程语句结构中使用。

用作局部数据存储。

在仿真过程中。

它不像信号那样,到了规定的仿真时间才进行赋值,变量的赋值是立即生效的。

变量常用在实现某种算法的赋值语句中。

VHDL的模块化教学方法反思与总结

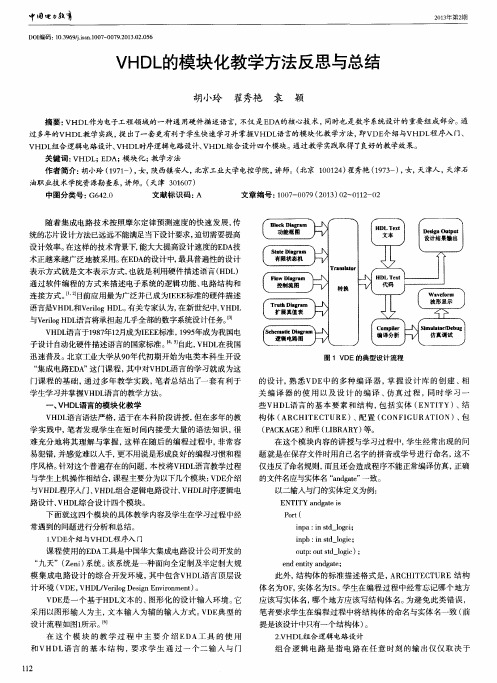

语言是v HD L 和V e r i l o g H D L 。 有关专家认 为, 在新世纪中, V HD L 与V e r i l o g HD L 语言将承担起几乎全 部的数字系统设计任务o 1 ] _ VH D L 语言于1 9 8 7 年1 2 月成为I E E E 标准, 1 9 9 5 年成为我国电

S i mu l a t o r / De b u g

编译分析 卜 _ ] / 1 仿真调试

迅速普及 。 北京工业大学从9 0 年代初期开始为电类本科 生开设

“ 集成 电路E D A ” 这 门课 程, 其 中对V HD L 语言 的学习就成为这 门课 程 的基 础 , 通 过多 年教学 实践 , 笔 者总结 出了一套有 利于 学生学习并掌握V H D L 语言 的教学方 法。

易犯错 , 并感觉难以人手, 更不用说是形成良好 的编程习惯和程

序风 格。 针对这个普 遍存 在的问题 , 本 校将V HD L 语言教学过程 与学生上机操 作相结合, 课程 主要 分为以下几个模 块 : V D E 介绍 与V H D L 程序入门、 V HD L 组合 逻辑电路 设计、 V HD L 时序逻辑 电 路设 计、 V HD L 综合设 计四个模块 。

过 多年 的V HDL 教学实践 , 提 出了一套更有利于学生快速学习并掌握VHDL i  ̄ 言的模 块化 教学方法, I  ̄ F VDE 介 绍与VHDL 程序入 门、 VHDL 组合逻辑电路设计、 VHDL 时序逻辑电路设计、 VHDL 综合设计四个模块 。 通过教学实践取得 了良好的教学效果。

—

i n p b: i n s t dl o g i c ;

—

课程 使用的E D A 工具是 中国华大 集成电路 设计公司开发 的

EDA 技术:VHDL语句总结

begin

if sel = "0001" then output <= in1(0) ; output2<=‘1’;

elsif (sel = "0010") then

output <= in1(0) xor in1(1) ; output2 <= ‘0’ ;

elsif sel = "0100" then

sel: in std_logic_vector(3 downto 0); output: out std_logic; output2: out std_logic); end ifexample1;

architecture arch of ifexample1 is

begin

process(in1, sel)

begin case (din) is when “00” => dout <=“0001” ; when “01” => dout <= “0010” ; when “10” => dout <=“0100” ; when “11” => dout <=“1000” ; end case;

end rtl ;

使用变量能获得比较好的综合结果,有利于优化, 但 需要锁存中间结果时必须使用信号。

❖ 初值(有三种形式,前两种综合忽略)

1、type states is (IDLE,S0,S1,S2); signal state:states; --信号state默认值为IDLE

2、signal Z : bit_vector(3 downto 0) :=“0000” ;

end if; end process; end rtl;

(完整word版)vhdl基本语法

VHDL 基础语法篇——VHDLVHDL硬件描述语言1。

1 VHDL概述1。

1。

1 VHDL的特点VHDL语言作为一种标准的硬件描述语言,具有结构严谨、描述能力强的特点,由于VHDL语言来源于C、Fortran等计算机高级语言,在VHDL语言中保留了部分高级语言的原语句,如if语句、子程序和函数等,便于阅读和应用。

具体特点如下:1。

支持从系统级到门级电路的描述,既支持自底向上(bottom-up)的设计也支持从顶向下(top—down)的设计,同时也支持结构、行为和数据流三种形式的混合描述。

2. VHDL的设计单元的基本组成部分是实体(entity)和结构体(architecture),实体包含设计系统单元的输入和输出端口信息,结构体描述设计单元的组成和行为,便于各模块之间数据传送.利用单元(componet)、块(block)、过程(procure)和函数(function)等语句,用结构化层次化的描述方法,使复杂电路的设计更加简便。

采用包的概念,便于标准设计文档资料的保存和广泛使用。

3. VHDL语言有常数、信号和变量三种数据对象,每一个数据对象都要指定数据类型,VHDL的数据类型丰富,有数值数据类型和逻辑数据类型,有位型和位向量型。

既支持预定义的数据类型,又支持自定义的数据类型,其定义的数据类型具有明确的物理意义,VHDL是强类型语言。

4. 数字系统有组合电路和时序电路,时序电路又分为同步和异步,电路的动作行为有并行和串行动作,VHDL语言常用语句分为并行语句和顺序语句,完全能够描述复杂的电路结构和行为状态。

1.1.2 VHDL语言的基本结构VHDL语言是数字电路的硬件描述语言,在语句结构上吸取了Fortran和C等计算机高级语言的语句,如IF语句、循环语句、函数和子程序等,只要具备高级语言的编程技能和数字逻辑电路的设计基础,就可以在较短的时间内学会VHDL语言。

但是VHDL毕竟是一种描述数字电路的工业标准语言,该种语言的标识符号、数据类型、数据对象以及描述各种电路的语句形式和程序结构等方面具有特殊的规定,如果一开始就介绍它的语法规定,会使初学者感到枯燥无味,不得要领.较好的办法是选取几个具有代表性的VHDL程序实例,先介绍整体的程序结构,再逐步介绍程序中的语法概念。

VHDL总结

第1部分EDA技术概述一、EDA技术的含义:EDA是Electronic Design Automation (电子设计自动化)的缩写。

以大规模可编程逻辑器件为设计载体,以硬件描述语言为系统逻辑描述的主要表达方式,以计算机、大规模可编程器件的开发软件及实验开发系统为设计工具,自动完成用软件方式描述的电子系统到硬件的逻辑编译、逻辑简化、逻辑分割、逻辑综合及优化、布局布线、逻辑仿真、直至完成对于特定目标芯片的适配编译、逻辑映射、编程下载等工作,最终形成集成电子系统或专用集成芯片的一门多学科融合的新技术。

二、EDA技术的实现目标及实现途径:1、实现目标完成专用集成电路ASIC或印制电路板PCB的设计和实现。

2、实现途径⑴. 超大规模可编程逻辑器件⑵. 半定制或全定制ASIC ⑶. 混合ASIC三、EDA技术的设计方法:(P8)传统的电路设计方法:自底向上的设计方法。

即首先确定可用的元器件,然后根据这些器件进行逻辑设计,完成各模块后进行连接,最后形成系统。

基于EDA技术的电路设计方法:自顶向下的设计方法。

自顶向下是指将数字系统的整体逐步分解为各个子系统和模块,若子系统的规模较大,则还需将子系统进一步分解为小的子系统和模块,层层分解,直至整个系统中各个子系统的关系合理,并便于工作于逻辑电路的设计和实现为止。

传统电路设计方法与采用EDA技术的电路设计方法的区别:1、设计方法不同:传统是自下而上的方法(Down-Top),EDA是自上而下的设计方法(Top-Down)。

2、传统设计基于电路板;EDA技术是基于芯片的设计方法。

3、描述方式不同:传统采用电路图为主,EDA以硬件描述语言为主。

4、设计手段不同:传统以手工设计为主,EDA设计为自动设计。

结论:EDA技术极大地降低硬件电路的设计难度,提高设计效率,是电子系统设计方法的质的飞跃!四、EDA技术的设计流程(P12)1、设计输入(原理图/HDL文本编辑)2、综合(自然语言综合/逻辑综合/行为综合/ 版图综合或结构综合)3、适配4、时序仿真和功能仿真(P14)5、编程下载6、硬件测试第2部分VHDL程序结构VHDL程序由实体(Entity)、结构体(Architecture)、库(Library)、程序包(Package)和配置(Configuration)5个部分组成。

VHDL语言学习总结

VHDL语言学习总结jackhuan@(初学VHDL,欢迎批评指正)1 VHDL的程序结构一个VHDL程序包含实体entity、结构体architecture、配置configuration、包集package 和库library五部分。

实体,用于描述设计系统的外部接口信号;结构体,用于描述系统的行为,系统数据的流程或系统组织结构形式;实体+结构体=设计实体;实体是设计实体的表层设计单元,其功能是对这个设计实体与外部的电路接口进行描述,它规定了设计单元的输入、输出接口信号和引脚,是设计实体与外界的一个通信界面;结构体是用于描述设计实体的内部结构以及实体端口间的逻辑关系,结构体具体实现一个实体。

一个电路系统的程序设计只有一个实体,可以有多个结构体。

在实体中类属说明放在端口说明上端,而其他说明类型说明如数据的定义说明则放在端口定义的下面。

配置一般用来为实体指定结构体,由于在设计中没有用到配置,故没有做深入研究。

包集是库的一部分,用来存放库中具有类似功能或在某一个部件中使用的元件、函数或过程。

库是一个设计中封装所有元器件的总和。

2 VHDL与C++的结构类比上述部分可以和C++的工程管理方式做一简单比较。

C++中有类的声明部分(一般为.H文件)和实现部分(一般为.CPP文件)。

在程序的编写过程中,我们首先在一个.H文件中将类的成员变量和成员函数做定义,然后在.CPP中使用具体的代码实现它。

这样在应用这个类的其他程序代码中,一般在引用文件的开始加入如下语句:#include “***.h” //***代表我们要包含的文件名称就可以随意使用其内部的类和函数了。

VHDL有类似之处。

首先我们编写了*.VHD文件,内有实体entity和结构体architecture,开始还要引入库library和包package。

在我们使用其他元件时,通常在architecture中做元件例化。

例如要在myexp中例化元件myand,则:Architecture behave of myexp isSignal mysig1 : bit_vector(7 downto 0);…component myandport( din1: in bit;din2: in bit;dout:out bit);end component;begin…p1: myand port map(din1,din2,dout);…end behave;实际上元件例化就是对元件的包含,相当于在C++中#include的功能。

VHDL是一种硬件描述语言(课程总结)

Label:BLOCK(卫士表达式)

[声明部分]

BEGIN

(卫士语句和其他并发描述语句)

END BLOCK label;

第六章顺序代码

VHDL本质上是一种并发执行的代码,但在PROCESS,FUNCTION,PROCEDURE内部的代码都是顺序执行的。

顺序代码并非只能与时序逻辑相对应,同样可以用他们来实现组合逻辑电路。顺序代码也可以称为行为描述代码。

同步时序电路中的时钟问题

在代码中,如果在参考时钟的两个边沿(上升沿和下降沿)都可以触发对同一信号的赋值操作,那么这样的代码通常是不可综合的。

如果一个信号出现在了敏感信号列表中,但没有在PROCESS内部的任何语句中出现,通常编译器会把它忽略掉。

如果确希望两个边沿(上升沿和下降沿)都可以触发对同一信号的赋值操作,可以写两个PROCESS。

可编程逻辑器件包括:复杂可编程逻辑器件(CPLD:Complex Programmable Logic Devices),现场可编程门阵列(FPGA:Field Programmable Gate Arrays)。

VHDL语言从根本上讲是并发执行的。因此常称之为代码,而不是程序。VHDL中,只有在进程(PROCESS)、函数(FUNCTION)、和过程(PROCEDURE)内部的语句才是顺序执行的。

变量(Variable)只能在顺序代码中使用,相对于信号而言,变量只能是局部的,所以它的值不能传递到PROCESS,FUNCTION,PROCEDURE外部。

PROCESS语句具有敏感信号列表(sensitivity list)。

在VHDL中有两种方法进行动态数值传递:信号和变量。其中信号可以在PACKAGE,ENTITY,ARCHITECTURE中声明,而变量只能在一段顺序代码中声明。因此信号通常是全局的,而变量通常是局部的。变量的值无法直接传递到PROCESS的外部。如果需要进行变量值的传递,则必须把这个值赋给一个信号,然后又该信号将变量的值传递到PROCSEE的外部。另一方面,赋予变量的值是立即生效的,在此后的代码中,此变量将使用新的变量值。而PROCESS中的信号,只有整个PROCESS运行完毕以后,新的信号值才开始生效。信号与变量的这一点区别足够一章的内容,于是第七章将用一章的内容来解释这个问题。

关于三段式状态机(VHDL)的写法心得和问题

关于三段式状态机(VHDL)的写法⼼得和问题

三段式状态机,看着很繁琐,但是⽤起来条理清晰,⾃⼰总结⼀下

第⼀段:状态改变

这⾥需要特别注意的是,第5⾏,状态变化的时候,必须要使⽤时钟沿,上升或下降,不能在两个沿都变化,虽然这样仿真正确,但是下载到硬件中⽆效,状态不会变化

1:process(clk,rst_n)

2:begin

3:if(rst_n = '0') then

4: current_state <= s_wait;

5: elsif rising_edge(clk) then

6: current_state <= next_state;

7:end if;

8:end process state_change;

第⼆段:状态转化

这⼀段注意:

敏感列表是current_state和process中涉及到变化的所有信号

在case xxx is 前⾯初始化 next_state <= s_wait; 这样就不⽤在下⾯状态中关⼼这个状态了

最后要写 when others => 空,据说是避免综合出锁存器,现在还不理解。