BiCMOS剖面图

半导体工艺原理-集成电路制造工艺介绍

GND

Vi

T

Vo

R VDD

23

二)、MOS集成电路芯片制 造工艺

(N阱硅栅CMOS工艺)

24

1、CMOS工艺中的元器件结构

电阻

NSD和PSD电阻结构剖面图

25

多晶硅电阻结构剖面图

26

N阱电阻结构剖面图

27

电容

CMOS工艺中PMOS晶体管电容剖面图

28

CMOS工艺中N阱电容剖面图

29

多晶硅-多晶硅电容器剖面图

双极工艺主要分类

3

CMOS

●标准CMOS工艺(数字电路的主流工艺 技术)特点:互补的NMOS、PMOS,工 艺流程简单,集成度高

●模拟CMOS工艺(应用最广泛的模拟IC 工艺)特点:在标准CMOS的基础上集成 高品质的无源器件,此外对阈值电压精度 和耐压的要求更高

●RF CMOS(RF IC) 特点:依靠缩小光刻尺寸提高MOS晶体管 的速度,集成模拟IC所必需的高品质无源 器件

30

二极管

PSD/N阱齐纳二极管剖面图

31

PSD保护环肖特基二极管剖面图

32

MOS晶体管

N阱CMOS工艺中MOS晶体管剖面图

33

P阱CMOS工艺中MOS晶体管剖面图

34

双阱CMOS工艺中MOS晶体管剖面图

35

2、主要工艺流程图

36

衬底准备

P型单晶片

P+/P外延片

37

工艺流程:

氧化、光刻N-阱(nwell)

NBL

NSINK

P阱

PBL

57

●BCD(智能功率集成芯片) 特点:在BiCMOS优势的基础上再集成 DMOS等功率器件,是智能功率芯片的理 想工艺平台

CMOS工艺阱的选择

CMOS集成电路工艺体硅CMOS工艺设计中阱工艺的选择(1) p阱工艺实现CMOS电路的工艺技术有多种。

CMOS是在PMOS工艺技术基础上于1963年发展起来的,因此采用在n型衬底上的p阱制备NMOS器件是很自然的选择。

由于氧化层中正电荷的作用以及负的金属(铝)栅与衬底的功函数差,使得在没有沟道离子注入技术的条件下,制备低阈值电压(绝对值)的PMOS器件和增强型NMOS器件相当困难。

于是,采用轻掺杂的n型衬底制备PMOS器件,采用较高掺杂浓度扩散的p阱做NMOS器件,在当时成为最佳的工艺组合。

考虑到空穴的迁移率比电子迁移率要低近2倍多,且迁移率的数值是掺杂浓度的函数(轻掺杂衬底的载流子迁移率较高)。

因此,采用p阱工艺有利于CMOS电路中两种类型器件的性能匹配,而尺寸差别较小。

p阱CMOS经过多年的发展,已成为成熟的主要的CMOS工艺。

与NMOS工艺技术一样,它采用了硅栅、等平面和全离子注入技术。

(2) n阱工艺为了实现与LSI的主流工艺增强型/耗层型(E/D)的完全兼容,n阱CMOS工艺得到了重视和发展。

它采用E/D NMOS的相同的p型衬底材料制备NMOS器件,采用离子注入形成的n阱制备PMOS器件,采用沟道离子注入调整两种沟遭器件的阈值电压。

n阱CMOS工艺与p阱CMOS工艺相比有许多明显的优点。

首先是与E/D NMOS工艺完全兼容,因此,可以直接利用已经高度发展的NMOS工艺技术;其次是制备在轻掺杂衬底上的NMOS的性能得到了最佳化--保持了高的电子迁移率,低的体效应系数,低的n+结的寄生电容,降低了漏结势垒区的电场强度,从而降低了电子碰撞电离所产生的电流等。

这个优点对动态CMOS电路,如时钟CMOS电路,多米诺电路等的性能改进尤其明显。

这是因为在这些动态电路中仅采用很少数目的PMOS器件,大多数器件是NMOS型。

另外由于电子迁移率较高,因而n阱的寄生电阻较低;碰撞电离的主要来源—电子碰撞电离所产生的衬底电流,在n 阱CMOS中通过较低寄生电阻的衬底流走。

2012级微电子工艺学试卷(A卷)参考答案

华中科技大学光学与电子信息学院考试试卷(A卷)2014~2015学年度第一学期课程名称:微电子工艺学考试年级:2012级考试时间:2015 年1 月28 日考试方式:开卷学生姓名学号专业班级一、判断下列说法的正误,正确的在后面括号中划“√”,错误的在后面括号中划“×”(本大题共10小题,每小题2分,共20分)1、随着器件特征尺寸不断缩小、电路性能不断完善、集成度不断提高,互连线所占面积已成为决定芯片面积的主要因素,互连线导致的延迟已可与器件门延迟相比较,单层金属互连逐渐被多层金属互连取代。

(√)2、采用区熔法进行硅单晶生长时,利用分凝现象将物料局部熔化形成狭窄的熔区,并令其沿锭长从一端缓慢地移动到另一端,重复多次使杂质被集中在尾部或头部,使中部材料被提纯。

区熔法一次提纯的效果比直拉法好,可以制备更高纯度的单晶。

(×)3、缺陷的存在对微电子器件利弊各半:在有源区不希望有二维和三维缺陷,而在非有源区的缺陷能够吸引杂质聚集,使邻近有源区内杂质减少,是有好处的。

(√)4、光刻胶的灵敏度是指完成曝光所需最小曝光剂量(mJ/cm2),由曝光效率决定(通常负胶比正胶有更高曝光效率) 。

灵敏度大的光刻胶曝光时间较短,但曝光效果较差。

(×)5、无论对于PMOS还是NMOS器件,要得到良好受控的阈值电压,需要控制氧化层厚度、沟道掺杂浓度、金属半导体功函数以及氧化层电荷。

(√)6、半导体掺杂中掺入的杂质必须是电活性的,能提供所需的载流子,使许多微结构和器件得以实现。

掺杂的最高极限由杂质固溶度决定,最低极限由硅晶格生长的杂质决定。

(√)7、离子注入过程是一个平衡过程,带有一定能量的入射离子在靶材内同靶原子核及其核外电子碰撞,逐步损失能量,最后停下来。

(×)8、溅射仅是离子对物体表面轰击时可能发生的四种物理过程之一,其中每种物理过程发生的几率取决于入射离子的剂量。

(√)9、等离子体刻蚀的优点是刻蚀速率较高、刻蚀选择性较好和刻蚀损伤较低,缺点是存在各向异性倾向。

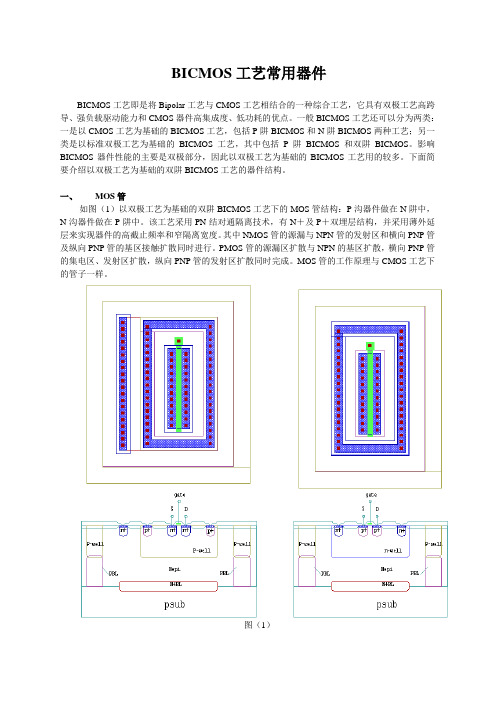

BiCMOS工艺常用器件

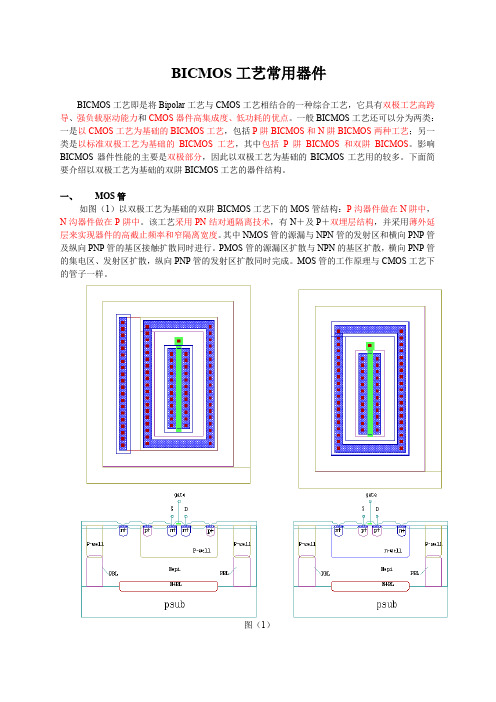

BICMOS工艺常用器件BICMOS工艺即是将Bipolar工艺与CMOS工艺相结合的一种综合工艺,它具有双极工艺高跨导、强负载驱动能力和CMOS器件高集成度、低功耗的优点。

一般BICMOS工艺还可以分为两类:一是以CMOS工艺为基础的BICMOS工艺,包括P阱BICMOS和N阱BICMOS两种工艺;另一类是以标准双极工艺为基础的BICMOS工艺,其中包括P阱BICMOS和双阱BICMOS。

影响BICMOS器件性能的主要是双极部分,因此以双极工艺为基础的BICMOS工艺用的较多。

下面简要介绍以双极工艺为基础的双阱BICMOS工艺的器件结构。

一、MOS管如图(1)以双极工艺为基础的双阱BICMOS工艺下的MOS管结构:P沟器件做在N阱中,N沟器件做在P阱中。

该工艺采用PN结对通隔离技术,有N+及P+双埋层结构,并采用薄外延层来实现器件的高截止频率和窄隔离宽度。

其中NMOS管的源漏与NPN管的发射区和横向PNP管及纵向PNP管的基区接触扩散同时进行。

PMOS管的源漏区扩散与NPN的基区扩散,横向PNP管的集电区、发射区扩散,纵向PNP管的发射区扩散同时完成。

MOS管的工作原理与CMOS工艺下的管子一样。

图(1)二、三极管(1)NPN管NPN晶体管是双极集成电路中的基本器件,如图(2)以N外延层为集电区,Basep为基区,在Basep中做一重掺杂的N+为发射区。

由其剖面图可见,NPN存在寄生的PNP,但是这个寄生的PNP不是在任何情况下都起作用。

在模拟电路中,由于NPN管一般都处于截止或正向工作区,V BC-NPN<0,所以寄生PNP的发射结是反偏的,因为V BE-PNP= V BC-NPN<0,因而寄生PNP管截止。

而在数字电路中,NPN工作在饱和区或反向工作区,此时V BE-PNP= V BC-NPN>0,寄生PNP将处于正向工作区,这将使相当大的一股反向NPN管的“发射极电流”变成无用电流流入衬底。

BiCMOS集成电路的基本制造工艺

半导体集成电路

1 以双极工艺为基础的P阱BiCMOS工艺

半导体集成电路

2 以双极型工艺为基础的双埋层双阱BiCMOS器件剖面图

• 这种结构的特点是采用N+及P+双埋层双阱 结构,采用薄外延层来实现双极器件的高截止 频率和窄隔离宽度。 • 此外,利用CMOS工艺的第二层多晶硅做双极 器件的多晶硅发射极,不必增加工艺就能形成 浅结和小尺寸发射极。

半导体集成电路

小结:

BiCMOS工艺是把双极器件和CMOS器件制做在 同一芯片上。它综合了两种器件的优点,给高速 度、高集成度、高性能的LSI及VLSI 的发展开辟 了一条新的道路。优势互补、取长补短。 BiCMOS工艺可分为两大类:一类是以CMOS工 艺为基础的;另一类是以标准双极工艺为基础的。 以标准双极工艺为基础的BiCMOS工艺对保证器 件中的双极器件有利。影响BiCMOS工艺器件性 能的主要是双极部分,因此以标准双极工艺为基 础的BiCMOS工艺用得较多。

3 采用多晶硅发射极以提高速度; 4 在P阱中制作横向NPN管,提高NPN管使用范 围。

半导体集成电路

横向NPN

B

C

E

C

D

G

S

C

G

C

P+ N+ N+ N+

P阱

N+

P阱

N+

P+

P+

N-—SUB

半导体集成电路

2 N阱CMOS为基础的BiCMOS

主要缺点:

NPN管的 集电极串连电 阻太大。

半导体集成电路

保证CMOS器件性能 保证双极器件性能

半导体集成电路

BiCMOS工艺分类

• BiCMOS工艺技术大致可以分为两类:分

BJT版图设计

Copyright by Huang Weiwei

BJT工作原理

雪崩击穿

NPN管的理想VCEO、VCER、VCES曲线轨迹

华侨大学厦门专用集成电路系统重点实验室

华侨大学电子工程系

Copyright by Huang Weiwei

BJT工作原理

热击穿和二次击穿

BJT工作于较高的温度时容易产出热击穿,假设 BJT功率管的稳定升高,引发VBE略微下降,由于电压 和电流间的指数关系,发射结电流微小增加会引发集电 极电流的较大增加,增加的功耗使得晶体管温度升高, 导致VBE的进一步下降。如此容易在晶体管内产生稳定 很高的“热点”,使器件失效。

华侨大学厦门专用集成电路系统重点实验室

华侨大学电子工程系

Copyright by Huang Weiwei

BJT工作原理

I BIAS

I1

I2

I3

Q1

Q2

Q3

基极限流电阻防止电流翘曲效应

华侨大学厦门专用集成电路系统重点实验室

华侨大学电子工程系

Copyright by Huang Weiwei

BJT工作原理

华侨大学电子工程系

Copyright by Huang Weiwei

标准双极小信号晶体管

C

E

B

-

N+

+

P

E

B

NBL

发射区电流集边效应

华侨大学厦门专用集成电路系统重点实验室

华侨大学电子工程系

Copyright by Huang Weiwei

标准双极小信号晶体管

C E B

华侨大学厦门专用集成电路系统重点实验室

E NPN

《集成电路制造工艺与工程应用》第一章课件

4

铝栅套刻不齐问题

PMOS源漏离子扩散工艺

(a)源漏有源区光刻

PMOS铝栅工艺

(b)显影

(c)源漏有源区刻蚀

(c)源漏离子扩散

(a)光刻

(b)显影

(c)刻蚀

《集成电路制造工艺与工程应用》讲义 2018/09/28

(a)铝互连和铝栅光刻

(b)显影

(c)铝互连和铝栅刻蚀

5

NMOS工艺技术

《集成电路制造工艺与工程应用》讲义 2018/09/28

2. CMOS是互补金属氧化物半导体,它是把NMOS和PMOS制造在同一个芯片上组成集成电路, CMOS 工艺技术就是利用互补对称电路来配置连接PMOS和NMOS从而形成逻辑电路。

3. CMOS工艺技术的特点:

a) 静态功耗几乎接近为零,可以很好的解决功耗问题;

b) 特征尺寸按比例缩小,可以选择较低的电源电压;

2. HV-CMOS工艺集成电路的基本设计思想: a) 芯片内部核心逻辑部分采用CMOS器件为主要单元门电路; b) 而输出缓冲电路和驱动部分电路要求驱动高压信号,所以输出缓冲电路和驱动部分电路使用高 压器件。

3. HV-CMOS工艺集成电路主要应用在LCD和LED屏幕驱动芯片。

13

《集成电路制造工艺与工程应用》讲义 2018/09/28

导致栅极寄生电容Cgs和Cgd增大 ==》 增加器件的尺寸 ==》 降低集成度。 4. PMOS主要用在速度比较慢的时钟控制电路。 1974年, 加德士半导体利用PMOS设计时钟集成电路。

源

铝栅

漏

源

铝栅

漏

《集成电路制造工艺与工程应用》讲义 2018/09/28

p+

p+

BCD工艺提图

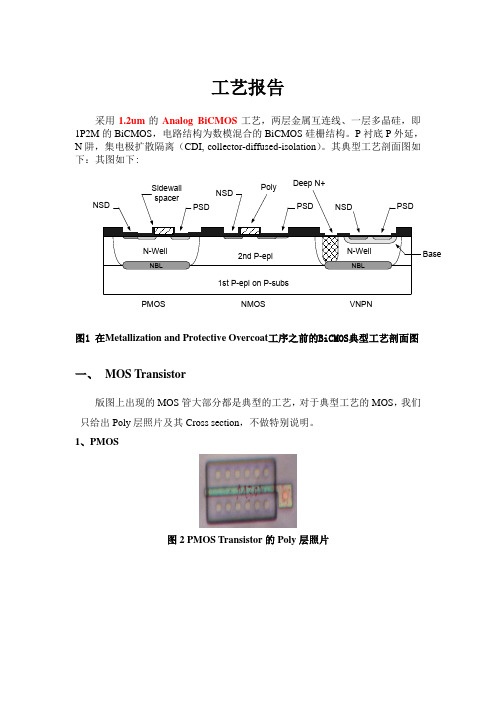

工艺报告采用1.2um 的Analog BiCMOS 工艺,两层金属互连线、一层多晶硅,即1P2M 的BiCMOS ,电路结构为数模混合的BiCMOS 硅栅结构。

P 衬底P 外延,N 阱,集电极扩散隔离(CDI, collector-diffused-isolation )。

其典型工艺剖面图如下:其图如下:Deep N+PMOS NMOS VNPNBase图1 在Metallization and Protective Overcoat 工序之前的BiCMOS 典型工艺剖面图一、 MOS Transistor版图上出现的MOS 管大部分都是典型的工艺,对于典型工艺的MOS ,我们只给出Poly 层照片及其Cross section ,不做特别说明。

1、PMOS图2 PMOS Transistor 的Poly 层照片图3 Cross section of a PMOS Transistor 2、nmos图4 NMOS Transistor的Poly层照片图5 Cross section of a NMOS Transistor3、Waffle transistor版图上的一半面积都用来做电路中的一个关键器件——Waffle transistor,版图示意如上。

源漏区域为矩阵结构,且漏极也做在n阱中,为非自对准工艺,可承受高压大电流。

Waffle transistor比常规的交叉指型管多提供33%的跨导,但是,这将使镀金电阻成为R ds(on)的主要组成部分,而且会使得源漏部分的雪崩击穿电压比晶体管其它部分低,衬底接触也不好。

图6 Waffle Transistor的Poly层照片G GG G S/D D/S S/D 图7 Cross section of a Waffle Transistor4、VDMOS图8二、Bipolar Transistors版图上出现的BTJ 大部分都是典型的Bipolar 工艺,对于典型工艺的BTJ ,我们只给出Poly 层照片及其Cross section ,也不做特别说明。

18 Bicmos

图一 输出特性

图二 转移特性

② BJT的输出电流随输入电压上升的变化快的多 的输出电流随输入电压上升的变化快的多 对于BJT, Ic ∝ exp(qVBE / KT) , 对于 对于MOS , IDS ∝ (VGS −VT ) 对于 存在基极电流. ③BJT存在基极电流. 存在基极电流

2

2.二类IC的差别 二类 的差别

开关速度慢

设计BJT的关键: 设计BJT的关键: 的关键 获得尽可能大的I 获得尽可能大的IC和尽可能小 的 IB

二、先进的双极工艺

双极型的一个重要特点是纵向尺寸无法跟横向 尺寸成正比缩减,这使得双极工艺始终落后于MOS 尺寸成正比缩减,这使得双极工艺始终落后于 一到二代。 一到二代。 BJT最重要的是 和截止频率 最重要的是β和 最重要的是 截止频率↑:Wb↓,寄生结电容 寄生结电容↓ 截止频率 : 寄生结电容 β↑:发射区掺杂浓度 基区掺杂浓度 注入效率 基区掺杂浓度↑注入效率 :发射区掺杂浓度/基区掺杂浓度 注入效率↑ 但是,基区掺杂浓度太低容易发生基区穿通, 但是,基区掺杂浓度太低容易发生基区穿通, 所以一般提高发射区掺杂浓度,但发射区浓度太高, 所以一般提高发射区掺杂浓度,但发射区浓度太高, 杂质高度简并,会使Eg ,少子复合↑ 注入效率↓, 杂质高度简并,会使 ↓,少子复合 ,注入效率 , β↓

片间涨落小, 片间涨落小,可 获得小的电压摆 幅

易于小 信号应 用

输入电压直接控制提供 输出电流的载流子密度

高跨导

输入电容由 扩散电容决 定

随工作电流的减 小而减小

可同时在大或小的电 流下工作而无需调整 输入电容

缺点: 缺点:

存在直流输入电 流,基极电流 饱和区中存储电 荷上升 开态电压无法成 为设计参数 功耗大

各种元件的版图

版图学习一.MOS管工艺(1)普通MOS管这种结构很容易和多晶硅电阻混淆,判别方法是:1.多晶硅是否放置在有源区上面;2.看多晶硅有几个端口引出。

高宽长比MOS器件:(2)叉指MOS管叉指MOS管判断的关键是看多晶硅层,观察它有几个输入。

(3)耐高压MOS管该晶体管为Extended-Drain,High-Voltage transistor,为非自对准工艺,版图示意如上。

这种晶体管使用n阱作为轻掺杂的漏极。

这种结构为源漏不对称的MOS管,具体实现高压原理不是很清楚。

(4)功率开关MOS管版图上的一半面积都用来做电路中的一个关键器件——功率开关MOS,版图示意如上。

源漏区域为矩阵结构,且漏极也做在n阱中,为非自对准工艺,因此判断这个晶体管是waffle transistor和Extended Drain HV transistor的结合,可承受高压大电流。

另外,在版图中,NMOS和PMOS可通过如下规则判断:1、对于数字电路,CMOS中的P管W/L大,N管W/L小2、源极接Vdd的一般为PMOS,接Vss的一般为NMOS3、模拟电路不完全服从以上规律。

可结合电路结构来分析。

如差分放大器尾电流接Vss,则差分对及尾电流MOS器件为NMOS,负载管则可以基本判定为PMOS二.BJT工艺基本规则:从版图上来看,晶体管的集电极和发射极具有相同的颜色。

BJT工艺一般分为VNPN和LPNP两种工艺,其中VNPN又分两种:Standard VNPN和double-base VNPN(1)VNPN(2)double-base VNPN(3)LPNP其他形式的版图:(4)LNPN这种结构与一般VNPN结构的区别在于,后者一般是用P-SUB制作,而它采用的是N-SUB,P-WELL的工艺。

在版图中,NPN管和PNP管可通过如下规则判断:纵向管:除极特殊的情况外,NPN管的C极接向电源正极,PNP的C极接向电源负极。

刻蚀培训教材

如气体流量、温度、或晶片上材料一批与一批间的差异,都会影响刻蚀时间

的控制,因此,必须时常检测刻蚀速率的变化;使用终点侦测器的方法。可

以计算出刻蚀结束的正确时间,进而准确地控制过度刻蚀的时间,以确保多

次刻蚀的再现性。

• 常见的终点侦测有三种方法:

•

1. 光学放射频谱分析(Optical Emission CO-483.5nm

• 金属刻蚀 (Al,W,Ti,TiN,Pt,…) • -工艺: WL, BL, Cap, MLM: Al, W, Pt, Ru, Ta, etc • -使用气体 : Cl2, BCl3, CCl4, etc

• 介质刻蚀(SiO2, Si3N4,PSG,BPSG,SiON… ) • -工艺: ISO, Contact (Poly C/T, Metal C/T, Via), Spacer ,

• 金属铝腐蚀 -Al Etch

• HNO3 : 氧化剂, H3PO4 :刻蚀剂, CH3COOH : 缓冲剂

• 氮化硅腐蚀 -Silicon Nitiride Etch

• Hot (>150℃) H3PO4 :刻蚀剂

• 3#去胶 - SC-3(120℃)

• H2SO4 + H2O2 = H2SO5 + H2O • H2SO5 + PR = H2SO4 + CO2 + H2O

什么是等离子体

等离子体是低压气体(一般 < 1 torr)在外 界电场(DC, AC, RF, µwave)作用下,局部 气体发生电离而产生的;它由正离子,电 子,中性原子,中性分子组成。

• 电离 Ionization • 分裂 Dissociation • 激发 Excitation

双极型晶体管

三、 CMOS 和BICMOS 工艺小信号双极型晶体管

1.模拟 CMOS 工艺,NPN,PNP性能很差 2 功率BICMOS工艺,DMOS,耐压高,速度慢 3 高速BICMOS工艺,速度快,耐压低,多晶硅发射 极,SiGe技术

1. 标准双极型NPN 晶体管

标准双极型NPN 晶体管的关键特征 发射区重掺杂磷,基区杂质精确控制, 集电极包括N型外延层,N+掩埋层,深N+侧阱降低电阻 轻掺杂的漂移区可以提高VCEO, NBL提供低阻通路

集电极必须接VSS VPNP即衬底PNP的发射极是与源漏扩散同时形成的, 基极是阱形成的,P衬底是集电极接最负电位。 其晶体管的作用发生在纵向,所以也叫纵向PNP。因基 区是阱,所以基区电阻较大。

CMOS 工艺 NPN 晶体管

在基本N阱CMOS工艺的基础上再加一道工序,即在 源漏扩散前加一掺杂的P型扩散层BP,就可以制作纵向 NPN管,即VNPN。

5. 寄生NPN 晶体管的饱和状态

寄生的PNP 管QP1 代表不希望出现的注入到衬底的 空穴流。寄生的PNP 管QP2 代表 饱和状态时横向流过隔离区侧壁的空穴流。

6. 双极型晶体管的寄生效应

1) 集电结电容CBC 和集电区-衬底结电容CCS 限制了 晶体管的工作频率。 2) 二极管DBE,DBC,DCS 的雪崩击穿电压限定了晶 体管的工作电压。 3) RE,RB,RC 分别代 表发射区、基区和集电 区扩散形成的集成电阻

模拟BICMOS 中 NPN晶体管

通过环形深N 阱,作为晶体管集电极,增加N掩埋层 Β高,具有更高的平面集电结击穿电压。

二极管

SiGe BiCMOS工艺集成技术研究

SiGe BiCMOS工艺集成技术研究李红征【摘要】SiGe(硅锗合金)BiCMOS工艺集成技术,是在制造电路结构中的双极晶体管时,在硅基区材料中加入一定含量的锗,形成应变硅异质结构晶体管,以改善双极晶体管特性的一种硅基工艺集成技术。

对硅锗合金BiCMOS工艺的核心器件——锗硅异质结双极晶体管SiGe HBT的关键工艺模块,包括收集区、基区、发射区和深槽隔离的器件结构与制作工艺进行了研究与探讨。

对常用的3种SiGe BiCMOS工艺集成技术BBGate工艺、BAGate工艺和BDGate工艺,进行了工艺集成技术难点与关键工艺方面的研究,并比较了各种工艺流程的优缺点及其适用范围。

%SiGe HBT, the essential device of SiGe BiCMOS technology, is introduced. The process modules of the formation of Collector, Base and Emitter of the SiGe HBT are introduced. Also 3 types of process flow, BBGate, BAGate, BDGate, applied in different SiGe BiCMOS technology nodes, are discussed. The paper reviews the process development and integration methodology, presents the device characteristics, and shows how the development and device selection were geared toward usage in mixed-signal IC development.【期刊名称】《电子与封装》【年(卷),期】2015(000)012【总页数】4页(P34-37)【关键词】硅锗合金;BiCMOS工艺;异质结双极晶体管;BBGate工艺;BAGate工艺;BDGate工艺【作者】李红征【作者单位】中国电子科技集团公司第58研究所,江苏无锡 214035【正文语种】中文【中图分类】TN305SiGe(硅锗合金)BiCMOS工艺集成技术,是在制造电路结构中的双极晶体管时,在硅基区材料中加入一定含量的锗,形成应变硅异质结构晶体管,以改善双极晶体管特性的一种硅基工艺集成技术。

集成电路分析与设计1

N+

N+

P N阱

N+- BL

1.4 BiCMOS工艺简介

双极工艺为基础 的BiCMOS工艺(1)

(1)以CMOS工艺为基础的BiCMOS工艺中,影响 BiCMOS电路性能的主要是双极型器件。显然, 若以双极工艺为基础,对提高双极型器件的性 能是有利的

(2)这种结构克服了以P阱CMOS工艺为基础的 BiCMOS结构的缺点,而且还可以用此工艺获得 对高压、大电流很有用的纵向PNP管和LDMOS及 VDMOS结构

C

EB

PMOS

NMOS

N+

P

N 阱 N+

N+

P+ P阱 P+

N 阱 P+ N+ N+

P阱 N+ 外 延 层

P+

P- SUB

1.4

BiCMOS工艺简介

双极工艺为基础 的BiCMOS工艺(4)

这种结构的特点是采用N+及P+双埋层双阱结构, 采用薄外延层来实现双极器件的高截止频率和 窄隔离宽度。

此外,利用CMOS工艺的第二层多晶硅做双极器 件的多晶硅发射极,不必增加工艺就能形成浅 结和小尺寸发射极。

这种结构的缺点是: (1)由于NPN晶体管的基区在P阱中,所以基 区的厚度太大,使得电流增益变小 (2)集电极的串联电阻很大,影响器件性能 (3)NPN管和PMOS管共衬底,使得NPN管只 能接固定电位,从而限制了NPN管的使用

1.4

BiCMOS工艺简介

N阱CMOS工艺为基础 的BiCMOS工艺(1)

(d)硅片刻蚀 (e)场氧生长 (f)表面去除氮化物或氧化物

1.2 CMOS工艺流程 基本流程(3)

亚微米BiCMOS[B]芯片与制程剖面结构

![亚微米BiCMOS[B]芯片与制程剖面结构](https://img.taocdn.com/s3/m/278886a51a37f111f0855b05.png)

b a s e d o n t h e b i p o l a r p r o c e s s , a n d t h e c o mp a t i b l e B i C MOS [ B 】 p r o c e s s i s i mp l e me n t e d o n t h e s a me s i l i c o n s u b s t r a t e 。 T h i s i s a s u b mi c r o n B i CMO S [ B 】 i n t e g r a t e d c i r c u i t c h i p s t r u c t u r e d e s i g n ,

S t r u c t u r e o f Su b mi c r o n B i CM OS[ B 】 Ch i p a n d

Pr oc e s s

PAN Gug h a i B e l l i n g Co . , L t d , S h a n g h a i 2 0 0 2 3 3 , Ch i n a .

摘要 :亚微米 B i CM OS [ B 】 技术能够 实现双极 型与 C M OS 元器件兼容 的工艺 。为 了便 于集成 ,采 用双极型制程为基础 ,引入 C MO S 元器件工艺 ,在 同一硅衬底 上实现兼容 的 B i C MOS [ B ] 工艺 。 这是采用亚微 米 B i C MOS [ B 】 集成 电路芯片结构设计、工艺与制造技术 ,依该技术得到 了芯 片制程 结构。 关键词 :集成 电路制造 , I工艺 ; 亚微 米 B i C MO S [ B 】 ;剖面结构

1 亚微 米 B i C MOS [ B J 技术 的主要 特 点

Bi CM OS『 B] 的 T wi n — We l l L 与 P. We l l L 或 N 。 We l l t j J 的制 造技 术有 很 大 的不 同 。主要 是 C MO S特

BCD工艺提图

工艺报告采用1.2um 的Analog BiCMOS 工艺,两层金属互连线、一层多晶硅,即1P2M 的BiCMOS ,电路结构为数模混合的BiCMOS 硅栅结构。

P 衬底P 外延,N 阱,集电极扩散隔离(CDI, collector-diffused-isolation )。

其典型工艺剖面图如下:其图如下:Deep N+PMOS NMOS VNPNBase图1 在Metallization and Protective Overcoat 工序之前的BiCMOS 典型工艺剖面图一、 MOS Transistor版图上出现的MOS 管大部分都是典型的工艺,对于典型工艺的MOS ,我们只给出Poly 层照片及其Cross section ,不做特别说明。

1、PMOS图2 PMOS Transistor 的Poly 层照片图3 Cross section of a PMOS Transistor2、nmos图4 NMOS Transistor的Poly层照片图5 Cross section of a NMOS Transistor3、Waffle transistor版图上的一半面积都用来做电路中的一个关键器件——Waffle transistor,版图示意如上。

源漏区域为矩阵结构,且漏极也做在n 阱中,为非自对准工艺,可承受高压大电流。

Waffle transistor 比常规的交叉指型管多提供33%的跨导,但是,这将使镀金电阻成为R ds(on)的主要组成部分,而且会使得源漏部分的雪崩击穿电压比晶体管其它部分低,衬底接触也不好。

图6 Waffle Transistor 的Poly 层照片GGGGS/DD/S S/D 图7 Cross section of a Waffle Transistor4、VDMOS图8二、Bipolar Transistors版图上出现的BTJ 大部分都是典型的Bipolar 工艺,对于典型工艺的BTJ ,我们只给出Poly 层照片及其Cross section ,也不做特别说明。

第8章三极管版图

16

IC IB或IB,IE (1 IB)或(1 )IB

三极管制作工艺的的特点: ----保证三极管具有放大作用的内部条件。

➢发射区的掺杂浓度比基区和集电区高得多

➢基区很薄且掺杂浓度底

➢集电极结面积大

e

NPN型

N PN

bc

管芯结构剖面图

双极性晶体管工艺:横向工艺和纵向工艺

横向工艺:横向NPN版图迫使P区变大,因为需要满足接 触需要,这就降低你开关的速度。

IC

RB I B

RC

U BB

U CC

电位 关系

对NPN型:VC > VB > VE

三极管内部载流子的传输过程(以NPN共射极电路为例)

IC

发射区

N

(大量电子)

RC

发射结

扩散

IB

RB

输

入

U BB

回 路

输

P

出 回

路

U CC

N

Байду номын сангаас

正偏

IE

复合

基区

集电结 正偏

IB

漂移

IC

IE

集电区

说明:发射区大量电子在发射结的扩散运动形成IE,在基区的与空穴的复 合,形成基极电流IB,电子在集电结的漂移形成IC。三极管中电流的形成 主要是发射区电子的运动形成,当然在三极管中还有其他载流子的漂移

8

基本IC单元版图设计 –双极性晶体管

纵向工艺: - 纵向npn晶体管的基极和集电极连接似乎很困难,但是因 器件各层的水平长度并不影响器件的速度,扩展水平长度是解 决问题的关键。 - 基区/发射区结的制备要比基区/集电区结的制备重要的多, 所以要使器件颠倒过来,最后制备发射区,因为先制备的层比 后制备的层要承受更多的扩散过程和应力作用。

BICMOS器件介绍

BICMOS工艺常用器件BICMOS工艺即是将Bipolar工艺与CMOS工艺相结合的一种综合工艺,它具有双极工艺高跨导、强负载驱动能力和CMOS器件高集成度、低功耗的优点。

一般BICMOS工艺还可以分为两类:一是以CMOS工艺为基础的BICMOS工艺,包括P阱BICMOS和N阱BICMOS两种工艺;另一类是以标准双极工艺为基础的BICMOS工艺,其中包括P阱BICMOS和双阱BICMOS。

影响BICMOS器件性能的主要是双极部分,因此以双极工艺为基础的BICMOS工艺用的较多。

下面简要介绍以双极工艺为基础的双阱BICMOS工艺的器件结构。

一、MOS管如图(1)以双极工艺为基础的双阱BICMOS工艺下的MOS管结构:P沟器件做在N阱中,N沟器件做在P阱中。

该工艺采用PN结对通隔离技术,有N+及P+双埋层结构,并采用薄外延层来实现器件的高截止频率和窄隔离宽度。

其中NMOS管的源漏与NPN管的发射区和横向PNP管及纵向PNP管的基区接触扩散同时进行。

PMOS管的源漏区扩散与NPN的基区扩散,横向PNP管的集电区、发射区扩散,纵向PNP管的发射区扩散同时完成。

MOS管的工作原理与CMOS工艺下的管子一样。

图(1)二、三极管(1)NPN管NPN晶体管是双极集成电路中的基本器件,如图(2)以N外延层为集电区,Basep为基区,在Basep中做一重掺杂的N+为发射区。

由其剖面图可见,NPN存在寄生的PNP,但是这个寄生的PNP不是在任何情况下都起作用。

在模拟电路中,由于NPN管一般都处于截止或正向工作区,V BC-NPN<0,所以寄生PNP的发射结是反偏的,因为V BE-PNP= V BC-NPN<0,因而寄生PNP管截止。

而在数字电路中,NPN工作在饱和区或反向工作区,此时V BE-PNP= V BC-NPN>0,寄生PNP将处于正向工作区,这将使相当大的一股反向NPN管的“发射极电流”变成无用电流流入衬底。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Page 2.8-2

n+ and p+ Buried Layers Starting Substrate:

p-substrate

BiCMOS-01

1µm 5µm

n+ and p+ Buried Layers:

NPN Transistor n+ buried layer p+ buried layer PMOS Transistor n+ buried layer NMOS Transistor p+ buried layer

n-well n+ buried layer

p-well p+ buried layer

n-well n+ buried layer

p-well

p-type Epitaxial Silicon

p+ buried layer

p-substrate

BiCMOS-03

1µm 5µm

Comment: • As the epi layer grows vertically, it assumes the doping level of the substrate beneath it. • In addition, the high temperature of the epitaxial process causes the buried layers to diffuse upward and downward.

FOX

n+ buried layer

p+ buried layer

n+ buried layer p-substrate

p+ buried layer 1µm 5µm

BiCMOS-08

CMOS Analog Circuit Design Chapter 2 – Section 8 (5/02/04)

BiCMOS-09

CMOS Analog Circuit Design

© P.E. Allen - 2004

Chapter 2 – Section 8 (5/02/04)

Page 2.8-10

Emitter Implant

NPN Transistor Emitter Implant FOX Collector Tub

FOX

n+ buried layer

p+ buried layer

n+ buried layer p-substrate

p+ buried layer 1µm 5µm

BiCMOS-12

Comments: • The surface of the region where the MOSFETs are to be built is cleared and a thin gate oxide is deposited with a polysilicon layer on top of the thin oxide • The polysilicon is removed over the source and drain areas • A light source/drain diffusion is done for the NMOS and PMOS (separately)

FOX

n+ buried layer

p+ buried layer

n+ buried layer p-substrate

p+ buried layer 1µm 5µm

BiCMOS-11

Comments: • The polysilicon not over the emitter window is removed and the n-type carriers diffuse into the base forming the emitter

Page 2.8-8

Base Definition

NPN Transistor FOX Collector Tub PMOS Transistor Field Oxide p-well Field Oxide n-well NMOS Transistor Field Oxide p-well p-type Epitaxial Silicon

n-well

p-well

p-type Epitaxial Silicon

n+ buried layer

p+ buried layer

n+ buried layer p-substrate

p+ buried layer 1µm 5µm

BiCMOS-04

Comment: • The collector area is developed by an initial implant followed by a drive-in diffusion to form the collector tub.

FOX

Field Oxide

n+ buried layer

p+ buried layer

n+ buried layer p-substrate

p+ buried layer 1µm 5µm

BiCMOS-07

CMOS Analog Circuit Design

© P.E. Allen - 2004

Chapter 2 – Section 8 (5/02/04)

© P.E. Allen - 2004 Page 2.8-9

Definition of the Emitter Window and Sub-Collector Implant

NPN Transistor

Sacrifical Oxide

PMOS Transistor Field Oxide p-well Field Oxide n-well

CMOS Analog Circuit Design Chapter 2 – Section 8 (5/02/04)

© P.E. Allen - 2004 Page 2.8-5

Active Area finition

NPN Transistor PMOS Transistor NMOS Transistor Nitride α-Silicon Collector Tub p-well n-well p-well p-type Epitaxial Silicon

Sub-Collector

PMOS Transistor Field Oxide p-well Field Oxide n-well

NMOS Transistor Field Oxide p-well p-type Epitaxial Silicon

FOX

n+ buried layer

p+ buried layer

n+ buried layer p-substrate

p+ buried layer 1µm 5µm

BiCMOS-10

Comments: • The polysilicon above the base is implanted with n-type carriers

CMOS Analog Circuit Design Chapter 2 – Section 8 (5/02/04)

CMOS Analog Circuit Design

© P.E. Allen - 2004

Chapter 2 – Section 8 (5/02/04)

Page 2.8-12

Formation of the MOS Gates and LD Drains/Sources

NPN Transistor FOX PMOS Transistor Field Oxide p-well Field Oxide n-well NMOS Transistor Field Oxide p-well p-type Epitaxial Silicon

n+ buried layer

p+ buried layer

n+ buried layer p-substrate

p+ buried layer 1µm 5µm

BiCMOS-05

Comment: • The silicon nitride is use to impede the growth of the thick oxide which allows contact to the substrate • α-silicon is used for stress relief and to minimize the bird’s beak encroachment

CMOS Analog Circuit Design Chapter 2 – Section 8 (5/02/04)

CMOS Analog Circuit Design © P.E. Allen - 2004

Chapter 2 – Section 8 (5/02/04)

Page 2.8-6

Field Oxide

NPN Transistor FOX Collector Tub PMOS Transistor Field Oxide p-well n-well Field Oxide p-well NMOS Transistor Field Oxide p-type Epitaxial Silicon

© P.E. Allen - 2004 Page 2.8-11

Emitter Diffusion