STM32与FPGA+之间的FSMC通信

STM32接口FSMCFMC难点的理解---写的比较明白,容易理解

STM32接⼝FSMCFMC难点的理解---写的⽐较明⽩,容易理解摘录者说:这篇⽂章说明⽩了以下两件事:(1)ARM CPU的的32位地址怎样对应到FSMC的25:0的26根地址线;(2) 存储器宽度为8位应该怎样对应,存储器宽度为16位应该怎样对应;⼀,FSMC简FSMC,即灵活的静态存储控制器,能够与同步或异步存储器和 16 位 PC 存储器卡连接,STM32 的 FSMC 接⼝⽀持包括 SRAM、NAND FLASH、NOR FLASH 和 PSRAM 等存储器。

⼆,FSMC存储块STM32F767的FMC将外部存储器划分为6个固定⼤⼩的256M的存储区域,如下图如图:FSMC分为4块,每块256M字节⼜被划分为4*64,即四个⽚选NOR / PSRAM使⽤块1,共256MNAND闪存使⽤块2,3,共512MPC卡使⽤块4,共256M三,存储块1(Bank1)寄存器STM32 的 FSMC 存储块 1(Bank1)被分为 4 个区,每个区管理 64M 字节空间,每个区都有独⽴的寄存器对所连接的存储器进⾏配置。

Bank1 的 256M 字节空间由 28 根地址线(HADDR[27:0])寻址。

这⾥ HADDR 是内部 AHB 地址总线,其中 HADDR[25:0]来⾃外部存储器地址FSMC_A[25:0],⽽ HADDR[26:27]对 4 个区进⾏寻址。

我们要特别注意 HADDR[25:0]的对应关系:当 Bank1 接的是 16 位宽度存储器的时候:HADDR[25:1]对应 FSMC-A[24:0]。

当 Bank1 接的是 8 位宽度存储器的时候:HADDR[25:0]对应FSMC_A[25:0]。

⽐如外部存储器接到FMC_NE1上⾯,那么外部存储器的地址为HADDR[26:27] +FMC_A[25:0]=0x60000000+FMC_A[25:0]。

注:不论外部接 8 位/16 位宽设备,FSMC_A[0] 永远接在外部设备地址 A[0] 。

基于EtherCAT技术的多轴运动控制系统

基于EtherCAT技术的多轴运动控制系统张从鹏;赵康康【摘要】以EtherCAT通信技术为基础,设计了一种基于ARM和FPGA双核的EtherCAT总线式多轴运动控制系统.提出了STM32作为系统管理芯片,通过SPI通信控制ET1200从站控制芯片实现Eth-erCAT总线从站通信功能的解决方案;并采用FPGA作为协处理器,完成运动控制算法的实现和执行.完成了运动控制系统的硬件电路设计和软件开发,并制作了样机.经试验测试,实现了EtherCAT总线通信功能,采用TwinCAT完成了闭环运动控制,并且可以独立工作实现运动规划,满足工业控制工程中的应用要求.%An EtherCAT bus based multi axis motion control system was designed based on ARM and FPGA , after systemat-ically study on EtherCAT technology .The solution of main control chip STM 32 controlling ET1200 through SPI was presented .A motion control algorithm based on FPGA was developed .The specific hardware circuit and software of control system was de-signed, and a prototype was produced .The experiment demonstrates that the communication function of EtherCAT bus was real -ized, and the closed-loop motion control was completed by TwinCAT .Motion control system can work independently to achieve motion planning , meetting the application of industrial control in engineering .【期刊名称】《仪表技术与传感器》【年(卷),期】2017(000)001【总页数】5页(P115-118,122)【关键词】EtherCAT;多轴;STM32;运动控制;FPGA;插补算法;TwinCAT【作者】张从鹏;赵康康【作者单位】北方工业大学机械与材料工程学院,北京 100144;北方工业大学机械与材料工程学院,北京 100144【正文语种】中文【中图分类】TP23现代制造系统正朝着柔性化、开放化、网络化方向发展,覆盖多学科、多领域相关技术。

STM32单片机FSMC的使用解析

STM32单片机FSMC的使用解析

在做项目的过程中遇到了这个问题,感觉文章写得不错,共享给对FSMC的使用怀有疑惑的同伴们!

LCD有如下控制线:

CS:Chip Select片选,低电平有效

RS:Register Select寄存器选择

WR:Write写信号,低电平有效

RD:Read读信号,低电平有效

RESET:重启信号,低电平有效

DB0-DB15:数据线

假如这些线,全部用普通IO口控制。

根据LCD控制芯片手册(大部分控制芯片时序差不多):

如果情况如下:

DB0-DB15的IO全部为1(表示数据0xff),也可以为其他任意值,这里以0xff为例。

CS为0(表示选上芯片,CS拉低时,芯片对传入的数据才会有效)

RS为1(表示DB0-15上传递的是要被写到寄存器的值),如果为0,表示传递的是数据。

WR为0,RD为1(表示是写动作),反过来就是读动作。

RESET一直为高,如果RESET为低,会导致芯片重启。

这种情况,会导致一个值0xff被传入芯片,被LCD控制芯片当作写寄存器值去解析。

LCD 控制芯片收到DB0-15上的值之后,根据其他控制线的情况,它得出结论,这个0xff是用来设置寄存器的。

一般情况下,LCD控制芯片会把传入的寄存器值的高8位当做寄存器地址(因为芯片内部肯定不止一个寄存器),低8位当做真正的要赋给对应寄存器值。

这样,就完成了一个写LCD控制芯片内部寄存器的时序。

如果上述情况不变,只将RS置低,那么得到的情况如下:LCD控制芯片会把DB0-15上的数据当做单纯的数据值来处理。

那么假如LCD处在画图状态,这个传入的值0xff,就。

STM32与FPGA+之间的FSMC通信

1.引言STM32是ST(意法半导体)公司推出的基于ARM内核Cortex-M3的32位微掌握器系列.Cortex-M3内核是为低功耗和价钱迟钝的运用而专门设计的,具有凸起的能效比和处理速度.经由过程采取Thumb-2高密度指令集,Cortex-M3内核下降了体系存储请求,同时快速的中止处理可以或许知足掌握范畴的高及时性请求,使基于该内核设计的STM32系列微掌握器可以或许以更优胜的性价比,面向更普遍的运用范畴.STM32系列微掌握器为用户供给了丰硕的选择,可实用于工业掌握.智能家电.建筑安防.医疗装备以及花费类电子产品等多方位嵌入式体系设计.STM32系列采取一种新型的存储器扩大技巧——FSMC,在外部存储器扩大方面具有奇特的优势,可依据体系的运用须要,便利地进行不合类型大容量静态存储器的扩大.2.F SMC机制2.1F SMC技巧优势①支撑多种静态存储器类型.STM32经由过程FSMC町以与SRAM.ROM.PSRAM.NOR Flash和NANDFlash存储器的引脚直接相连.②支撑丰硕的存储操纵办法.FSMC不但支撑多种数据宽度的异步读/写操纵,并且支撑对NOR/PSRAM/NAND存储器的同步突发拜访方法.③支撑同时扩大多种存储器.FSMC的映射地址空间中,不合的BANK 是自力的,可用于扩大不合类型的存储器.当体系中扩大和运用多个外部存储器时,FSMC会经由过程总线悬空延迟时光参数的设置,防止各存储器对总线的拜访冲突.④支撑更为普遍的存储器型号.经由过程对FSMC的时光参数设置,扩大了体系中可用存储器的速度规模,为用户供给了灵巧的存储芯片选择空间.⑤支撑代码从FSMC扩大的外部存储器中直接运行,而不须要起首调入内部SRAM.STM32微掌握器之所以可以或许支撑NOR Flash和NAND Flash这两类拜访方法完全不合的存储器扩大,是因为FSMC内部现实包含NOR Flash和NAND/PC Card两个掌握器,分离支撑两种截然不合的存储器拜访方法.在STM32内部,FSMC的一端经由过程内部高速总线AHB衔接到内核Cortex-M3,另一端则是面向扩大存储器的外部总线.内查对外部存储器的拜访旌旗灯号发送到AHB 总线后,经由FSMC转换为相符外部存储器通讯规约的旌旗灯号,送到外部存储器的响应引脚,实现内核与外部存储器之间的数据交互.FSMC起到桥梁感化,既可以或许进行旌旗灯号类型的转换,又可以或许进行旌旗灯号宽度和时序的调剂,屏障失落不合存储类型的差别,使之对内核而言没有差别.FSMC治理 1 GB的映射地址空间.该空间划分为4个大小为256 MB的BANK,每个BANK又划分为4个64 MB的子BANK,如表1所列.FSMC的2个掌握器治理的映射地址空间不合.NOR Flash掌握器治理第1个BANK,NAND/PC Card掌握器治理第2~4个BANK.因为两个掌握器治理的存储器类型不合,扩大时应依据选用的存储装备类型肯定其映射地位.个中,BANK1的4个子BANK失去自力的片选线和掌握存放器,可分离扩大一个自力的存储装备,而BANK2~BANK4只有一组掌握存放器.3.F SMC扩大外部SRAM设置装备摆设在STM32 与 FPGA 进行通讯的时刻,FPGA其实可以看做STM32外部的SRAM,是以响应的设置装备摆设可以参考对外部SRAM的设置装备摆设.SRAM/ROM.NOR Flash和PSRAM类型的外部存储器都是由FSMC的NOR Flash掌握器治理的,扩大办法基底细同,个中NOR Flash最为庞杂.经由过程FSMC扩大外部存储器时,除了传统存储器扩大所须要的硬件电路外,还须要进行FSMC初始化设置装备摆设.FSMC供给大量.过细的可编程参数,以便可以或许灵巧地进行各类不合类型.不合速度的存储器扩大.外部存储器可否正常工作的症结在于:用户可否依据选用的存储器型号,对设置装备摆设存放器进行合理的初始化设置装备摆设3.1地址映射空间经由过程对FSMC特别功效存放器FSMC_BCRi(i为子BANK号,i=1,…,4)中对应掌握位的设置,FSMC依据不合存储器特点可灵巧地进行工作方法和旌旗灯号的调剂.依据选用的存储器芯片肯定须要设置装备摆设的存储器特点,重要包含以下方面:①存储器类型(MTYPE)是SRAM/ROM.PSRAM,照样NOR FlaSh;②存储芯片的地址和数据引脚是否复用(MUXEN),FSMC可以直接与AD0~AD15复用的存储器相连,不须要增长外部器件;③存储芯片的数据线宽度(MWID),FSMC支撑8位/16位两种外部数据总线宽度;④对于NOR Flash(PSRAM),是否采取同步突发拜访方法(BURSTEN);⑤对于NOR Flash(PSRAM),NWAIT旌旗灯号的特点解释(WAITEN.WAITCFG.WAITPOL);⑥对于该存储芯片的读/写操纵,是否采取雷同的时序参数来确准时序关系(EXTMOD).FSMC经由过程运用可编程的存储器时序参数存放器,拓宽了可选用的外部存储器的速度规模.FSMC的SRAM掌握器支撑同步和异步突发两种拜访方法.选用同步突发拜访方法时,FSMC将HCLK(体系时钟)分频后,发送给外部存储器作为同步时钟旌旗灯号FSMC_CLK.此时须要的设置的时光参数有2个:①HCLK与FSMC_CLK的分频系数(CLKDIV),可认为2~16分频;②同步突发拜访中获得第1个数据所须要的等待延迟(DATLAT).对于异步突发拜访方法,FSMC重要设置3个时光参数:地址树立时光(ADDSET).数据树立时光(DATAST)和地址保持时光(ADDHLD).FSMC分解了SRAM/ROM.PSRAM和NOR Flash产品的旌旗灯号特色,界说了4种不合的异步时序模子.选用不合的时序模子时,须要设置不合的时序参数,如表2所列.在现实扩大时,依据选用存储器的特点确准时序模子,从而肯定各时光参数与存储器读/写周期参数指标之间的盘算关系;运用该盘算关系和存储芯片数据手册中给定的参数指标,可盘算出FSMC所须要的各时光参数,从而对时光参数存放器进行合理的设置装备摆设.4.S TM32扩大外部SRAM实例4.1难点解析第一个角度懂得 STM32 有FSMC(其实其他芯片根本都有相似的总线功效),FSMC 的利益就是你一旦设置好之后,WR(写).RD(读).DB0DB15 这些掌握线和数据线,都是FSMC 主动掌握的.打个比方,当你在程序中写到:*(volatile unsigned short int *)(0x60000000)=val;那么FSMC 就会主动履行一个写的操纵,其对应的主控芯片的WE.RD 这些脚,就会呈现出写的时序出来(即WE=0,RD=1),数据val 的值也会经由过程DB015 主动呈现出来(即FSMCD0:FSMCD15=val ).地址0x60000000 会被呈如今数据线上(即A0A25=0,地址线的对应最麻烦,要依据具体情形来.4.1.2 硬件衔接硬件平台:(STM32F103VC + EP3C5E144C8N)将图中的IS61WV512BLL 改为FPGA 对应的接口即,可按照模式ASRAM/PSRAM进行衔接那么在硬件上面,我们须要做的,仅仅是MCU 和LCD 掌握芯片的衔接关系:WEWR,均为低电平有用RDRD,均为低电平有用FSMCD015 接LCD DB015FSMC_NE1CS 接PD7衔接好之后,读写时序都邑被FSMC 主动完成.但是还有一个很症结的问题,就是RS 没有接因为在FSMC 里面,根本就没有对应RS.怎么办呢?这个时刻,有一个好办法,就是用某一根地址线来接RS.比方我们选择了A16 这根地址线来接,那么当我们要写存放器(备注:此处应为数据)的时刻,我们须要RS,也就是A16(RS 为高)置高.软件中怎么做呢?也就是将FSMC 要写的地址改成0x60010000,如下:*(volatile unsigned short int *)(0x60010000)=val;这个时刻,A16 在履行其他FSMC 的同时会被拉高,因为A0A18 要呈现出地0x60010000.0x60010000 里面的Bit17=1,就会导致A16 为1.当要读数据(备注:此处为存放器)时,地址由0x60010000 改为了0x60000000,这个时刻A16 就为0了.RS 问题:RS 为0 暗示;读写存放器;RS 为1,读写数据RAM;ST公司为用户开辟供给了完全.高效的对象和固件库,个中运用C说话编写的固件库供给了笼罩所有尺度外设的函数,运用户无需运用汇编操纵外设特点,从而进步了程序的可读性和易保护性.STM32固件库中供给的FSMC的SRAM掌握器操纵固件,重要包含1个数据构造和3个函数FSMC_NORSRAMInitStructure (挪用库函数)RCC_Configuration(); (时钟选择)NVIC_Configuration(); (中止优先级)FSMC_GPIO_Configuration(); (衔接IO 口初始化)FSMC_SRAM_Init(); (FMSC设置装备摆设)USART_Initial(); (UART1端口设置装备摆设)4.2其他人调试碰到问题点(摘录)项目中须要运用STM32和FPGA通讯,运用的是地址线和数据线,在FPGA中依据STM32的读写模式A的时序完成写入和读取.之前的PCB设计中只运用了8跟数据线和8根地址线,调试进程中没有发明什么问题,在如今的PCB中运用了8根地址线和16根数据线,数据宽度也改成了16位,刚开端是读取数据不准确,后来发明了问题,STM32在16位数据宽度下有个表里地址映射的问题,只须要把FPGA中的设定的地址乘以2在STM32中拜访就可以了,但是在写操纵的时刻会消失写当前地址的时刻把后面的地址写成0的情形,比方说我给FPGA中界说的偏移地址0x01写一个16位数据,按照地址映射,在STM32中我把地址写入0x02,.现实测试发明这个地址上的数据是对的,但是FPGA中0x02地址上的数据也变成了00.块1存储区被划分为4个NOR/PSRAM区,这四个区在内部地址上是持续分列的.但是现实上每个区共用的是统一组地址线与数据线,是以须要有表里的一个地址映射,是以在STM32中现实上有两个地址,一个是在内部拜访的地址,别的一个是现实地址线输出的地址.HADDR[27:0]对应的是须要转换到外部存储器的内部AHB地址线,其HADDR[27:26]位用于选择四个存储块之一.HADDR[25:0]包含外部存储器地址.HADDR是字节地址,而不合的外部存储器数据长度也不一样,是以在数据宽度为8位和16位时映射关系也不一样.在数据宽度为8位时HADDR[25:0]与FSMC_A[25:0]对应相连,这时刻在STM32中拜访的地址和现实地址线产生的地址是一致的.而在16位数据宽度时HADDR[25:1]与FSMC_A[24:0]对应相连,HADDR[0]未接,这时刻现实地址线上给出的地址为须要拜访的偏移地址的一半.经由一晚上的测试,发明写数据时现实上是进行了多次写入,导致把后面的地址也给写上了,最终导致数据凌乱,后来经由学长提示,决议把拜访的地址界说为16位的,本来是32位的,经由测试问题解决.所以这儿也算是长了经验,因为我只用了8根地址线,为了防止可能的问题,地址最好界说成对应的位数.但是照样很纳闷为什么之前八位数据线读写的时刻没有这个问题.5.结语STM32作为新一代ARM CortexM3核处理器,其卓著的机能和功耗掌握可以或许实用于普遍的运用范畴;而其特别的可变静态存储技巧FSMC具有高度的灵巧性,对于存储容量请求较高的嵌入式体系设计,可以或许在不增长外部分立器件的情形下,扩大多种不合类型和容量的存储芯片,下降了体系设计的庞杂性,进步了体系的靠得住性.。

浅析STM32 FSMC操作LCD的过程

浅析STM32 FSMC操作LCD的过程FSMC称为灵活的静态存储器,它能够与同步或异步存储器和16位PC存储器卡连接,(STM32)F4的FSMC(接口)支持包括S(RAM)、NAND FLASH、NOR FLASH和PSRAM等存储器。

FSMC框图从FSMC框图可以看到,FSMC将外部设备分为2类:NOR/PSRAM设备和NAND/PC卡设备。

所有外部存储器共享地址、数据和控制(信号),但有各自的片选信号。

FSMC 一次只能访问一个外部器件。

这里将LCD的片选接口与FSMC_NE4相连,即利用FSMC_NE4实现对LCD的片选;另外SRAM(芯片)的片选接口与FSMC_NE3相连,即利用FSMC_NE3实现对SRAM芯片的片选。

FSMC本身就是静态存储器(控制器),通过FSMC接口访问SRAM是理所当然的事,这里能将LCD也连接到FSMC,显然说明LCD在操作上与SRAM有相似之处。

SRAM的控制一般有:地址线(如A18A0)、数据线(如D15D0)、写信号(WE)、读信号(OE)、片选信号(CS),如果SRAM支持字节控制,那么还有UB/LB信号。

LCD的信号则包括:(寄存器)选择((RS))、数据线(D15-D0)、写信号(WE)、读信号(OE)、片选信号(CS)、复位信号RST和背光BL。

除去与访问过程无关的信号RST、BL,则两者的控制信号是极度的一致,区别仅在于SRAM有地址线(A18-A0),而LCD有RS信号线,从作用上看,两者也是一致的,都决定访问数据的位置。

若假定SRAM仅一根地址线A0,则说明数据位置仅有两个,通过A0取0和取1,区分访问的数据到底在哪个地址空间;而LCD的RS取0和取1,也说明有两个存储空间,即ILI9341的寄存器的GRAM。

显然,当把RS理解成一根地址线时,LCD就等效成SRAM了。

RS与地址线A6进行相连,因此通过把地址线中的A6置0可以访问ILI9341的寄存器,而把A6置1则可以访问GRAM。

STM32 FSMC 配置说明

STM32 FSMC 配置说明typedef struct{uint32_t FSMC_Bank;//nor 被分为四块,其中这个参数是说明对那个块编程uint32_t FSMC_DataAddressMux;//地址\数据是否复用uint32_t FSMC_MemoryType;//存储器类型uint32_t FSMC_MemoryDataWidth;//数据总线宽度8 位/16 位uint32_t FSMC_BurstAccessMode;//是否进行成组模式访问uint32_t FSMC_WaitSignalPolarity;//等待信号有效级性uint32_t FSMC_WrapMode;//该位决定控制器是否支持把非对齐的AHB 成组操作分割成2 次线性操作;该位仅在存储器的成组模式下有效。

uint32_tFSMC_WaitSignalActive;//当闪存存储器处于成组传输模式时,NWAIT 信号指示从闪存存储器出来的数据是否有效或是否需要插入等待周期。

该位决定存储器是在等待状态之前的一个时钟周期产生NWAIT 信号,还是在等待状态期间产生NWAIT 信号。

uint32_t FSMC_WriteOperation;//该位指示FSMC 是否允许/ 禁止对存储器的写操作。

uint32_t FSMC_WaitSignal;//当闪存存储器处于成组传输模式时,这一位允许/禁止通过NWAIT 信号插入等待状态。

uint32_tFSMC_ExtendedMode;//该位允许FSMC 使用FSMC_BWTR 寄存器,即允许读和写使用不同的时序。

uint32_t FSMC_WriteBurst;//对于处于成组传输模式的闪存存储器,这一位允许/禁止通过NWAIT 信号插入等待状态。

读操作的同步成组传输协议使能位是FSMC_BCRx 寄存器的BURSTEN 位。

FSMC_NORSRAMTimingInitTypeDef*FSMC_ReadWriteTimingStruct;//读时序配置指针FSMC_NORSRAMTimingInitTypeDef*FSMC_WriteTimingStruct;//写时序配置指针}FSMC_NORSRAMInitTypeDef;typedef struct{uint32_t FSMC_AddressSetupTime;//这些位定义地址的建立时间,适用于SRAM、ROM 和异步总线复用模式的NOR 闪存操作。

FSMC

STM32系列采用一种新型的存储器扩展技术——FSMCFSMC(Flexible Static Memory Controller,可变静态存储控制器)是STM32系列中内部集成256 KB以上FlaSh,后缀为xC、xD和xE的高存储密度微控制器特有的存储控制机制。

之所以称为“可变”,是由于通过对特殊功能寄存器的设置,FSMC能够根据不同的外部存储器类型,发出相应的数据/地址/控制信号类型以匹配信号的速度,从而使得STM32系列微控制器不仅能够应用各种不同类型、不同速度的外部静态存储器,而且能够在不增加外部器件的情况下同时扩展多种不同类型的静态存储器,满足系统设计对存储容量、产品体积以及成本的综合要求。

①支持多种静态存储器类型。

STM32通过FSMC可以与SRAM、ROM、PSRAM、NOR Flash和NANDFlash存储器的引脚直接相连。

②支持丰富的存储操作方法。

FSMC不仅支持多种数据宽度的异步读/写操作,而且支持对NOR/PSRAM/NAND存储器的同步突发访问方式。

③支持同时扩展多种存储器。

FSMC的映射地址空间中,不同的BANK是独立的,可用于扩展不同类型的存储器。

当系统中扩展和使用多个外部存储器时,FSMC会通过总线悬空延迟时间参数的设置,防止各存储器对总线的访问冲突。

④支持更为广泛的存储器型号。

通过对FSMC的时间参数设置,扩大了系统中可用存储器的速度范围,为用户提供了灵活的存储芯片选择空间。

⑤支持代码从FSMC扩展的外部存储器中直接运行,而不需要首先调入内部SRAM。

FSMC起到桥梁作用,既能够进行信号类型的转换,又能够进行信号宽度和时序的调整,屏蔽掉不同存储类型的差异,使之对内核而言没有区别。

根据选用的存储器类型确定扩展使用的映射地址空间。

NOR Flash只能选用BANK1中的4个子BANK。

选定映射子BANK后,即可确定以下2方面内容:①硬件电路中用于选中该存储器的片选线FSMC_NEi(i为子BANK号,i=1,…,4);②FSMC配置中用于配置该外部存储器的特殊功能寄存器号(如表1所列)。

STM32的FSMC理解注释

TFT 液晶和STM32的FSMC 理解注释我们下面所说的都是指TFT 液晶16位数据接口而言,而TFT 的8080时序刚刚和FSMC 的时序可以设计成一样,一定要先明白各自时序(看手册),不然会不明白为什么RS 的操作。

一.TFT 不用FSMC 时候的液晶引脚及时序:首先要明白TFT 液晶的连接线有:RD=读选择线,WR=写选择线,CS=片选,RS=写寄存器和写Sram 选择线,其中前面3条引脚线都是低电平有效,所以一般选择写的时候,RD 要拉高,WR 拉低。

选择读的时候,WR 要拉高,RD 拉低。

所以有时候用51驱动TFT 液晶的时候,只要写功能,不要读功能,就把RD 线留空,但是经过测试这样子有时候会成功驱动,有时候会驱动不了,这时候最好还是把RD 上拉就可以。

二.TFT 用STM 的FSMC 时候的液晶引脚:(时序自动不用管)只要操作TFT 的:步1. Reset :直接拉高即可(不复位不用管)步2.RD:读选择线连接FSMC_NOE (固定)=GPIO.PD4 步3.WR:写选择线连接FSMC_NWE (固定)=GPIO.PD5 步4.CS 片选以选择FSMC 的NOR 块;(选择=GPIO.PD7.PG9.PG10.PG12) 步5.RS 以选择写寄存器和写Sram 选择线(选择=如何一根FSMC 的地址线A[25:0]) 步6.DAT 【15:0】接FSMC_D 【15:0】 (固定) 所以只要关心的是步4和步5。

步4:TFT.CS 和STM32的FSMC 连接引脚选择:首先要明白FSMC 功能要看几遍数据手册的FSMC ,不然会不明白(废话!),简单的说,FSMC 操作TFT 就是在NOR 区,NOR 区的基址是0X60 00 00 00,结束地址是0X6F FF FF FF, 大小是256M ,分成4块,每块64M 。

我们可以选择任何一块就可以,怎么选择呢?根据AHB 总线的HADDR(AHB的地址线,可以先理解为一个寄存器)的第26位27位选择决定,如表1。

基于STM32的FSMC接口驱动TFT彩屏的设计方案

基于STM32的FSMC接口驱动TFT彩屏的设计方案一、背景介绍TFT(Thin Film Transistor)彩屏是一种薄膜晶体管彩色液晶显示屏,具有高分辨率、广视角和真实色彩等特点,广泛应用于消费电子产品和工业设备等领域。

STM32是意法半导体(STMicroelectronics)推出的一系列基于ARM Cortex-M内核的32位微控制器,具有丰富的外设和强大的计算性能。

二、设计方案1.硬件选型选择适配的TFT彩屏模块和STM32系列微控制器,确保彩屏和微控制器之间的电气和通信接口兼容。

在硬件设计中,需要注意考虑TFT彩屏的分辨率、尺寸、显示接口、电源供应和触摸屏等特性。

2.接口连接将TFT彩屏的数据总线连接到STM32微控制器的FSMC(Flexible Static Memory Controller)接口,FSMC接口支持多种外部存储器和显示器设备的数据交互,包括SRAM、NOR Flash和LCD等。

在硬件设计中,需要根据TFT彩屏的接口类型(如RGB接口、SPI接口等)选择合适的引脚进行连接,并参考STM32的技术手册或数据手册配置FSMC接口的参数。

3.驱动程序编写根据TFT彩屏的型号和厂家提供的数据手册,编写合适的驱动程序来实现对TFT彩屏的初始化、配置和数据传输等操作。

驱动程序需要调用STM32的FSMC接口相关的函数来进行数据收发,并通过设置FSMC寄存器来配置时序和控制信号。

在编写驱动程序时,可以参考STM32提供的示例代码和库函数,或者使用第三方开源的驱动程序库。

4.显示数据处理通过使用TFT彩屏的驱动程序,可以实现对图像和文本等数据的显示。

在STM32微控制器中,可以通过使用内部存储器或外部存储器来存储需要显示的数据。

在显示数据处理时,需要根据TFT彩屏的分辨率和颜色配置,将数据转化为对应的像素点或颜色值,并通过驱动程序进行传输和显示。

5.功能扩展在基于STM32的FSMC接口驱动TFT彩屏的设计中,可以进一步扩展功能,如添加触摸屏控制、图形界面设计、动画效果和多任务处理等。

Verilog实现FPGA作为从机与STM32进行SPI协议通信

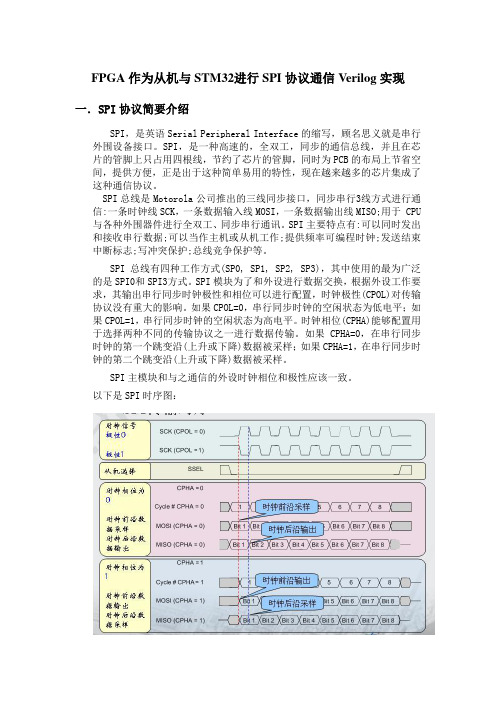

FPGA作为从机与STM32进行SPI协议通信Verilog实现一.SPI协议简要介绍SPI,是英语Serial Peripheral Interface的缩写,顾名思义就是串行外围设备接口。

SPI,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。

SPI总线是Motorola公司推出的三线同步接口,同步串行3线方式进行通信:一条时钟线SCK,一条数据输入线MOSI,一条数据输出线MISO;用于 CPU 与各种外围器件进行全双工、同步串行通讯。

SPI主要特点有:可以同时发出和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志;写冲突保护;总线竞争保护等。

SPI总线有四种工作方式(SP0, SP1, SP2, SP3),其中使用的最为广泛的是SPI0和SPI3方式。

SPI模块为了和外设进行数据交换,根据外设工作要求,其输出串行同步时钟极性和相位可以进行配置,时钟极性(CPOL)对传输协议没有重大的影响。

如果CPOL=0,串行同步时钟的空闲状态为低电平;如果CPOL=1,串行同步时钟的空闲状态为高电平。

时钟相位(CPHA)能够配置用于选择两种不同的传输协议之一进行数据传输。

如果 CPHA=0,在串行同步时钟的第一个跳变沿(上升或下降)数据被采样;如果CPHA=1,在串行同步时钟的第二个跳变沿(上升或下降)数据被采样。

SPI主模块和与之通信的外设时钟相位和极性应该一致。

以下是SPI时序图:主要讲解一下广泛使用的两种方式设置:SPI0方式:CPOL=0,CPHA=0;SCK空闲状态为低电平,第一个跳变沿(上升沿)采样数据,无论对Master还是Slaver都是如此。

SPI3方式:CPOL=1,CPHA=1;SCK空闲状态为高电平,第二个跳变沿(上升沿采样数据,无论对Master还是Slaver都是如此。

STM32通过FSMC读写FPGA

STM32通过FSMC读写FPGA/***********************************************************据此定义如下STM32与FPGA间通信用的寄存器********************************************************** */#define ARM_FPGA_REG0 *((volatile unsigned short *)((u32)0x60000000))#define ARM_FPGA_REG1 *((volatile unsigned short*)( (u32)0x60020000))#define ARM_FPGA_REG2 *((volatile unsigned short*)( (u32)0x60040000))#define ARM_FPGA_REG3 *((volatile unsigned short*)( (u32)0x60060000))#define ARM_FPGA_REG4 *((volatile unsigned short*)( (u32)0x60080000))#define ARM_FPGA_REG5 *((volatile unsigned short *)((u32)0x600a0000))#define ARM_FPGA_REG6 *((volatile unsigned short *)((u32)0x600c0000))#define ARM_FPGA_REG7 *((volatile unsigned short *)((u32)0x600e0000))/* FSMC对应的GPIO选第二功能,100pin的和非100pin的管脚是有差别的 */void FSMC_GPIO_Configuration(void){GPIO_InitTypeDef GPIO_InitStructure;/* SRAM 数据线双向IO PD 和 PE */GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 | GPIO_Pin_1 | GPIO_Pin_8 | GPIO_Pin_9 |GPIO_Pin_10 | GPIO_Pin_14 | GPIO_Pin_15;GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP; //GPIO_Mode_AF_PP是复用第二功能,也即FSMCGPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;GPIO_Init(GPIOD, &GPIO_InitStructure);GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7 | GPIO_Pin_8 | GPIO_Pin_9 | GPIO_Pin_10 |GPIO_Pin_11 | GPIO_Pin_12 | GPIO_Pin_13 | GPIO_Pin_14 |GPIO_Pin_15;GPIO_Init(GPIOE, &GPIO_InitStructure);/* SRAM Address lines configuration PD11 12 13 对应 A16 17 18PE2 3 4 5 6 对应 A23 19 20 21 22 总共8根地址线 */ GPIO_InitStructure.GPIO_Pin = GPIO_Pin_11 |GPIO_Pin_12 | GPIO_Pin_13;GPIO_Init(GPIOD, &GPIO_InitStructure);GPIO_InitStructure.GPIO_Pin = GPIO_Pin_6 | GPIO_Pin_2 | GPIO_Pin_3 |GPIO_Pin_4 | GPIO_Pin_5;GPIO_Init(GPIOE, &GPIO_InitStructure);/* WR and RD configuration */GPIO_InitStructure.GPIO_Pin = GPIO_Pin_4 |GPIO_Pin_5;GPIO_Init(GPIOD, &GPIO_InitStructure);/* NE1 PD7 片选 */GPIO_InitStructure.GPIO_Pin = GPIO_Pin_7;GPIO_Init(GPIOD, &GPIO_InitStructure);/* NBL0, NBL1 configuration 高低字节使能*/// GPIO_InitStructure.GPIO_Pin = GPIO_Pin_0 | GPIO_Pin_1;// GPIO_Init(GPIOE, &GPIO_InitStructure);}/*设置FSMC接口时序,控制对象,以及BANK以及区(一个Bank有4个区(4个片选)) */void FSMC_SRAM_Init(void){FSMC_NORSRAMInitTypeDef FSMC_NORSRAMInitStructure;FSMC_NORSRAMTimingInitTypeDef p;/*-- FSMC Configuration ------------------------------------------------------*/p.FSMC_AddressSetupTime = 0;p.FSMC_AddressHoldTime = 0;p.FSMC_DataSetupTime = 2;p.FSMC_BusTurnAroundDuration = 0;p.FSMC_CLKDivision = 0;p.FSMC_DataLatency = 0;p.FSMC_AccessMode = FSMC_AccessMode_A;FSMC_NORSRAMInitStructure.FSMC_Bank = FSMC_Bank1_NORSRAM1;FSMC_NORSRAMInitStructure.FSMC_DataAddressMux = FSMC_DataAddressMux_Disable;FSMC_NORSRAMInitStructure.FSMC_MemoryType = FSMC_MemoryType_SRAM;FSMC_NORSRAMInitStructure.FSMC_MemoryDataWidth = FSMC_MemoryDataWidth_16b;//FSMC_MemoryDataWidth_ 8b;FSMC_NORSRAMInitStructure.FSMC_BurstAccessMode = FSMC_BurstAccessMode_Disable;FSMC_NORSRAMInitStructure.FSMC_WaitSignalPolarity = FSMC_WaitSignalPolarity_Low;FSMC_NORSRAMInitStructure.FSMC_WrapMode = FSMC_WrapMode_Disable;FSMC_NORSRAMInitStructure.FSMC_WaitSignalActive = FSMC_WaitSignalActive_BeforeWaitState;FSMC_NORSRAMInitStructure.FSMC_WriteOperation = FSMC_WriteOperation_Enable;FSMC_NORSRAMInitStructure.FSMC_WaitSignal = FSMC_WaitSignal_Disable;FSMC_NORSRAMInitStructure.FSMC_ExtendedMode = FSMC_ExtendedMode_Disable;FSMC_NORSRAMInitStructure.FSMC_AsyncWait = FSMC_AsyncWait_Disable;FSMC_NORSRAMInitStructure.FSMC_WriteBurst = FSMC_WriteBurst_Disable;FSMC_NORSRAMInitStructure.FSMC_ReadWriteTimingStruct = &p;FSMC_NORSRAMInitStructure.FSMC_WriteTimingStruct = &p;FSMC_NORSRAMInit(&FSMC_NORSRAMInitStructure);/* Enable FSMC Bank1_SRAM Bank */FSMC_NORSRAMCmd(FSMC_Bank1_NORSRAM1, ENABLE);}/* 另外不要忘了使能FSMC时钟以及对应GPIO的时钟,放在RCC_Configuration()里面了 */RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOC |RCC_APB2Periph_GPIOD | RCC_APB2Periph_GPIOE,ENABLE);RCC_AHBPeriphClockCmd(RCC_AHBPeriph_FSMC, ENABLE);至此STM32配置FSMC就完成了,可以编写测试程序了:void main(void){u32 i = 0;u16 j = 0;RCC_Configuration();NVIC_Configuration();FSMC_GPIO_Configuration();FSMC_SRAM_Init();USART_Initial();//UART1端口配置printf("start test!\r\n");for(j = 0; j < 256; j++){ARM_FPGA_REG2 = j << 8 | j;printf("0x%4x\r\n", ARM_FPGA_REG2);}for(i = 0; i < 65536; i++){ARM_FPGA_REG1 = (u16)i;if(ARM_FPGA_REG1 != i)printf("%d\r\n", ARM_FPGA_REG1);}printf("test over!\r\n");while(1){。

STM32与FPGA进行SPI通信

STM32与FPGA进⾏SPI通信⼀、器件32单⽚机:STM32F407ZGFPGA :EP4CE6E22C8N⼆、通信⽅式STM32作为主机(软件);FPGA作为从机;SPI通信⽅式为1;三、STM32源代码1 #include "delay.h"2 #include "stm32f4xx.h"34 #ifndef __SPI_H5#define __SPI_H67#define SPI1_SCK PBout(2)8#define SPI1_MOSI PBout(3)9#define SPI1_MISO PBin(4)10#define CS PBout(5)1112//CPOL=0,CPHA=013 u8 SOFT_SPI_RW(u8 byte);14//SPI初始化15void SPIInit(void);1617#endifspi.h1 #include "spi.h"2 #include "delay.h"3 #include "stm32f4xx.h"45//CPOL=0,CPHA=06 u8 SOFT_SPI_RW(u8 byte)7 {8 u8 i;9 u8 Temp=0; //接收数据存储10 SPI1_SCK = 0;11 delay_init(168); //初始化延时函数12for(i=0;i<8;i++) // 循环8次13 {14if(byte&0x80) SPI1_MOSI = 1; //若字节最⾼位为1,则输出⾼15else SPI1_MOSI = 0; //若字节最⾼位为0,则输出低16byte <<= 1; //低⼀位移位到最⾼位17 delay_us(1); //延时1us18 SPI1_SCK = 1; //拉低时钟19 Temp <<= 1; //数据左移20if(SPI1_MISO) Temp++; //若从从机接收到⾼电平,数据⾃加⼀21 delay_us(1); //延时1us22 SPI1_SCK = 0; //拉低时钟23 }24return (Temp); //返回数据25 }2627void SPIInit(void)28 {29 GPIO_InitTypeDef GPIO_InitStructure;30 RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_GPIOB,ENABLE);//使能PORTB时钟3132//PB2,PB3,PB5设置33 GPIO_InitStructure.GPIO_Pin = GPIO_Pin_2 | GPIO_Pin_3 | GPIO_Pin_5;34 GPIO_InitStructure.GPIO_Mode = GPIO_Mode_OUT;35 GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;36 GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz;37 GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_UP;38 GPIO_Init(GPIOB,&GPIO_InitStructure);39//PB4设置42 GPIO_InitStructure.GPIO_OType = GPIO_OType_PP;43 GPIO_InitStructure.GPIO_Speed = GPIO_Speed_100MHz;44 GPIO_InitStructure.GPIO_PuPd = GPIO_PuPd_UP;45 GPIO_Init(GPIOB,&GPIO_InitStructure);46 }spi.c四、FPGA源代码1//FPGA作为从设备2 module spi_s(I_clk,I_rst_n,I_data_in,O_data_out,O_tx_done,O_rx_done,I_spi_miso,I_spi_sck,I_spi_cs,O_spi_mosi,sck_posedge,sck_negedge,rxd_flag,txd_flag);3 input I_clk; //全局时钟50MHz4 input I_rst_n; //复位信号,低电平有效5//input I_rx_en; //读(接收)使能信号6//input I_tx_en; //写(发送)使能信号7 input [7:0]I_data_in; //要发送的数据8 output[7:0]O_data_out; //接收到的数据9 output O_tx_done; //发送⼀个数据完毕标志位10 output O_rx_done; //接收⼀个字节完毕标志位1112//四线标准SPI信号定义13 input I_spi_miso; //SPI串⾏输⼊,⽤来接收从机的数据14 input I_spi_sck; //SPI时钟15 input I_spi_cs; //SPI⽚选信号16 output O_spi_mosi; //SPI输出,⽤来给从机发送数据1718 output sck_posedge,sck_negedge;19 output rxd_flag;//接收标志位20 output txd_flag;//发送标志位2122 reg [7:0] O_data_out;23 reg O_tx_done;24 reg O_rx_done;25 reg O_spi_mosi;2627 reg [2:0] R_tx_state;28 reg [2:0] R_rx_state;2930 reg sck_r0,sck_r1;//当前SCK态,之前SCK态31 wire sck_posedge; //SCK上升沿32 wire sck_negedge; //SCK下降沿3334//获取SCK时钟当前态以及之前态35 always @(posedge I_clk,negedge I_rst_n)36 begin37if(!I_rst_n)38 begin39 sck_r0 <= 1'b0;40 sck_r1 <= 1'b0;//⼯作⽅式0,空闲时为低电平41 end42else43 begin44 sck_r0 <= I_spi_sck; //当前SCK态45 sck_r1 <= sck_r0; //之前SCK态46 end47 end4849//捕获SCK时钟上升沿以及下降沿50 assign sck_posedge = (~sck_r0 & sck_r1)? 1'b1:1'b0;//上升沿51 assign sck_negedge = (~sck_r1 & sck_r0)? 1'b1:1'b0;//下降沿5253//发送数据触发54 always @(posedge I_clk,negedge I_rst_n)55 begin56//置位57if(!I_rst_n)58 begin59 R_tx_state <= 3'b0;60 O_spi_mosi <= 1'b0;61 O_tx_done <= 0;62 end63//SCK上跳沿时发送数据(⽅式0)64else if(sck_posedge && !I_spi_cs)65 begin66case(R_tx_state)673'd0://发送第七位68 begin69 O_spi_mosi <= I_data_in[7];70 R_tx_state <= R_tx_state + 1'b1;71 O_tx_done <= 1'b0;75 O_spi_mosi <= I_data_in[6];76 R_tx_state <= R_tx_state + 1'b1;77 O_tx_done <= 1'b0;78 end793'd2://发送第五位80 begin81 O_spi_mosi <= I_data_in[5];82 R_tx_state <= R_tx_state + 1'b1;83 O_tx_done <= 1'b0;84 end853'd3://发送第四位86 begin87 O_spi_mosi <= I_data_in[4];88 R_tx_state <= R_tx_state + 1'b1;89 O_tx_done <= 1'b0;90 end913'd4://发送第三位92 begin93 O_spi_mosi <= I_data_in[3];94 R_tx_state <= R_tx_state + 1'b1;95 O_tx_done <= 1'b0;96 end973'd5://发送第⼆位98 begin99 O_spi_mosi <= I_data_in[2]; 100 R_tx_state <= R_tx_state + 1'b1; 101 O_tx_done <= 1'b0;102 end1033'd6://发送第⼀位104 begin105 O_spi_mosi <= I_data_in[1]; 106 R_tx_state <= R_tx_state + 1'b1; 107 O_tx_done <= 1'b0;108 end1093'd7://发送第零位110 begin111 O_spi_mosi <= I_data_in[0]; 112 R_tx_state <= R_tx_state + 1'b1; 113 O_tx_done <= 1'b1;//发送完毕114 end115default:R_tx_state <= 3'd0;116 endcase117 end118 end119120121122//接收数据触发123 always @(posedge I_clk,negedge I_rst_n) 124 begin125if(!I_rst_n)126 begin127 O_data_out <= 8'b0;128 R_rx_state <= 3'b0;129 O_rx_done <= 1'b0;130 end131else if(sck_negedge && !I_spi_cs)132case(R_rx_state)1333'd0://接收第七位134 begin135 R_rx_state <= R_rx_state + 1'b1; 136 O_rx_done <= 1'b0;137 O_data_out[7] <= I_spi_miso; 138 end1393'd1://接收第六位140 begin141 R_rx_state <= R_rx_state + 1'b1; 142 O_rx_done <= 1'b0;143 O_data_out[6] <= I_spi_miso; 144 end1453'd2://接收第五位146 begin147 R_rx_state <= R_rx_state + 1'b1; 148 O_rx_done <= 1'b0;149 O_data_out[5] <= I_spi_miso; 150 end1513'd3://接收第四位152 begin153 R_rx_state <= R_rx_state + 1'b1; 154 O_rx_done <= 1'b0;155 O_data_out[4] <= I_spi_miso;159 R_rx_state <= R_rx_state + 1'b1;160 O_rx_done <= 1'b0;161 O_data_out[3] <= I_spi_miso;162 end1633'd5://接收第⼆位164 begin165 R_rx_state <= R_rx_state + 1'b1;166 O_rx_done <= 1'b0;167 O_data_out[2] <= I_spi_miso;168 end1693'd6://接收第⼀位170 begin171 R_rx_state <= R_rx_state + 1'b1;172 O_rx_done <= 1'b0;173 O_data_out[1] <= I_spi_miso;174 end1753'd7://接收第零位176 begin177 R_rx_state <= R_rx_state + 1'b1;178 O_rx_done <= 1'b1;//接收完毕179 O_data_out[0] <= I_spi_miso;180 end181default:R_rx_state <= 3'd0;182 endcase183 end184185 reg rxd_flag_r0,rxd_flag_r1;//接收标志位(当前态),接收标志位(之前态)186 always@(posedge I_clk or negedge I_rst_n)187 begin188if(!I_rst_n)189 begin190 rxd_flag_r0 <= 1'b0;191 rxd_flag_r1 <= 1'b0;192 end193else194 begin195 rxd_flag_r0 <= O_rx_done;196 rxd_flag_r1 <= rxd_flag_r0;197 end198 end199//接收标志位200 assign rxd_flag = (~rxd_flag_r1 & rxd_flag_r0)? 1'b1:1'b0;201202 reg txd_flag_r0,txd_flag_r1;//发送标志位(当前态),发送标志位(之前态)203 always@(posedge I_clk or negedge I_rst_n)204 begin205if(!I_rst_n)206 begin207 txd_flag_r0 <= 1'b0;208 txd_flag_r1 <= 1'b0;209 end210else211 begin212 txd_flag_r0 <= O_tx_done;213 txd_flag_r1 <= txd_flag_r0;214 end215 end216//发送标志位217 assign txd_flag = (~txd_flag_r1 & txd_flag_r0)? 1'b1:1'b0;218219220 endmodulespi_s.v1 `timescale 1 ns/ 1 ps2 module spi_s_vlg_tst();3// constants4// general purpose registers5 reg eachvec;6// test vector input registers7 reg I_clk;8 reg [7:0] I_data_in;9 reg I_rst_n;10 reg I_spi_cs;11 reg I_spi_miso;12 reg I_spi_sck;13// wires14 wire [7:0] O_data_out;15 wire O_rx_done;16 wire O_spi_mosi;20 wire sck_posedge;21 wire txd_flag;2223// assign statements (if any)24 spi_s i1 (25// port map - connection between master ports and signals/registers26 .I_clk(I_clk),27 .I_data_in(I_data_in),28 .I_rst_n(I_rst_n),29 .I_spi_cs(I_spi_cs),30 .I_spi_miso(I_spi_miso),31 .I_spi_sck(I_spi_sck),32 .O_data_out(O_data_out),33 .O_rx_done(O_rx_done),34 .O_spi_mosi(O_spi_mosi),35 .O_tx_done(O_tx_done),36 .rxd_flag(rxd_flag),37 .sck_negedge(sck_negedge),38 .sck_posedge(sck_posedge),39 .txd_flag(txd_flag)40 );41 reg [2:0]state;42 initial43 begin44 I_clk = 0;45 I_rst_n = 0;46 I_data_in = 8'h00;47 I_spi_miso = 0;48 I_spi_cs = 1;49 I_spi_sck = 0;50 #10051 I_rst_n = 1;52 I_spi_cs = 0;53 end54 always55 begin56 #10 I_clk = ~I_clk;57 end5859 always60 begin61 #20 I_spi_sck = ~I_spi_sck;62 end6364 always @(posedge I_spi_sck,negedge I_rst_n)65 begin66if(!I_rst_n)67 I_data_in <= 8'h00;68else if(I_data_in == 8'hff)69 begin70 I_data_in <= 8'h00;71 end72else if(txd_flag)73 I_data_in <= I_data_in + 1'b1;74 end75//1110101076 always @(negedge I_spi_sck,negedge I_rst_n)77 begin78if(!I_rst_n)79 state <= 3'b000;80else81case(state)823'd0:83 begin84 state <= state + 1;85 I_spi_miso <= 1'b1;86 end873'd1:88 begin89 state <= state + 1;90 I_spi_miso <= 1'b1;91 end923'd2:93 begin94 state <= state + 1;95 I_spi_miso <= 1'b1;96 end973'd3:98 begin99 state <= state + 1;100 I_spi_miso <= 1'b0;103 begin104 state <= state + 1; 105 I_spi_miso <= 1'b1; 106 end1073'd5:108 begin109 state <= state + 1; 110 I_spi_miso <= 1'b0; 111 end1123'd6:113 begin114 state <= state + 1; 115 I_spi_miso <= 1'b1; 116 end1173'd7:118 begin119 state <= state + 1; 120 I_spi_miso <= 1'b0; 121 end122default:state <= 3'b000; 123 endcase124 end125 endmodulespi_s.vt(测试代码)五、仿真波形图六、参考资料。

STM32与FPGA+之间的FSMC通信

1.引言STM32是ST(意法半导体)公司推出的基于ARM内核Cortex-M3的32位微控制器系列。

Cortex-M3内核是为低功耗和价格敏感的应用而专门设计的,具有突出的能效比和处理速度。

通过采用Thumb-2高密度指令集,Cortex-M3内核降低了系统存储要求,同时快速的中断处理能够满足控制领域的高实时性要求,使基于该内核设计的STM32系列微控制器能够以更优越的性价比,面向更广泛的应用领域。

STM32系列微控制器为用户提供了丰富的选择,可适用于工业控制、智能家电、建筑安防、医疗设备以及消费类电子产品等多方位嵌入式系统设计。

STM32系列采用一种新型的存储器扩展技术——FSMC,在外部存储器扩展方面具有独特的优势,可根据系统的应用需要,方便地进行不同类型大容量静态存储器的扩展。

2.F SMC机制2.1F SMC技术优势①支持多种静态存储器类型。

STM32通过FSMC町以与SRAM、ROM、PSRAM、NOR Flash和NANDFlash存储器的引脚直接相连。

②支持丰富的存储操作方法。

FSMC不仅支持多种数据宽度的异步读/写操作,而且支持对NOR/PSRAM/NAND存储器的同步突发访问方式。

③支持同时扩展多种存储器。

FSMC的映射地址空间中,不同的BANK是独立的,可用于扩展不同类型的存储器。

当系统中扩展和使用多个外部存储器时,FSMC会通过总线悬空延迟时间参数的设置,防止各存储器对总线的访问冲突。

④支持更为广泛的存储器型号。

通过对FSMC的时间参数设置,扩大了系统中可用存储器的速度范围,为用户提供了灵活的存储芯片选择空间。

⑤支持代码从FSMC扩展的外部存储器中直接运行,而不需要首先调入内部SRAM。

2.2FSMC内部结构STM32微控制器之所以能够支持NOR Flash和NAND Flash这两类访问方式完全不同的存储器扩展,是因为FSMC内部实际包括NOR Flash和NAND/PC Card两个控制器,分别支持两种截然不同的存储器访问方式。

基于FPGA与STM32的液晶检测电路设计

基于FPGA与STM32的液晶检测电路设计徐虎【摘要】为了精确检测出不同款式液晶中存在的缺陷,采用FPGA的运行速度快、精度高、抗干扰性强,以及STM32自带存储功能和FSMC双向通信功能的特点,设计了一款基于FPGA与STM32的液晶检测电路。

通过液晶各厂家的实际应用,结果表明,基于FPGA与STM32的液晶检测电路能够准确、方便的实现检测功能,达到预期的设计效果,具有较高的市场价值。

%For the accuracy of detectionof liquid crystal in different styles, taking the advantage of quickness, high precision and strong anti-interference ability from FPGA,and build-in memory function of STM32,as well as the characteristic of bidirectional communication in FSMC, we designed a liquid crystal detection circuit based on FPGA and STM32. Through the practical application, the results show that the circuit for detection based on FPGA and STM32 can accurately, conveniently realize detection function and achieve the desired results,having a high market value.【期刊名称】《电子设计工程》【年(卷),期】2016(024)005【总页数】3页(P87-88,92)【关键词】液晶;FPGA;STM32;FSMC通信【作者】徐虎【作者单位】广州航海学院广东广州 510725【正文语种】中文【中图分类】TN321+.5液晶显示器(LCD)由于其体积小、能耗低、显示效果好等特点,已被广泛应用于我们的生产和生活中。

【转】STM32FSMC总线深入研究

【转】STM32FSMC总线深⼊研究原⽂:由于CPU与FPGA通信的需要,以及对8080总线的熟悉,⾸选采⽤了STM32的FSMC总线,作为⽚间通信接⼝。

FSMC能达到16MHz的写⼊速度,理论上能写20fps的1024*768的图⽚哈哈。

(当然实际上是不可能的,就算是DMA传输,数据源也跟不上,实际上刷模拟的图⽚每秒10fps,刷的很high)当然这不是本篇的要点,这⾥主要研究STM32的FSMC接⼝,将速度提升到极限。

1. FSMC协议分析如下为ILI9325的8080接⼝的协议CS(⽚选信号):低电平⽚选有效,⾼电平失能(默认为⾼:失能)RS(数据寄存器):低电平写寄存器,⾼电平写数据(默认为⾼:写数据)FSMC默认为低。

RD(读信号):低电平有效,上升沿写⼊数据,⾼电平失能(默认为⾼,失能)WR(写信号):低电平有效,上升沿写⼊数据,⾼电平失能(默认为⾼,失能)FSMC写SRAM模式如下:(1)读操作(2)写操作HCLK为系统时钟72MHz综上,分析出FSMC与8080接⼝协议异同点(1)同:CS,RS,RD有效电平都⼀样,单个字节的写⼊与读取时序完全⼀样(2)异:A:8080 默认RS为⾼,⽽FSMC默认RS为低B:8080接⼝协议能保持CS,RS等有效,连续写数据,⽽FSMC以此只能输出⼀个数据。

C:8080协议没有地址线,⽽FSMC还有地址线,这使得数据输出不连续。

2. FSMC时序研究下图为FSMC写命令与数据的时序图,从中根据上图可以分析出FSMC可以实现16M的数据写⼊。

FSMC的信号线翻转⾮常快,这使得IC或者FPGA时序设计上得⾮常严谨。

FSMC最⼤实现了72MHz(66.7到100MHz之间,实际为72MHz,HCLK)的翻转速度,这要求外部器件⽀持那么⾼的速率。

寄存器配置(寄存器+数据)连续数据写⼊(0xBB:写数据开始),命令后,RS默认拉低(FSMC和标准不⼀样的地⽅)数据建⽴很快写数据,然后默认RS拉低整体的时序可模拟为:task task_writecmd;input [15:0] cmd;beginmcu_cs = 0;mcu_rs = 0;mcu_data = cmd;#20;mcu_we = 0;#20;mcu_we = 1;#15;mcu_rs = 1;mcu_cs = 1;#20;endendtasktask task_writedata;input [15:0] data;beginmcu_cs = 0;mcu_rs = 1;mcu_data = data;#20;mcu_we = 0;#20;mcu_we = 1;#15;mcu_rs = 1;mcu_cs = 1;#20;endendtask3. FSMC接⼝初始化根据⼿册,相关参数如下表所⽰。

STM32单片机FSMC的使用解析

STM32单片机FSMC的使用解析STM32单片机FSMC的使用解析在做项目的过程中遇到了这个问题,感觉文章写得不错,共享给对FSMC的使用怀有疑惑的同伴们!LCD有如下控制线:CS:Chip Select片选,低电平有效RS:Register Select寄存器选择WR:Write写信号,低电平有效RD:Read读信号,低电平有效RESET:重启信号,低电平有效DB0-DB15:数据线假如这些线,全部用普通IO口控制。

根据LCD控制芯片手册(大部分控制芯片时序差不多):如果情况如下:DB0-DB15的IO全部为1(表示数据0xff),也可以为其他任意值,这里以0xff为例。

CS为0(表示选上芯片,CS拉低时,芯片对传入的数据才会有效)RS为1(表示DB0-15上传递的是要被写到寄存器的值),如果为0,表示传递的是数据。

WR为0,RD为1(表示是写动作),反过来就是读动作。

RESET一直为高,如果RESET为低,会导致芯片重启。

这种情况,会导致一个值0xff被传入芯片,被LCD控制芯片当作写寄存器值去解析。

LCD 控制芯片收到DB0-15上的值之后,根据其他控制线的情况,它得出结论,这个0xff是用来设置寄存器的。

一般情况下,LCD控制芯片会把传入的寄存器值的高8位当做寄存器地址(因为芯片内部肯定不止一个寄存器),低8位当做真正的要赋给对应寄存器值。

这样,就完成了一个写LCD控制芯片内部寄存器的时序。

如果上述情况不变,只将RS置低,那么得到的情况如下:LCD控制芯片会把DB0-15上的数据当做单纯的数据值来处理。

那么假如LCD处在画图状态,这个传入的值0xff,就。

27.STM32的FSMC的特性及架构(2)

27.STM32的FSMC的特性及架构(2)

利用STM32的FSMC外设来管理扩展SRAM

Flexible Static Memory Controller 灵活的静态存储控制器

一。

FSMC介绍

控制SRAM时使用NOR存储控制器

一般的外设都挂在APB1或APB2总线上,FSMC直接挂在AHB 总线上。

1. 通讯引脚

与SRAM相对应的引脚:

当访问STM32不同的空间的时候NE1/2/3/4会根据空间的不同输出相应引脚的低电平,因此可以认为是输出不同的使能信号。

2. 存储器控制器

3. 时钟控制逻辑

二。

FSMC的地址映射

每一个BANK1内部的一个小块地址区域都有64M的空间。

当访问STM32这些空间的时候就会自动映射到SRAM中的地址空间。

三。

FSMC控制SRAM的时序

ADDSET来配置从发出地址信号到发出读使能信号的时长。

把扩展模式使能位EXMOD置1,允许读和写使用不同的时序。

STM32的FSMC灵活静态存储器控制器

STM32的FSMC灵活静态存储器控制器FSMC(Flexihie Static Memory Controller)模块只适用于大容量产品。

FSMC模块能够与同步或异步存储器和16位PC存储器卡接口,主要将AHB传输信号转换到适当的外部设备协议,满足访问外部设备的时序要求。

存储器接口包括:①SRAM静态随机存储器②ROM只读存储器③NOR闪存④PSRAM(4个存储块)⑤两个NAND闪存块⑥16位PC卡STM32之所以能够支持NOR FLASH和NAND FLASH两类访问方式完全不同的存储器扩展,是因为FSMC内部实际包括NOR FLASH和NAND / PC Card两个控制器,分别支持两种截然不同的存储器访问方式。

在STM32内部,FSMC的一端通过内部高速总线AHB连接到内核Cortex-M3,另一端则是面向扩展器的外部总线。

内核对外部存储器访问信号发送到AHB总线后,经FSMC转换为符合外部存储器通信规约的信号,送到外部存储器相应的引脚,实现数据交互。

FSMC起着桥梁作用,既能进行信号类型的转换,又能进行信号宽度和时序的调整,屏蔽掉不同存储类型的差异,使之对内核而言没有区别。

FSMC模块框图如下:存储块外设地址映射(具体说明请看数据手册,此处只用图表形式简单表示):下表为NOR/PSRAM存储块选择:三个存储块可用于NAND或PC:对于NAND闪存,空间可在低256K字节部分划分为三个区:时序参数:FSMC通过使用可编程的存储器时序参数寄存器,拓展了可选用的外部存储器的速度范围。

FSMC的NOR FLASH控制器支持同步和异步突发两种访问方式。

选用同步突发访问方式时,FSMC将系统时钟HCLK分频后,发送给外部存储器作为同步时钟信号FSMC_CLK。

此时需要设置的时间参数有两个:CLK的分频系数和访问中获得第1个数据所需要的等待延迟(DATLAT)。

选用异步突发访问方式时,FSMC主要设置3个时间参数:地址建立时间(ADDSET),数据建立时间(DATAST)和地址保持时间(ADDHLD)。

基于STM32单片机FSMC接口驱动LCD的配置与分析

基于STM32单片机FSMC接口驱动LCD的配置与分析STM32单片机的FSMC(Flexible Static Memory Controller)接口是一种灵活的静态存储器控制器,可以用于连接外部存储器设备,如LCD显示屏。

本文将对基于STM32单片机FSMC接口驱动LCD的配置与分析进行详细介绍。

首先,我们需要了解FSMC接口的基本原理和功能。

FSMC接口是一种高性能、低功耗的外部总线接口,可以连接到SRAM、PSRAM、NOR Flash、NAND Flash、LCD显示屏等外部存储器设备。

FSMC接口提供了多种数据传输模式(如并行、串行)和多种数据总线宽度选择,以满足不同应用的需求。

要实现FSMC接口驱动LCD,首先需要配置FSMC接口的相关寄存器。

在STM32单片机中,FSMC的配置主要包括以下几个方面:1.时序配置:通过设置FSMC_RCC和FSMC_BTR寄存器来定义访问存储器的时序。

时序配置非常重要,需要根据外部存储器的时序规格进行调整,以确保数据的正确传输。

2.地址配置:通过设置FSMC_BANK1或FSMC_BANK2寄存器来定义存储器的基地址和各种地址范围。

3.数据总线配置:根据外部存储器的数据宽度,设置FSMC_BCR和FSMC_BWTR寄存器来选择数据总线宽度(比特数)。

4.控制信号配置:通过设置FSMC_BCR、FSMC_BTR和FSMC_BWTR寄存器来配置控制信号,如写使能信号、读使能信号、片选信号等。

配置完成后,就可以使用FSMC接口进行数据的读写操作。

读取操作可以通过读取FSMC_BANK1或FSMC_BANK2的数据寄存器来实现。

写入操作可以通过写入FSMC_BANK1或FSMC_BANK2的数据寄存器来实现。

对于LCD显示屏的驱动,可以通过FSMC接口的并行模式来实现。

在并行模式下,数据总线的宽度由FSMC_BCR和FSMC_BWTR寄存器的设置决定,可以通过并行总线同时传输多个像素数据和控制信号,从而提高数据传输速度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.引言STM32是ST(意法半导体)公司推出的基于ARM内核Cortex-M3的32位微控制器系列。

Cortex-M3内核是为低功耗和价格敏感的应用而专门设计的,具有突出的能效比和处理速度。

通过采用Thumb-2高密度指令集,Cortex-M3内核降低了系统存储要求,同时快速的中断处理能够满足控制领域的高实时性要求,使基于该内核设计的STM32系列微控制器能够以更优越的性价比,面向更广泛的应用领域。

STM32系列微控制器为用户提供了丰富的选择,可适用于工业控制、智能家电、建筑安防、医疗设备以及消费类电子产品等多方位嵌入式系统设计。

STM32系列采用一种新型的存储器扩展技术——FSMC,在外部存储器扩展方面具有独特的优势,可根据系统的应用需要,方便地进行不同类型大容量静态存储器的扩展。

2.F SMC机制2.1F SMC技术优势①支持多种静态存储器类型。

STM32通过FSMC町以与SRAM、ROM、PSRAM、NOR Flash和NANDFlash存储器的引脚直接相连。

②支持丰富的存储操作方法。

FSMC不仅支持多种数据宽度的异步读/写操作,而且支持对NOR/PSRAM/NAND存储器的同步突发访问方式。

③支持同时扩展多种存储器。

FSMC的映射地址空间中,不同的BANK是独立的,可用于扩展不同类型的存储器。

当系统中扩展和使用多个外部存储器时,FSMC会通过总线悬空延迟时间参数的设置,防止各存储器对总线的访问冲突。

④支持更为广泛的存储器型号。

通过对FSMC的时间参数设置,扩大了系统中可用存储器的速度范围,为用户提供了灵活的存储芯片选择空间。

⑤支持代码从FSMC扩展的外部存储器中直接运行,而不需要首先调入内部SRAM。

2.2FSMC内部结构STM32微控制器之所以能够支持NOR Flash和NAND Flash这两类访问方式完全不同的存储器扩展,是因为FSMC内部实际包括NOR Flash和NAND/PC Card两个控制器,分别支持两种截然不同的存储器访问方式。

在STM32内部,FSMC的一端通过内部高速总线AHB连接到内核Cortex-M3,另一端则是面向扩展存储器的外部总线。

内核对外部存储器的访问信号发送到AHB总线后,经过FSMC转换为符合外部存储器通信规约的信号,送到外部存储器的相应引脚,实现内核与外部存储器之间的数据交互。

FSMC起到桥梁作用,既能够进行信号类型的转换,又能够进行信号宽度和时序的调整,屏蔽掉不同存储类型的差异,使之对内核而言没有区别。

2.3FSMC映射地址空间FSMC管理1 GB的映射地址空间。

该空间划分为4个大小为256 MB的BANK,每个BANK 又划分为4个64 MB的子BANK,如表1所列。

FSMC的2个控制器管理的映射地址空间不同。

NOR Flash控制器管理第1个BANK,NAND/PC Card控制器管理第2~4个BANK。

由于两个控制器管理的存储器类型不同,扩展时应根据选用的存储设备类型确定其映射位置。

其中,BANK1的4个子BANK拥有独立的片选线和控制寄存器,可分别扩展一个独立的存储设备,而BANK2~BANK4只有一组控制寄存器。

3.F SMC扩展外部SRAM配置在STM32 与FPGA 进行通信的时候,FPGA其实可以看做STM32外部的SRAM,因此相应的配置可以参考对外部SRAM的配置。

SRAM/ROM、NOR Flash和PSRAM类型的外部存储器都是由FSMC的NOR Flash控制器管理的,扩展方法基本相同,其中NOR Flash最为复杂。

通过FSMC扩展外部存储器时,除了传统存储器扩展所需要的硬件电路外,还需要进行FSMC初始化配置。

FSMC提供大量、细致的可编程参数,以便能够灵活地进行各种不同类型、不同速度的存储器扩展。

外部存储器能否正常工作的关键在于:用户能否根据选用的存储器型号,对配置寄存器进行合理的初始化配置3.1地址映射空间3.2读写时序控制3.3配置存储器基本特征通过对FSMC特殊功能寄存器FSMC_BCRi(i为子BANK号,i=1,…,4)中对应控制位的设置,FSMC根据不同存储器特征可灵活地进行工作方式和信号的调整。

根据选用的存储器芯片确定需要配置的存储器特征,主要包括以下方面:①存储器类型(MTYPE)是SRAM/ROM、PSRAM,还是NOR FlaSh;②存储芯片的地址和数据引脚是否复用(MUXEN),FSMC可以直接与AD0~AD15复用的存储器相连,不需要增加外部器件;③存储芯片的数据线宽度(MWID),FSMC支持8位/16位两种外部数据总线宽度;④对于NOR Flash(PSRAM),是否采用同步突发访问方式(B URSTEN);⑤对于NOR Flash(PSRAM),NWAIT信号的特性说明(WAITEN、WAITCFG、WAITPOL);⑥对于该存储芯片的读/写操作,是否采用相同的时序参数来确定时序关系(EXTMOD)。

3.4配置存储器时序参数FSMC通过使用可编程的存储器时序参数寄存器,拓宽了可选用的外部存储器的速度范围。

FSMC的SRAM控制器支持同步和异步突发两种访问方式。

选用同步突发访问方式时,FSMC将HCLK(系统时钟)分频后,发送给外部存储器作为同步时钟信号FSMC_CLK。

此时需要的设置的时间参数有2个:①HCLK与FSMC_CLK的分频系数(CLKDIV),可以为2~16分频;②同步突发访问中获得第1个数据所需要的等待延迟(DATLAT)。

对于异步突发访问方式,FSMC主要设置3个时间参数:地址建立时间(ADDSET)、数据建立时间(DATAST)和地址保持时间(ADDHLD)。

FSMC综合了SRAM/ROM、PSRAM和NOR Flash产品的信号特点,定义了4种不同的异步时序模型。

选用不同的时序模型时,需要设置不同的时序参数,如表2所列。

在实际扩展时,根据选用存储器的特征确定时序模型,从而确定各时间参数与存储器读/写周期参数指标之间的计算关系;利用该计算关系和存储芯片数据手册中给定的参数指标,可计算出FSMC所需要的各时间参数,从而对时间参数寄存器进行合理的配置。

4.S TM32扩展外部SRAM实例4.1难点解析4.1.1 数据传输自动化第一个角度理解 STM32 有FSMC(其实其他芯片基本都有类似的总线功能),FSMC 的好处就是你一旦设置好之后,WR(写)、RD(读)、DB0-DB15 这些控制线和数据线,都是FSMC 自动控制的。

打个比方,当你在程序中写到:*(volatile unsigned short int *)(0x60000000)=val;那么FSMC 就会自动执行一个写的操作,其对应的主控芯片的WE、RD 这些脚,就会呈现出写的时序出来(即WE=0,RD=1),数据val 的值也会通过DB0-15 自动呈现出来(即FSMC-D0:FSMC-D15=val )。

地址0x60000000 会被呈现在数据线上(即A0-A25=0,地址线的对应最麻烦,要根据具体情况来。

4.1.2 硬件连接硬件平台:(STM32F103VC + EP3C5E144C8N)将图中的IS61WV512BLL 改为FPGA 对应的接口即,可按照模式A-SRAM/PSRAM进行连接那么在硬件上面,我们需要做的,仅仅是MCU 和LCD 控制芯片的连接关系:WE-WR,均为低电平有效RD-RD,均为低电平有效FSMC-D0-15 接LCD DB0-15FSMC_NE1--CS 接PD7连接好之后,读写时序都会被FSMC 自动完成。

但是还有一个很关键的问题,就是RS 没有接因为在FSMC 里面,根本就没有对应RS。

怎么办呢?这个时候,有一个好方法,就是用某一根地址线来接RS。

比如我们选择了A16 这根地址线来接,那么当我们要写寄存器(备注:此处应为数据)的时候,我们需要RS,也就是A16(RS 为高)置高。

软件中怎么做呢?也就是将FSMC 要写的地址改成0x60010000,如下:*(volatile unsigned short int *)(0x60010000)=val;这个时候,A16 在执行其他FSMC 的同时会被拉高,因为A0-A18 要呈现出地0x60010000。

0x60010000 里面的Bit17=1,就会导致A16 为1。

当要读数据(备注:此处为寄存器)时,地址由0x60010000 改为了0x60000000,这个时候A16 就为0了。

RS 问题:RS 为0 表示;读写寄存器;RS 为1,读写数据RAM;4.2应用STM32固件对FSMC进行初始化配置ST公司为用户开发提供了完整、高效的工具和固件库,其中使用C语言编写的固件库提供了覆盖所有标准外设的函数,使用户无需使用汇编操作外设特性,从而提高了程序的可读性和易维护性。

STM32固件库中提供的FSMC的SRAM控制器操作固件,主要包括1个数据结构和3个函数FSMC_NORSRAMInitStructure (调用库函数)RCC_Configuration(); (时钟选择)NVIC_Configuration(); (中断优先级)FSMC_GPIO_Configuration(); (连接IO口初始化)FSMC_SRAM_Init(); (FMSC配置)USART_Initial(); (UART1端口配置)4.2其他人调试遇到问题点(摘录)项目中需要使用STM32和FPGA通信,使用的是地址线和数据线,在FPGA中根据STM32的读写模式A的时序完成写入和读取。

之前的PCB设计中只使用了8跟数据线和8根地址线,调试过程中没有发现什么问题,在现在的PCB中使用了8根地址线和16根数据线,数据宽度也改成了16位,刚开始是读取数据不正确,后来发现了问题,STM32在16位数据宽度下有个内外地址映射的问题,只需要把FPGA中的设定的地址乘以2在STM32中访问就可以了,但是在写操作的时候会出现写当前地址的时候把后面的地址写成0的情况,比如说我给FPGA中定义的偏移地址0x01写一个16位数据,按照地址映射,在STM32中我把地址写入0x02,。

实际测试发现这个地址上的数据是对的,但是FPGA中0x02地址上的数据也变成了00。

块1存储区被划分为4个NOR/PSRAM区,这四个区在内部地址上是连续排列的。

但是实际上每个区共用的是同一组地址线与数据线,因此需要有内外的一个地址映射,因此在STM32中实际上有两个地址,一个是在内部访问的地址,另外一个是实际地址线输出的地址。

HADDR[27:0]对应的是需要转换到外部存储器的内部AHB地址线,其HADDR[27:26]位用于选择四个存储块之一。