计算机组成原理(3.5组合逻辑控制器设计)

计算机组成原理(3.5组合逻辑控制器设计)

哈尔滨工程大学计算机科学与技术学院 姚爱红

7

2)时钟周期数:

一个工作周期中的时钟数可变。 每个工作周期第一拍T=0,

用计数器T控制节拍数 每开始一个新节拍T计数, 工作周期结束时T清0。

将计数值译码,可产生节拍电位。

哈尔滨工程大学计算机科学与技术学院 姚爱红

31

2.优缺点

● 产生微命令的速度较快。 ● 设计不规整,设计效率较低;

● 不易修改、扩展指令系统功能。

3.应用场合

用于高速计算机,或小规模计算机。

哈尔滨工程大学计算机科学与技术学院 姚爱红

32

DMAT

<-DMA请求

DACK 1->DMAT

与系统总线断开 1->FT

FT0 恢复原程序执行

哈尔滨工程大学计算机科学与技术学院 姚爱红

28

(9)启动与复位

1)上电 2)按复位键

哈尔滨工程大学计算机科学与技术学院 姚爱红

29

3.5.3 微命令的综合与产生

综合化简产生微命令的条件,形成逻辑式,用 组合逻辑电路实现; 执行指令时,由组合逻辑电路(微命令发生器) 在相应时间发出所需微命令,控制有关操作。

3)目的周期DT

按寻址方式(非R寻址)形成目的地址,或从M取出

目的操作数,暂存于D。

哈尔滨工程大学计算机科学与技术学院 姚爱红

5

(1)工作周期(续)

4)执行周期ET

按操作码完成相应操作(传送、运算、取转移地址送入PC、 返回地址压栈保存);后续指令地址送入MAR。

5)中断周期IT

IT指CPU响应中断请求后,到执行中断服务程序前。

十六位体系结构计算机组成原理

十六位体系结构计算机组成原理

十六位体系结构计算机组成原理是指计算机的硬件和软件组成原理,可以分为以下几个部分:

1.中央处理器(Central Processing Unit, CPU):负责执行计算机指令和进行数据处理。

CPU包括指令寄存器、程序计数器、算术逻辑单元(ALU)和寄存器等。

2.存储器:存储器包括主存储器和辅助存储器。

主存储器用于存储正在运行的程序和数据,可分为RAM和ROM。

辅助存储器用于长期存储程序和数据,如硬盘、光盘等。

3.输入输出设备:用于与外部设备进行数据交互,如键盘、鼠标、打印机、显示器等。

4.总线(Bus):计算机内各个部件之间传送数据和控制信息的通道。

总线分为数据总线、地址总线和控制总线。

5.指令系统:计算机的指令系统决定了计算机的操作特性和功能。

按照十六位体系结构,指令由16位表示,可以包括逻辑运算、算术运算、存储和转移等操作。

6.中断系统:用于处理紧急情况和异步事件,如异常中断、硬件中断和软件中断等。

7.时钟系统:用于同步计算机内各个部件的工作节奏和时序,提供时钟脉冲。

8.控制单元(Control Unit):负责控制计算机的操作,根据指令操作码的不同,控制单元产生特定的控制信号和时序信号,控制各个部件的工作。

9.运算器(アrithmetic and Logic Unit, ALU):负责进行算术运算和逻辑运算,包括加法、减法、乘法、除法和与、或、非、异或等逻辑运算。

以上是十六位体系结构计算机组成原理的基本内容,具体实施中可能会有一些差异。

计算机组成原理教案

计算机组成原理教案一、概述计算机组成原理是计算机科学与技术专业的一门基础课程,主要介绍计算机硬件系统的原理和结构。

本节课程将系统讲解计算机组成原理的相关知识,包括计算机系统的层次结构、指令系统、数据表示、计算机运算、控制单元、存储器等内容。

二、计算机系统的层次结构1. 计算机系统的五大组成部分计算机系统由五大组成部分构成,包括输入设备、输出设备、运算器、控制器和存储器。

其中,输入设备用于接收外部信息,输出设备用于显示处理结果,运算器执行程序运算,控制器控制程序执行,存储器存储数据和程序。

2. 计算机系统的层次结构计算机系统的层次结构分为硬件层和软件层,硬件层包括处理器、存储器、输入输出设备等;软件层包括系统软件和应用软件。

硬件层和软件层相互配合,共同完成计算机系统的功能。

三、指令系统1. 指令系统的基本概念指令系统是计算机执行程序的基本单位,包括指令集合、地址寻址方式、指令格式等。

指令集合是计算机可以执行的指令的集合,地址寻址方式是指令中操作数的寻址方式,指令格式定义了指令的组成形式。

2. 指令执行过程指令的执行过程包括取指、分析指令、执行指令和结果存储等步骤。

取指是从存储器中读取指令,分析指令是对指令进行解码,执行指令是根据指令操作码执行相应操作,结果存储是将执行结果存储到指定位置。

四、数据表示1. 数字系统数字系统是计算机数据的表示方式,常用的数字系统包括二进制、八进制、十进制和十六进制等。

在计算机系统中,二进制是最基本的数据表示方式。

2. 数据表示格式数据在计算机中以位、字节、字等单位来表示,位是最小的数据单元,字节由8位组成,字由若干字节构成。

在计算机中,数据的表示格式包括无符号数表示和有符号数表示。

五、计算机运算1. 计算机的算术逻辑单元计算机的算术逻辑单元(ALU)是计算机执行算术和逻辑运算的核心组件,包括加法、减法、与、或、非等运算。

ALU通过控制单元的指令执行相应的运算操作。

2. 运算指令的执行运算指令包括算术运算指令和逻辑运算指令,算术运算指令用于执行加减乘除等算术运算,逻辑运算指令用于执行与或非等逻辑运算。

计算机组成原理实验-组合逻辑设计CU控制单元

组合逻辑设计CU控制单元--计算机组成原理实验报告一、实验目的:深入了解控制单元的执行过程和节拍分配,学会自己分析设计机器指令的微操作指令,通过VHDL设计出相应的控制单元CU,并完成相应的机器指令操作。

二、实验原理:1.根据控制单元的外特性,指令的操作码决定控制单元发出不同的控制信号。

2.以时钟为基数脉冲,通过一个计数器,有称节拍发生器,便可产生一个与时钟周期等宽的节拍序列。

3.微操作的节拍安排遵循的规则4.微指令操作时间表三、实验步骤:1.列出微操作命令的操作时间表,指令一共10条,FE,IND,EX为CPU工作周期标志,I为间指标志,若I=1,则进入间指周期。

在执行周期的T2时刻,CPU要向所有的中断源发出中断查询信号,若检测到有中断请求并且满足响应条件,则INT触发器置1,标志进入中断周期。

2.写出微操作命令的最简逻辑表达式。

根据位操作命令操作时间表可列出每一个微操作命令的初始逻辑表达式,经化简,整理便可获得能用现成电路实现的微操作命令逻辑表达式。

3.画出微操作命令的逻辑图。

对应每一个微操作命令的逻辑表达式都可画出一个逻辑图。

4.通过以上几条进行相应的VHDL代码编写,执行结果如下。

四、实验结果:通过一个4位二进制数为IR制定指令的标号:根据写出的微操作命令的最简逻辑表达式编写VHDL代码:波形图展示:Ir(指令号),m(工作周期),t(节拍),i(间指标志),a0(负标记),c(微指令执行标志,1代表相应微指令执行)。

指令1展示:STP指令上图为三个工作周期,其中每个工作周期分为3个节拍,最后一行是用到的微操作命令指示。

指令2展示:上图为三个工作周期,其中每个工作周期分为3个节拍,最后一行是用到的微操作命令指示。

五、结论与总结:通过自主着手设计控制单元CU,我对控制单元执行过程产生了更加深入的理解。

将每一条机器指令通过分析设计,转化成CU 可执行的微指令操作。

其间,用到了数字逻辑的化简逻辑表达式,复习了化简得过程。

计算机组成原理实验报告

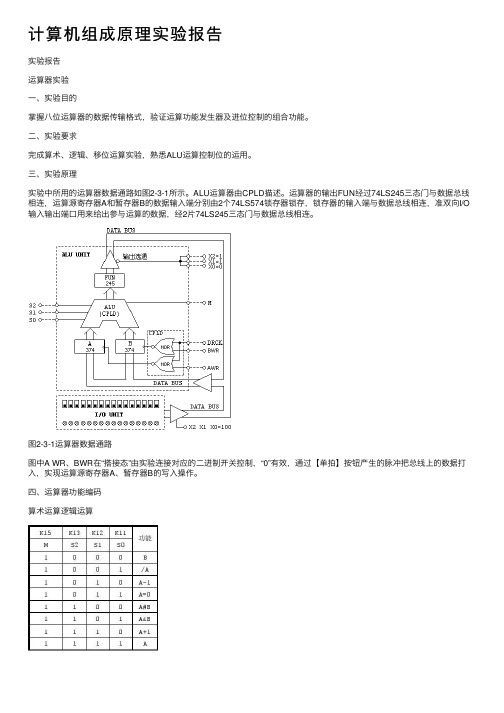

计算机组成原理实验报告实验报告运算器实验⼀、实验⽬的掌握⼋位运算器的数据传输格式,验证运算功能发⽣器及进位控制的组合功能。

⼆、实验要求完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运⽤。

三、实验原理实验中所⽤的运算器数据通路如图2-3-1所⽰。

ALU运算器由CPLD描述。

运算器的输出FUN经过74LS245三态门与数据总线相连,运算源寄存器A和暂存器B的数据输⼊端分别由2个74LS574锁存器锁存,锁存器的输⼊端与数据总线相连,准双向I/O 输⼊输出端⼝⽤来给出参与运算的数据,经2⽚74LS245三态门与数据总线相连。

图2-3-1运算器数据通路图中A WR、BWR在“搭接态”由实验连接对应的⼆进制开关控制,“0”有效,通过【单拍】按钮产⽣的脉冲把总线上的数据打⼊,实现运算源寄存器A、暂存器B的写⼊操作。

四、运算器功能编码算术运算逻辑运算K23~K0置“1”,灭M23~M0控位显⽰灯。

然后按下表要求“搭接”部件控制路。

表2.3.2 运算实验电路搭接表算术运算1.运算源寄存器写流程通过I/O单元“S7~S0”开关向累加器A和暂存器B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K18=K17=“1”,按下流程分别读A、B。

3.加法与减法运算令M S2 S1 S0(K15 K13~K11=0100),为算术加,FUN及总线单元显⽰A+B的结果令M S2 S1 S0(K15 K13~K11=0101),为算术减,FUN及总线单元显⽰A-B的结果。

逻辑运算1.运算源寄存器写流程通过“I/O输⼊输出单元”开关向寄存器A和B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K17= K18=1,按下流程分别读A、B。

①若运算控制位设为(M S2 S1 S0=1111)则F=A,即A内容送到数据总线。

②若运算控制位设为(M S2 S1 S0=1000)则F=B,即B内容送到数据总线。

组合逻辑控制原理

组合逻辑控制原理

组合逻辑控制原理,是指利用逻辑门(包括与门、或门、非门等)来实现逻辑运算和逻辑函数的一种电路设计方法。

它将多个逻辑门按照一定的组合方式连接在一起,以实现复杂的逻辑功能。

在组合逻辑控制原理中,逻辑门的输入和输出只受当前输入信号的影响,与过去的输入信号无关。

这种控制方式可以通过真值表、卡诺图等方法进行逻辑函数的化简和分析,从而设计出所需的电路。

组合逻辑控制原理的主要特点是无记忆性和无反馈性。

无记忆性是指输出仅与当前输入有关,无法通过当前的输出来控制过去的输入;无反馈性是指输出不会作为输入再次输入到逻辑门中,避免了回路的产生。

组合逻辑控制原理的应用非常广泛,常见于各类数字电路、计算机设计、自动化控制、数字信号处理等领域。

通过合理设计和组合不同的逻辑门,可以实现各种逻辑运算、逻辑函数和逻辑操作,满足不同应用需求。

总之,组合逻辑控制原理是一种利用逻辑门进行逻辑运算和逻辑函数设计的方法,通过组合逻辑门的输入和输出关系,实现复杂的逻辑功能。

它具有无记忆性和无反馈性的特点,被广泛应用于各种电子领域。

计算机组成原理CPU设计实验报告

计算机组成原理CPU设计实验报告课程设计题目:16位CPU设计学院: 信息学院班级:电子A班学号:1115102015姓名:方茹1目录1 实验方法 ..................................................................... . (4)2 总体说明 ..................................................................... ................................................. 5 2.1指令系统: .................................................................... .......................... 5 2.1.1指令格式分类(按指令字长和操作数不同): ...................................................... 5 2.1.2具体指令汇总表: .................................................................... .......................... 6 2.1.3相关指令流程图: .................................................................... .......................... 6 2.1.4指令数据通路的构建: .................................................................... ................... 8 2.1.5指令的分组及节拍: .................................................................... ..................... 12 2.1.6指令执行状态图:(见下页)..................................................................... ........... 13 2.1.7具体微指令: .................................................................... ............................... 13 2.2 系统整体介绍 ..................................................................... .................. 16 2.2.1系统基本模块划分 ..................................................................... ....................... 16 2.2.2总体结构图:(见下页)..................................................................... (17)3 CPU的控制逻辑与具体数据通道设计 ..................................................................... ......18 3.1取指令逻辑的设计 ..................................................................... .. (19)3.1.1指令地址的保存 ..................................................................... (19)3.1.2指令存储器 ..................................................................... .................................. 20 3.1.3下一条指令地址的计算 ..................................................................... ................ 20 3.2指令译码逻辑的设计...................................................................... ...................... 21 3.3指令执行逻辑的设计...................................................................... ...................... 22 3.4存储器访问逻辑的设计 ..................................................................... ................... 23 3.5结果写回逻辑的设计...................................................................... ...................... 24 3.6单周期CPU的总成...................................................................... (25)4各部分说明 ..................................................................... .............................................26 4.1ALU .................................................................................................................... 26 4.2数据选择器BUS_MUX ................................................................ ........................ 28 4.3器件T1 ..................................................................... .......................................... 30 4.4标志寄存器FLAG_REG ............................................................... ........................ 31 4.5T2: .................................................................... ................................................ 33 4.6程序计数器PC ..................................................................... ............................... 33 4.7地址寄存器AR和指令寄存器IR: .................................................................... .. 34 4.8寄存器、寄存器组和寄存器的选择.......................................................................36 4.9一位控制信号/WR .................................................................... ........................... 37 4.10 节拍发生器 ..................................................................... .................................. 37 4.11控制逻辑 ..................................................................... ...................................... 39 4.12T3...................................................................... ................................................ 42 4.13REG_OUT ......................................................................................................... 43 4.14存储器 ..................................................................... .......................................... 44 4.15总线选择器 ..................................................................... .. (45)24.16REG_TEST ............................................................... .. (46)5附录: .................................................................... .. (47)附录A:组员分工: .................................................................... .. (47)附录B:组员设计总结: .................................................................... . (47)31 实验方法实验要完成的工作主要包括:指令系统的设计,FPGA-CPU的整体结构设计及其细化,逻辑设计的具体实现(VHDL语言程序的编写),软件模拟,以及硬件调试。

计算机组成原理讲义

计算机组成原理讲义计算机组成原理是一门研究计算机硬件和软件协同工作的学科。

它研究计算机系统的组成、结构、工作原理和设计方法,涉及到计算机的各个层次、各个组成部分和各种操作。

计算机组成原理作为计算机科学和计算机工程的基础课程,对于理解计算机的工作原理和提高计算机系统设计和性能优化具有重要意义。

首先,计算机组成原理涵盖了计算机的硬件组成。

计算机的硬件部分主要包括中央处理器(CPU)、存储器、输入输出设备和总线等。

中央处理器是计算机的核心部件,又被称为计算机的大脑。

它包括算术逻辑单元(ALU)和控制单元(CU),负责执行指令、算术运算和逻辑运算等。

存储器用于存储数据和指令,分为主存储器(RAM)和辅助存储器(硬盘、固态硬盘等)。

输入输出设备用于与计算机交互,包括键盘、鼠标、显示器、打印机等。

总线用于连接计算机的各个组成部分,包括数据总线、地址总线和控制总线等。

了解计算机硬件组成,对于设计和优化计算机系统具有重要意义。

其次,计算机组成原理涉及计算机的工作原理。

计算机的工作原理主要包括数据的表示和存储、指令的执行和流水线技术等。

数据的表示和存储是计算机进行数据处理的基础。

计算机使用二进制表示数据,将数据存储在内存中。

指令的执行是计算机进行计算和逻辑操作的基本单元。

计算机通过解码和执行指令,对数据进行处理。

流水线技术是提高计算机执行效率的一种重要方法。

通过将指令执行分解成多个阶段,可以提高指令的吞吐量。

计算机组成原理对于理解计算机工作原理和提高计算机系统性能具有重要意义。

最后,计算机组成原理涉及计算机的设计方法。

计算机的设计方法包括指令系统的设计、组合逻辑电路的设计和微程序设计等。

指令系统的设计是计算机体系结构的基础,决定了计算机的功能和性能。

组合逻辑电路设计是实现计算机各个功能模块的基础,包括加法器、乘法器、寄存器和控制电路等。

微程序设计是实现指令的执行和控制的基础,将指令分解成微指令并存储在控制存储器中。

组合逻辑控制器原理

组合逻辑控制器的设计方法

解析法

总结词

解析法是一种基于数学逻辑和布尔代数的方法,通过将逻辑表达式转换为电路结构来实现组合逻辑控 制器的设计。

详细描述

解析法的基本步骤包括将逻辑表达式进行化简、因式分解和化简,然后根据化简后的表达式设计相应 的电路结构。这种方法能够得到最简电路结构,但计算过程较为复杂,需要较高的数学基础。

在智能家居中的应用

智能照明系统

组合逻辑控制器能够根据环境光线、时间等 因素,自动调节家庭照明系统的亮度和色温 ,提供舒适的照明环境。

智能安防系统

组合逻辑控制器可以集成各种安防设备,如摄像头 、烟雾报警器等,实现家庭安全监控和预警。

智能环境控制系统

通过组合逻辑控制器,可以控制家庭中的空 调、暖气、空气净化器等设备,实现智能环 境调节。

定时器/计数器

用于产生时间基准和控制脉冲,实现定时控制和计数控制等功能 。

输出部分

驱动电路

将控制部分输出的控制信号转换为能够驱动执行机构 的大功率信号。

执行机构

根据控制信号驱动相应的设备或机构,实现控制目标 。

反馈电路

将执行机构的输出信号反馈给输入部分,形成闭环控 制系统,提高控制精度和稳定性。

03

特点

组合逻辑控制器具有结构简单、可靠 性高、易于编程和调试等优点,广泛 应用于工业自动化控制领域。

组合逻辑控制器的重要性

提高生产效率

通过自动化控制,组合逻辑控制 器能够提高生产效率,减少人工 干预,降低生产成本。

保证产品质量

精确的控制逻辑能够保证产品质 量的一致性和稳定性,提高产品 合格率。

增强系统可靠性

信号调理

02

对采集到的信号进行滤波、放大、去噪等处理,以消除干扰和

计算机组成原理

计算机组成原理计算机组成原理是指计算机由硬件和软件组成的过程和原理。

它涉及了计算机内部各部件的功能和相互关系,以及它们如何协同工作,实现计算、存储和通信等功能的基本原理。

计算机组成原理主要包括指令执行周期、存储器层次结构、总线结构、I/O系统、中央处理单元(CPU)、寄存器以及各种逻辑门电路等基本概念和原理。

计算机组成原理是计算机科学与技术的核心课程之一,它为我们深入了解计算机的工作原理以及如何有效地设计和优化计算机系统提供了重要基础。

指令执行周期是计算机工作的基本单位,它由取指令、指令译码、指令执行、访问存储器、写回数据等若干步骤组成。

存储器层次结构是指计算机系统中不同速度和容量的存储器层级,包括高速缓存、主存储器和辅助存储器等。

各级存储器通过读写控制线和数据线相连,实现数据的传输和存储。

总线结构是计算机内部各部件之间传输数据和控制信号的途径。

它包括数据总线、地址总线和控制总线等,用于在CPU、存储器和I/O设备之间传输数据和控制信息。

I/O系统是计算机与外部设备之间的接口,负责数据的输入输出和设备的管理。

它通过I/O控制器和外设接口等实现计算机与外部设备的通信。

CPU是计算机的核心部件,负责执行程序中的指令。

它由控制单元和算术逻辑单元组成,控制单元负责指令的控制和管理,算术逻辑单元负责进行数据的运算和逻辑判断。

寄存器是CPU内部用于存储数据和指令的临时存储器,包括通用寄存器、指令寄存器、程序计数器等。

逻辑门电路是计算机中最基本的构建单元,包括与门、或门、非门等。

通过逻辑门的组合和连接,可以实现各种逻辑运算和控制功能。

计算机组成原理涉及的其他概念还包括指令集体系结构、流水线技术、中断处理等。

总之,计算机组成原理是计算机科学与技术中的重要基础课程,它为我们理解计算机工作原理、设计高效的计算机系统提供了基础。

通过学习计算机组成原理,我们可以更好地理解计算机的内部结构和原理,为后续的计算机体系结构、操作系统、编译原理等课程奠定坚实的基础。

组合逻辑控制器的设计步骤

组合逻辑控制器的设计步骤嘿,咱今儿就来说说组合逻辑控制器的设计步骤。

这可不是什么随随便便就能搞定的事儿,就像搭积木,得一块一块精心摆弄才行。

首先呢,你得明确自己要干啥,就跟你出门得知道往哪儿走一样。

搞清楚系统的要求和功能,这可是基础中的基础。

你想想,要是连目标都不清楚,那不就瞎忙活啦?然后呢,根据这些要求,开始设计指令系统。

这指令系统就好比是一套规则,让各个部件知道该干啥,啥时候干。

这可得仔细琢磨,不能出岔子,不然整个系统都得乱套。

接下来,就是设计状态图啦。

这就像是给系统画一幅运行的路线图,每个状态都得考虑清楚,怎么转换,有啥条件。

这可不是闹着玩的,得费点心思呢。

再然后,根据状态图来确定逻辑表达式。

这可有点像解数学题,得一步步推导出来。

这里可不能马虎,一个小错误都可能导致大问题哦。

之后呢,就得选择合适的逻辑器件啦。

这就好比给系统选合适的工具,得好用又顺手。

要是选不好,那可就麻烦啦。

再接着,把这些逻辑器件组合起来,搭建出整个控制器。

这就像盖房子,一砖一瓦都得放对地方。

最后,可别忘了测试和优化呀。

就跟你新做了个东西得试试好不好用一样。

有问题就得赶紧改,可不能等出了大毛病再后悔。

你看,这组合逻辑控制器的设计步骤,一环扣一环,哪一步都不能马虎。

就像一场精彩的表演,每个环节都得配合好,才能呈现出完美的效果。

咱可不能小瞧了这些步骤,只有认真对待,才能设计出好用又可靠的组合逻辑控制器。

这不就跟咱过日子一样嘛,每一步都得走稳了,才能过得踏实,过得好呀!你说是不是这个理儿?。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

例2:MOV(R0),(R1);FT0: M ST0: R1 ST1: M DT0: R0 ET0: C ET1: MDR ET2: PC

IR,PC+1 PC

MAR MDR

MAR

源数

C

目的地址

MDR

M

MAR

例3:MOV X(R0),X(R1);FT0: M IR

PC+1 PC

ST0: PC MAR 形地 ST1: M MDR C

2)流程图

FT0: M IR PC+1 PC

3)操作时间表

FT0:

电位型微命令

脉冲型微命令

M IR EMAR, R, SIR

PC+1 PC PC A, A+1,DM CPPC

1 ST 或

CPFT( P)

1 DT 或 1 ET

CPST( P)

转

CPDT( P)

换

CPET( P)

CPT ( P)

工作周期中,每拍结束时发CPT;工作周期结束时,

关中断、保存断点和PSW、转服务程序入口。

由硬件完成

6)DMA周期DMAT DMAT指CPU响应DMA请求后,到传送完一次数据。

DMA控制器接管总线权,控制直传。

由硬件完成

哈尔滨工程大学计算机科学与技术学院 姚爱红

6

(2)时钟周期(节拍)T

1)时钟周期时间: 1微秒 完成一步操作:

一次从M读出,并经数据通路传送的操作;或 一次数据通路传送操作;或 一次向M写入的操作

在整个指令周期中, 任何时候必须、且只 能有一个工作周期状 态标志为“1”。

4

(1)工作周期(续)

1)取指周期FT 从M取出指令并译码;修改PC。 公操作

取指结束时,按操作码和寻址方式(R/非R寻址) 转相应工作周期。

2)源周期ST 按寻址方式(非R寻址)形成源地址,从M取出源操 作数,暂存于C。

3)目的周期DT

按寻址方式(非R寻址)形成目的地址,或从M取出

目的操作数,暂存于D。

哈尔滨工程大学计算机科学与技术学院 姚爱红

5

(1)工作周期(续)

4)执行周期ET

按操作码完成相应操作(传送、运算、取转移地址送入PC、 返回地址压栈保存);后续指令地址送入MAR。

5)中断周期IT

IT指CPU响应中断请求后,到执行中断服务程序前。

5个时序打入命令都发。

4)时序关系 FT0: EMAR

PC A S3 S2 S1 S0 M C0 DM

FT0: CPPC 1 FT CPFT( P) 1 ST CPST( P) CPDT( P) CPET( P) T+1 CPT ( P)

(2)传送指令 1)流程图

例1:MOV R0,R1; FT0: M IR,PC+1 PC ET0: R1 R0 ET1: PC MAR

初始化置入 总清

复位初始化

1

Q

Q

S FT R

D

C

1 FT

CPFT 运算过程中 同步打入

哈尔滨工程大学计算机科学与技术学院 姚爱红

12

(1)取指周期FT

单 SR

FT

双 SR

ST

DR

DT

转 DR

ET

N DMA请求?

Y

DMAT

N 中断请求?

Y

IT

( ) ( ) 哈1尔→滨工F程T大=学E计T算1机→科学D与M技A术T学⋅院1→姚I爱T红+ IT + DMAT1→ DMAT⋅1→ IT 13

哈尔滨工程大学计算机科学与技术学院 姚爱红

30

1.微命令逻辑条件的综合化简

归纳微命令,综合化简条件,用组合逻辑 电路实现。

例: 读命令 R= FT0 +MOV(ST1+ST4+……) +……

CPPC= FT0 P +MOV(ST2+DT2) X P +……

( ) ( ) 1→ FT = ET 1→ DMAT⋅1→ IT + IT + DMAT1→ DMAT⋅1→ IT

ST2:SP+1 SP SP A A+1 DM CPSP 1 DT CPFT(P) CPET(P) CPT(P)

DT0:R1 ET0:C

MAR R1 A 输出A DM CPMAR 1 ET CPFT(P) CPET(P) CPT(P)

MDR C B 输出B DM CPMDR T+1 CPT(P)

ET1:MDR M EMAR W T+1 CPT(P)

DMAT

中断请求? N Y

IT

3.5.2指令流程图与操作时间表

拟定指令流程:确定各工作周期中每拍完成的具体 操作(寄存器传送级)。

列操作时间表:列出每一步操作所需的微命令及产 生条件。

哈尔滨工程大学计算机科学与技术学院 姚爱红

11

(1)取指周期FT

1)进入FT的方式

初始化时置入FT,程序正常运行时同步打入FT。

中断隐指令

FT ET

IT0 IT1

主程序 <-INT

1->IT, INTA 0->I

SP-1->SP,MAR

PC->MDR

IT2

MDR->M

IT3

向量地址->MAR

IT4 FT0

入口地址->PC,MAR 1->FT

子程序

哈尔滨工程大学计算机科学与技术学院 姚爱红

27

(8)DMA周期 DMAT

FT ET

哈尔滨工程大学计算机科学与技术学院 姚爱红

8

(3)工作脉冲P

每个时钟结束时设置一个脉冲。

T

1µS

P 打入寄存器

进行时序转换

(周期状态设置/清除 时钟T计数/清除)

哈尔滨工程大学计算机科学与技术学院 姚爱红

9

(4)控制流程(工作周期转换)

单 SR

FT

双 SR

ST

DR

DT

转 DR

ET

DMA请求? N Y

子程序入口。 1101 010 001 000000

例:JSR(R2); FT0: M IR, PC+1 PC

ST0: R2 MAR

子程序

ST1: M MDR C 入口

ET0: SP-1 SP、MAR

ET1: PC MDR ET2: MDR M

返回地 址压栈

ET3: C PC、MAR

(7)中断周期IT

ST1: M MDR C ST2: PC+1 PC

目的数

DT0: PC MAR DT1: M MDR D DT2: PC+1 PC

形式地址

DT3: D+R1 MAR DT4: M MDR D ET0:C+D MDR ET1:MDR M ET2:PC MAR

(4)单操作数指令 例:COM -(R0);

时钟周期2

(节拍2)

….

指令周期

工作周期2

时钟周期m

(节拍m)

工作脉冲1 工作脉冲2

工作脉冲k

……….

…..

……

….

工作周期n

哈尔滨工程大学计算机科学与技术学院 姚爱红

2

时序关系举例:

晶振输出

工作脉冲P

对微操作定时

打入IR

打入PC

时钟T1 控制分步操作时间

取出指令

时钟T2

修改PC

工作周期1 控制不同阶段操作时间

FT0:M IR,PC+1 PC

ET0:PC ET1:M

MAR MDR

C

位移量

ET2:PC+C PC 、MAR

哈尔滨工程大学计算机科学与技术学院 姚爱红

25

(6)转子指令 无条件转子: R (R) (R)+ (PC)+ (SP)+

入口在R中 入口在M中 入口在堆栈中

在ST形成子程序入口;在ET保存返回地址,并转

工作周期2 工作周期3

取指

取数

指令周期

执行

模型机时序系统设计

(1)工作周期

取指周期FT 源周期 ST 目的周期DT 执行周期ET 中断周期IT DMA周期DMAT

用于指令正常执行 用于I/O传送控制

设置6个触发器分别 1 工作周期开始 作为各周期状态标志

0 工作周期结束

哈尔滨工程大学计算机科学与技术学院 姚C+1 PC

暂存于C,

ST3: C+R1 MAR 源数

需5步。

ST4: M MDR C

DT0: PC MAR 形地 DT1: M MDR D DT2: PC+1 PC 目的地址 DT3: D+R0 MAR

取目的地址, 暂存于MAR, 需4步。

ET0: C MDR ET1: MDR M ET2: PC MAR

哈尔滨工程大学计算机科学与技术学院 姚爱红

31

2.优缺点

● 产生微命令的速度较快。 ● 设计不规整,设计效率较低;

● 不易修改、扩展指令系统功能。

3.应用场合

用于高速计算机,或小规模计算机。

哈尔滨工程大学计算机科学与技术学院 姚爱红

32

FT0:M IR,PC+1 PC ET0:R0 PC 、MAR

例2:RST (SP)+;1100 100 011 000000

FT0:M IR,PC+1 PC

ET0:SP MAR

ET1:SP+1 SP

ET2:M MDR PC、MAR

哈尔滨工程大学计算机科学与技术学院 姚爱红

24

例3:JMP X(PC);1100 111 101 000000