synopsis VCS makefile编写

c语言makefile编写规则(一)

c语言makefile编写规则(一)C语言Makefile编写规则1. Makefile介绍Makefile是一种文件,其中包含了一组规则(rules)用于编译和构建项目。

它的作用是告诉系统如何编译代码,生成可执行文件。

2. Makefile规则基本结构Makefile规则由以下几部分组成:目标(Target)目标是一个文件,可以是源代码文件、中间文件或最终生成的可执行文件。

依赖(Dependencies)依赖指的是生成目标所需要的文件或其他目标。

当某个依赖文件发生变化时,目标就需要重新生成。

命令(Commands)命令是指执行编译、链接等操作的具体命令。

当目标需要重新生成时,Makefile会执行相应的命令。

规则示例以下是一个简单的示例,展示了一个C语言源文件的编译过程:target: dependenciescommand其中, - target表示目标文件; - dependencies表示生成目标所需要的文件或其他目标; - command表示具体的编译命令。

例如,假设有一个名为`的C语言源文件,我们想要生成一个名为hello`的可执行文件。

那么对应的Makefile规则可以定义如下:hello:gcc -o hello3. Makefile变量Makefile中还可以定义变量,以提高代码的可读性和重用性。

变量可以存储命令、文件名、路径等信息。

变量定义变量的定义采用变量名 = 值的方式进行,例如:CC = gcc其中,CC是变量名,gcc是变量的值。

变量引用使用变量时,需要在变量名前加$符号进行引用。

例如,使用上述定义的CC变量可以这样写:$(CC) -o hello4. Makefile示例以下是一个完整的Makefile示例,展示了多个目标之间的依赖关系和命令定义:CC = gccall: hellohello:$(CC) -o hello:$(CC) -cclean:rm -f hello在上述示例中,共定义了3个目标:all、hello和。

MakeFile脚本的编写

MakeFile脚本的编写1.Eclipse Debug下默认会⽣成 .mk格式的makefile多⽂件2.下连接可以⽤⼀个⽂件来实现MakeFile功能。

转载⾸先进⾏的内容是参数设置部分,如下:设置项⽬名字,它决定了我们make之后,⽣成的⽂件名。

⽐如libXX.so或者XXX.a或者XXXX#set your project namePRJ_NAME=libXXX.so设置项⽬的类型,是共享库、可执⾏程序还是静态库#set your project type : choose one belowPRJ_TYPE =g++ -shared#PRJ_TYPE = g++#PRJ_TYPE = ar -r设置编译的类型,是Debug还是Release#set Debug or ReleaseCompile_Flag = Debug#Compile_Flag = Release设置编译后的⽂件的输出路径,这个⽂件夹⼀定要有才可以,否则会出错的。

所以要事先建⽴好#set your output pathOutput:= bin这⾥是设置代码所在的⽂件夹#set your source folderSRC:=code如果引⽤了什么库,就在这⾥添加好了.#add the lib you used here#LIBS := -lLib1 -lLib2 -lLib3LIBS := -lpthread#LIBPATH := -Lpath1 -Lpath2 -Lpath3LIBPATH :=INCLUDEPATH :=# INCLUDEPATH := -I/usr/lib/XXX/include要设置的参数就这么多。

下⾯进⼊第⼆部分,makefile核⼼内容的解释。

下⾯我仔细讲⼀下。

#符号,表⽰注释。

makefile⾥⾯有它的那⾏,就不会起作⽤了。

⽐如下⾯两⾏就是注释。

####################################DON"T MODIFY THE BELOWS#combine output folderFinalOutput := $(Output)/$(Compile_Flag)/上⾯的代码,定义了⼀个变量,名字是FinalOutput,给它赋值,可以⽤=或者:=,等⼀下说区别。

sv中 makefile文件的写法

很高兴接到您的指示,让我来帮助您撰写关于sv中makefile文件的文章。

让我们来深入了解一下makefile文件的概念和作用。

1. 什么是makefile文件?在SV(SystemVerilog)编程中,makefile文件是用来组织和管理编译工程中的各个源文件和依赖关系的文件。

它定义了编译规则和指令,用于自动化编译和构建整个项目。

2. makefile文件的基本结构在编写makefile文件时,通常会包含以下基本元素:- 变量定义:定义编译器、编译选项、源文件列表等变量。

- 规则定义:定义编译规则,包括目标文件、依赖文件和编译指令。

- 依赖关系:明确指出各个源文件之间的依赖关系,以便make工具能够正确地进行编译。

3. sv中makefile文件的写法在SV项目中,编写makefile文件需要特别关注以下几点:- 定义变量:可以通过定义变量来指定编译器、编译选项、原文件列表等信息,使得makefile文件更加灵活和可维护。

- 设置规则:需要设置好编译规则,包括目标文件、依赖文件和编译指令。

这些规则应该准确反映出SV项目的结构和依赖关系。

- 定义依赖:在makefile文件中,需要清晰地定义各个源文件之间的依赖关系,以确保make工具能够正确地进行增量编译,提高编译效率。

4. 个人观点和理解在我看来,编写高质量的makefile文件对于SV项目的管理和维护至关重要。

一个良好的makefile文件可以提高项目的编译效率,简化编译过程,并且便于团队协作和代码管理。

在编写makefile文件时,应该注重规范和细节,以确保项目的可维护性和稳定性。

总结回顾通过编写这篇文章,我深入了解了sv中makefile文件的写法,并且通过我的个人观点和理解对这个主题进行了探讨。

在文章中多次提及了主题文字,并采用了从简到繁、由浅入深的方式来探讨主题,以便您能更深入地理解。

希望这篇文章能够对您有所帮助。

以上是我为您准备的关于sv中makefile文件的文章,希望能够满足您的要求。

makefile的通用编写 -回复

makefile的通用编写-回复Makefile是一种用于自动化构建和管理项目的工具,它使用一种被称为Makefile的文件来指定构建和管理项目的规则。

Makefile通常由一系列目标(target)、依赖关系(dependencies)和命令(commands)组成。

在本文中,我们将详细介绍Makefile的通用编写方法,从创建一个简单的Makefile文件开始,到使用变量、条件、循环和函数等高级特性,帮助读者更好地理解和使用Makefile。

让我们一步一步地回答您的问题,教您如何编写一个高效的Makefile。

第一步:创建一个简单的Makefile文件为了开始编写Makefile,我们首先需要在项目的根目录下创建一个名为Makefile的文本文件。

可以使用任何文本编辑器来创建并编辑这个文件。

在开始编写之前,我们需要了解一些基本的语法和规则。

Makefile文件由一系列规则组成,每个规则包含一个或多个目标、依赖关系和命令。

例如,我们可以创建一个简单的规则来构建一个名为hello的可执行文件:hello: main.ogcc -o hello main.omain.o: main.cgcc -c main.c在这个例子中,我们创建了一个名为hello的目标,它依赖于main.o 文件。

我们还创建了一个名为main.o的目标,它依赖于main.c文件。

每个目标都有相应的命令,用于构建目标所需的文件。

第二步:使用变量变量是Makefile中非常常用的机制,它可以帮助我们更好地管理和维护项目。

可以通过在Makefile文件中定义变量,然后在规则和命令中使用这些变量来简化代码。

例如,我们可以使用变量来代替文件名:CC = gccCFLAGS = -chello: main.o(CC) -o hello main.omain.o: main.c(CC) (CFLAGS) main.c在这个例子中,我们定义了两个变量CC和CFLAGS。

c语言makefile编写规则

c语言makefile编写规则C语言Makefile编写规则什么是MakefileMakefile是一种用于管理和构建软件项目的文件,通常被用于编译和链接C语言程序。

Makefile中包含了一系列的规则和指令,用于告诉编译器如何编译程序中的各个部分,并最终生成可执行文件。

Makefile的基本结构Makefile的基本结构由多个规则组成,每个规则由一个目标(target)和一个或多个依赖(dependencies)组成。

目标指明了要生成的文件或要执行的操作,依赖指明了目标所依赖的文件或操作。

一个简单的Makefile规则的语法如下:target: dependenciescommand其中,target是生成的文件或要执行的操作,dependencies是目标所依赖的文件或操作,command是执行的命令。

每个规则的命令必须以一个tab键开始。

Makefile的应用场景Makefile广泛应用于C语言项目的构建中,它可以自动化执行编译、链接和清理等操作。

通过Makefile,我们可以方便地管理源代码文件、头文件和库文件之间的关系,从而提高项目的可维护性和可扩展性。

Makefile的编写规则1.目标和依赖应该使用合适的命名方式,能够清晰地表达其作用以及所依赖的内容。

避免使用中文、空格和特殊字符,使用下划线和英文字母进行命名。

2.命令行命令应该以tab键开始,而不是空格。

这是Makefile的语法要求,且使用tab键可以提高代码的可读性。

3.注意规则的顺序,确保前置依赖在目标之前。

Makefile会按照规则的声明顺序进行构建,如果前置依赖在目标之后,可能导致构建失败。

4.使用变量来定义重复使用的内容,如编译器选项、源文件列表等。

这样可以提高代码的可维护性,并方便进行后续的修改和维护。

5.使用通配符来表示一类文件,如使用*.c表示所有的C语言源文件,使用$(wildcard pattern)函数来获取符合某种模式的文件列表。

MakeFile编写规则

MakeFile编写规则什么是makefile (3)关于程序的编译和链接 (3)Makefile 介绍 (4)一、Makefile的规则 (4)二、一个示例 (4)三、make是如何工作的 (6)四、makefile中使用变量 (6)五、让make自动推导 (7)六、另类风格的makefile (8)七、清空目标文件的规则 (8)Makefile 总述 (9)一、Makefile里有什么 (9)二、Makefile的文件名 (9)三、引用其它的Makefile (9)四、环境变量MAKEFILES (10)五、make的工作方式 (10)实例说明 (11)一、简单例子 (11)二、规则的语法 (11)三、在规则中使用通配符 (12)四、文件搜寻 (12)五、伪目标 (13)六、多目标 (14)七、静态模式 (15)八、自动生成依赖性 (16)书写命令 (17)一、显示命令 (17)二、命令执行 (18)三、命令出错 (18)四、嵌套执行make (19)五、定义命令包 (20)使用变量 (21)一、变量的基础 (21)二、变量的赋值 (21)第一种方式 (22)第二种方式 (22)三、变量高级用法 (23)一种是变量值的替换 (23)第二种高级用法——“把变量的值再当成变量” (24)四、追加变量值 (25)五、override 指示符 (26)六、多行变量 (26)七、环境变量 (26)八、目标变量 (27)九、模式变量 (27)十、自动化变量 (28)使用条件判断 (30)makefile的编写规则--语法及函数 (31)条件表达式 (31)函数 (32)一、函数的调用语法 (32)二、字符串处理函数 (33)$(subst <from>,<to>,<text> ) (33)$(patsubst <pattern>,<replacement>,<text> ) (33)$(strip <string> ) (34)$(findstring <find>,<in> ) (34)$(filter <pattern...>,<text> ) (34)$(filter-out <pattern...>,<text> ) (34)$(sort <list> ) (35)$(word <n>,<text> ) (35)$(wordlist <s>,<e>,<text> ) (35)$(words <text> ) (35)$(firstword <text> ) (36)三、文件名操作函数 (36)$(dir <names...> ) . (36)$(notdir <names...> ) .. (36)$(suffix <names...> ) .. (37)$(basename <names...> ) .. (37)$(addsuffix <suffix>,<names...> ) (37)$(addprefix <prefix>,<names...> ) .. (37)其他函数 (37)$(join <list1>,<list2> ) (37)foreach 函数 (38)if 函数 (38)call函数 (38)origin函数 (39)shell函数 (40)控制make的函数 (40)$(error <text ...> ) . (40)$(warning <text ...> ) . (40)make 的运行 (41)一、make的退出码 (41)二、指定Makefile (41)三、指定目标 (41)四、检查规则 (42)什么是makefile什么是makefile?或许很多Winodws的程序员都不知道这个东西,因为那些Windows 的IDE都为你做了这个工作,但要作一个好的和professional的程序员,makefile还是要懂。

MAKEFILE的编写

MAKEFILE的编写第一章Makefile简介什么是makefile?或许很多Winodws的程序员都不知道这个东西,因为那些Windows 的IDE都为你做了这个工作,但我觉得要作一个好的和professional的程序员,makefile还是要懂。

这就好像现在有这么多的HTML的编辑器,但如果你想成为一个专业人士,你还是要了解HTML的标识的含义。

特别在Unix下的软件编译,你就不能不自己写makefile了,会不会写makefile,从一个侧面说明了一个人是否具备完成大型工程的能力。

因为,makefile关系到了整个工程的编译规则。

一个工程中的源文件不计数,其按类型、功能、模块分别放在若干个目录中,makefile定义了一系列的规则来指定,哪些文件需要先编译,哪些文件需要后编译,哪些文件需要重新编译,甚至于进行更复杂的功能操作,因为makefile就像一个Shell脚本一样,其中也可以执行操作系统的命令。

makefile带来的好处就是——“自动化编译”,一旦写好,只需要一个make命令,整个工程完全自动编译,极大的提高了软件开发的效率。

make是一个命令工具,是一个解释makefile中指令的命令工具,一般来说,大多数的IDE都有这个命令,比如:Delphi的make,Visual C++的nmake,Linux下GNU的make。

可见,makefile都成为了一种在工程方面的编译方法。

make命令执行时,需要一个Makefile 文件,以告诉make命令需要怎么样的去编译和链接程序。

首先,我们用一个示例来说明Makefile的书写规则。

以便给大家一个感兴认识。

这个示例来源于GNU的make使用手册,在这个示例中,我们的工程有8个C文件,和3个头文件,我们要写一个Makefile来告诉make命令如何编译和链接这几个文件。

我们的规则是:1)如果这个工程没有编译过,那么我们的所有C文件都要编译并被链接。

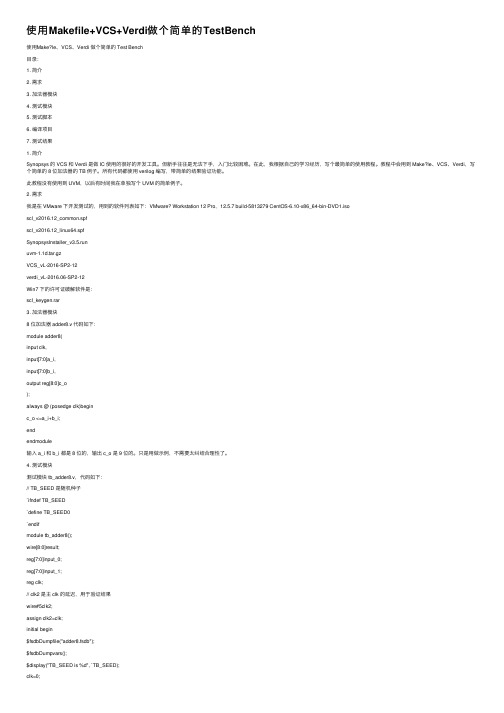

使用Makefile+VCS+Verdi做个简单的TestBench

使⽤Makefile+VCS+Verdi做个简单的TestBench使⽤Make?le、VCS、Verdi 做个简单的 Test Bench⽬录:1. 简介2. 需求3. 加法器模块4. 测试模块5. 测试脚本6. 编译项⽬7. 测试结果1. 简介Synopsys 的 VCS 和 Verdi 是做 IC 使⽤的很好的开发⼯具。

但新⼿往往是⽆法下⼿,⼊门⽐较困难。

在此,我根据⾃⼰的学习经历,写个最简单的使⽤教程。

教程中会⽤到 Make?le、VCS、Verdi,写个简单的 8 位加法器的 TB 例⼦。

所有代码都使⽤ verilog 编写,带简单的结果验证功能。

此教程没有使⽤到 UVM,以后有时间我在单独写个 UVM 的简单例⼦。

2. 需求我是在 VMware 下开发测试的,⽤到的软件列表如下:VMware? Workstation 12 Pro,12.5.7 build-5813279 CentOS-6.10-x86_64-bin-DVD1.isoscl_v2016.12_common.spfscl_v2016.12_linux64.spfSynopsysInstaller_v3.5.runuvm-1.1d.tar.gzVCS_vL-2016-SP2-12verdi_vL-2016.06-SP2-12Win7 下的许可证破解软件是:scl_keygen.rar3. 加法器模块8 位加法器 adder8.v 代码如下:module adder8(input clk,input[7:0]a_i,input[7:0]b_i,output reg[8:0]c_o);always @ (posedge clk)beginc_o <=a_i+b_i;endendmodule输⼊ a_i 和 b_i 都是 8 位的,输出 c_o 是 9 位的。

只是⽤做⽰例,不需要太纠结合理性了。

4. 测试模块测试模块 tb_adder8.v,代码如下:// TB_SEED 是随机种⼦`ifndef TB_SEED`define TB_SEED0`endifmodule tb_adder8();wire[8:0]result;reg[7:0]input_0;reg[7:0]input_1;reg clk;// clk2 是主 clk 的延迟,⽤于验证结果wire#5clk2;assign clk2=clk;initial begin$fsdbDumpfile("adder8.fsdb");$fsdbDumpvars();$display("TB_SEED is %d", `TB_SEED);clk=0;input_0=8'd0;input_1=8'd0;#10000$display("All test PASS!");$finish;end// 主时钟 50MHzalways begin#10clk=~clk;end// 产⽣随机输⼊always @ (negedge clk)begininput_0=$random()%256;input_1=$random()%256;end// 获取验证输出always @ (posedge clk2)beginif((input_0+input_1)!=result)begin$display("Test failed for %x + %x = %x", input_0, input_1, result);$finish;end else begin$display("%x + %x = %x", input_0, input_1, result);endend// 连接加法器模块adder8dut(.clk(clk),.a_i(input_0), .b_i(input_1), .c_o(result) );endmodule5. 测试脚本整个编译过程采⽤ Make?le 控制,Make?le ⽂件内容如下:VCS = vcs -sverilog -timescale=1ns/1ns +vpi -l build.log -debug_access+allSIMV = ./simv -l simv.logifndef TB_SEEDTB_SEED = 1024endifall: comp runcomp:$(VCS) +define+TB_SEED=$(TB_SEED) +incdir+. \adder8.v \tb_adder8.vrun:$(SIMV) +fsdbfile+top.fsdbdbg:verdi -f file.f -ssf top.fsdb &clean:rm -rf core csrc simv* vc_hdrs.h ucli.key urg* *.log *.fsdb novas.* verdiLogMake?le ⾥⾯的空格排版都是 TAB 键,否则会出错,修改的时候请注意⼀下这个细节。

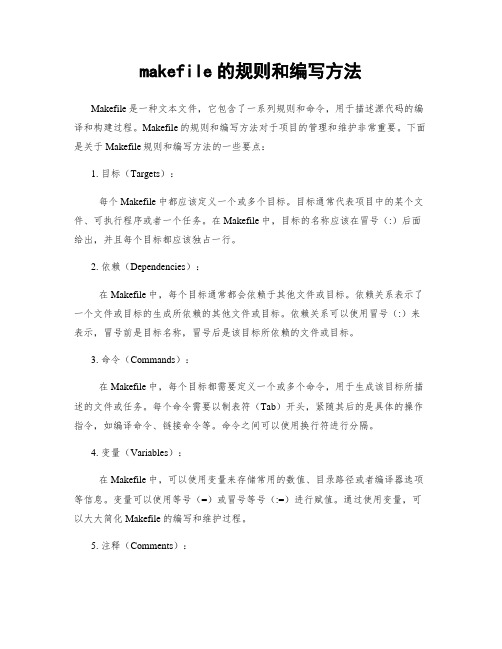

makefile的规则和编写方法

makefile的规则和编写方法Makefile是一种文本文件,它包含了一系列规则和命令,用于描述源代码的编译和构建过程。

Makefile的规则和编写方法对于项目的管理和维护非常重要。

下面是关于Makefile规则和编写方法的一些要点:1. 目标(Targets):每个Makefile中都应该定义一个或多个目标。

目标通常代表项目中的某个文件、可执行程序或者一个任务。

在Makefile中,目标的名称应该在冒号(:)后面给出,并且每个目标都应该独占一行。

2. 依赖(Dependencies):在Makefile中,每个目标通常都会依赖于其他文件或目标。

依赖关系表示了一个文件或目标的生成所依赖的其他文件或目标。

依赖关系可以使用冒号(:)来表示,冒号前是目标名称,冒号后是该目标所依赖的文件或目标。

3. 命令(Commands):在Makefile中,每个目标都需要定义一个或多个命令,用于生成该目标所描述的文件或任务。

每个命令需要以制表符(Tab)开头,紧随其后的是具体的操作指令,如编译命令、链接命令等。

命令之间可以使用换行符进行分隔。

4. 变量(Variables):在Makefile中,可以使用变量来存储常用的数值、目录路径或者编译器选项等信息。

变量可以使用等号(=)或冒号等号(:=)进行赋值。

通过使用变量,可以大大简化Makefile的编写和维护过程。

5. 注释(Comments):注释用于解释Makefile中的规则和命令,以提高代码的可读性。

在Makefile 中,可以使用井号(#)表示注释,井号后的内容会被忽略。

编写一个简单的Makefile示例:```# 定义变量CC = gccCFLAGS = -Wall -O2# 定义目标和依赖关系myprogram: main.o func1.o func2.o$(CC) $(CFLAGS) -o myprogram main.o func1.o func2.o# 生成目标的命令main.o: main.c$(CC) $(CFLAGS) -c main.cfunc1.o: func1.c$(CC) $(CFLAGS) -c func1.cfunc2.o: func2.c$(CC) $(CFLAGS) -c func2.c# 清理目标文件的命令clean:rm -f *.o myprogram```以上是一个简单的Makefile示例。

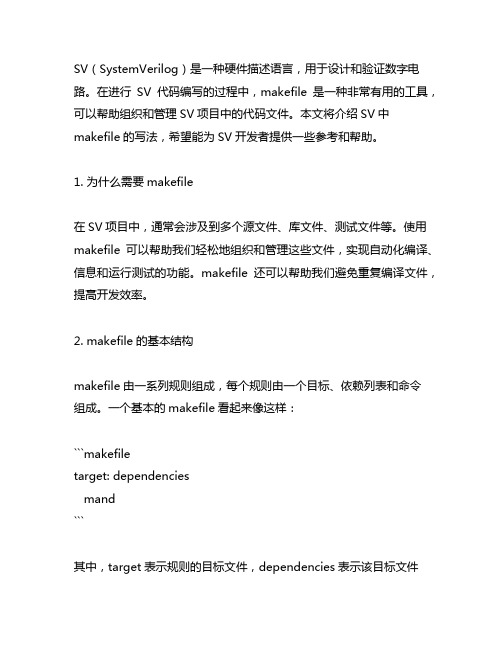

sv 中的makefile 写法

SV(SystemVerilog)是一种硬件描述语言,用于设计和验证数字电路。

在进行SV代码编写的过程中,makefile是一种非常有用的工具,可以帮助组织和管理SV项目中的代码文件。

本文将介绍SV中makefile的写法,希望能为SV开发者提供一些参考和帮助。

1. 为什么需要makefile在SV项目中,通常会涉及到多个源文件、库文件、测试文件等。

使用makefile可以帮助我们轻松地组织和管理这些文件,实现自动化编译、信息和运行测试的功能。

makefile还可以帮助我们避免重复编译文件,提高开发效率。

2. makefile的基本结构makefile由一系列规则组成,每个规则由一个目标、依赖列表和命令组成。

一个基本的makefile看起来像这样:```makefiletarget: dependenciesmand```其中,target表示规则的目标文件,dependencies表示该目标文件的依赖文件mand表示需要执行的命令。

3. 使用变量在makefile中,我们可以使用变量来定义一些常量,方便我们在后续的规则中使用。

例如:```makefileSV_SRC = file1.sv file2.sv file3.sv```这样,我们就可以在后续的规则中使用$(SV_SRC)来表示这些文件,而不需要重复地写出它们的文件名。

4. 基本规则在SV项目中,常见的makefile规则包括编译规则、信息规则和运行测试规则。

以下是一个简单的例子:```makefileall: $(SV_SRC)vlog $(SV_SRC)sim: allvsim top_module```在这个例子中,我们定义了两个规则,分别是all和sim。

all规则依赖于$(SV_SRC)中的文件,使用vlog命令对这些文件进行编译。

sim规则依赖于all规则,使用vsim命令来运行测试。

5. 使用通配符在makefile中,我们还可以使用通配符来表示一类文件。

如何写一个简单的Makefile

如何写一个简单的Makefile当我们在提示符号之下下一个命令:$ make program就是说你要去”make”一个新版本—而且通常是最新版本—的程序. 如果这个程序是一个可执行文件,你所下的这个命令意思就是说你想要完成有所必须的编译(compiling)与连结(linking),然后得出一一个可执行文件. 你可以使用make来使这些程序自动化,不必不断输入为数可观的gcc(or cc)这些编译器指令.当我们讨论make的时候,我们把我们所要建造的程序(program)称做目标(target). 程序是由一个或一个以上的文件汇集在一起所建造出来的,这些文件的关系分为必要文件(prerequisites)与附属文件(dependents). 每一个构成程序的文件依序有他们自己的必要文件和附属文件.例如,你由连结建造了可执行文件. 一旦你的原始文件(source file)或头文件(head file)改变了,你就必须再连结新的可可执行文件之前重新编译目标文件(object file). 每一个原始文件都是一个目标文件的必要文件.Make的优点就是它对附属的隶属关系是非常敏感的,像是原始文件->目标文件,目标文件->可可执行文件. 你负责在描述文件(description file)中指定一些附属文件,这个描述文件的文件名通常为makefile 或是Makefile. 但是make也知道自己所在的执行环境,它也会自己决定许多它自己的附属文件. make会利用文件的文件名,这些文件最近修改的时间,和一些內建的规则,决定编译时要使用哪些文件与如何去建立它们. 在这样的技术背景之下,之前所做的那个简单的make指令会保证在隶属中所有建造目标时必须存在的部分都会被更新.描述文件(Description File)假设你写了一个程序,程序由以下部分所組成:*用C语言写的原始文件— main.c iodat.c dorun.c*用其它语言写的程序码—lo.s ,此文件被C写成的原始文件所调用*一組位于/usr/fred/lib/crtn.a 之中的函数库方法(library routine)如果你用手一一下指令建造这个程序,你会在提示符号下打入:$cc –c main.c$cc –c iodat.c$cc –c dorun.c$as –0 lo.o lo.s$cc –o program main.o iodat.o dorun.o lo.o /usr/fred/lib/crtn.a当然你也可以在一行cc命令之內就做好编译,连结的工作(要下很长的一串指令),但是在实际的程序设计环境下这是很少发生的(因为指令实在是又长又复杂),因为以下原因: 首先,每一个原始文件都可能被不同的人所建立或测试. 第二,一个大程序会花掉好几小时的编译工作,所以程序设计师一般都会尽可能的使用已经存在的目标文件而不要再重新编译(可以节省时间).现在让我们来看看如何透过描述文件下指令給make. 我们建立了一个新的文件叫做makefile,这个文件和所有的原始码放在同一个目录之下. 为了方便起见,这个描述文件中的每一个指令和附属文件都明显的打出来,很多对make来说都是不需要的. 这个描述文件的內容如下:program : main.o iodat.o dorun.o lo.o /usr/fred/lib/crtn.acc –o program main.o iodat.o dorun.o lo.o /usr/fred/lib/ctrn.amain.o : main.ccc –c main.ciodat.o : iodat.ccc –c iodat.cdorun.o : dorun.ccc –c dorun.clo.o : lo.sas –0 lo.o lo.s在每一行左边的数字并不属于描述文件的一部份,只是为了待会解释方便这个描述文件中包含了五个项目(或说是入口点)(entry). 每一个项目由一个含有冒号(:)(叫做附属列[dependency line]或是规则列[rules line]),和一个或一个以上以tab(4个字元空白)开头的命令列(command line). 在附属行那个冒号左边的叫做目标(target);冒号左边的就是目标的必要文件. 受tab影响的(tab-indented)命令列,告诉make如何从他们的必须文件中建造出目标.从上面的描述文件来看,第1列说明了program这个目标依靠main.o,iodat.o,dorun.o,lo.o这些目标文件,还有依靠函数库/usr/fred/lib/crtn.a .第2列指定了从必要文件构造program这个目标文件所必须下的编译器指令.(这些文件都是目标文件与函数库,所以实际上并不用编译,只调用了连结器(linker)而已). 假设program这的目标文件不存在,你可以下这个指令:$make programmake会去执行第二行的命令. 如果其中一个目标文件不在该怎么办呢? 你能够把这个目标文件当作参数传給make(例如:没有main.o ,你可以下指令$make main.o ,就可以得到main.o 这个文件),但是几乎不必这样做.Make最重要的贡献就在于它有能力可以自己决定什么东西必须被建立(例如:在建立program时,如果少了main.o,则他会根据附属列所指定的內容,自己建立main.o这个文件).检查附属文件(Dependency Checking)当你要求make去建造program这个目标时,make会去参考前面所列出的那一个描述文件,但是,第二列的编译器指令并不会立刻就执行. make所做的动作应该如下: 首先,make先去检查目录下是否有program这个文件,如果有的话,make会去检查main.o , iodat.o , dorun.o , lo.o , 还有/usr/fred/lib/crtn.a 这些文件,看看这些文件有没有比program这个文件更新(更新的意思是说,这些文件比program这个文件建造的时间更晚). 这个动作非常容易,因为操作系统会储存每一个文件最近被修改的时间,你只要下一个指令ls –l就可以看到这个信息. 如果program的建造时间比它所有的必要文件的最近修改时间还要晚,make会决定不再重新建造program这个文件,然后不会发出任何指令就离开(跳回提示符号下). 但是在make下这个决定之前,它还会做一些检查: make会根据附属列所描述的必要文件,去检查每一个 .o文件的必要文件是否有更新的情况.例如,从第3列就可以看出main.o的建造必须依靠main.c. 因此,如果再main.o被建造之后,main.c才又被修改,则make就会去执行第4列的指令重新建造一个新的main.o. 只有在program的必要文件都被检查而且更新过(这必要文件的必要文件也要被检查且更新过. 例如:main.o是program的必要文件,main.c是main.o的必要文件). make 才会去执行第2列的指令建造program这个目标文件. 假设自从上一次建造program这个文件之后,iodat.c是唯一被更新过的文件,所以当我们再次执行$make program之后,make所发出的编译器指令实际上只有cc –c main.ccc –o program main.o iodat.o dorun.o lo.o /usr/fred/lib/crtn.a这两行指令而已.make命令执行以后,会在标准输出上显示出它所发出的指令,因此当你使用make的时候,你可以从你的屏幕上看到它所发出的命令的顺序.总而言之,一个程序的建造包含了顺序正确的指令连接(chain). 一般而言,你只要要求make去建造连接中最后的那个文件即可. make会透过附属文件连接(你在描述文件中所指定的那些必要文件所构成的树状結构构成附属文件连接),自己回朔跟踪(traces back,也就是往树状結构的叶子方向)这个连接,然后找出哪些指令必须被执行. 最后,make会慢慢在连接中前进(moves forward,就是往数状結构的根部移动),执行每个建造目标所必须要有的指令直到目标建立完成(或被更新). 因为这种特性,make是一个使用后序方法(backward-chaining:在人工智能领域中,一种搜索问题答案的方法,它的搜索方向是由目标状态开始,然后向初始状态前进,最后再慢慢回来)这个技巧最有名的例子,这个技巧通常仅使用在像是Prolog语言这一类大家比较不熟悉的环境上.重建最小化(Minimizing Rebuilds)现在我们来讨论一个可以以各种不同版本形式存在的程序(通常是不同平台,或是不同操作系统,或是要分散(release)給不同层级使用者的版本),这是一个可以告诉你make如何节省你的时间,而且可以避免混淆的例子,比前的例子更复杂一点. 假设你写了一个可以绘出文件的程序,它可以在终端(文字模式)或是图形界面(例如:X window)之下执行. 涉及到计算和文件处理的部分在两个版本之中都相同,而且你把它们都存放在basic.c这个文件中. 处理文字模式下使用者输入的程序放在prompt.c之中,而处理图形界面上使用者输入的程序放在window.c之中.因此,这个程序可以以两种不同的版本被发行(release),当你想要建立这个程序时,你可以选择要建立你觉得最适合你现在工作环境的版本. 以文字模式下的版本来说,你可以由basic.c 与prompt.c这两个文件来产生plot_prompt这个可执行文件. 对图形界面的版本来说,你就可以使用basic.c与window.c这两个文件来产生叫做plot_win的可执行文件. 以下产生这两种版本所使用的自述文件:plot_prompt : basic.o prompt.occ –o plot_prompt basic.o prompt.oplot_win : basic.o window.occ –o plot_win basic.o window.obasic.o : basic.ccc –c basic.cprompt.o : prompt.ccc –c prompt.cwindow.0 : window.ccc –c window.c当你第一次建造其中一个可执行文件时,你必须编译basic.c这个文件. 但是只要你没有改变basic.c这个文件,也没有刪除掉basic.o的话,下一次你想要重新产生新的图形界面可执行文件时,就可以不必再重新编译basic.c. 如果你修改了prompt.c,然后重新建立plot_prompt的话,make会去检查修改时间,然后就明白只要重新编译prompt.c,然后再连结就可以了. 也就是说,如果你重新下$make plot_prompt这个指令,你会在屏幕上看到下面的結果:cc –c promptcc –o plot_prompt basic.o prompt.o这这些范例之中的描述文件,实际上可以被大量的简化. 因为make 有內建的规则和宏(macro)的定义可以用来处理在文件中一再重复出现的附属物(dependencies),例如”.o”文件的附属文件”.c”文件,他们都是前面的名称相同,只有副文件名不同而已. 我们会讨论这些make的特色. 在这里,我们只把附属(dependency)和更新(updating)的概念传达給你而已引用make(Invoking make)前面的几个小节的范例都有以下的假设:*工程文件(project file),也就是描述文件,和原始码放在同一个目录底下*描述文件的文件名叫做makefile或是Makefile*將你输入make指令时,工作目录就是这些文件放置的目录有了这些假设,你只要下一个$make target的指令,就可以建立在描述文件中的任何一个目标. 建造这个目标所必须要下的指令都会被显示在终端上,然后执行. 如果一些中间文件(intermediate file)已经存在或者已经被更新过,make会掠过建造这些中间文件的指令. make只会发出建造这个目标所必须执行的最少指令. 如果在上次建造这个目标后,没有任何必要文件被修改或是删除,make会发出一个信息‘target’ is up to date然后什么事情也不做.如果你想要建造在描述文件中没有指定,后置规则(suffix rule)中所讨论的內定规则所蕴涵的目标,例如:你下了一个指令建造一个不存在的目标$make nottarget则make会回应:‘nottarget’ is up to date或是make: Don’t know ho to ma ke nontarget. Stop.如果再目前的工作目录之下真的有nontarget这个文件存在,就会发出上面的第一个信息. 我们可以一次要make建立好几个目标. 这个命令的效果就跟连续的发出好几个make命令相同,例如:$make main.o target就相当于$make main.o$make target一样我们也可以只简单的打上$make没有附上任何的目标名称. 在此情況下,在描述文件中的第一个目标將会被建立(同时他的必要文件也会一起被建立)在命令列下发出make指令有许多的选择项(option,通常前面会加上”-“). 例如,你可以选择不要在终端上显示出make所发出的命令. 反过来说,你也可以要求显示出哪些命令会被执行,而实际上并没有执行它们.语法的基本规则(Basic Rules of Syntax)在你开始要尝试写自己的描述文件之前,你应该了解一些在make所使用的一些难懂的条件(requirement),这些条件如果单独从范例中来体会,是不够不清楚的.最重要的一条规则就是”每一个命令列的开头都要是一个tab字元(四个空格)”. 一个常常犯的错误就是在每个命令列的开头省略了tab字元. 就算在每个命令列中按空白键插入四个空白也不行,因为make无法辨別出这就是tab字元,而且非常不幸的,在这种情況下,就算出了错误,make也无法提供有用的信息.make是靠开头的那个tab字来辨认命令列,所以一定要注意不要在其他不是命令列的那一列之前加上tab字元. 如果你把tab当作第一个字元加在附属列,注解,或这甚至是一个空白列之前,你都会得到错误信息.Tab字元可以用在每一列的任何地方,只有在每一列的第一个字元才有上述的限制.如果你想要检查描述文件中的tab字元,你可以下指令$cat –v –t –e makefile在这里–v 与–t会使得描述文件中的每一个tab字元以^I 的方式显示出来,而–e 会使得每一列的最后以$ 的样子显示出来,所以你可以看出在每一列的結束之前有几个空白.你可以打很长一串指令,如果已经到了文字编辑器的右边界,你可以在到达右边界之前放入一个斜线(\)符号. 你必须确定在新的一列开始之前,会有一个斜线符号在哪里.斜线符号和新的一行之间不要有空白(don’t let any white space slip in between). 由斜线符号所连续的每一列都会被当作单独一列来语法分析(parsing).make会忽略描述文件中的空白行(blank line). 同样的,它也会忽略掉以# 符号开头,到每一列結尾之间的字元,所以# 符号用来当作每个注解的开头.命令列跟附属列不一定都要各自佔掉一列的空间,你可以写成plot_prompt : prompt.o ; cc –o plot_prompt prompt.o虽然之前有说过命令列的开头都要有一个tab字元,不过这里是唯一的例外.一个单独的目标也可以用多个附属列来表示. 当你为了要易于区分附属文件的的种类时,这是一个很实用的技巧,例如file.o : file.ccc –c file.c……file.o : global.h defs.h虽然实际上建造file.o的命令是第一个附属列的下面那一行,即使重新建造时,file.c并没有被修改,可是如果附属的.h文件被修改过的话,file.o仍然会被重新编译.如果你使用了多个附属列的技巧,只有其中一个附属列才能有能够伴随有指令列. 但是如果你在一个附属列中使用了两个冒号,则不在此限.在描述文件中可以有”没有附属文件的目标”(但是冒号还是要打上去,不能省略),这些文件通常不全是文件名. 例如,许多描述文件含有下面的目标,用来幫助程序设计师在一天辛苦的测试之后删除临时文件.clean :/bin/rm –f core *.o当我们下指令$make clean如果工作目录下没有clean这个文件,make就会去执行claen这个项目下的命令脚本(command script). 这是因为make把每一个不存在的目标当作是一个过时的目标在每个项目中的命令,就目前来说,应该要是單一一行的Bourne Shell指令.不要尝试去使用別名(aliases),环境变数(environment variables),或是像if或for这一类会有很多行的命令,同时要避免使用cd,现在你已经能够借由输入你习惯在终端前打的指令来建立你自己的描述文件了. 但是很快的,你会发现非常的乏味. 往后你可简化(simplify)与一般化(generalize)你属于你自己的描述文件的方法.。

synopsis VCS makefile编写

个流程大致步骤都相同都是:Compile,SIM(urg,覆盖#率的分析和采集),debug时主要是跑一个pattern,并dump VPD文件,SIM的同时可以打开DVE视图界面,结束后观察波形,regress主要用#于采集覆盖率,一般要跑多个pattern,这时就无需dump VPD文件(节约时间),由于是debug后有进行的重复运行,所以叫regress(回归)。

# 在我们的验证平台中,若不做代码覆盖率的功能,可以不写regress,只要写debug的流程和跑多个pattern的脚本就好了。

#---------------------------------------------------------------------------------------------------------------------# The DEBUG flow turns on VPD dumping and turns off coverage collection. After # building a testcase using the debug targets, you can debug the TB and the DUT# source code using the testbench debugger and DVE. Of course, you can turn on # coverage metrics and run in debug mode by changing compile and runtime options # in the makefile. These changes are independent of the regression flow so that# the regressions will still run optimally without the interference of VPD dumping.# debug流程打开VPD文件的dump并关闭覆盖率在build了一个包含DUT的testcase后,可以使用VCS的debugger和DVE进行debug。

visual studio 编译 makefile

visual studio 编译makefile 在 Visual Studio 中编译 Makefile 文件通常需要一些额外的步骤,因为 Visual Studio 使用不同的构建系统。

以下是一种可能的方法:1. 使用 Visual Studio 内置工具:•打开 Visual Studio。

•在 "文件" 菜单中,选择 "打开" -> "项目/解决方案",然后选择包含 Makefile 的文件夹。

• Visual Studio 会尝试识别项目并加载。

2. 使用 "Visual Studio Code" 编辑器:•如果您使用Visual Studio Code 编辑器,可以安装"Makefile Tools" 扩展,该扩展支持在 Visual Studio Code 中使用 Makefile 进行构建。

3. 在 Visual Studio 中设置自定义生成命令:•在Visual Studio 中,您可以手动设置生成命令,以执行Makefile。

以下是一些步骤:•在 "项目" 菜单中,选择 "属性"。

•在 "配置属性" 对话框中,选择 "自定义生成步骤"。

•添加自定义命令,例如 make -f Makefile。

•在 "生成事件" 选项卡中,可以配置在生成前或生成后运行的自定义命令。

请注意,这些步骤可能需要根据您的具体情况进行调整。

确保您的项目结构、Makefile 文件和构建系统设置都正确无误。

如果项目依赖于其他库,您还需要确保这些库的头文件和库文件路径正确设置。

如果您使用的是 Visual Studio 内置的项目系统,可能需要将项目迁移到Visual Studio 的本机项目文件(例如 .vcxproj 文件),以便更好地集成 Visual Studio 的构建系统。

makefile 的编写及应用

makefile 的编写及应用Makefile是一种用来管理编译程序的工具,它提供了一种自动化编译的方式,可以根据文件的依赖关系来自动编译相关的文件,从而提高编译的效率。

Makefile的编写通常包括以下几个部分:目标、依赖关系、命令和变量。

一般来说,一个Makefile文件中可以包含多个规则,每个规则由一个或多个目标、依赖关系和命令组成。

其中目标是需要生成的文件,依赖关系是生成目标所需要依赖的其他文件,命令则是生成目标所执行的命令。

一个简单的Makefile示例如下:```# 定义变量CC = gccCFLAGS = -Wall -Wextra# 定义目标和依赖关系target: main.o func.o$(CC) $(CFLAGS) -o target main.o func.omain.o: main.c func.h$(CC) $(CFLAGS) -c main.cfunc.o: func.c func.h$(CC) $(CFLAGS) -c func.c# 定义清理操作clean:rm -f target main.o func.o```在上述示例中,我们定义了两个目标:target和clean。

其中,target这个目标所依赖的是main.o和func.o两个文件,生成目标的命令是使用gcc编译这两个文件,最后生成一个名为target的可执行文件。

clean这个目标用来清理生成的文件。

应用Makefile可以帮助我们自动地完成编译、链接和清理等操作,提高了开发的效率。

可以在命令行中执行`make`命令来根据Makefile文件来生成目标程序,执行`make clean`命令可以清理生成的文件。

总结起来,Makefile的编写及应用包括以下几个步骤:1. 定义变量,用来保存编译器和编译选项等信息;2. 定义目标和依赖关系,用来描述生成文件之间的依赖关系;3. 编写命令,用来执行生成目标的操作;4. 可选地定义清理操作,用来清理生成的文件;5. 在命令行中执行make命令来根据Makefile文件来自动编译生成目标程序。

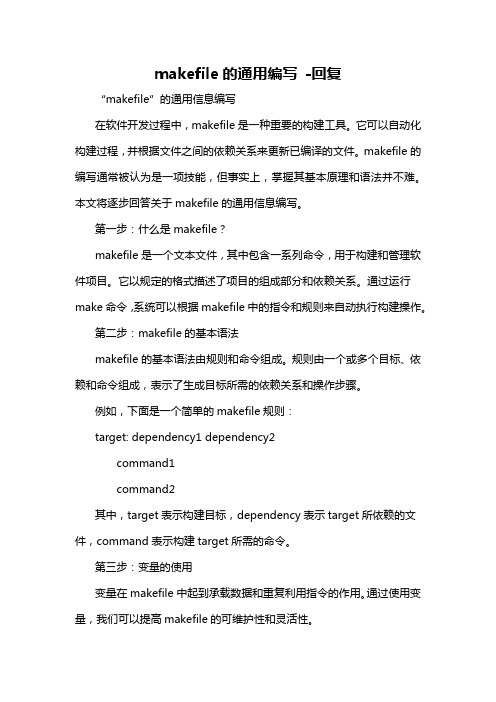

makefile的通用编写 -回复

makefile的通用编写-回复“makefile”的通用信息编写在软件开发过程中,makefile是一种重要的构建工具。

它可以自动化构建过程,并根据文件之间的依赖关系来更新已编译的文件。

makefile的编写通常被认为是一项技能,但事实上,掌握其基本原理和语法并不难。

本文将逐步回答关于makefile的通用信息编写。

第一步:什么是makefile?makefile是一个文本文件,其中包含一系列命令,用于构建和管理软件项目。

它以规定的格式描述了项目的组成部分和依赖关系。

通过运行make命令,系统可以根据makefile中的指令和规则来自动执行构建操作。

第二步:makefile的基本语法makefile的基本语法由规则和命令组成。

规则由一个或多个目标、依赖和命令组成,表示了生成目标所需的依赖关系和操作步骤。

例如,下面是一个简单的makefile规则:target: dependency1 dependency2command1command2其中,target表示构建目标,dependency表示target所依赖的文件,command表示构建target所需的命令。

第三步:变量的使用变量在makefile中起到承载数据和重复利用指令的作用。

通过使用变量,我们可以提高makefile的可维护性和灵活性。

变量的使用分为两个步骤:变量的定义和变量的引用。

例如,下面是一个变量的定义和引用示例:CC = gccCFLAGS = -Wall -O2target: dependency1 dependency2(CC) (CFLAGS) -o target dependency1 dependency2 在上述示例中,CC和CFLAGS分别定义了编译器和编译选项的变量。

在命令中,我们可以通过(CC)和(CFLAGS)来引用这些变量。

第四步:模式匹配规则模式匹配规则允许我们使用通配符来处理多个相似的文件。

它们在处理大型项目时非常有用。

如何编写Makefile,一份由浅入深的Makefile全攻略

如何编写Makefile,⼀份由浅⼊深的Makefile全攻略本⽂转载整理⾃陈浩⼤⼤的⽂章(),由于原⽂内容庞⼤,故梳理出⽬录结构以便于学习及查阅参考。

⼀、概述——什么是makefile?或许很多Winodws的程序员都不知道这个东西,因为那些Windows的IDE都为你做了这个⼯作,但我觉得要作⼀个好的和professional的程序员,makefile还是要懂。

这就好像现在有这么多的HTML的编辑器,但如果你想成为⼀个专业⼈⼠,你还是要了解HTML 的标识的含义。

特别在Unix下的软件编译,你就不能不⾃⼰写makefile了,会不会写makefile,从⼀个侧⾯说明了⼀个⼈是否具备完成⼤型⼯程的能⼒。

因为,makefile关系到了整个⼯程的编译规则。

⼀个⼯程中的源⽂件不计数,其按类型、功能、模块分别放在若⼲个⽬录中,makefile定义了⼀系列的规则来指定,哪些⽂件需要先编译,哪些⽂件需要后编译,哪些⽂件需要重新编译,甚⾄于进⾏更复杂的功能操作,因为makefile就像⼀个Shell脚本⼀样,其中也可以执⾏操作系统的命令。

makefile带来的好处就是——“⾃动化编译”,⼀旦写好,只需要⼀个make命令,整个⼯程完全⾃动编译,极⼤的提⾼了软件开发的效率。

make是⼀个命令⼯具,是⼀个解释makefile中指令的命令⼯具,⼀般来说,⼤多数的IDE都有这个命令,⽐如:Delphi的make,VisualC++的nmake,Linux下GNU的make。

可见,makefile都成为了⼀种在⼯程⽅⾯的编译⽅法。

现在讲述如何写makefile的⽂章⽐较少,这是我想写这篇⽂章的原因。

当然,不同产商的make各不相同,也有不同的语法,但其本质都是在“⽂件依赖性”上做⽂章,这⾥,我仅对GNU的make进⾏讲述,我的环境是RedHat Linux 8.0,make的版本是3.80。

必竟,这个make是应⽤最为⼴泛的,也是⽤得最多的。

Makefile万能通用版(C++和C混合编译也适用)

Makefile万能通用版(C++和C混合编译也适用)

1.、该Makefile 是我自己写的,可用于编译均是.c文件的工程,基本不用修改什么东西。

2、将该文件拷贝到工程文件夹下,在终端执行:

#make create (将会在根目录下创建出include, src, bin 三个目录)

#make 即可编译

#make clean 删除所有生成的中间文件和可执行文件

3、如果需要编译C++的.cpp和C语言的.c文件,即C 、C++混合编译,将CC=gcc 改为CC=g++即可。

(如果还不行,那就需要在.cpp文件的extern “C”中将被调用的.c声明一下,或者将所有.c 文件做成成静态库,后者适合.c文件较多的情况)CC=gcc CFLAGS=-o

PARAM=-Wall

CUR=$(shell pwd)

SRC=$(CUR)/src

SRCS=$(SRC)/*.c

TARGET=$(CUR)/bin/exe

.PHONY:$(TARGET)

all:$(TARGET)

$(TARGET):$(SRCS)

$(CC) $^ $(CFLAGS) $@ $(PARAM)

clean:

@-rm -rf $(TARGET)

@-rm -rf $(CUR)/include/*~

@-rm -rf $(SRC)/*~

@-rm -rf $(CUR)/*~

create:

@-mkdir src/

@-mkdir include/ @-mkdir bin/。

makefile的编写

makefile的编写Makefile是一种文本文件,它描述了如何编译和链接源文件来构建程序。

它包含规则、变量和命令,用于指示编译器怎样工作。

Makefile通常用于编译大型项目,以确保能够快速构建和生成目标文件。

下面我们将分步骤阐述如何编写一个Makefile。

第一步:定义变量在编写Makefile时,我们首先需要定义变量。

变量可以用于存储文件名、目录名、选项、标志等信息。

在Makefile中,为了提高可读性和可维护性,最好把常量值都定义成变量。

变量的定义格式为:变量名=变量值。

例如:```CC = g++CFLAGS = -Wall -O2```上述代码中,CC变量定义为编译器g++,CFLAGS变量定义为编译选项-Wall -O2。

这样,我们在Makefile中就可以直接使用这些变量,而不用每次都输入完整的命令。

第二步:编写规则Makefile中的规则描述了如何生成目标文件。

一般来说,每一条规则包含两部分:目标(target)和依赖关系(dependencies)。

目标是指要生成的文件,依赖关系是指这个文件所依赖的其他文件。

规则的格式为:```target: dependenciescommands```例如:main: main.cpp func.cpp$(CC) $(CFLAGS) -o main main.cpp func.cpp```这条规则表示将main.cpp和func.cpp编译成可执行文件main。

当我们使用make命令时,Makefile会检查main.cpp和func.cpp是否有修改,如果有修改,则重新编译目标文件main。

第三步:定义伪目标伪目标(phony target)用于定义一些没有实际文件对应的操作,例如清理、安装等。

伪目标的语法格式为:```.PHONY: target```例如:```.PHONY: cleanclean:rm -f *.o main```这个规则定义了一个名为clean的伪目标,用于删除所有的目标文件和可执行文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

个流程大致步骤都相同都是:Compile,SIM(urg,覆盖#率的分析和采集),debug时主要是跑一个pattern,并dump VPD文件,SIM的同时可以打开DVE视图界面,结束后观察波形,regress主要用#于采集覆盖率,一般要跑多个pattern,这时就无需dump VPD文件(节约时间),由于是debug后有进行的重复运行,所以叫regress(回归)。

# 在我们的验证平台中,若不做代码覆盖率的功能,可以不写regress,只要写debug的流程和跑多个pattern的脚本就好了。

#---------------------------------------------------------------------------------------------------------------------# The DEBUG flow turns on VPD dumping and turns off coverage collection. After # building a testcase using the debug targets, you can debug the TB and the DUT# source code using the testbench debugger and DVE. Of course, you can turn on # coverage metrics and run in debug mode by changing compile and runtime options # in the makefile. These changes are independent of the regression flow so that# the regressions will still run optimally without the interference of VPD dumping.# debug流程打开VPD文件的dump并关闭覆盖率在build了一个包含DUT的testcase后,可以使用VCS的debugger和DVE进行debug。

当# 然,你也以通过改变makefile文件中的compile和runtime选项参数来开启覆盖率功能。

Debug流程和regress流程是各自独立的,regression# 流程一般不生成VPD。

#--------------------------------------------------------------------------------------------------------------------------------# The REGRESSION flow turns off VPD dumping and turns on Coverage Metrics and TB # coverage collection. This flow is intended to support verification engineers who# are working through the regression process and are interested in coverage# collection and urg.# REGRESSION流程关闭VPD dump并打开Coverage collection功能,该流程是为了支持验证引擎进行“流水线验证“(跑多个testcase)和# 代码覆盖率功能。

??在验证平台中可以将运行多个testcase的脚本命名为regress,运行单个testcase的脚本命名为regone??,这只是# synopsys的模版,我们不必完全遵守,可以不区分debug和regress,然后将是否打开波形和coverage设置成参数。

#-------------------------------------------------------------------------------------------------------------------------------# Command Line make命令行# -----------------# The Makefile supports the following command line# makefile支持下列命令行# % make target_name_* <SEED=xxx> <DEFINES=xxxx># makefile文件放在哪?放在仿真路径。

make [-f makefile文件名][选项][宏定义][目标]# -f 指定makefile 若没有则make程序首先在当前目录查找名为makefile的文件,如果没有找到,它就会转而查找名为Makefile的文件。

# Where target_name is the name of a testcase located in the testdirectory. Every# test in the test directory is named using test_{test_name}. All of the test targets# are listed in the TEST TARGETS section of the makefile.# target_name是test路径下的一个testcase的名字,test路径下的testcase的名字使用test_{test_name}来命名,例如test_1# 所有的test target 都在makefile文件中的TEST TARGETS部分列出#---------------------------------------------------------------------------------------------------------------------------# Compile and Run Testcases 编译与运行testcase# -------------------------------# To compile and run a tescase use the test_* and regress_test_* targets.# 编译与运行testcase,(test_1 就是执行了下面的两个命令先编译在运行)test_1==> compile_1 run_1 详见下面命令定义# % make test_1 // Builds and runs test 1 with VPD dumping 其实就是debug的前边的流程# % make regress_test_1// Builds and runs test 1 with coverage turned on# -------------------------------------------------------------------------------------------------------------------------# Debugging Testcases Debug 实在上面命令之后在进行的# ------------------------# You can use DVE and the testbench debugger to visualize waveforms and testbench # execution. You must first build the testbench using the make compile_* command.# dubug必须是在DVE(VCS的debug工具,与debussy一样的功能)下进行,因为要看波形嘛,但是debug之前必须先compile# % make compile_1 // Builds test 1 for debugging //需要重新编译一次吗?# Once you have built the environment with the proper debug switches, you can use DVE and the testbench debugger.# # testbench debugger 是否是指编译后的那个simv可执行文件呢?其实gui_1 和上面test_1中的run_1是一样的只是增加了-gui项# 即增加了打开gui界面的参数,其他雷同# % make gui_1 // Debug test 1 with DVE# % make tb_gui_1 // Debug test 1 with the testbench debugger# % make both_guis_1 // Debug using both guis# % make pp_1 // Debug using the VPD file VPD文件要在执行simv之后才有吧?# If you want, you can turn on coverage for the DEBUG flow by uncommenting the # coverage flag in the makefile. If you do this, you can still look at coverage.# This may be useful in helping those who are debugging coverage related issues. # 如果在makefile中的debug流程中使用了coverage功能,那么可以使用下面命令观察覆盖率# % make urg // Visualize coverage data from debug runs# -----------------------------------------------------------------------------------------------------------------------------# Regression Testcases# --------------------# Regression tests are used to collect coverage information. To build a testcase# for coverage collection use a command similar to the following.# regress流程主要是为了收集代码覆盖率信息,在执行regress之前需要重新build testcase 类似debug时的compile# % make regress_build_1 // Build and run a regression test with a default seed# Once the test has been built, you can run it again with a new seed.# 与debug不同的是regress需要重新run(使用新的SEED)一下,【还是debug的时候也要run一下?】# % make regress_run_1 SEED=1234# After running one or more regression runs, you can visualize the coverage data # using urg and the following command# run完之后可以用下面命令看代码覆盖率# % make regress_urg#----------------------------------------------------------------------------------------------------------------------------# HOW TO REUSE THIS FILE ON ANOTHER DUT //如何重用该模版# STEP 1: Update the file locations as required //设置file所属的路径# STEP 2: Update the DUT section with directory and source location info//更新模版中DUT部分,指定DUT的路径和include的路径# STEP 3: Update the TB section with directory and source location info//更新模版中TB部分,指定TB的路径和include的路径# STEP 4: Update the Coverage section with name of dut top (eg top.dut)//跟新模版中Coverage部分,指定要测试代码覆盖率的dut的top# STEP 5: Add test targets to the debug and regression targets section//将debug 和regress的target加入模版中对应的部分# STEP 5: Adjust the debug and regression compile and run time arguments//调整debug和regress的compile和runtime的命令参数# STEP 7: Adjust command line options as required//调整命令行命令(后边带百分号和冒号的就表示可以在make命令行中使用的命令)# STEP 8: Update the env class so that it extends dkm_env//更新env class(环境类)使得它可以提供dkm_env# You will need to have a copy of the dkm directory and it should //dkm 是什么?# be located at $(TB_SRC_DIR)/dkm# a) Add [`include "dkm_env.sv"]# b) Add [extends dkm_env] to the environment class definition# c) Call the super.new("name") from the constructor# STEP 9: Run the debug and regression targets# % make testbench_target_* // testbench_target_* 是指test_1之类的testcase#-----------------------------------------------------------------------------看了上文,大家应该可以简单了解这个Makefile的功能了。