三八译码器解读

74HC138三八译码器的应用 - 单片机

74HC138三八译码器的应用 - 单片机在我们设计单片机电路的时候,单片机的IO口数量是有限的,有时并满足不了我们的设计需求,比如我们的STC89C52RC一共是32个IO口,但是我们为了控制更多的器件,就要使用一些外围的数字芯片,这种数字芯片由简单的输入逻辑来控制输出逻辑,比如74HC138这个三八译码器,图1是74HC138在我们原理图上的一个应用。

图174HC138应用原理图从这个名字来分析,三八译码器,就是把3种输入状态翻译成8种输出状态。

从图1所看出来的,74HC138一共有1~6一共是6个输入引脚,但是其中4、5、6这三个引脚是使能引脚。

使能引脚和我们前边讲74HC245的OE引脚是一样的,这三个引脚如果不符合规定的输入要求,Y0到Y7不管你输入的1、2、3引脚是什么电平状态,总是高电平。

所以我们要想这个74HC138正常工作,ENLED那个输入位置必须输入低电平,ADDR3位置必须输入高电平,这两个位置都是使能控制端口。

不知道大家是否记得我们第二课的程序有这么两句ENLED=0;ADDR3=1;就是控制使这个74HC138使能的。

这类逻辑芯片,大多都是有使能引脚的,使能符合要求了,那下面就要研究逻辑控制了。

对于数字器件的引脚,如果一个引脚输入的时候,有0和1两种状态;对于两个引脚输入的时候,就会有00,01,10,11这四种状态了,那么对于3个输入的时候,就会出现8种状态了,大家可以看下边的这个真值表——图,其中输入是A2,A1,A0的顺序,输出是从Y0,Y1....Y7的顺序。

图274HC148真值表从图2可以看出,任一输入状态下,只有一个输出引脚是低电平,其他的引脚都是高电平。

我们清楚的知道,8个LED小灯的总开关三极管Q16基极的控制端是LEDS6,也就是Y6输出一个低电平的时候,可以开通三极管Q16,从右侧的希望输出的结果,我们可以推导出我们的A2,A1,A0的输入状态应该是110,那我们再来看下原理图3。

三八译码器原理

三八译码器原理三八译码器是一种常用的数字电路元件,它可以将三位二进制输入信号转换为八位输出信号。

在数字系统中,三八译码器扮演着重要的角色,它可以将输入的数字信号进行译码,输出对应的信号。

接下来,我们将详细介绍三八译码器的原理及其工作方式。

三八译码器的原理是基于二进制编码的原理。

在二进制编码中,每个数字都有唯一的二进制表示方式。

在三八译码器中,输入信号有三位,输出信号有八位,因此可以表示0-7的数字。

当输入信号为000时,输出信号为00000001;当输入信号为001时,输出信号为00000010;当输入信号为010时,输出信号为00000100;当输入信号为011时,输出信号为00001000;当输入信号为100时,输出信号为00010000;当输入信号为101时,输出信号为00100000;当输入信号为110时,输出信号为01000000;当输入信号为111时,输出信号为10000000。

通过这种方式,三八译码器可以将三位二进制输入信号转换为八位输出信号。

三八译码器的工作方式是通过逻辑门来实现的。

在数字电路中,逻辑门是实现各种逻辑运算的基本元件,包括与门、或门、非门等。

在三八译码器中,通过组合逻辑电路来实现输入信号到输出信号的转换。

通过逻辑门的组合,可以实现不同输入信号到输出信号的映射关系,从而实现译码的功能。

三八译码器在数字系统中有着广泛的应用。

它可以用于将数字信号转换为对应的控制信号,从而控制各种数字设备的工作。

例如,可以将三八译码器与显示器结合,实现对数字显示的控制;可以将三八译码器与存储器结合,实现对存储器的地址选择;可以将三八译码器与逻辑门结合,实现对数字逻辑电路的控制等。

因此,三八译码器在数字系统中具有重要的作用。

总之,三八译码器是一种重要的数字电路元件,它可以将三位二进制输入信号转换为八位输出信号。

通过逻辑门的组合,可以实现输入信号到输出信号的映射关系,从而实现译码的功能。

在数字系统中,三八译码器有着广泛的应用,可以用于控制各种数字设备的工作。

3 8译码器

试验一组合逻辑3线-8线译码器设计试验一、试验目的1、了解并初步掌握ModelSim软件的使用;2、了解使用ModelSim进行组合数字电路设计的一般步骤;3、掌握组合逻辑电路的设计方法;4、掌握组合逻辑电路3线-8线译码器的原理;5、掌握门级建模的方法;二、试验原理译码器(Decoder)的逻辑功能是将每个输入的二进制代码译成对应得输出高、低电平或另外一个代码。

因此,译码是编码的反操作。

常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器等。

二进制译码器的输入是一组二进制代码,输出是一组与输入代码一一对应得高、低电平信号。

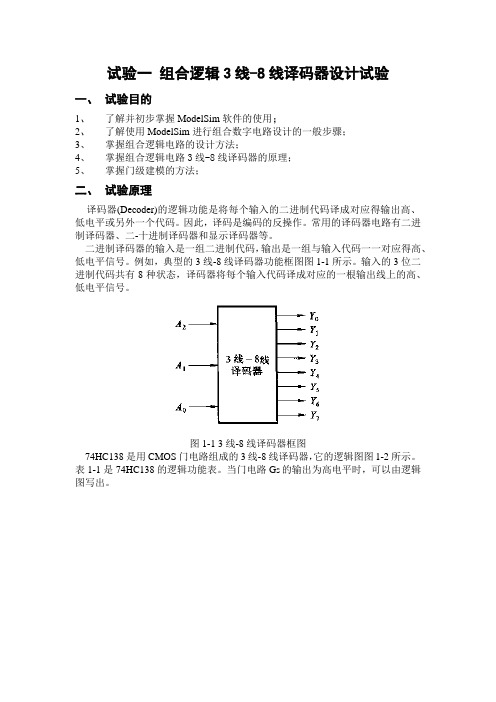

例如,典型的3线-8线译码器功能框图图1-1所示。

输入的3位二进制代码共有8种状态,译码器将每个输入代码译成对应的一根输出线上的高、低电平信号。

图1-1 3线-8线译码器框图74HC138是用CMOS门电路组成的3线-8线译码器,它的逻辑图图1-2所示。

表1-1是74HC138的逻辑功能表。

当门电路G S的输出为高电平时,可以由逻辑图写出。

图1-2 74HC138逻辑功能图表1-1 74HC138逻辑功能表由上式可以看出,由''07Y Y -同时又是210,,A A A 这三个变量的全部最小项的译码输出,所以也将这种译码器称为最小项译码器。

74HC138有3个附加的控制端''123,S S S 和。

当''123S 1,S S 0=+=时,s G 输出为高电平,译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁为高电平。

这3个控制端也称为“片选”输入端,利用片选的作用可以将多片连接起来以扩展译码器的功能;三、 预习要求1、数字电子技术基础组合逻辑电路设计一般设计方法;2、74HC138的逻辑功能;3、门级建模的一般方法和基本语句;4、ModelSim 软件的一般使用方法(ModelSim SE Tutorial);四、 实验步骤(一)、熟悉ModelSim 软件环境 1、建立一个新Project1-1双击左面快捷方式或者电击[程序]/[ModelSim SE 6.1f]/[ModelSim]启动ModelSim 6.1(如图1-3);注意:必须首先关闭IMPORTANT Information 对话框才能开始其它操作;图1-31-2 [File]/[New]/[Project…]新建一个project,会弹出Create Project对话框(如图1-4);图1-4⏹Project Name(项目名称)需要填入你所建立的项目的名称;⏹指定项目所在路径;如果所指定的目录不存在,会弹出对话框提示是否建立这个目录;一般选择是;⏹缺省的工作库名;注意:1、路径一般不应包含汉字;2、逻辑应在ModelSim的安装目录下指定;3、缺省的工作库的名称一般不需要改动;2、载入HDL元文件2-1设定好1-2步骤的每项内容后,点击OK,弹出Add items to the Projects对话框;如图1-5所示。

38译码器原理

38译码器原理38译码器是一种常见的数字逻辑电路,它在数字系统中扮演着十分重要的角色。

它能够将输入的数字信号进行解码,输出对应的控制信号,从而实现不同功能的控制。

本文将对38译码器的原理进行介绍,希望能够帮助读者更好地理解和应用这一电路。

首先,我们来看一下38译码器的基本结构。

38译码器由三个输入端和八个输出端组成,输入端共有三位,输出端共有八位。

在输入端,我们可以输入0至7的数字信号;而在输出端,每个输出端对应一个特定的数字信号。

当输入端接收到某一数字信号时,对应的输出端将会输出高电平信号,而其他输出端则输出低电平信号。

接下来,我们来详细了解38译码器的工作原理。

当输入端接收到一个数字信号时,比如输入为3,那么在输出端,对应的第3个输出端将会输出高电平信号,而其他输出端则输出低电平信号。

这样,我们就可以根据输入端的信号来控制对应的输出端,实现不同功能的控制。

在实际应用中,38译码器通常被用于数字系统中的地址译码和显示控制等方面。

在地址译码中,它可以根据输入的地址信号来选择对应的存储单元或外设,实现对存储器或外设的控制和访问。

而在显示控制中,它可以根据输入的数字信号来控制七段数码管等显示设备,实现数字信息的显示和输出。

除此之外,38译码器还可以与其他逻辑电路相结合,实现更复杂的逻辑功能。

比如,它可以与门电路、触发器等组合,构成各种数字逻辑电路,满足不同的应用需求。

因此,熟练掌握38译码器的原理和应用对于数字系统的设计和实现至关重要。

总的来说,38译码器作为一种常见的数字逻辑电路,具有解码输入信号并输出对应控制信号的功能,其原理和应用十分重要。

通过本文的介绍,相信读者对38译码器有了更深入的了解,希望能够对读者在数字系统设计和应用中起到一定的帮助。

希望本文能够帮助读者更好地理解38译码器的原理和应用,同时也希望读者能够在实际应用中灵活运用这一电路,为数字系统的设计和实现提供帮助。

三八译码器

三八译码器预备知识三八译码器是一种常用的译码器一译码器知识1 译码是编码的逆过程,在编码时,每一种二进制代码,都赋予了特定的含义,即都表示了一个确定的信号或者对象。

把代码状态的特定含义“翻译”出来的过程叫做译码,实现译码操作的电路称为译码器。

或者说,译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

2 译码器是组合逻辑电路的一个重要的器件3 译码器是一种具有“翻译”功能的逻辑电路,这种电路能将输入二进制代码的各种状态,按照其原意翻译成对应的输出信号。

有一些译码器设有一个和多个使能控制输入端,又成为片选端,用来控制允许译码或禁止译码。

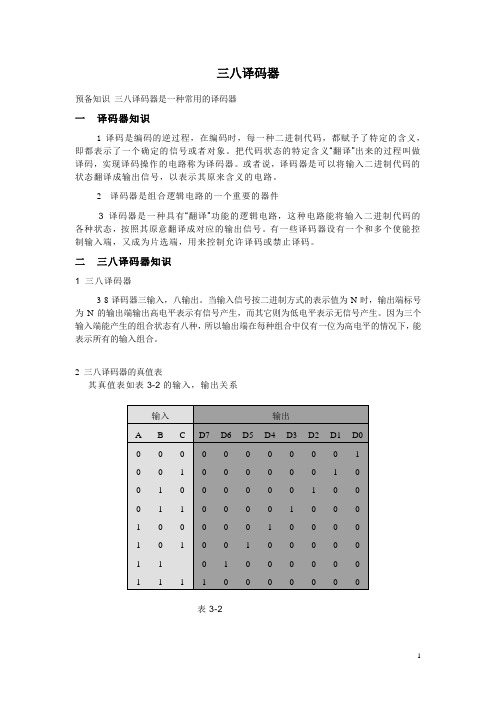

二三八译码器知识1 三八译码器3-8译码器三输入,八输出。

当输入信号按二进制方式的表示值为N时,输出端标号为N的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。

2 三八译码器的真值表其真值表如表3-2的输入,输出关系输入输出A B C D7 D6 D5 D4 D3 D2 D1 D00 0 0 0 0 0 0 0 0 0 10 0 1 0 0 0 0 0 0 1 00 1 0 0 0 0 0 0 1 0 00 1 1 0 0 0 0 1 0 0 01 0 0 0 0 0 1 0 0 0 01 0 1 0 0 1 0 0 0 0 01 1 0 1 0 0 0 0 0 01 1 1 1 0 0 0 0 0 0 0表3-23电路中的实现本电路图中,有三个输入A,B,C及八个输出D0-D7,其输入,输出关系如表3-24 现象的体现在本实验中,用三个拨动开关来表示三八译码器的三个输入(A、B、C);用八个LED 来表示三八译码器的八个输出(D0-D7)。

通过输入不同的值来观察输入的结果与三八译码器的真值表(表3-2)是否一致。

实验箱中的拨动开关与FPGA的接口电路如下图3-3所示,当开关闭合(拨动开关的档位在下方)时其输出为低电平,反之输出高电平。

38译码器

实验五 译码器、数据选择器及其应用一、实验目的1.掌握中规模集成译码器、数据选择器的逻辑功能和使用方法。

2.了解译码器的应用。

3.学习用数据选择器构成组合逻辑电路的方法。

二、实验原理1.译码器是将输入的具有特定含义的二进制代码翻译成输出信号的不同组合,实现电路控制功能的逻辑电路。

译码器在数字系统中应用广泛,可用于代码的转换、终端数字的显示、数据的分配等等。

译码器可分为变量译码器和显示译码器。

74LS138是目前常用的三线——八线译码器(变量译码器),它有三根输入线,可以输入三位二进制数码,共有八种状态组合,即可译出8个输出信号。

管脚图如图1所示。

该集成芯片共有16个引脚,其中8脚应接地线,16脚接+5V 电源,脚0A 、1A 、2A 为二进制编码输入端(2A 为高位,0A 为低位);0Y ~7Y 为译码输出端(7Y 为高位,0Y 为低位),1E 、A E 2、B E 2为信号输入允许端,也称使能端。

A E 2、B E 2为低电平有效(图中用管脚处的圆圈来表示低电平有效),1E 为高电平有效。

只有信号输入允许端有效时输入的信号才有效,才可能实现译码。

74LS138的功能见表一。

图1 74LS138管脚和符号图表一 74LS138的逻辑功能2.74LS138可用作函数信号发生器,如图2所示,实现的逻辑函数是ABC C B A C B A C B A Z +++= 图23.数据选择器又叫“多路开关”。

数据选择器在选择控制电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。

数据选择器的功能类似一个多掷开关,,如图3所示,图中有四路数据0D ~3D ,通过选择从控制信号1A 、0A 从四路数据中选中某一路数据送至输出端W 。

数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别。

8选1数据选择器74LS151:74LS151引脚排列如图3,功能如表二。

3-8译码器原理

3-8译码器原理3-8译码器是一种数字电路,它将一个3位二进制数转换为8个输出信号之一。

它的原理是基于布尔代数和逻辑门电路实现的。

下面将详细介绍3-8译码器的原理。

3-8译码器由三个输入引脚和八个输出引脚组成。

输入引脚是A0、A1和A2,它们可以是0或1。

输出引脚是Y0到Y7,它们中的一个会被激活,其它的则处于非激活状态。

当输入引脚的二进制值为000时,输出引脚Y0会被激活。

当输入引脚的二进制值为001时,输出引脚Y1会被激活,以此类推,直到输入引脚的二进制值为111时,输出引脚Y7会被激活。

3-8译码器的实现基于布尔代数和逻辑门电路。

首先,使用Karnaugh图或真值表来确定每个输出引脚的布尔表达式。

然后,使用逻辑门电路来实现这些布尔表达式。

在3-8译码器中,使用了AND门、NOT门和OR门。

对于每个输出引脚,都需要一个布尔表达式。

例如,对于输出引脚Y0,其布尔表达式为:Y0 = A2' A1' A0'其中,A2'表示A2的反相,A1'表示A1的反相,A0'表示A0的反相。

这个布尔表达式表示当A2、A1和A0都为0时,Y0会被激活。

对于每个布尔表达式,都需要使用逻辑门电路来实现。

例如,对于Y0的布尔表达式,可以使用三个NOT门和一个AND门来实现。

首先,使用三个NOT门来反相A2、A1和A0,然后将它们的输出连接到一个AND门的输入引脚上。

当A2、A1和A0都为0时,三个NOT门的输出都为1,这样AND门的输出就会变为1,从而激活Y0。

3-8译码器的原理基于布尔代数和逻辑门电路实现。

它可以将一个3位二进制数转换为8个输出信号之一。

对于每个输出引脚,都需要一个布尔表达式和一个逻辑门电路来实现。

3-8译码器在数字电路中有广泛的应用,例如在计算机内存芯片中用于选择特定的存储单元。

38译码器原理

38译码器原理

38译码器是一种常用的数字电路,用于将二进制编码信号转

换成十进制输出信号。

它包含3个输入引脚(A, B, C)和8个输出引脚(Y0 - Y7),每个输入引脚都对应一个比特位。

这样,通过输入不同的二进制编码,译码器可以将其转换成对应的十进制输出。

译码器的工作原理基于二进制编码和权重的概念。

对于3位二进制编码来说,最低位(LSB)对应权重为2^0的位,次低位

对应权重为2^1的位,最高位(MSB)对应权重为2^2的位。

因此,一个3位二进制编码可以表示的十进制数的范围为0到7。

当输入的二进制编码与其权重对应的比特位值相等时,相应的输出引脚会输出高电平(逻辑1),其他输出引脚都输出低电

平(逻辑0)。

例如,当输入为二进制编码“011”时,输出引

脚Y1和Y2会输出高电平,其他引脚输出低电平。

这样,我

们可以通过读取输出引脚的状态来获取对应的十进制输出。

总结来说,38译码器将3位的二进制编码信号转换成一个10

进制数字输出。

它的工作原理是根据输入信号的比特位值和权重来决定输出引脚的状态。

这种译码器在数字电路中应用广泛,可用于计算、显示和控制等各种应用场合。

38译码器的工作原理

38译码器的工作原理

38译码器是一种数字电路,用于将输入的二进制代码转换为相应的输出信号。

它的工作原理如下:

1. 输入信号:38译码器通常有5个输入引脚,标记为A0、A1、A2、A3和A4。

这些引脚接收二进制代码作为输入信号。

每个引脚可以接收0或1的电平。

2. 译码功能:根据输入信号的组合,38译码器将选择性地激活其输出引脚之一或多个。

输出引脚的数量取决于译码器的类型。

3. 输出信号:38译码器通常有8个输出引脚,标记为Y0、Y1、Y2、Y3、Y4、Y5、Y6和Y7。

这些引脚可以输出高电平(1)或低电平(0),具体取决于输入信号的组合。

4. 真值表:为了理解38译码器的工作原理,可以查看其真值表。

真值表列出了所有可能的输入组合及其对应的输出。

通过观察真值表,可以确定输入信号与输出信号之间的关系。

总结起来,38译码器的工作原理是根据输入信号的组合选择性地激活输出引脚,将输入的二进制代码转换为相应的输出信号。

tanner pro 3-8译码器课程设计

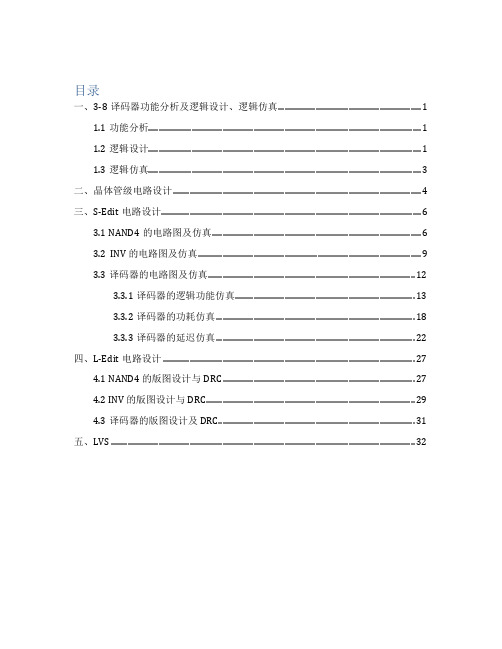

目录一、3-8译码器功能分析及逻辑设计、逻辑仿真 (1)1.1功能分析 (1)1.2逻辑设计 (1)1.3逻辑仿真 (3)二、晶体管级电路设计 (4)三、S-Edit电路设计 (6)3.1 NAND4的电路图及仿真 (6)3.2 INV 的电路图及仿真 (9)3.3译码器的电路图及仿真 (12)3.3.1译码器的逻辑功能仿真 (13)3.3.2译码器的功耗仿真 (18)3.3.3译码器的延迟仿真 (22)四、L-Edit电路设计 (27)4.1 NAND4 的版图设计与DRC (27)4.2 INV 的版图设计与DRC (29)4.3译码器的版图设计及DRC (31)五、LVS (32)一、3-8译码器功能分析及逻辑设计、逻辑仿真1.1功能分析3-8 译码器的输入是 3 个口 , 输出是 8 个口。

如果输入是 101 那么就是第 5 个口为低电平,表示二进制数是 5 。

3-8 译码器的功能就是把输入的 3 位 2 进制数翻译成 10 进制的输出。

3-8译码器具有3个数据输入端A2、A1和A0,1个片选输入端C S,8个数据输出端Y0~Y7,实现数据输入端到输出端的译码逻辑功能,片选端C S低电平有效。

1.2逻辑设计各个输出口的逻辑表达式如下:Y0=C S A2 A1 A0Y1=C S A2 A1 A0Y2=C S A2 A1 A0Y3=C S A2 A1 A0Y4=C S A2 A1 A0Y5=C S A2 A1 A0Y6=C S A2 A1 A0Y7=C S A2 A1 A0表1.2.1为译码器真值表。

表1.2.1 3-8译码器真值表根据 3-8 译码器的逻辑表达式及真值表,在quartus2设计出相应的电路原理图,如图 1.2.1所示。

图1.2.1 quartus2原理图1.3逻辑仿真在quartus2中对刚刚画出的3-8译码器进行仿真,设置仿真时长为16ns,Cs 周期为16ns,A2周期为8ns,A1周期为4ns,A0周期为2ns。

EDA课程设计-3-8译码器

第一章绪论1.1 EDA技术介绍EDA(Electronic Design Automation)技术是现代电子工程领域的一门新技术。

基于可编程逻辑器件的数字系统EDA技术可以简单概括为以大规模可编程逻辑器件为设计载体,通过硬件描述语言输入给相应开发软件,经过编译和仿真,最终下载到设计载体中,从而实现系统电路。

在数字系统中,能将二进制代码翻译成所表示信息的电路称为译码器。

译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

而常用的译码器有二进制译码器,二—十进制译码器和显示译码器。

译码器可分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n 个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

本次课程设计的题目为3-8译码器。

要求用掌握3-8译码器的构成、原理与设计方法;熟悉quartus60软件的使用方法;能用VHDL语言设计3-8译码器电路;并仿真出3—8译码器的功能。

第二章 3—8译码器2.1 3—8译码器介绍译码器属于组合逻辑电路,它的逻辑功能是将二进制代码按其编码时的原意译成对应的输出高、底电平信号,又叫解码器。

在数字电子技术中,它具有非常重要的地位,应用也很广泛。

它除了常为其它集成电路产生片选信号之外,还可以作为数据分配器、函数发生器用,而且在组合逻辑电路设计中它可替代繁多的逻辑门,简化设计电路。

这次我们运用的3 线-8 线译码器就是一个典型例子。

38译码器为3 线-8 线译码器,共有 54/74S138和 54/74LS138 两种线路结构型式,其主要电特性的典型值如下:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

3-8译码器设计

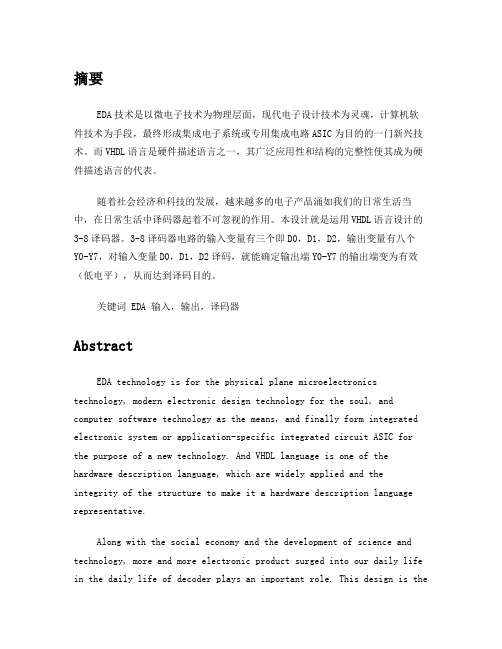

摘要EDA技术是以微电子技术为物理层面,现代电子设计技术为灵魂,计算机软件技术为手段,最终形成集成电子系统或专用集成电路ASIC为目的的一门新兴技术。

而VHDL语言是硬件描述语言之一,其广泛应用性和结构的完整性使其成为硬件描述语言的代表。

随着社会经济和科技的发展,越来越多的电子产品涌如我们的日常生活当中,在日常生活中译码器起着不可忽视的作用。

本设计就是运用VHDL语言设计的3-8译码器。

3-8译码器电路的输入变量有三个即D0,D1,D2,输出变量有八个Y0-Y7,对输入变量D0,D1,D2译码,就能确定输出端Y0-Y7的输出端变为有效(低电平),从而达到译码目的。

关键词 EDA 输入,输出,译码器AbstractEDA technology is for the physical plane microelectronics technology, modern electronic design technology for the soul, and computer software technology as the means, and finally form integrated electronic system or application-specific integrated circuit ASIC for the purpose of a new technology. And VHDL language is one of the hardware description language, which are widely applied and theintegrity of the structure to make it a hardware description language representative.Along with the social economy and the development of science and technology, more and more electronic product surged into our daily life in the daily life of decoder plays an important role. This design is theuse of the design of 3-VHDL language 8 decoder. 3-8 decoder circuit, input variables have three namely D0, D1, D2, output variable has eight Y0-Y7, D0 to input variables, D1, D2 decoding, can determine the output, the output terminal of the Y0-Y7 into effective (low level), so as to achieve the purpose decoding.Key word EDA input output decode目录引言EDA(Electronic Design Automation)技术是现代电子工程领域的一门新技术。

EDA设计38译码器

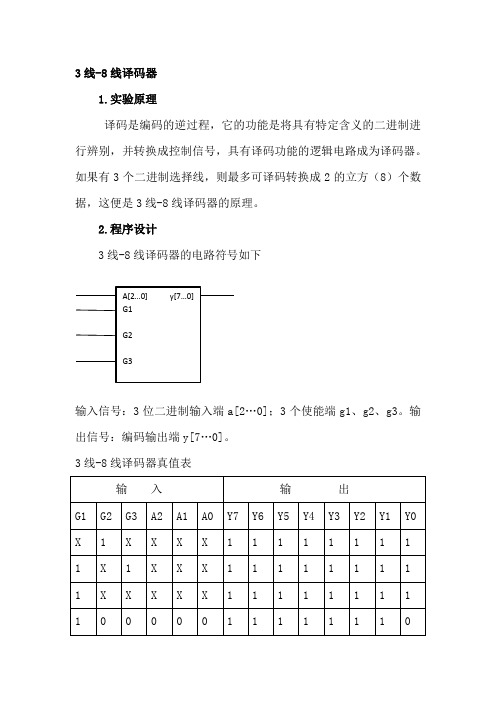

3线-8线译码器

1.实验原理

译码是编码的逆过程,它的功能是将具有特定含义的二进制进行辨别,并转换成控制信号,具有译码功能的逻辑电路成为译码器。

如果有3个二进制选择线,则最多可译码转换成2的立方(8)个数据,这便是3线-8线译码器的原理。

2.程序设计

3线-8线译码器的电路符号如下

输入信号:3位二进制输入端a[2…0];3个使能端g1、g2、g3。

输出信号:编码输出端y[7…0]。

3线-8线译码器真值表

3.仿真实验

Verilog HDL代码如下:

module decoder3_8(y,a,g1,g2,g3);

output[7:0] y;

input[2:0] a;

input g1,g2,g3;

reg[7:0] y;

always@(a or g1 or g2 or g3)

begin

if(g1==0)y=8'b11111111;

else if(g2==1)y=8'b11111111;

else if(g3==1)y=8'b11111111;

else

begin

y=8'b00000001<<a;

y=~y;

end

end

endmodule

建立波形编辑文件进行功能仿真,仿真结果如下图所示

生成的RTL电路如下

实验总结。

用多种方法描述3_8译码器

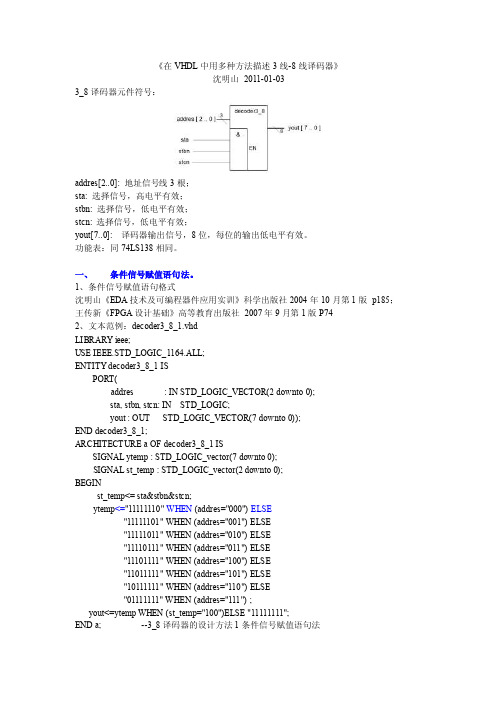

《在VHDL中用多种方法描述3线-8线译码器》沈明山2011-01-033_8译码器元件符号:addres[2..0]: 地址信号线3根;sta: 选择信号,高电平有效;stbn: 选择信号,低电平有效;stcn:选择信号,低电平有效;yout[7..0]: 译码器输出信号,8位,每位的输出低电平有效。

功能表:同74LS138相同。

一、条件信号赋值语句法。

1、条件信号赋值语句格式沈明山《EDA技术及可编程器件应用实训》科学出版社2004年10月第1版p185;王传新《FPGA设计基础》高等教育出版社2007年9月第1版P742、文本范例:decoder3_8_1.vhdLIBRARY ieee;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder3_8_1 ISPORT(addres : IN STD_LOGIC_VECTOR(2 downto 0);sta, stbn, stcn: IN STD_LOGIC;yout : OUT STD_LOGIC_VECTOR(7 downto 0));END decoder3_8_1;ARCHITECTURE a OF decoder3_8_1 ISSIGNAL ytemp : STD_LOGIC_vector(7 downto 0);SIGNAL st_temp : STD_LOGIC_vector(2 downto 0);BEGINst_temp<= sta&stbn&stcn;ytemp<="11111110" WHEN (addres="000") ELSE"11111101" WHEN (addres="001") ELSE"11111011" WHEN (addres="010") ELSE"11110111" WHEN (addres="011") ELSE"11101111" WHEN (addres="100") ELSE"11011111" WHEN (addres="101") ELSE"10111111" WHEN (addres="110") ELSE"01111111" WHEN (addres="111") ;yout<=ytemp WHEN (st_temp="100")ELSE "11111111";END a; --3_8译码器的设计方法1条件信号赋值语句法3、仿真波形图二、选择信号赋值语句法1、选择信号赋值语句格式沈明山《EDA技术及可编程器件应用实训》科学出版社2004年10月第1版p185;王传新《FPGA设计基础》高等教育出版社2007年9月第1版P742、文本范例:decoder3_8_2.vhdLIBRARY ieee;USE IEEE.STD_LOGIC_1164.ALL;ENTITY decoder3_8_2 ISPORT(addres : IN STD_LOGIC_VECTOR(2 downto 0);sta,stbn,stcn: IN STD_LOGIC;yout : OUT STD_LOGIC_VECTOR(7 downto 0));END decoder3_8_2;ARCHITECTURE a OF decoder3_8_2 ISSIGNAL ytemp : STD_LOGIC_vector(7 downto 0);SIGNAL st_temp : STD_LOGIC_vector(2 downto 0);BEGINst_temp<= sta&stbn&stcn;WITH addres SELECTytemp<="11111110" WHEN "000","11111101" WHEN "001","11111011" WHEN "010","11110111" WHEN "011","11101111" WHEN "100","11011111" WHEN "101","10111111" WHEN "110","01111111" WHEN "111","11111111" WHEN OTHERS; --必须加此句,以便对U、Z等情况做出限定yout<=ytemp WHEN (st_temp="100")ELSE "11111111";END a; --3_8译码器的设计方法2:选择信号赋值法。

实验一 3-8译码器的设计

1 2 3

ห้องสมุดไป่ตู้任务分析: 任务分析:电路工作原理

知识准备:基于PLD的电路设计流程 知识准备:基于PLD的电路设计流程 PLD

任务实施: 任务实施:图形输入法实施步骤

1

一、任务分析:三八译码器工作原理 任务分析: 译码是编码的逆过程, 译码是编码的逆过程,它的功能是将具有特 定含义的二进制码进行辨别,并转换成控制信号, 定含义的二进制码进行辨别,并转换成控制信号, 具有译码功能的逻辑电路称为译码器。 具有译码功能的逻辑电路称为译码器。 三八译码器属于二进制译码器,即它具有N 三八译码器属于二进制译码器,即它具有N 个输入端, 个输出端和一个使能输入端。 个输入端,2n个输出端和一个使能输入端。在使 能输入端为有效电平时,对应每一组输入代码, 能输入端为有效电平时,对应每一组输入代码, 只有其中一个输出端为有效电平, 只有其中一个输出端为有效电平,其余输出端则 为非有效电平。下图为三八译码器的真值表。 为非有效电平。下图为三八译码器的真值表。

6

3、仿真:仿真包括功能仿真、时序仿真和定时分析, 、仿真:仿真包括功能仿真、时序仿真和定时分析, 可以利用软件的仿真功能来验证设计项目的逻辑功能 是否正确。 是否正确。

4、编程与验证:用经过仿真确认后的编程文件通过编 、编程与验证: 程器( 程器(Programmer)将设计下载到实际芯片中,最 )将设计下载到实际芯片中, 后测试芯片在系统中的实际运行性能。 后测试芯片在系统中的实际运行性能。

4、设计输入 1)放置器件在原理图上 在原理图的空白处双击鼠标左键,出现下图: a、在原理图的空白处双击鼠标左键,出现下图:

b、在光标处输入元件名称(如:input, input, 在光标处输入元件名称( output,and2,and3,nand2,or2,not,xor, output,and2,and3,nand2,or2,not,xor, dff等 或用鼠标点击库元件,按下OK即可。 OK即可 dff等)或用鼠标点击库元件,按下OK即可。 如果安放相同的元件,只要按住Ctrl Ctrl键 c、如果安放相同的元件,只要按住Ctrl键, 同时用鼠标按左键拖动该元件复制即可。 同时用鼠标按左键拖动该元件复制即可。 一个完整的电路包括:输入端口input input、 d、一个完整的电路包括:输入端口input、 电路元件集合、输出端口output。 电路元件集合、输出端口output output。 e、下图为3-8译码器元件安放结果。 下图为3 译码器元件安放结果。

方案一3-8译码器

方案一3-8译码器译码器和编码器译码器(Decoder)和编码器(Encoder)是数字系统中广泛使用的多输入多输出组合逻辑部件。

一. 译码器译码器的功能是对具有特定含义的输入代码进行"翻译",将其转换成相应的输出信号。

译码器的种类很多,常见的有二进制译码器、二-十进制译码器和数字显示译码器。

1.二进制译码器(1) 定义二进制译码器:能将n个输入变量变换成2n个输出函数,且输出函数与输入变量构成的最小项具有对应关系的一种多输出组合逻辑电路。

(2) 特点●二进制译码器一般具有n个输入端、2n个输出端和一个(或多个)使能输入端。

●在使能输入端为有效电平时,对应每一组输入代码,仅一个输出端为有效电平,其余输出端为无效电平(与有效电平相反)。

●有效电平可以是高电平(称为高电平译码),也可以是低电平(称为低电平译码)。

(3) 典型芯片常见的MSI二进制译码器有2-4线(2输入4输出)译码器、3-8线(3输入8输出)译码器和4-16线(4输入16输出)译码器等。

图7.7(a)、(b)所示分别是T4138型3-8线译码器的管脚排列图和逻辑符号。

数字显示译码器是驱动显示器件(如荧光数码管、液晶数码管等)的核心部件,它可以将输入代码转换成相应数字,并在数码管上显示出来。

常用的数码管由七段或八段构成字形,与其相对应的有七段数字显示译码器和八段数字显示译码器。

例如,中规模集成电路74LS47,是一种常用的七段显示译码器,该电路的输出为低电平有效,即输出为0时,对应字段点亮;输出为1时对应字段熄灭。

该译码器能够驱动七段显示器显示0~15共16个数字的字形。

输入A3、A2、A1和A0接收4位二进制码,输出Q a、Q b、Q c、Q d、Q e、Q f和Q g分别驱动七段显示器的a、b、c、d、e、f和g段。

(74LS47逻辑图和真值表可参见教材中有关部分。

)七段译码显示原理图如图7.8(a)所示,图7.8(b)给出了七段显示笔画与0~15共16个数字的对应关系。

实验五 3-8线译码器

实验五 3-8线译码器一、实验目的1、熟悉常用译码器的功能逻辑。

2、掌握复杂译码器的设计方法。

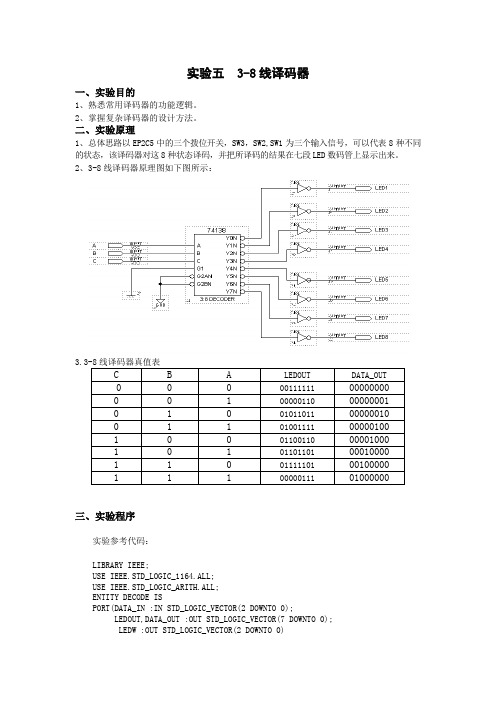

二、实验原理1、总体思路以EP2C5中的三个拨位开关,SW3,SW2,SW1为三个输入信号,可以代表8种不同的状态,该译码器对这8种状态译码,并把所译码的结果在七段LED数码管上显示出来。

2、3-8线译码器原理图如下图所示:三、实验程序实验参考代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;ENTITY DECODE ISPORT(DATA_IN :IN STD_LOGIC_VECTOR(2 DOWNTO 0);LEDOUT,DATA_OUT :OUT STD_LOGIC_VECTOR(7 DOWNTO 0);LEDW :OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END DECODE;ARCHITECTURE ADO OF DECODE ISSIGNAL OUTA,D_OUT : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGINLEDW<="000";PROCESS (DATA_IN)VARIABLE DIN: STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINDIN:=DATA_IN;LEDOUT<=OUTA;DATA_OUT<=D_OUT;CASE DIN ISwhen "000" => OUTA<="00111111" ; --"0"when "001" => outa<="00000110" ; --"1"when "010" => outa<="01011011"; --"2"when "011" => outa<="01001111"; --"3"when "100" => outa<="01100110"; --"4"when "101" => outa<="01101101"; --"5"when "110" => outa<="01111101"; --"6"when "111" => outa<="00000111"; --"7"WHEN OTHERS => OUTA<="XXXXXXXX";END CASE;CASE DIN ISWHEN "000" => D_OUT<="00000000";WHEN "001" => D_OUT<="00000001";WHEN "010" => D_OUT<="00000010";WHEN "011" => D_OUT<="00000100";WHEN "100" => D_OUT<="00001000";WHEN "101" => D_OUT<="00010000";WHEN "110" => D_OUT<="00100000";WHEN "111" => D_OUT<="01000000";WHEN OTHERS=> D_OUT<="XXXXXXXX";END CASE;END PROCESS;END ADO;四、实验步骤1、打开Quartus II,选择“File”菜单下的“New Project Wizard”,建立Project及顶层实体的名称为ADO,期间,选择的目标芯片为EP2C5Q208C8N;2、选择“File”菜单下的“New”命令,在“New”窗口中选择“VHDL Files”,输入程序,进行编译;3、选择“File”菜单中的“New”项,在“New”窗口中选择“Other Files”中的“VectorWaveform File”项,打开空白的波形编辑器,输入所有的信号节点,给输入随机赋值,保存,单击工具栏上的快捷方式,进行波形仿真;4、打开“Assignments”菜单下的“Pins”命令,打开引脚锁定窗口,进行引脚锁定,再次对VHDL Files进行编译;5、连接EDA实验箱,将EP2C5适配板左下角的JTAG用十芯排线和万用下载区左下角的SOPC JTAG 口连接起来,万用下载区右下角的电源开关拨到 SOPC下载的一边,将JPLED1短路帽右插,JPLED的短路帽全部上插,请将JP103的短路帽全部插上。

138译码器 文档

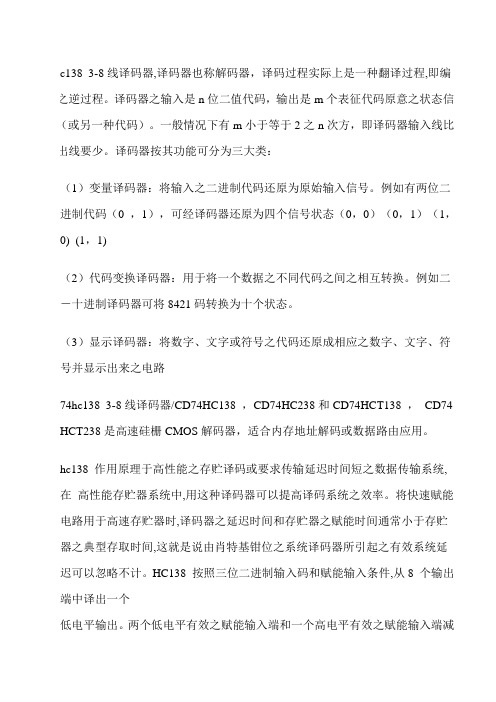

74h c138 3-8线译码器,译码器也称解码器,译码过程实际上是一种翻译过程,即编码之逆过程。

译码器之输入是n位二值代码,输出是m个表征代码原意之状态信号(或另一种代码)。

一般情况下有m小于等于2之n次方,即译码器输入线比输出线要少。

译码器按其功能可分为三大类:(1)变量译码器:将输入之二进制代码还原为原始输入信号。

例如有两位二进制代码(0 ,1),可经译码器还原为四个信号状态(0,0)(0,1)(1,0) (1,1)(2)代码变换译码器:用于将一个数据之不同代码之间之相互转换。

例如二-十进制译码器可将8421码转换为十个状态。

(3)显示译码器:将数字、文字或符号之代码还原成相应之数字、文字、符号并显示出来之电路74hc138 3-8线译码器/CD74HC138 ,CD74HC238和CD74HCT138 ,CD74 HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

hc138 作用原理于高性能之存贮译码或要求传输延迟时间短之数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统之效率。

将快速赋能电路用于高速存贮器时,译码器之延迟时间和存贮器之赋能时间通常小于存贮器之典型存取时间,这就是说由肖特基钳位之系统译码器所引起之有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效之赋能输入端和一个高电平有效之赋能输入端减少了扩展所需要之外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

图1 引脚图图2 功能图图3 测试电路和波形应用电路:图4 舞台发光二极管灯光图5 可编程时钟定时器电路由上表可见74HC138译码器输出低电平有效。

为增加译码器功能,除三个输入端C、 B、 A 外,还设置了G1、/G2A,/G2B,使译码器具有较强之抗干扰能力且便于扩展。

方案一38译码器

译码器和编码器译码器(Decoder)和编码器(Encoder)是数字系统中广泛使用的多输入多输出组合逻辑部件。

一. 译码器译码器的功能是对具有特定含义的输入代码进行"翻译",将其转换成相应的输出信号。

译码器的种类很多,常见的有二进制译码器、二-十进制译码器和数字显示译码器。

1.二进制译码器(1) 定义二进制译码器:能将n个输入变量变换成2n个输出函数,且输出函数与输入变量构成的最小项具有对应关系的一种多输出组合逻辑电路。

(2) 特点●二进制译码器一般具有n个输入端、2n个输出端和一个(或多个)使能输入端。

●在使能输入端为有效电平时,对应每一组输入代码,仅一个输出端为有效电平,其余输出端为无效电平(与有效电平相反)。

●有效电平可以是高电平(称为高电平译码),也可以是低电平(称为低电平译码)。

(3) 典型芯片常见的MSI二进制译码器有2-4线(2输入4输出)译码器、3-8线(3输入8输出)译码器和4-16线(4输入16输出)译码器等。

图7.7(a)、(b)所示分别是T4138型3-8线译码器的管脚排列图和逻辑符号。

图7.7 T4138译码器的管脚排列图和逻辑符图中, A2、A1、A0 ------ 输入端;Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7------- 输出端;S1,S2,S3 -------- 使能端,作用是禁止或选通译码器。

该译码器真值表如表7.1所示。

表7.1 T4138译码器真值表输入S1 S2+S3 A2 A1 A0输出Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y71 0 0 0 0 1 0 0 0 1 1 0 0 1 0 1 0 0 1 1 1 0 1 0 0 1 0 1 0 1 0 1 1 1 1 1 1 11 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 11 0 1 1 0 1 0 1 1 10 d d d dd 1 d d d 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1由真值表可知,当s1=1,s2+s3=0 时,无论A2、A1和A0取何值,输出Y0、…、Y7中有且仅有一个为0(低电平有效),其余都是1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《集成电路设计实践》报告题目:3-8译码器设计

院系:自动化学院电子工程系

专业班级:微电

学生学号:

学生姓名:

指导教师姓名:戴力职称:讲师

起止时间:2015.12.25-2016.01.08

成绩:

一、设计任务

1) 依据3-8译码器的真值表,给出3-8译码器的电路图,完成3-8译码器由电路图到晶体管级的转化(需提出至少2种方案);

2) 绘制原理图(Sedit),完成电路特性模拟(Tspice,瞬态特性),给出电路最大延时时间;

3) 遵循设计规则完成译码器晶体管级电路图的版图,流程如下:

4) 版图布局规划-基本单元绘制-功能块的绘制-布线规划-总体版图);

5) 版图检查与验证(DRC检查);

6) 针对自己画的版图,给出实现该电路的工艺流程图。

二、电路设计方案的确定

3-8译码器真值表

由三个输入端A,B,C和八个输出端Y0,Y1,Y2,Y3,Y4,Y5 ,Y6,Y7组成,输入输出用二进制表示。

从真值表可看出3-8译码器的八个输出管脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出管脚全为高电平1。

如果出现两个输出管脚在同一个时间为0的情况,说明该芯片已经损坏。

可通过使用三输入与非门及反相器实现功能,三输入与非门由三个pmos和三个nmos组成。

三、电路特性及其仿真

首先用S-Edit软件画出电路的模拟图,然后检查所画电路是否存在错误,将各个管子的尺寸标注出来,检查无误后点击T-Spice按钮将出现电路的网表图,然后给检测出的电路网表加上电源和输入信

号,经检查,确认添加无误后进行电路模拟仿真,即可得到电路模拟仿真图像。

网表如下:

仿真图如下:电路图如下:

结果:

据仿真结果和设计电路要求对比可以看出,所设计的电路满足设计需求,并且可以实现3-8译码器的功能,所以设计的电路是可以正常使用的。

四、版图的布局规划及基本单元设计

根据前面所画的电路模拟图,可以看出3-8译码器需要30个PMOS和30个NMOS,PMOS和NOMS一部分组成反向器,一部分组成多个逻辑门,制作版图时采用L-Edit软件,制作版图时应注意版图各层的相关设计规则及对尺寸的要求,在制作版图时需注意所有光刻孔的几何尺寸都必须大于或等于最小距离。

版图如下:

整个版图中一部分的反相器版图如下:

五、该电路实现工艺流程

n阱CMOS工艺流程:选择衬底---n阱光刻---有源区光刻---多晶硅光刻---n+区光刻----p+区光刻---光刻接触孔---金属化内连线---光刻钝化孔,便得到了反相器;然后,将nmos与pmos合理布局;最后,将pmos和coms按电路要求用金属连接起来,做钝化和封装处理;

六、总结

本次设计中,共使用了60个晶体管,其中一部分用于反相器,一部分用于逻辑门,课设中,应注意一些问题:

1、在S-edit中绘制原理图:更改每个MOS管的属性为NENH或PENH,以及管子的尺寸;

2、在T-Spice中进行原理图的仿真:在提取库文件时确保是正确的路径,并添加“tt”,仿真前输入正确的命令语句;

3、在L-Edit中绘制版图,注意各种规则,确保正确的绘制版图;

4、画版图和电路设计图时应严格按照要求电路来进行设计,应实现电路实际功能。

心得体会:在本次课设中,加深了对平时所学基础知识的理解,巩固平时所学的并进行运用,对于制作工艺流程有了更深的理解。

七、设计成果汇总

版图网表:

版图仿真:

版图网表与电路图网表的对比:

版图信息表格:

读书的好处

1、行万里路,读万卷书。

2、书山有路勤为径,学海无涯苦作舟。

3、读书破万卷,下笔如有神。

4、我所学到的任何有价值的知识都是由自学中得来的。

——达尔文

5、少壮不努力,老大徒悲伤。

6、黑发不知勤学早,白首方悔读书迟。

——颜真卿

7、宝剑锋从磨砺出,梅花香自苦寒来。

8、读书要三到:心到、眼到、口到

9、玉不琢、不成器,人不学、不知义。

10、一日无书,百事荒废。

——陈寿

11、书是人类进步的阶梯。

12、一日不读口生,一日不写手生。

13、我扑在书上,就像饥饿的人扑在面包上。

——高尔基

14、书到用时方恨少、事非经过不知难。

——陆游

15、读一本好书,就如同和一个高尚的人在交谈——歌德

16、读一切好书,就是和许多高尚的人谈话。

——笛卡儿

17、学习永远不晚。

——高尔基

18、少而好学,如日出之阳;壮而好学,如日中之光;志而好学,如炳烛之光。

——刘向

19、学而不思则惘,思而不学则殆。

——孔子

20、读书给人以快乐、给人以光彩、给人以才干。

——培根。