ALLEGRO中常见的DRC错误代码意思

ALLEGRO培训包常见设置规则检查DRC报警含义及处理全套PPT

03 建A设LL基EG础RO中常见的DRC错误代码含义

10

03 建A设LL基EG础RO中常见的DRC错误代码含义

在ALLEGRO中,可以根据系统提示的错误或告警的具体类型进 行具体的修改,一旦修改成功,错误或告警提示就会自动消失。

11

3

03 建设AL基LE础GRO中常见的DRC错误代码含义

4

03 建设AL基LE础GRO中常见的DRC错误代码含义

5

03 建A设LL基EG础RO中常见的DRC错误代码含义

6

03 建设AL基LEG础RO中常见的DRC错误代码含义

7

03 建A设LL基EG础RO中常见的DRC错误代码含义

8

03 建A设LL基E础GRO中常见的DRC错误代码含义

ALLEGRO培训包

1

规03则管建理设器基设础置与创建 常见设置规则检查DRC报警含义及处理

深圳职业技术学院 物联网专业 王毅峰

2

02 建设方案 DRC规则管理器界面

ALLEGRO中常见的DRC错误代码含义 常见设置规则检查DRC报警含义及处理 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 深圳职业技术学院 物联网专业 王毅峰 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义 ALLEGRO中常见的DRC错误代码含义

allegro学习

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE –GLOSS—PARAMETERS—CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,―CHANGE Control Trace‖Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture——dimension/draft —–dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

直接操作:在Add Shape 后,shape —parameters 里,Create pin Voids 选中IN line3.倒角Manufacture——dimension/draft――Fillet圆角Manufacture——dimension/draft――Chamfer斜角以上操作只对LINE 画的外框有效,而对Shape 无效。

allegro DRC错误代码

Test Via与Through Pin太近

Through Pin to Through Via Spacing

Through Pin与Through Via太近

RC

Package to Hard Room

元件在其他的Room之内

RE

Min Length Route End Segment at 135Degree

Test Pin to Test Pin Spacing

Test元件脚与Test元件脚太近

Test Pin to Through Pin Spacing

Test元件脚与Through元件脚太近

Through Pin to SMD Pin Spacing

Through元件脚与SMD元件脚太近

Through Pin to Through Pin Spacing

DF

Differential Pair Length Tolerance

差分对走线的长度误差过长

Differential Pair Primary Max Separation

差分对走线的主要距离太大

Differential Pair Secondary Max Separation

差分对走线的次要距离太大

BB Via与Test Via太近

BB Via to Through Via Spacing

BB Via与Through Via太近

Test Via to Test Via Spacing

Test Via之间太近

Test Via to Through Via Spacing

Test Via与Through Via太近

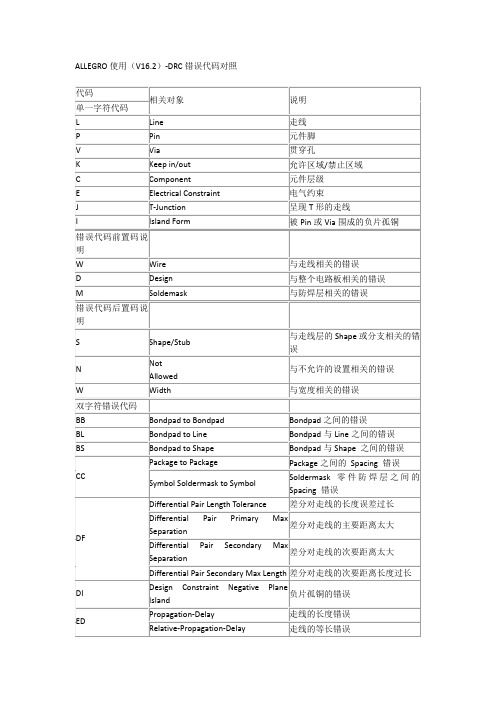

ALLEGRO使用(V16.2)-DRC错误代码对照

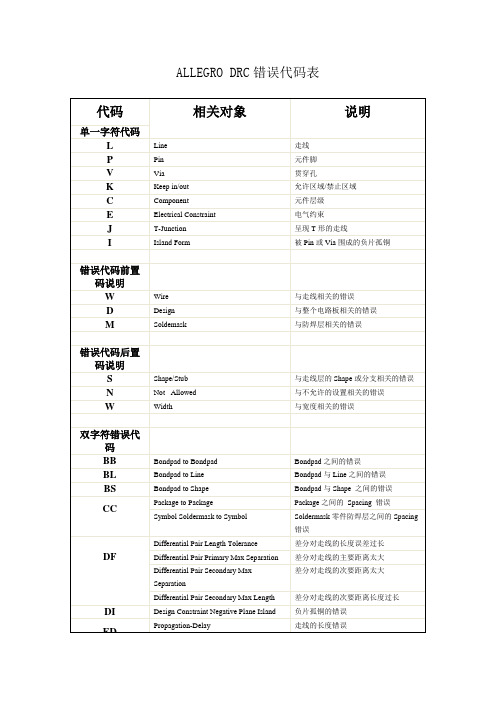

ALLEGRO使用(V16.2)‐DRC错误代码对照代码相关对象 说明单一字符代码L Line 走线P Pin 元件脚V Via 贯穿孔K Keep in/out 允许区域/禁止区域C Component 元件层级E Electrical Constraint 电气约束J T‐Junction 呈现T形的走线I Island Form 被Pin或Via围成的负片孤铜 错误代码前置码说明W Wire 与走线相关的错误D Design 与整个电路板相关的错误M Soldemask 与防焊层相关的错误错误代码后置码说明S Shape/Stub 与走线层的Shape或分支相关的错误N NotAllowed与不允许的设置相关的错误W Width 与宽度相关的错误双字符错误代码BB Bondpad to Bondpad Bondpad之间的错误BL Bondpad to Line Bondpad与Line之间的错误 BS Bondpad to Shape Bondpad与Shape 之间的错误CC Package to Package Package之间的 Spacing 错误 Symbol Soldermask to SymbolSoldermask零件防焊层之间的Spacing 错误DF Differential Pair Length Tolerance 差分对走线的长度误差过长 Differential Pair Primary MaxSeparation差分对走线的主要距离太大 Differential Pair Secondary MaxSeparation差分对走线的次要距离太大 Differential Pair Secondary Max Length差分对走线的次要距离长度过长DI Design Constraint Negative PlaneIsland负片孤铜的错误ED Propagation‐Delay 走线的长度错误 Relative‐Propagation‐Delay 走线的等长错误EL Max Exposed Length 走线在外层(TOP&BOTTOM)的长度过长EP Max Net Parallelism Length‐DistancePair已超过Net之间的平行长度ES Max Stub Length 走线的分支过长ET Electrical Topology 走线连接方式的错误EV Max Via Count 已超过走线使用的VIA的最大数目EX Max Crosstalk 已超过Crosstalk值 Max Peak Crosstalk 已超过Peak Crosstalk值HH Hold to Hold Spacing 钻孔之间的距离太近HW Diagonal Wire to Hold Spacing 斜线与钻孔之间的距离太近Hold to Orthogonal Wire Spacing钻孔与垂直/水平线之间的距离太近IM Impedance Constraint 走线的阻抗值错误 JN T Junction Not Allowed 走线呈T形的错误KB Route Keepinto BondpadBondpad在Keepin之外 Route keepoutto BondpadBondpad在keepout之内 Via KeepouttoBondpadBondpad在Via Keepout之内KC Package to Place Keepin Spacing 元件在Place Keepin之外 Package to Place Keepout Spacing 元件在Place Keepout之内KL Line to Route Keepin Spacing 走线在Route Keepin之外 Line to Route Keepout Spacing 走线在Route Keepout之内KS Shape to Route Keepin Spacing Shape在Route Keepin之外 Shape to Route Keepout Spacing Shape在Route Keepout之内KV BBVia to Route Keepin Spacing BBVia在Route Keepin之外 BBVia to Route Keepout Spacing BBVia在Route Keepout之内 BBVia to Via Keepout Spacing BBVia在Via Keepout之内Test Via to Route Keepin Spacing Test Via在Route Keepin之外 Test Via to Route Keepout Spacing Test Via在Route Keepout之内 Test Via to Via Keepout Spacing Test Via在Via Keepout之内 Through Via to Route Keepin Spacing Through Via在Route Keepin之外 Through Via to Route Keepout Spacing Through Via在Route Keepout之内Through Via to Via Keepout Spacing Through Via在Via Keepout之内LB Min Self Crossing Loopback Length 无LL Line to Line Spacing 走线之间太近LS Line to Shape Spacing 走线与Shape 太近 LW Min Line Width 走线的宽度太细Min Neck Width 走线变细的宽度太细MASoldermask Alignment Error PadSoldermask Tolerance太小MC Pin/Via Soldermask to SymbolSoldermaskPad与Symbol Soldermask之间的错误MM Pin/Via Soldermask to Pin/ViaSoldermaskPadSoldermask之间的错误PB Pin to Bondpad Pin与Bondpad之间的错误PL Line to SMD Pin Spacing 走线与SMD元件脚太近 Line to Test Pin Spacing 走线与Test元件脚太近 Line to Through Pin Spacing 走线与Through元件脚太近PP SMD Pin to SMD Pin Spacing SMD元件脚与SMD元件脚太近 SMD Pin to Test Pin Spacing SMD元件脚与Test元件脚太近 Test Pin to Test Pin Spacing Test元件脚与Test元件脚太近 Test Pin to Through Pin Spacing Test元件脚与Through元件脚太近Through Pin to SMD Pin Spacing Through元件脚与SMD元件脚太近Through Pin to Through Pin SpacingThrough元件脚与Through元件脚太近PS Shape to SMD Pin Spacing Shape与SMD元件脚太近 Shape to Test Pin Spacing Shape与Test元件脚太近 Through Pin to Shape Spacing Through元件脚与Shape太近PV BBVia to SMD Pin Spacing BBVia与SMD元件脚太近 BBVia to Test Pin Spacing BBVia与Test元件脚太近 BBVia to Through Pin Spacing BBVia 与Through元件脚太近 SMD Pin to Test Via Spacing SMD Pin与Test Via太近SMD Pin to Through Via Spacing SMD Pin与Through Via太近 Test Pin to Test Via Spacing Test Pin与Test Via太近Test Pin to Through Via Spacing Test Pin与Through Via太近 Test Via to Through Pin Spacing Test Via与Through Pin太近 Through Pin to Through Via Spacing Through Pin与Through Via太近RC Package to Hard Room 元件在其他的Room之内RE Min Length Route End Segment at 135Degree无 Min Length Route End Segment at 45/90Degree无SB 135Degree Turn to Adjacent Crossing Distance无 90Degree Turn to Adjacent Crossing Distance无SL Min Length Wire Segment 无 Min Length Single Segment Wire 无SN Allow on Etch Subclass 允许在走线层上SO Segment Orientaion 无BB Bondpad to Bondpad Bondpad之间的错误SS Shape to Shape Shape之间的错误TA Max Turn Angle 无VB Via to Bondpad Via 与Bondpad之间的错误VG Max BB Via Stagger Distance 同一段线的BB Via之间的距离太长Min BB Via Gap BB Via之间太近Min BB Via Stagger Distance 同一段线的BB Via之间的距离太近Pad/Pad Direct Connect Pad 在另一个Pad 之上VL BB Via to Line Spacing BB Via与走线太近Line to Through Via Spacing 走线与Through Via太近 Line to Test Via Spacing 走线与Test Via太近VS BB Via to Shape Spacing BB Via与Shape太近 Shape to Test Via Spacing Shape 与Test Via太近 Shape to Through Via Spacing Shape与Through Via太近VV BB Via to BB ViaSpacingBB Via之间太近BB Via to Test Via Spacing BB Via与Test Via太近BB Via to Through Via Spacing BB Via与Through Via太近 Test Via to Test Via Spacing Test Via之间太近Test Via to Through Via Spacing Test Via与Through Via太近 Through Via to Through Via Spacing Through Via之间太近WA Min Bonding Wire Length Bonding Wire 长度太短WE Min End Segment Length 无 Min Length Wire End Segment at 135Degree无 Min Length Wire End Segment at 45/90Degree无WI Max Bonding Wire Length Bonding Wire 长度太长WW Diagonal Wire to Diagonal WireSpacing斜线之间太近Diagonal Wire to Orthogonal WireSpacing斜线与垂直/水平线之间的距离太近Orthogonal Wire to Orthogonal WireSpacing垂直/水平线之间的距离太近WX Max Number of Crossing 无 Min Distance between Crossing 无XB 135 Degree Turn to Adjacent Crossing Distance无 90 Degree Turn to Adjacent Crossing 无DistanceXD Externally Determined Violation 无XS Crossing to Adjacent Segment Distances无。

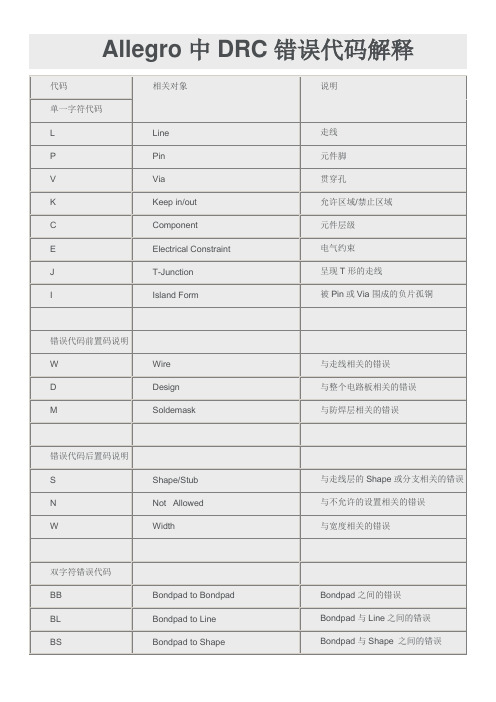

Allegro中常见的DRC错误代码解析

Hold to Orthogonal Wire Spacing

钻孔与垂直/水平线之间的距离太近

IM

Impedance Constraint

走线的阻抗值错误

JN

T Junction Not Allowed

走线呈T形的错误

KB

RouteKeepintoBondpad

Bondpad在Keepin之外

Through ViatoThrough Via Spacing

Through Via之间太近

WA

Min Bonding Wire Length

Bonding Wire长度太短

WE

Min End Segment Length

无

Min Length Wire End Segment at 135Degree

EV

Max Via Count

已超过走线使用的VIA的最大数目

EX

Max Crosstalk

已超过Crosstalk值

Max Peak Crosstalk

已超过Peak Crosstalk值

HH

Hold to Hold Spacing

钻孔之间的距离太近

HW

Diagonal Wire to Hold Spacing

BBVia与Test元件脚太近

BBViato Through Pin Spacing

BBVia与Through元件脚太近

SMD Pin to Test Via Spacing

SMD Pin与Test Via太近

SMDPin toThrough Via Spacing

SMD Pin与Through Via太近

Allegro常见问题点

Q: Allegro中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters,选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE --GLOSS---PARAMETERS---CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,“CHANGE Control Trace”Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture------dimension/draft -----dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

直接操作:在Add Shape 后,shape ---parameters 里,Create pin Voids 选中IN line3.倒角Manufacture------dimension/draft――Fillet圆角Manufacture------dimension/draft――Chamfer斜角以上操作只对LINE 画的外框有效,而对Shape 无效。

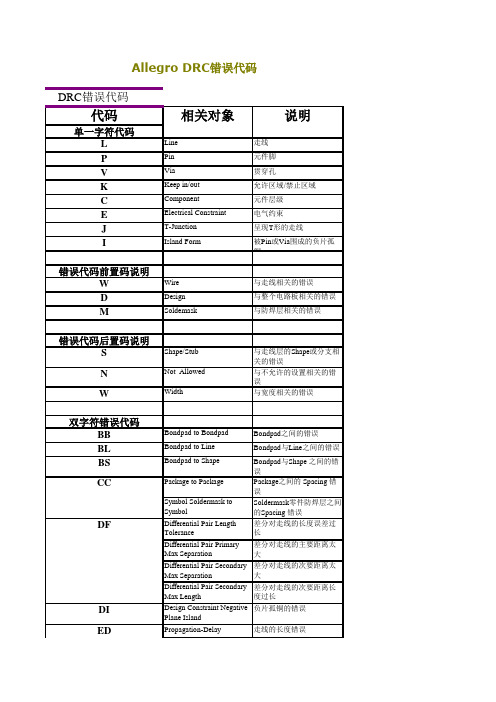

Allegro DRC错误代码清单

DRC 错误代码代码单一字符代码L Line 走线P Pin 元件脚V Via贯穿孔K Keep in/out 允许区域/禁止区域C Component 元件层级E Electrical Constraint 电气约束J T-Junction 呈现T 形的走线I Island Form被Pin 或Via 围成的负片孤铜错误代码前置码说明W Wire 与走线相关的错误D Design 与整个电路板相关的错误M Soldemask与防焊层相关的错误错误代码后置码说明SShape/Stub 与走线层的Shape 或分支相关的错误N Not Allowed 与不允许的设置相关的错误WWidth 与宽度相关的错误双字符错误代码BB Bondpad to Bondpad Bondpad 之间的错误BL Bondpad to Line Bondpad 与Line 之间的错误BSBondpad to Shape Bondpad 与Shape 之间的错误Package to Package Package 之间的 Spacing 错误Symbol Soldermask to SymbolSoldermask 零件防焊层之间的Spacing 错误Differential Pair Length Tolerance差分对走线的长度误差过长Differential Pair Primary Max Separation差分对走线的主要距离太大Differential Pair Secondary Max Separation差分对走线的次要距离太大Differential Pair Secondary Max Length差分对走线的次要距离长度过长DI Design Constraint Negative Plane Island负片孤铜的错误Propagation-Delay走线的长度错误相关对象说明CCDFEDAllegro DRC 错误代码152 | 顶:0 顶一下 | 评论:0 | 收藏| 打印 |下一篇:Allegro学习笔记之3—电源层、 >>。

ALLEGRO中常见的DRC错误代码意思

90Degree Turn to Adjacent Crossing Distance

EV

Max Via Count

已超过走线使用的VIA的最大数目

EX

Max Crosstalk

已超过Crosstalk值

Max Peak Crosstalk

已超过Peak Crosstalk值

HH

Hold to Hold Spacing

钻孔之间的距离太近

HW

Diagonal Wire to Hold Spacing

BBVia to SMD Pin Spacing

BBVia与SMD元件脚太近

BBVia to Test Pin Spacing

BBVia与Test元件脚太近

BBVia to Through Pin Spacing

BBVia与Through元件脚太近

SMDPin to Test Via Spacing

斜线与垂直/水平线之间的距离太近

Orthogonal Wire to Orthogonal Wire Spacing

垂直/水平线之间的距离太近

WX

Max Number of Crossing

无

Min Distance between Crossing

无

XB

135 Degree Turn to Adjacent Crossing Distance

Test元件脚与Test元件脚太近

Test Pin to Through Pin Spacing

Test元件脚与Through元件脚太近

Through Pin to SMD Pin Spacing

Through元件脚与SMD元件脚太近

ALLEGRO中常见的DRC错误代码意思

KL

Line to RouteKeepinSpacing

走线在RouteKeepin之外

Line to RouteKeepoutSpacing

走线在RouteKeepout之内

KS

Shape to RouteKeepinSpacing

Shape在RouteKeepin之外

Test Via在ViaKeepout之内

Through Via to RouteKeepinSpacing

Through Via在RouteKeepin之外

Through Via to RouteKeepoutSpacing

Through Via在RouteKeepout之内

Through Via to ViaKeepoutSpacing

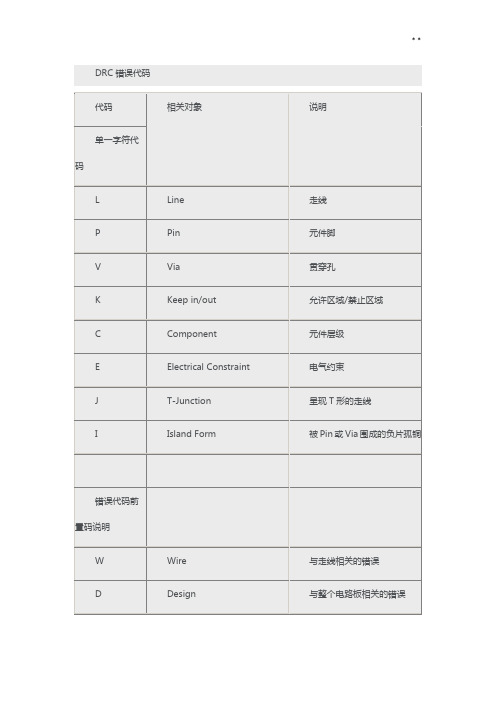

DRC错误代码

代码

相关对象

说明

单一字符代码

L

Line

走线

P

Pin

元件脚

V

Via

贯穿孔

K

Keep in/out

允许区域/禁止区域

C

Component

元件层级

E

Electrical Constraint

电气约束

J

T-Junction

呈现T形的走线

I

Island Form

被Pin或Via围成的负片孤铜

错误代码前置码说明

Through ViatoThrough Via Spacing

Through Via之间太近

WA

Min Bonding Wire Length

Bonding Wire长度太短

WE

Min End Segment Length

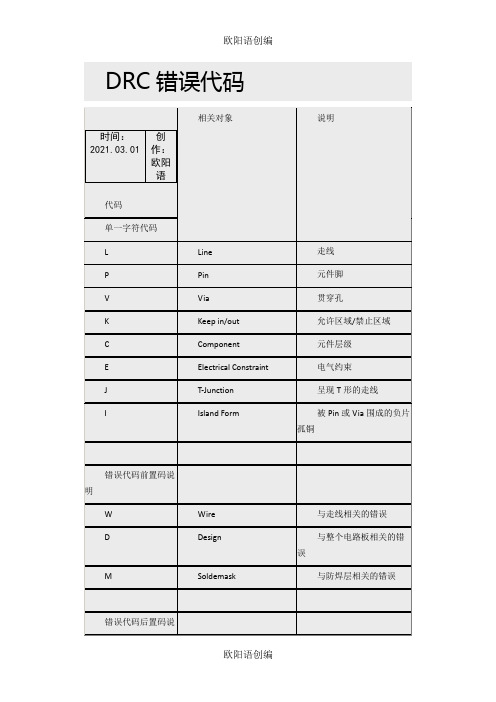

ALLEGRO中常见的DRC错误代码意思之欧阳语创编

时间:2021.03.01

创作:欧阳语

代码

相关对象

说明

单一字符代码

L

Line

走线

P

Pin

元件脚

V

Via

贯穿孔

K

Keep in/out

允许区域/禁止区域

C

Component

元件层级

E

Electrical Constraint

电气约束

J

T-Junction

呈现T形的走线

I

Island Form

BBVia to Via Keepout Spacing

BBVia在Via Keepout之内

Test Via to Route Keepin Spacing

Test Via在Route Keepin之外

Test Via to Route Keepout Spacing

Test Via在Route Keepout之内

Test Pin to Test Pin Spacing

Test元件脚与Test元件脚太近

Test Pin to Through Pin Spacing

Test元件脚与Through元件脚太近

Through Pin to SMD Pin Spacing

Through元件脚与SMD元件脚太近

Through Pin to Through Pin Spacing

EV

Max Via Count

已超过走线使用的VIA的最大数目

EX

Max Crosstalk

已超过Crosstalk值

Max Peak Crosstalk

已超过Peak Crosstalk值

allegro出光绘文件出现的几个问题

allegro出光绘文件出现的几个问题首先出光绘前要保证没有DRC错误出Gerber时提示如下错误:一:设置好光绘文件参数后,选择check dabase before artwork 后,点击生成光绘时出现错误告警信息:database has errors:artwork generation cancled.please run dbdoctor.可行的解决方法:1.运行内部,或外部dbdoctor ,内部的在tools-database check2.TOOLS-PADSTACK-modify design padstack。

在option中的purge选ALL。

3.place-update symbols-选择器件并选择下方的update symbols padstacks选项4.tools-padstack-refresh上述4种方法过后,基本上能解决问题。

二:WARNING: Shape at (XX XX) contains void at (XX XX)which touches another shape当该层不铺这块铜时可以正常出Gerber.这个主要是敷铜的问题,同一NET的两个独立的shape 重叠就会出现该错误告警。

出 Gerber时 , Allegro不允许2个或更多 Dynamic 类型的形状彼此接触,即使他们用相同的 netname。

解决方法:对动态敷铜与静态敷铜重叠的,可视情况删除掉静态的,或者利用merge shape来将2个分立的shape合并成一块shape。

打开shape boundary 可便于操作。

三:在能成功生成gerber文件时,文件中可能存在的许多告警信息:WARNING: Segment with same start and end points at(67.0201 174.2666) will be ignored. Increasing output accuracy may allow segment to be generated.等这个主要是底片精度设置导致的问题。

ALLEGRO中常见的DRC错误代码意思讲课稿

Hold to Orthogonal Wire Spacing

钻孔与垂直/水平线之间的距离太近

IM

Impedance Constraint

走线的阻抗值错误

JN

T Junction Not Allowed

走线呈T形的错误

KB

Route Keepin to Bondpad

Bondpad在Keepin之外

BBVia to Via Keepout Spacing

BBVia在Via Keepout之内

Test Via to Route Keepin Spacing

Test Via在Route Keepin之外

Test Via to Route Keepout Spacing

Test Via在Route Keepout之内

LS

Line to Shape Spacing

走线与Shape太近

LW

Min Line Width

走线的宽度太细

Min Neck Width

走线变细的宽度太细

MA

Soldermask Alignment Error Pad

Soldermask Tolerance太小

MC

Pin/Via Soldermask to Symbol Soldermask

Pad与Symbol Soldermask之间的错误

MM

Pin/Via Soldermask to Pin/Via Soldermask

Pad Soldermask之间的错误

PB

Pin to Bondpad

EV

Max Via Count

已超过走线使用的VIA的最大数目

ALLEGRO常见问题大全

ALLEGRO常见问题大全Q: Allegra中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters,选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE --GLOSS---PARAMETERS---CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,“CHANGE Control Trace”Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture------dimension/draft -----dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

ALLEGRO-DRC-错误代码

ALLEGRO-DRC-错误代码(2013-01-04 10:54:48)转载▼标签:杂谈Q: Allegra中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters, 选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE –GLOSS—PARAMETERS—CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,―CHANGE Control Trace‖Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture——dimension/draft —–dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

ALLEGRO DRC错误代码表

BBVia在Via Keepout之内

Test Via to Route Keepin Spacing

Test Via在Route Keepin之外

Test Via to Route Keepout Spacing

Test Via在Route Keepout之内

无

VB

Via to Bondpad

Via与Bondpad之间的错误

VG

Max BB Via Stagger Distance

同一段线的BB Via之间的距离太长

Min BB Via Gap

BB Via之间太近

Min BB Via Stagger Distance

同一段线的BB Via之间的距离太近

Pad/Pad Direct Connect

Through Via在Route Keepout之内

Through Via to Via Keepout Spacing

Through Via在Via Keepout之内

LB

Min Self Crossing Loopback Length

无

LL

Line to Line Spacing

走线之间太近

Pad在另一个Pad之上

VL

BB Via to Line Spacing

BB Via与走线太近

Line to Through Via Spacing

走线与Through Via太近

Line to Test Via Spacing

走线与Test Via太近

VS

BB Via to Shape Spacing

BBVia to SMD Pin Spacing

Allegro常见问题点

Q: Allegro中颜色设置好以后,应该可以导出相关设置文件,下次碰到不同设置的板子,看着难受就可以直接读入自己的文件改变设置了A:16.2版本的可以这样做:file->export->parameters,选中颜色就行了,其它的参数一样可以保存。

Q:ALLEGRO 自动布线后,为直角.如何调整成45度角走线A: ROUTE --GLOSS---PARAMETERS---CONVERT CORNET TO ARC一、群组布线;群组布线包括总线布线和一次布多外Trance.1.一次布多个Trance .鼠标左键进行选择多外PIN,或VIA. 同时可以在布线过程中用右键切换到单线模式。

群组布线只能在一个层中,不允许打过孔。

也可以在群组布线过程中,右键,“CHANGE Control Trace”Cadence CIS即原理图中,放大缩小缩小的快捷键按住CTRL键+鼠标中间滚轮)5. ALLEGRO 出光绘文件前,最好加个PHOTO_OUTLINE,确认输出光绘文件的范围Class: manufacture — Subclass: photoplot outline6. 光绘设置详解/bbs/viewthread.php?tid=28&page=1ALLEGRO 标注 1. dimension linear : 对于比较规则,简单的板子,通常采用.2.dimension datum :对于较复杂的板子可以采用。

先确定一个基准点,接下来对每个点所标注的数据都是相对基准点的坐标值。

Manufacture------dimension/draft -----dimension linear / dimension datum2.表层铺铜时,由于铺铜和PIN 的间距问题,在PIN 和PIN 之间经常产生一些尖角。

产生这种原因的解决办法:一。

一个一个修改Boundary二。

直接操作:在Add Shape 后,shape ---parameters 里,Create pin Voids 选中IN line3.倒角Manufacture------dimension/draft――Fillet圆角Manufacture------dimension/draft――Chamfer斜角以上操作只对LINE 画的外框有效,而对Shape 无效。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Min Length Single Segment Wire

无

SN

Allow on Etch Subclass

允许在走线层上

SO

Segment Orientaion

无

BB

Bondpad to Bondpad

Bondpad之间的错误

SS

Shape to Shape

Shape之间的错误

TA

Max Turn Angle

Through Via在Route Keepout之内

Through Via to Via Keepout Spacing

Through Via在Via Keepout之内

LB

Min Self Crossing Loopback Length

无

LL

Line to Line Spacing

走线之间太近

BBVia to SMD Pin Spacing

BBVia与SMD元件脚太近

BBVia to Test Pin Spacing

BBVia与Test元件脚太近

BBVia to Through Pin Spacing

BBVia与Through元件脚太近

SMD Pin to Test Via Spacing

Through Via to Through Via Spacing

Through Via之间太近

WA

Min Bonding Wire Length

Bonding Wire长度太短

WE

Min End Segment Length

无

Min Length Wire End Segment at 135Degree

无

Min Length Route End Segment at 45/90Degree

无

SB

135Degree Turn to Adjacent Crossing Distance

无

90Degree Turn to Adjacent Crossing Distance

无

SL

Min Length Wire Segment

Test Via to Through PinSpacing

Test Via与Through Pin太近

Through Pin to Through Via Spacing

Through Pin与Through Via太近

RC

Package to Hard Room

元件在其他的Room之内

RE

Min Length Route End Segment at 135Degree

Pad与Symbol Soldermask之间的错误

MM

Pin/Via Soldermask to Pin/Via Soldermask

Pad Soldermask之间的错误

PB

Pin to Bondpad

Pin与Bondpad之间的错误

PL

Line to SMD Pin Spacing

走线与SMD元件脚太近

斜线与垂直/水平线之间的距离太近

Orthogonal Wire to Orthogonal Wire Spacing

垂直/水平线之间的距离太近

WX

Max Number of Crossing

无

Min Distance between Crossing

无

XB

135 Degree Turn to Adjacent Crossing Distance

元件在Place Keepout之内

KL

Line to Route Keepin Spacing

走线在Route Keepin之外

Line to Route Keepout Spacing

走线在Route Keepout之内

KS

Shape to Route Keepin Spacing

Shape在Route Keepin之外

Line t元件脚太近

Line to Through Pin Spacing

走线与Through元件脚太近

PP

SMD Pin to SMD Pin Spacing

SMD元件脚与SMD元件脚太近

SMD Pin to Test Pin Spacing

SMD元件脚与Test元件脚太近

BBVia to Via Keepout Spacing

BBVia在Via Keepout之内

Test Via to Route Keepin Spacing

Test Via在Route Keepin之外

Test Via to Route Keepout Spacing

Test Via在Route Keepout之内

Bondpad之间的错误

BL

Bondpad to Line

Bondpad与Line之间的错误

BS

Bondpad to Shape

Bondpad与Shape之间的错误

CC

Package to Package

Package之间的Spacing错误

Symbol Soldermask to Symbol

Soldermask零件防焊层之间的Spacing错误

走线的等长错误

EL

Max Exposed Length

走线在外层(TOP&BOTTOM)的长度过长

EP

Max Net Parallelism Length-Distance Pair

已超过Net之间的平行长度

ES

Max Stub Length

走线的分支过长

ET

Electrical Topology

走线连接方式的错误

BB Via与Shape太近

Shape to Test Via Spacing

Shape与Test Via太近

Shape to Through Via Spacing

Shape与Through Via太近

VV

BB Via to BB Via Spacing

BB Via之间太近

BB Via to Test Via Spacing

Through元件脚与Through元件脚太近

PS

Shape to SMD Pin Spacing

Shape与SMD元件脚太近

Shape to Test Pin Spacing

Shape与Test元件脚太近

Through Pin to Shape Spacing

Through元件脚与Shape太近

PV

BB Via与Test Via太近

BB Via to Through Via Spacing

BB Via与Through Via太近

Test Via to Test Via Spacing

Test Via之间太近

Test Via to Through Via Spacing

Test Via与Through Via太近

EV

Max Via Count

已超过走线使用的VIA的最大数目

EX

Max Crosstalk

已超过Crosstalk值

Max Peak Crosstalk

已超过Peak Crosstalk值

HH

Hold to Hold Spacing

钻孔之间的距离太近

HW

Diagonal Wire to Hold Spacing

LS

Line to Shape Spacing

走线与Shape太近

LW

Min Line Width

走线的宽度太细

Min Neck Width

走线变细的宽度太细

MA

Soldermask Alignment Error Pad

Soldermask Tolerance太小

MC

Pin/Via Soldermask to Symbol Soldermask

Test Via to Via Keepout Spacing

Test Via在Via Keepout之内

Through Via to Route Keepin Spacing

Through Via在Route Keepin之外

Through Via to Route Keepout Spacing

Differential Pair Secondary Max Length

差分对走线的次要距离长度过长

DI

Design Constraint Negative Plane Island

负片孤铜的错误

ED

Propagation-Delay

走线的长度错误

Relative-Propagation-Delay

DF

Differential Pair Length Tolerance

差分对走线的长度误差过长

Differential Pair Primary Max Separation

差分对走线的主要距离太大

Differential Pair Secondary Max Separation

差分对走线的次要距离太大

SMD Pin与Test Via太近

SMD Pin to Through Via Spacing

SMD Pin与Through Via太近

Test Pin to Test Via Spacing

Test Pin与Test Via太近

Test Pin to Through Via Spacing

Test Pin与Through Via太近

无

Min Length Wire End Segment at 45/90Degree