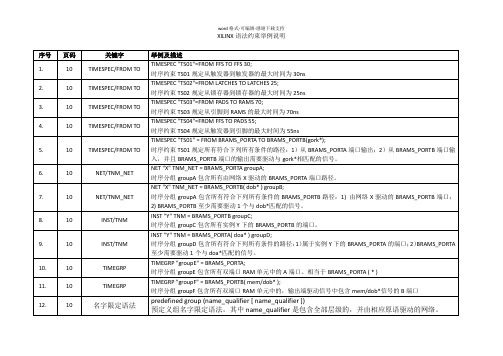

XILINX语法约束举例说明

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明

赛灵思(Xilinx)FPGA用户约束文件的分类和语法说明FPGA设计中的约束文件有3类:用户设计文件(.UCF文件)、网表约束文件(.NCF文件)以及物理约束文件(.PCF文件),可以完成时序约束、管脚约束以及区域约束。

3类约束文件的关系为:用户在设计输入阶段编写UCF文件,然后UCF文件和设计综合后生成NCF文件,最后再经过实现后生成PCF 文件。

UCF文件是ASC 2码文件,描述了逻辑设计的约束,可以用文本编辑器和Xilinx约束文件编辑器进行编辑。

NCF约束文件的语法和UCF文件相同,二者的区别在于:UCF文件由用户输入,NCF文件由综合工具自动生成,当二者发生冲突时,以UCF文件为准,这是因为UCF的优先级最高。

PCF文件可以分为两个部分:一部分是映射产生的物理约束,另一部分是用户输入的约束,同样用户约束输入的优先级最高。

一般情况下,用户约束都应在UCF文件中完成,不建议直接修改NCF文件和PCF文件。

约束文件的后缀是.ucf,所以一般也被称为UCF文件。

创建约束文件有两种方法,一种是通过新建方式,另一种则是利用过程管理器来完成。

第一种方法:新建一个源文件,在代码类型中选取ImplementaTIon Constrains File,在File Name中输入约束文件的名称。

单击Next按键进入模块选择对话框,选择要约束的模块,然后单击Next进入下一页,再单击Finish按键完成约束文件的创建。

第二种方法:在工程管理区中,将Source for设置为Synthesis/ImplementaTIon。

Constrains Editor是一个专用的约束文件编辑器,双击过程管理区中User Constrains下的Create TIming Constrains就可以打开Constrains Editor。

需要注意的是,UCF文件是大小敏感的,端口名称必须和源代码中的名字一致,且端口名字不能和关键字一样。

Xilinx时序约束设计

Constraints Practical Design for Xilinx!!该文的版权归Xilinx公司所有!由收集整理。

Make EDA serve you!When to use Timing Constraints? Constraints add to run time, so don’t use them unless you need toFaster designs need constraining—it depends on the speed grade of the device selected, but in general, any design with a clock speed of 50MHz or less and a reasonable number of logic levels (7 or less),doesn’t need timing constraints—designs over 50MHz should use timing constraintsDesigns with multiple clock should have timing constraints —if you have a signal clock and are under the 50MHz limit above, you will not need timing constraints -you can always add them later if you need toIf you have multi-cycle clock paths, you need constraints—these are paths where you know you have two or more clock cycles for logic to steady-state after an input changeRule of Thumb:run non-timing driven PAR without constraints, unless you are not reaching your timing goals.—add constraints sparingly, DO NOT over constrain your design -it won’t help, and increases can increase your run time dramatically!!Why use Design Constraints?Constraints allow you to lock your pins after the board pin out is fixed —Xilinx M1.5i software has automatic pin locking, and uses the constraints file to pass these pin locks to future runs of the designConstraints allow you to give your exact timing requirement to the place and route or fitting software—for many designs, the constraints are not needed for place and route to meet timing -but are an excellent way to get a detailed static timing report whether or not your design meets your goals—for more challenging designs, the constraints tell the software where the critical paths are -and where to focus their effortsTo know quickly if your design met your goals—Xilinx has the best timing analysis tools in the FPGA industry—applying some simple constraints will allow you to get a quick GO/NO-GO after place and route. The software will tell you all the constraints were met,and you can quickly move on to board debug, without ever looking at a report—if your constraints were not met,Xilinx gives you the level of detail needed to quickly understand why -and where your design needs more work.What Needs Constraining? Internal clock speed for one or more clocksI/O speedLogic using multi-cycle clocksPin to pin timingPin locations and logic locationsOUT1 XY Z<0:9>2 Levels of Logic I/O SpeedPin 2 Pin SpeedI/O SpeedLogicLocations1 Level of LogicQD QDCLK Clk & CE SpeedPinLocationsOUT2PinLocationsTypes of Constraints Supported Timing Constraints—specify delay along logic paths—allows both “quick and dirty”and “highly detailed”timing control Location Constraints—specify location of components on FPGA—specify mapping constraints I N S T M Y _FM AP BL KN M=AB CI NS TF LO P1BL KN M=AB CI NS TF LO P2BL KN M=AB CWhere do Constraints go?Timing constraints may be applied to a schematic using the timespec symbol (FROM:TO’s)They can be added to HDL source code if your compiler supports them They can be input in a separate file called a .UCF (user constraints file), or a synthesizer generated .NCF (netlist constraints file)Some constraints must be placed in the PCF (physical constraints file).Normally, the PCF should be avoided by users.TIMESPECHow do I Create Constraints?Write them by hand using the Xilinx Libraries Guide as a syntax guide —this is the most difficult method, but provides the most controlEnter them with your HDL or schematic, and pass them through with the netlist—this is a much easier method—it has limited control over the naming of constraints -in some cases can over constrain the design—additionally, you need to learn two constraint languages -the synthesizer’s and eventually Xilinx’sUse the Xilinx Graphic Constraints Editor—provides the easiest path to entering most constraints—exports standard Xilinx Constraints Syntax—gives complete control over the design—in some case, some advanced constraints are not yet supported, like temperature or voltage for exampleConstraints EditorRemoves the need to know constraint syntaxDoes not remove the need to know the designCreates Xilinx time and placement constraintsFive tabs used for constraining:—Global Constraints: PERIOD, OFFSET IN BEFORE, OFFSET OUT AFTER, Pad to Pad—Port Constraints: Pin Locations, OFFSET IN BEFORE, OFFSET OUT AFTER, FAST/SLOW, Pin Prohibits—Advanced Constraints: TIMEGRP, TPTHRU, Group OFFSET IN BEFORE, Group OFFSET OUT AFTER, FROM:TO, FROM:TO:TIG, NET TIG —Editable Constraints: List groups and constraints created. Disabling or deletion of constraints.—Source Constraints: Read Only. Constraint from .ngd file. Constraints can be overridden, but not removed.Brief Review of Constraint Flow PHYSICALUser netlist and existingconstraintsPAR TRCE EPICNGDANNO DRC XNF/EDIF netlist Constraint Editor UCF NGDBUILD MAP.PCF.NCD Constraints EditorNGDBUILDDesign_name.ngd XNF/EDIF netlist Existing UCF User Constraints File LOGICAL DOMAINDESIGNTRANSLATIONMapped design and physical constraintsTiming Constraints (I) Using Constraint Editor to create PERIOD and OFFSETconstraintsGlobal TABPeriod, Pad to Setup, and Clock To Pad, Pad to Pad will be automatically filled in by CE from your UCF periods and global offsets (if they exist). You may modify existing constraints or create new constraints. These global values are overridden by any morePeriod ConstraintsPERIODPeriod is the duration of the clock, and can be configured to have different duty cyclesDerived clocks can be defined as a function of another clock (*,/)Period is preferred over from:to constraints; M1 tools will have a faster runtime -Period should cover most of design.Practical Design for Xilinx, Section 7, The Period ConstraintPeriod : This constraint covers all timing paths which start or end at a flip-flop, latch or synchronous RAM which is clocked by the referenced net. (Every synchronous element is effectively identified by forward propagation.)It does not cover paths to output pads, but does cover inputpads. UCF Example :—Using “simple”method:NET A_CLK PERIOD=40: LOW 15;……(LOW is optional; Specifies duty cycle)OUT1OUT2Q D QD CLKRAMPERIOD=30GLATCHFLOPPath controlled by PERIODForward propagation pathEntering Period ConstraintsExplicit allows the user to specify theclock period as well as the dutycycle. It is always better to specifythe HIGH cycle.The user can also specify a periodconstraint relative to another periodconstraint -as well as the multiple ordivisor.Period Path TracingPeriod analyzes the following:—synchronous element to synchronous element data path calculations —PAD to synchronous element data path—automatically deals with inverted clock pins—deals with non 50% clock duty cycles—synchronous element to PAD and PAD to PAD not includedClock Network to Clock Network uses Target Clock as Time ConstraintPeriod #2 will control this path Period#1Period#2Period and Two-Phase ClocksThe allowed path delay will automatically be reduced if a two-phase clock is detected—if period does not have a “HIGH”or “LOW”keyword to define duty-cycle, then allowed path delay will be cut in halfSingle-Phase MaximumTwo-Phase Maximum =====================================================================Timing constraint: NET "clock" PERIOD = 45nS HIGH 50.000 % ;2 items analyzed, 0 timing errors detected.Minimum period is 8.586ns.---------------------------------------------------------------------Slack: 18.207ns path qneg_buf to qneg_buf relative to22.500ns delay constraint (two-phase clock)Path qneg_buf to qneg_buf contains 2 levels of logic:Path starting from Comp: CLB_R1C7.K (from clock_buf)To Delay type Delay(ns) Physical ResourceLogical Resource(s) ---------------------------------------------------------CLB_R1C7.XQ Tcko 1.830R qneg_bufCLB_R1C7.C2 net (fanout=2) 0.543R qpos_bufCLB_R1C7.K Thh1ck 1.920R qneg_buf-------------------------------------------------Total (3.750ns logic, 0.543ns route) 4.293ns (to clock_buf)“Two-phase clock”is indicated hereThis indicates the magnitude of the path delay between flops. There is no “adjustment”to this figure.This indicates that the worst-case period for thisentire spec is 8.586ns (4.293ns x 2). If there had been a single-phase path in this period spec that was 9ns, it would have been reported as the worst-case value -if it were 8ns, it would not.TRCE cut the spec in half (45ns/2=22.5ns) for this path45ns is the maximum allowed PERIOD declared in the UCFPeriod and RAMPeriod will trace THROUGH the address pins of all RAM, and TO the D/WE pins of sync RAM (THROUGH WE of Async)Sync RAMWEDWCLKADDRESSASync RAMWEADDRESSI/O Timing: OFFSETOffset allows the user to specify external data and clock relationships for the timing on paths to and from the I/Os. The software determines the internal requirements (OFFSET IN AFTER, OFFSET OUT BEFORE).Optionally, offset allows the user to specify the internal delay(OFFSET IN BEFORE, OFFSET OUT AFTER).Offset was originally added to support Synopsys set_input_delay and set_output_delay constraintsFor clocks using global resources, clock delay is used in the equationNote: The path from the pad to a flip-flop in an IOB is not constrained by offset. This is considered a fixed delay and is not reported.Specify I/O timingOffset allows the user to specify external data and clock relationships for the timing on paths to and from the IO’s.It enables the user to inform the M1 system of external setup and clock-to-out delays with respect to a clock. The M1 system can then determine the internal timing requirements without the need for PADS:TO:FFS or FFS:TO:PADS constraints.FPGACLKd1d2d3d4DEV1DEV2OFFSET IN OFFSET OUTInternal delays determinedby the toolsPractical Design for Xilinx, Section 7, NET Din OFFSET = IN 20nS BEFORE CLKCLKFPGAThis says, data will be valid here , 20nS before the clock arrives here .In other words: “The data to be registered in the FPGA will be available on the FPGA’s input pad 20ns BEFORE the clock pulse is seen by the FPGA’s clock pad.”Therefore, the M1 tools will calculate: Maximum_Allowable_Internal_P2S_Delay = OFFSET + internal_CLK_delay.the tools can automatically calculate and control internal data and clock delays to meet TsuFFTsuFF Tbufg20nsdata out of DEV1 on this edge.data registered in FPGA on this edge.Internal delayDinCLKValidValiddesigner must ensure thatT(clock_period) -20ns = ext-delayThe OFFSET IN -‘BEFORE’ConstraintUPSTREAM DEVICENET CLK PERIOD = 45nS;NET Din OFFSET = IN16nS AFTER CLK;CLKUPSTREAM DEVICE FPGAThis says, data will be valid here, 16nS after the clock arrives here!….. In other words: “The data to be registered in the FPGA will be available on the FPGA’s input pad 16ns AFTER the clock pulse is seen by the upstream device.” For the purpose of the offset constraint syntax, assume no skew on CLK between the chips. A period constraint is required to indicate when the subsequent clock pulse will be seen by the FPGA to clock in the data (Maximum_Allowable_Internal_P2S_Delay = PERIOD -OFFSET + internal_CLK_delay).16ns data outof DEV1 onthis edge.data registeredin FPGA onthis edge.DinCLKfor this example, the max. P2S delaywould be calculated by M1 as :45ns-16ns+3ns = 32ns.(assuming internal CLK delay is 3ns.) ValidThe OFFSET IN -‘AFTER’ConstraintNET Din OFFSET = OUT 22nS AFTER CLKThis says, data will be valid here , 22nS AFTER the clock arrives here !…..In other words: “The data to be registered in the downstream device will be available on the FPGA’s output pad 22ns AFTER the clock pulse is seen by the FPGA.” (Maximum_Allowable_Internal_Dout_Delay = OFFSET -internal_CLK_delay).DOWNSTREAM DEVICEFPGAdesigner must ensure thatT(clock_period) -22ns = ext-delay ext-delay = sufficient time for external delays involved with meeting DEV2 setup time.22nsValiddata clocked into DEV2 on this edge.data out of FPGA on this edge.NET CLK PERIOD = 45nS;NET Din OFFSET = OUT 25nS BEFORE CLK;d4DEV2FPGAThis says, data will be valid here , 25nS BEFORE the clock arrives here !…..In other words: “The data to be registered in the downstream device will be available on the FPGA’s output pad 25ns BEFORE the clock pulse is seen by the downstream device.” For the purpose of the offset constraint syntax, assume no skew on CLK between the chips. A period constraint is required to indicate when the initial clock pulse was seen by the FPGA to clock out the data (Maximum_Allowable_Internal_C2P_Delay = PERIOD -OFFSET -internal_CLK_delay).for this example, the max. C2P delay would be calculated by M1 as :45ns-25ns-3ns = 17ns.(assuming internal CLK delay is 3ns.)25nsdata into DEV2 on this edge.data out of FPGA on this edge.ValidOFFSET Constraints in M1.5Global: All inputs/outputs are offset relative to a clock; for example, OFFSET = IN 20ns BEFORE clk1 indicates that all inputs will have data present at the pad at least 20ns before the triggering edge of clk1 arrives at the pad.Net-Specific: A specific input/output is offset relative to a clock; for example, NET DATA_IN OFFSET = IN 20nsBEFORE clk1 indicates that DATA_IN will have data present at the pad at least 20ns before the triggering edge of clk1 arrives at the pad.Entering Global Pad to Setup andClock to PadThe global tab givesthe user the ability tocreate global offsetconstraints. The datapath is determined bythe clock net.Entering Net-SpecificPad to Setup and Clock to PadThe ports tab gives theuser the ability tocreate net-specificoffset constraints. Thedata path isdetermined by the padand clock net.Clock Register Groups in OFFSETClock register time groups allow the user to define a specific set of registers to which an OFFSET constraint applies, based on a clock edge. Consider the following example...AB CDATA NET CLK PERIOD = 45nS;OFFSET = IN 10 BEFORE CLK TIMEGRP AB;OFFSET = IN 20 BEFORE CLK TIMEGRP C;CLKYou can define time groups for registers A, B, and C, even though these registers have the same data and clock source. TIMEGRP AB = RISING FFS; TIMEGRP C =FALLING FFS.This allows the user to perform two different timing analysis for the registers.Data Path Groups in OFFSETTIMEGRP DATA_GRP = PADS(DATA*);NET CLK PERIOD = 45nS;TIMEGRP DATA_GRP OFFSET = IN 10 BEFORE CLK;Data Path Groups allow the user to define a specific set of input pads to which an offset constraint applies. Consider the following example...You can also add a clock register time group.TIMEGRP BEF = FFS(Out*); TIMEGRP DATA_GROUP OFFSET = IN 10 BEFORE CLK BEF; This restricts the constraint to registers B, E, and F.A BD C EFGOut1Out2Out3ResultData1Data2Data3InputAdvanced TABThe advanced tab allows theuser to specify constraints withTIMEGRPs.These buttons are used to createthe groups.These buttons are used to creategroups offset timespecs.These buttons are used to creategroup FROM: to timespecs. Thedialog box is the same for allthree; however, the defaultsettings change to make it easierfor the user.These buttons are used to createtime group exceptions.Time Group DialogTime Group Dialog allow theuser to sort nets by FFS,RAMS, LATCHES, and PADSto create TIMEGRPs.The group name.Filter net namesFilter resultsTime group membersPad To SetupAllows the user to createOFFSETs using pad groupsand register groups.The pad group nameThe clock net the offset isrelative toRegister group nameTiming Constraints (II) Using TIMEGRP, TNM, FROM:TO and other constraintsMulti-Cycle Delays Grouping by net nameUsing pattern matching on register’s output net names to create groups.TIMEGRP “DATAOBUS”= FFS(“DATA01”“DATA02”);TIMEGRP “MY_REG”= FFS(“MY_REG_1”“MY_REG_2”);TIMESPEC TS _MYBUS = FROM:DATA0BUS :TO:MY_REG :20;DATA0TS_MYBUSQDQDQDQDMY_REG_0MY_REG_2reg0reg1reg2reg3MY_REG_1CNT16MY_REG_3Time Group DialogTime Group Dialog allows theuser to sort nets by FFS,RAMS, LATCHES, and PADSto create TIMEGRPs.The group nameFilter net namesFilter resultsTime group membersMulti-Cycle Delays Grouping by Instance NameUsing INST to create groups -INST pattern matches on the symbol name…good for SynthesisINST CNT16/U1 TNM=CNT25;INST reg 0 TNM=MYREG ;TIMESPEC TS _MYBUS = FROM:CNT25:TO:MYREG :20;DATA0TS_MYBUSCNT16QDQDQDQDMY_REG_0MY_REG_1MY_REG_2MY_REG_3reg0reg1reg2reg3Time Name DialogTime Name Dialog sorts clockenable nets, clock nets and allnets. The user can also sortFFS, RAMS, LATCHES, andPADS by INST to createTNMs.The group nameFilter net namesTime group membersFilter resultsBasic Timing Constraints( using the FROM-TO Syntax)Constraint Editor allows the use of default keywords:TIMESPEC TS _C2S =FROM:FFS:TO:FFS:30;TIMESPEC TS_P2S =FROM:PADS:TO:FFS:25;TIMESPEC TS_P2P =FROM:PADS:TO:PADS:26;TIMESPEC TS_C2P =FROM:FFS:TO:PADS:9;TS_C2PTS_C2STS_P2SOUT1QDQDCLKTS_P2POUT2Slow ExceptionsSlow exceptions are FROM:TOs that define a different delay for portion of the design. The majority of the design has period.Preferred methodology; PAR and TRCE will execute faster.IN CLKOUTD Q D Q D Q60 nsExample 1: Using FROM:TO’s only --OK, but not best method FROM:flop1:TO:flop2:30FROM:flop2:TO:flop3:6030 nsIN CLKOUT30 nsD Q D Q D Q60 nsExample 2: Using PERIOD with a FROM:TO Slow Exception --BESTFROM:flop2:TO:flop3:60NET CLK PERIOD=30Slow Exceptions: Multi-Cycle Delays with Clock EnablesTNM=FASTTNM=FAST TNM=SLOWTimespecs applying to elements with more than one TNM will be resolved with a priority system…….discussed later.IN CLKCLK_ENOUTDQDQCEDQCEForward trace on the clock enable to create a slow exceptionNET “CLK_EN”TNM=SLOW ;NET “CLK”TNM = FAST ;TIMESPEC TS01=PERIOD FAST 30;TIMESPEC TS02=FROM:SLOW :TO:SLOW :TS01*2;60 ns30 nsTNM=FAST TNM=SLOWSpecific Delays going through Specific Logic (TPTHRU)Forces the path through specific logicThe TPTHRU attribute is attached to net / instance / macro in top blob.NET $3M17/ON_THE_WAY TPTHRU = ABC ;TIMESPEC TS_FIFOS =FROM:RAM_GRP:THRU:ABC :TO:FFS_GRP:25;FIFORAMMYFIFOQDQD QDMY_REG_0reg0reg1reg2TPTHRU=abcMY_REG_1MY_REG_2Constraining Between MultipleClock DomainsQDDQDQDQDefine clock groups—NET CLK_A TNM=A_GRP;—NET CLK_B TNM=B_GRP;Define timing constraints—TIMESPEC TS_CLKA=PERIOD A_GRP 20;—TIMESPEC TS_CLKB=PERIOD B_GRP TS_CLKA*2;—TIMESPEC TS_CLKA2B=FROM:A_GRP:TO:B_GRP:20;OUT1 CLK_ACLK_BControlling False Paths (TPTHRU) Design has bi-directional bus with sets of registers in different blocks.There is a false path from control registers through the TBUF to the status registers.NET DATA_BUS0TPTHRU = DATABUS;NET DATA_BUS1TPTHRU = DATABUS;TIMESPEC TS_TIG=FROM:FFS:THRU:DATABUS:TO:FFS:TIG;DATA_BUS(7:0)ControlRegisterStatusRegistersControl_Enable Status_EnableFROM:THRU:TOAllows the user to create FROM:TOor FROM:THRU:TO constraints fromthe following groups: FFS, RAMS,LATCHES, PADS, USER GROUPS.Default for slow/fast path exceptions.Default for multi-cycle paths.Default for false paths(FROM:TO:TIG)Ignoring Paths (TIG)If no TIMEPEC is selected, then the net is removed from all timing analysis NET CHIP_MODE TIG;If a TIMESPEC is selected, then the net is ignored for the specified timespec NET SLOW_SIG TIG=TS_01;Timing Constraint Priority (2)Within a particular source:—Highest Priority Timing ignores (TIG)FROM:THRU:TO specsSource and destination defined by userSource or destination defined by userSource and destination are pre-defined groupsFROM:TO specsSource and destination defined by userSource or destination defined by userSource and destination are pre-defined groupsPERIOD specs—Lowest Priority“Allpaths”type specs (.pcf only)—Note: offset does not override and cannot be overridden. This will be resolved for M2.1.Practical Design for Xilinx, Section 7,Placement and Other ConstraintsUsing LOC, Slew Rate, and other physical constraintsPin Location ConstraintsThe Ports Tab allows the user to specify the pin locations. The constraint editor does not verify if the location is valid -this is the users responsibility.Output Slew RateThe Ports Tab allows the user to specify slew rate for output pads. Select the I/O configuration options check box to enable this column, then right click to choose fast/slow.Prohibit Location Constraints“PROHIBIT”disallows the use of these sites within PAR:—I/O constraint based on net nameCONFIG PROHIBIT=P12;Editable Constraints TABDisplays all of the constraints read from an existing ucf file, and new constraints as they are created.Allows the user to delete or disable constraints before they are written to the ucf. This is done by selecting the constraint, then right click with the mouse.。

手把手课堂-Xilinx FPGA设计时序约束指南

手把手课堂:Xilinx FPGA 设计时序约束指南

作为赛灵思用户论坛的定期访客,我注意到新用户往往对时序收敛以

及如何使用时序约束来达到时序收敛感到困惑。

为帮助FPGA 设计新手实现时序收敛,让我们来深入了解时序约束以及如何利用时序约束实现FPGA 设计的最优结果。

何为时序约束?

为保证设计的成功,设计人员必须确保设计能在特定时限内完成指定任务。

要实现这个目的,我们可将时序约束应用于连线中从某FPGA 元件到FPGA 内部或FPGA 所在PCB 上后续元件输入的一条或多条路径。

在FPGA 设计中主要有四种类型的时序约束:PERIOD、OFFSET IN、OFFSET OUT 以及FROM: TO(多周期)约束。

PERIOD 约束与建组

每个同步设计要有至少一个PERIOD 约束(时钟周期规格),这是最基本的约束类型,指定了时钟周期及其占空比。

若设计中有不止一个时钟,则每

个时钟都有自己的PERIOD 约束。

PERIOD 约束决定了我们如何进行布线,来满足设计正常工作的时序要求。

为简化时序约束应用过程,常常可将具有类似属性的连线分组为一组总

线或一组控制线。

这样做有助于完成正确为设计约束定义优先级这一关键步骤。

设计约束优先次序排列

若设计有多重约束,则需进行优先次序排列。

一般来说,约束的一般性

越强,其优先级越低。

相反,约束的针对性越强,其优先级越高。

举例来说,

时钟网络上的某个一般性PERIOD 约束将被特定网络的具有更高优先级的。

FPGA全局时钟约束(Xilinx)

FF1

FF2

假设:

– – –

CLK 50-%占空比的CLK信号 BUFG INV 10ns的PERIOD约束 由于FF2时钟采用CLK的下降沿,因此两个触发器间路径的实际 约束为10ns的50% = 5ns

时钟输入抖动

时钟输入抖动是时钟不确定性的原因之一 时钟不确定性被从下面路径中减去

– –

PERIOD约束的建立路径 OFFSET IN约束的建立路径 PERIOD约束的保持路径 OFFSET IN约束的保持路径 OFFSET OUT约束路径

OFFSET约束还考虑到时钟输入抖动

–

时钟延迟

计算OFFSET约束时同时使用数据通道延迟和时钟传输延迟

– –

OFFSET IN = T_data_In - T_clk_In OFFSET OUT = T_data_Out + T_clk_Out

T_data_In In T_clk_In Clk OFFSET-IN T_clk_Out

– –

OFFSET IN: PADA 至 FLOP 和 PADB 至 RAM OFFSET OUT: LATCH 至OUT1, LATCH 至OUT2, 和RAM 至OUT1

PADA

FLOP D Q

LATCH D G Q

CLK BUFG PADB

RAM

OUT1

OUT2 PADC

要点

简介 全局约束 约束编辑器 总结

创建一条时序约束的过程包括两步

– –

全局约束使用缺省路径端点组

–

小测验

复习问题

一条全局约束可覆盖多条延迟路径 如果箭头所指的路径是约束路径,该电路中的约束路径的端 点是什么? 本电路中的所有寄存器有什么共同之处?

XilinxFPGA编程技巧之常用时序约束详解

Xilinx FPGA编程技巧之常用时序约束详解i.基本的约束方法为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。

最普遍的三种路径为: .输入路径(In put Path ),使用输入约束.寄存器到寄存器路径(Register-to-Register Path ),使用周期约束.输出路径(Output Path ),使用输出约束.具体的异常路径(Path specific exceptio ns ),使用虚假路径、多周期路径约束1.1. 输入约束In put Co nstrai ntOFFSET IN约束限定了输入数据和输入时钟边沿的关系。

1.1.1. 系统同步输入约束System Sy nchron ous In put在系统同步接口中,同一个系统时钟既传输数据也获取数据。

考虑到板子路径延时和时钟抖动,接口的操作频率不能太高。

1-1简化的系统同步输入SDR接口电路图1-2SDR系统同步输入时序上述时序的约束可写为:NET "SysCIk" TNM_NET = "SysCIk";TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;OFFSET = IN 5 ns VALID 5 ns BEFORE "SysClk";1.1.2. 源同步输入约束Source Syn chro nous In put在源同步接口中,时钟是在源设备中和数据一起产生并传输。

1-3简化的源同步输入DDR接口电路1-4DDR源同步输入时序上图的时序约束可写为:NET "SysCIk" TNM_NET = "SysCIk";TIMESPEC "TS_SysCIk" = PERIOD "SysCIk" 5 ns HIGH 50%;OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" RISING;OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" FALLING;1.2. 寄存器到寄存器约束Register-to-Register Constraint寄存器到寄存器约束往往指的是周期约束,周期约束的覆盖范围包括:.覆盖了时钟域的时序要求.覆盖了同步数据在内部寄存器之间的传输.分析一个单独的时钟域内的路径.分析相关时钟域间的所有路径.考虑不同时钟域间的所有频率、相位、不确定性差异1.2.1. 使用DLL, DCM, PLL, and MMCM 等时钟器件自动确定同步关系使用这一类时钟IP Core,只需指定它们的输入时钟约束,器件将自动的根据用户生成IP Core时指定的参数约束相关输出,不需用户手动干预。

Xilinx约束学习笔记(一)——约束方法学

Xilinx约束学习笔记(⼀)——约束⽅法学《Xilinx约束学习笔记》为⾃⼰阅读 Xilinx 官⽅ UG903 ⽂档后的学习笔记,⼤多数为翻译得来,⽅便⼤家学习。

1 约束⽅法学1.1 组织约束⽂件Xilinx 建议将时序约束和物理约束分开保存为两个不同的⽂件。

甚⾄可以将针对某⼀个模块的约束单独保存在⼀个⽂件中。

1.1.1 综合和实现可以使⽤不同的约束⽂件可以使⽤ USED_IN_SYNTHESIS 和 USED_IN_IMPLEMENTATION 属性指定约束⽂件是在综合或实现过程中使⽤。

注意:特别是IP、DCP这类使⽤OOC模式的模块,因为这些模块在综合过程中是⼀个⿊盒,当顶层约束指定的约束路径为⿊盒中的内容时,可能在综合过程中会报找不到⽬标的错误。

因此,最好的⽅法是将约束会为两个⽂件,⼀个综合⽤,⼀个实现时⽤。

在⼯程模式中可以使⽤如下代码指定约束⽂件使⽤时机。

set_property USED_IN_SYNTHESIS false [get_files wave_gen_pins.xdc]set_property USED_IN_IMPLEMENTATION true [get_files wave_gen_pins.xdc]⾮⼯程模式中,不需要如此设置。

因为什么时候使⽤约束⽂件,只和读取约束⽂件的时机相关。

如下:其中 wave_gen_timing.xdc 会在综合和实现过程中使⽤,⽽wave_gen_pins.xdc 只会在实现过程中使⽤。

read_verilog [glob src/*.v]read_xdc wave_gen_timing.xdcsynth_design -top wave_gen -part xc7k325tffg900-2read_xdc wave_gen_pins.xdcopt_designplace_designroute_design1.2 约束的顺序推荐约束顺序如下:## Timing Assertions Section# Primary clocks# Virtual clocks# Generated clocks# Clock Groups# Bus Skew constraints# Input and output delay constraints## Timing Exceptions Section# False Paths# Max Delay / Min Delay# Multicycle Paths# Case Analysis# Disable Timing## Physical Constraints Section# located anywhere in the file, preferably before or after the timing constraints# or stored in a separate constraint file1.3 创建综合约束Vivado 综合将设计中的 RTL 描述转换为⼯艺映射⽹表。

ise时钟约束写法

ise时钟约束写法

ISE (Integrated Software Environment) 是Xilinx公司的一款集成开发环境软件,用于FPGA设计。

在ISE中,时钟约束是指对时钟信号进行约束,以确保设计在时序上能够正确工作。

时钟约束的写法包括以下几个方面:

1. 周期约束,时钟的周期约束是指规定时钟信号的周期,以确保设计能够在指定的时钟周期内完成操作。

在ISE中,可以使用语法类似于“create_clock -period 10 [get_ports clk]”来指定时钟信号的周期为10个时钟周期。

2. 约束时钟延迟,除了周期约束外,还可以对时钟信号的延迟进行约束。

这可以通过语法类似于“set_clock_latency -max 2 [get_clocks clk]”来实现,其中“-max 2”表示最大延迟为2个时钟周期。

3. 时钟分配约束,在设计中可能存在多个时钟域,需要对时钟进行分配约束,以确保时序正确。

可以使用语法类似于

“create_clock -period 10 -name clk [get_ports clk]”来为特定时钟信号分配时钟域。

4. 时钟域约束,除了时钟分配约束外,还可以对时钟域进行约束,以确保时序正确。

可以使用语法类似于“derive_clocks -period 10 [get_pins {/clk}]”来为时钟域添加约束。

总之,在ISE中,时钟约束的写法需要遵循特定的语法规则,并且需要根据设计的实际情况进行合理的约束设置,以确保设计在时序上能够正确工作。

希望以上信息能够帮助你更好地理解时钟约束的写法。

xilinx官方论坛解释时序约束

Timing ConstraintsFollowing along the forum traffic, it has come to may attention that timing constraints are often a mystery to new users. In order to help those who have never had to constrain their timing, I offer the following part one, of five parts, on timing constraints.Some BasicsTiming constraints apply to nets or networks, the path or paths taken from one element to all of the inputs of subsequent elements. One can also call out a specific path that is part of a net or network.Every design should have at least one period constraint that specifies the clock and the duty cycle of the clock. A clock is always required for synchronous design, and so the period constraint is the most basic and is always a required constraint for any design. If there is more than one clock, each requires its own period constraint.The period constraint will define how all nets must be routed in order to meet the timing requirements for proper operation.A group may be defined to generically refer to many nets or paths of a selected set, such as a bus or control group.PriorityWhen it comes to having many constraints for a design the following applies: the more general the constraint, the lower its priority, and, conversely, the more specific a constraint, the higher the priority.For example, a period constraint on a clock net or network is very general and will be over-ruled by a from:to constraint on a specific net or network.The specific constraint for the from:to (or from:thru:to) is deemed more important than the more general constraint for any net within a clock domain.There is a timing specification interaction report (the .tsi report) that details how the constraints interact. Select this option in the timing analyzer for reporting if you have a set of constraints, and you need to know how they are interacting and which priorities have been set.One can override the assumed priorities and manually set the priority of any timing constraint. The use of the priority command allows setting a very low priority, such as 0, or even a negative priority, such as -10, which will be evaluated with an even higher priority than 0.Example 1The PERIOD constraint only covers nets from Synchronous Elements to Synchronous Elements, such as FFS to FFS, as shown in blue below:NET "clk20" TNM_NET = “tnm_clk20";TIMESPEC "TS_clk20" = PERIOD “tnm_clk20" 20 ns HIGH 50 %;A TIMEGRP (timing group) is created called tnm_clk20 which contains all of the downstream synchronous components that net clk20 drives. All of the paths between these synchronous elements are then constrained with the timing specification TS_clk20, which specifies a 20 ns requirement from synchronous element to synchronous element and a HIGH 50% (clk20 has a 50/50 duty cycle).Example 2FROM:TO constraints are used to define a requirement for paths that go between two groups.TIMESPEC TS_my_fromto = FROM my_from_grp TO my_to_grp 40 ns;tells the tools that you need to ensure that data makes it from the components in the timing group ‘my_from_grp’ to ‘my_to_grp’ in 40 ns. Timing Analyzer will still calculate the clock skew from source group to destination group, but at a lower priority (if the clocks are related). Predefined groups can be used, for example:TIMESPEC TS_F2F = FROM FFS TO FFS 40 ns;If we need leave out the time unit (ns, ps, etc…), then the tools presume ns:TIMESPEC TS_P2P = FROM PADS TO PADS 30;You can leave FROM or TO off of the constraint and make it more generic:TIMESPEC TS_2P = TO PADS 40;All of the FROM:TO constraints in the examples above would be of higher priority than the PERIOD constraint.TSI ReportThe TSI report is generated with the ‘-tsi design.tsi’ switch in the TRCE command line, or by specifying the option in the timing analyzer. If a user does not see a path under the correct constraint, this is the best place to start. This report will also make suggestions on ways toimprove constraints in the universal constraints file (UCF). This report will also notify the user of any paths that are constrained by multiple clock domains:Example 3Constraint Interaction Report=============================Constraint interactions for TS_clk0_1 = PERIOD TIMEGRP "clk0_1" TS_clk HIGH 50%;1 paths removed by TS_my_fromto = MAXDELAY FROM TIMEGRP "my_to_grp" TO TIMEGRP "FFS" 40 ns;Analysis of Example 3In other words, the FROM:TO constraint (just one) was applied ahead (higher priority) of the PERIOD constraint.Following along the forum traffic, it has come to my attention that timing constraints are often a mystery to new users. In order to help those who have never had to constrain their timing, I continue with part 2 (of 5) on timing constraints.Setup and HoldIn a practical synchronous digital system, the data must arrive before the clock edge that samples it. The minimum amount of time in which the data must arrive before the clock edge is called the setup time.As well as arriving before the clock edge, the data must persist for some finite amount of time at the clock edge. This is called hold time. Hold time may be negative, zero, or positive. When it is negative, the data goes away before the clock edge. When it is zero, the data persists until the clock edge. When it is positive, the data persists for some time after the clock edge.By design, in the FPGA fabric, for all speed grades, all hold times are either negative or zero. This simplifies the placement and routing, as the data only needs to arrive before the clock edge, and is allowed to change immediately following a clock edge. The value that the data exceeds the minimum setup time is known as slack. Slack should always be positive. If a report shows a negative slack, then the setup timing will be inadequate (data will arrive too late).The clock path itself has delay, or skew. Thus, to analyze the timing, the tools will calculate the arrival time of the data and the clock at the flip-flop of interest. ConstraintsIf you recall from last time, the period constraint defines the clock period for the synchronous elements of interest (the flip-flops). The timing analyzer verifies that all paths between synchronous elements meet the setup and hold timing for your design. A violation of a period constraint will appear in the timing report, and have a negative slack value. It will either be identified as violating a setup requirement or a hold requirement.If a setup requirement has been violated, then the data needs to arrive at the flip-flop sooner. To do so may require a faster path. If the place and route software cannot find a faster path, you do have the option of placing the path manually in the FPGA_Editor tool, but this is a tool of last resort. It is better to try to re-architect the circuit to meet the requirement. One way to do this is to place a flip-flop earlier in the path. This is known as pipe-lining, and will add latency to the signal, but it will also allow the value to be captured properly.If a hold requirement has been violated (the data went away before the clock edge arrived), then this is often an indication that you have a design problem (bad architecture). Values should only change on the clock edge, and not before. If an external value is changing before the clock edge, one needs to delay the clock edge (using a DCM or PLL) so that the data is now registered properly by the new delayed clock.An alternative is to use the Idelay element in the IOB to move the data to where the clock is valid.Data Valid WindowThe time from before the clock edge (setup) plus the time after the edge (hold) is known as the data valid window, or the time the data must be stable to be properly registered. If the data is not valid for at least this amount of time, then the results are indeterminate, or unknown.MetastabilityJust because the data was not valid for as long as required does not mean that the output of the flip-flop is metastable--metastable is different from indeterminate! An output could be 0 or 1, seemingly at random, if the timing is not met. Metastability means the edge was “almost” capable of capturing the state and the flip-flop output is in some intermediate state (not 1, not 0) for some time after the clockedge. Metastability cannot be prevented, as it is a fact of the physics of the circuits, if the clock edge and the data are almost perfectly “missed.”In a properly designed synchronous system there are no problems with metastability. Metastability is a problem when something is asynchronous, like pressing a key on a keyboard, or when two synchronous clocks are asynchronous to each other. When something is asynchronous, it needs to be synchronized.For how to deal with metastability, please consult:/class/ee183/handouts_spr2003/synchronization_pres.pdfNext time: Tprop, or offsets.Following along the forum traffic, it has come to may attention that timing constraints are often a mystery to new users. In order to help those who have never had to constrain their timing, I continue with part 3 (of 5 parts) on timing constraints.Tprop or OffsetThe time it takes to get a signal from point A to point B is called the propagation time. It is based on the speed of light through a medium. For example, a trace on a printed circuit board carries signals at around 6 to 7 picoseconds per millimeter. Finding this time can be done by running simulations or solving equations when you know the dielectric constant for the material and the geometry of the wiring traces. Inside the silicon device the signals behave in much the same way, but also may be delayed by going through active circuits (buffers, inverters, logic and interconnect).Often, you can also measure these times with the help of an oscilloscope. Propagation times generally do not vary much at all when the path has no active elements. If the path is in silicon, the strength of the transistors will cause the path delay to vary with both a maximum value and a minimum value. Timing needs to be met for both, obviously.In order to tell the tools when data arrives at a particular location, offset constraints are used.OFFSET_INThe OFFSET IN constraint defines the relationship of a clock and data as they enter the device:OFFSET = IN 2 ns VALID 16 ns BEFORE “clk20";This constraint tells the tools that data will be setup at PADs 2 ns before the clk20 rising edge, and that the data will remain valid for 16 ns after it arrives. This constraint only applies to PADs that go to registers that are clocked by clk20, or a derivative of clk20 (a derived constraint).OFFSET requires a PERIOD constraint on clk20, so that it understands the clocking structure. This following is also acceptable:OFFSET = IN 2 ns BEFORE “clk20";However, the above statement will not check the hold time because we do not know when the data goes away at the PIN of the FPGA. If the data will not be setup until 2 ns after the clock edge, then we use the following:OFFSET = IN -2 ns VALID 16 ns BEFORE “clk20"; # Do not use OFFSET IN AFTER(the text after the # is a comment)OFFSET_OUTThe OFFSET OUT constraint defines the amount time you need to ensure that data makes it out of the device after a clock transition at the input to the FPGA:OFFSET = OUT 3 ns AFTER “clk20";This constraint tells the tools that you need to ensure that data is at the output pin of the FPGA 3 ns after a clock transition at the input of the specified clock to the FPGA. This constraint only applies to PADs that are driven by registers that are clocked by clk20, or a derivative of clk20 (a derived constraint). OFFSET requires a PERIOD constraint on clk20, so that it understands the clocking structure. Hold times are not checked for OFFSET OUT.If we need the data 2 ns before the clock edge, then we use the following:OFFSET = OUT -2 ns AFTER “clk20"; # Do not use OFFSET OUT BEFORENext time: how to define and use groups and a ssign group names.Following along the forum traffic, it has come to may attention that timing constraints are often a mystery to new users. In order to help those who have never had to constrain their timing, I continue with part 4 (of 5 parts) on timing constraints.Groups and Group NamesA time group is a way to identify a constraint for a collection of paths or nets between synchronous elements. To add components to a time group, you would use:TNMTNM_NETorTIMEGRPPaths are constrained by defining groups, and then giving requirements between those groups. There are few constraints that do not require Time Groups, such as:NET MAXDELAYThe Maximum Delay (MAXDELAY) attribute defines the maximum allowable delay on a net.TNM – Timing NameTo add a component to a user defined group:[NET|INST|PIN] object_name TNM = predefined_group identifier;whereobject_name is the name of the element or signal to be groupedpredefined_group is an optional keywordidentifier can be any combination of letters, numbers, or underscoresDo not use reserved words such as FFS, LATCHES, and RAMS. This variable is case sensitive (TNM=abc ? TNM=ABC). TNM can be applied to any net, element pin, primitive, or macro.Components can be part of more than one group:my_ffs_group TNM can have the my_ff component in itmy_ffs_group2 TNM can also have the my_ff component in itTo create a group:NET CLOCK TNM=clk_group;Any Keyword element can be made into a group for timing purposes. In this example, the net CLOCK is traced forward to the flip-flops (FFS). These flip-flops are timing-named (TNM) with the name clk_group. clk_group can now be referenced by this TNM in TIMESPECs.One can create a group using an instance:INST macro1 TNM = LATCHES latchgroup;All LATCHES in the macro called macro1 will be in a group called latchgroup.INST mymac TNM = RAMS memories;All RAMS in the macro called mymac will be in a group called memories.INST tester TNM = coverall;All PADS, LATCHES, RAMS, and FFS in the macro called tester will be in a group called coverall. For a complete listing of the predefined groups, search the applicable Constraints Guide for ‘predefined group.’SuggestionIn general, the fewer constraints, the better. Complex constraints can often cause more problems than they solve. As well, some paths or nets may be non-critical, and you may wish to declare that no constraints should be applied to these nets.TIG (timing ignore) constraints are used to remove things we don’t care about, or to remove constraints from a ‘false path.’NET "rst" TIG;This tells the tools that you do not need to constrain this path. It is important so that the tools do not work to meet timing on paths that you do not care about. Setting timing ignore on such paths will also reduce run times, and may improve the quality of the timing on the paths you do care about.You can also use TIG with FROM:TO constraints:TIMESPEC TS_my_fromto = FROM "my_to_grp" TO "FFS" TIG;Next time, the last part, 5 of 5, will discuss timing on double data rate (DDR) interfaces.Following along the forum traffic, it has come to may attention that timing constraints are often a mystery to new users. In order to help those who have never had to constrain their timing, I conclude with part 5 on timing constraints.Dual Data Rate (DDR)DDR interfacing uses both the rising and falling edges of the clock in a source-synchronous interface to capture or transfer twice as much data per clock cycle.Arriving DDRTo properly constrain data arriving at the device, you must first constrain the clock being used to capture the data, and also constrain the arrival of the data for both the rising and falling edges of the clock.For this example, the complete OFFSET IN specification with associated PERIOD constraint is:NET "SysCLk" TNM_NET = "SysClk";TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;OFFSET = IN 1.25 ns V ALID 2.5 ns BEFORE "SysClk" RISING;OFFSET = IN 1.25 ns V ALID 2.5 ns BEFORE "SysClk" FALLING;This global constraint covers both the data bits of the bus, as in each clock period two bits are captured: ?data1 and ?data2.Leaving DDRSimilar to specifying when the data arrives is specifying the output of DDR data.For this example, the complete OFFSET OUT specification for both the rising and falling clock edges is based on the clock supplied to the DDR register:NET “CLkIn” TNM_NET = “ClkIn”;OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” RISING;OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” FALLING;Note that the complete constraint format is OFFSET=OUT <value>, and this determines the maximum time from the rising clock edge at the input clock port until the data first becomes valid at the data output port of the FPGA device.When <value> is omitted from the OFFSET OUT constraint, as in the example above, the constraint becomes a report-only specification which reports the skew of the output bus. The REFERENCE_PIN keyword defines the regenerated output clock as the reference point against which the skew of the output data pins is reported.Of course, do not forget that the output clock also needs a period constraint (it was not needed for the specification of the output timing, but is required for getting the data to the DDR output register).SummaryIn this series we have provided a snapshot of common constraints and how to use them. Depending on how you liked this series, I can provide further articles on timing, as there is a lot more to say about the reports that can be generated by the timing analyzer.。

vivado for语句

vivado for语句"Vivado for语句"是指在Xilinx Vivado设计套件中使用的一种循环语句。

该语句可用于在嵌入式系统设计和FPGA编程中对块代码进行重复执行。

在本文中,我将逐步解释Vivado for语句的基本语法、用法和示例,并探讨其在设计和开发过程中的重要性。

第一步:了解Vivado for语句的基本语法和用法Vivado for语句是一种结构化的循环语句,可用于指定代码块的重复执行次数。

它的基本语法如下:for (initialization; condition; increment) {code block to be repeated}其中:- initialization:循环变量初始化的语句,用于设置循环的初始条件。

- condition:循环的终止条件。

只要条件为真,代码块就会被执行,否则循环将被终止。

- increment:循环变量的更新语句,用于在每次循环迭代结束后更新循环变量的值。

第二步:使用Vivado for语句的示例为了更好地理解Vivado for语句的用法,下面是一个示例:c++for (int i = 0; i < 5; i++) {code block to be repeated}在这个示例中,我们使用循环变量i初始化为0,条件i < 5表示只要i的值小于5,代码块就会重复执行。

在每次循环迭代结束后,i的值会自动递增1。

代码块内的内容将被重复执行5次。

第三步:理解Vivado for语句的重要性Vivado for语句在嵌入式系统设计和FPGA编程中具有重要的作用。

下面是一些说明:1. 提高代码的可读性和可维护性:使用for语句可以更清晰地表达对代码块的重复操作。

不再需要手动编写多个重复的语句,因此可以极大地提高代码的可读性和可维护性。

2. 优化资源利用:使用for语句可以有效地利用FPGA硬件的资源。

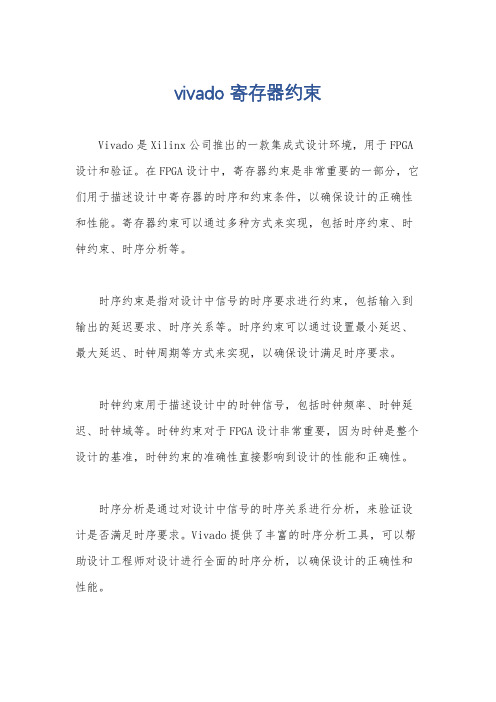

vivado 寄存器约束

vivado 寄存器约束

Vivado是Xilinx公司推出的一款集成式设计环境,用于FPGA 设计和验证。

在FPGA设计中,寄存器约束是非常重要的一部分,它们用于描述设计中寄存器的时序和约束条件,以确保设计的正确性和性能。

寄存器约束可以通过多种方式来实现,包括时序约束、时钟约束、时序分析等。

时序约束是指对设计中信号的时序要求进行约束,包括输入到输出的延迟要求、时序关系等。

时序约束可以通过设置最小延迟、最大延迟、时钟周期等方式来实现,以确保设计满足时序要求。

时钟约束用于描述设计中的时钟信号,包括时钟频率、时钟延迟、时钟域等。

时钟约束对于FPGA设计非常重要,因为时钟是整个设计的基准,时钟约束的准确性直接影响到设计的性能和正确性。

时序分析是通过对设计中信号的时序关系进行分析,来验证设计是否满足时序要求。

Vivado提供了丰富的时序分析工具,可以帮助设计工程师对设计进行全面的时序分析,以确保设计的正确性和性能。

除了以上提到的内容,寄存器约束还涉及到时钟域的划分、时序路径的优化、时序约束的调整等方面。

在实际的FPGA设计中,合理的寄存器约束可以帮助设计工程师充分发挥FPGA的性能优势,提高设计的稳定性和可靠性。

总之,寄存器约束在Vivado中扮演着非常重要的角色,它涉及到设计的时序要求、时钟约束、时序分析等多个方面,合理的寄存器约束可以帮助设计工程师确保设计的正确性和性能,是FPGA设计中不可或缺的一部分。

XILINX语法约束举例说明

38.

59

异步时钟域

设置举例

DATAPATHONLY

NET "CLKA" TNM_NET = FFS "GRP_A";

建立以网络CLKA驱动的寄存器时序分组GRP_A。

5.

10

TIMESPEC/FROM TO

TIMESPEC "TS01" = FROM BRAMS_PORTA TO BRAMS_PORTB(gork*);

时序约束TS01规定所有符合下列所有条件的路径:1)从BRAMS_PORTA端口输出;2)从BRAMS_PORTB端口输入,并且BRAMS_PORTB端口的输出需要驱动与gork*相匹配的信号。

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "sysClk" FALLING;

34.

57

周期约束

NET "ClockName" TNM_NET = "TNM_NET_Name";

建立以网络ClockName驱动的约束组TNM_NET_Name。

TIMESPEC "TS_name"= PERIOD "TNM_NET_Name"PeriodValueHIGH HighValue %;

17.

29

Verilog

always@(current_state or reset)

begin (* parallel_case *) (* full_case *)

Xilinx约束学习笔记(二)——定义时钟

Xilinx约束学习笔记(⼆)——定义时钟2. 定义时钟2.1 关于时钟为了获得最佳精度路径覆盖信息,必须正确定义时钟。

时钟要定义在时钟树的根 pin 或 port 上,称为 source point。

时钟的边缘应该由周期和波形进⾏组合描述。

周期使⽤纳秒做为单位进⾏定义。

它对应于波形重复的时间。

波形是⼀系列的上升沿和下降沿绝对时间列表,单位为纳秒,并且所有时间在⼀个时钟周期内。

列表必须包含偶数个值。

第⼀个值始终对应于第⼀个上升边缘。

如果没有指定波形,波形的默认占空⽐为 50%,相移为 0。

2.1.1 传播时钟周期和波形属性只展现出了时钟的理想特性。

当时钟进⼊ FPGA 并通过时钟树传播时,时钟边沿被延缓,并受噪声和硬件⾏为引影响。

这些特性称为时钟⽹络延迟和时钟不确定性。

时钟的不确定性包括:时钟抖动(clock jitter)相位错误⽤户指定添加的不确定性默认情况下,Vivado 在做时序分析时,始终将时钟视为传播时钟,即⾮理想时钟,以此提供准确的余量值,其中包括时钟树插⼊延迟和不确定性。

2.1.2 专⽤硬件资源FPGA 有⼤量专⽤的时钟管脚,这个管脚可以专门⽤来做时钟的输⼊。

FPGA 内部包含有 MMCM、PLL 和 BUR 之类的时钟资源。

2.2 基准时钟(Primary Clock)基准时钟是通过 FPGA 输⼊端⼝或千兆收发器输出引脚(例如,恢复时钟)进⼊设计的时钟。

基准时钟只能通过 create_clock 指令进⾏定义。

(为什么是千兆收发器?下⾯的话应该可以解释,7 系列的 GT 恢复时钟不能⾃动推导,必须⼿动定义。

⽽ US 和 USP 系列的可以⾃动推导,不需要⼈为定义)Primary clocks must be defined on a gigabit transceiver output only for Xilinx® 7 series FPGAs. For UltraScale and UltraScale+™ devices, the timer automatically derives clocks on the GT output ports.基准时钟必须附加到⽹表对象。

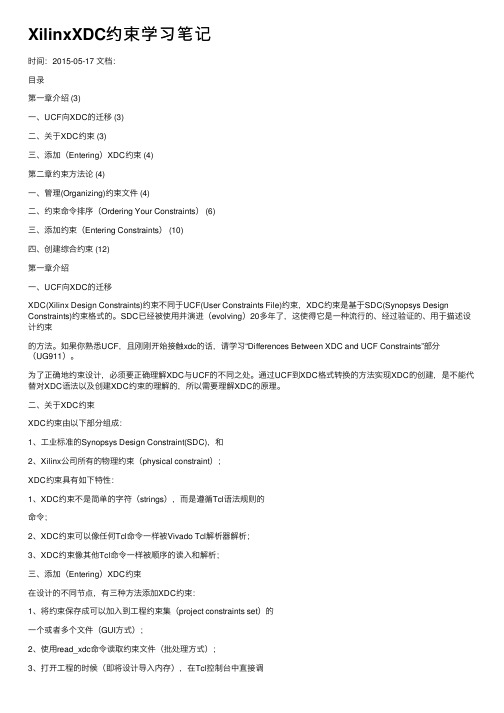

XilinxXDC约束学习笔记

XilinxXDC约束学习笔记时间:2015-05-17 ⽂档:⽬录第⼀章介绍 (3)⼀、UCF向XDC的迁移 (3)⼆、关于XDC约束 (3)三、添加(Entering)XDC约束 (4)第⼆章约束⽅法论 (4)⼀、管理(Organizing)约束⽂件 (4)⼆、约束命令排序(Ordering Your Constraints) (6)三、添加约束(Entering Constraints) (10)四、创建综合约束 (12)第⼀章介绍⼀、UCF向XDC的迁移XDC(Xilinx Design Constraints)约束不同于UCF(User Constraints File)约束,XDC约束是基于SDC(Synopsys Design Constraints)约束格式的。

SDC已经被使⽤并演进(evolving)20多年了,这使得它是⼀种流⾏的、经过验证的、⽤于描述设计约束的⽅法。

如果你熟悉UCF,且刚刚开始接触xdc的话,请学习“Differences Between XDC and UCF Constraints”部分(UG911)。

为了正确地约束设计,必须要正确理解XDC与UCF的不同之处。

通过UCF到XDC格式转换的⽅法实现XDC的创建,是不能代替对XDC语法以及创建XDC约束的理解的,所以需要理解XDC的原理。

⼆、关于XDC约束XDC约束由以下部分组成:1、⼯业标准的Synopsys Design Constraint(SDC),和2、Xilinx公司所有的物理约束(physical constraint);XDC约束具有如下特性:1、XDC约束不是简单的字符(strings),⽽是遵循Tcl语法规则的命令;2、XDC约束可以像任何Tcl命令⼀样被Vivado Tcl解析器解析;3、XDC约束像其他Tcl命令⼀样被顺序的读⼊和解析;三、添加(Entering)XDC约束在设计的不同节点,有三种⽅法添加XDC约束:1、将约束保存成可以加⼊到⼯程约束集(project constraints set)的⼀个或者多个⽂件(GUI⽅式);2、使⽤read_xdc命令读取约束⽂件(批处理⽅式);3、打开⼯程的时候(即将设计导⼊内存),在Tcl控制台中直接调⽤约束命令(命令⾏⽅式);第⼆章约束⽅法论这⼀章将讨论推荐地添加约束的流程(Constraints Entry Flow)。

第九章 XILINX FPGA设计技术1-时序约束

PADA

FLOP D Q LATCH D G Q

CLK BUFG PADB

RAM

OUT1

OUT2 PADC

提纲

简介 全局约束 约束编辑器 小结

提纲

简介 全局约束 约束编辑器 小结

问题与回顾

给定系统框图如下,在约束编辑器中如何编辑才能使系统工 作在100MHz? -假定设备之间没有时钟延迟与抖动

Upstream Device Downstream Device 5 ns

4 ns

答案

给定系统框图如下,在约束编辑器中如何编辑才能使系统工 作在100MHz?

RAM D

OUT2

偏移约束

偏移约束覆盖的路径包括:

输入 pads 到同步单元 (OFFSET IN) 同步单元到输出 pads (OFFSET OUT) OFFSET IN

ADATA

CLK BUFG

FLOP D Q FLOP D Q FLOP D Q FLOP D Q FLOP D Q

OFFSET OUT

执行约束编辑器

在项目源文件窗口上展开 User Constraints 双击 Create Timing Constraints

进入周期和Pad-to-Pad 约束

通过全局Tab进入周期 和 Pad-to-Pad 约束 双击这里来建立周期 约束 全局Pad-to-Pad 约束 约束可以通过选择 <Delete>来删除

Upstream Device 4 ns

Downstream Device

XILINX 时序约束使用指南中文翻译

XILINX时序约束使用指南笔记(UG612)第一章时序约束介绍第二章时序约束方法第三章时序约束原则第四章在XST中指定时序约束第五章在Synplify中指定时序约束方法第六章时序约束分析第一章时序约束介绍基本的时序约束包括:“PERIOD Constraints”“OFFSET Constraints”“FROM:TO(Multi-Cycle)约束”第二章时序约束方法1,简介:2,基本的约束方法根据覆盖的路径不同,时序要求变成一些不同的全局约束。

最普通的路径类型包括:1,输入路径2,同步元件到同步元件路径3,指定路径4,输出路径XILINX的时序约束与每一种全局约束类型都有关。

最有效的方法就是一开始就指定全局约束然后再加上指定路径的约束。

在很多案例中,只要全局约束就可满足需求。

FPGA器件执行工具都是由指定的时序要求驱动的。

如果时序约束过头的话,就会导致内存使用增加,工具运行时间增加。

更重要的是,过约束还会导致性能下降。

因此,推荐使用实际设计要求的约束值。

3,输入时序约束输入时序约束包括2种“系统同步输入”“源同步输入”输入时钟约束覆盖了输入数据的FPGA外部引脚到获取此数据的寄存器之间的路径。

输入时钟约束经常用”OFFSET IN”约束。

指定输入时钟要求的最好方法,取决于接口的类型(源/系统同步)和接口是SDR还是DDR。

OFFSET IN定义了数据和在FPGA引脚抓取此数据的时钟沿之间的关系。

在分析OFFSET IN 约束时,时序分析工具自动将影响时钟和数据延迟的因素考虑进去。

这些因素包括:时钟的频率和相位转换时钟的不确定数据延迟调整除了自动调整,还可以在与接口时钟相关的”PERIOD”约束中另外增加时钟不确定。

关于增加”INPUT_JITTER”的更多信息,参见第三章的”PERIOD Constraints”。

“OFFSET IN”与单输入时钟有关,默认情况下,OFFSET IN约束覆盖了从输入pad到内部同步元件之间的所有路径。

xdc约束文件语法

xdc约束文件语法

XDC,全称Xilinx Design Constraints,是用于对FPGA设计进行约束和控制的一种常用约束文件类型。

其基本语法主要可以分为三大类:时钟约束、I/O约束以及时序例外约束。

-对于时钟约束,可以通过set_property命令设置属性值,例如设置时钟频率、IO标准等。

在设计中,根据时钟结构和设计要求来创建合适的时钟约束是非常重要的。

-I/O约束和时序例外约束也是XDC约束文件中的重要部分,主要用于规定输入输出端口的标准和处理特殊情况下的时序问题。

值得一提的是,尽管XDC是Xilinx的专有格式,但其基础语法来源于业界统一的约束规范SDC (Synopsys Design Constraints),最早由Synopsys公司提出。

这使得XDC具有很多优势,比如统一了前后端约束格式,便于管理;可以像命令一样实时录入并执行;允许增量设置约束,加速调试效率;覆盖率高,可扩展性好,效率高;业界统一,兼容性好,可移植性强。

赛灵思(Xilinx)FPGA 设计约束的分类

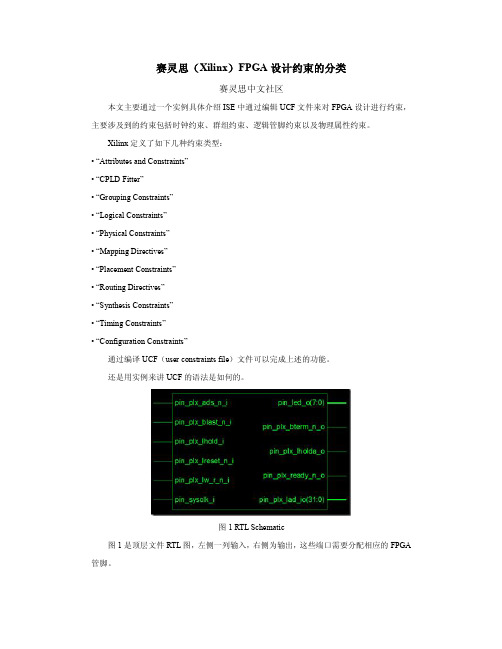

赛灵思(Xilinx)FPGA设计约束的分类赛灵思中文社区本文主要通过一个实例具体介绍ISE中通过编辑UCF文件来对FPGA设计进行约束,主要涉及到的约束包括时钟约束、群组约束、逻辑管脚约束以及物理属性约束。

Xilinx定义了如下几种约束类型:•“Attributes and Constraints”•“CPLD Fitter”•“Grouping Constraints”•“Logical Constraints”•“Physical Constraints”•“Mapping Directives”•“Placement Constraints”•“Routing Directives”•“Synthesis Constraints”•“Timing Constraints”•“Configuration Constraints”通过编译UCF(user constraints file)文件可以完成上述的功能。

还是用实例来讲UCF的语法是如何的。

图1 RTL Schematic图1是顶层文件RTL图,左侧一列输入,右侧为输出,这些端口需要分配相应的FPGA 管脚。

表1 UCF example对上面的UCF文件进行一些注释该UCF文件主要是完成了管脚的约束、时钟的约束,以及组的约束。

第一、二行:主要定义了时钟以及对应的物理管脚。

第一行,端口pin_sysclk_i 分配到FPGA管脚AD12,并放到了pin_sysclk_i group中。

那如何得知是AD12的管脚呢,请看图2,FPGA管脚AD12是一个66MHz的外部时钟。

FPGA的开发板肯定有电路原理图供你分配外部管脚。

图2电路原理图图2,电路原理图第二行:时钟说明:周期15ns,占空比50%。

关键词TIMESPEC(Timing Specifications),即时钟说明。

一般的语法是:TIMESPEC "TSidentifier"=PERIOD "timegroup_name" value [units];其中TSidentifier用来指定TS(时钟说明)的唯一的名称。

约束的作用

约束的作用有些人不知道何时该添加约束,何时不需要添加?有些人认为低速设计不需要时序约束?关于这些问题,希望下面关于约束作用的论述能够有所帮助!附加约束的基本作用有3:(1)提高设计的工作频率对很多数字电路设计来说,提高工作频率非常重要,因为高工作频率意味着高处理能力。

通过附加约束可以控制逻辑的综合、映射、布局和布线,以减小逻辑和布线延时,从而提高工作频率。

(2)获得正确的时序分析报告几乎所有的FPGA设计平台都包含静态时序分析工具,利用这类工具可以获得映射或布局布线后的时序分析报告,从而对设计的性能做出评估。

静态时序分析工具以约束作为判断时序是否满足设计要求的标准,因此要求设计者正确输入约束,以便静态时序分析工具输出正确的时序分析报告。

(3)指定FPGA/CPLD引脚位置与电气标准FPGA/CPLD的可编程特性使电路板设计加工和FPGA/CPLD设计可以同时进行,而不必等FPGA/CPLD引脚位置完全确定,从而节省了系统开发时间。

这样,电路板加工完成后,设计者要根据电路板的走线对FPGA/CPLD 加上引脚位置约束,使FPGA/CPLD与电路板正确连接。

另外通过约束还可以指定IO引脚所支持的接口标准和其他电气特性。

为了满足日新月异的通信发展,Xilinx新型FPGA/CPLD可以通过IO引脚约束设置支持诸如AGP、BLVDS、CTT、GTL、GTLP、HSTL、LDT、LVCMOS、LVDCI、LVDS、LVPECL、LVDSEXT、LVTTL、PCI、PCIX、SSTL、ULVDS等丰富的IO接口标准时序约束的概念和基本策略!时序约束主要包括周期约束(FFS到FFS,即触发器到触发器)和偏移约束(IPAD到FFS、FFS到OPAD)以及静态路径约束(IPAD到OPAD)等3种。

通过附加约束条件可以使综合布线工具调整映射和布局布线过程,使设计达到时序要求。

例如用OFFSET_IN_BEFORE约束可以告诉综合布线工具输入信号在时钟之前什么时候准备好,综合布线工具就可以根据这个约束调整与IPAD相连的Logic Circuitry的综合实现过程,使结果满足FFS的建立时间要求。

FPGA时钟约束技巧

XDC约束技巧之时钟篇Xilinx©的新一代设计套件Vivado中引入了全新的约束文件XDC,在很多规则和技巧上都跟上一代产品ISE中支持的UCF大不相同,给使用者带来许多额外挑战。

Xilinx工具专家告诉你,其实用好XDC很容易,只需掌握几点核心技巧,并且时刻牢记:XDC的语法其实就是Tcl语言。

XDC的优势XDC是Xilinx Design Constraints的简写,但其基础语法来源于业界统一的约束规范SDC(最早由Synopsys公司提出,故名Synopsys Design Constraints)。

所以SDC、XDC跟Vivado Tcl的关系如下图所示。

XDC的主要优势包括:1.统一了前后端约束格式,便于管理;2.可以像命令一样实时录入并执行;3.允许增量设置约束,加速调试效率;4.覆盖率高,可扩展性好,效率高;5.业界统一,兼容性好,可移植性强;XDC在本质上就是Tcl语言,但其仅支持基本的Tcl语法如变量、列表和运算符等等,对其它复杂的循环以及文件I/O等语法可以通过在Vivado中source一个Tcl文件的方式来补充。

(对Tcl话题感兴趣的读者可以参考作者的另一篇文章《Tcl在Vivado中的应用》)XDC与UCF的最主要区别有两点:1.XDC可以像UCF一样作为一个整体文件被工具读入,也可以在实现过程中被当作一个个单独的命令直接执行。

这就决定了XDC也具有Tcl命令的特点,即后面输入的约束在有冲突的情况下会覆盖之前输入的约束(时序例外的优先级会在下节详述)。

另外,不同于UCF是全部读入再处理的方式,在XDC中,约束是读一条执行一条,所以先后顺序很重要,例如要设置IO约束之前,相对应的clock一定要先创建好。

2.UCF是完全以FPGA的视角看问题,所以缺省认为所有的时钟之间除非预先声明是同步的,否则就视作异步而不做跨时钟域时序分析;XDC则恰恰相反,ASIC世界的血缘背景决定了在其中,所有的时钟缺省视作全同步,在没有时序例外的情况下,工具会主动分析每一条跨时钟域的路径。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

10

INST/TNM

INST "Y" TNM = BRAMS_PORTB groupC;

时序分组groupC包含所有实例Y下的BRAMS_PORTB的端口。

9.

10

INST/TNM

INST "Y" TNM = BRAMS_PORTA( doa* ) groupD;

时序分组groupD包含所有符合下列所有条件的路径:1)属于实例Y下的BRAMS_PORTA的端口;2)BRAMS_PORTA至少需要驱动1个与doa*匹配的信号。

10.

10

TIMEGRP

TIMEGRP "groupE" = BRAMS_PORTA;

时序分组groupE包含所有双端口RAM单元中的A端口。相当于BRAMS_PORTA ( * )

11.

10

TIMEGRP

TIMEGRP "groupF" = BRAMS_PORTB( mem/dob* );

时序分组groupF包含所有双端口RAM单元中的,输出端驱动信号中包含mem/dob*信号的B端口

28.

53

蒋实例myInst放置在引脚P53,IO标准为LVPECL33,摆率设置为高速

27.

53

OFFSETIN/VALID/

BEFORE

OFFSET = IN value1VALID value2BEFORE clock;

全局约束,信号应在时钟clock之前value1时间有效,并且需要保持value2时间。

12.

10

名字限定语法

predefined group (name_qualifier [ name_qualifier ])

预定义组名字限定语法。其中name_qualifier是包含全部层级的,并由相应原语驱动的网络。

13.

22

NET/TNM_NET

NET "netname" TNM_NET=[predefined_group ] identifier;

XILINX语法约束举例说明

序号

页码

关键字

举例及描述

1.

10

TIMESPEC/FROM TO

TIMESPEC "TS01"=FROM FFS TO FFS 30;

时序约束TS01规定从触发器到触发器的最大时间为30ns

2.

10

TIMESPEC/FROM TO

TIMESPEC "TS02"=FROM LATCHES TO LATCHES 25;

14.

29

Verilog

(*attribute_name*)

默认值为1。与(*attribute_name="1"*)意义相同。

15.

29

Verilog

(* clock_buffer = "IBUFG" *) input CLK;

16.

29

Verilog

(* INIT = "0000" *) reg [3:0] d_out;

17.

29

Verilog

always@(current_state or reset)

begin (* parallel_case *) (* full_case *)

case (current_state)

18.

30

Verilog

(* mult_style = "pipe_lut" *) MULT my_mult (a, b, c);

19.

32

疑问

NET "$SIG_0 MAXDELAY" = 10;

NET "$SIG_1 MAXDELAY" = 12 ns;

疑问:上面是否应将"$SIG_0 MAXDELAY"改为"$SIG_0 "MAXDELAY

20.

33

EXCEPT

TIMEGRP "input_pads"=PADS EXCEPT output_pads;

时序分组input_pads是除output_pads分组外的所有引脚。

21.

33

保留字

NET net OFFSET=IN 20 BEFORE CLOCK;错误

NET "net" OFFSET=IN 20 BEFORE CLOCK;正确

NET "$SIG_0" OFFSET=IN 20 BEFORE CLOCK;正确

NET "~OUTSIG1" OFFSET=IN 20 BEFORE CLOCK;正确

22.

33

通配符

NET "*AT?" FAST;

将倒数第3、2个字符为AT的所有网络设置为高速属性。

23.

33

通配符

INST "$1I3*/ROM2" INIT=5555;

将指定ROM的初始值设置为16进制的5555。

时序约束TS02规定从锁存器到锁存器的最大时间为25ns

3.

10

TIMESPEC/FROM TO

TIMESPEC "TS03"=FROM PADS TO RAMS 70;

时序约束TS03规定从引脚到RAMS的最大时间为70ns

4.

10

TIMESPEC/FROM TO

TIMESPEC "TS04"=FROM FFS TO PADS 55;

6.

10

NET/TNM_NET

NET "X" TNM_NET = BRAMS_PORTA groupA;

时序分组groupA包含所有由网络X驱动的BRAMS_PORTA端口路径。

7.

10

NET/TNM_NET

NET "X" TNM_NET = BRAMS_PORTB( dob* ) groupB;

时序分组groupA包含所有符合下列所有条件的BRAMS_PORTB路径:1)由网络X驱动的BRAMS_PORTB端口;2)BRAMS_PORTB至少需要驱动1个与dob*匹配的信号。

24.

33

通配符

INST "/loads_of_logic/*" LOC=SLICE_X*Y8;

25.

34

Hierarchy

UCF Design Hierarchy

UCF设计的层举例

26.

35

多重约束

INST myInst LOC = P53 | IOSTANDARD = LVPECL33 | SLEW = FAST;

时序约束TS04规定从触发器到引脚的最大时间为55ns

5.

10

TIMESPEC/FROM TO

TIMESPEC "TS01" = FROM BRAMS_PORTA TO BRAMS_PORTB(gork*);

时序约束TS01规定所有符合下列所有条件的路径:1)从BRAMS_PORTA端口输出;2)从BRAMS_PORTB端口输入,并且BRAMS_PORTB端口的输出需要驱动与gork*相匹配的信号。